Page 1

SPT8100

16-BIT, 5 MSPS CMOS A/D CONVERTER

FEATURES

• 16-bit, 5 MSPS CMOS analog-to-digital converter

• On-chip PGA: gain range from 0 to 20 dB in seven

selectable settings:

0 dB, +3 dB, +6 dB, +12 dB, +15 dB, +18 dB, +20 dB

• DNL: ±0.5 LSB, INL: ±1.25 LSB

• SFDR: 94 dB @ ƒIN = 900 kHz, –8.1 dBFS

• Internal sample-and-hold and voltage reference

• Power dissipation: 465 mW at 5 MSPS; 230 mW at

2.5 MSPS

• +5 V analog supply and +3.3 to +5.25 V digital output

supply

• 44-lead LQFP plastic package.

GENERAL DESCRIPTION

The SPT8100 is a high performance, 16-bit analog-to-digital

converter that operates at a sample rate of up to 5 MSPS.

Excellent dynamic performance and high linearity is

achieved by a digitally calibrated pipelined architecture fabricated in CMOS process technology.

A low-noise programmable gain amplifier (PGA) is also incorporated on chip. The PGA is digitally programmable in

seven selected settings over a 0 to +20 dB range. The

APPLICATIONS

• Data acquisition systems

• IR imaging

• Scanners and digital copiers

• High-end CCD cameras

• Medical imaging

• Wireless communications

• Lab and test equipment

• Automatic test equipment

SPT8100 also features an on-chip internal sample-and-hold

and internal reference for minimal external circuitry.

It operates from a single +5 V supply. Total power dissipation, including internal reference, is 465 mW. A separate

digital output supply pin is provided for +3.3 V or 5 V logic

output levels. The SPT8100 is available in a 44-lead LQFP

package over the industrial temperature range of –40 °C to

+85 °C.

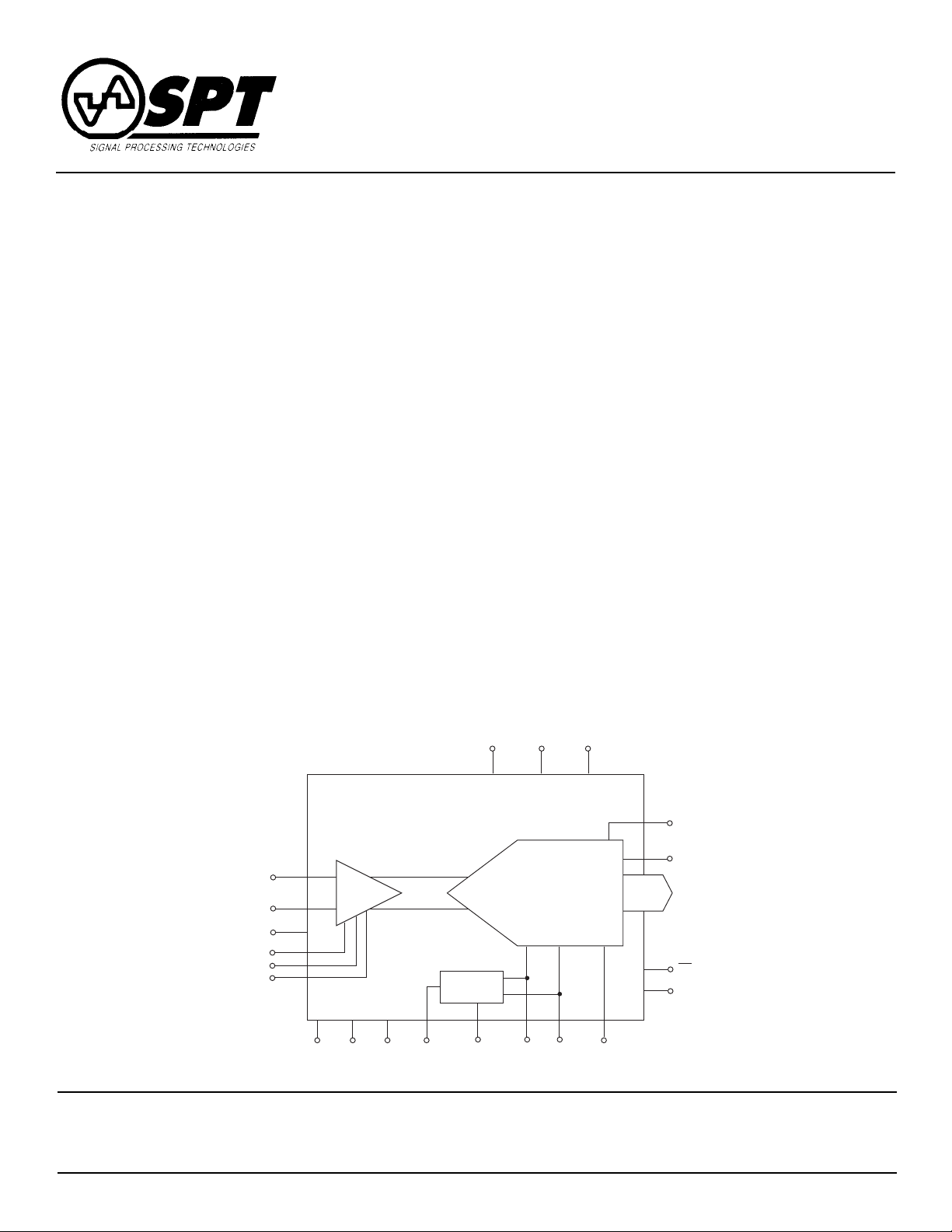

BLOCK DIAGRAM

Signal Processing Technologies, Inc.

Phone: (719) 528-2300 FAX: (719) 528-2370 Website: http://www.spt.com E-Mail: sales@spt.com

V

IN

V

V

CM

GS2 – GS0

(Gain Set)

AV

+5V

Low-Noise

PGA

+

–

IN

VREF

AGND

BIAS

OGNDDGND

(Ext Bias

Capacitor)

BIAS

C

(Ext Bias

Resistor)

DV

DD

16-bit, 5 MSPS ADC

V

R

RTVRB

+5V

OV

DD

DD

+3/5 V

16-bits

CLK

4755 Forge Road, Colorado Springs, Colorado 80907, USA

OE (Output Enable)

OVR (Over-Range)

D15 – D0

(Data Outputs)

RS (Reset)

RDY (Ready)

Page 2

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

DD

Output

Digital Outputs ......................................................10 mA

Temperature

Operating Temperature ............................. –40 to +85 °C

Junction Temperature ........................................+175 °C

Lead Temperature (soldering 10 seconds) ........ +300 °C

Storage Temperature ..............................–65 to +150 °C

Supply Voltages

AVDD........................................................................+6 V

DVDD........................................................................+6 V

OVDD........................................................................+6 V

Input Voltages

Analog Input................................... –0.5 V to VDD +0.5 V

CLK Input..................................................................V

AV

– DVDD.....................................................±100 mV

DD

Delta between AGND, DGND, and OGND .......±100 mV

Note 1: Operation at any Absolute Maximum Rating is not implied. See Electrical Specifications for proper nominal applied conditions

in typical applications.

ELECTRICAL SPECIFICATIONS

TA=T

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Resolution 16 Bits

DC Accuracy

MIN

to T

, AVDD=DVDD=+5.0 V, OVDD= 3.3 V, ƒS=5 MSPS, 2.5 VPP input span, R

MAX

=1.43 kΩ, unless otherwise specified.

EXT

TEST TEST SPT8100

Integral Nonlinearity V ±1.25 LSB

Differential Nonlinearity V ±0.5 LSB

Gain Error

Offset Error

1

2

VI –7.5 +7.5 %FSR

V –5 +5 %FSR

Analog Input (into PGA)

Differential Input Voltage Range

+, VIN–V5V

V

IN

PP

Input Capacitance IV 15 pF

Input Resistance

Input Bandwidth

3

4

PGA Gain = 0 dB IV 5.5 kΩ

V 11 MHz

Input Common Mode Voltage Range V 1.1 2.35 3.6 V

Programmable Gain Amp

Composite Input-Referred PGA Gain = 0 dB V 45.0 nV/√Hz

Noise Floor PGA Gain = 20 dB V 8.0 nV/√Hz

> 300 kHz

ƒ

IN

PGA Range V 20 dB

PGA Gain Steps

3

VI 3,6,12,15,18,20 dB

PGA Gain Accuracy VI ±0.3 dB

Conversion Characteristics

Maximum Conversion Rate VI 5 MHz

Pipeline Delay (Latency) IV 6

Clock Cycles

Reset Pulse Time (RS) IV 3 Clock Cycles

Reset Calibration Time FS = 5 MSPS V 150 ms

References and External Bias

– VRB (Internal Ref) VI 2.375 2.5 2.625 V

V

RT

Bias Resistor Range (External) IV 800 1430 2500 Ω

Output Voltage IV 2.23 2.35 2.47 V

V

CM

Output Current IV 50 µA

V

CM

V

RT

V

RB

1

Total gain error of PGA and ADC using internal references.

2

Total offset error of PGA and ADC relative to mid-scale.

3

See table I for input resistance as a function of PGA gain.

4

Input bandwidth is a frequency to which the fundamental energy drops by 3 dB

IV 3.45 3.65 3.85 V

IV 0.95 1.15 1.35 V

SPT

SPT8100

2 5/12/00

Page 3

ELECTRICAL SPECIFICATIONS

TA=T

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Dynamic Performance

MIN

to T

, AVDD=DVDD=+5.0 V, OVDD= 3.3 V, ƒS=5 MSPS, 2.5 VPP input span, R

MAX

=1.43 kΩ, unless otherwise specified.

EXT

TEST TEST SPT8100

1

Effective Number of Bits ADC Input = –1 dBFS

ƒ

= 60 kHz VI 12.2 13.0 Bits

IN

= 900 kHz V 12.7 Bits

ƒ

IN

2

Signal-to-Noise Ratio

(without Harmonics) ADC Input = –1 dBFS

ƒ

= 75 kHz VI 78 81 dB

IN

ƒ

= 900 kHz V 80 dB

IN

2

Harmonic Distortion ADC Input = –0.5 dBFS

= 60 kHz V –92 –84 dB

ƒ

IN

ƒ

= 900 kHz VI –82 dB

IN

Signal-to-Noise and Distortion

(SINAD) ADC Input = –1 dBFS

= 60 kHz V 75 80 dB

ƒ

IN

= 900 kHz VI 78 dB

ƒ

IN

Spurious Free Dynamic Range

ƒ

= 60 kHz ADC Input = –0.5 dB VI 85 94 dBc

IN

= 900 kHz VI 94 dBc

ƒ

IN

= 2 MHz R

ƒ

IN

ƒIN = 3 MHz R

3

= 1 kΩ @ 10 MSPS V 83 dBc

EXT

= 1 kΩ @ 10 MSPS V 78 dBc

EXT

Two-Tone Intermodulation

3rd Order Distortion ƒ

=400 kHz, ƒ2=410 kHz

1

ƒ1=890 kHz, ƒ2=900 kHz

4

V –94 dB

5

VI –89 dB

Inputs

GS0–GS2 Logic 1 Voltage VI 2.4 V

GS0–GS2 Logic 0 Voltage VI 0.8 V

CLK, RS Logic 1 Voltage VI 2.0 V

CLK, RS Logic 0 Voltage VI 0.8 V

Maximum Input Current Low VI –10 +10 µA

Maximum Input Current High VI –10 +10 µA

Input Capacitance V 5 pF

Digital Outputs

Logic 1 Voltage I

= –2 mA VI ODVDD – 0.5 V

OH

Logic 0 Voltage IOL = 2 mA VI 0.4 V

CLK to Output Delay Time (t

)C

D

= 20 pF IV 30 ns

LOAD

Power Supply Requirements

Voltages ODV

AV

DD

DV

Currents I

DD

DD

DD

IV 3.0 3.3 5.25 V

IV 4.75 5.0 5.25 V

IV 4.75 5.0 5.25 V

VI 93 103 mA

Power Dissipation VI 465 515 mW

1

Dynamic performance tested at ƒs=4.4 MSPS

2

0 dBFS is 5.0 V peak-to-peak differential

3

ADC Input = –8.1 dBFS, unless otherwise noted

TEST LEVEL CODES

TEST LEVEL TEST PROCEDURE

All electrical characteristics are subject

to the following conditions:

All parameters having min/max specifications are guaranteed. The Test Level

column indicates the specific device

testing actually performed during production and Quality Assurance inspection. Any blank section in the data

column indicates that the specification

is not tested at the specified condition.

4

Test Conditions: PGA setting of 6 dB; Analog Input at ADC = –0.7 dB

5

Test Conditions: PGA setting of 0 dB; Analog Input at ADC = –1.9 dB

I 100% production tested at the specified temperature.

II 100% production tested at T

= +25 °C, and sample tested at the specified

A

temperatures.

III QA sample tested only at the specified temperatures.

IV Parameter is guaranteed (but not tested) by design and characterization

data.

V Parameter is a typical value for information purposes only.

VI 100% production tested at T

= +25 °C. Parameter is guaranteed over

A

specified temperature range.

SPT

SPT8100

3 5/12/00

Page 4

DEVICE OVERVIEW

The SPT8100 combines a high-resolution 5 MSPS 16-bit

ADC, a built-in reference, and a programmable gain amplifier (PGA) with resistive input impedance in a 44-pin

package.

The device includes a digitally calibrated pipeline ADC,

which is calibrated on assertion of a simple reset signal. The

combination of low noise, high linearity , a high-input impedance buffer (with programmable gain), wideband S/H, onboard voltage references, and simple digital interface

(16-bit parallel output word synchronous with the master

sampling clock) makes the SPT8100 extremely easy to use

in a wide variety of systems.

For optimum performance, the analog inputs should be

driven differentially , and may be AC-coupled or DC-coupled

to a source. Typical applications include high-performance

data acquisition systems, automatic test equipment, and

wideband digital communications receivers such as wireless basestations.

OPERATIONAL DESCRIPTION

The following sections describe in greater detail individual

blocks and functions of the SPT8100.

The incoming analog differential signal (maximum level 5 V

peak-to-peak differential) enters the device at the pins

VIN+/VIN–. The analog signal path is partitioned into a programmable gain amplifier (PGA) and an ADC. The PGA has

maximum gain of +20 dB; the gain is set by the digital control signals GS0 to GS2.

The output of the PGA is fed directly to the ADC, which

samples at a rate equal to the CLK frequency and outputs a

16-bit wide parallel word. The ADC uses a pipeline multistage architecture. Latency is 6 clock cycles.

ADC CLOCK

The chip requires a single low-jitter clock to be applied at the

CLK pin, with nominal 40–60% duty cycle. All clock generation is performed internally and all converter and S/H clocks

in the ADC path are directly derived from CLK.

If the sample rate is changed by more than a factor of 2, the

device must be recalibrated using the RS (reset) pin.

DEVICE STARTUP/INITIALIZATION SEQUENCE

Note: This initialization sequence is

required

. Without

it, the device will not work.

Allow sufficient time for the analog blocks on the SPT8100

to power on and come up to their quiescent DC states.

Allowance may also be needed for thermal time constants

associated with the package/board.

On powerup, the SPT8100’s RS (reset) should be held low

for at least three clock cycles. The power supply voltages

applied to the device must be stable during this time. The

clock signal (CLK) must be running for at least three clock

cycles prior to the rising edge of RS, and must continue

running.

When the RS signal goes from low to high, calibration is

initiated. RDY is driven low two clock cycles after the rising

edge of RS, and will stay low for 150 ms with a 5 MHz clock.

When the initialization is complete, RDY returns high and

the device is ready for normal operation. Note that the calibration of the ADC can be interrupted (before completion)

by changing the RS signal from high to low, which will cause

another reset to occur. When RS goes from low back to

high, another calibration cycle will begin.

RDY cannot be tri-stated: it is always driven either high or

low. The CLK clock must be constantly running throughout

the initialization phase until RDY is deasserted. Note that

Figure 1 – Device Initialization Timing

PWR ON

A

IN

CLK

RS

RDY

D

OUT

Requires external reset on powerup

SPT

3 clock cycles min

N+8

N+4

N+5

2 clock cycles

Initialization period: 150 ms with 5 MHz clock

INVALID DATA

N+7

N+6

5 ns typ

24 ns typ

N N+1 N+2

SPT8100

4 5/12/00

Page 5

although typically the device is initialized when power is first

applied, the initialization is only started when the RS is

asserted; there is no “power-on-reset” circuitry on chip.

may be held low for an indefinite period of time. While RS is

low, RDY will remain high. After RS is returned to high, RDY

will go low for the duration of the calibration.

RS

PROGRAMMABLE GAIN AMPLIFIER

The programmable gain amplifier (PGA) precedes the ADC

inputs. The differential inputs, which are resistive, are at

pins VIN+ and VIN–.The maximum input range is 5 V peakto-peak differential (2.5 V single-ended). To achieve maximum overall system noise performance, the source driving

these inputs needs to be as low-noise and as low-jitter as

possible, while maintaining the required distortion performance. In addition, the driving source must be low impedance to maintain the accuracy of the PGA gain.

The internal 0 dB analog signal level and ADC full-scale output level is 5 V peak-to-peak differential (2.5 V singleended). The PGA may be used to provide gain for an input

less than 5 V peak-to-peak differential.

The gain of the PGA can be programmed using a three-bit

control, available at pins GS0 to GS2. See table I. Note that

the input resistance is a function of the gain setting.

Table I – PGA Gain Control

Input

GS2 GS1 GS0 PGA Gain Resistance V/V Gain

(dB) (kΩ)

0 0 0 0 5.57 1

0 0 1 2.9 4.65 1.41

0 1 0 5.8 3.97 2.0

0 1 1 11.8 2.23 3.98

TYPICAL INTERFACE CIRCUIT

ANALOG INPUT DRIVER

The differential analog inputs (VIN+, VIN–) have a resistive

input impedance of 1 kΩ minimum. For best performance,

the input source should be a differential input, as shown in

figure 2, typical interface circuit. The SPT8100 provides its

own common-mode voltage on the pin marked VCM. Output

drive capability of VCM is a maximum of 47 µA (50 kΩ to

ground).

The SPT8100 application note (AN8100) shows an example of two modes of driving the SPT8100. One mode is

through a transformer and the other is through a single-todifferential converter. In all cases, both inputs VIN+ and VIN–

must be kept within the input common-mode range (1.15 V

to 3.65 V).

BIASC CONNECTION

An external capacitor, C

for noise filtering of an internal voltage associated with the

references. Its value is not critical: 1 µF in parallel with

0.01 µF are recommended.

BIASR CONNECTION

As shown in the typical interface circuit, R

connect between BIASR to ground. This resistor ranges

from 800 Ω to 2.5 kΩ. The proper selection of R

function of the sample rate and input frequency. Nominally,

at 5 MSPS, R

large signal levels at an analog bandwidth of 2 MHz is critical, the value should be decreased to R

for even higher-frequency analog inputs, R

be used. At lower sample rates (for example 2 MSPS), and

lower analog input frequencies, the value may be increased

to R

figure 2b.)

=2 kΩ. (Refer to the typical interface circuit table in

EXT

=1.43 kΩ is recommended. If linearity for

EXT

on the BIASC pin, is used only

EXT

is needed to

EXT

=1.24 kΩ; and

EXT

=1.0 kΩ can

EXT

EXT

is a

1 0 0 14.8 1.66 5.62

1 0 1 17.5 1.25 7.94

1 1 0 19.5 1.00 10

1 1 1 X Forbidden

SPT

POWER SUPPLIES AND GROUNDING

The SPT8100 requires three power supplies: analog AVDD,

digital DVDD and output supply ODVDD. This device works

best if all three supplies are coming from the analog supply

side of the system as shown in the typical interface circuit

(figure 2a).

Note, in figure 2a, that the supplies to the logic interface

circuit and the ODVDD are separate from each other. In a

case where the +A3.3/5 V supply is not available, try to

implement the design as close as possible to that shown in

figure 2b. Place the ferrite bead (FB1) as close to the device

as possible. To avoid latch-up, the delta between all three

grounds must stay with 100 mV; this includes transients.

(Refer to the absolute maximum ratings specifications.)

SPT8100

5 5/12/00

Page 6

Figure 2a – Typical Interface Circuit

A

IN

Transformer

Mini-Circuit

T1-6T

0.1

+

4.7

R

T

(50)

+

10 0.1 1nF

Figure 2b – Typical Interface Circuit

1.43K

R

EXT

VIN+

V

C

Reset

RS

Gain Control

GS1

GS2

1.0

+

.01

BIAS

BIAS

R

V

CM

SPT8100

–

IN

V

RT

V

1.0

RB

AV

DD

+

AGND DGND OGND OV

DV

DD

0.1

10

+

+A5V +A3.3/5V

Gain Control

Reset

GS0

Output

Enable

(active Hi)

OE

0.1

10

+

FB1

Output

Enable

(active Hi)

Clock

Input

CLK

RDY

D0–15

OVR

DD

Clock

Input

16

Logic

Interfacing

Circuit

+D3.3/5V

.01

A

IN

ƒs (MSPS) R

Transformer

Mini-Circuit

T1-6T

EXT

0.1

(kΩ)ƒ

≤5 1.43 <2 MHz

+

4.7

R

T

(50)

+

10 0.1 1nF

IN

1.43K

R

EXT

VIN+

V

IN

BIAS

RS

GS2

C

BIAS

R

V

CM

SPT8100

–

V

RT

V

RB

AV

DD

AGND DGND OGND OV

DV

DD

0.1

10

+

GS1

GS0

FB1

OE

0.1

10

CLK

RDY

D0–15

OVR

DD

+

FB2

FB3

16

Logic

Interfacing

Circuit

≤2 2.00 <2 MHz

≤5 1.24 ≥2 MHz

+A5V +D3.3/5V

≤2 1.00 ≥2 MHz

800 Ω ≤ R

≤ 2.5 kΩ

EXT

Notes:

1. To avoid device latch-up, closely follow either figure 2a or 2b, depending on what is available in the system. The difference between

figure 2a and 2b is in the grounding.

2. FB = ferrite bead. FB1 must be placed as close to the device as possible.

= 1.43 kΩ, optimized for ƒs = 5 MSPS. Refer to the above table for recommended value of R

3. R

EXT

is AIN source termination resistor.

4. R

T

with respect to ƒs and ƒIN.

EXT

5. Power supplies and references pins must have adequate decoupling. Surface-mount capacitors are highly recommended. The

smallest value of capacitors are to be placed as close to the pin as possible.

SPT

SPT8100

6 5/12/00

Page 7

Figure 3 – Timing Diagram 1

n

Analog In

CLK

t

D

n+1

n+2

n+3

n+4

n+5

n+6 n+7

n+8

D0–D15

OVR

INPUT/OUTPUT TIMING

The SPT8100 implements a simple interface: the 16 ADC

outputs appear on the pins D15–D0 as a parallel word synchronous with the ADC sampling clock. D0 is the LSB and

D15 is the MSB. The timing diagram for the ADC digital outputs is shown in figure 3. The data is sampled at the rising

edge of the clock. The ADC sampling clock is at the same

frequency as CLK.

The output data is updated on the rising edge of CLK with a

clock latency of 6 clock cycles.

OUTPUT LOGIC LEVEL

The voltage levels on the D15–D0 lines and OVR are CMOS

levels: the HIGH level is determined by the power supply

voltage on the ODVDD pin, which can be set independently

of the other supply pins on the device over the range from

3.0 V to 5.25 V (3.3 V typical). The RDY pin level is deter-

mined by DVDD (+5 V).The external digital output buffers

should be placed as close as possible to the SPT8100 digital outputs to minimize any line reflections that would cause

performance degradation.

ADC REFERENCES

The ADC full-scale range is set by reference voltages generated on chip. These two reference voltages appear on

pins VRT and VRB; nominally their difference is 2.5 V. The

references are not designed to be overdriven. The VRT and

VRB pins should be very carefully decoupled on the board

using as short a trace as possible. Some optimization of the

decoupling may be required, as shown in the typical interface circuit diagram. The smallest capacitor should be the

closest one to the chip. (Refer to the typical interface circuit

diagram.)

n

n+1

n+2

OUTPUT ENABLE

The ADC digital outputs are enabled by the active high output enable pin (OE).

OE = 1: ADC digital outputs are enabled

OE = 0: ADC digital outputs are high-impedance

(tri-stated)

DIGITAL CODE RANGE AND

OUT-OF-RANGE DETECTION

The output format of the ADC digital data is offset binary.

Due to the calibration algorithm used, there is a slight loss in

digital code range from the ADC. Instead of FFFFH and

0000H at the extremes of the range, the actual maximum

and minimum codes are less than that by 1.6% at both ends

of the scale, and vary from chip to chip. Effectively, this is a

loss in dynamic range of a few tenths of a dB, and is negligible in many applications. The out-of-range function is defined accordingly , and sets the state of the active high digital

output OVR, as follows:

OVR is HIGH if the ADC digital code is greater than

or equal to FC00H or less than or equal to 03FFH.

(See figure 4.)

If the output code exceeds FC00(max) or 03FF(min), this

implies that output is clipping. Therefore, once these limits

are crossed, the second harmonic becomes significant and

degrades performance.

Figure 4 – ADC Digital Code Range and Overrange Bit

Function

FFFFH

FC00H

ADC

Digital Code

Range

OVR = 1

OVR = Ø

65535

64512

1.6% FSR

SPT

03FFH

OVR = 1

0000H

1023

0

1.6% FSR

SPT8100

7 5/12/00

Page 8

Figure 5 – Timing Diagram 2

Table II – Timing Parameters

CLK

Digital

Outputs

OE

t

D1

FFT Plot

Parameter Symbol Min Typ Max Units

CLK high to Data Valid t

OE inactive to HiZ t

OE active to Data Valid t

1

t

D2

t

D3

Conditions: load capacitance = 20 pF, VOH = 3.3 V

D1

D2

D3

18 24 40

10 16 30 ns

10 16 30 ns

1

ns

Typical Differential Non-Linearity (DNL)

Test Conditions:

ƒIN = 2 MHz

ƒ

= 4.4 MHz

CLK

PGA Gain = 18 dB

Test Conditions:

ƒ1 = 890 kHz

= 900 kHz

ƒ

2

= 4.4 MHz

ƒ

CLK

PGA Gain = 6 dB

R

= 1.08 kΩ

EXT

ADC Input (Post PGA) = –5.4 dBFS

= +25 °C

T

A

Two-Tone Intermodulation FFT

R

= 1.43 kΩ

EXT

ADC Input (Post PGA) = –8.0 dBFS

= +25 °C

T

A

Test Conditions:

= 75 kHz

ƒ

IN

ƒ

= 4.4 MHz

CLK

100

0.9 MHz, low

95

0.9 MHz, med

0.9 MHz, high

90

85

80

75

70

SFDR (dBc)

65

60

55

50

45

–10

PGA Gain = 0 dB

Near Full-Scale Input

Spurious Free Dynamic Range

2 MHz, high

2 MHz, med

2 MHz, low

3 MHz, high

3 MHz, med

3 MHz, low

–4

–3

–5

–6

–7

–8

–9

Composite Level at ADC Input (dBFS)

–2

–1

5 V

0

P-P

SPT

Test Conditions:

10 MSPS, 5 V, 25 °C

Low: R

=1.43 kΩ @96 mA

EXT

Med: R

High: R

=1.24 kΩ @109 mA

EXT

=1 kΩ @129 mA

EXT

SPT8100

8 5/12/00

Page 9

PACKAGE OUTLINE

44-Lead LQFP

A

B

SYMBOL MIN MAX MIN MAX

INCHES MILLIMETERS

A 0.465 0.480 11.80 12.20

B 0.390 0.398 9.90 10.10

Pin 1

Index

C 0.390 0.398 9.90 10.10

D 0.465 0.480 11.80 12.20

E 0.031 0.08

F 0.012 0.018 0.30 0.45

G 0.053 0.057 1.35 1.45

C

D

H 0.002 0.006 0.05 0.15

I 0.018 0.030 0.45 0.75

J 0.039 typ 1.0 typ

K 0–7° 0–7°

E F

G

H

I

K

J

SPT

SPT8100

9 5/12/00

Page 10

PIN ASSIGNMENTS PIN FUNCTIONS

AGND

DGND

DV

DV

OGND

ODV

CLK

OE

D0 (LSB)

AV

DD

44

1

2

DD

3

4

DD

5

6

DD

7

8

9

D1

10

D2

11

12

D3

GS0

43

13

D4

V

V

IN

IN

+

–

42

41

14

15

D5

D6

GS1

40

16

D7

AGND

V

CM

RT

38

39

17

18

D8

D9

V

37

19

D10

RB

V

36

20

D11

BIASRBIAS

C

35

34

21

22

D12

D13

Pin Name Description

AGND Analog ground

RDY

33

N/C

32

31

N/C

RS

30

AGND

29

28

AV

DD

GS2

27

N/C

26

OVR

25

24

D15 (MSB)

23

D14

DGND Digital ground

DV

DD

Digital +5.0 V supply

OGND Ground for digital I/O

ODV

DD

Digital outputs supply (+3.3/5 V)

CLK Master reference clock

OE Output enable (active high)

D0–D15 Data output bits; D0 is LSB; D15 is MSB

OVR Overrange indicator bit (active high)

N/C No connect

GS[2:0] 3-bit PGA gain setting control inputs

AV

DD

Analog +5.0 V supply

RS Resets internal state of chip (active low)

RDY Initialization in progress indicator; RDY goes

low during reset initialization. Chip is ready for

normal operation when RDY is high.

BIAS

BIAS

VRT, V

V

CM

C

R

External bias capacitor connection

External bias resistor connection

ADC reference voltage outputs

RB

Common mode reference voltage output

VIN+, VIN– Analog inputs to the PGA

ORDERING INFORMATION

PART NUMBER TEMPERATURE RANGE PACKAGE

SPT8100SIT –40 to +85 °C 44L LQFP

Signal Processing Technologies, Inc. reserves the right to change products and specifications without notice. Permission is hereby expressly

granted to copy this literature for informational purposes only. Copying this material for any other use is strictly prohibited.

WARNING – LIFE SUPPORT APPLICATIONS POLICY – SPT products should not be used within Life Support Systems without the specific

written consent of SPT. A Life Support System is a product or system intended to support or sustain life which, if it fails, can be reasonably

expected to result in significant personal injury or death.

Signal Processing Technologies believes that ultrasonic cleaning of its products may damage the wire bonding, leading to device

failure. It is therefore not recommended, and exposure of a device to such a process will void the product warranty.

SPT

SPT8100

10 5/12/00

Loading...

Loading...