Page 1

SPT7937

12-BIT, 28 MSPS, 170 mW A/D CONVERTER

FEATURES

• Monolithic 28 MSPS Analog-to-Digital Converter

• 170 mW Power Dissipation

• On-Chip Track-and-Hold

• Single +5 V Power Supply

• TTL/CMOS Outputs

• 5 pF Input Capacitance

• Selectable +3 V or +5 V Logic I/O

GENERAL DESCRIPTION

The SPT7937 is a 12-bit monolithic, low-cost, low-power

analog-to-digital converter capable of minimum sample

rates of 28 MSPS. The SPT7937 has incorporated proprietary parallel SAR circuit design and CMOS processing

technologies to achieve its advanced performance.The onchip track-and-hold function assures very good dynamic

performance without the need for external components.

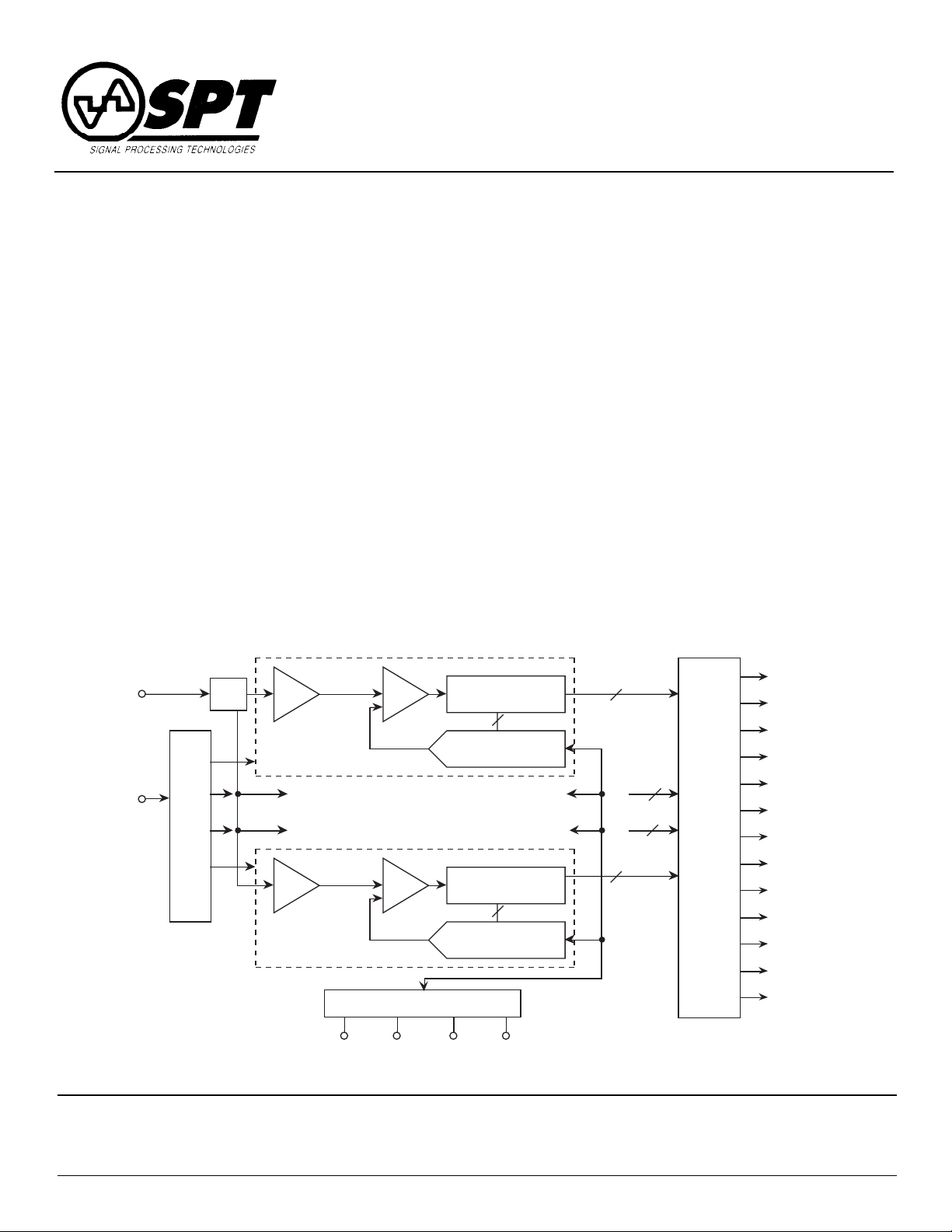

BLOCK DIAGRAM

ADC Section 1

A

CLK In

Timing

and

Control

1:18

Mux

P1

P2

.

.

.

P17

P18

IN

T/H

ADC Section 2

ADC Section 17

ADC Section 18

T/H

.

.

.

Auto-

Zero

CMP

Auto-

Zero

CMP

APPLICATIONS

• All High-Speed Applications Where

Low Power Dissipation Is Required

• Video Imaging

• Medical Imaging

• IR Imaging

• Digital Communications

Power dissipation is extremely low at only 170 mW typical at

28 MSPS with a power supply of +5.0 V. The digital outputs

are +3 V or +5 V, and are user selectable. Inputs and outputs are TTL/CMOS compatible to interface with TTL/

CMOS logic systems. Output data format is straight binary.

The SPT7937 is available in a 28-lead SSOP package over

the industrial temperature range.

13-Bit

SAR

13

DAC

13-Bit

SAR

13

DAC

13

.

.

.

13

.

.

.

13

13

13-Bit

18:1

Mux/

Error

Correction

D12 Out of Range

D11 (MSB)

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

Reference Ladder

V

RHF

V

RHS

V

RLS

V

RLF

DØ (LSB)

Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: (719) 528-2300 FAX: (719) 528-2370 Website: http://www.spt.com E-Mail: sales@spt.com

Page 2

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

Supply Voltages

AVDD.........................................................................+6 V

Output

Digital Outputs .......................................................10 mA

DVDD.........................................................................+6 V

OVDD.........................................................................+6 V

Temperature

Operating Temperature ............................. –40 to +85 °C

Input Voltages

Analog Input.................................... –0.7 V to VDD +0.7 V

CLK Input ...................................................................V

AV

– DVDD......................................................±100 mV

DD

DD

Junction Temperature .........................................+175 °C

Lead Temperature, (soldering 10 seconds)........+300 °C

Storage Temperature............................... –65 to +150 °C

AGND – DGND ..................................................±100 mV

Note: 1. Operation at any Absolute Maximum Rating is not implied. See Electrical Specifications for proper nominal

applied conditions in typical applications.

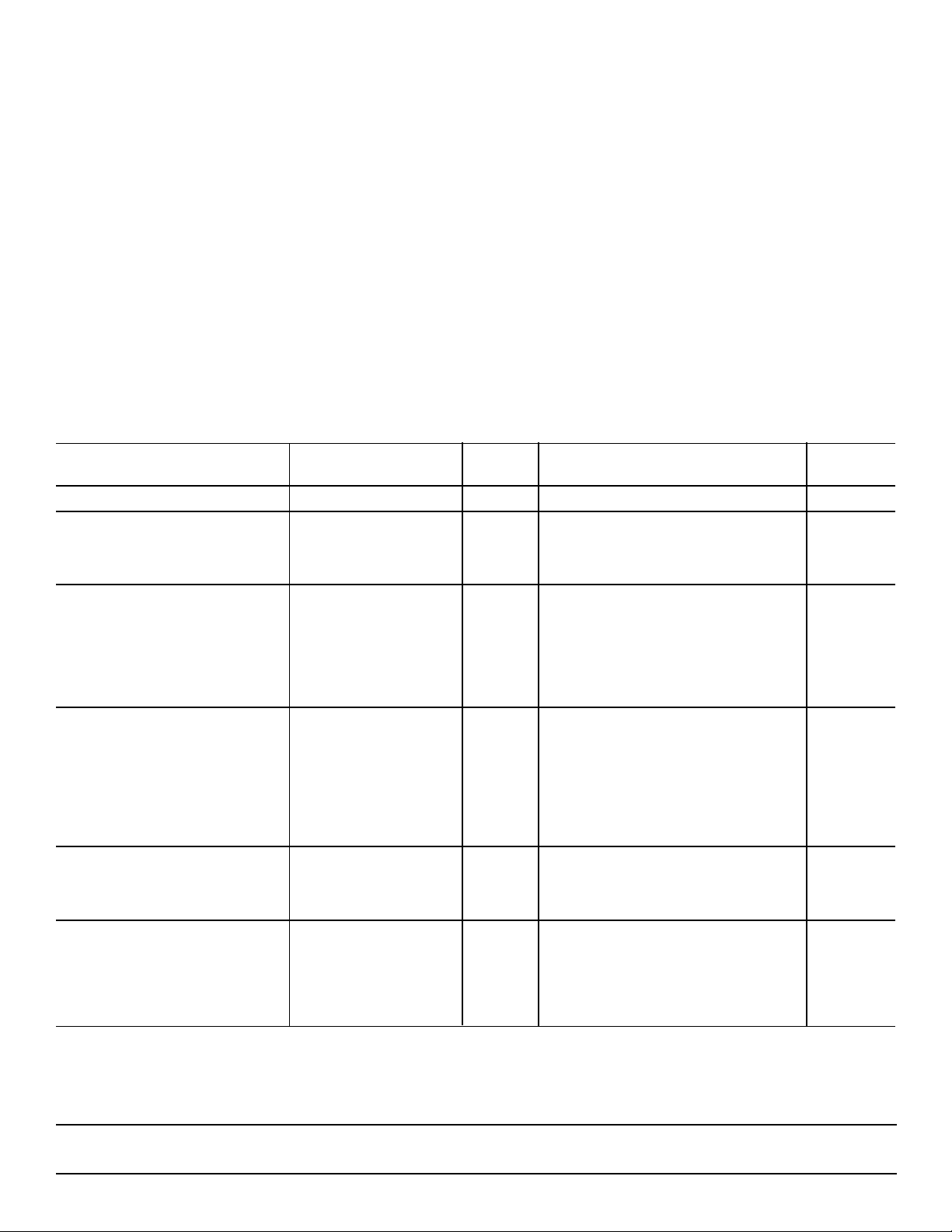

ELECTRICAL SPECIFICATIONS

TA=T

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Resolution 12 Bits

DC Accuracy

Analog Input

Conversion Characteristics

Dynamic Performance

Reference Input

MIN

to T

, VDD=+5.0 V, ƒS=28 MSPS, VIN=0 to 4 V, V

MAX

=4.0 V, V

RHS

=0.0 V, unless otherwise specified.

RLS

TEST TEST SPT7937

Integral Nonlinearity V ±1.75 LSB

Differential Nonlinearity V ±0.9 LSB

No Missing Codes VI Guaranteed

Input Voltage Range VI V

RLS

V

RHS

V

Input Capacitance V 5.0 pF

Input Bandwidth V 250 MHz

Input Impedance 35 kΩ

–Full-Scale Error

+Full-Scale Error

1

1

V 1.0 LSB

V 0.12 %FS

Maximum Conversion Rate VI 28 MHz

Minimum Conversion Rate V 1 MHz

Pipeline Delay (Latency) IV 14

Clock Cycles

Aperture Delay Time (TAP) V 1.0 ns

Aperture Jitter Time V 5.0 ps (RMS)

Clock Duty Cycle V 40 60 %

Over-Voltage Recovery Time

2

36 ns

Effective Number of Bits

= 3.58 MHz V 10.3 Bits

ƒ

IN

ƒ

= 10 MHz VI 10.0 Bits

IN

Resistance VI 350 500 650 Ω

– V

3

RLS

IV 3.0 V

DD

IV 0.0 2.0 V

V 1.0 4.0 5.0 V

V

Voltage Range

V

RHS

V

RLS

V

RHS

1

The full-scale range spans the reference ladder sense pins, V

2

Due to internal architecture, over-voltage recovery time is less than one clock cycle (i.e., 25 ns at ƒ

3

For optimum performance, the full-scale voltage range (V

RHS–VRLS

SPT

RHS

and V

. Refer to the Voltage Reference section for discussion.

RLS

) should be between 3 V to 5 V.

2 1/14/00

= 40 MHz).

CLK

SPT7937

Page 3

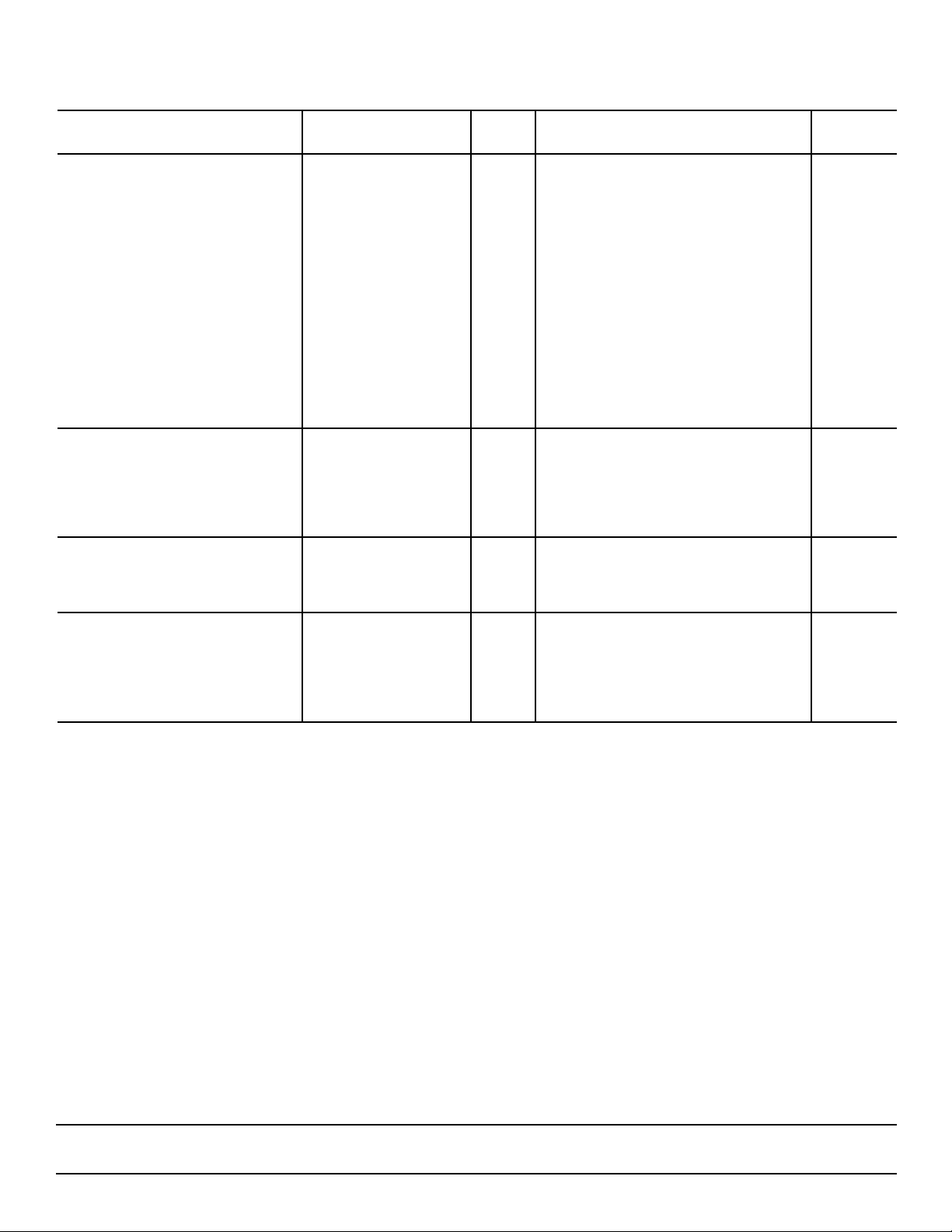

ELECTRICAL SPECIFICATIONS

TA=T

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Dynamic Performance

Inputs

Digital Outputs

Power Supply Requirements

to T

MIN

Signal-to-Noise Ratio

(without Harmonics)

ƒ

ƒ

Harmonic Distortion

ƒ

ƒ

Signal-to-Noise and Distortion

(SINAD)

ƒ

ƒ

Spurious Free Dynamic Range

ƒ

Differential Phase V 0.6 Degree

Differential Gain V 0.5 %

Logic 1 Voltage VI 2.0 V

Logic 0 Voltage VI 0.8 V

Maximum Input Current Low VI –10 +10 µA

Maximum Input Current High VI –10 +10 µA

Input Capacitance V 5 pF

Logic 1 Voltage IOH = 0.5 mA VI VDD – 0.5 V

Logic 0 Voltage IOL = 1.6 mA VI 0.4 V

CLK to Output Delay Time (tD)IV15ns

Voltages OV

Currents I

Power Dissipation VI 170 200 mW

Power Supply Rejection Ratio V 60 dB

, VDD=+5.0 V, ƒS=28 MSPS, VIN=0 to 4 V, V

MAX

TEST TEST SPT7937

= 3.58 MHz V 65 dB

IN

= 10 MHz VI 61 63 dB

IN

= 3.58 MHz V –73 dB

IN

= 10 MHz VI –72 –63.5 dB

IN

= 3.58 MHz V 64 dB

IN

= 10 MHz VI 60 62 dB

IN

= 10 MHz V 73 dB

IN

DD

V

DD

DD

=4.0 V, V

RHS

IV 3.0 5.0 V

IV 4.75 5.0 5.25 V

VI 34 40 mA

=0.0 V, unless otherwise specified.

RLS

TEST LEVEL CODES

All electrical characteristics are subject to the

following conditions:

All parameters having min/max specifications

are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data

column indicates that the specification is not

tested at the specified condition.

SPT

TEST LEVEL

I

II

III

IV

V

VI

3 1/14/00

TEST PROCEDURE

100% production tested at the specified temperature.

100% production tested at TA = +25 °C, and sample

tested at the specified temperatures.

QA sample tested only at the specified temperatures.

Parameter is guaranteed (but not tested) by design

and characterization data.

Parameter is a typical value for information purposes

only.

100% production tested at TA = +25 °C. Parameter is

guaranteed over specified temperature range.

SPT7937

Page 4

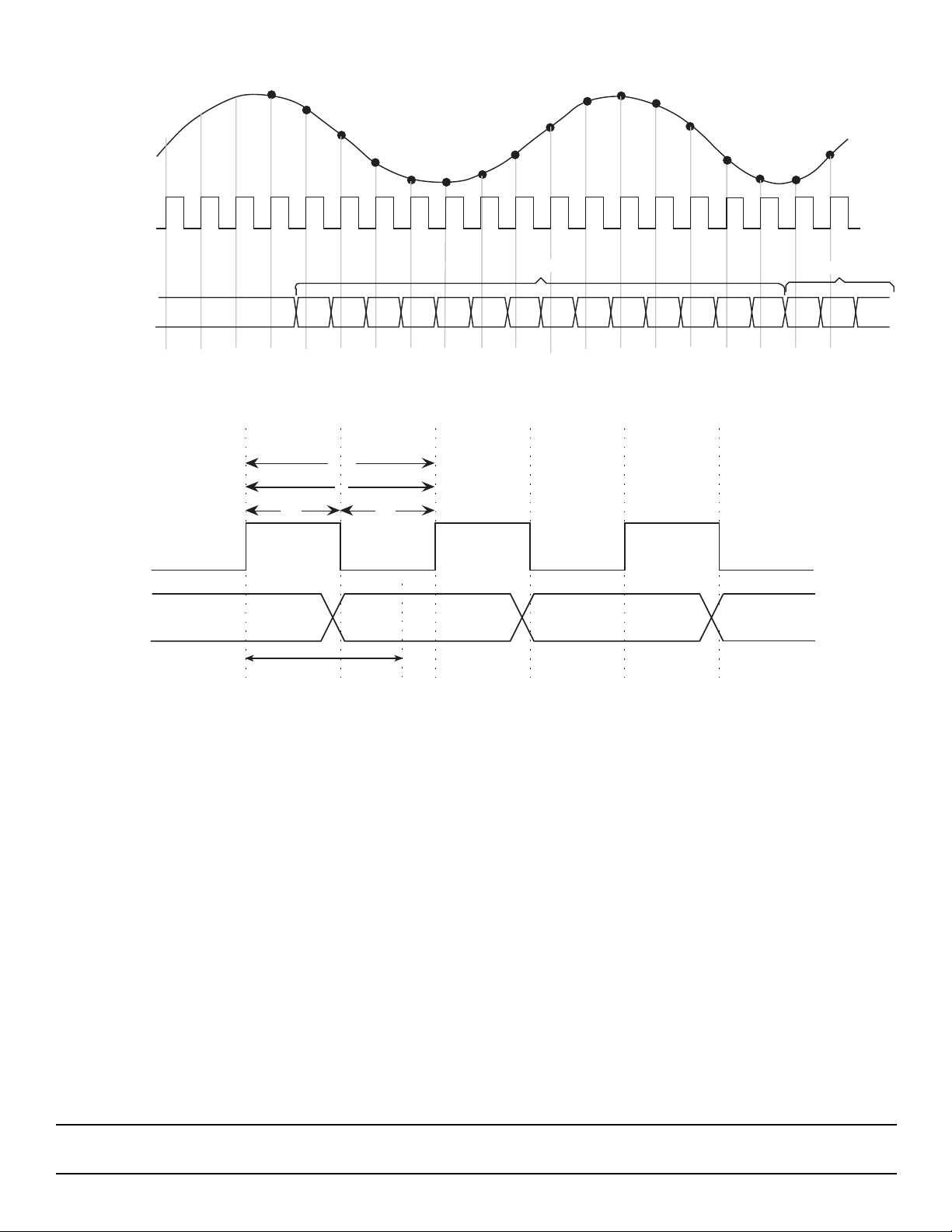

Figure 1a – Timing Diagram

ANALOG IN

CLOCK IN

1

2

3

4

5

7

6

9

8

11

10

12

13

14

15

17

16

DATA OUTPUT

Figure 1b – Timing Diagram

CLOCK IN

DATA

OUTPUT

Data Ø Data 1 Data 2 Data 3

t

CH

t

t

CLK

D

INVALID

t

C

t

CL

VALID

12

3

SPT

SPT7937

4 1/14/00

Page 5

TYPICAL PERFORMANCE CHARACTERISTICS

THD, SNR, SINAD vs Input Frequency

75

70

THD

65

SNR

60

SINAD

55

THD, SNR, SINAD (dB)

50

45

0 5 10 15 20

Input Frequency (MHz)

THD, SNR, SINAD vs Temperature

85

80

75

THD, SNR, SINAD vs Sample Rate

90

80

70

60

50

THD, SNR, SINAD (dB)

40

30

0

1

85

80

75

THD

SNR

SINAD

52040

10 30 50

Sample Rate (MSPS)

SFDR vs Temperature

70

65

THD, SNR, SINAD (dB)

60

55

–55 –40 0 25 70 85 125

Temperature (°C)

Input Bandwidth

0

–5

–10

–15

–20

Output Fundamental (dBm)

–25

THD

SNR

SINAD

70

SFDR (dB)

65

60

55

30

25

20

15

(mA)

DD

I

10

5

–55 –40 0 25 70 85 125

Temperature (°C)

IDD vs Sample Rate

–30

100 200 300 400 1000

500

Frequency (MHz)

SPT

0

10

–1

10

0

10

1

10

Sample Rate (MSPS)

SPT7937

5 1/14/00

2

Page 6

Figure 2 – Typical Interface Circuit

CLK IN

+A5

A

IN

U1

TK11240B

+A5

Ext V

(+4 V)

+

+

REF

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

DD

Out of Range Bit

MSB

LSB

128

+

+D3/5V

Interfacing Logic

+D3/5V

OGND

DGND

+

CLK

DV

AV

DGND

VINR

V

RGND

V

V

V

V

DV

FB

DD

DD

U1

(DUT)

IN

RHS

RHF

RLF

RLS

DD2

OTR

D11

D10

SPT7937

OV

+A5

+

10 µF

AGND+A5

Notes:

1) Unless otherwise specified, all non-polarized capacitors are 0.01 microfarad

surface-mount chip capacitors. They need to be placed as close to the pin as possible

2) All polarized capacitors are 4.7 to 10 microfarad tantalum surface-mount capacitors

3) FB is a ferrite bead. Place FB as close to the DUT as possible

4) U1 is TOKO regulator TK11240B (4.0 V)

TYPICAL INTERFACE CIRCUIT

Very few external components are required to achieve the

stated device performance. Figure 2 shows the typical interface requirements when using the SPT7937 in normal

circuit operation. The following sections provide descriptions of the major functions and outline critical performance

criteria to consider for achieving the optimal device

performance.

+D3/5

+

10 µF

DGND+D3/5

POWER SUPPLIES AND GROUNDING

SPT suggests that both the digital (DVDD) and the analog

(AVDD) supply voltages on the SPT7937 be derived from a

single analog supply as shown in figure 2. A separate digital

supply should be used for the digital output driver supply

(OVDD) and all interface circuitry. SPT suggests using this

power supply configuration to prevent a possible latch-up

condition on power up. In addition, the power supplies must

be powered up before the analog input is applied.

SPT

SPT7937

6 1/14/00

Page 7

OPERATING DESCRIPTION

VOLTAGE REFERENCE

The general architecture for the CMOS ADC is shown in the

block diagram. The design contains 18 identical successive

approximation ADC sections (all operating in parallel), an

18-phase clock generator, a 13-bit 18:1 digital output multiplexer, correction logic, and a voltage reference generator

which provides common reference levels for each ADC

section.

The high sample rate is achieved by using multiple SAR

ADC sections in parallel, each of which samples the input

signal in sequence. Each ADC uses 18 clock cycles to

complete a conversion. The clock cycles are allocated as

follows:

Table II – Clock Cycles

Clock Operation

1 Reference zero sampling

2 Auto-zero comparison

3 Auto-calibrate comparison

4 Input sample

5-17 13-bit SAR conversion

18 Data transfer

The SPT7937 requires the use of a single external voltage

reference for driving the high side of the reference ladder. It

must be within the range of 3 V to 5 V. The lower side of the

ladder is typically tied to AGND (0.0 V), but can be run up to

2.0 V with a second reference. The analog input voltage fullscale range will track the total voltage difference measured

between the ladder sense lines, V

mum performance the full-scale voltage range (V

RHS

and V

. For opti-

RLS

RHS–VRLS

should be between 3 V to 5 V.

Force and sense taps are provided to ensure accurate and

stable setting of the upper and lower ladder sense line voltages across part-to-part and temperature variations. By

using the configuration shown in figure 3, offset and gain

errors of less than ±2 LSB can be obtained.

Figure 3 – Ladder Force/Sense Circuit

1

AGND

+

–

2

V

RHF

3

V

RHS

)

The 18-phase clock, which is derived from the input clock,

synchronizes these events. The timing signals for adjacent

ADC sections are shifted by one clock cycle so that the analog input is sampled on every cycle of the input clock by exactly one ADC section. After 18 clock periods, the timing

cycle repeats. The latency from analog input sample to the

corresponding digital output is 14 clock cycles.

• Since only 18 comparators are used, a huge power savings is realized.

• The auto-zero operation is done using a closed loop

system that uses multiple samples of the comparator’s

response to a reference zero.

• The auto-calibrate operation, which calibrates the gain

of the MSB reference and the LSB reference, is also

done with a closed loop system. Multiple samples of

the gain error are integrated to produce a calibration voltage for each ADC section.

• Capacitive displacement currents, which can induce sampling error, are minimized since only one comparator

samples the input during a clock cycle.

• The total input capacitance is very low since sections of

the converter which are not sampling the signal are isolated from the input by transmission gates.

4 N/C

5

V

–

+

6

V

7

V

All capacitors are 0.01 µF

RLS

RLF

IN

SPT

SPT7937

7 1/14/00

Page 8

Figure 4 – Simplified Reference Ladder Drive Circuit

Without Force/Sense Circuit

+4.0 V

External

Reference

(+3.91 V)

V

RHS

21 mV

R/2

R

R

ANALOG INPUT

VIN is the analog input. The input voltage range is from V

to V

(typically 4.0 V) and will scale proportionally with re-

RHS

spect to the voltage reference. (See the Voltage Reference

section.)

The drive requirements for the analog inputs are very minimal when compared to most other converters due to the

SPT7937’s extremely low input capacitance of only 5 pF

and very high input resistance in excess of 35 kΩ.

RLS

V

RLF

V

RLS

(0.075 V)

(AGND)

0.0 V

50 mV

R

R

R

R

R/2

R=30 Ω (typ)

All capacitors are 0.01 µF

In cases in which wider variations in offset and gain can be

tolerated, V

be tied directly to V

can be tied directly to V

Ref

as shown in figure 4. Decouple force

RLF

and AGND can

RHF

and sense lines to AGND with a 0.01 µF capacitor (chip cap

preferred) to minimize high-frequency noise injection. If this

simplified configuration is used, the following considerations

should be taken into account:

The reference ladder circuit shown in figure 4 is a simplified

representation of the actual reference ladder with force and

sense taps shown. Due to the actual internal structure of the

ladder, the voltage drop from V

to the voltage drop from V

RLF

Typically, the top side voltage drop for V

RHF

to V

to V

RLS

is not equivalent

RHS

.

to V

RHF

RHS

will

equal:

V

– V

RHF

and the bottom side voltage drop for V

V

– V

RLS

= 0.5% of (V

RHS

= 1.25% of (V

RLF

RHF

RHF

– V

– V

) (typical),

RLF

RLS

) (typical).

RLF

to V

will equal:

RLF

Figure 4 shows an example of expected voltage drops for a

specific case. V

tied to AGND. A 21 mV drop is seen at V

a 50 mV increase is seen at V

of 4.0 V is applied to V

REF

(= 0.050 V).

RLS

and V

RHF

(= 3.79 V) and

RHS

RLF

is

The analog input should be protected through a series resistor and diode clamping circuit as shown in figure 5. To prevent possible latch-up condition, the power supplies must

be powered up before the input is applied.

Figure 5 – Recommended Input Protection Circuit

+V

D1

47 Ω

D2

–V

D1 = D2 = Hewlett Packard HP5712 or equivalent

AV

ADCBuffer

DD

CALIBRATION

The SPT7937 uses a user-transparent, auto-calibration

scheme to ensure 12-bit accuracy over time and temperature. Gain and offset errors are continually adjusted to 12-bit

accuracy during device operation.

Upon power up, the SPT7937 begins its calibration algorithm. In order to achieve the calibration accuracy required,

the offset and gain adjustment step size is a fraction of a 12bit LSB. Since the calibration algorithm is an oversampling

process, a minimum of 10,000 clock cycles are required.

This results in a minimum calibration time upon power-up of

357 µsec (for a 28 MHz clock). Once calibrated, the

SPT7937 remains calibrated over time and temperature.

Since the calibration cycles are initiated on the rising edge

of the clock, the clock must be continuously applied for the

SPT7937 to remain in calibration.

SPT

SPT7937

8 1/14/00

Page 9

Figure 6 – On-Chip Protection Circuit

V

DD

120 Ω

120 Ω

Pad

Analog

DIGITAL OUTPUTS

The digital outputs (D0–D12) are driven by a separate supply (OVDD) ranging from +3 V to +5 V. This feature makes it

possible to drive the SPT7937’s TTL/CMOS-compatible

outputs with the user’s logic system supply. The format of

the output data (D0–D11) is straight binary. (See table III.)

The outputs are latched on the rising edge of CLK.

Table III – Output Data Information

ANALOG INPUT OVERRANGE OUTPUT CODE

D12 D11–D0

+F.S. + 1/2 LSB 1 11 1111 1111

+F.S. –1/2 LSB 0 11 1111 111Ø

+1/2 F.S. 0 ØØ ØØØØ ØØØØ

+1/2 LSB 0 00 0000 000Ø

0.0 V 0 00 0000 0000

(Ø indicates the flickering bit between logic 0 and 1).

INPUT PROTECTION

All I/O pads are protected with an on-chip protection circuit

shown in figure 6. This circuit provides ESD robustness to

3.5 kV and prevents latch-up under severe discharge condi-

tions without degrading analog transition times.

CLOCK INPUT

The SPT7937 is driven from a single-ended TTL-input

clock. Because the pipelined architecture operates on the

rising edge of the clock input, the device can operate over a

wide range of input clock duty cycles without degrading the

dynamic performance.

OVERRANGE OUTPUT

The Overrange Output (D12) is an indication that the analog

input signal has exceeded the positive full scale input voltage by 1 LSB. When this condition occurs, D12 will switch to

logic 1. All other data outputs (D0 to D11) will remain at

logic 1 as long as D12 remains at logic 1. This feature

makes it possible to include the SPT7937 in higher resolution systems.

EVALUATION BOARD

The EB7937 evaluation board is available to aid designers

in demonstrating the full performance of the SPT7937. This

board includes a reference circuit, clock driver circuit, output

data latches and an on-board reconstruction of the digital

data. An application note (AN7937) describing the operation

of this board, as well as information on the testing of the

SPT7937, is also available. Contact the factory for price and

availability.

SPT

SPT7937

9 1/14/00

Page 10

PACKAGE OUTLINE

28-Lead SSOP

INCHES MILLIMETERS

SYMBOL MIN MAX MIN MAX

A 0.397 0.407 10.07 10.33

28

I H

1

B 0.002 0.008 0.05 0.21

C 0.0256 typ 0.65 typ

D 0.010 0.015 0.25 0.38

E 0.004 0.008 0.09 0.20

F 0.066 0.070 1.68 1.78

G 0.025 0.037 0.63 0.95

H 0.301 0.311 7.65 7.90

I 0.205 0.212 5.20 5.38

B

A

CD

H

F

G

E

SPT

SPT7937

10 1/14/00

Page 11

PIN ASSIGNMENTS PIN FUNCTIONS

Name Function

DV

OV

DD

D0 (LSB)

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11 (MSB)

D12

128

2

326

4

524

6

722

28L SSOP

8

9

10

11

12 17

13

14 15

27

25

23

21

20

19

18

16

DD2

V

RLS

V

RLF

V

RHF

V

RHS

RGND

V

IN

VINR

AGND

AV

DD

DV

DD1

CLK

DGND

OGND

OV

DD

Digital Output Driver Supply

D0-D11 Data Output, Bits 0 – Bit 11

D12 Out of Range

OGND Digital Output Driver Ground

DGND Digital Ground

CLK Input Clock

DV

DV

AV

DD1

DD2

DD

Digital V

Digital VDD; must be tied to DV

Analog V

AGND Analog Ground

VINR Analog Input Return

V

IN

Analog Input, Full Scale from V

RGND Analog Ground Shield (Junction Isolated)

V

V

V

V

RHS

RHF

RLS

RLF

Reference High Sense

Reference High Force (V

Reference Low Sense

Reference Low Force

DD

DD

RHF

DD1

RLS

≤AVDD)

to V

RHS

ORDERING INFORMATION

PART NUMBER TEMPERATURE RANGE PACKAGE TYPE

SPT7937SIR –40 to +85 °C 28L SSOP

Signal Processing Technologies, Inc. reserves the right to change products and specifications without notice. Permission is hereby expressly

granted to copy this literature for informational purposes only. Copying this material for any other use is strictly prohibited.

WARNING – LIFE SUPPORT APPLICATIONS POLICY – SPT products should not be used within Life Support Systems without the specific

written consent of SPT. A Life Support System is a product or system intended to support or sustain life which, if it fails, can be reasonably

expected to result in significant personal injury or death.

Signal Processing Technologies believes that ultrasonic cleaning of its products may damage the wire bonding, leading to device

failure. It is therefore not recommended, and exposure of a device to such a process will void the product warranty.

SPT7937

SPT

11 1/14/00

Loading...

Loading...