Page 1

SPT7721

8-BIT, 250 MSPS ADC WITH DEMUXED OUTPUTS

TECHNICAL DATA

FEBRUARY 20, 2001

FEATURES

• High conversion rate: 250 MSPS

• Single +5 V pow er supply

• V ery low pow er dissipation: 310 mW

• 500 MHz full power bandwidth

• Po wer-down mode

• +3.0 V/+5.0 V (LVCMOS) digital output logic

compatibility

• Demuxed output ports

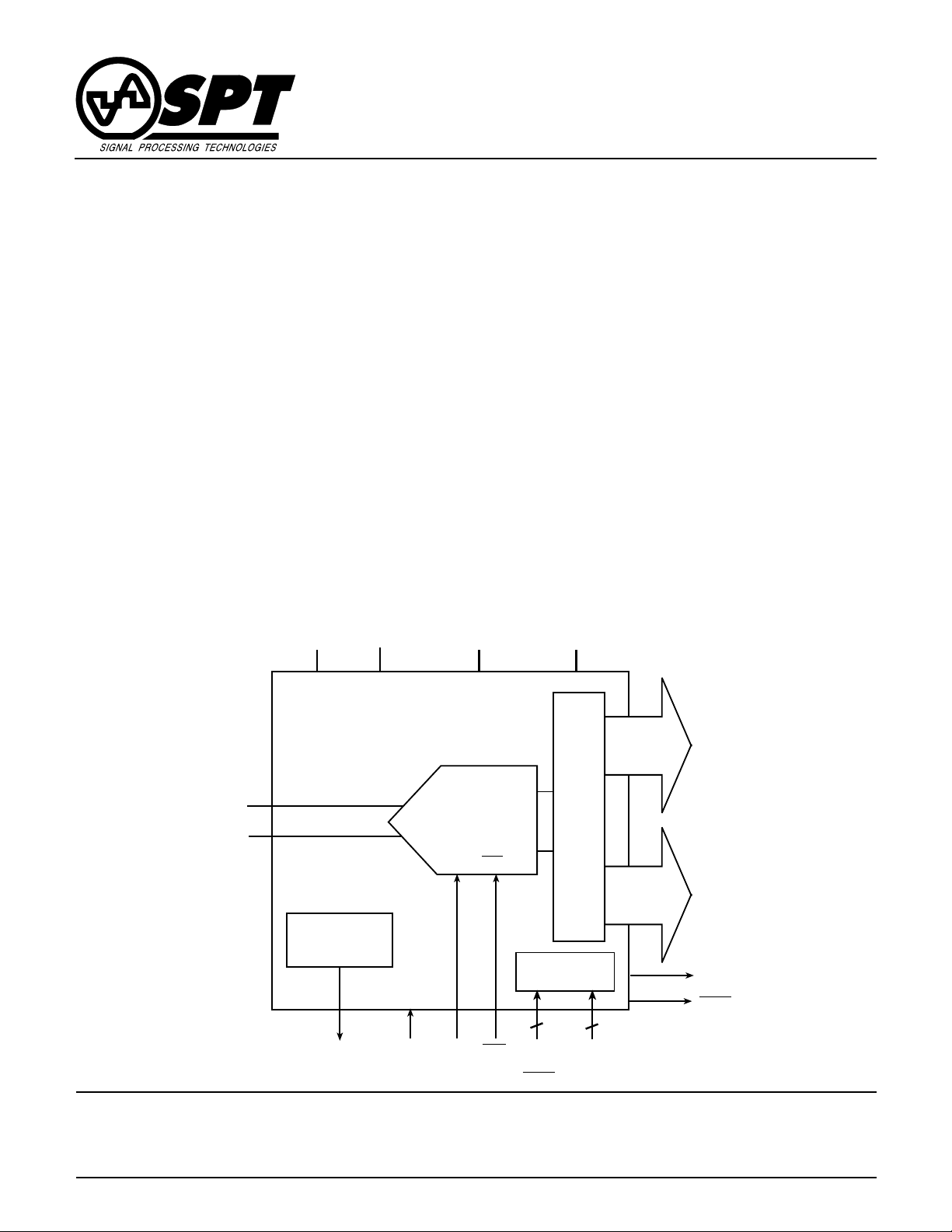

GENERAL DESCRIPTION

The SPT7721 is a high-speed, 8-bit analog-to-digital converter implemented in an advanced BiCMOS process. An

advanced folding and interpolating architecture provides

both a high conversion rate and v ery low power dissipation

of only 310 mW. The analog inputs can be operated in

either single-ended or differential input mode. A 2.5 V common mode reference is provided on chip for the singleended input mode to minimize external components.

BLOCK DIAGRAM

AGND DGND

APPLICATIONS

• RGB video processing

• Digital communications

• High-speed instrumentation

• Digital sampling oscilloscopes (DSO)

• Projection display systems

The SPT7721 digital outputs are demuxed (double-wide)

with both dual-channel and single-channel selectable output modes. Demuxed mode supports either parallel

aligned or interleaved data output. The output logic is both

+3.0 V and +5.0 V compatible. The SPT7721 is av ailable in

a 44-lead TQFP surf ace mount package ov er the industrial

temperature range of –40 to +85 °C.

AV

CC

OV

DD

DA0DA

V

+

IN

8-Bit

7

250 MSPS

VIN

Common Mode

Voltage

Reference

+2.5 V

V

CM

PD CLK

ADC

CLK CLK

CLK

Data Output Latches

Data Output

Mode Control

22

Reset

DMODE

&

Reset

1,2

DB0DB

DCLK

OUT

DCLK

OUT

7

Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: 719-528-2300 Fax: 719-528-2370 Web Site: http://www .spt.com e-mail: sales@spt.com

Page 2

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

Supply V oltages

AVCC...................................................................... +6 V

OVDD..................................................................... +6 V

Input V oltages

Analog Inputs ............................... –0.5 V to VCC +0.5 V

Digital Inputs ................................ –0.5 V to V

+0.5 V

CC

T emperatures

Operating Temperature........................... –40 to +85 °C

Storage Temperature ............................ –65 to +125 °C

Note: 1. Operation at any Absolute Maximum Rating is not implied.

See Electrical Specifications for proper nominal applied

conditions in typical applications.

ELECTRICAL SPECIFICATIONS

TA = T

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Resolution 8 Bits

DC Performance

Analog Input

to T

, AV

MIN

MAX

= +5.0 V, ƒ

CC

= 250 MHz, unless otherwise specified.

CLK

TEST TEST SPT7721

Differential Linearity Error (DLE) +25 °C V –0.75/+1.25 LSB

–40 °C to +85 °C V –1.0/+2.0 LSB

Integral Linearity Error (ILE) +25 °C V ±2.0 LSB

–40 °C to +85 °C V ±3.0 LSB

No Missing Codes @250 MSPS VI Guaranteed

Input V oltage Range

(with respect to V

–) V ±512 mV

IN

Input Common Mode IV 2.3 2.5 2.7 V

Input Bias Current VI 5 µA

Input Resistance +25 °C V 50 kΩ

Input Capacitance +25 °C V 5 pF

Input Bandwidth +25 °C (–3 dB of FS) V 500 MHz

±FS Error VI ±2 %FS

Offset Error VI ±10 mV

P-P

Timing Characteristics

Conversion Rate VI 2 50 MSPS

Output Delay (t

) +25 °C IV 6 8 10 ns

pd1

Output Delay Tempco V 21 ps/°C

Aperture Delay Time (t

) V 0.5 ns

ap

Aperture Jitter Time V 2 ps rms

Pipeline Delay (Latency)

Single Channel Mode V 3.5 Clocks

Demuxed Interleaved Mode V 4.5 Clocks

Demuxed Parallel Mode

Channel B V 4.5 Clocks

Channel A V 5.5 Clocks

CLK to DCLK

Single Channel Mode (t

Dual Channel Mode (t

Delay Time

OUT

)V6ns

pd2

)V6ns

pd3

Dynamic Performance

Effective Number of Bits (ENOB)

= 70 MHz +25 °C VI 5.8 6.3 Bits

ƒ

IN

= 70 MHz –40 °C to +85 °C IV 5.4 5.9 Bits

ƒ

IN

Signal-to-Noise Ratio (SNR)

= 70 MHz +25 °C VI 42 43 dB

ƒ

IN

ƒIN = 70 MHz –40 °C to +85 °C IV 36 39 dB

SPT

SPT7721

2 2/20/01

Page 3

ELECTRICAL SPECIFICATIONS

TA = T

MIN

to T

MAX

, AV

= +5.0 V, ƒ

CC

= 250 MHz, OVDD = 5 V, unless otherwise specified.

CLK

TEST TEST SPT7721

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Dynamic Performance

Total Harmonic Distortion (THD)

= 70 MHz +25 °C VI –43 –40 dB

ƒ

IN

= 70 MHz –40 °C to +85 °C IV –41 –37 dB

ƒ

IN

Signal-to-Noise and Distortion (SINAD)

= 70 MHz +25 °C VI 37 39 dB

ƒ

IN

= 70 MHz –40 °C to +85 °C IV 35 37 dB

ƒ

IN

Power Supply Requirements

Voltage (Analog Supply) IV 4.75 5.0 5.25 V

AV

CC

OVDD Voltage (Digital Supply) IV 2.75 5.25 V

Current VI 62 70 mA

AV

CC

Power Dissipation with Inter nal Voltage Reference VI 3 10 3 50 mW

Power Supply Rejection Ratio V 35 mV/V

Common Mode Reference

Voltage VI 2.45 2.5 2.55 V

Voltage Tempco V 119 ppm/°C

Output Impedance V 1 kΩ

Current Capability V 50 µA

Power Supply Rejection Ratio V 34 mV/V

Clock and Reset Inputs (Differential and Single-Ended)

Differential Signal Amplitude V

Differential High Input Voltage V

Differential Low Input Voltage V

DIFF

IHD

ILD

Differential Common-Mode Input V

Single-Ended High Input Voltage V

Single-Ended Low Input Voltage V

CMD

IH

IL

VI 400 mV

IV 1.7 AV

CC

V

IV 0 AVCC –0.4 V

IV 1.5 V

IV 1.8 V

IV 0 1.2 V

P-P

High Current Level VID <2.5 V VI –100 2 0 +100 µA

Low Current Level V

ID

VI –100 20 +100 µA

Power Down and Mode Control Inputs (Single-Ended)

High Input Voltage IV 2.0 AV

CC

V

Low Input Voltage IV 0 1.0 V

Maximum Input Current Low VI –100 10 +100 µA

Maximum Input Current High <4.0 V VI –100 10 +100 µA

Digital Outputs

Logic "1" Voltage (IOH = –100 µA) VI OVDD – 0.2 V

Logic "0" Voltage (I

Data (10 pF load) V 3 ns

T

R/TF

= +100 µA) VI 0.2 V

OL

TR/TF DCLK = (10 pF load) V 1.5 ns

TEST LEVEL CODES

All electrical characteristics are subject to the

following conditions:

All parameters having min/max specifications

are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data

column indicates that the specification is not

tested at the specified condition.

LEVEL TEST PROCEDURE

I 100% production tested at the specified temperature.

II 100% production tested at TA = +25 °C, and sample tested at the

specified temperatures.

III QA sample tested only at the specified temperatures.

IV Parameter is guaranteed (but not tested) by design and characteri-

zation data.

V Parameter is a typical value for information purposes only.

VI 100% production tested at TA = +25 °C. Parameter is guaranteed

over specified temperature range.

SPT

3 2/20/01

SPT7721

Page 4

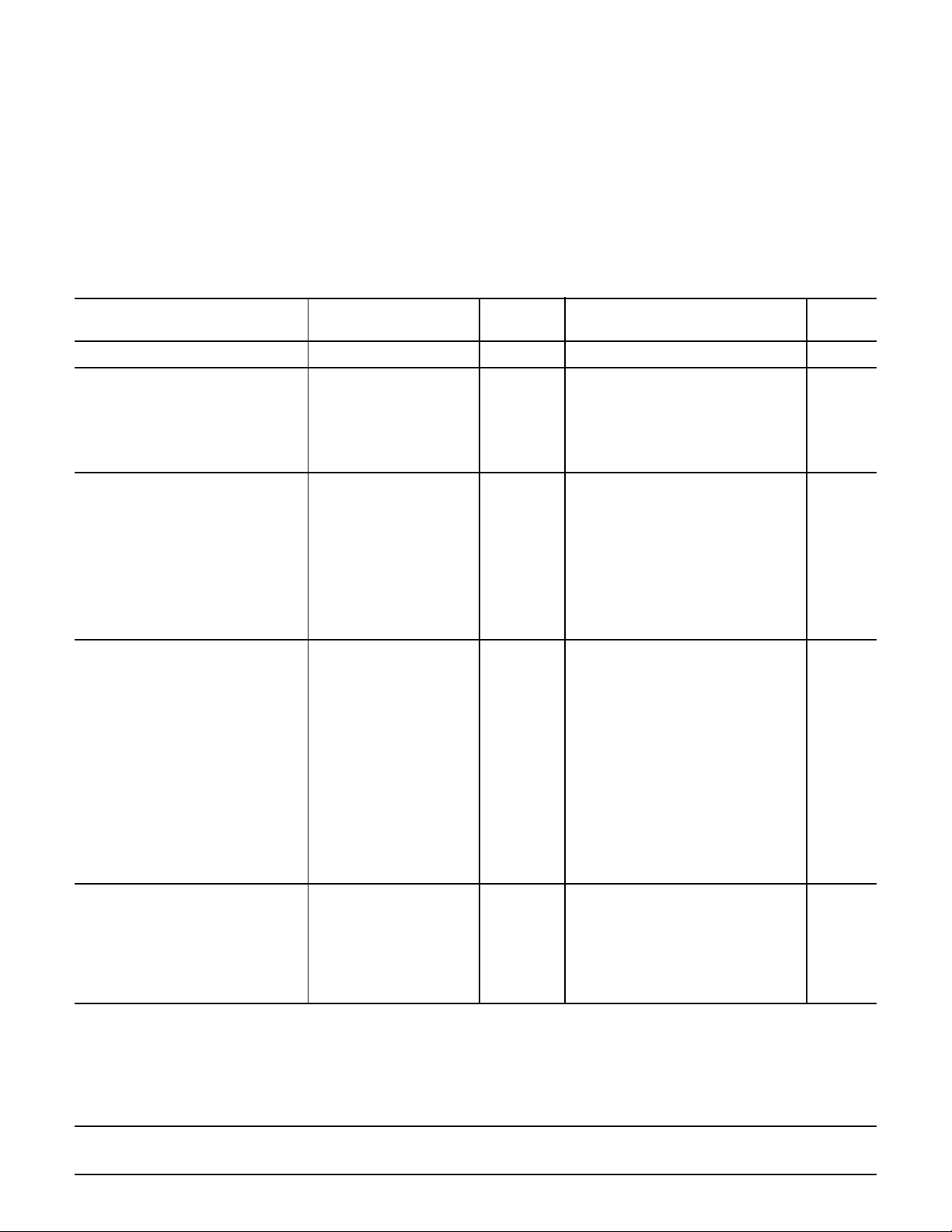

TYPICAL PERFORMANCE CHARACTERISTICS

SFDR, THD, SNR vs Temperature

60

55

50

45

40

35

SFDR, THD, SNR (dB)

30

40

20

0

Temperature (°C)

AV

Current vs Temperature

CC

75

70

65

(mA)

60

CC

AV

55

20

40

60 80

SFDR

THD

SNR

100

SFDR, SNR, THD, SINAD vs Sample Rate

60

55

50

45

40

35

SFDR, SNR, THD, SINAD (dB)

30

0

50

100

150

200

Sample Rate (MSPS)

AVCC Current Power Do wn vs Temperature

3.0

2.8

2.6

(mA)

CC

2.4

AV

SFDR

SNR

THD

SINAD

250 300

50

45

6.0

4.0

2.0

0.0

mV

2.0

4.0

6.0

2.2

40

20

0

20

40

Temperature (°C)

60 80

100

2.0

40

20

0

20

40

Temperature (°C)

V olta ge Offset Error vs Temperature Percent Gain Error vs Temperature

1.06

1.05

1.04

1.03

%

1.02

1.01

40

20

0

20

40

Temperature (°C)

60 80

100

1.00

40

20

0

20

40

Temperature (°C)

60 80

60 80

100

100

SPT

SPT7721

4 2/20/01

Page 5

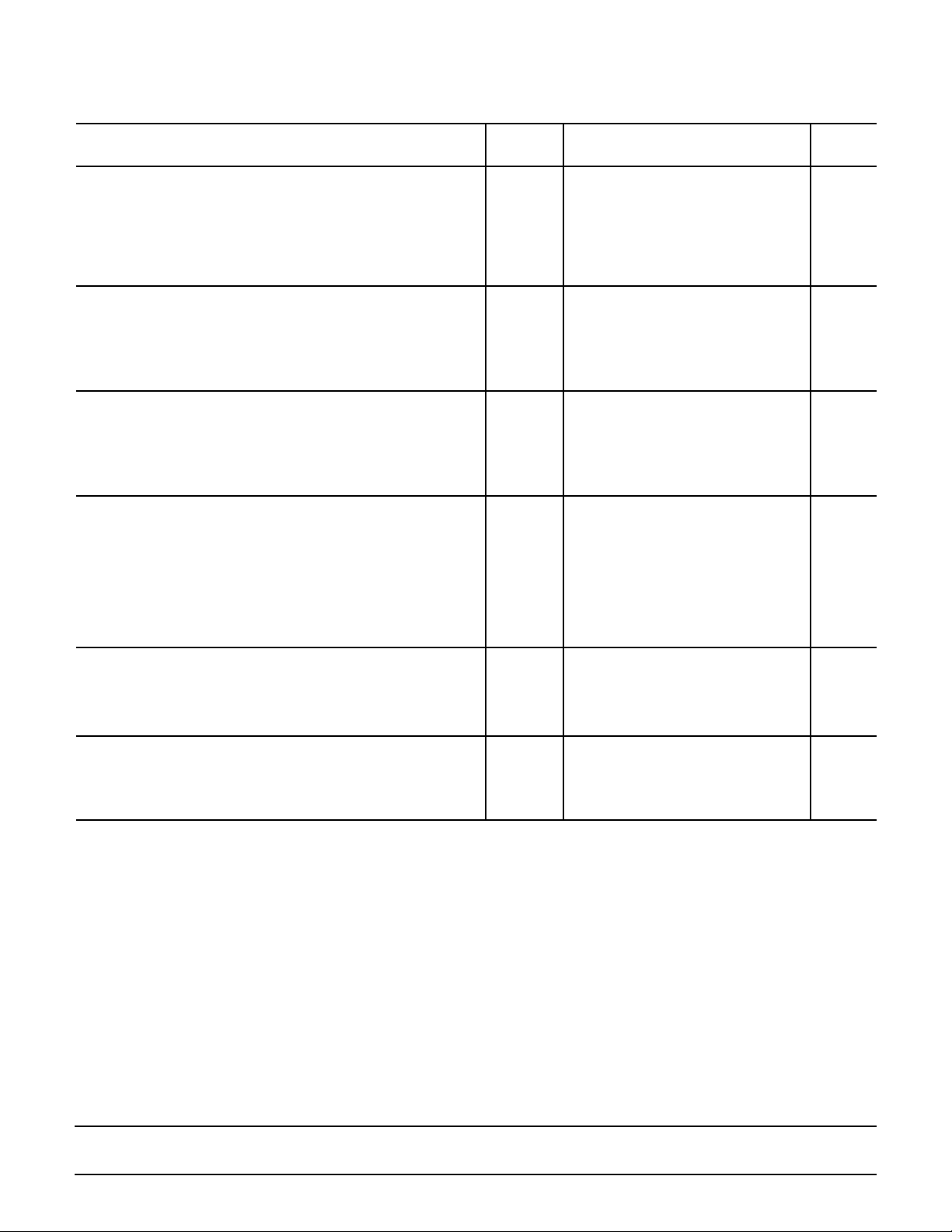

TYPICAL PERFORMANCE CHARACTERISTICS

Input Bandwidth Common Mode Reference V oltage vs V

1

0

1

2

dB

3

4

5

100

0

200

300

400

Input Frequency (MHz)

Output VDD vs Clock Frequency, Dual Mode

120

100

80

60

mA

40

500 600

Output VDD=5 V

Output VDD=3 V

2.50

2.49

2.48

2.47

V

2.46

OUT

2.45

2.44

VCM

2.43

2.42

2.41

2.40

4.5

4.7

4.9

5.1

5.3

VCC V

Output VDD vs Clock Frequency, Single Mode

60

50

40

30

mA

20

Output VDD=5 V

Output VDD=3 V

5.5

CC

5.7

20

0

0

50

100

Clock Frequency (MHz)

T otal Power vs Clock Frequency

1000

800

700

600

500

400

Power Dissipation (mW)

300

0

50

with 6 pF loads

100

Clock Frequency (MHz)

150

150

200

200

250 300

OVDD=5 V

OVDD=3 V

250 300

10

0

0

25

50

75

100

125 150

Clock Frequency (MHz)

SPT

SPT7721

5 2/20/01

Page 6

THEORY OF OPERATION

The SPT7721 is a three-step subranger. It consists of two

THAs in series at the input, followed by three ADC b locks .

The first block is a three-bit folder with over/under range

detection. The second b lock consists of two single-bit f olding interpolator stages. There are pipelining THAs between

each ADC block.

The analog decode functions are the input buffer, input

THAs, three-bit folder , f olding interpolators, and pipelining

THAs. The input buffer enables the part to withstand railto-rail input signals without latchup or excessive currents

and also performs single-ended to differential conv ersion.

All of the THAs have the same basic architecture. Each

has a differential pair buffer followed by switched emitter

followers driving the hold capacitors. The input THA also

has hold mode feedthrough cancellation de vices.

The three MSBs of the ADC are generated in the first

three-bit folder block, the output of which driv es a differential reference ladder which also sets the full-scale input

range. Differential pairs at the ladder taps generate

midscale, quarter and three-quarter scale , overr ange, and

underrange. Every other differential pair collector is crosscoupled to generate the eighth scale zero crossings. The

middle ADC block generates two bits from the folded signals of the previous stages after pipeline THAs. Its outputs

drive more pipeline THAs to push the decoding of the three

LSBs to the next half clock cycle . The three LSBs are generated in interpolators that are latched one full clock cycle

after the MSBs.

The digital decode consists of comparators, exclusive of

cells for gray to binary decoding, and/or cells used for

mostly over/under range logic. There is a total of 3.5 cloc k

cycles latency before the output bank selection. In order to

reduce sparkle codes and maintain sample rate, no more

than three bits at a time are decoded in any half clock

cycle.

The output data mode is controlled by the state of the

demux mode inputs. There are three output modes .

• All data on bank A with clock r ate limited to one-half

maximum

• Interleav ed mode with data alternately on banks A and

B on alternate clock cycles

• Parallel mode with bank A delayed one cycle to be

synchronous with bank B every other clock cycle

If necessary , the input clock is divided b y tw o. The divided

clock selects the correct output bank. The user can synchronize with the divided clock to select the desired output

bank via the differential RESET input.

The output logic family is L VCMOS with output VDD supply

adjustable from 2.7 volts to 5.3 v olts. There are also differential clock output pins that can be used to latch the output

data in single bank mode or to indicate the current output

bank in demux mode.

Finally , a pow er-down mode is availab le, which causes the

outputs to become tri-state, and overall power is reduced

to about 10 mW . There is a 2.5 V reference to supply common mode for single-ended inputs that is not shut down in

power-down mode .

Figure 1 – Single Mode Timing Diagram

3.5 CLK Cycles of Latency

N+1

t

pd2

V

IN

/CLK

CLK

D0D7

(Port A)

DCLKOUT

/DCLKOUT

t

N

pd2

t

ap

NOTES

Typically:

= Aperture Delay = 0.5 ns

1) t

ap

2) t

= Clock to output delay = 8 ns

pd1

3) t

= CLK to DCLKout delay = 6 ns

pd2

4) DCLKout rate is same as the rate of CLK input

SPT

N+2

t

pd1

N+3

N1N2N3N4 N

N+4

N+5

N+1

SPT7721

6 2/20/01

Page 7

Figure 2 – Dual Mode Timing Diagram

V

IN

CLK

/CLK

U6-Reset

/Reset

Reset

Port A

Port B

Port A

Port B

DCLKOUT

/DCLKOUT

N

t

ap

N+1

550ps

4.5 CLK Cycles of Latency

N+2

550ps

t

reset

t

s

N+3

t

pd1

N+4

t

pd1

N+5

N+6

t

pd1

6 ns typ

INTERLEAVED DATA OUTPUT

N5

6 ns typ

N4

PARALLEL DATA OUTPUT

N5

N4

t

pd3

N6

t

pd3

N7

N6

N3

N2

N2

N1

N

N1N3

N

N+1

V

IN

CLK

/CLK

U6-Reset

/Reset

Reset

Port A

Port B

Port A

Port B

/DCLKOUT

DCLKOUT

N

t

ap

N+1

550ps

4.5 CLK Cycles of Latency

N+2

550ps

t

reset

t

s

N+3

t

pd1

N+4

t

pd1

N+5

N+6

t

pd1

6 ns typ

INTERLEAVED DATA OUTPUT

N6

N4

N5

t

pd3

PARALLEL DATA OUTPUT

N6

N5

t

pd3

N3

N2

N3

N2

N1

N

N1

N

N+1

Data Output Possibilities w/o Reset

SPT

SPT7721

7 2/20/01

Page 8

Figure 3 – Typical Interface Cir cuit

T1

A

IN

Mini-Circuit

T1-6T

.01

Mode

Select

OUT

1 (2)

CC

AV

DMode1

2 (2)

CC

AV

VCM

VIN+

50

V

IN

Reset

Diff In

Reset

DMode2

SPT7721

AGND1 (4)

AGND2 (2)

Reset

Clock

Diff In

CLK

DA0DA

DCLK

DCLK

DB0DB

DGND (3)

CLK

(3)

OV

OUT

OUT

DD

7

Interfacing

Logics

7

Notes:

1) FB = Ferrite bead. It must placed as close to the ADC as possible.

2) All inputs are internally biased:

a) DMode1 to GND through 100K

b) DMode2 to VCC through 50K

c) CLK, PD and Rest pins to GND through 100K

d) /CLK and /Reset pins to 1.5 V through 5K

e) V

+ and VIN to +2.5 V through 50K

IN

3) All 0.01microfarad capacitors are surface mount caps. They must be

placed as close to the respective pin as possible

Default = interleave dual

}

channel output

.01(2x)

TYPICAL INTERFACE CIRCUIT

V ery few e xternal components are required to achiev e the

stated device performance. Figure 3 shows the typical

interface requirements when using the SPT7721 in normal

circuit operation. The following sections provide descriptions of the major functions and outline performance

criteria to consider for achieving the optimal device

performance.

ANALOG INPUT

The input of the SPT7721 can be configured in various

ways depending on whether a single-ended or differential

input is desired.

The AC-coupled input is most conveniently implemented

using a transformer with a center-tapped secondary winding. The center tap is connected to the VCM pin as shown in

figure 3. To obtain low distor tion, it is important that the

selected transformer does not exhibit core saturation at

the full-scale voltage. Proper termination of the input is important for input signal purity. A small capacitor across the

input attenuates kickback noise from the internal trackand-hold.

Figure 4 illustrates a solution (based on operational amplifiers) that can be used if a DC-coupled single-ended input

is desired. It is v ery important to select op amps with a high

open-loop gain, a bandwidth high enough so as not to impair the performance of the ADC, low THD , and high SNR.

.01(3x)

+A5

.01(3x)

+

10

FB

+

10

+D3/5

+D3/5

Figure 4 – DC-Coupled Single-Ended to Differential

Conversion (power supplies and bypassing

are not shown)

V

CM

Input

Voltage

(±0.5 V)

R3

(R3)/2

R3

+

R

R2

R2

51 W

R

RR

R

+

+

51 W

15 pF

51 W

INPUT PROTECTION

All I/O pads are protected with an on-chip protection

circuit. This circuit provides ESD robustness and prevents

latchup under severe discharge conditions without

degrading analog transmission times.

POWER SUPPLIES AND GR OUNDING

The SPT7721 is operated from a single power supply in

the range of 4.75 to 5.25 volts. Normal operation is suggested to be 5.0 volts. All po wer supply pins should be b ypassed as close to the package as possible. The analog

and digital grounds should be connected together with a

ferrite bead as shown in the typical interface circuit and as

close to the ADC as possible.

ADC

V

V

+

IN

IN

SPT

SPT7721

8 2/20/01

Page 9

POWER DO WN MODE

DIGIT AL OUTPUTS

To save on power, the SPT7721 incorporates a powerdown function. This function is controlled by the signal on

pin PD. When pin PD is set high, the SPT7721 enters the

power-down mode . All outputs are set to high impedance.

In the power-down mode the SPT7721 dissipates 10 mW

typically.

REFERENCES

To save on parts count, design time, and PC board real

estate, the SPT7721 utilizes an internal reference. No

other external components are required to implement this

feature.

COMMON MODE VOLTAGE REFERENCE CIRCUIT

The SPT7721 has an on-board common-mode voltage

reference circuit (VCM). It is 2.5 v olts and is capable of driving 50 µA loads typically. The circuit is commonly used to

drive the center tap of the RF transformer in fully differential applications. For single-ended applications, this output

can be used to provide the level shifting required for the

single-to-differential conv erter conversion circuit.

CLOCK INPUT

The clock input on the SPT7721 can be driven by either a

single-ended or double-ended clock circuit and can handle

TTL, PECL, and CMOS signals. When operating at high

sample rates it is important to keep the pulse width of the

clock signal as close to 50% as possible. For TTL/CMOS

single-ended clock inputs, the rise time of the signal also

becomes an important consideration.

The output circuitry of the SPT7721 has been designed to

be able to support three separate output modes. The

demuxed (double-wide) mode supports either parallel

aligned or interleaved data output. The single-channel

mode is not demuxed and can support direct output at

speeds up to 125 MSPS.

The data output mode is set using the DMODE1 and

DMODE2 inputs (pins 32 & 31 respectively). Table I

describes the mode switching options.

Table I – Output Data Modes

Output Mode DMODE1DMODE

Parallel Dual Channel Output 0 0

Interleaved Dual Channel Output 0 1

Single Channel Data Output

(Bank A only 125 MSPS max) 1 X

2

EVALUATION BOARD

The EB7721 evaluation board is av ailable to aid designers

in demonstrating the full performance of the SPT7721.

This board includes a clock driver and reset circuit, adjustable references and common mode , a single-ended to differential input buffer and a single-ended to differential

transformer (1:1). An application note (AN7721) describing the operation of this board, as well as information on

the testing of the SPT7721, is also available. Contact the

factory for price and availability of the EB7721.

SPT

SPT7721

9 2/20/01

Page 10

PACKAGE OUTLINE

44-Lead TQFP

A

B

INCHES MILLIMETERS

SYMBOL MIN MAX MIN MAX

A 0.472 Typ 12.00 Typ

Pin 1

Index

B 0.394 Typ 10.00 Typ

C 0.394 Typ 10.00 Typ

D 0.472 Typ 12.00 Typ

E 0.031 Typ 0.80 Typ

C

D

F 0.012 0.018 0.300 0.45

G 0.053 0.057 1.35 1.45

H 0.002 0.006 0.05 0.15

I 0.020 0.030 0.500 0.750

J 0.039 Typ 1.00 Typ

K 0-7° 0-7°

E F

G

K

H

I

J

SPT

SPT7721

10 2/20/01

Page 11

PIN ASSIGNMENTS

AV

CCAVCC

43

3

AGND

41

42

SPT7721

TOP VIEW

44L TQFP

DA2DA

1

DA

AGND

CLK

CLK

RESET

RESET

OV

DGND

7

(MSB)

DA

DA

PD

AGND

44

1

2

3

4

5

6

DD

6

5

7

8

9

10

11

1213141516

DA4DA

V

IN

+

40

DA

0

(LSB)

V

IN

39

171918

OV

DD

AGND

38

DGND

V

CM

37

DB

0

(LSB)

AV

AV

CC

CC

35

36

202221

DB

1DB2DB3

AGND

34

33

32

31

30

29

28

27

26

25

24

23

AGND

DMODE

DMODE

OV

DD

DGND

DCLK

DCLK

(MSB)

DB

7

DB

6

DB

5

DB

4

PIN FUNCTIONS

Pin Name Description

VIN+ Non-Inverted Analog Input; nominally 1 V

100k pullup to VCC and 100k pulldown to AGND,

internally

V

– Inverted Analog Input; nominally 1 V

IN

1

2

DA

–DA

0

pullup to V

internally

Data output; Bank A. 3 V / 5 V LVCMOS

7

compatible.

DB

–DB7Data output; Bank B. 3 V / 5 V LVCMOS

OUT

OUT

0

DCLK

compatible.

Non-Inverted data output clock. 3 V / 5 V

OUT

LVCMOS compatible.

DCLK

Inverted data output clock. 3 V / 5 V LVCMOS

OUT

compatible.

CLK Non-Inverted clock input pin; 100k pulldown to

AGND, internally

CLK Inverted clock input pin; 17.5k pullup to V

7.5k pulldown to AGND, internally

RESET RESET synchronizes the data sampling and data

output bank relationship when in Dual Channel

Mode (DMODE

7.5k pulldown to AGND, internally

RESET Inverted RESET input pin

DMODE

1,2

Internally:

100k pulldown to AGND on DMODE1

50k pullup to V

Data Output Mode pins:

DMODE

Channel Output

DMODE

Channel Output

DMODE

Data Output on Bank A (125 MSPS max)

PD Power Down pin; PD = 1 for power-down mode.

Outputs set to high impedance in power-down

mode; 100k pulldown to AGND, internally

V

AV

OV

CM

CC

DD

2.5 V Common Mode Voltage Reference Output

+5 V Analog Supply

+3 V / +5 V Digital Output Supply

AGND Analog Ground

DGND Digital Ground

and 100k pulldown to AGND,

CC

= 0); 17.5k pullup to VCC and

1

on DMODE2

CC

= 0, DMODE2 = 0: Parallel Dual

1

= 0, DMODE2 = 1: Interleaved Dual

1

= 1, DMODE2 = X: Single Channel

1

P-P

P-P

; 100k

CC

;

and

ORDERING INFORMATION

PART NUMBER TEMPERATURE RANGE PACKAGE

SPT7721SIT –40 to +85 °C 44L TQFP

Signal Processing Technologies, Inc. reserves the right to change products and specifications without notice. Permission is hereby

expressly granted to copy this literature for informational purposes only. Copying this material for any other use is strictly prohibited.

WARNING – LIFE SUPPORT APPLICATIONS POLICY – SPT products should not be used within Life Support Systems without the

specific written consent of SPT. A Life Support System is a product or system intended to support or sustain life which, if it fails, can

be reasonably expected to result in significant personal injury or death.

Signal Processing Technologies believes that ultrasonic cleaning of its products may damage the wire bonding, leading to

device failure. It is therefore not recommended, and exposure of a device to such a process will void the product warranty.

SPT7721

SPT

11 2/20/01

Loading...

Loading...