Datasheet SN74LS293DR2, SN74LS293N, SN74LS290N, SN74LS293D, SN74LS290D Datasheet (MOTOROLA)

...Page 1

5-1

FAST AND LS TTL DAT A

DECADE COUNTER;

4-BIT BINARY COUNTER

The SN54/74LS290 and SN54/74LS293 are high-speed 4-bit ripple type

counters partitioned into two sections. Each counter has a divide-by-two section and either a divide-by-five (LS290) or divide-by-eight (LS293) section

which are triggered by a HIGH-to-LOW transition on the clock inputs. Each

section can be used separately or tied together (Q to CP

)to form BCD,

Bi-quinary , or Modulo-16 counters. Both of the counters have a 2-input gated

Master Reset (Clear), and the LS290 also has a 2-input gated Master Set

(Preset 9).

• Corner Power Pin Versions of the LS90 and LS93

• Low Power Consumption . . . Typically 45 mW

• High Count Rates . . . Typically 42 MHz

• Choice of Counting Modes . . . BCD, Bi-Quinary, Binary

• Input Clamp Diodes Limit High Speed Termination Effects

14 13 12 11 10 9

123456

8

7

VCCMR MR CP

1CP0Q0Q3

MS NC MS Q2Q1NC GND

CONNECTION DIAGRAM DIP (TOP VIEW)

LS290

LS293

NOTE:

The Flatpak version

has the same pinouts

(Connection Diagram) as

the Dual In-Line Package.

14 13 12 11 10 9

123456

8

7

VCCMR MR CP

1CP0Q0Q3

NC NC NC Q2Q1NC GND

PIN NAMES LOADING (Note a)

HIGH

LOW

CP

0

Clock (Active LOW going edge) Input to ÷2 Section. 0.05 U.L. 1.5 U.L.

CP1 Clock (Active LOW going edge) Input to ÷5 Section (LS290). 0.05 U.L. 2.0 U.L.

CP1 Clock (Active LOW going edge) Input to ÷8 Section (LS293). 0.05 U.L. 1.0 U.L.

MR1, MR2 Master Reset (Clear) Inputs 0.5 U.L. 0.25 U.L.

MS1, MS2 Master Set (Preset-9, LS290) Inputs 0.5 U.L. 0.25 U.L.

Q0 Output from ÷2 Section (Notes b & c) 10 U.L. 5 (2.5) U.L.

Q1, Q2, Q3 Outputs from ÷5 & ÷8 Sections (Note b) 10 U.L. 5 (2.5) U.L.

NOTES:

a) 1 TTL Unit Load (U.L.) = 40 µA HIGH/1.6 mA LOW.

b) The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

c) The Q0 Outputs are guaranteed to drive the full fan-out plus the CP

1

Input of the device.

SN54/74LS290

SN54/74LS293

DECADE COUNTER;

4-BIT BINARY COUNTER

LOW POWER SCHOTTKY

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXD SOIC

J SUFFIX

CERAMIC

CASE 632-08

N SUFFIX

PLASTIC

CASE 646-06

14

1

14

1

14

1

D SUFFIX

SOIC

CASE 751A-02

Page 2

5-2

FAST AND LS TTL DATA

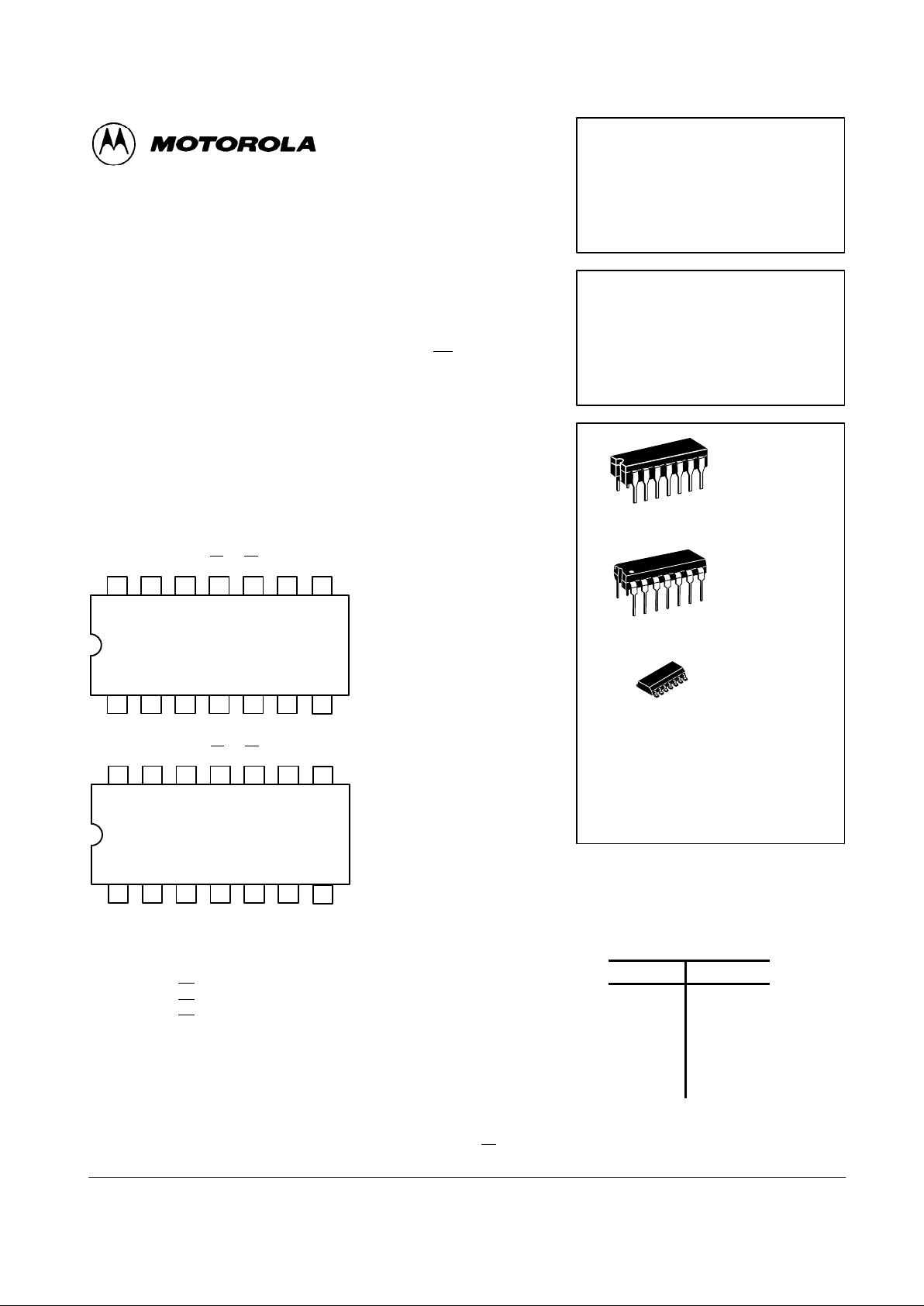

SN54/74LS290 D SN54/74LS293

LOGIC SYMBOL

LS290 LS293

VCC = PIN 14

GND = PIN 7

NC = PINS 2, 6

13

12

12

10

11

MS

CP

0

CP

1

MR Q0Q1Q2Q

3

12 13 9 5 4 8

VCC = PIN 14

GND = PIN 7

NC = PINS 1, 2, 3, 6

12

10

11

CP

0

CP

1

MR Q0Q1Q2Q

3

12 13 9 5 4 8

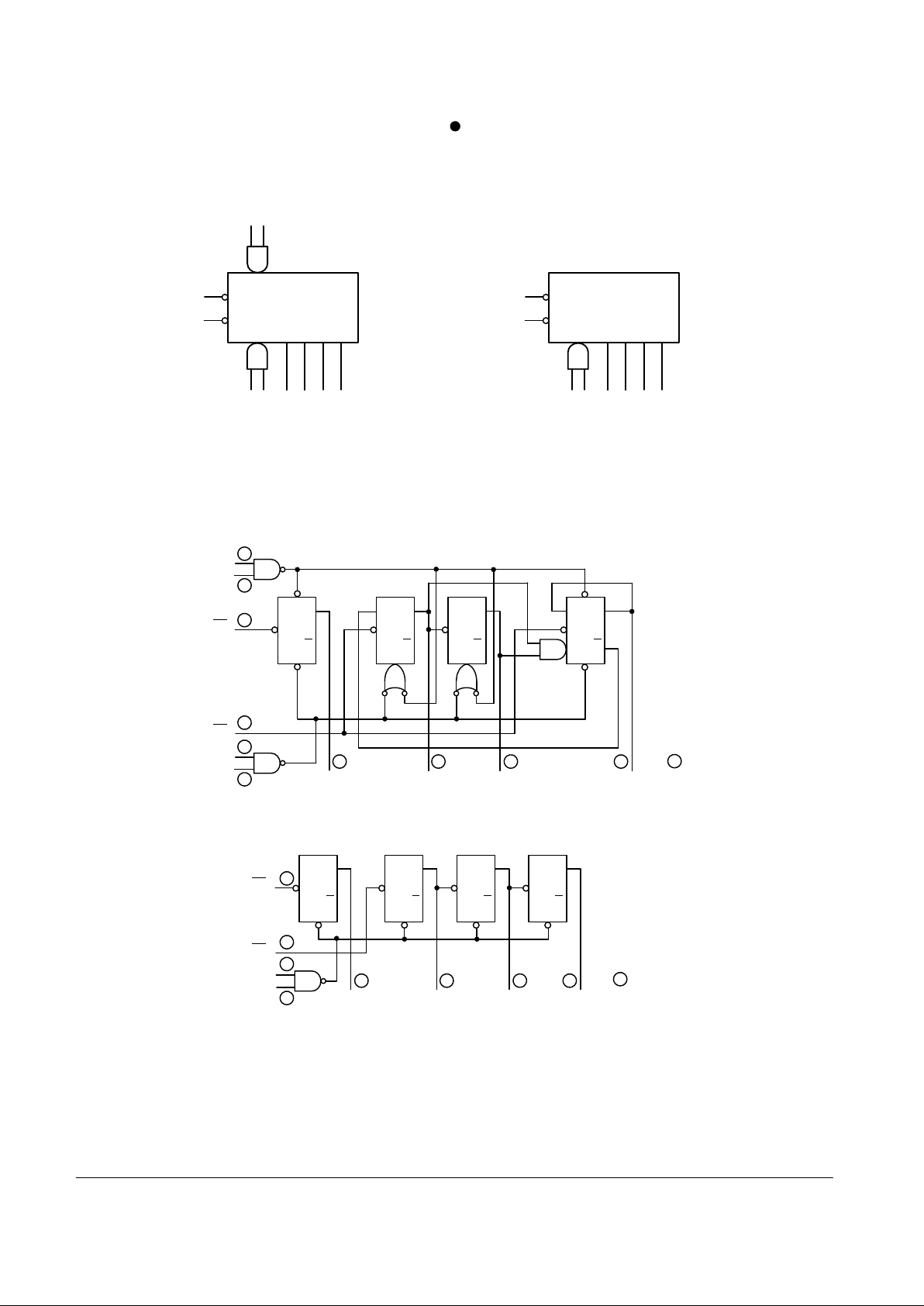

LS290

LS293

LOGIC DIAGRAMS

S

D

J

CP

C

D

Q

QJ

CP

C

D

Q

QJ

CP

C

D

Q

QR

CP

C

D

Q

Q

S

D

KS

J

CP

C

D

Q

Q

K

J

CP

C

D

Q

Q

K

J

CP

C

D

Q

Q

K

J

CP

C

D

Q

Q

K

MS

1

MS

2

CP

0

CP

1

MR

1

MR

2

CP

0

CP

1

MR

1

MR

2

Q

0

Q

1

Q

2

Q

3

Q

0

Q

1

Q

2

Q

3

VCC = PIN 14

GND = PIN 7

= PIN NUMBERS

VCC = PIN 14

GND = PIN 7

= PIN NUMBERS

1

3

8459

11

12

10

13

10

13

11

12

8459

K

Page 3

5-3

FAST AND LS TTL DATA

SN54/74LS290 D SN54/74LS293

FUNCTIONAL DESCRIPTION

The LS290 and LS293 are 4-bit ripple type Decade, and

4-Bit Binary counters respectively. Each device consists of

four master/slave flip-flops which are internally connected to

provide a divide-by-two section and a divide-by-five (LS290)

or divide-by-eight (LS293) section. Each section has a

separate clock input which initiates state changes of the

counter on the HIGH-to-LOW clock transition. State changes

of the Q outputs do not occur simultaneously because of

internal ripple delays. Therefore, decoded output signals are

subject to decoding spikes and should not be used for clocks

or strobes. The Q0 output of each device is designed and

specified to drive the rated fan-out plus the CP

1

input of the

device.

A gated AND asynchronous Master Reset (MR1 ⋅ MR2) is

provided on both counters which overrides the clocks and

resets (clears) all the flip-flops. A gated AND asynchronous

Master Set (MS1 ⋅ MS2) is provided on the LS290 which

overrides the clocks and the MR inputs and sets the outputs to

nine (HLLH).

Since the output from the divide-by-two section is not

internally connected to the succeeding stages, the devices

may be operated in various counting modes:

LS290

A. BCD Decade (8421) Counter — the CP

1

input must be

externally connected to the Q0 output. The CP

0

input

receives the incoming count and a BCD count sequence is

produced.

B. Symmetrical Bi-quinary Divide-By-Ten Counter — The Q

3

output must be externally connected to the CP

0

input. The

input count is then applied to the CP

1

input and a

divide-by-ten square wave is obtained at output Q0.

C. Divide-By-Two and Divide-By-Five Counter — No external

interconnections are required. The first flip-flop is used as a

binary element for the divide-by-two function (CP

0

as the

input and Q0 as the output). The CP

1

input is used to obtain

binary divide-by-five operation at the Q3 output.

LS293

A. 4-Bit Ripple Counter — The output Q0 must be externally

connected to input CP

1

. The input count pulses are applied

to input CP

0

. Simultaneous division of 2, 4, 8, and 16 are

performed at the Q0, Q1, Q2, and Q3 outputs as shown in

the truth table.

B. 3-Bit Ripple Counter — The input count pulses are applied

to input CP

1

. Simultaneous frequency divisions of 2, 4, and

8 are available at the Q1, Q2, and Q3 outputs. Independent

use of the first flip-flop is available if the reset function

coincides with reset of the 3-bit ripple-through counter.

LS290 MODE SELECTION

RESET/SET INPUTS OUTPUTS

MR1MR

2

MS1MS

2

Q0Q1Q

2

Q

3

H H L X L L L L

H H X L L LL L

X X H H HLLH

L X L X Count

X L X L Count

L X X L Count

X L L X Count

LS290

BCD COUNT SEQUENCE

OUTPUT

COUNT

Q0Q1Q

2

Q

3

0 L L L L

1 H LLL

2 LHLL

3 HHLL

4 LLH L

5 HLHL

6 LHH L

7 HHH L

8 LLLH

9 HLLH

NOTE: Output Q0 is connected to Input CP

1

for BCD count.

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don’t Care

LS293 MODE SELECTION

RESET INPUTS OUTPUTS

MR

1

MR

2

Q0Q1Q

2

Q

3

H H L L L L

L H Count

H L Count

L L Count

TRUTH TABLE

OUTPUT

COUNT

Q0Q

1

Q

2

Q

3

0 L L L L

1 H LL L

2 LHL L

3 HHL L

4 LLH L

5 HLH L

6 LHH L

7 HHH L

8 LLL H

9 HLL H

10 L HL H

11 H HL H

12 L LH H

13 H LH H

14 L HH H

15 H H H H

Note: Output Q0 connected to input CP1.

Page 4

5-4

FAST AND LS TTL DATA

SN54/74LS290 • SN54/74LS293

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

CC

Supply Voltage 54

74

4.5

4.75

5.0

5.0

5.5

5.25

V

T

A

Operating Ambient Temperature Range 54

74

–55

0

25

25

125

70

°C

I

OH

Output Current — High 54, 74 –0.4 mA

I

OL

Output Current — Low 54

74

4.0

8.0

mA

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

Symbol Parameter

Min Typ Max

Unit Test Conditions

V

IH

Input HIGH Voltage 2.0 V

Guaranteed Input HIGH Voltage for

All Inputs

54

0.7

Guaranteed Input LOW Voltage for

VILI

nput

LOW Volt

age

74

0.8

V

pg

All Inputs

V

IK

Input Clamp Diode Voltage –0.65 –1.5 V VCC = MIN, IIN = –18 mA

54 2.5 3.5 V

VCC = MIN, IOH = MAX, VIN = V

IH

VOHOutput HIGH Volt

age

74 2.7 3.5 V

CC

,

OH

,

IN IH

or VIL per Truth Table

54, 74 0.25 0.4 V IOL = 4.0 mA

VCC = VCC MIN,

VOLOutput LOW Volt

age

74 0.35 0.5 V IOL = 8.0 mA

V

IN

=

V

IL

or

V

IH

per Truth Table

20 µA VCC = MAX, VIN = 2.7 V

IIHI

nput

HIGH C

urren

t

0.1 mA VCC = MAX, VIN = 7.0 V

I

IL

Input LOW Current

MS, MR

CP

0

CP

1

(LS290)

CP1 (LS293)

–0.4

–2.4

–3.2

–1.6

mA VCC = MAX, VIN = 0.4 V

I

OS

Short Circuit Current (Note 1) –20 –100 mA VCC = MAX

I

CC

Power Supply Current 15 mA VCC = MAX

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

Page 5

5-5

FAST AND LS TTL DATA

SN54/74LS290 D SN54/74LS293

AC CHARACTERISTICS (T

A

= 25°C, VCC = 5.0 V, CL = 15 pF)

Limits

LS290 LS293

Symbol Parameter

Min Typ Max Min Typ Max

Unit

f

MAX

CP0 Input Clock Frequency 32 32 MHz

f

MAX

CP1 Input Clock Frequency 16 16 MHz

t

PLH

t

PHL

Propagation Delay,

CP

0

Input to Q0 Output

10

12

16

18

10

12

16

18

ns

t

PLH

t

PHL

CP0 Input to Q3 Output

32

34

48

50

46

46

70

70

ns

t

PLH

t

PHL

CP1 Input to Q1 Output

10

14

16

21

10

14

16

21

ns

t

PLH

t

PHL

CP

1

Input to Q2 Output

21

23

32

35

21

23

32

35

ns

t

PLH

t

PHL

CP1 Input to Q3 Output

21

23

32

35

34

34

51

51

ns

t

PHL

MS Input to Q0 and Q3 Outputs 20 30 ns

t

PHL

MS Input to Q1 and Q2 Outputs 26 40 ns

t

PHL

MR Input to Any Output 26 40 26 40 ns

AC SETUP REQUIREMENTS (T

A

= 25°C, VCC = 5.0 V)

Limits

LS290 LS293

Symbol Parameter

Min Max Min Max

Unit

t

W

CP0

Pulse Width

15 15 ns

t

W

CP1

Pulse Width

30 30 ns

t

W

MS Pulse Width 15 ns

t

W

MR Pulse Width 15 15 ns

t

rec

Recovery Time MR to CP 25 25 ns

RECOVERY TIME (t

rec

) is defined as the minimum time required between the end of the reset pulse and the clock transition form HIGH-to-LOW in order to

recognize and transfer HIGH data to the Q outputs.

Figure 1

*CP

Q

1.3 V 1.3 V

1.3 V1.3 V

t

PHL

t

PLH

Figure 2 Figure 3

1.3 V 1.3 V

1.3 V

1.3 V

1.3 V1.3 V

1.3 V

1.3 V

MR & MS

CP

Q

t

PHL

t

PLH

MS

CP

Q0 ⋅Q

3

(LS290)

*The number of Clock Pulses required between the t

PHL

and t

PLH

measurements can be determined from the appropriate Truth Tables.

AC WAVEFORMS

t

W

t

W

t

rec

t

W

t

rec

Loading...

Loading...