Page 1

5-1

FAST AND LS TTL DAT A

BCD DECADE/MODULO

16 BINARY SYNCHRONOUS

BI-DIRECTIONAL COUNTERS

The SN54 / 74LS168 and SN54 / 74LS169 are fully synchronous 4-stage

up/down counters featuring a preset capability for programmable operation,

carry lookahead for easy cascading and a U/D input to control the direction

of counting. The SN54/74LS168 counts in a BCD decade (8, 4, 2, 1)

sequence, while the SN54/74LS169 operates in a Modulo 16 binary

sequence. All state changes, whether in counting or parallel loading, are

initiated by the LOW-to-HIGH transition of the clock.

• Low Power Dissipation 100 mW Typical

• High-Speed Count Frequency 30 MHz Typical

• Fully Synchronous Operation

• Full Carry Lookahead for Easy Cascading

• Single Up/Down Control Input

• Positive Edge-Trigger Operation

• Input Clamp Diodes Limit High-Speed Termination Effects

NOTE:

The Flatpak version

has the same pinouts

(Connection Diagram) as

the Dual In-Line Package.

14 13 12 11 10 9

123456

7

16 15

8

V

CC

U/D

TC Q0Q1Q

2

CETQ

3

PE

CP P0P1P2P3CEP GND

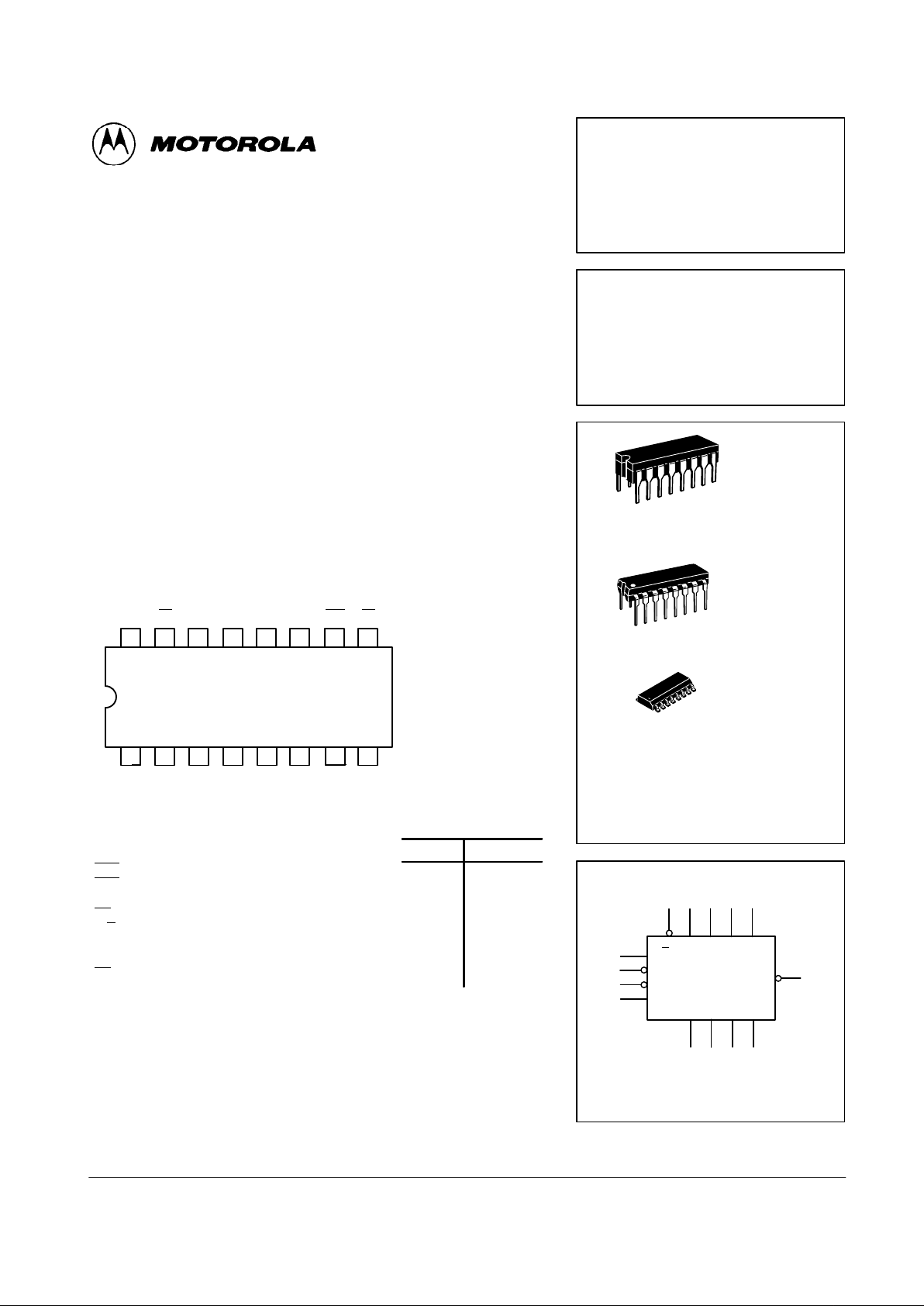

CONNECTION DIAGRAM DIP (TOP VIEW)

PIN NAMES LOADING (Note a)

HIGH

LOW

CEP

CET

CP

PE

U/D

P0–P

3

Q0–Q

3

TC

Count Enable Parallel (Active LOW) Input

Count Enable Trickle (Active LOW) Input

Clock Pulse (Active positive going edge) Input

Parallel Enable (Active LOW) Input

Up-Down Count Control Input

Parallel Data Inputs

Flip-Flop Outputs

Terminal Count (Active LOW) Output

0.5 U.L.

1.0 U.L.

0.5 U.L.

0.5 U.L.

0.5 U.L.

0.5 U.L.

10 U.L.

10 U.L.

0.25 U.L.

0.5 U.L.

0.25 U.L.

0.25 U.L.

0.25 U.L.

0.25 U.L.

5 (2.5) U.L.

5 (2.5) U.L.

NOTES:

a. 1 TTL Unit Load (U.L.) = 40 µA HIGH/1.6 mA LOW.

b. The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74)

b. T emperature Ranges.

SN54/74LS168

SN54/74LS169

BCD DECADE/MODULO

16 BINARY SYNCHRONOUS

BI-DIRECTIONAL COUNTERS

LOW POWER SCHOTTKY

J SUFFIX

CERAMIC

CASE 620-09

N SUFFIX

PLASTIC

CASE 648-08

16

1

16

1

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXD SOIC

16

1

D SUFFIX

SOIC

CASE 751B-03

LOGIC SYMBOL

934 56

7

10

2

15

14 13 12 11

PE P0P1P2P

3

CEP

CET

CP

Q0Q1Q2Q

3

TC

VCC = PIN 16

GND = PIN 8

1

U/D

Page 2

5-2

FAST AND LS TTL DATA

SN54/74LS168 • SN54/74LS169

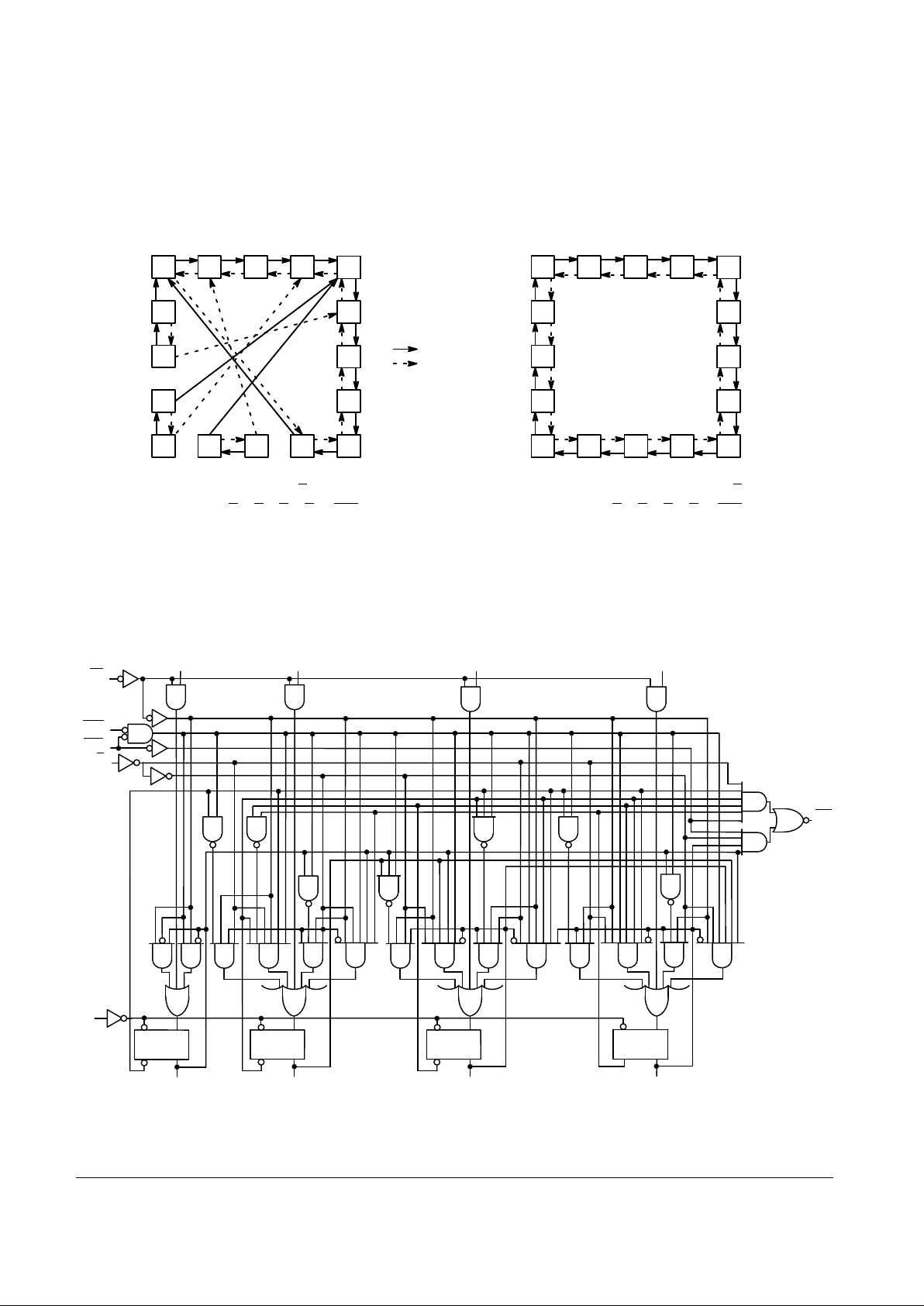

STATE DIAGRAMS

SN54/74LS168

UP/DOWN DECADE COUNTER

0123

4

5

6

7

891011

12

13

14

15

0123

4

5

6

7

891011

12

13

14

15

SN54/74LS169

LOGIC DIAGRAMS

TC

PE

CEP

CET

U/D

CP

P

0

P

1

P

2

P

3

Q

0

Q

1

Q

2

Q

3

CP D

SN54/74LS168

SN54/74LS168

UP: TC = Q0 ⋅ Q3 ⋅ (U/D

)

DOWN: TC = Q

0

⋅ Q1 ⋅ Q2 ⋅ Q3 ⋅ (U/D)

SN54/74LS169

UP: TC = Q0 ⋅ Q1 ⋅ Q2 ⋅ Q3 ⋅ (U/D

)

DOWN: TC = Q

0

⋅ Q1 ⋅ Q2 ⋅ Q3 ⋅ (U/D)

Count Up

Count Down

Page 3

5-3

FAST AND LS TTL DATA

SN54/74LS168 • SN54/74LS169

LOGIC DIAGRAMS (continued)

SN54/74LS169

TC

PE

CEP

CET

U/D

CP

P

0

P

1

P

2

P

3

Q

0

Q

1

Q

2

Q

3

CP D

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

CC

Supply Voltage 54

74

4.5

4.75

5.0

5.0

5.5

5.25

V

T

A

Operating Ambient Temperature Range 54

74

–55

0

25

25

125

70

°C

I

OH

Output Current — High 54, 74 –0.4 mA

I

OL

Output Current — Low 54

74

4.0

8.0

mA

Page 4

5-4

FAST AND LS TTL DATA

SN54/74LS168 • SN54/74LS169

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

Symbol Parameter

Min Typ Max

Unit Test Conditions

V

IH

Input HIGH Voltage 2.0 V

Guaranteed Input HIGH Voltage for

All Inputs

54 0.7

Guaranteed Input LOW Voltage for

VILI

nput

LOW Volt

age

74 0.8

V

pg

All Inputs

V

IK

Input Clamp Diode Voltage –0.65 –1.5 V VCC = MIN, IIN = –18 mA

54 2.5 3.5 V

VCC = MIN, IOH = MAX, VIN = V

IH

VOHOutput HIGH Volt

age

74 2.7 3.5 V

CC

,

OH

,

IN IH

or VIL per Truth Table

54, 74 0.25 0.4 V IOL = 4.0 mA

VCC = VCC MIN,

VOLOutput LOW Volt

age

74 0.35 0.5 V IOL = 8.0 mA

V

IN

=

V

IL

or

V

IH

per Truth Table

I

IH

Input HIGH Current

Other Inputs

CET

Input

20

40

µA VCC = MAX, VIN = 2.7 V

I

IH

Other Input

CET

Input

0.1

0.2

mA VCC = MAX, VIN = 7.0 V

I

IL

Input LOW Current

Other Input

CET

Input

–0.4

–0.8

mA VCC = MAX, VIN = 0.4 V

I

OS

Short Circuit Current (Note 1) –20 –100 mA VCC = MAX

I

CC

Power Supply Current 34 mA VCC = MAX

Note 1: Not more than one output should be shorted at one time, nor for more than 1 second.

FUNCTIONAL DESCRIPTION

The SN54/74LS168 and SN54/74LS169 use edgetriggered D-type flip-flops that have no constraints on

changing the control or data input signals in either state of the

Clock. The only requirement is that the various inputs attain

the desired state at least a set-up time before the rising edge of

the clock and remain valid for the recommended hold time

thereafter.

The parallel load operation takes precedence over the other

operations, as indicated in the Mode Select T able. When PE

is

LOW, the data on the P0–P3 inputs enters the flip-flops on the

next rising edge of the Clock. In order for counting to occur,

both CEP

and CET must be LOW and PE must be HIGH. The

U/D

input then determines the direction of counting.

The T erminal Count (TC

) output is normally HIGH and goes

LOW, provided that CET

is LOW, when a counter reaches zero

in the COUNT DOWN mode or reaches 15 (9 for the

SN54/74LS168) in the COUNT UP mode. The TC

output state

is not a function of the Count Enable Parallel (CEP

) input level.

The TC

output of the SN54/74LS168 decade counter can also

be LOW in the illegal states 11, 13 and 15, which can occur

when power is turned on or via parallel loading. If illegal state

occurs, the SN54/74LS168 will return to the legitimate

sequence within two counts. Since the TC

signal is derived by

decoding the flip-flop states, there exists the possibility of

decoding spikes on TC

. For this reason the use of TC as a

clock signal is not recommended.

MODE SELECT TABLE

PE CEP CET U/D Action on Rising Clock Edge

L X X X Load (Pn → Qn)

H L L H Count Up (increment)

H L L L Count Down (decrement)

H H X X No Change (Hold)

H X H X No Change (Hold)

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Page 5

5-5

FAST AND LS TTL DATA

SN54/74LS168 • SN54/74LS169

AC CHARACTERISTICS (T

A

= 25°C, VCC = 5.0 V)

Limits

Symbol Parameter

Min Typ Max

Unit Test Conditions

f

MAX

Maximum Clock Frequency 25 32 MHz

t

PLH

t

PHL

Propagation Delay,

Clock to TC

23

23

35

35

ns

t

PLH

t

PHL

Propagation Delay,

Clock to any Q

13

15

20

23

ns

VCC = 5.0 V

C

= 15 pF

t

PLH

t

PHL

Propagation Delay,

CET

to TC

15

15

20

20

ns

C

L

= 15

pF

t

PLH

t

PHL

Propagation Delay,

U/D to TC

17

19

25

29

ns

AC SETUP REQUIREMENTS (T

A

= 25°C)

Limits

Symbol Parameter

Min Typ Max

Unit Test Conditions

t

W

Clock Pulse Width 25 ns

t

s

Setup Time,

Data or Enable

20 ns

t

s

Setup Time

PE

25 ns

VCC = 5.0 V

t

s

Setup Time

U/D

30 ns

t

h

Hold Time

Any Input

0 ns

Page 6

5-6

FAST AND LS TTL DATA

SN54/74LS168 • SN54/74LS169

AC WAVEFORMS

Figure 1. Clock to Output Delays,

Count Frequency, and Clock Pulse Width

Figure 2. Count Enable Trickle Input

To Terminal Count Output Delays

Figure 3. Clock to Terminal Delays Figure 4. Setup Time (ts) and Hold (th)

for Parallel Data Inputs

1.3 V 1.3 V

1.3 V 1.3 V

1.3 V 1.3 V

1.3 V

1.3 V

CP

Q OR TC

t

PHL

t

PLH

t

PLH

t

PHL

CET

TC

1/f

max

t

W

1.3 V

1.3 V 1.3 V 1.3 V

1.3 V 1.3 V

1.3 V 1.3 V

ts(H)

ts(L)

th(L) = 0th(H) = 0

Q0

•

Q1 • Q2 • Q

3

CP

TC

t

PLH

t

PHL

1.3 V 1.3 V1.3 V1.3 VP0 • P1 • P2 • P

3

1.3 V

1.3 V

1.3 V 1.3 V 1.3 V

1.3 V 1.3 V

1.3 V 1.3 V

SR OR PE

CP

U/D

TC

ts(L)

ts(H)

th(L) = 0th(H) = 0

ts(H)

th(H) = 0 th(L) = 0

ts(H)

ts(L)

t

PLH

t

PHL

1.3 V 1.3 V

1.3 V

1.3 V

1.3 V1.3 V

1.3 V

1.3 V

1.3 V 1.3 V1.3 V1.3 V

t

s(L)

th(L) = 0 th(H) = 0

Figure 5. Setup Time and Hold Time for

Count Enable and Parallel Enable Inputs,

and Up-Down Control Inputs

Figure 6. Up-Down Input to

Terminal Count Output Delays

The shaded areas indicate when the

input is permitted to change for

predictable output performance.

CP

CEP

CET

CP

Loading...

Loading...