Page 1

5-1

FAST AND LS TTL DATA

8-BIT SHIFT REGISTERS

The SN54L/ 74LS166 is an 8-Bit Shift Register. Designed with all inputs

buffered, the drive requirements are lowered to one 54/74LS standard load.

By utilizing input clamping diodes, switching transients are minimized and

system design simplified.

The LS166 is a parallel-in or serial-in, serial-out shift register and has a

complexity of 77 equivalent gates with gated clock inputs and an overriding

clear input. The shift/load input establishes the parallel-in or serial-in mode.

When high, this input enables the serial data input and couples the eight

flip-flops for serial shifting with each clock pulse. Synchronous loading occurs

on the next clock pulse when this is low and the parallel data inputs are

enabled. Serial data flow is inhibited during parallel loading. Clocking is done

on the low-to-high level edge of the clock pulse via a two input positive NOR

gate, which permits one input to be used as a clock enable or clock inhibit

function. Clocking is inhibited when either of the clock inputs are held high,

holding either input low enables the other clock input. This will allow the

system clock to be free running and the register stopped on command with

the other clock input. A change from low-to-high on the clock inhibit input

should only be done when the clock input is high. A buffered direct clear input

overrides all other inputs, including the clock, and sets all flip-flops to zero.

• Synchronous Load

• Direct Overriding Clear

• Parallel to Serial Conversion

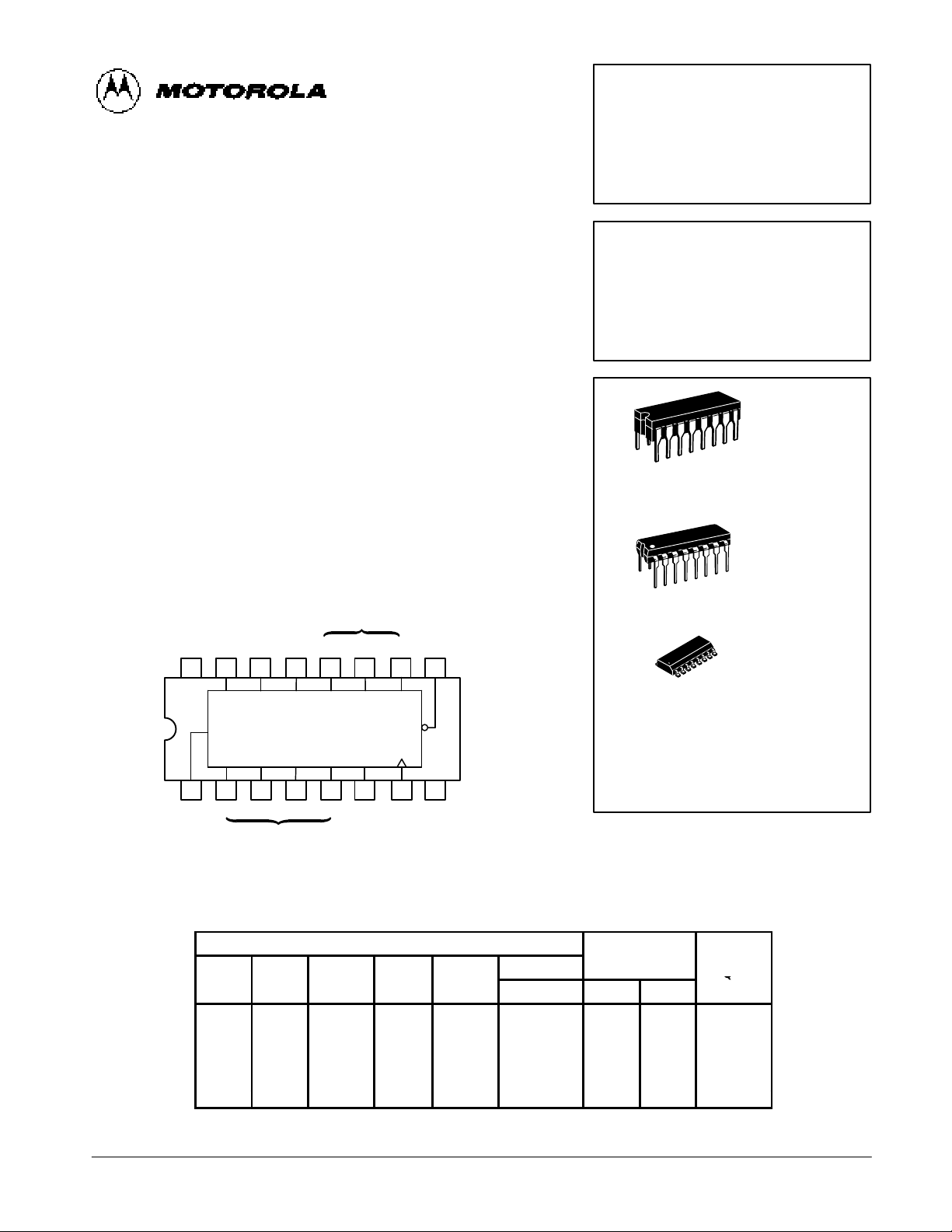

14 13 12 11 10 9

1 2 3 4 5 6

7

16 15

8

V

CC

SERIAL

INPUT

SHIFT/

LOAD

H QHG EF CLEAR

A B C D CLOCK

INHIBIT

CLOCK GND

PARALLEL PARALLEL INPUTS

INPUT OUTPUT

PARALLEL INPUTS

SHIFT/

LOAD

SERIAL INPUT

CLOCK

INHIBIT

H QHG F E

A B C D

CK

CLEAR

FUNCTION TABLE

INPUTS

INTERNAL

SHIFT/

CLOCK

PARALLEL

INTERNAL

OUTPUTS

OUTPUT

Q

CLEAR

SHIFT/

LOAD

CLOCK

INHIBIT

CLOCK

SERIAL

A . . . H Q

A

Q

B

Q

H

L X X X X X L L L

H X L L X X Q

A0

Q

B0

Q

H0

H L L ↑ X a . . . h a b h

H H L ↑ H X H Q

An

Q

Gn

H H L ↑ L X L Q

An

Q

Gn

H X H ↑ X X Q

A0

Q

B0

Q

H0

SN54/74LS166

8-BIT SHIFT REGISTERS

LOW POWER SCHOTTKY

J SUFFIX

CERAMIC

CASE 620-09

N SUFFIX

PLASTIC

CASE 648-08

16

1

16

1

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXD SOIC

16

1

D SUFFIX

SOIC

CASE 751B-03

Page 2

5-2

FAST AND LS TTL DATA

SN54/74LS166

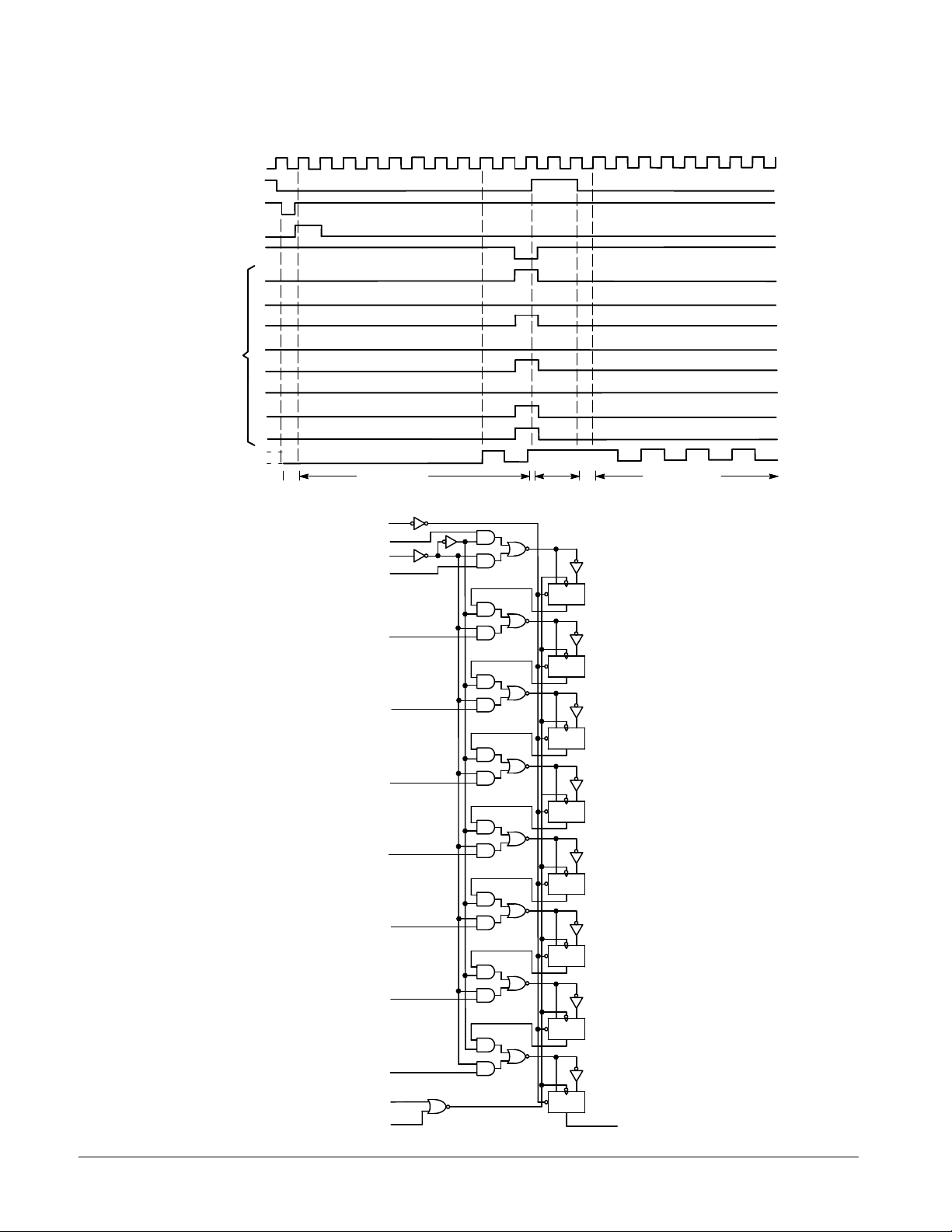

Typical Clear, Shift, Load, Inhibit, and Shift Sequences

PARALLEL

INPUTS

A

B

C

D

CLOCK INIHIBIT

CLOCK

SHIFT/LOAD

H

OUTPUT Q

H

G

F

E

CLEAR

SERIAL INPUT

H

H

H

H

H

L

L

L

H H H H H

L L

L

CLEAR

SERIAL SHIFT

LOAD

INHIBIT

SERIAL SHIFT

CLEAR

SERIAL INPUT

SHIFT/LOAD

A

B

C

D

H

G

F

E

(9)

(1)

(15)

(2)

(3)

(4)

(5)

(10)

(11)

(12)

(14)

(7)

(6)

CLOCK INHIBIT

CLOCK

(13)

RCKS

Q

A

RCKS

Q

B

RCKS

Q

C

RCKS

Q

D

RCKS

Q

E

RCKS

Q

F

RCKS

Q

G

RCKS

Q

H

Page 3

5-3

FAST AND LS TTL DATA

SN54/74LS166

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

CC

Supply Voltage 54

74

4.5

4.75

5.0

5.0

5.5

5.25

V

T

A

Operating Ambient Temperature Range 54

74

–55

0

25

25

125

70

°C

I

OH

Output Current — High 54, 74 –0.4 mA

I

OL

Output Current — Low 54

74

4.0

8.0

mA

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

Symbol

Parameter

Min Typ Max

Unit

Test Conditions

V

IH

Input HIGH Voltage 2.0 V

Guaranteed Input HIGH Voltage for

All Inputs

54 0.7

VILInput LOW Voltage

74 0.8

V

Guaranteed Input LOW Voltage for

All Inputs

V

IK

Input Clamp Diode Voltage –0.65 –1.5 V VCC = MIN, IIN = –18 mA

54 2.5 3.5 V

CC

= MIN, IOH = MAX, VIN = V

IH

VOHOutput HIGH Voltage

74 2.7 3.5 V

VCC = MIN, IOH = MAX, VIN = V

IH

or VIL per Truth Table

54, 74 0.25 0.4 V IOL = 4.0 mA

VOLOutput LOW Voltage

74 0.35 0.5 V IOL = 8.0 mA

VIN = VIL or V

IH

per Truth Table

20 µA VCC = MAX, VIN = 2.7 V

IIHInput HIGH Current

0.1 mA VCC = MAX, VIN = 7.0 V

I

IL

Input LOW Current –0.4 mA VCC = MAX, VIN = 0.4 V

I

OS

Short Circuit Current (Note 1) –20 –100 mA VCC = MAX

I

CC

Power Supply Current 38 mA VCC = MAX

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

Guaranteed Input LOW Voltage for

V

VCC = VCC MIN,

Page 4

5-4

FAST AND LS TTL DATA

SN54/74LS166

TEST TABLE FOR SYNCHRONOUS INPUTS

DATA INPUT

FOR TEST

SHIFT/LOAD OUTPUT TESTED

H 0 V QH at t

n+1

Serial

Input

4.5 V QH at t

n+8

AC WAVEFORMS

NOTE 1. tn = bit time before clocking transition

NOTE 1. t

n+1

= bit time after one clocking transition

NOTE 1. t

n+8

= bit time after eight clocking transition

NOTE 1. LS166 V

ref

= 1.3 V.

CLEAR INPUT

CLOCK INPUT

DATA

INPUT

(SEE TEST

TABLE)

OUTPUT Q

V

ref

t

w(clear)

t

PHL

(clear-Q)

(SEE NOTE 1)

tn +

1

t

n

t

su

t

h

t

PLH

(CLK-Q)

3 V

0 V

V

OH

V

OL

3 V

3 V

0 V

0 V

V

ref

V

ref

V

ref

V

ref

V

ref

V

ref

V

ref

V

ref

t

n

tn +

1

t

su

t

h

t

PHL

t

w(clock)

(CLK-Q)

V

ref

V

ref

V

ref

AC CHARACTERISTICS (T

A

= 25°C)

Limits

Symbol

Parameter

Min Typ Max

Unit

Test Conditions

f

MAX

Maximum Clock Frequency 25 35 MHz

t

PHL

Clear to Output 19 30 ns

t

PLH

t

PHL

Clock to Output

23

24

35

35

ns

CC

= 5.0 V

CL = 15 pF

AC SETUP REQUIREMENTS (T

A

= 25°C)

Limits

Symbol

Parameter

Min Typ Max

Unit

Test Conditions

t

W

Clock Clear Pulse Width 30 ns

t

s

Mode Control Setup Time 30 ns

t

s

Data Setup Time 20 ns

VCC = 5.0 V

t

h

Hold Time, Any Input 15 ns

VCC = 5.0 V

Loading...

Loading...