Page 1

SUMMIT

MICROELECTRONICS, Inc.

Distributed Power Hot-Swap Controller

FEATURES

SMH4812

Preliminary

!!

! Soft Starts Main Power Supply on Card Insertion

!!

or System Power Up

!!

! Senses Card Insertion via Short Pins or Ejector

!!

Switches

!!

! Master Enable to Allow System Control of Power

!!

Up or Down

""

" Can be used as a Temperature Sense Input

""

!!

! Programmable Independent Controls of a DC/DC

!!

Converter

""

" Not Enabled until Host Supply Fully Soft

""

Started

""

" Programmable Time Delay

""

""

" Available Input to hold off Dependant Enables

""

until Conditions are Satisfied

!!

! Highly Programmable Circuit Breaker

!!

""

" Programmable Quick-Trip

""

""

" Programmable Current Limiting

""

""

" Programmable Duty Cycle Times

""

""

" Programmable Over-current Filter

""

TM

Values

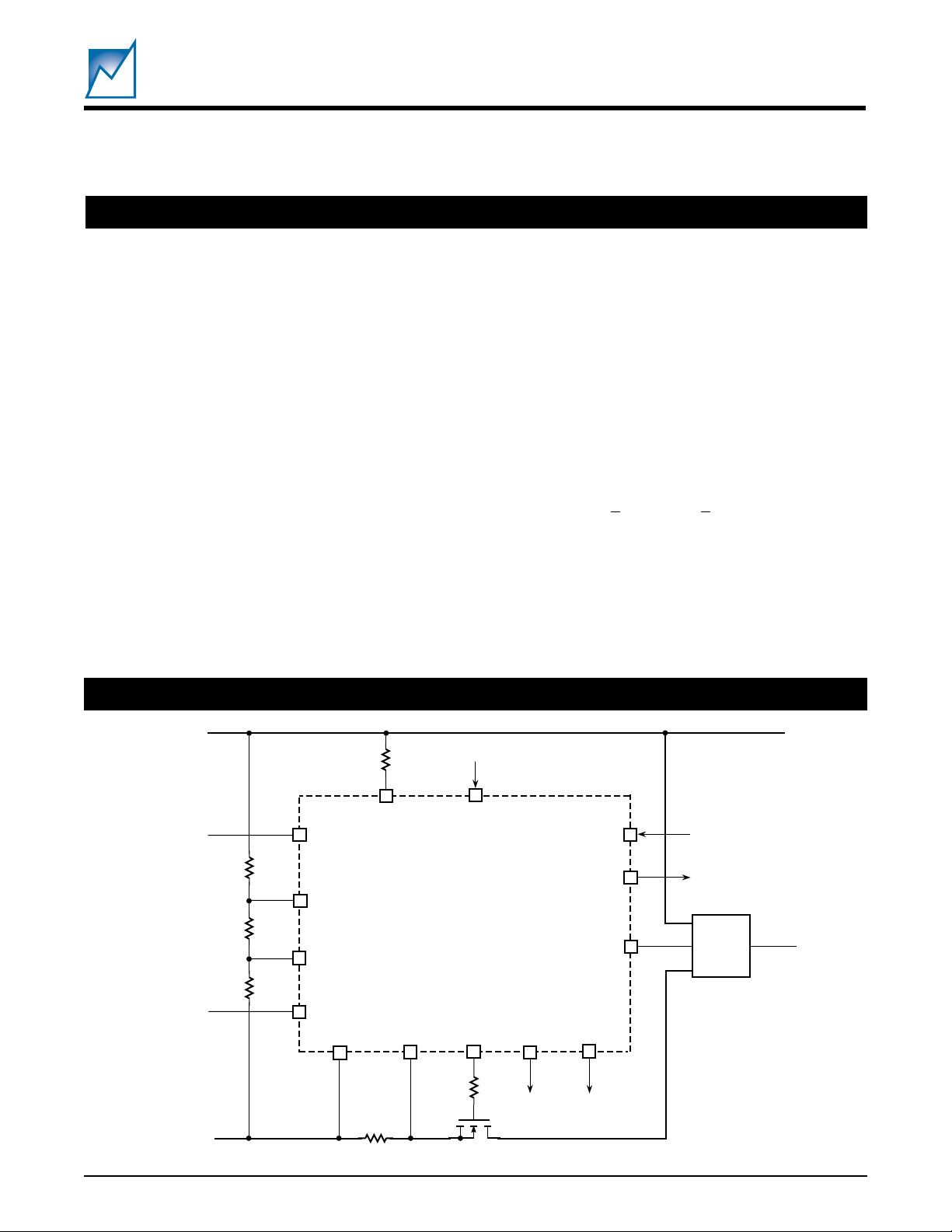

SIMPLIFIED APPLICATION DRAWING

!!

! Programmable Host Voltage Fault Monitoring

!!

""

" Programmable Under-Voltage Hysteresis

""

""

" Programmable UV/OV Voltage Filter

""

""

" Programmable Fault Mode: Latched or Duty

""

Cycle

!!

! Programmable Forced Shutdown Timer

!!

!!

! 2.5V and 5.0V Reference Outputs

!!

""

" Eliminates the Need for Other Primary Volt-

""

ages

""

" Easy Expansion of External Monitor Func-

""

tions

!!

! Supply Range +20VDC to >+500VDC

!!

0V

Disable/Enable

ENPG

FS#

FAULT#

Pin Detect

VDD

PD1#

UV

SMH4812

PG2#

5.0VREF

Pin Detect

OV

PD2#

VSS

CBSENSE

VGATE

2.5VREF

–48V

©SUMMIT MICROELECTRONICS, Inc., 2000 • 300 Orchard City Dr., Suite 131 • Campbell, CA 95008 • Phone 408-378-3970 • FAX 408-378-6586 • www.summitmicro.com

Characteristics subject to change without notice

2055 4.0 12/22/00

DC/DC

2055 SAD 1.1

1

Page 2

DESCRIPTION

SMH4812

Preliminary

The SMH4812 is designed to control hot swapping of plugin cards operating from a single supply, which can have an

output range from 20V to 500V. The SMH4812 hot-swap

controller provides under-voltage and over-voltage monitoring of the host power supply, it drives an external power

MOSFET switch that connects the supply to the load, and

it protects against over-current conditions that might disrupt the host supply. When the input and output voltages

to the SMH4812 controller are within specification it pro-

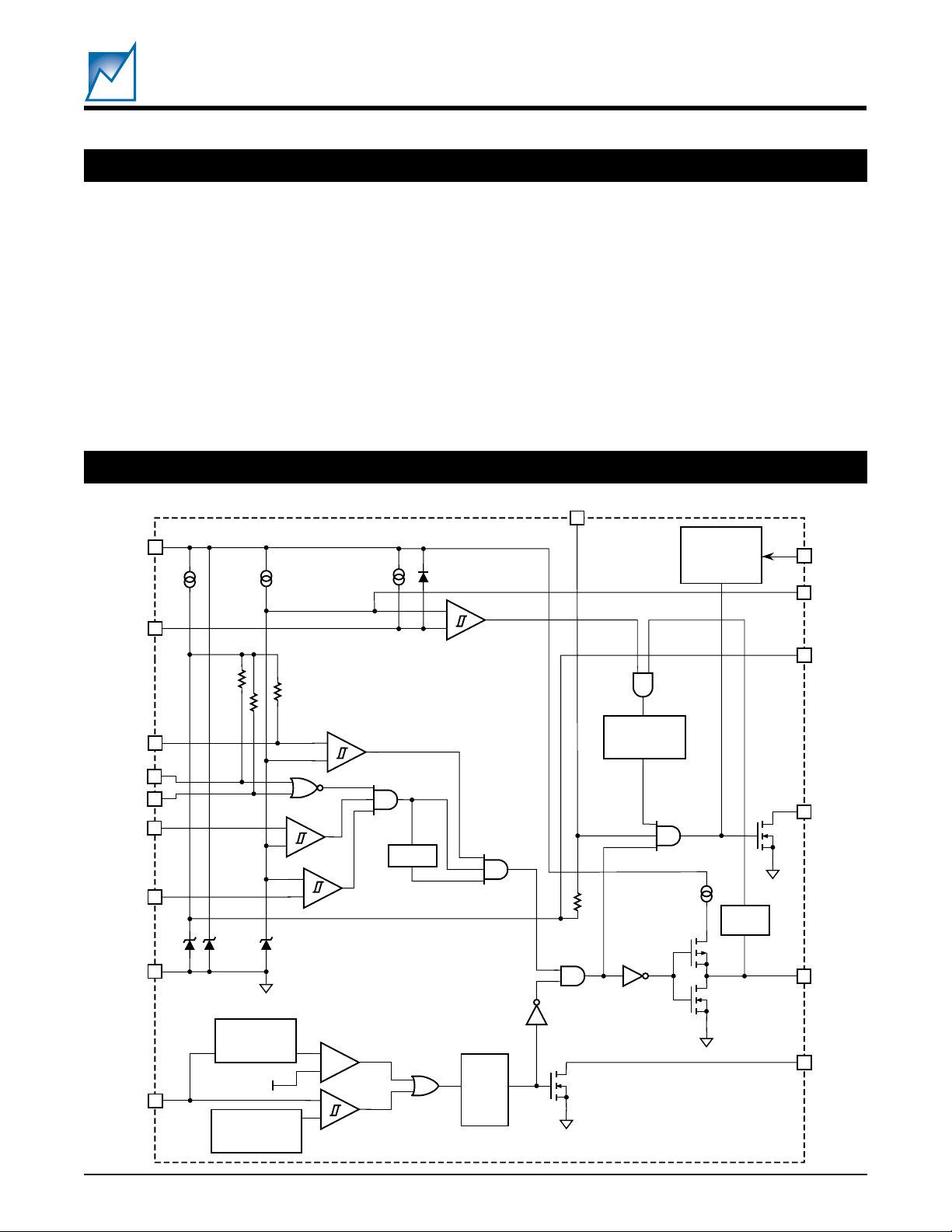

FUNCTIONAL BLOCK DIAGRAM

VDD

DRAIN

SENSE

16

1

50kΩ

12VREF

+

–

vides a Power Good logic output that may be used to

enable a DC-DC converter. Additional features of the

device include: temperature sense or master enable

input, 2.5V and 5V reference outputs for expanding monitor functions, two Pin-Detect enable inputs for fault protection, and duty-cycle or latched over-current protection

modes. All of these features can be programmed by the

factory according to the user's requirements.

ENPG

14

PROGRAMM-

ABLE

SHUTDOWN

TIMER

13

12

11

FS#

2.5VREF

5.0VREF

EN/TS

PD1#

PD2#

VSS

CBSENSE

2

UV

OV

50kΩ

50kΩ

3

4

5

9

10

12V

5V

8

PROGRAMM-

7

Programmable

Quick Response

2.5V

ABLE

DELAY

50mV

Ref. Voltage

+

–

+

–

+

–

+

–

+

–

FILTER

DUTY

CYCLE

TIMER

2055 4.0 12/22/00

50kΩ

PROGRAMM-

ABLE

DELAY

15

PG#

VGATE

SENSE

2

VGATE

6

FAULT#

2055 BD 3.0

SUMMIT MICROELECTRONICS, Inc.

Page 3

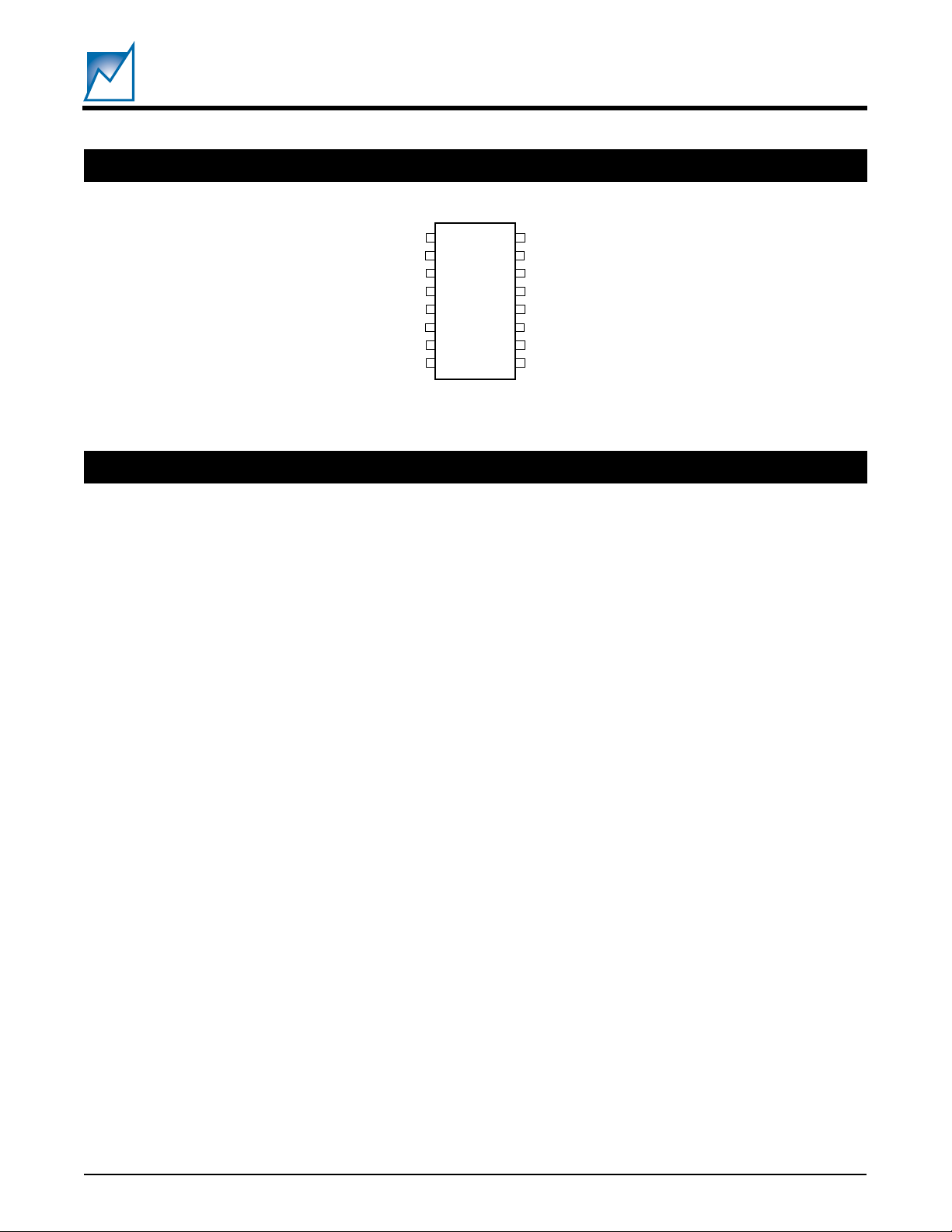

PIN CONFIGURATION

SMH4812

Preliminary

SS

1

2

3

4

5

6

7

8

DRAIN SENSE

VGATE

EN/TS

PD1#

PD2#

FAULT#

CBSENSE

V

PIN DESCRIPTIONS

DRAIN SENSE (1)

The DRAIN SENSE input monitors the voltage at the drain

of the external power MOSFET switch with respect to VSS.

An internal 10µA source pulls the DRAIN SENSE signal

towards the 5V reference level. DRAIN SENSE must be

held below 2.5V to enable the PG outputs.

EN/TS (3)

The Enable/Temperature Sense input is the master enable input. If EN/TS is less than 2.5V, VGATE will be

disabled. This pin has an internal 200kW pull-up to 5V.

V

16

15

14

13

12

11

10

PG#

ENPG

FS#

2.5V

5V

OV

UV

9

2055 PCon 2.0

DD

REF

REF

OV (10)

The OV pin is used as an over-voltage supply monitor,

typically in conjunction with an external resistor ladder.

VGATE will be disabled if OV is greater than 2.5V. A filter

delay is available on the OV input.

VGATE (2)

The VGATE output activates an external power MOSFET

switch. This signal supplies a constant current output

(100µA typical), which allows easy adjustment of the

MOSFET turn on slew rate.

PD1#, PD2# (4, 5)

These are logic level active low inputs that can optionally

be employed to enable VGATE and the PG outputs when

they are at VSS. These pins each have an internal 50kW

pull-up to 5V.

CBSENSE (7)

The circuit breaker sense input is used to detect overcurrent conditions across an external, low value sense

resistor (RS) tied in series with the Power MOSFET. A

voltage drop of greater than 50mV across the resistor for

longer than t

will trip the circuit breaker. A program-

CBD

mable Quick-Trip sense point is also available.

UV (9)

The UV pin is used as an under-voltage supply monitor,

typically in conjunction with an external resistor ladder.

VGATE will be disabled if UV is less than 2.5V. Programmable internal hysteresis is available on the UV input,

adjustable in increments of 62.5mV. Also available is a

filter delay on the UV input.

FAULT# (6)

FAULT# is an open-drain, active-low output that indicates

the fault status of the device.

5VREF (11)

This is a precision 5V output reference voltage that may be

used to expand the logic input functions on the SMH4812.

The reference output is with respect to VSS.

2.5VREF (12)

This is a precision 2.5V output reference voltage that may

be used to expand the logic input functions on the

SMH4812. The reference output is with respect to VSS.

FS# (13)

The Forced Shutdown (FS#) pin is an active low input that

causes VGATE and PG outputs to be shut down at any

time after an internal hold-off timer has expired. The holdoff timer allows supervisory circuits on the secondary side

(which are not powered up initially) to control shut down of

the SMH4812 via an opto-isolator. This input has no pullup resistor.

SUMMIT MICROELECTRONICS, Inc.

2055 4.0 12/22/00

3

Page 4

SMH4812

Preliminary

ENPG (14)

The ENPG input controls the PG# output. When ENPG is

pulled low the PG# output is immediately placed in a high

impedance state. If ENPG is driven high then the PG#

output will immediately be driven low.

PG# (15)

PG# is an open-drain, active-low output with no internal

pull-up resistor. It can be used to switch a load or enable

a DC/DC converter. PG# is enabled immediately after

VGATE reaches V

– VGT and the DRAIN SENSE

DD

voltage is less than 2.5V. Voltage on these pins cannot

exceed 12V, as referenced to V

SS.

VDD (16)

VDD is the positive supply connection. An internal shunt

regulator connected between VDD and VSS develops approximately 12V that supplies the SMH4812. A resistor

must be placed in series with the VDD pin to limit the

regulator current (RD in the application illustrations).

V

(8)

SS

VSS is connected to the negative side of the supply.

4

2055 4.0 12/22/00

SUMMIT MICROELECTRONICS, Inc.

Page 5

ABSOLUTE MAXIMUM RATINGS*

SMH4812

Preliminary

Temperature Under Bias ...................... –55°C to 125°C

Storage Temperature ........................... –65°C to 150°C

Lead Solder Temperature (10 secs) ................... 300 °C

Terminal Voltage with Respect to VSS:

V

................................. –0.5V to V

DD

DD

OV, UV, DRAIN SENSE,

FS#, CBSENSE .....–0.5V to VDD+0.5V

PD1#, PD2#, ENPG, EN/TS ......... 10V

FAULT#, PG# ........–0.5V to VDD+0.5V

VGATE ................................ VDD+0.5V

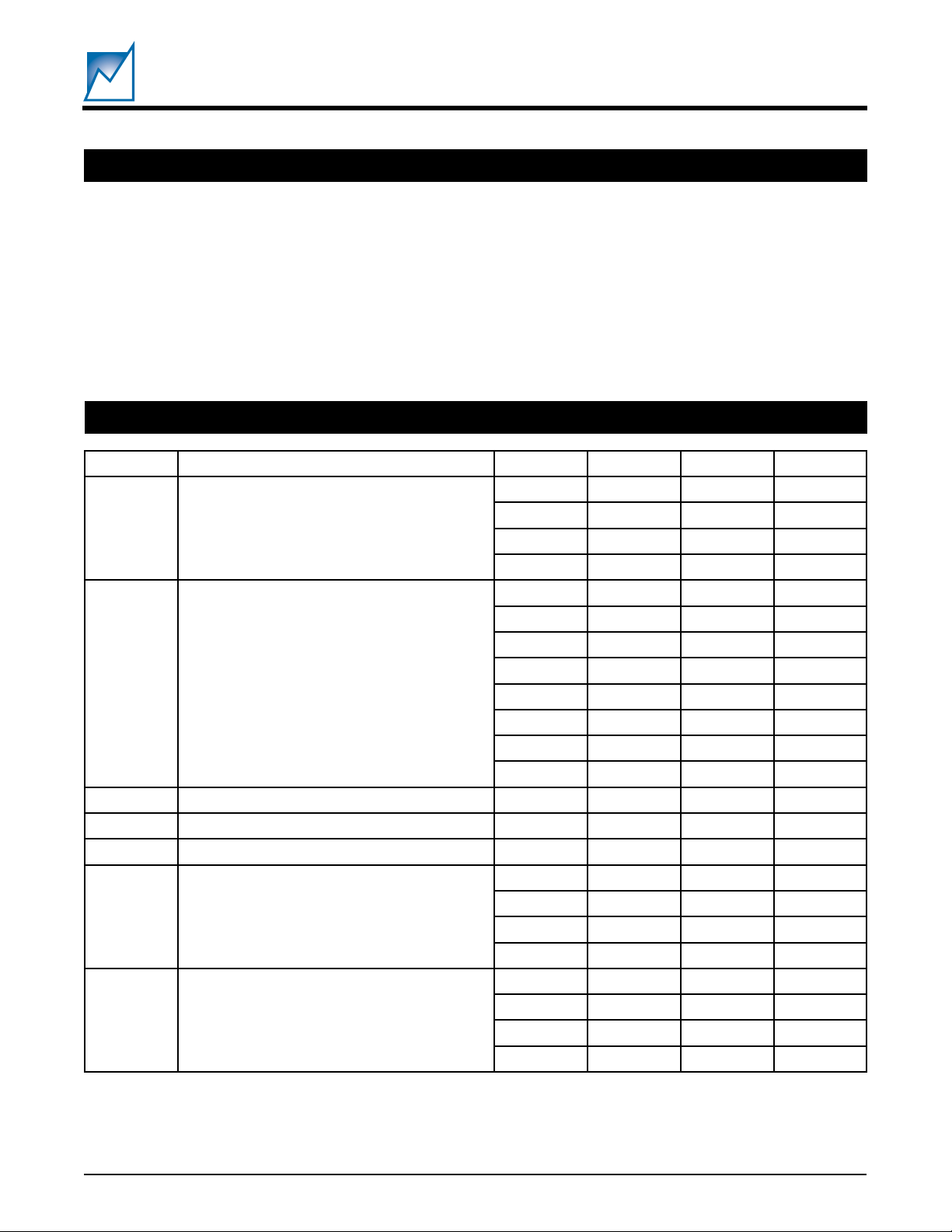

AC OPERATING CHARACTERISTICS

lobmySnoitpircseD.niM.pyT.xaMstinU

t

DBC

t

DGV

t

NDTHSTSF

t

CYC

t

TSRBC

t

FVUP

t

DDP

)retlif(

yaleddooGrewoPelbammargorP

VottluaFmorfyalednwodtuhstsaF

ETAG

emitelcycrekaerbtiucriC5.2s

BC

TESER

htdiweslup002sn

retlifegatloV-rednUelbammargorP

tceteDniPelbammargorP

*COMMENT

Stresses listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions

outside those listed in the operational sections of this specification is not

implied. Exposure to any absolute maximum rating for extended

periods may affect device performance and reliability.

5sµ

05

yaledrekaerBtiucriCVm05elbammargorP

*

051sµ

004sµ

05sµ

052sµ

005sµ

0051sµ

*

5

02sm

08sm

061sm

ffo002sn

FFO

*

—

5sm

08sm

061sm

5.0sm

5sm

*

08

061sm

2055 Prog Table

sµ

sm

sm

* = Default value

SUMMIT MICROELECTRONICS, Inc.

2055 4.0 12/22/00

5

Page 6

DC OPERATING CHARACTERISTICS

(Over Recommended Operating Conditions; Voltages are relative to VSS, except VGT)

lobmySretemaraPsnoitidnoC.niM.pyT.xaMstinU

V

DD

V5

FER

I

5DAOL

V5.2

FER

I

5.2DAOL

I

DD

V

VU

V

TSYHVU

V

VO

V

TSYHVO

V

ETAG

I

ETAG

V

ESNES

I

ESNES

V

BC

V

BCQ

V

STNE

V

V

V

V

I

V

(1) TA = 25ºC.

TSYHSTNE

HI

LI

LO

LI

TG

V

ETAG

V

ETAG

egatlovylppuSI

tuptuoecnereferV5I

tnerructuptuoecnereferV5I

tuptuoecnereferV5.2I

tnerructuptuoecnereferV5.2I

Am3=112131V

DD

Am3=57.400.552.5V

DD

Am3=1– 1Am

DD

DD

DD

)1(Am3=574.2005.2525.2V

Am3=2.0– 1Am

tnerrucylppusrewoP 01Am

dlohserhtegatloV-rednUI

siseretsyhegatloV-rednUI

dlohserhtegatloV-revOI

siseretsyhegatloV-revOI

DD

DD

DD

DD

)1(Am3=574.2005.2525.2V

Am3=36Vm

)1(Am3=574.2005.2525.2V

Am3=01Vm

egatlovtuptuo V

tuptuotnerruc001Aµ

dlohserhtESNESNIARDI

tuptuotnerrucESNESNIARDV

dlohserhtrekaerbtiucriCI

DD

ESNES

DD

)1(Am3=574.2005.2525.2V

V=

)1(9 0111Aµ

SS

Am3=040506Vm

002Vm

tiucricpirTkciuQelbammargorP

dlohserhtrekaerb

001Vm

06Vm

ffO —

dlohserhtST/NEI

siseretsyhST/NEI

DD

DD

)1(Am3=574.2005.2525.2V

Am3=01Vm

3V5

GPNE:egatlovhgihtupnI

02V

#TLUAF:egatlovwoltuptuOI

#GP:egatlovwoltuptuOI

ST/NE,#2DP,#1DP:tnerructupnIV

Am3=0 4.0V

LO

Am3=0 4.0V

LO

V=

LI

SS

001Aµ

dlohserhtetaG7.08.10.3V

SMH4812

Preliminary

DD

FER

V

V

2055 Elect Table

RECOMMENDED OPERATING CONDITIONS

Temperature –40°C to 85°C.

6

2055 4.0 12/22/00

SUMMIT MICROELECTRONICS, Inc.

Page 7

FUNCTIONAL DESCRIPTION

SMH4812

Preliminary

GENERAL OPERATION

The SMH4812 is an integrated power controller for hot

swappable add-in cards. The device operates from a wide

supply range and generates the signals necessary to drive

an isolated output DC/DC converter. As a typical add-in

board is inserted into the powered backplane physical

connections must first be made with the chassis to discharge any electrostatic voltage potentials. The board

then contacts the long pins on the backplane that provide

power and ground. As soon as power is applied the device

starts up, but does not immediately apply power to the

output load. Under-voltage and over-voltage circuits

inside the controller check to see that the input voltage is

within a user-specified range, and pin detection signals

determine whether the card is seated properly.

These requirements must be met for a Pin Detect Delay

period of t

, after which time the hot-swap controller

PDD

enables VGATE to turn on the external power MOSFET

switch. The VGATE output is current limited to I

VGATE

allowing the slew rate to be easily modified using external

passive components. During the controlled turn-on period

the VDS of the MOSFET is monitored by the drain sense

input. When drain sense drops below 2.5V, and VGATE

gets above VDD – VGT, the power good output can begin

turning on the DC/DC controller. The Power Good Enable

input may be used to activate or deactivate the output load.

Steady state operation is maintained as long as all conditions are normal. Any of the following events may cause

the device to disable the DC/DC controller by shutting

down the power MOSFET: an under-voltage or overvoltage condition on the host power supply; an overcurrent event detected on the CBSENSE input; a failure of

the power MOSFET sensed via the DRAIN SENSE pin;

the pin detect signals becoming invalid; the master enable

(EN/TS) falling below 2.5V; the FS# input being driven low

by events on the secondary side of the DC/DC controller.

The SMH4812 may be configured so that after any of

these events occur the VGATE output shuts off and either

latches into an off state or recycles power after a cooling

down period, t

Powering V

DD

CYC

.

The SMH4812 contains a shunt regulator on the VDD pin

that prevents the voltage from exceeding 12V. It is

necessary to use a dropper resistor (RD) between the host

power supply and the VDD pin in order to limit current into

the device and prevent possible damage. The dropper

resistor allows the device to operate across a wide range

of system supply voltages, and also helps protect the

device against common-mode power surges. Refer to the

Applications Section for help on calculating the R

tance value.

System Enables

There are several enabling inputs, which allow a host

system to control the SMH4812. The Pin Detect pins

(PD1# & PD2#) are two active low enables that are

generally used to indicate that the add-in circuit card is

properly seated. This is typically done by clamping the

inputs to V

through the implementation of an injector

SS

switch, or alternatively through the use of a staggered pins

at the card-cage interface. Two shorter pins arrayed at

opposite ends of the connector force the card to be fully

seated (not canted) before both pin detects are enabled.

Care must be taken not to exceed the maximum voltage

rating of these pins during the insertion process. Refer to

details in the Applications Section for proper circuit implementation.

,

The EN/TS input provides an active high comparator input

that may be used as a master enable or temperature

sense input. These inputs must be held low for a period of

t

before a power-up sequence may be initiated.

PDD

Under-/Over-Voltage Sensing

The Under-Voltage (UV) and Over-Voltage (OV) inputs

provide a set of comparators that act in conjunction with an

external resistive divider ladder to sense when the host

supply voltage exceeds the user defined limits. If the input

to the UV pin rises above 2.5V, or the input to the OV pin

falls below 2.5V for a period of t

quence may be initiated. The t

, the power-up se-

PDD

filter helps prevent

PDD

spurious start-up sequences while the card is being inserted. If UV falls below 2.5V or OV rises above 2.5V, the

PG and VGATE outputs will be shut down immediately.

Under-/Over-Voltage Filtering

The SMH4812 may also be configured so that an out of

tolerance condition on UV/OV will not shut off the output

immediately. Instead, a filter delay may be inserted so that

only sustained under-voltage or over-voltage conditions

will shut off the output. When the UV/OV filter option is

enabled an out of tolerance condition on UV/OV for longer

than the filter delay time, t

, activates the FAULT#

UOFLTR

output, and the VGATE and PG outputs will be latched in

the off state. See Figure 1. To initiate another power-up

sequence the FAULT# output must first be reset. Refer to

the appropriate section on resetting the FAULT# output.

The Under-/Over-Voltage Filtering feature is disabled in

the default configuration of the device.

resis-

D

SUMMIT MICROELECTRONICS, Inc.

2055 4.0 12/22/00

7

Page 8

SMH4812

Preliminary

OV / UV

FAULT#

V

DD

2.5V

t

UOFLTR

11 ≤ VDD ≤ 13

2055 Fig01

CBSENSE

VGATE

<t

PUVF

T

CBD

50mV

T

CYC

T

CBD

2055 Fig02

Figure 2. Circuit Breaker Cycle ModeFigure 1. Under-/Over-Voltage Filter Timing

UV

OV

PD1#/

PD2#

VGATE

DRAIN

SENSE

CBSENSE

PG#

5V

2.5V

50mV

REF

REF

t

PDD

VDD – V

GT

2.5V

REF

V

DD

<t

CBD

2055 Fig03

Figure 3. Power On Timing Sequence

8

2055 4.0 12/22/00

SUMMIT MICROELECTRONICS, Inc.

Page 9

SMH4812

Preliminary

Under-Voltage Hysteresis

The Under-Voltage comparator input may be configured

with a programmable level of hysteresis. The compare

level may be set in steps (up to 15) of 62.5mV below 2.5V.

The default under-voltage hysteresis level is set to

62.5mV.

Soft Start Slew Rate Control

Once all of the preconditions for powering up the DC/DC

controllers have been met, the SMH4812 provides a

means to soft start the external power FET. It is important

to limit in-rush current to prevent damage to the add-in

card or disruptions to the host power supply. For example,

charging the filter capacitance (normally required at the

input of the DC/DC controllers) too quickly may generate

very high current. The VGATE output of the SMH4812 is

current limited to I

, allowing the slew rate to be easily

VGATE

modified using external passive components. The slew

rate may be found by dividing I

by the gate-to-drain

VGATE

capacitance placed on the external FET. A complete

design example is given in the Applications Section.

Load Control — Sequencing the Secondary Supplies

Once power has been ramped to the DC/DC controllers,

two conditions must be met before the PG# output can be

enabled: the Drain Sense voltage must be below 2.5V,

and the VGATE voltage must be greater than VDD – VGT.

The Drain Sense input helps ensure that the power MOSFET is not absorbing too much steady state power from

operating at a high VDS. This sensor remains active at all

times (except during the current regulation period). The

VGATE sensor makes sure that the power MOSFET is

operating well into its saturation region before allowing the

loads to be switched on. Once VGATE reaches VDD – V

GT

this sensor is latched.

When the external MOSFET is properly switched on the

PG# output may be enabled (if ENPG is high). Output PG#

is activated after a t

delay. The delay time is program-

PGD

mable from 50µs to 160ms.

timer allows the SMH4812 to ignore the state of the FS#

input until the timer period expires. The FS# input must be

driven high by the end of this timer period. A low level on

this input will cause a Fault condition, driving FAULT# low

and shutting off the VGATE and PG# outputs.

The purpose of the holdoff timer is to allow enough time for

devices on the secondary side of the DC/DC controllers to

power up and stabilize. This unique feature of the

SMH4812 allows supervisory circuits such as an SMS44

to control the shutdown of the primary side soft start circuit,

even though the secondary side initially has no power.

The FS# input can be programmed to act as a second

ENPG input controlling the PG# output.

Circuit Breaker Operation

The SMH4812 provides a number of circuit breaker functions to protect against over current conditions. A sustained over-current event could damage the host supply

and/or the load circuitry. The board’s load current passes

through a series resistor (RS) connected between the

MOSFET source (which is tied to CBSENSE) and VSS.

The breaker trips whenever the voltage drop across RS is

greater than 50mV for more than t

(a programmable

CBD

filter delay ranging from 10µs to 500µs).

Quick-Trip

TM

Circuit Breaker

Additionally, the SMH4812 provides a Quick-Trip feature

that will cause the circuit breaker to trip immediately if the

voltage drop across RS exceeds V

. The Quick-Trip

QCB

level may be set to 60mV, 100mV (default), 200mV, or the

feature may be disabled.

<T

CBD

CBSENSE

V

QCB

50mV

The PG# output has a 12V withstand capability, so high

voltages must not be connected to this pin. A bipolar

transistor or an opto-isolator can be used to boost the

withstand voltage to that of the host supply. See Figure 9

for connections.

Forced Shutdown — Secondary Feedback

The Forced Shutdown signal (FS#) is an active low input

that provides a method of receiving feedback from the

secondary side of the DC/DC controllers. A built-in holdoff

SUMMIT MICROELECTRONICS, Inc.

2055 4.0 12/22/00

T

FSTSHTDN

VGATE

Figure 4. Circuit Breaker Quick Trip Response

2055 Fig04

9

Page 10

Current Regulation

The current regulation mode is an optional feature that

provides a means to regulate current through the MOSFET for a programmable period of time. See Figures 5a

and 5b. If enabled the device will start the internal timer

when the voltage at CBSENSE exceeds 50mV (A & G, H).

Also, it attempts to limit the voltage at CBSENSE to 60mV

by regulating the VGATE output (B & C vs. I). The circuit

breaker will trip if the over-current condition remains after

the time-out (D, E, F; & J, K, L). However, if CBSENSE

drops below 50mV before the timer ends, the timer is reset

and VGATE resumes normal operation. If the Quick-Trip

level is exceeded then the device will bypass the current

regulation timer and shut down immediately. The Current

Regulation feature is disabled in the default configuration.

12V

0V

50mV

0V

VGATE

1

FAULT#

0

CBSENSE

SMH4812

Preliminary

C

F

E

B

A

D

2055 Fig05a

Non-Volatile Fault Latch

The SMH4812 also provides an optional nonvolatile fault

latch (NVFL) circuit breaker feature. The nonvolatile fault

latch essentially provides a programmable fuse on the

circuit breaker. When enabled the nonvolatile fault latch

will be set whenever the circuit breaker trips. Once set, it

cannot be reset by cycling power.

N

OTE

UNTIL

: THE

IT IS

DEVICE REMAINS PERMANENTLY DISABLED

REPROGRAMMED AT THE FACTORY

.

As long as the NVFL is set, the FAULT# output will be

driven active. The Non-Volatile Fault Latch feature is

disabled in the default configuration.

Resetting FAULT#

When the circuit breaker trips the VGATE output is turned

off and FAULT# is driven low. In the default condition the

breaker resets automatically after a time of t

CYC

. In the

latched condition cycling power to the board or toggling the

EN/TS input will also reset the circuit breaker. If the over

current condition still exists after the MOSFET switches

back on, the circuit breaker will re-trip.

Figure 5.a. Current Regulation & Shutdown

12V

VGATE

0V

1

FAULT#

0

50mV

CBSENSE

0V

I

L

K

H

G

J

2055 Fig05b

Figure 5.b. Current Regulation & Shutdown

10

2055 4.0 12/22/00

SUMMIT MICROELECTRONICS, Inc.

Page 11

APPLICATIONS

SMH4812

Preliminary

Operating at High Voltages

The breakdown voltage of the external active and passive

components limits the maximum operating voltage of the

SMH4812 hot-swap controller. Components that must be

able to withstand the full supply voltage are: the input and

output decoupling capacitors, the protection diode in series with the DRAIN SENSE pin, the power MOSFET

switch and the capacitor connected between its drain and

gate, the high-voltage transistors connected to the power

good outputs, and the dropper resistor connected to the

controller’s VDD pin.

Over-Voltage and Under-Voltage Resistors

In the following examples, the three resistors, R1, R2, and

R3, connected to the OV and UV inputs, must be capable

of withstanding the maximum supply voltage of several

hundred volts. The trip voltage of the UV and OV inputs is

2.5V relative to V

. As the input impedance of UV and OV

SS

is very high, large value resistors can be used in the

resistive divider. The divider resistors should be high

stability, 1% metal-film resistors to keep the under-voltage

and over-voltage trip points accurate.

Telecom Design Example

A hot-swap telecom application may use a 48V power

supply with a –25% to +50% tolerance (

i.e.

, the 48V supply

can vary from 36V to 72V). The formulae for calculating

R1, R2, and R3 follow.

First a peak current, ID

, must be specified for the

MAX

resistive network. The value of the current is arbitrary, but

it can't be to high (self-heating in R3 will become a

problem), or too low (the value of R3 becomes very large,

and R3 becomes very expensive). To set the calculations

a nominal value of 250µA will be assumed.

With VOV (2.5V) being the over-voltage trip point, R1 is

calculated by the formula:

V

OV

=

R1

ID

MAX

.

Substituting:

MIN

VS

MAX

.

×

ID VS

MAX MIN

=

ID

Substituting:

µ

72V

−

MIN UV

ID

MIN

−

µ

×

µ

.

:

MIN

.

.

250 A 36V

==

ID 125 A

MIN

Now the value of R3 is calculated from ID

VS V

=

R3

V

is the under-voltage trip point, also 2.5V. Substituting:

UV

36V 2.5V

==Ω

R3 268k

125 A

The closest standard 1% resistor value is 267kΩ

Then R2 is calculated:

V

+=

R1 R2

()

ID

UV

MIN

,

or

V

UV

=−

R2 R1

ID

MIN

.

Substituting:

2.5V

=−Ω=Ω−Ω=Ω

R2 10k 20k 10k 10k

µ

125 A

.

Dropper Resistor Selection

The SMH4812 is powered from the high-voltage supply

via a dropper resistor, RD. The dropper resistor must

provide the SMH4812 (and its loads) with sufficient operating current under minimum supply voltage conditions,

but must not allow the maximum supply current to be

exceeded under maximum supply voltage conditions.

The dropper resistor value is calculated from:

2.5V

==Ω

R1 10k

µ

250 A

.

Next the minimum current that flows through the resistive

divider, ID

, is calculated from the ratio of minimum and

MIN

maximum supply voltage levels:

SUMMIT MICROELECTRONICS, Inc.

2055 4.0 12/22/00

R

where VS

V

is the upper limit of the SMH4812 supply voltage,

DDMAX

MIN DD

=

D

II

DD LOAD

is the lowest operating supply voltage,

MIN

MAX

+

,

−

VS V

IDD is minimum current required for the SMH4812 to

operate, and I

is any additional load current from the

LOAD

2.5V and 5V outputs and between VDD and VSS.

11

Page 12

SMH4812

Preliminary

The min/max current limits are easily met using the dropper resistor, except in circumstances where the input

voltage may swing over a very wide range (

e.g.

, input

varies between 20V and 100V). In these circumstances it

may be necessary to add an 11V zener diode between

VDD and VSS to handle the wide current range. The zener

voltage should be below the nominal regulation voltage of

the SMH4812 so that it becomes the primary regulator.

MOSFET VDS(ON) Threshold

The drain sense input on the SMH4812 monitors the

voltage at the drain of the external power MOSFET switch

with respect to V

. When the MOSFET’s VDS is below the

SS

user-defined threshold the MOSFET switch is considered

to be ON. The VDS(ON)

THRESHOLD

is adjusted using the

resistor, RT, in series with the drain sense protection

diode. This protection, or blocking, diode prevents high

voltage breakdown of the drain sense input when the

MOSFET switch is OFF. A low leakage MMBD1401 diode

offers protection up to 100V. For high voltage applications

(up to 500V) the Central Semiconductor CMR1F-10M

diode should be used. The VDS(ON)

THRESHOLD

is calcu-

lated from:

VON V I R V

() ( )

where V

DS SENSE SENSE T DIODE

DIODE

THRESHOLD

is the forward voltage drop of the protection

diode. The VDS(ON)

due to the temperature dependence of V

The calculation below gives the VDS(ON)

=−×−

THRESHOLD

varies over temperature

DIODE

THRESHOLD

and I

SENSE

under

the worst case condition of 85°C ambient. Using a 68kΩ

resistor for RT gives:

VON 2.5V15A68k 0.5V1V

() ( )

DS

THRESHOLD

=− ×Ω−=

µ

The voltage drop across the MOSFET switch and sense

resistor, V

, is calculated from:

DSS

The dropper resistor value should be chosen such that the

minimum and maximum I

and VDD specifications of the

DD

SMH4812 are maintained across the host supply’s valid

operating voltage range. First, subtract the minimum V

of the SMH4812 from the low end of the voltage, and divide

by the minimum IDD value. Using this value of resistance

as RD find the operating current that would result from

running at the high end of the supply voltage to verify that

the resulting current is less than the maximum IDD current

allowed. If some range of supply voltage is chosen that

would cause the maximum IDD specification to be violated,

then an external zener diode with a breakdown voltage of

≈12V should be used across V

DD

.

As an example of choosing the proper RD value, assume

the host supply voltage will range from 36 to 72V. The

largest dropper resistor that can be used is: (36V-11V)/

3mA = 8.3kΩ. Next, confirm that this value of RD also

works at the high end: (72V-13V)/8.3kΩ = 7.08mA, which

is less than 10mA.

The FS# input can also be used in conjunction with a

secondary-side supervisory circuit providing a positive

feedback loop during the power up sequence. As an

example, assume the SMH4812 is configured to turn on –

,

48V to a DC/DC converter with a 1.6ms delay. Further

assume all of the enable inputs are true and PG# has just

been sequenced on. If FS# option 4 (100

has been selected, then FS# must be driven high within

.

in register 5)

BIN

1.6ms after PG# goes low, otherwise the PG output will be

disabled. Ideally, there would be a secondary-side supervisor similar to the SMS44 that would have its reset timeout period programmed to be less than 1.6ms. After the

supply turns on the RESET# output of the SMS44 would

be released and FS# pulled high. However, if for any

.

reason the supply doesn't turn on, the RESET# will not be

released and the SMH4812 will disable the PG output.

DD

=+

VIRR

DSS D S ON

()

,

where ID is the MOSFET drain current, RS is the circuit

breaker sense resistor and RON is the MOSFET on resistance.

12

2055 4.0 12/22/00

SUMMIT MICROELECTRONICS, Inc.

Page 13

APPLICATIONS CIRCUITS

SMH4812

Preliminary

–48V

0V

10nF

100V

10kΩ

10kΩ

100nF

50V

R1

R3

R2

EN/TS

UV

OV

PD1#

PD2#

FAULT#

SS

V

20mΩ

6.8kΩ

DD

V

R

S

R

D

REF

2.5V

CBSENSE

ENPG

SMH4812

GATE

V

100nF

1kΩ

*10Ω

10nF

100V

FS#

PG#

5V

REF

DRAIN SENSE

R

T

68kΩ

MMBD1401

MMBD-

47kΩ

100nF

50V

0V

MMBTA-

06LT1

1401

100µF

100V

–48V

2055 Fig06

Figure 6. Changing Polarity of Power Good Output (PG#)

Note: Figures 6 through 9 — the *10Ω resistor must be located as close as possible to the MOSFET

SUMMIT MICROELECTRONICS, Inc.

2055 4.0 12/22/00

13

Page 14

SMH4812

R

T

68kΩ

1kΩ

*10Ω

10nF

100V

MMBD1401

100nF

100kΩ

MMBTA06LT1

100nF

50V

100nF

50V

10nF

100V

UV

OV

PD1#

PD2#

FAULT#

V

DD

ENPG

PG#

5V

REF

SMH4812

V

SS

CBSENSE

V

GATE

DRAIN SENSE

0V

–48V

10kΩ

10kΩ

R1

R

D

6.8kΩ

100µF

100V

R3

1MΩ

R2

R

S

20mΩ

0V

–48V

2.5V

REF

EN/TS

+

–

LMV331

1kΩ

50kΩ

NTC

50kΩ

@T

MAX

100nF

50V

2055 Fig07

FS#

Preliminary

Note: Figures 6 through 9 — the *10Ω resistor must be located as close as possible to the MOSFET

14

Figure 7. Overtemperature Shutdown

2055 4.0 12/22/00

SUMMIT MICROELECTRONICS, Inc.

Page 15

SMH4812

Preliminary

EN1

EN2

EN3

EN4

–48V

0V

0V

10kΩ

10nF

100V

1MΩ

+

–

+

–

LMV

339

+

–

10kΩ

+

–

10kΩ

100nF

50V

R3

1kΩ

EN/TS

UV

R2

OV

PD1#

PD2#

FAULT#

R1

SS

V

R

S

20mΩ

R

D

6.8kΩ

DD

REF

V

2.5V

SMH4812

CBSENSE

100nF

*10Ω

ENPG

GATE

V

1kΩ

10nF

100V

FS#

PG#

5V

REF

DRAIN SENSE

100nF

50V

R

T

68kΩ

MMBD1401

MMBTA06LT1

100kΩ

100nF

50V

100µF

100V

–48V

2055 Fig08

SUMMIT MICROELECTRONICS, Inc.

Figure 8. Expanding Input Monitoring Capability

2055 4.0 12/22/00

15

Page 16

0V

R3

R

D

6.8kΩ

SMH4812

Preliminary

–48V

10nF

100V

10kΩ

10kΩ

100nF

50V

R2

R1

SS

R

DD

V

S

SMH4812

GATE

CBSENSE

100nF

V

*10Ω

1kΩ

10nF

100V

ENPG

FS#

PG2#

5V

REF

DRAIN SENSE

68kΩ

MMBD1401

MMBTA06LT1

100kΩ

100nF

50V

EN/TS

UV

OV

PD1#

PD2#

FAULT#

V

Figure 9. Typical Application for DC/DC Converter

100µF

100V

DC / DC

Converter

with

Active Low

On/Off Control

+VIN

+VOUT

–VIN

–VOUT

ON/OFF

2055 Fig09

V

0V

Note: Figures 6 through 9 — the *10Ω resistor must be located as close as possible to the MOSFET

16

2055 4.0 12/22/00

SUMMIT MICROELECTRONICS, Inc.

Page 17

JEDEC

MO-137

SMH4812

Preliminary

PACKAGES

SSOP PACKAGE

D

H

1

E

S

A

hx45

C

noisnemiD

.niM.moN.xaM.niM.moN.xaM

0 to 8

typ

L

e

sehcnIsretemilliM

A

2

B

A

A160.0460.0860.055.136.137.1

1A400.0600.08900.021.051.052.0

2A550.0850.0160.04.174.155.1

B800.0010.0210.002.052.013.0

C5700.0800.08900.091.002.052.0

D733.0243.0443.065.896.847.8

E051.0551.0751.018.349.399.3

eCSB520.0CSB536.0

H032.0632.0442.048.599.502.6

h010.0310.0610.052.033.014.0

L610.0520.0530.014.046.098.0

S0050.05250.00550.072.133.104.1

1

2055 SSOP

2055 SSOP Dim

SUMMIT MICROELECTRONICS, Inc.

2055 4.0 12/22/00

17

Page 18

16 PIN SOIC PACKAGE

SMH4812

Preliminary

0.155±0.005

0.236 ± 0.008

.004

Pin 1 Index

0.05 BSC

7 ± 1

0.390 ± 0.005

SOIC 16

0.016 ± 0.003

7 ± 1

.0085 ± .0010

(After Plating)

916

0.151 ± 0.005

81

0 ± 8

155 ± 0.005

DETAIL A

.016 ±.002

45 ± 1

0.024 ± 0.002

0.054 ± 0.005

0.069 MAX

.007 ± .003

7 ± 1

0.390 ± 0.005

Note: 1. Reference: JEDEC publication MS-012 PTX 360-120

2. Unit: Inches

3. Mold flash, protrusion & gate burr shall not exceed 0.006 inch per side.

0.007 ± 0.003

0.023 ± 0.005

0.041

DETAIL A

2055 SOIC 1.0

18

2055 4.0 12/22/00

SUMMIT MICROELECTRONICS, Inc.

Page 19

ORDERING INFORMATION

SMH4812

Preliminary

Base Part Number

SMH4812

G

Package

G = SSOP

S = SOIC

2055 T ree 1.0

NOTICE

SUMMIT Microelectronics, Inc. reserves the right to make changes to the products contained in this publication in order

to improve design, performance or reliability. SUMMIT Microelectronics, Inc. assumes no responsibility for the use of

any circuits described herein, conveys no license under any patent or other right, and makes no representation that

the circuits are free of patent infringement. Charts and schedules contained herein reflect representative operating

parameters, and may vary depending upon a user’s specific application. While the information in this publication has

been carefully checked, SUMMIT Microelectronics, Inc. shall not be liable for any damages arising as a result of any

error or omission.

SUMMIT Microelectronics, Inc. does not recommend the use of any of its products in life support or aviation applications

where the failure or malfunction of the product can reasonably be expected to cause any failure of either system or to

significantly affect their safety or effectiveness. Products are not authorized for use in such applications unless

SUMMIT Microelectronics, Inc. receives written assurances, to its satisfaction, that: (a) the risk of injury or damage has

been minimized; (b) the user assumes all such risks; and (c) potential liability of SUMMIT Microelectronics, Inc. is

adequately protected under the circumstances.

This document supersedes all previous versions.

© Copyright 2000 SUMMIT Microelectronics, Inc.

SUMMIT MICROELECTRONICS, Inc.

2055 4.0 12/22/00

19

Loading...

Loading...