Page 1

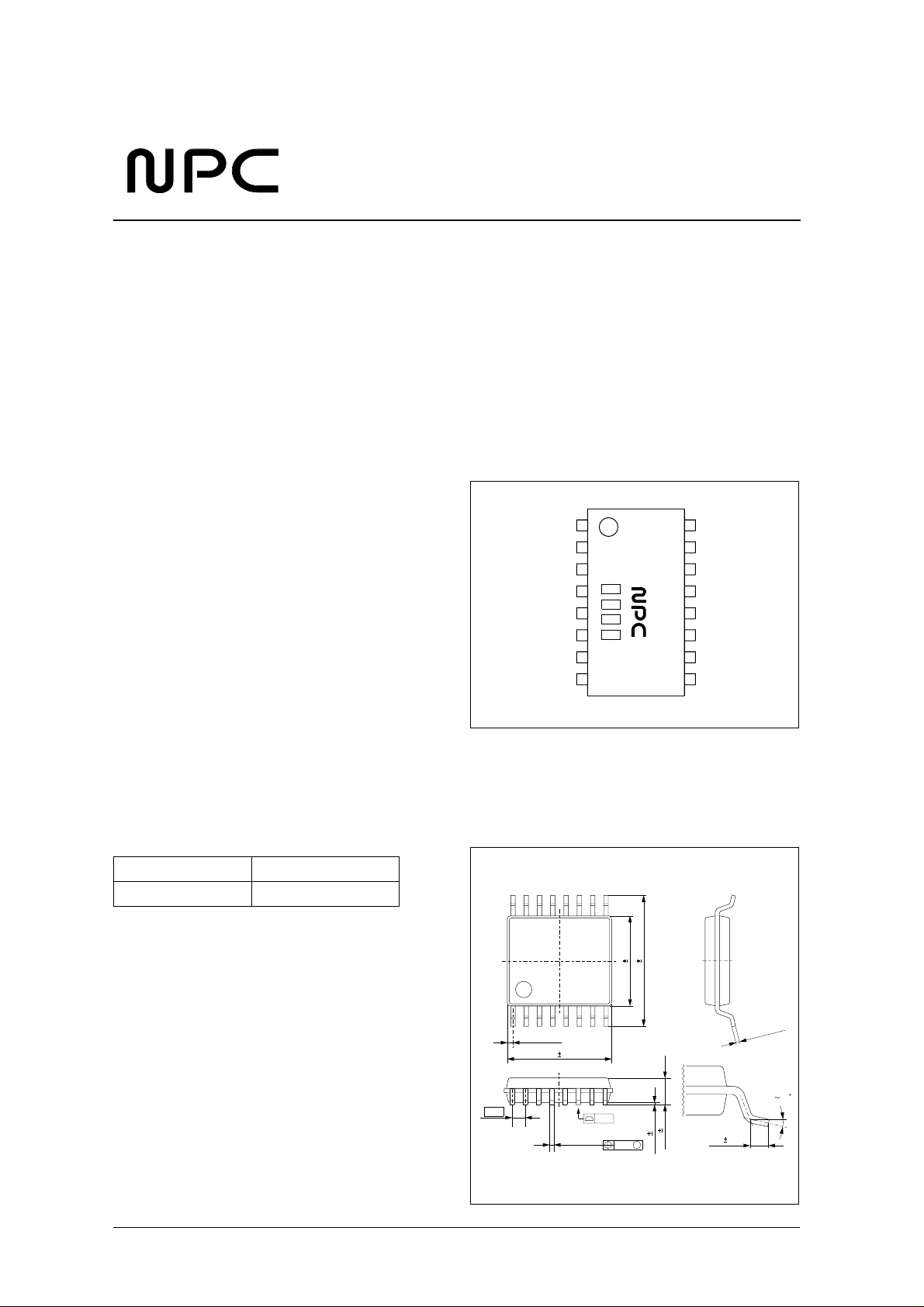

SM6451BV

NIPPON PRECISION CIRCUITS INC.

Audio Variable V olume IC

OVERVIEW

The SM6451BV is a 3-wire serial-controlled electronic variable volume IC for audio applications. It provides

electronic volume control for a stereo system (left and right channels), and independent channel attenuation

and muting, with greatly enhanced digital zip noise suppression. The chip address function allows up to four

SM6451BV devices to be connected and individually controlled over the 3-wire control interface from a single

CPU. It is available in 16-pin VSOP packages.

FEATURES

■

Stereo inputs and outputs

■

Attenuation function

• 2-channel independent control

• 1.0 dB/step over 80 steps

• 0 to − 80 dB range

■

Mute function

■

3-wire serial data control (MDT, MCK, MLEN)

■

Chip addressing (up to 4 devices can be connected

in parallel)

■

Low noise

• 0.003 % THD + noise

• 12 µ Vrms residual noise

■

2.5 to 3.6 V single power supply

■

Silicon-gate CMOS process

PINOUT

(T op V iew)

RSTN

1

16

ADRS1

ADRS2

6451BV

DVDD

LOUT

LIN

AVDD

8

VRL VRR

9

MDT

MCK

MLEN

DVSS

ROUT

RIN

AVSS

APPLICATIONS

■

Audio equipment

ORDERING INFORMATION

De vice Pack ag e

SM6451BV 16-pin VSOP

PACKAGE DIMENSIONS

(Unit: mm)

16 pin VSOP

4.4 0.2

6.4 0.2

0.275TYP

5.1 0.2

0.65

0.22

+ 0.10

- 0.05

0.10

0.12

M

1.15 0.1

0.10 0.05

0.5 0.2

0.15

+ 0.1

- 0.05

010

NIPPON PRECISION CIRCUITS—1

Page 2

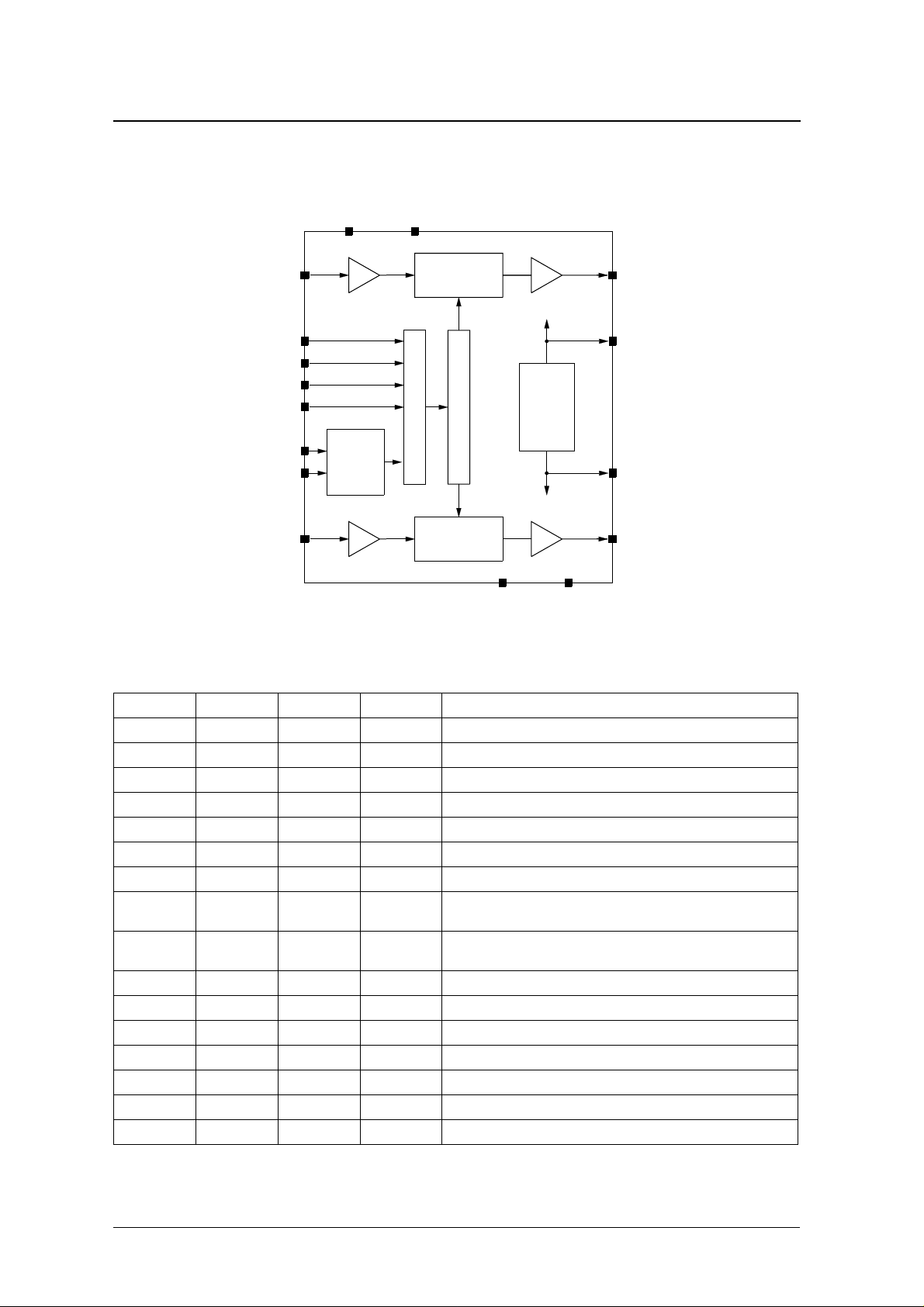

BLOCK DIAGRAM

SM6451BV

DVDD DVSS

LIN

Attenuation

Control

1/2VDD

MLEN

MCK

MDT

Attenuation Decoder

Interface Control

Circuits

RSTN

Decoder

Address

ADRS1

Chip

ADRS2

1/2VDD

RIN

Attenuation

Control

AVDD AVSS

PIN DESCRIPTION

Number Name I/O

1 RSTN Ip D System reset input (LOW -level reset)

2 ADRS1 Ip D Chip address set 1

3 ADRS2 Ip D Chip address set 2

4 D VD D – D Digital supply

5 LOUT O A Left-channel audio output

6 LIN I A Left-channel audio input

7 AV D D – A Analog supply

8 VRL O A

9 VRR O A

10 AVS S – A Analog ground

11 R IN I A Right-channel audio input

12 R O U T O A Right-channel audio output

13 D VS S – D Digital ground

14 MLEN Ip D Microcontroller latch enable input

15 MCK Ip D Microcontroller clock input

16 M D T Ip D Microcontroller data input

1. Ip = input pin with pull-up, A = analog, D= digital

1

A/D

1

Left-channel reference voltage (0.5V

between VRL and AV SS.

Right-channel reference voltage (0.5V

between VRR and AV SS.

Reference

Voltage

LOUT

VRL

VRR

ROUT

Description

). Connect a 10 µF capacitor

DD

). Connect a 10 µF capacitor

DD

NIPPON PRECISION CIRCUITS—2

Page 3

−

−

−

−

−

°

°

SPECIFICATIONS

Absolute Maximum Ratings

−

° C

SM6451BV

DVSS = AVSS = 0 V, DVDD = AVDD = V

DD

Parameter Symbol Rating Unit

Supply voltage V

Input voltage V

Po w er dissipation P

Storage temperature T

Soldering temperature T

Soldering time t

Recommended Operating Conditions

DVSS = AVSS = 0 V, DVDD = AVDD = V

Parameter Symbol Rating Unit

Supply voltage V

Supply voltage deviation DV

Operating temperature T

DD

DD

AV

DC Characteristics

DD

DD

IN

D

stg

sld

sld

DD

, DV

opr

SS

AV

SS

0.3 to 7.0 V

V

SS

0.3 to V

+ 0.3 V

DD

150 m W

55 to 125

255

10 s

2.5 to 3.6 V

±0.1 V

40 to 85

C

C

DVDD = AVDD = V

= 2.5 to 3.6 V, V

DD

Parameter Symbol Condition

Data transfer stopped, MDT, MCK,

MLEN, RSTN, ADRS1, ADRS2 = V

ADRS1 = ADRS2 = 0V, 0.8 Vrms

analog input, ATT = 0 d B , data transfer

active

IH

IL

I

V

IL

I

IH

= 0 V – 70 15 0 µ A

IN

V

= V

IN

DVDD Current consumption

AVDD Current consumption I

HIGH-level input voltage

L O W -level input voltage

Input current

1

Input leakage current

1

1

1

I

DDD1

I

DDD2

DDA

V

V

1. MD T, MCK, MLEN, RSTN, ADRS1, ADRS2

= 0 V, Ta = − 40 to 85 ° C

SS

DD

DD

Rating

min typ max

– 0.2 1.0 µA

– 0.4 1.0 m A

– 1.9 5.5 m A

0.7V

DD

– – 0.3V

––V

DD

– – 1.0 µ A

Unit

V

NIPPON PRECISION CIRCUITS—3

Page 4

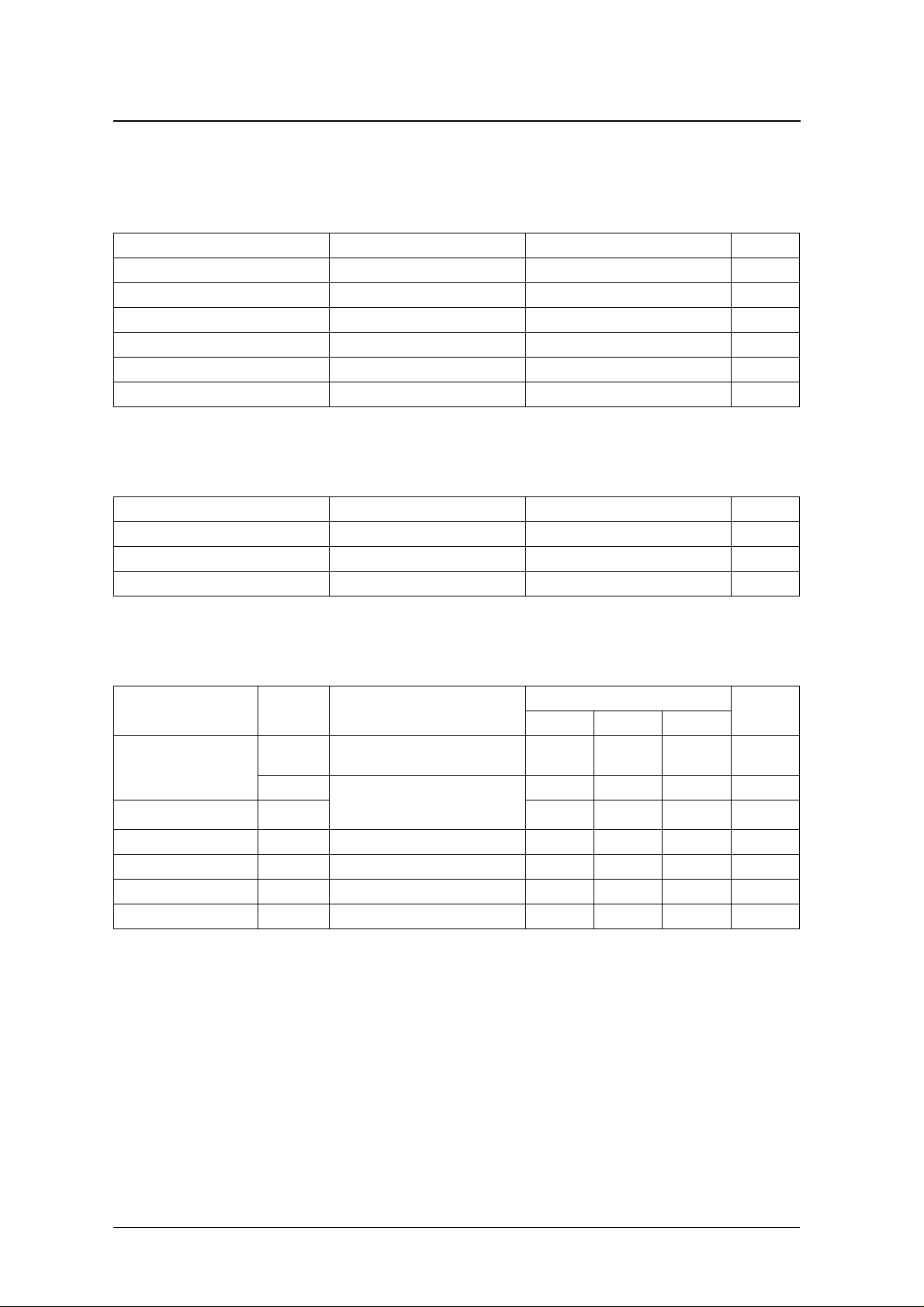

AC Digital Characteristics

SM6451BV

DVDD = AVDD = V

= 2.5 to 3.6 V, V

DD

= 0 V, Ta = − 40 to 85 ° C

SS

Serial inputs (MDT, MCK, MLEN)

Parameter Symbol

MCK, MLEN rise time t

MCK, MLEN fall time t

MDT setup time t

MDT hold time t

MLEN setup time t

MLEN hold time t

MLEN LOW-level pulsewidth t

MLEN HIGH-level pulsewidth t

MDT

tMDS

tMDH

r

f

MDS

MDH

MCS

MCH

MEWL

MEWH

Rating

Unit

min typ max

– – 100 ns

– – 100 ns

50 – – ns

50 – – ns

50 – – ns

50 – – ns

50 – – ns

50 – – ns

0.5VDD

MCK

tMCS

tMEWL

tf tr

MCK

MLEN

0.9VDD

0.1VDD

Reset input (RSTN)

Parameter Symbol

RSTN LOW-level pulsewidth t

RSTN

tMCH

tMEWH

0.5VDD

0.5VDDMLEN

0.9VDD

0.1VDD

Rating

min typ max

100 – – ns

0.5VDD

Unit

NIPPON PRECISION CIRCUITS—4

Page 5

µ

−

−

−

SM6451BV

AC Analog Characteristics

V

= 3.0 V, 0.8 Vrms amplitude, 1 kHz input frequency, 100 k Ω output load resistance, Ta = 25 ° C,

DD

AC-coupled inputs

Analog inputs (LIN, RIN)

−

−

−

−

Parameter Symbol Condition

Rating

min typ max

Reference input amplitude V

Input resistance R

Input clipping voltage V

AI

IN

CLP

THD + N = 1%, ATT = 0 dB – 1.1 – Vrm s

– 0.8 – Vrm s

40 50 60 k Ω

Analog outputs (LOUT, ROUT)

Parameter Symbol Condition

min typ max

Residual noise voltage V

NS

Signal-to-noise ratio S NR 92 96 – dBr

Total harmonic distortion + noise THD + N

Gain control range R

CNT

Input signal: 0 Vrm s ,

A- w eight filter, 0 dBr = 0.8

Vrm s, ATT = 0 dB

ATT = 0 dB, 20 kHz

lowpass filter

–1220

– 0.0025 0.005 %

– 80 – 0 d B

Step size Step 0.8 1.0 1.8 dB

Attenuation error (1k to 20kHz)

Absolute attenuation (1 kHz)

ERR

ERR

AT

AT

AT

AT

AT

0

2

4

6

8

0 to

1

2

60 dB – 2 – 1 dB

61 to

80 dB – 6 – 0 d B

ATT = 0 dB – – 0.0 – d B

ATT =

20 dB – – 20.0 – d B

ATT =

40 dB – – 40.0 – d B

ATT =

60 dB – – 60.4 – d B

ATT =

80 dB – – 84.2 – d B

Mute attenuation (1 kHz) Mute ATT = Mute – 85.0 – 88.0 – d B

Channel crosstalk CT AT T = 0 dB – 103 – 105 – dB

Frequency response FR ATT = 0 dB, f = 200 kHz – 10 – 8 – dB

Quiescent output zip noise voltage

(while AT T value adjusting)

Minimum driver load resistance R

N

J

ML

0 Vrms input – – 3 mV

ATT = 0 dB, THD + N = 1% – 8 12 k Ω

Rating

Unit

Unit

Vrm s

Reference voltage (VRL, VRR)

Parameter Symbol Condition

Reference voltage output V

REF

Rating

min typ max

0.45V

DD

0.5V

DD

NIPPON PRECISION CIRCUITS—5

0.55V

DD

Unit

V

Page 6

MEASUREMENT CIRCUIT

Chip address: ADRS1 = LOW, ADRS2 = LOW

SM6451BV

10µF

0.001µF

+

0.022µF10µF

+

0.022µF

+

1µF

+

1µF

+

1 RSTN

2 ADRS1

3 ADRS2

4 DVDD

5 LOUT

6 LIN

7 AVDD

8 VRL

0.022µF10µF 0.022µF10µF

Generator Analyzer

Audio Precision

System Two SYS − 2322A

MDT 16

MCK 15

MLEN 14

SM6451

DVSS 13

ROUT 12

RIN 11

AVSS 10

VRR 9

CPU

+

+

1µF

+

1µF

100kΩ100kΩ

NIPPON PRECISION CIRCUITS—6

Page 7

SM6451BV

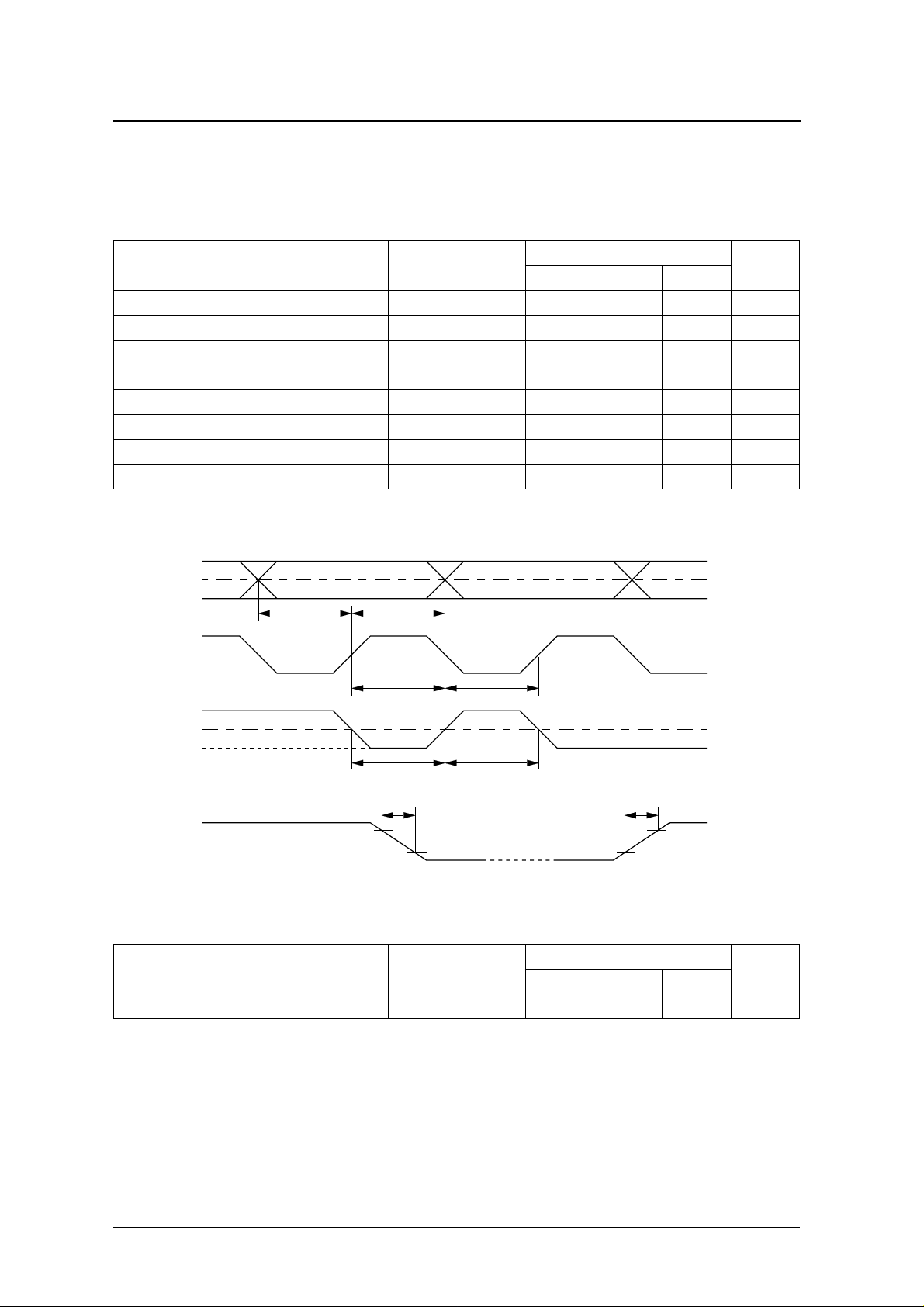

MICROCONTROLLER INTERFACE

The SM6451BV uses a 3-wire serial interface comprising MDT (data), MCK (clock) and MLEN (latch enable)

to select channels and attenuation levels for the addressed device.

Input Timing

The microcontroller data input timing is shown in figure 1.

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0MDT

MCK

MLEN

Figure 1. Microcontroller data input timing

Data is shifted into the internal shift register on the rising edge of MCK, and the attenuation value is updated on

the rising edge of MLEN. Accordingly, data on MDT should be changed on the falling edge of MCK. The dotted lines for MCK and MLEN also indicate valid timing.

Note, however, a minimum of 16 MCK input pulses are required.

Data Format

The format of microcontroller input data is shown in figure 2.

MDT

D15, D14

Care

Don't

Care

Don't

Chip

Address 1

Chip

Don't

Address 2

Care

Care

Don't

Select

Channel

Select

Channel

Data 7

Attenuation

Attenuation

Data 6

Attenuation

Data 5

Attenuation

Data 4

Data 3

Attenuation

Attenuation

Data 2

Attenuation

Data 1

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Figure 2. Microcontroller data format

Data 0

Attenuation

Don’t care.

D13, D12

Chip address bits. D13 corresponds to ADRS1 and D12 corresponds to ADRS2. The device is addressed only

when ADRS1:ADRS2 matches D13:D12.

Example 1: If D13 = LOW, D12 = HIGH and ADRS1 = LOW, ADRS2 = LOW, then the device is not

addressed since ADRS2 and D12 do not match.

Example 2: If D13/D12 = LOW and ADRS1/ADRS2 = LOW, then the device is addressed and all input data

is read and the attenuation settings updated.

D11, D10

Don’t care.

NIPPON PRECISION CIRCUITS—7

Page 8

SM6451BV

D9, D8

Channel select bits. The selected channel(s) are shown in table 1.

Table 1. Channel select

D9 D8 Selected channel

L O W L O W Both left and right channels

LOW HIGH Left channel

HIGH LOW Right channel

HIGH HIGH No change

D7 to D0

Attenuation register (ATT) set bits.

−

−

−

−

−

−

−

−

−

Table 2. Attenuation setting

Attenuation ATT

0 dB 00 LOW LOW LOW LOW LOW LOW LOW LOW

1 dB 01 LOW LOW LOW LOW LOW LOW LOW HIGH

2 dB 02 LOW LOW LOW LOW LOW LOW HIGH L OW

: :::::::::

15 dB 0F L OW LOW LOW LOW HIGH HIGH HIGH HIGH

16 dB 10 LOW LOW LOW HIGH L OW LOW LOW LOW

17 dB 11 LOW LOW LOW HIGH L OW LOW LOW HIGH

: :::::::::

63 dB 3F L OW LOW HIGH HIGH HIGH HIGH HIGH HIGH

64 dB 40 LOW HIGH LOW LOW LOW LOW LOW LOW

65 dB 41 LOW HIGH LOW LOW LOW LOW LOW HIGH

: :::::::::

79 dB 4F L OW HIGH LOW LOW HIGH HIGH HIGH HIGH

−

80 dB 50 LOW HIGH LOW HIGH LOW LOW LOW LOW

Mute 51 L OW HIGH LOW HIGH LOW LOW LOW HIGH

Mute 52 L OW HIGH LOW HIGH LOW LOW HIGH LOW

: :::::::::

Mute F E HIGH HIGH HIGH HIGH HIGH HIGH HIGH LOW

Mute FF HIGH HIGH HIGH HIGH HIGH HIGH HIGH HIGH

1. Outputs are muted after system reset.

Attenuation error is changed dependent on the supply voltage when attenuation level is under – 60dB. In the case of the supply voltage being

under 2.6V, mute level inv erses up to the same level of – 80dB setting or more. (see Figure 6)

H

1

D7 D6 D5 D4 D3 D2 D1 D0

NIPPON PRECISION CIRCUITS—8

Page 9

SM6451BV

ANALOG PERFORMANCE CHARACTERISTICS

DVDD = AVDD = 3.0 V, 100 kΩ output load resistance, Ta = 25 °C

1

f=1kHz

ATT=0dB

20kHz LPF

0.1

0.1

THD+N(%)

0.01

0.001

.1

.2 .5

VIN(Vrms)

VDD=3.3V

VDD=3.0V

VDD=2.7V

0.01

THD+N(%)

1

1.2

0.001

VIN=0.2Vrms

VIN=0.5Vrms

VIN=0.8Vrms

1k 10k 20k10020

Frequency(Hz)

Figure 3. THD + N vs. input amplitude Figure 4. THD + N vs. input frequency

2

1

0

-1

-2

Error(dB)

-3

-4

-5

ATT(dB)

VIN=0.8Vrms

f=1kHz

-80-70-60-50-40-30-20-100

-64

-68

-72

-76

-80

Gain(dB)

-84

-88

-92

Ideal Gain

VDD=3V

VDD=2.7V

VDD=2.5V

ATT(dB)

-80-76-72-68-64

ATT=0dB

20kHz LPF

Mute

Figure 5. Attenuation error Figure 6. Attenuation characteristic (– 64dB to MUTE)

20

16

12

8

Residual Noise(µVrms)

4

0

ATT(dB)

VIN=0Vrms

A-Weight Filter

-80-70-60-50-40-30-20-100

+10

+0

-10

-20

-30

-40

-50

Gain(dB)

-60

-70

-80

-90

-100

ATT=0dB

ATT=-20dB

ATT=-40dB

ATT=-60dB

ATT=-80dB

ATT=MUTE

100

1k 10k 100k 200k20

Frequency(Hz)

Figure 7. Residual noise vs. ATT Figure 8. Frequency response

NIPPON PRECISION CIRCUITS—9

IN=0.8Vrms

V

Page 10

SM6451BV

-40

-60

VIN=0.8Vrms

ATT=0dB

+0

-20

-40

-80

-100

Cross Talk(dB)

-120

-60

-80

-100

FFT Spectrum(dBr)

-120

-140

20 200k100 1k 10k 100k

Frequency(Hz)

-140

0

2k 4k 6k 8k 10k

Frequency(Hz)

Figure 9. Crosstalk frequency response Figure 10. FFT spectrum

100

10

1

0.1

THD+N(%)

0.01

IN=0.8Vrms

V

f=1kHz

ATT=0dB

20kHz LPF

6

5

4

3

2

Current Consumption(mA)

1

V

IN=0.8Vrms=0dBr

f=1kHz

ATT=0dB

BH Window

12k 14k 16k 18k

AVDD+DVDD

ADRS1=ADRS2=0V

20k

0.001

1 10 100

Load Resistance(kΩ)

0

2.4 2.7 3 3.3 3.6

Power Supply(V)

Figure 11. THD + N vs. load resistance Figure 12. Current consumption vs. supply voltage

6

5

4

VDD=3.3V

3

VDD=3.0V

2

VDD=2.7V

Current Consumption(mA)

1

0

-50 -25 0 25 50 75 100

AVDD+DVDD

ADRS1=ADRS2=0V

Operating Temperature(°C)

Figure 13. Current consumption vs. operating

temperature

NIPPON PRECISION CIRCUITS—10

Page 11

SM6451BV

TYPICAL APPLICATIONS

Connection Guidelines

Decoupling capacitors of approximately 10 µF should be connected from AVDD, VRL, VRR to AVSS, and

from DVDD to DVSS.

In addition, approximately 0.01 µF capacitors should also be connected from AVDD, VRL, VRR to AVSS, and

from DVDD to DVSS to suppress digital switch noise.

An approximately 0.001 µF capacitor connected from RSTN to DVSS will force a system reset when power is

applied.

Connection 1 (to DAC)

CPU

MDT MCK MLEN

DAC

LPF

LPF

2.5 to 3.6V

LIN

RIN

SM6451

DVDD

LOUT

ROUT

DVSS

L-ch OUT

R-ch OUT

AVDD

ADRS1

AVSS

ADRS2

Connection 2

When there is a possibility that the input peak-to-peak amplitude will exceed the supply voltage, input protection diodes should be connected to prevent device breakdown.

AVDDAVDD

L-ch Input

R-ch Input

LIN LOUT

SM6451

RIN ROUT

AVSS

L-ch Output

R-ch Output

NIPPON PRECISION CIRCUITS—11

Page 12

SM6451BV

NIPPON PRECISION CIRCUITS INC. reserves the right to make changes to the products described in this data sheet in order to

improve the design or performance and to supply the best possible products. Nippon Precision Circuits Inc. assumes no responsibility for

the use of any circuits shown in this data sheet, conveys no license under any patent or other rights, and makes no claim that the circuits

are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision

Circuits Inc. makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification.

The products described in this data sheet are not intended to use for the apparatus which influence human lives due to the failure or

malfunction of the products. Customers are requested to comply with applicable laws and regulations in effect now and hereinafter,

including compliance with export controls on the distribution or dissemination of the products. Customers shall not export, directly or

indirectly, any products without first obtaining required licenses and approvals from appropriate government agencies.

NIPPON PRECISION CIRCUITS INC.

4-3, Fukuzumi 2-chome

Koto-ku, Tokyo 135-8430, Japan

NIPPON PRECISION CIRCUITS INC.

Telephone: 03-3642-6661

Facsimile: 03-3642-6698

NC9925AE 2000.02

NIPPON PRECISION CIRCUITS—12

Loading...

Loading...