Page 1

DESCRIPTION

The SM5K3/5K4/5K5 are CMOS 4-bit single-chip

microcomputers incorporating 4-bit parallel processing function, ROM, RAM, 10-bit A/D converter

and timer/counters.

It provides three kinds of interrupts and 4 levels

subroutine stack. Being fabricated through CMOS

process, the chip requires less power and available

in a small package : best suitable for Low power

controlling, compact equipment like a precision

charger.

FEATURES

• ROM capacity : 2 048 x 8 bits

• RAM capacity : 128 x 4 bits

• Instruction sets : 50

• Subroutine nesting : 4 levels

• I/O port :

Input 8

Output 4

Input/output 12 (36QFP/32SOP)

11 (30SDIP)

8 (28SOP)

• Interrupts :

Internal interrupt x 1 (timer)

External interrupt x 2 (2 external interrupt

inputs)

• A/D converter :

Resolution 10 bits

Channels 4

• Timer/counter : 8-bit x 1

• Built-in main clock oscillator for system clock

Ceramic/crystal oscillator (SM5K3/5K5)

CR oscillator (SM5K4)

•

Signal generation for real time clock∗(SM5K3/5K5)

• Built-in 15 stages divider

(

for real time clock∗: SM5K3/5K5)

• Instruction cycle time :

1 µs (MIN.) (2 MHz, at 5 V ± 10%) (SM5K3/5K5)

2 µs (MIN.) (1 MHz, at 2.2 to 5.5 V) (SM5K3/5K5)

1 µs (MIN.) (1.67 MHz ± 20%, at 5 V ± 10%) (SM5K4)

• Large current output pins (LED direct drive) :

15mA (TYP.)

x 4

(sink current)

•

Supply voltages :

2.2 to 5.5 V (SM5K3/5K5)

2.7 to 5.5 V (SM5K4)

•

Packages :

30-pin SDIP (SDIP030-P-0400)

32-pin SOP (SOP032-P-0525)

36-pin QFP (QFP036-P-1010)

28-pin SOP (SOP028-P-0450) (SM5K3/5K5)

24-pin SSOP (SSOP024-P-0275) (SM5K4)

∗

In case of using crystal oscillator

SM5K3/SM5K4/SM5K5

SM5K3/SM5K4

SM5K5

4-Bit Single-Chip Microcomputers

(Controllers With 10-Bit A/D Converter)

- 1 -

In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP devices shown in catalogs, data books,

etc. Contact SHARP in order to obtain the latest device specification sheets before using any SHARP device.

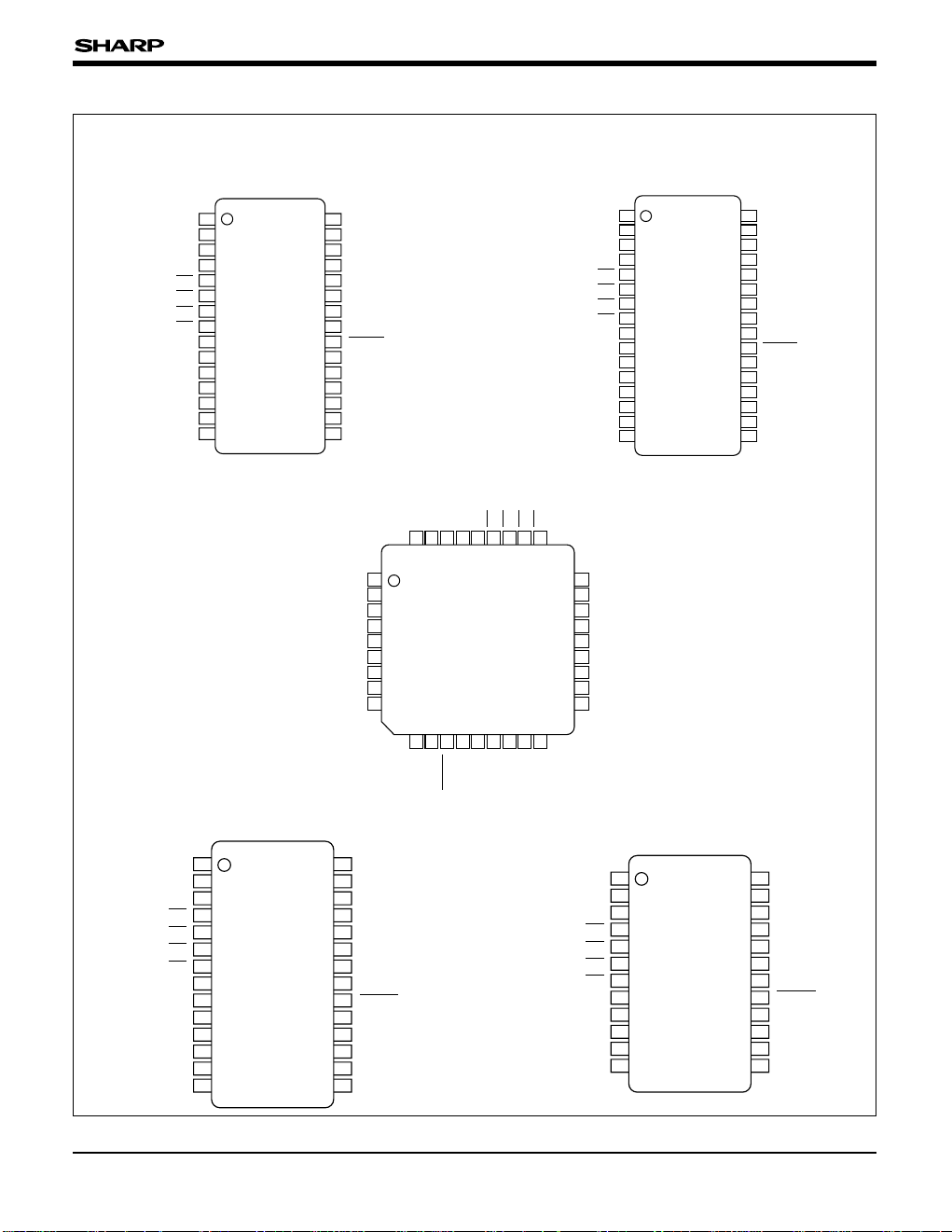

Page 2

- 2 -

36-PIN QFP

10

11

12

13

14

P4

1

P42

P43

P00

P01

P02

P03

P10

P11

P12

P13

P20

P21

P22

28

27

26

25

24

23

22

21

20

19

18

17

16

15

GND

P4

0

AGND

P3

3

P32

P31

P30

VR

RESET

V

DD

OSCOUT

OSCIN

P23

GND

1

2

3

4

5

6

7

8

9

SM5K3/SM5K4/SM5K5

PIN CONNECTIONS

P53

P41

P42

P43

P00

P01

P02

P03

P10

P11

P12

P13

P20

P21

P22

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

GND

P4

0

AGND

P3

3

P32

P31

P30

VR

RESET

V

DD

OSCOUT

OSCIN

P23

P51

P50

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

10

11

12

13

14

15

16

P5

3

P41

P42

P43

P00

P01

P02

P03

P10

P11

P12

P13

P20

P21

P22

GND

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

GND

P5

2

P40

AGND

P3

3

P32

P31

P30

VR

RESET

V

DD

OSCOUT

OSCIN

P23

P51

P50

1

2

3

4

5

6

7

8

9

30-PIN SDIP 32-PIN SOP

TOP VIEW

28-PIN SOP (SM5K3/5K5)

10

11

12

P4

1

P42

P43

P00

P01

P02

P03

P10

P11

P20

P21

P22

24

23

22

21

20

19

18

17

16

15

14

13

GND

P4

0

AGND

P3

2

P31

P30

VR

RESET

V

DD

OSCOUT

OSCIN

P23

1

2

3

4

5

6

7

8

9

24-PIN SSOP (SM5K4)

P13

P12

P11

P10

(NC)

P03

P02

P01

29 28

P20

P21

P22

(NC)

GND

P50

P51

P23

OSCIN

36 35 34 33 32 31 30

1

2

3

4

5

6

7

8

9

P00

P43

27

P42

26

P41

25

P53

24

GND

23

(NC)

22

P52

21

P40

20

AGND

19

10 1112 13 14 15 16 17 18

VR

P31

P32

P33

RESET

(NC)

P30

VDD

OSCOUT

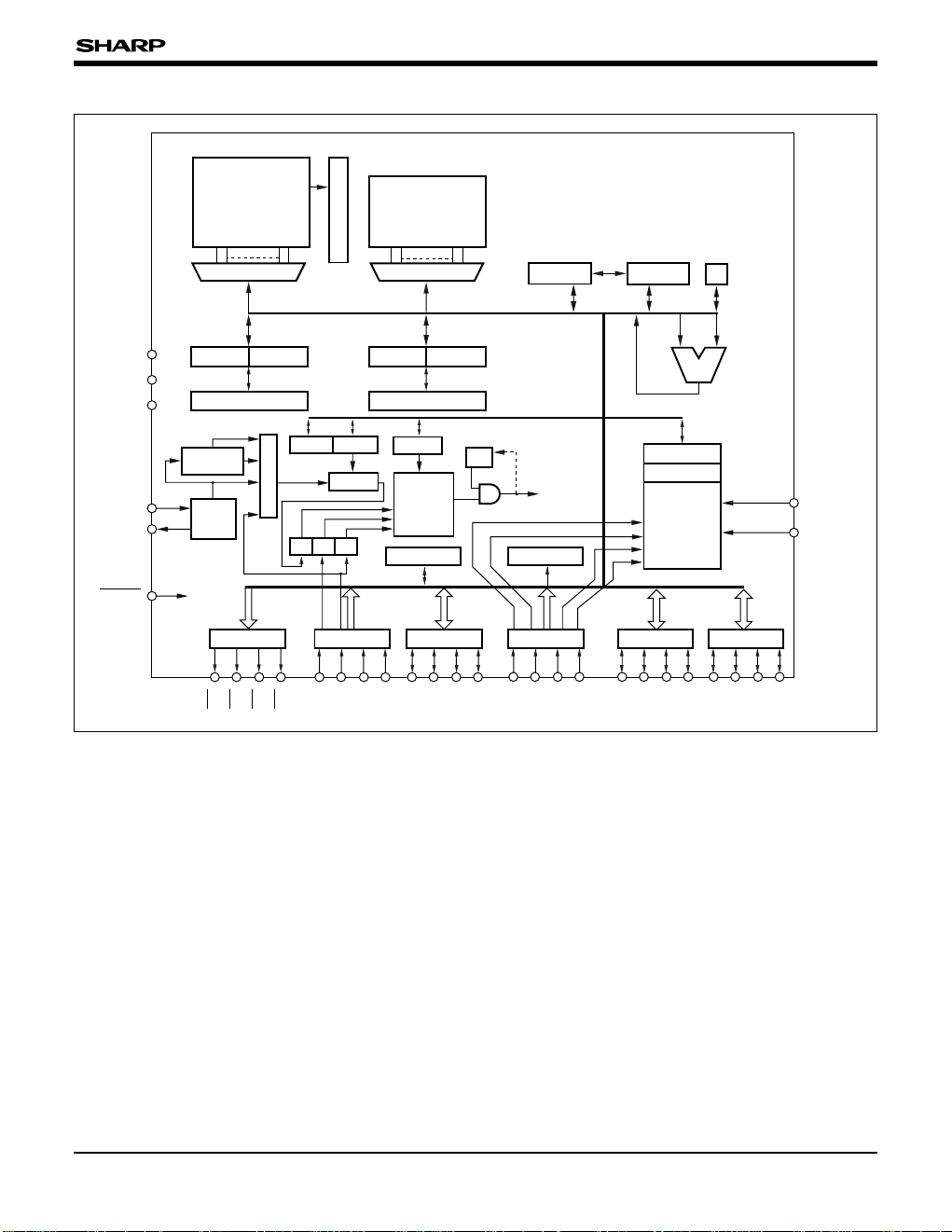

Page 3

- 3 -

SM5K3/SM5K4/SM5K5

BLOCK DIAGRAM

Nomenclature

A : A register

A/D : A/D converter unit

ALU : Arithmetic logic unit

B

M, BL : RAM address register

C : Carry flag

IFA, IFB, IFT : Interrupt request flag

IME : Interrupt master enable flag

INST. DEC. : Instruction decoder

INT : Interrupt control unit

P0-P5 : Port register

P

U, PL : Program counter

R8, R9, RC, RE, RF

: Mode register

RA : Count register

RB : Modulo register

SB : SB register

SR : Stack register

P00

P01

P02

P03

P10

P11

P12

P13

P20

P21

P22

P23

P30

P31

P32

P33

P40

P41

P42

P43

P50

P51

P52

P53

P2

P0

P1

P3 P4 P5

IFT IFAIFB

FR R3

INT

A/D

VR

AGND

OSC

RC RB

RE

SR x 4

PRESCALER

SR (8)

P

U (5) PL (6)

B

M (4) BL (4)

IME

RA

INTERRUPT

CONTROLLER

DECDEC

X (4)

A (4)

C

ALU

ROM

VDD

GND

OSC

IN

OSCOUT

RESET

2 048-BYTE

128 x 4-BIT

RAM

R8

R9

INST.DEC.

SELECTOR

ALU

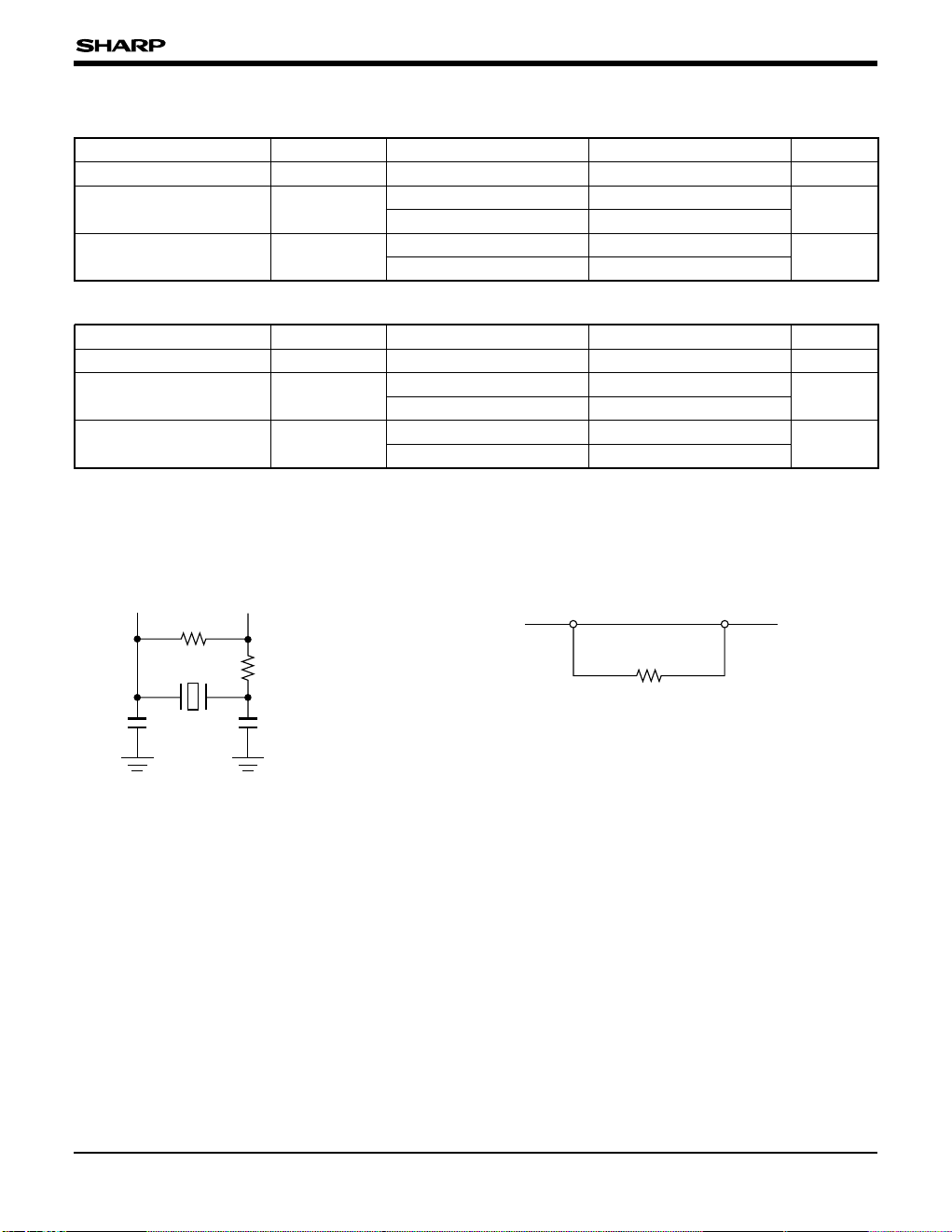

Page 4

- 4 -

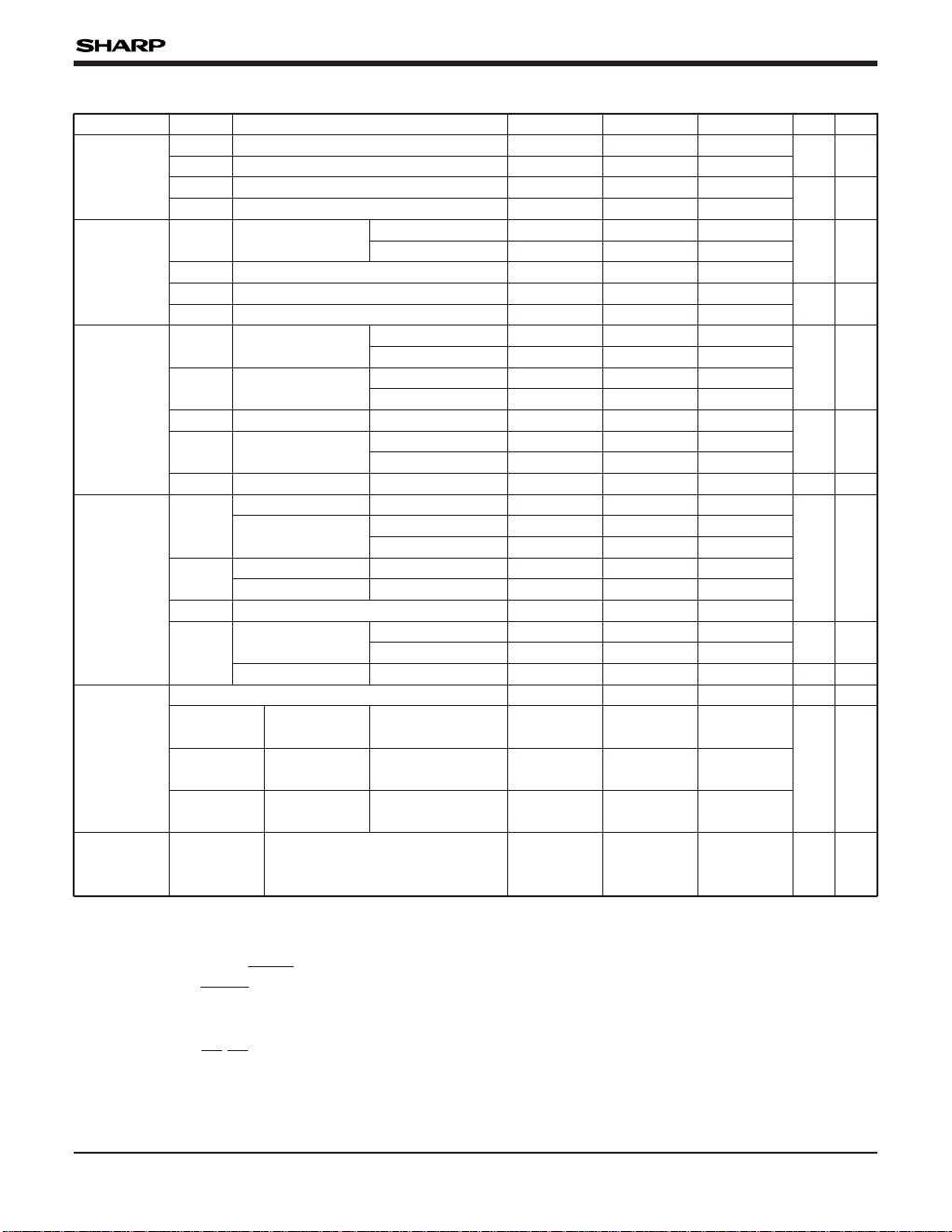

PARAMETER

SM5K3/SM5K4/SM5K5

PIN DESCRIPTION

ABSOLUTE MAXIMUM RATINGS

SYMBOL I/O FUNCTION

P00-P03

O High current output (sink current 15 mA)

P10-P11 I Input (standby release) (counter input : P11) with pull-up resistor

P12-P13 I Input (standby release) with pull-up resistor

P20-P23 I/O Input (with pull-up resistor) or output (independent)

P30-P33 I Input (also used as analog input) with pull-up resistor

P40-P43, P50-P53 I/O Input (with pull-up resistor) and output

OSCIN, OSCOUT I/O Ceramic/crystal oscillation pin (SM5K3/5K5)/CR oscillation pin (SM5K4)

RESET

I Reset signal input with pull-up resistor

VR, AGND I A/D converter reference supply input port

VDD, GND I Power supply, Ground

SYMBOL CONDITIONS RATING UNIT

Supply voltage VDD – 0.3 to +7.0 V

Input voltage VI – 0.3 to VDD+0.3 V

Output voltage VO – 0.3 to VDD+0.3 V

Maximum output current

IOH High-level output current (all outputs) 4 mA

IOL0 Low-level output current (

P0

0-P03

) 30 mA

IOL1

Low-level output current (all but P00-P03)

4 mA

Total output current

∑IOH High-level output current (all outputs) 20 mA

∑IOL Low-level output current (all outputs) 80 mA

TOPR

–20 to +70 (SM5K3/5K5)

–20 to +85 (SM5K4)

°C

Storage temperature

TSTG –55 to +150 °C

Operating temperature

NOTE :

Symbols apply to 32-pin SOP and 36-pin QFP. (

In case of 30-pin SDIP, P52does not exist. In case of 28-pin SOP, P50-P53do not exist.

In case of 24-pin SSOP, P12, P13, P33, P50-P53 pins do not exist.)

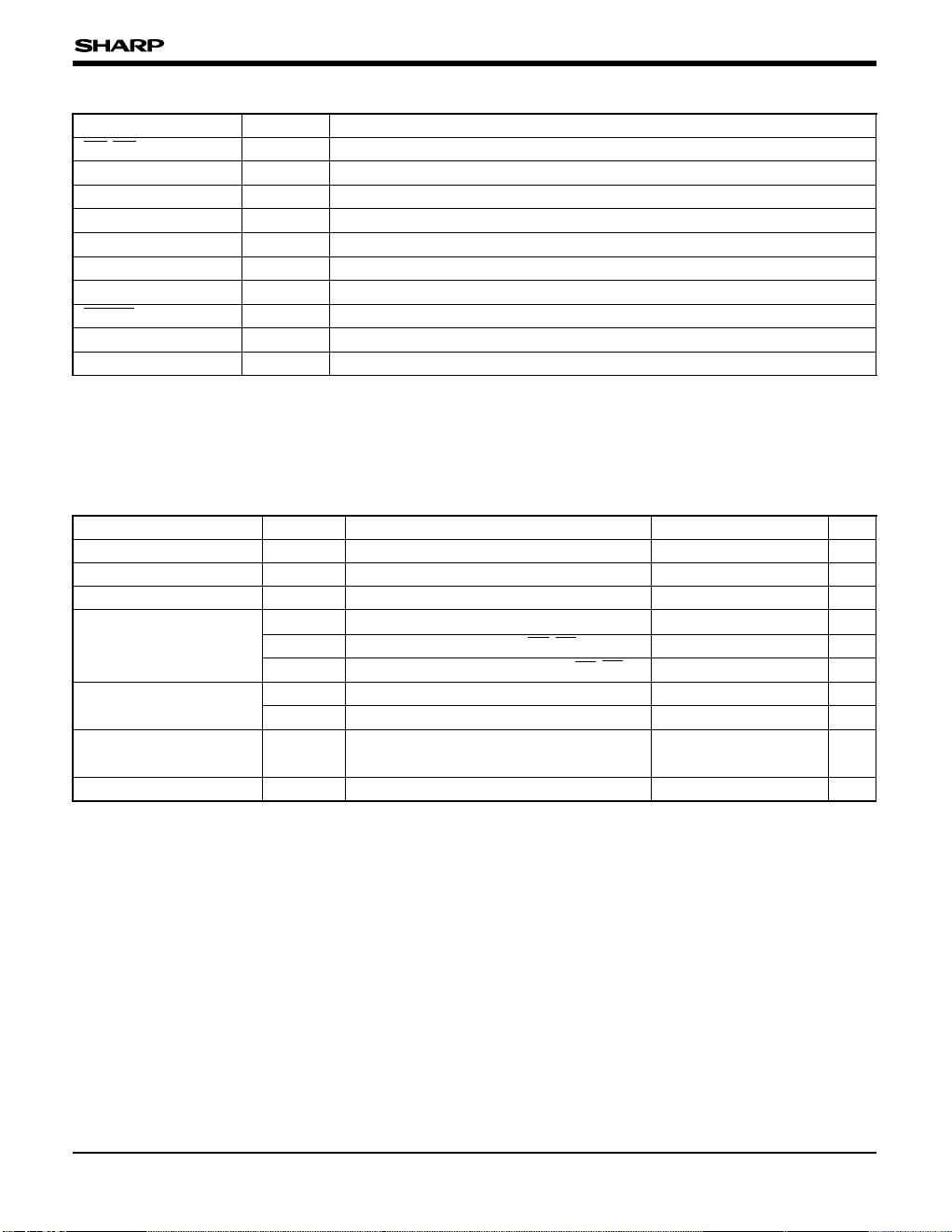

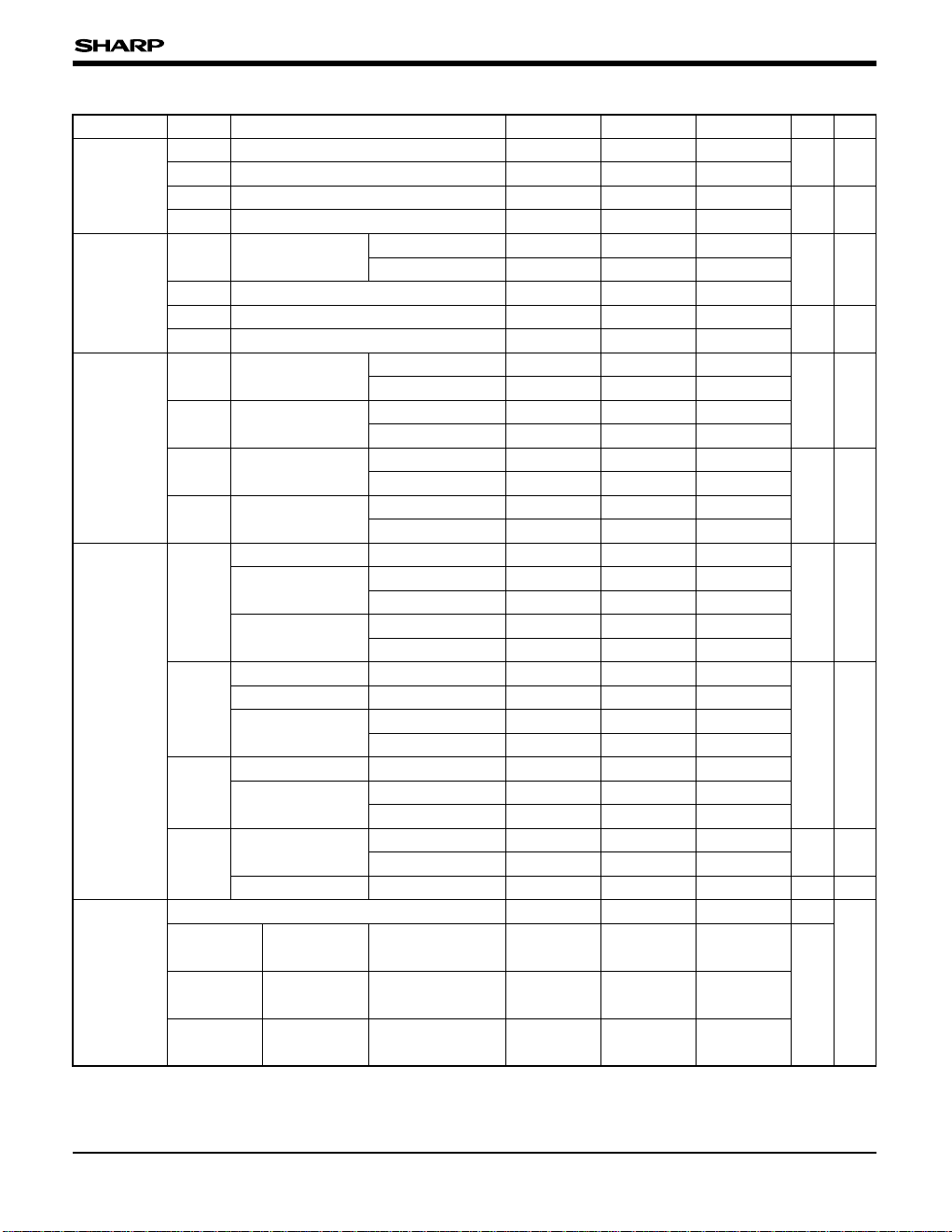

Page 5

- 5 -

SM5K3/SM5K4/SM5K5

RECOMMENDED OPERATING CONDITIONS

(SM5K3/5K5)

PARAMETER SYMBOL CONDITIONS RATING UNIT

Supply voltage VDD 2.2 to 5.5 V

Instruction cycle TSYS

VDD = 2.2 to 5.5 V 2 to 61

µs

VDD = 5.0 V ± 10% 1 to 61

Main clock frequency

(OSC

IN-OSCOUT)

fOSC

VDD = 2.2 to 5.5 V 1 M to 32.768 k

Hz

VDD = 5.0 V ± 10% 2 M to 32.768 k

(SM5K4)

NOTES :

• The typical oscillation frequency shall be determined in

consideration of operating condition and fluctuation

frequency.

• Mount Rf, RD, C

1, C2, Oscillator (SM5K3/5K5)/Rf (SM5K4)

as close as possible to the oscillator pins of the LSI, in

order to reduce an influence from floating capacitance.

• Since the value of resistor Rf, RD, C

1, C2, Oscillator

(SM5K3/5K5)/Rf (SM5K4) varies depending on circuit

pattern and others, the final Rf, RD, C

1, C2, Oscillator

(SM5K3/5K5)/Rf (SM5K4) value shall be determined on the

actual unit.

• Don't connect any line to OSC

IN and OSCOUT except

oscillator circuit.

• Don't put any signal line across the oscillator circuit line.

• On the multilayer circuit, do not let the oscillator circuit

wiring cross other circuit.

• Minimize the wiring capacitance of GND and V

DD .

OSCILLATION CIRCUIT

PARAMETER SYMBOL CONDITIONS RATING UNIT

Supply voltage VDD 2.7 to 5.5 V

Instruction cycle TSYS

VDD = 2.7 to 5.5 V 2 to 5

µs

VDD = 5.0 V ± 10% 1 to 5

Main clock frequency ∗

(OSCIN-OSCOUT)

fOSC

VDD = 2.7 to 5.5 V 1 M to 400 k

Hz

VDD = 5.0 V ± 10% 2 M to 400 k

∗

Degree of fluctuation frequency :

± 20%

OSCOUTOSCIN

Rf

Rf = 33 kΩ

(fosc = 1.67 MHz, TYP.)

• SM5K3/5K5

∗

Reference only : Circuit configuration varies according to

oscillator used.

• SM5K4

OSCOUTOSCIN

Rf

RD

Oscillator

C

1 C2

Page 6

- 6 -

NOTES :

1. Applicable pins : P12, P13, P20-P23, P30-P33 (digital input

mode), P4

0-P43 P50-P53

2. Applicable pins : OSCIN, RESET, P10, P11

3. Applicable pins : RESET, P10-P13, P20-P23, P40-P43,

P5

0-P53 (digital input mode)

4. Applicable pins : P3

0-P33 (analog input mode)

5. Applicable pins : P0

0-P03 (high current mode)

6. Applicable

pins :

P20-P23, P40-P43, P50-P53(output mode)

∗

1

7. Applicable pins : P30-P33

∗

2

8. No load (A/D conversion is stop.)

9. A/D conversion in operation (operation enable)

10. A/D conversion in stop (operation disable)

∗

1

In case of 32-pin SOP and 36-pin QFP.

(In case of 30-pin SDIP, P5

2

dose not exist. In case of

28-pin SOP, P5

0

-P53do not exist.)

∗

2

P3 ports are normally used for input ports with pull-up

resistor. These ports can be also used.

SM5K3/SM5K4/SM5K5

VIH1 0.8 x VDD VDD

V1

V

IL1 0 0.2 x VDD

VIH2 0.9 x VDD VDD

V2

V

IL2 0 0.1 x VDD

VDD = 2.2 to 3.3 V 2 25 90

I

IL1 VIN = 0 V

V

DD = 4.5 to 5.5 V 25 70 250 µA 3

I

IH1 VIN = VDD 2

I

IL2 VIN = 0 V 1.0 10

µA 4

I

IH2 VIN = VDD 1.0 10

V

DD = 2.2 to 3.3 V 5 15

I

OL1 VO = 1.0 V

V

DD = 4.5 to 5.5 V 15 25

mA 5

V

DD = 2.2 to 3.3 V 0.3 1.5

I

OH1 VO = VDD – 0.5 V

V

DD = 4.5 to 5.5 V 1.0 2.2

V

DD = 2.2 to 3.3 V 1.2 5.0

I

OL2 VO = 1.5 V

V

DD = 4.5 to 5.5 V 5 9.0

mA 6

V

DD = 2.2 to 3.3 V 0.3 2.0

I

OH2 VO = VDD – 0.5 V

V

DD = 4.5 to 5.5 V 1.0 2.4

V

DD = 2.2 to 3.3 V 0.15

I

OH3 VOH = VDD – 1.0 V mA 7

V

DD = 4.5 to 5.5 V 0.5

f

OSC = 2 MHZ

V

DD = 4.5 to 5.5 V 1 200 2 500

V

DD = 2.2 to 3.3 V 300 800

f

OSC = 1 MHz

I

DD VDD = 4.5 to 5.5 V 600 1 200

f

OSC = 32.768 kHz

V

DD = 2.2 to 3.3 V 20 120

(Crystal OSC mode)

fOSC = 2 MHz

V

DD = 4.5 to 5.5 V 760 1 500

V

DD = 2.2 to 3.3 V 200 600 µA 8

f

OSC = 1 MHz

I

HLT VDD = 4.5 to 5.5 V 400 900

f

OSC = 32.768 kHz

V

DD = 2.2 to 3.3 V 20 75

(Crystal OSC mode)

Ceramic OSC mode

VDD = 2.2 to 3.3 V 2

I

STOP fOSC = 32.768 MHz

V

DD = 2.2 to 3.3 V 15 40

(Crystal OSC mode)

A/D in operation

V

DD = 4.5 to 5.5 V 220 450 µA 9

I

VR

A/D in stop

V

DD = 4.5 to 5.5 V 2 µA 10

Resolution

10 bit

Differential

fOSC = 1 MHz

V

DD = VR = 5.0 V ± 2.5 ± 4.0

linearity error

TOPR = 25°C

Sequential

fOSC = 1 MHz

V

DD = VR = 5.0 V ± 3.2 ± 5.0 LSB

linearity error

TOPR = 25°C

f

OSC = 1 MHz

Total error VDD = VR = 5.0 V ± 4.0 ± 6.0

TOPR = 25°C

A/D

conversion

Input voltage

Input current

Output current

Supply cerrent

DC CHARACTERISTICS

• SM5K3 (TOPR = –20 to +70°C, TYP. value : VDD = 5.0 or 3.0 V, Unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS MIN. TYP. MAX.

UNIT

NOTE

Page 7

- 7 -

Resolution 10

Differential

fOSC = 1.0 MHz

VDD = VR = 5.0 V ± 2.5 ± 4.0

linearity error

TOPR = 25°C

Sequential

fOSC = 1 MHz

V

DD = VR = 5.0 V ± 3.2 ± 5.0

linearity error

TOPR = 25°C

f

OSC = 1 MHz

Total error V

DD = VR = 5.0 V ± 4.0 ± 6.0

T

OPR = 25°C

V

IH1 0.8 x VDD VDD

VIL1 0 0.2 x VDD

VIH2 0.9 x VDD VDD

VIL2 0 0.1 x VDD

VDD= 2.7 to 3.3 V

1.0 25 90

I

IL1 VIN = 0 V

VDD= 4.5 to 5.5 V

15 70 250

I

IH1 VIN = VDD 3.0

I

IL2 VIN = 0 V 1.0 10

I

IH2 VIN = VDD 1.0 10

VDD= 2.7 to 3.3 V

315

I

OL1 VO = 1.0 V

VDD= 4.5 to 5.5 V

12 25

VDD= 2.7 to 3.3 V

0.2 1.5

I

OH1 VO = VDD – 0.5 V

VDD= 4.5 to 5.5 V

0.8 2.2

I

OL2 VO = 1.5 V

VDD= 4.5 to 5.5 V

4.0 9.0

VDD= 2.7 to 3.3 V

0.2 2.0

I

OH2 VO = VDD – 0.5 V

VDD= 4.5 to 5.5 V

0.8 2.4

I

OH3 VOH = VDD – 1.0 V

VDD= 4.5 to 5.5 V

0.5

f

OSC = 2.0 MHz

VDD= 4.5 to 5.5 V

1 200 2 800

I

DD

VDD= 2.7 to 3.3 V

300 900

f

OSC = 1.0 MHz

VDD= 4.5 to 5.5 V

600 1 400

f

OSC = 2.0 MHz

VDD= 4.5 to 5.5 V

760 1 700

I

HLT

fOSC = 1.0 MHz

VDD= 4.5 to 5.5 V

400 1 000

I

STOPVDD

= 2.7 to 5.5 V

5

A/D conversion

VDD= 2.7 to 3.3 V

130 350

I

VR in operation

VDD= 4.5 to 5.5 V

220 500

A/D conversion in stop

VDD= 2.7 to 5.5 V

3

• SM5K4 (TOPR = –20 to +85°C, TYP. value : VDD = 5.0 or 3.0 V, Unless otherwise noted.)

SM5K3/SM5K4/SM5K5

PARAMETER SYMBOL

CONDITIONS MIN. TYP. MAX.

UNIT

NOTE

Input voltage

V 1

V 2

Input current

µA 3

µA

4

Output current

mA 5

mA

6

mA

7

Supply current

µA 8

µA

9

µA 10

A/D

conversion

Reference

clock oscillator

frequency

bit

LSB

MHz

NOTES :

1. Applicable pins : P12, P13, P20-P23, P30-P33 (digital input

mode), P4

0-P43, P50-P53

∗

1

2. Applicable pins : OSCIN, RESET, P10, P11

3. Applicable pins : RESET, P10-P13, P20-P23, P40-P43,

P5

0-P53 (digital input mode)

∗

1

4. Applicable pins : P30-P33 (analog input mode)

5. Applicable pins : P0

0-P03 (high current output)

6. Applicable

pins :

P20-P23, P40-P43, P50-P53(output mode)

∗

1

7. Applicable pins : P30-P33

∗

2

8. No load (A/D conversion in stop)

9. A/D conversion in operation (A/D conversion enable)

10. A/D conversion in stop (A/D conversion disable)

∗

1

In case of 32-pin SOP and 36-pin QFP.

(In case of 30-pin SDIP, P5

2

pin dose not exist. In case of

24-pin SSOP, P1

2

, P13, P33, P50-P53pins do not exist.)

∗

2 P3 ports are normally used for input port with pull-up

resistor. These ports can be also used as a suspected

case of output port.

fOSC

VDD= 4.5 to 5.5 V, Rf = 33 kΩ

1.34 1.67 2.0

Page 8

SM5K3/SM5K4/SM5K5

- 8 -

• SM5K5 (TOPR = –20 to +70°C, TYP. value : VDD = 5.0 or 3.0 V, Unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS MIN.

UNIT

NOTE

Input voltage

VIH1

0.8 x VDD

0

0.9 x VDD

0

VDD

0.2 x VDD

VDD

0.1 x VDD

VV1

2

Input current

IIL1

VIN = 0 V

2

25

25

70

1

1

90

250

2

10

10

µAµA3

4

Output current

IOL1 VO = 1.0 V

5

15

0.3

1.0

7

20

300

1 000

15

25

1.5

2.2

35

60

2 000

2 400

mA

µA

5

6

Supply current

IDD

fOSC = 2 MHz 1 200

300

600

20

40

760

400

15

20

2

10

130

220

2 500

800

1 200

120

160

1 500

900

60

90

2

10

25

300

450

2

µA

µA

µA

µA

7

7

8

9

A/D

conversion

Resolution 10

± 2.5

± 3.2

± 4.0

± 4.0

± 5.0

± 6.0

bit

LSB

VIH2

VIL1

VIL2

IIL2

IIH1

IIH2

IOL2

IOH1

IOH2

ISTOP

IHLT

IVR

Sequential

linearity error

Differential

linearity error

Total error

VDD = VR = 5.0 V

V

DD = VR = 5.0 V

V

DD = VR = 5.0 V

fOSC = 1 MHz

TOPR = 25°C

fOSC = 1 MHz

T

OPR = 25°C

fOSC = 1 MHz

T

OPR = 25°C

VIN = VDD

VIN = 0 V

VIN = VDD

VDD= 2.2 to 3.3 V

VDD= 4.5 to 5.5 V

VO = VDD–0.5 V

VO = 0.5 V

VO = VDD–0.5 V

VDD= 2.2 to 3.3 V

VDD= 4.5 to 5.5 V

VDD= 2.2 to 3.3 V

VDD= 4.5 to 5.5 V

VDD= 2.2 to 3.3 V

VDD= 4.5 to 5.5 V

VDD= 2.2 to 3.3 V

VDD= 4.5 to 5.5 V

VDD= 4.5 to 5.5 V

A/D in operation

Ceramic OSC mode

fOSC = 32.768 kHz

(Crystal OSC mode)

fOSC = 1 MHz

fOSC = 32.768 kHz

(Crystal OSC mode)

fOSC = 1 MHz

fOSC = 2 MHz

fOSC = 32.768 kHz

(Crystal OSC mode)

A/D in stop

VDD= 4.5 to 5.5 V

VDD= 4.5 to 5.5 V

VDD= 2.2 to 3.3 V

VDD= 2.2 to 3.3 V

VDD= 4.5 to 5.5 V

VDD= 4.5 to 5.5 V

VDD= 4.5 to 5.5 V

VDD= 2.2 to 3.3 V

VDD= 4.5 to 5.5 V

VDD= 2.2 to 5.5 V

VDD= 2.2 to 3.3 V

VDD= 4.5 to 5.5 V

VDD= 2.2 to 3.3 V

VDD= 2.2 to 3.3 V

MAX.TYP.

Page 9

SM5K3/SM5K4/SM5K5

- 9 -

NOTES :

1. Applicable pins : P12, P13, P20-P23, P30-P33 (digital input

mode), P4

0-P43, P50-P53

∗

1

2. Applicable pins : OSCIN, RESET, P10, P11

3. Applicable pins : RESET, P10-P13, P20-P23, P40-P43,

P5

0-P53 (digital input mode)

∗

1

4. Applicable pins : P30-P33 (analog input mode)

5. Applicable pins : P0

0-P03 (high current port)

6. Applicable pins : P2

0-P23, P40-P43, P50-P53 (output mode)

∗

1

7. No load (A/D conversion in stop)

8. A/D conversion in operation (operation enable)

9. A/D conversion in stop (operation disable)

∗

1 In case of 32-pin SOP and 36-pin QFP.

( In case of 30-pin SDIP, P5

2 dose not exist. In case of

28-pin SOP, P5

0-P53 do not exist.)

SYSTEM CONFIGURATION

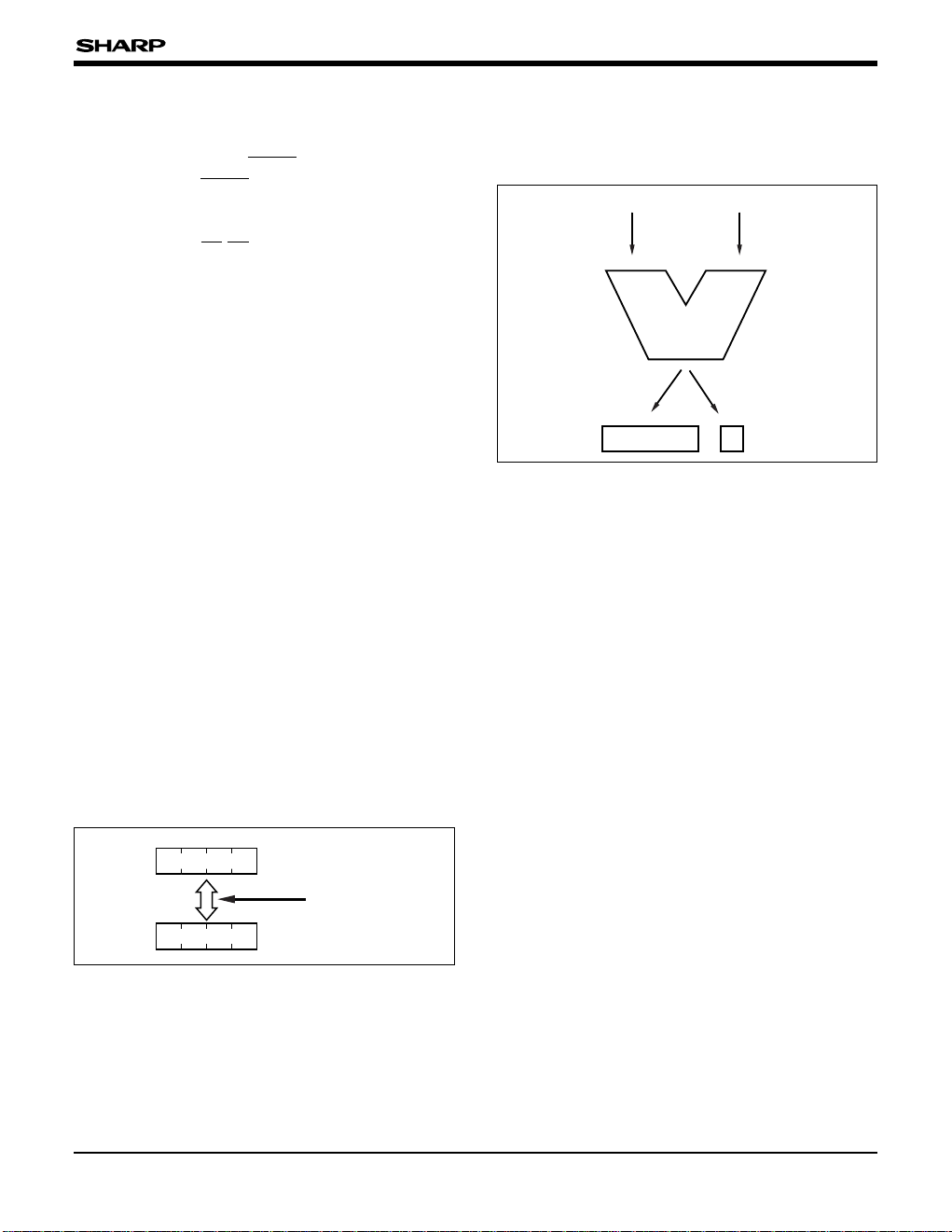

A Register and X Register

The A register (or accumulator : ACC) is a 4-bit

general purpose register. The register is mainly

used in conjunction with the ALU, C flag and RAM

to transfer numerical value and data to perform

various operations. The A register is also used to

transfer data between input and output pins.

The X register (or auxiliary accumulator) is a 4-bit

register and can be used as a temporary register.

It loads contents of the A register or its content is

transferred to the A register. When the table

reference instruction PAT is used, the X and A

registers load ROM data. A pair of A and X

registers can accommodate 8-bit data.

Arithmetic and Logic Unit (ALU) and

Carry Signal Cy

The ALU performs 4-bit parallel operation

The ALU operates binary addition in conjunction

with RAM, C flag and A register. The carry signal

Cy is generated if a carry occurs during ALU

operation. Some instructions use Cy : ADC

instruction sets/clears the content of the C flag;

ADX instruction causes the program to skip the

next instruction. Note that Cy is the symbol for

carry signal and not for C flag.

3

3

0

0

A register

X register

EXAX instruction

Fig. 1 Data Transfer Example between

A Register and X Register

c

Areg

ALU

Result of operation

4-bit data 4-bit data

Fig. 2 ALU

Page 10

SM5K3/SM5K4/SM5K5

- 10 -

Data Memory (RAM)

The data memory (RAM) is used to store data up

to 4 x 16 x 8 = 512 bits.

Fig. 3 B Register and SB Register

File

(0-7)

B

M

BL

0

1

2

3

4

5

6

7

0123456789ABCDEF

Word (0-F

H)

1 word = 4-bit

Fig. 4 RAM File and Word

B Register and SB Register

• B register (BM, BL)

The B register is an 8-bit register that is used to

specify the RAM address. The upper 4-bit section

is called B

M register and lower 4-bit BL.

• SB register

The SB register is an 8-bit register used as the

save register for the B register. The contents of B

register and SB register can be exchanged through

EX instruction.

7

3

0

003

EX instruction (swap)

SB register

B

M registerB register BL register

Page 11

SM5K3/SM5K4/SM5K5

- 11 -

The program counter PC specifies the ROM

address. The PC consists of 12-bit as shown in

Fig. 5 : The upper 6-bit (P

U) represents a page

while the lower 6-bit (P

L) denotes a step. The PU

section is a register and the PL section, a binary

counter.

Execution of interrupt handling and the table

reference instruction PAT also automatically uses 1

stage of the stack register SR.

Program Memory (ROM)

The ROM is used to store the program. The

capacity of the ROM is 2 048-step (32-page by 64-

step. See Fig. 6). The configuration of the ROM

and program jumps are illustrated in Fig. 7.

PU

Specifies a page (Pages 00H-1FH) Specifies a page (Pages 00H-3FH)

PL

Fig. 6 Page and Step for ROM

Fig. 5 Program Counter PC and Stack Register SR

Program Counter PC and Stack Register SR

Program counter PC

Page Step

PU PL

MSB LSB

Push Pop

SR ( level 1 )

SR ( level 2 )

SR ( level 3 )

SR ( level 4 )

Stack register SR

Page 12

SM5K3/SM5K4/SM5K5

- 12 -

PU (page) PU (page)

Start address upon hardware reset

Front cover of

subroutine TRS

Reference to the table during execution

of PAT instructions

Interrupt

Standby released

00H

01H

02H

03H

04H

05H

06H

07H

08H

09H

0AH

0BH

0CH

0DH

0EH

0FH

10H

11H

12H

13H

14H

15H

16H

17H

18H

19H

1AH

1BH

1CH

1DH

1EH

1FH

Number in a circle is a step number in the program jump.

Last page, last step (1F3F

H)

RTN

TLxy

RTN

TRSx

TRSx

TLxy

TRx

RTN

CALLxy

TRx

2

1

3

2

1

1

1

1

1

2

Fig. 7 ROM Configuration and Program Jump Example

Page 13

SM5K3/SM5K4/SM5K5

- 13 -

Output Latch Register and Mode Register

The SM5K3/5K4/5K5 contain 6 output-latch

registers and 8 mode-registers which either latch

contents of output ports or control some functions

of the SM5K3/5K4/5K5.

These registers, their functions and available

transfer instructions are shown in Table 1 below.

An output latch register sets the output level of the

pin to which it is connected.

Refer to the section of “MODE REGISTERS”

concerning about the details mode registers.

SYMBOL FUNCTION OUT INL OUT IN/TPB ANP/ORP CONTENT OF BL

P0 Output register

O

– O – O 0

P1 Input register – O – O – 1

P2 I/O register (independent) – – O O O 2

P3 Input register (and analog input) – – – O – 3

R3 Control register – – O – – 3

P4 I/O register – – O O O 4

P5 I/O register – – O O O 5

R8∗

A/D data/control register – – O O – 8

R9∗

A/D data register – – O O – 9

RA∗

Timer/counter register – – O O – A

RB∗

Timer/modulo register – – O O – B

RC Timer control register – – O O – C

RE Interrupt mask register – – O O – E

RF P2 directional register – – O O – F

Table 1 Output Latch Registers and Mode Registers

∗

8-bit register

NOTE :

Bit 4 (R84) in the R8 register is read only.

(Read or write operation of this bit does not affect any other operation.)

Page 14

SM5K3/SM5K4/SM5K5

- 14 -

FUNCTIONAL DESCRIPTION

Hardware Reset Function

Reset function initializes the SM5K3/5K4/5K5

systems. When the input on the RESET pin goes

Low, the system enters reset condition after 2

command cycles. After the RESET pin goes High

level, the reset condition is removed as the input

pulse from OSC

IN pin repeats 2

15

times, forcing the

program counter to start at 0 page and 0 address.

Initialized status of the system immediately after

resetting is shown below.

Reset causes the following changes.

1) I/O pins are set input.

2) All mode registers are reset.

3) Output latch register P0 is reset, causing P0

0 to

P0

3 pins go High level.

4) Interrupt request flags (IFA, IFB, and IFT),

interrupt master enable flag (IME) are reset,

disabling all interrupts.

Standby Feature

The standby function saves power by stopping the

program whenever it is not necessary to run. The

mode in which the microcomputer is executing the

program is called the run mode and the mode in

which it stops the program is called the standby

mode. Standby mode is further divided into two

modes : stop mode and halt mode, one of which is

selected by halt instruction or stop instruction. Upon

removal of standby condition, the SM5K3/5K4/5K5

return from the standby mode to the normal run

mode. To enter the standby mode, select either

stop mode or halt mode whichever is appropriate

(Fig. 8).

Table 2 Status of Flags and Registers Immediately after Reset

FLAG REGISTER STATUS FLAG REGISTER STATUS

PC 0 IFA flag 0

SP Level 1 IFB flag 0

RAM Undefined IFT flag 0

Register A Undefined IME flag 0

Register X Undefined C flag Undefined

P0, P2, P4, P5 output latch register 0 BM, BL registers, SB register Undefined

Timers (RA, RB), divider 0

R3, R8∗, R9, RC, RE, RF

0

∗

The content of the bit R84 is undefined because it is read only.

Page 15

SM5K3/SM5K4/SM5K5

- 15 -

• Blocks stopped during standby mode

In the halt mode

The system clock generating circuit stops during

the halt mode, deactivating all the blocks driven by

the system clock. The main clock and dividers

remain active. This means that timers can be used

while in the halt mode. Both internal and external

clocks can be used as the count clock.

In the stop mode

The main clock and system clock stop upon

entering the stop mode. Therefore, only timers

using the external clock remain active.

• Counters that the system retains during

standby mode

The contents that will be retained in the halt mode

will also be retained in the stop mode. These items

are shown in Table 3.

Operation mode Standby mode

HALT mode

Run HALT command

HALT mode

release event

Normal

operation

Run STOP command

STOP mode

release event

STOP mode

Fig. 8 Operation Shift of Program

Table 3 System Contents Secured During Standby Mode

FLAG REGISTER OUTPUT LATCH REGISTER/MODE REGISTER OTHER

IFA flag

IFB flag

IFT flag

IME flag

C flag

A register

X register

B

M, BL register

SP

SR

P0, P2, R3, P5

R8, R9, RA, RB

RC, RE, RF

RAM

• Releasing events of standby mode (6-type)

RELEASING EVENT FLAG INT/EXT MASKABLE / NONMASKABLE PRIORITY

Reset input – External Nonmaskable –

Low level input on P10 pin IFA External Maskable 1

Low level input on P11 pin IFB External Maskable 2

Low level input on P12 pin – External Nonmaskable –

Low level input on P13 pin – External Nonmaskable –

Timer overflow IFT Internal Maskable 3

Page 16

SM5K3/SM5K4/SM5K5

- 16 -

• Interrupt used with SM5K3/5K4/5K5

Interrupt event occurs on the falling edge of P1

0 or

P1

1 pin input, or the overflow at the timer. These

events set flags IFA, IFB and IFT respectively, that

then serve as interrupt request flag.

Table 4 shows interrupt handling priority level and

jump address.

Table 4 Interrupt Event Summary

INTERRUPT EVENT

(REQUEST FLAG)

JUMP ADDRESS

PRIORITY ORDER INTERRUPT MASK FLAG

Falling edge of input on P10 (IFA) 2 1 RE0

Falling edge of input on P11 (IFB) 2 2 RE1

Timer overflow (IFT) 2 3 RE2

PAGE STEP

0

2

4

• Usage of halt mode and stop mode

The system returns back to the normal operation

mode upon occurring of a standby mode releasing

condition. The halt mode should be used when the

system must enter and exit normal operation

frequently as in the case of key operation.

The halt mode should also be used to keep timers

that are operating from the internal clock, while in

the standby mode.

The stop mode further saves power than the halt

mode but requires slightly longer time to return to

the normal mode. Therefore, the stop mode should

be used when the system will not be required to

return to the normal mode in a short time.

Interrupt Feature

The interrupt block consists of mask flags (bits RE0,

RE1 and RE2), IME flag and interrupt request

handling circuit. Fig. 9 shows the configuration of the

interrupt block.

Mask flag (mode register RE)

RE2

I FA

I FB

I FT

RE1 RE0

Interrupt request flag

IME

Interrupt enable flag

(master enable flag)

Interrupt handling circuit

INT signal

Stack register SR

Program counter PC

Fig. 9 Interrupt Block Diagram

Page 17

SM5K3/SM5K4/SM5K5

- 17 -

• IME flag (master enable flag)

The IME enables or disables all interrupts at the

same time. The IE command, when executed, sets

the IME flag and enables the interrupt specified by

the mask flag setting. The ID command resets the

IME flag, disabling process of any interrupt request.

Setting the IME flag to reset after releasing

hardware reset, all interrupts are inhibited.

• Mode register RE (interrupt mask flag)

The mode register RE (RE0, RE1 and RE2;

interrupt mask flag) individually enables or disables

three type of interrupts.

Timer/Counter

The SM5K3/5K4/5K5 have a pair of built-in

timer/counter. The timer/counter are used to handle

periodic interrupts and to count. The overflowing

timer can be used to disable the halt mode. The

timer/counter serve as interval timer.

The timer/counter consists of an 8-bit count register

RA, modulo register RB (for counter initial value

setting), 15-bit divider and 4-bit mode register RC

(for count clock selection). The configuration of the

timer/counter is shown in Fig. 10.

fSYS

System clock

P11 pin

( external event clock )

Divider

Mode register

( RC register )

f

SYS / 2

0

0

3

3

03

0303

47

47

03

15

fSYS / 2

7

AX

AX

I FT

Modulo register

( RB register )

Count register

( RA register )

After setting BL = 0BH

OUT command ( RB←[ X, A ] )

IN command ( [ X, A ]←RB )

After setting B

L = 0AH

OUT command

After setting BL = 0AH

IN command

Interrupt request flag

Count clock selsctor

Fig. 10 Configuration of Timer/Counter

• Selecting count clock

A count clock is selected by the bit settings in the

mode register RC.

LOWER 2-BIT OF RC BITS

SELECTED COUNT CLOCK

0 fSYS (system clock)

0

f

SYS

/2

7

1

f

SYS

/2

15

1

External event clock (P11)

1 0

0

1

0

1

Table 5 Count Clock Selection

Page 18

SM5K3/SM5K4/SM5K5

- 18 -

A/D CONVERSION MODE

In the A/D conversion mode, the converter converts

the analog input voltage to the digital value. The

analog input voltage is successively compared with

the internal voltage charged on the weighted

capacitor array until its digital equivalent is

determined. The resultant digital data is stored into

the mode registers R8 and R9.

The conversion requires 152.5 µs (main clock at

400 kHz/system clock at 5 µs) or 1.86 ms (main

clock at 32.768 kHz/system clock at 61 µs).

COMPARISON MODE

In the comparison mode, the analog voltage from

one of P3

0 to P33 pins is compared, in amplitude,

with internally generated voltage whose value is set

by the mode registers R8 and R9. The result data

of the comparison is saved into the bit 4 (bit R84)

position of the mode register R8. The comparison

cycle lasts 62.5 µs (main clock at 400 kHz, system

clock at 5 µs) or 763 µs (main clock at 32.768

kHz/system clock at 61 µs).

A/D Conversion

The SM5K3/5K4/5K5 are provided with a built-in

10-bit A/D converter having 4-channel multiplexer

analog inputs. The A/D converter operates in A/D

conversion mode and comparison mode. In the

A/D conversion mode, the converter converts the

analog input from the P3 pin to the digital value;

and in the comparison mode, it compares the input

analog amplitude with that of a reference voltage

set inside the SM5K3/5K4/5K5. The P3

0 to P33

pins can be used as analog voltage inputs. One or

more of these 4 inputs can be set to assume A/D

pin by the bit operation of the mode register R3.

One of these A/D pins is further set as analog input

by the bit operation of the mode register R8. The

A/D converter is controlled by the bits set in the

mode register R8. For details of the mode register

R8, refer to " MODE REGISTERS R8 ".

Configuration of the A/D converter is illustrated in

Fig. 11.

CAUTIONS

• Keep the A/D converter reference voltage on the VR pin

equal to or below V

DD.

• Do not apply the voltage to the VR pin before V

DD is

applied.

• Connect AGND to GND.

Fig. 11 A/D Converter Block Diagram

P30

P31

P32

P33

A/D pins

Multiplexer

Normal input pin

Changeover

R3 register

A register

X, A registers

X, A registers

A/D control, data

(mode register R8 )

A/D data

( Mode register R9 )

VR

AGND

10-bit

D/A

Comparator

Control circuit

Page 19

SM5K3/SM5K4/SM5K5

- 19 -

MODE REGISTERS

The registers which control functions of the

SM5K3/5K4/5K5 and which serve as counter/timer are

commonly referred to as “mode registers”. In the

SM5K3/5K4/5K5, R8 to RB are 8-bit mode registers;

and R3, RC, RE and RF are 4-bit mode registers.

To set data into the mode registers, the OUT

command is used; and to check the contents of the

mode registers IN command is used.

R3 (A/D pin selection register)

Any pin on 4-pin port P3 can be set accommodate

analog voltage (hereafter called A/D pin).

Bit 3 0

Bit i (i = 3 to 0)

Sets P3i pin to either general purpose input or

A/D pin

0 | (General purpose) input

1 | A/D input

R8 (A/D conversion control & A/D data

register)

An 8-bit register used to control A/D conversion

and storing part of A/D conversion result. It also

stores the results of comparison.

Bit 7 0

Bits 7 to 6

Storage of A/D conversion result (A/D conversion

mode) and setting of internal voltage (comparison

mode)

• Use as part of a 10-bit data ragister in

combination with mode register R9.

• Bit R86 is the LSB.

• Store lower 2-bit of converted data in A/D

conversion mode.

• Use as lower 2-bit of internal voltage setting

data in comparison mode.

Bit 5

∗ A/D operation enable/disable flag

0 | Disable (A/D power source off)

1 | Enable (A/D power source on)

Bit 4

Storages of comparison result (read only)

0 | P3i pin voltage < internal setting voltage

1 | P3i pin voltage > internal setting voltage

(i = 3 to 0)

Bit 3

∗ S/R flag (start/clear)

0 | End of operation (or stop)

1 | Start of operation (or in operation)

Bit 2

Operation mode selection

0 | A/D conversion

1 | Comparison

Bits 1 to 0

Select one of A/D pins as A/D conversion

00 | P30

01 | P31

10 | P32

11 | P33

R9 (A/D data register)

The register to store the upper 8-bit of 10-bit data

resulting from A/D conversion.

Bit 7 0

Bit i (i = 7 to 0)

Storages of A/D conversion result (A/D conversion

mode) and setting of internal voltage (comparison

mode)

• Uses as part of a 10-bit data register in

combination with mode register R8.

• Bit R97 is the MSB.

• Stores upper 8-bit of A/D conversion result.

• Uses as upper 8-bit of internal voltage setting

data in comparison mode.

∗

When operation is end, these bits are cleared.

∗

Select one pin which is to be selected by mode register R8.

Page 20

SM5K3/SM5K4/SM5K5

- 20 -

RA (Count register)

Bit 7 0

Bit i (i = 7 to 0)

Count clock input register

• Uses as counter part of timer/counter (count

clock input).

• Loads the content of RB to RA when the RA

overflows or when OUT command (B

L = 0AH)

is executed.

RA←RB

• Loads the content of RA to X and A registers

upon execution of IN command (B

L = 0AH).

(X, A)←RA

• Bit 7 = MSB, bit 0 = LSB

RB (Modulo register)

Bit 7 0

Bit i (i = 7 to 0)

Count initial value storage register

• Uses as modulo register of timer/counter

• Loads the content of RB to X and A registers

upon execution of

IN command (B

L = 0BH) : X = upper bits,

A = lower bits.

(X, A)←RB

• Loads the contents of X and A registers to RB

upon execution of

OUT command (B

L = 0BH) : X = upper bits,

A = lower bits.

RB←(X, A)

• Bit 7 : MSB, Bit 0 : LSB

RC (Timer control)

Bit 3 0

Bit 3

Starts up count of the timer.

0 | Stop

1 | Start

Bit 2 (Unused)

Bits 1 to 0

Select the source clock to the timer.

00 | fSYS (system clock)

01 | fSYS/2

7

10 | fSYS/2

15

11 | Falling edge input on P11 pin

RE (Interrupt mask flag)

Bit 3 0

Bit 3 (Unused)

Bit 2

Removes overflow interrupt from timer or standby

condition.

0 | Disable

1 | Enable

Bit 1

Interrupts on the falling edge of input from P11 pin,

or releases of standby mode by the Low input from

P1

1

pin.

0 | Disable

1 | Enable

Bit 0

Interrupts on the falling edge of input on P10pin, or

releases of standby mode by the Low input from

P1

0

pin.

0 | Disable

1 | Enable

RF (P2 port direction register)

Bit 3 0

Bit i (i = 3 to 0)

Selection of input pin/output pin

0 | Set P2i pin to input.

1 | Set P2i pin to output.

Page 21

SM5K3/SM5K4/SM5K5

- 21 -

I/O Ports

The SM5K3/5K4/5K5 have 24 ports : 8-input, 4output and 12-I/O port. To verify the input, use

suitable instruction to transfer the input on the pin

directly to the A register. To select the output latch

register to which the content of the A register is to

be transferred, and to select the input port from

which the signal or data is to be transferred to the

A register, use the B

L register. For details of BL

settings and associated ports, refer to Table 1.

• Port P0

0 to P03 (CMOS inverting output port)

The data transfers in 4-bit string (use OUT or

OUTL instruction) or in unit of 1-bit (use ANP or

ORP instruction).

• Port P10to P13(input port with pull-up resistor)

The data transfers in unit of 4-bit. This port can be

used as standby/external interrupt input or count

pulse input. The P1 port can also be used as a

standby release port without requiring specific

setting on P1

2 and P13 pins. Pins P10 and P11

require settings through the mode resister RE.

When using the P1 port as an external interrupt

input, use pins P1

0 and P11 with suitable settings in

the mode register RE. When using the P1 port as

the count pulse input, use P1

1 pin.

•

Port P20 to P23 (I/O port with pull-up

resistor

)

Each bit can be independently be set its direction

and can be transferred independently or in

combination of other 3-bit. The direction of the bits

is determined by the RF register. After reset, the

P2 port is set input.

• Port P30to P33(input port with pull-up resistor)

The data transfers in unit of 4-bit. The port can also

be used as A/D analog voltage input. To use the P3

port as the A/D port, set the mode register R3.

• Port P40 to P43 (I/O port with pull-up

resistor

)

The data transfers in unit of 4-bit.

When set output, content of each bit can be set.

Executing the input instruction (IN) sets the P4

ports (P4

0 to P43) to input; and executing output

instruction (OUT, ANP or ORP) sets the port to

output. After reset, the P4 port is set input.

• Port P5

0 to P53 (I/O port with pull-up

resistor

)

The data transfers in unit of 4-bit.

When set output, content of each bit can be set.

Executing the input instruction (IN) sets the P5

ports (P5

0 to P53) to input; and executing output

instruction (OUT, ANP or ORP) sets the port to

output. After reset, the P5 port is set input.

Flags

The SM5K3/5K4/5K5 have 4 flags (C flag and

interrupt request flags [IFA, IFB, IFT] ), which are

used to perform setting and judgments.

Page 22

SM5K3/SM5K4/SM5K5

- 22 -

• Divider

The divider consists of 15 divided-by-two dividers,

providing 2 (f

SYS/2

7

, fSYS/215) of 4 count clocks that

are fed to the counter RA from the system clock.

Its configuration is shown below. The divider can

be cleared by using the DR instruction.

• Oscillator mask option

Selection of type of oscillator, ceramic or crystal, is

made by mask option.

System clock

(fSYS)

Main clock

(fOSC)

Fig. 12 Main Clock and System Clock

Fig. 13 System Clock Generator and Divider

System Clock Generator and Dividers

•

System clock generator

The system clock is the divided-by-two main clock

applied through OSC

IN and OSCOUT (See Fig. 12).

The system clock generator is shown in Fig. 13.

One system clock cycle period is equal to one

instruction execution time when the instruction

consists of 1 word. When the ceramic oscillator

runs at 400 kHz, the system clock fsys is 200 kHz.

This means that the instruction execution time is 5

µs/word. Using a 32.768 kHz crystal oscillator

generates 16.384 kHz fsys and the instruction

execution time is 61 µs/word. The system clock

can be used as count input pulse to the timer.

OSCIN

OSCOUT

CG

111111111111111

fSYS

( System clock )

222222222222222

System clock generator (divided-by-two main clock)

Divider (can be cleared by DR instruction)

fSYS/2

fSYS/2

7

15

Page 23

- 23 -

INSTRUCTION SET

Definition of Symbols

M : Content of RAM at the address defined

by the B register.

← : Transfer direction

∪

: Logical OR

∩

: Logical AND

⊕ : Exclusive OR

Ai : An i bit of A register (i = 3 to 0)

Push : Saves the contents of PC to stack

register SR.

Pop : Returns the contents saved in the stack

register back to PC.

Pj : Indicates output latch register or input

register. Pj ( j = 0, 1, 2, 3, 4, 5)

Rj : Mode register. Rj register ( j = 3, A, B,

C, E, F)

ROM ( ) : Content stored in ROM location defined

by the value in ( ).

CY : Carry in ALU (independent of C flag)

The CY(carry) is a signal which is

generated when the ALU has been

carried by the execution of a command.

It is different from the C flag.

X : Used to represent a group of bits in the

content of a register or memory. For

example, the X in the LDAX instruction

denotes the lower 2 digits (I

1 and I0) of A

register.

• A bit in a register is affixed to the register symbol,

e.g. a bit (i = 0, 1, 2, 3....) of X register is

expressed as Xi and P (R) register as P (R) i.

• Increment means binary addition of 1

H and

decrement addition of F

H.

• Skipping an instruction means to ignore that

instruction and to do nothing until starting the next

instruction. In this sense, an instruction to be

skipped is treated as an NOP instruction.

Skipping 1-byte instruction requires 1-cycle, and

2-byte instruction 2-cycle. Skipping 1-byte 2-cycle

instruction requires 1-cycle.

SM5K3/SM5K4/SM5K5

MNEMONIC

MACHINE CODE

OPERATION

ROM Addressing Instructions

TR x 80 to BF

PL←x (I5-I0)

TL xy

E0 to E7,

00 to FF

PU←x (I11-I6)

PL←y (I5-I0)

TRS x C0 to DF

Push, PU←01H,

P

L←x (I4, I3, I2, I1, I0)

CALL xy

F0 to F7

00 to FF

Push, PU←x (I11-I6)

PL←y (I5-I0)

RTN 7D Pop

RTNS 7E

Pop, Skip the next step

RTNI 7F

Pop, IME←1

Data Load Instructions

LAX x 10 to 1F

A←x (I3-I0)

LBMX x 30 to 3F

BM←x (I3-I0)

LBLX x 20 to 2F

BL←x (I3-I0)

LDA x 50 to 53

A←M, BMi←BMi ⊕ x (I1, I0),

(i = 1, 0)

EXC x 54 to 57

M↔A, BMi←BMi ⊕ x (I1, I0),

(i = 1, 0)

EXCI x 58 to 5B

M↔A, BL←BL+1

BMi←BMi ⊕ x (I1, I0), (i = 1, 0)

Skip the next step, if result

of B

L = 0

EXCD x 5C to 5F

M↔A, BL←BL–1

BMi←BMi ⊕ x (I1, I0), (i = 1, 0)

Skip the next step, if result

of B

L is = FH

EXAX 64

A↔X-reg

ATX 65

X-reg←A

EXBM 66

BM↔A

EXBL 67

BL↔A

EX 68

B↔SB

Instruction Summary

Page 24

- 24 -

SM5K3/SM5K4/SM5K5

MNEMONIC

ADX x

ADD 7A

A←A+M

ADC 7B

A←A+M+C, C←CY

Skip the next step, if CY = 1

COMA 79

A←A

–

INCB 78

BL←BL+1, Skip the next

step, if result of BL = 0

DECB 7C

BL←BL–1, Skip the next

step, if result of B

L = FH

Test Instructions

TAM 6F

Skip the next step, if A = M

TC 6E Skip the next step, if C = 1

TM x 48 to 4B

Skip the next step, if Mi = 1,

(i = 3 to 0)

TABL 6B

Skip the next step, if A = B

L

TPB x 4C to 4F

Skip the next step, if P (R)

i = 1, (i = I1, I0)

TA 6C

Skip the next step, if IFA = 1

IFA←0

TB 6D

Skip the next step, if IFB = 1

IFB←0

TT

69

02

Skip the next step, if IFT = 1

IFT←0

Bit Operation Instructions

SM x 44 to 47

Mi←1 (i = 3 to 0)

RM x 40 to 43

Mi←0 (i = 3 to 0)

SC 61

C←1

RC 60

C←0

IE 63

IME←1 (Interrupt enable)

ID 62

IME←0 (Interrupt disable)

A←A+x (I3-I0)

Skip the next step, if CY = 1

00 to 0F

Arithmetic Instructions

OPERATION

MACHINE CODE

MNEMONIC

MACHINE CODE

OPERATION

I/O Instructions

INL 70

A←P1

OUTL 71

P0←A

ANP 72

Pj←Pj ∩A ( j = 0, 2, 4, 5)

ORP 73

Pj←Pj ∪A ( j = 0, 2, 4, 5)

IN 74

A←Pj ( j = 1, 2, 3, 4, 5)

X-reg, A←Rj ( j = 8, 9, A, B)

A←Rj ( j = C, E, F)

OUT 75

Pj←A ( j = 0, 2, 4, 5)

Rj←X-reg, A ( j = 8, 9, B)

RA←RB

Rj←A ( j = 3, C, E, F)

Table Search Instruction

PAT 6A

Push

PU←04H, PL←(X1, X0, A)

X-reg←ROM

H, A←ROML

Pop

Divider Operation Instruction

DR

69

03

Divider (f0-f15) clear

Special Instructions

STOP 76 Standby mode (STOP)

HALT 77 Standby mode (HALT)

NOP 00 No operation

Page 25

SM5K3/SM5K4/SM5K5

- 25 -

SYSTEM CONFIGURATION EXAMPLE

• Charger controller

OSCOUT

OSCIN

P42

SM5K3/5K5

P41

P40

VR

V

DD

P00 P01 P02 P03

RESET

GND AGND

P30

P21

P20

Battery

Switching circuit

To 10-bit A/D converter

DC supply source

+

OSCOUT

OSCIN

P42

SM5K4

P41

P40

P00 P01 P02 P03

RESET

P30

P21

P20

Battery

Switching circuit

To 10-bit A/D converter

DC supply source

VDD

VDD

VDD

+

VR

GND AGND

Page 26

SM5K3/SM5K4/SM5K5

- 26 -

± 0.1

27.2

16

15

1

30

± 0.25

± 0.2

0.25

0.46

± 0.1

TYP.

0.51

MIN.

± 0.2

± 0.2

8.6

4.4

3.85

3.25

TYP.

10.16

1.778

0°-15°

± 0.2

M0.25

30 SDIP (SDIP030-P-0400)

± 0.2

1.275

± 0.1

0.1

2.7

(1.4)

± 0.2

1.270.4

32

1

17

16

20.6

(1.4)

11.3

14.1

0.15

(12.5)

± 0.1

TYP.

± 0.2

± 0.4

± 0.05

0.15

0.1

0.15

M

32 SOP (SOP032-P-0525)

Page 27

SM5K3/SM5K4/SM5K5

- 27 -

0.8

0.38

27

19

13.5

(1.75)

(1.75)

10.0

13.5

10.0

(1.75)

(1.75)

19

10

18

36

28

0.15

(11.5)

0.85

1.45

0.1

TYP.

± 0.1

± 0.2

± 0.4

± 0.2

± 0.4

± 0.05

± 0.2

± 0.2

± 0.1

0.15

0.15

M

Package

base plane

36 QFP (QFP036-P-1010)

1.27

0.4

0.15

(10.6)

12.0

± 0.2

8.6

(1.7)

(1.7)

± 0.1

0.1

± 0.2

2.2

1.025

18.0

14

15

1

28

± 0.1

TYP.

± 0.05

± 0.2

± 0.3

0.15

0.1

0.12 M

28 SOP (SOP028-P-0450)

Page 28

SM5K3/SM5K4/SM5K5

- 28 -

1.05

0.1

0.45

6.0

7.8

0.65

0.27

0.15

12

13

1

24

± 0.2

7.6

± 0.1 TYP.

± 0.2

± 0.4

± 0.1

± 0.05

(6.6)

± 0.1

0.15

0.15

0.15

M

24 SSOP (SSOP024-P-0275)

Loading...

Loading...