Page 1

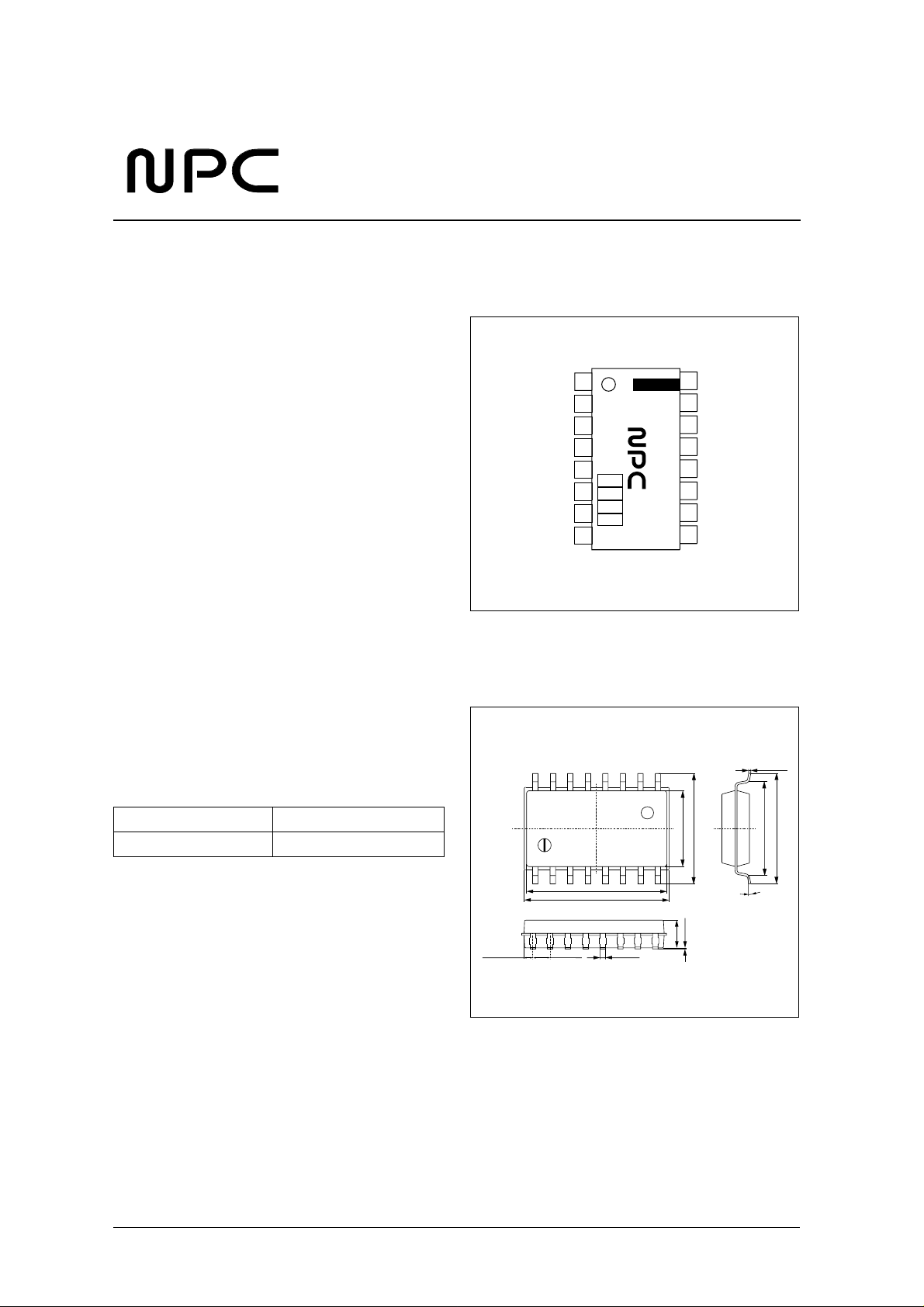

SM5852DS

NIPPON PRECISION CIRCUITS INC.

OVERVIEW

The SM5852DS is a digital signal processor IC that

performs XBS (extra bass system), LIVE (pseudosound field) and ASC (train position) processing for

use in digital audio reproduction equipment. It is

designed for use with a 44.1 kHz sampling

frequency.

FEATURES

■

2-channel processing

■

XBS/LIVE functions

■

XBS/LIVE processing bypass mode

■

ASC function ON/OFF switching

■

Input-level dependent dynamic gain characteristics

■

Serial input/output interface

2s complement, MSB first, 16-bit

■

384fs system clock

■

23 × 23-bit multiplier/30-bit high-precision

accumulator

■

TTL-compatible input/output

■

3.2 to 5.5 V operating voltage range

■

16-pin SOP

■

Molybdenum-gate CMOS

ORDERING INFOMATION

Digital Audio Processor LSI

PINOUT

LRCI

1

BCKI

2

DI

3

CLK

4

VSS

5

RSTN

6

TESTN

7

MUTEN

8

PACKAGE DIMENSIONS

16-pin SOP (Unit: mm)

SM5852DS

DB/DS

16

MOD2

15

MOD1

14

OPT

13

VDD

12

LRCO

11

BCKO

10

DOUT

9

0.17±0.05

Device Package

SM5852DS 16pin SOP

0.635±0.15

8.0±0.3

5.5±0.3

10.16±0.3

10.5 MAX

0.1±0.1

1.27±0.15

0.4±0.15

NIPPON PRECISION CIRCUITS—1

2.0±0.2

0 to 15

6.8±0.3

8.0±0.3

Page 2

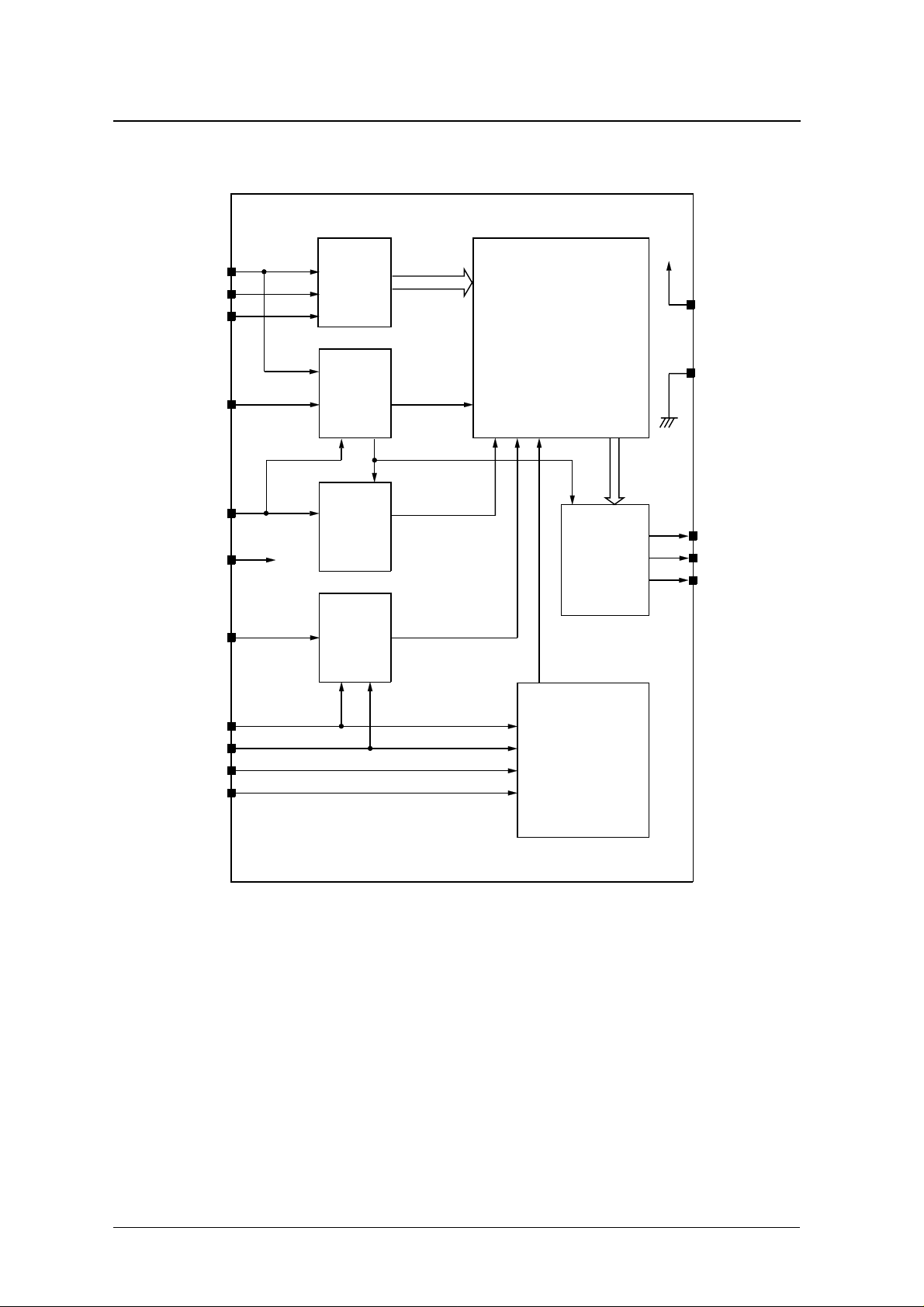

BLOCK DIAGRAM

SM5852DS

LRCI

BCKI

DI

CLK

RSTN

TESTN

MUTEN

Input data

Interface

System

Clock

Sequence

Control

Mute

Control

DSP Block

Output data

Interface

VDD

VSS

LRCO

BCKO

DOUT

DB/DS

OPT

MOD1

MOD2

Mode Control

NIPPON PRECISION CIRCUITS—2

Page 3

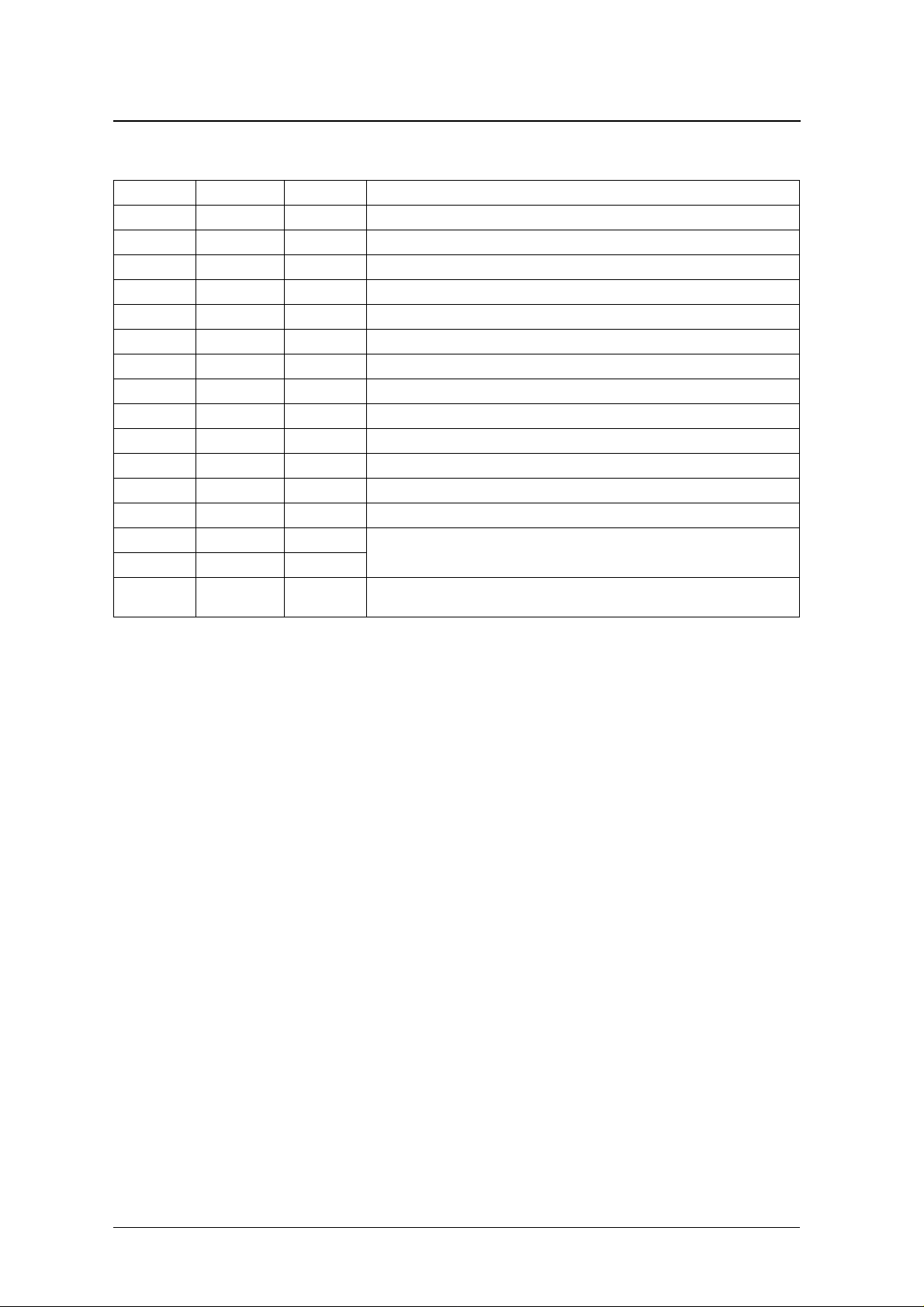

PIN DESCRIPTION

SM5852DS

Number Name I/O

1 LRCI Ip Input data sample rate (fs) clock input

2 BCKI Ip Bit clock input

3 DI Ip Serial data input

4 CLK I Clock inpu t

5 VSS – Ground

6 RSTN Ip System reset initialization. Reset when LOW.

7 TESTN Ip Test mode input. Testing when LOW.

8 MUTEN Ip Mute input. Muting when LOW.

9 DOUT O Serial data output

10 BCKO O Bit clock output

11 LRCO O Output data sample rate (fs) clock output

12 VDD – 3.2 to 5.5 V supply

13 O P T Ip ASC ON/OFF switch control. OFF when HIGH, and ON when LOW.

14 MOD1 Ip

15 MOD2 Ip

16 DB/DS Ip

1. Ip = Input pin with pull-up resistor. Accordingly, they can be left open f or HIGH-level input.

1

XBS/LIVE low-pass gain select inputs. The XBS/LIVE function is bypassed when both MOD1

and MOD2 are HIGH.

LIVE ON/OFF switch control. OFF when HIGH, and ON when LOW. The LIVE function is

bypassed when both MOD1 and MOD2 are HIGH.

Description

NIPPON PRECISION CIRCUITS—3

Page 4

−

−

−

°

°

−

° C

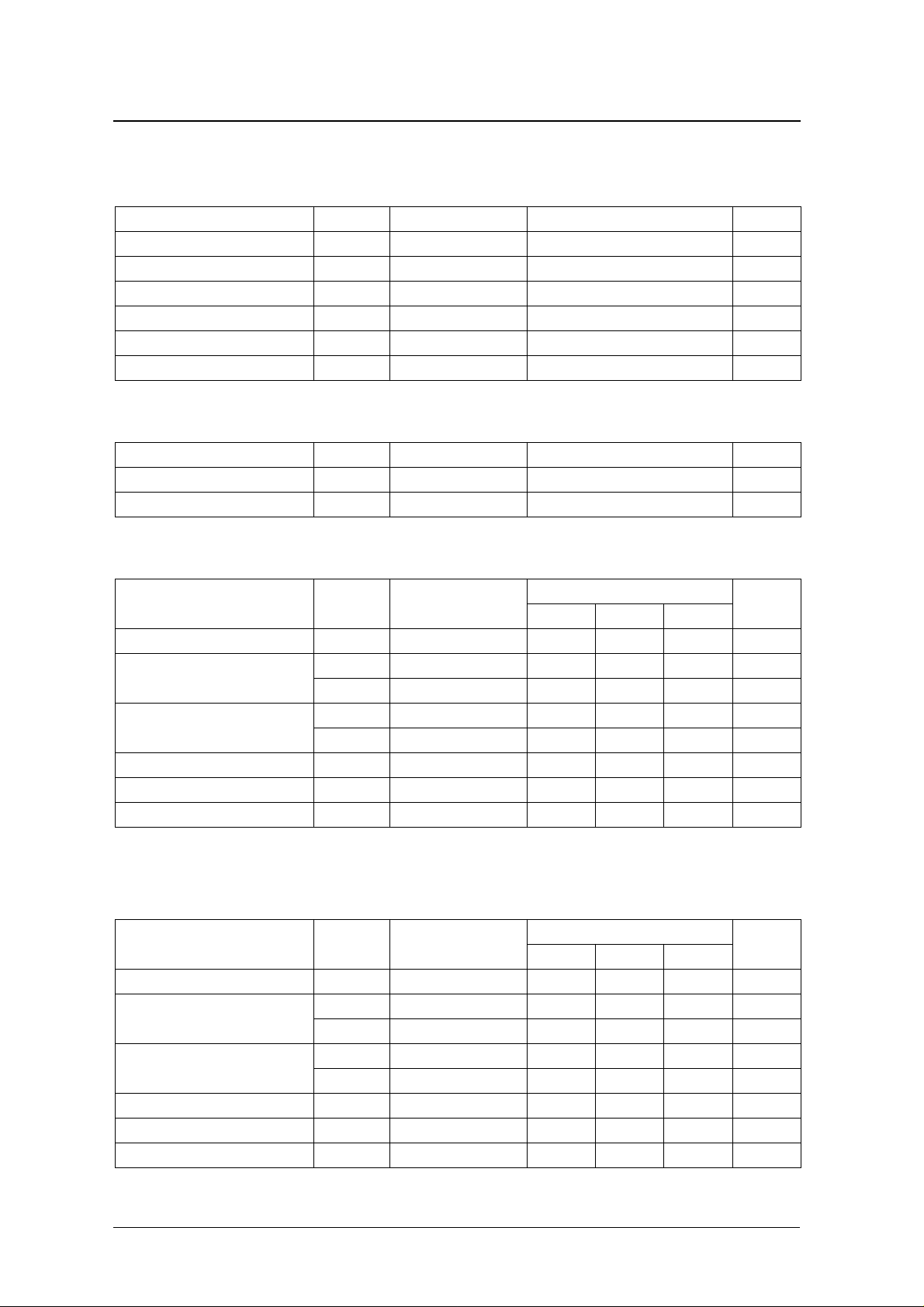

SPECIFICATIONS

Absolute Maximum Ratings

V

= 0 V

SS

Parameter Symbol Condition Rating Unit

Supply voltage V

Input voltage V

Storage temperature T

Power dissipation P

Soldering temperature T

Soldering time t

Recommended Operating Conditions

V

= 0 V

SS

Parameter Symbol Condition Rating Unit

Supply voltage V

Operating temperature T

DD

IN

stg

D

sld

sld

DD

opr

SM5852DS

0.3 to 7.0 V

V

SS

0.3 to V

+ 0.3 V

DD

55 to 125

C

250 mW

255

C

10 s

3.2 to 5.5 V

20 to 80

DC Characteristics

Standard voltage: V

Parameter Symbol Condition

Current consumption

Input voltage for all inputs

Output voltage for all outputs

Input leakage current for all inputs

CLK input leakage current I

Input current for all inputs except CLK I

1. f

= 384fs = 16.9344 MHz, no output load, input data conformance with NPC test pattern

CLK

2. LRCI, BCKI, DI,RSTN, TESTN, MUTEN, OPT, MOD1, MOD2, DB / DS

3. LRCO, BCKO, DOUT

Low voltage: V

Parameter Symbol Condition

Current consumption

Input voltage for all inputs

Output voltage for all outputs

Input leakage current for all inputs I

CLK input leakage current I

Input current for all inputs except CLK I

1. f

= 384fs = 16.9344 MHz, no output load, input data conformance with NPC test pattern

CLK

2. LRCI, BCKI, DI,RSTN, TESTN, MUTEN, OPT, MOD1, MOD2, DB / DS

3. LRCO, BCKO, DOUT

= 4.5 to 5.5 V, V

DD

1

2

3

1

= 3.2 to 4.5 V, V

DD

1

2

3

SS

I

DD

V

IH

V

IL

V

OH

V

OL

I

LH

LL

IL

= 0 V, T

SS

I

DD

V

IH

V

IL

V

OH

V

OL

LH

LL

IL

= 0 V, T

= − 20 to 80 ° C

a

V

= 5.0 V – 16 23 mA

DD

I

= − 0.4 mA 2.5 – – V

OH

I

= 1.6 mA – – 0.4 V

OL

V

= V

IN

DD

V

= 0 V – – 1.0 µA

IN

V

= 0 V – – 20 µA

IN

= − 20 to 70 ° C

a

V

= 3.4 V – 7 10 mA

DD

I

= − 0.2 mA 2.5 – – V

OH

I

= 0.8 mA – – 0.4 V

OL

V

= V

IN

DD

V

= 0 V – – 1.0 µA

IN

V

= 0 V – – 12 µA

IN

Rating

Unit

min typ max

2.4 – – V

– – 0.5 V

– – 1.0 µA

Rating

Unit

min typ max

2.4 – – V

– – 0.5 V

– – 1.0 µA

NIPPON PRECISION CIRCUITS—4

Page 5

AC Characteristics

SM5852DS

Standard voltage: V

Low voltage: V

= 4.5 to 5.5 V, V

DD

= 3.2 to 4.5 V, V

DD

CLK (384fs)

Parameter Symbol Condition

Clock pulsewidth t

Clock cycle time t

CLK

RSTN

Parameter Symbol Condition

Reset LOW-level pulsewidth t

= 0 V, T

SS

CW

CY

RST

= 0 V, T

SS

= − 20 to 80 ° C

a

= − 20 to 70 ° C

a

tcy

Rating

min typ max

24 – 500 ns

55 59 1000 ns

VIH

1.5VDD

tCW

At power-ON 1 – – µs

At all other times 50 – 1000 ns

tCW

min typ max

VIL

Rating

Unit

Unit

3.2V

VDD

tRST 1µsec

RSTN

RSTN should be set LOW at power-ON and after

reacquiring synchronization. Note that if RSTN is

LOW for longer than 1 µs, a through-current flows in

the internal dynamic circuits because the internal

clock is stopped. The through-current has no rated

value, so the reset pulse should be kept as short as

possible at all times other than at power-ON.

tRST

1.5V

NIPPON PRECISION CIRCUITS—5

Page 6

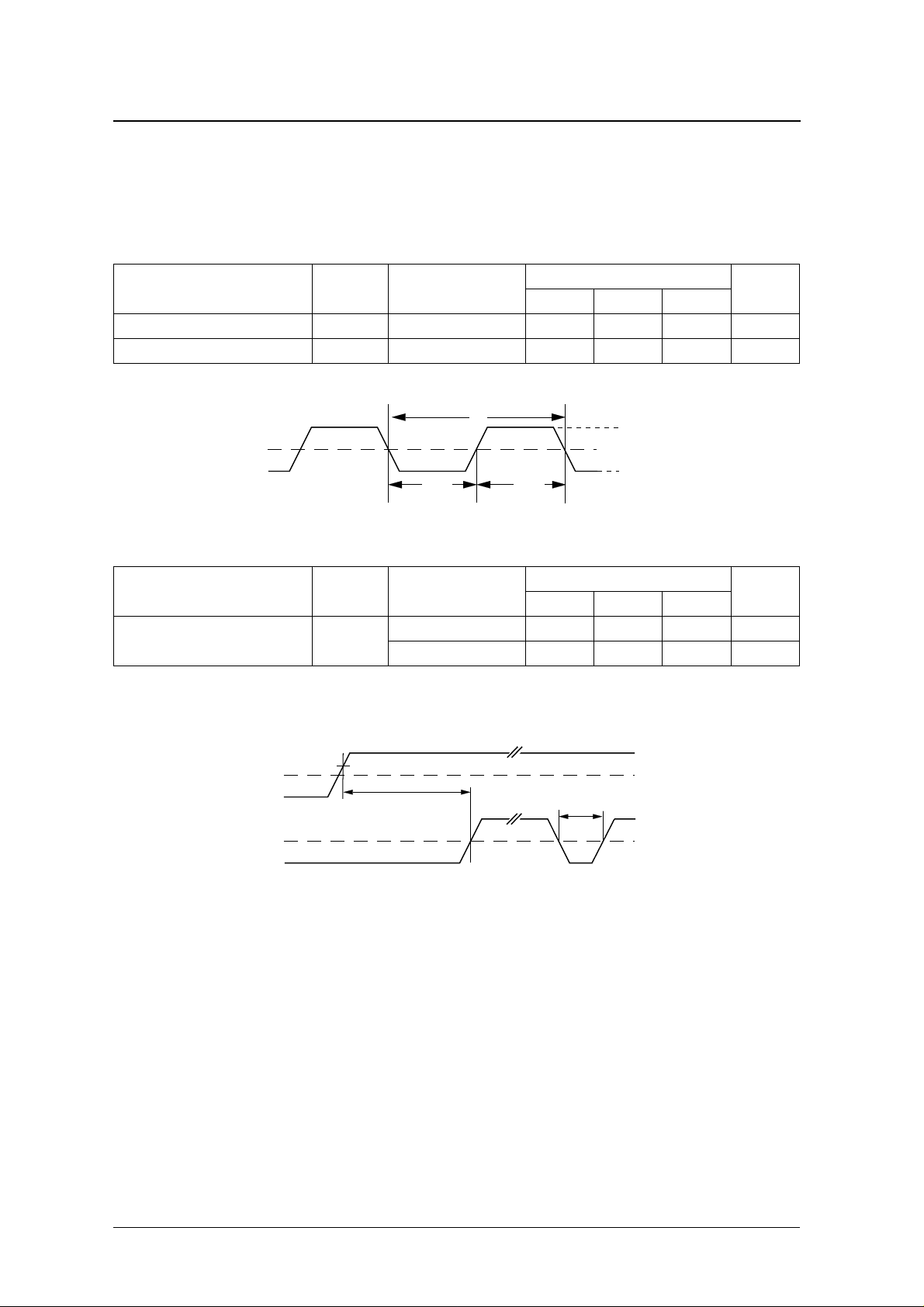

Serial input timing

SM5852DS

Parameter Symbol Condition

BCKI pulsewidth t

BCKI cycle time t

DI setup time t

DI hold time t

LRCI setup time t

LRCI hold time t

BCKI

tBCIW tBCIW

DI

BCIW

BCIY

DIS

DIH

LIS

LIH

tBCIY

Rating

Unit

min typ max

100 – – ns

200 – – ns

75 – – ns

75 – – ns

75 – – ns

75 – – ns

1.5V

1.5V

tDIS

LRCI

tLIS

DB/DS, OPT

Parameter Symbol Condition

Minimum pulsewidth t

When DB/DS or OPT change state, the input level

must be constant for a minimum of 2/fs (2 × LRCI

cycle time). Input levels of duration less than 2/fs

may be ignored.

W

tDIH

1.5V

tLIH

Rating

Unit

min typ max

2/fs – – ns

NIPPON PRECISION CIRCUITS—6

Page 7

Serial output timing

SM5852DS

−

−

Parameter Symbol Condition

BCKO pulsewidth t

BCKO cycle time t

DOUT, LRCO output delay time

BCKO

DOUT

LRCO

tDHL

BCOW

BCOY

t

DHL

t

DLH

Rating

min typ max

15 pF load 180 1/96fs – ns

15 pF load 400 1/48fs – ns

15 pF load

15 pF load

20 – 60 ns

20 – 60 ns

1.5V

tBCOW

tBCOW

tBCOY

1.5V

tDLH

Unit

NIPPON PRECISION CIRCUITS—7

Page 8

Filter Characteristics

ASC filter frequency response (theoretical)

+ 3

0

- 3

- 6

- 9

-12

-15

SM5852DS

Attenuation (dB)

-18

-21

-24

-27

-30

1K 10k 100K2K 5K 7K

Frequency

20K 50K

(Hz)

NIPPON PRECISION CIRCUITS—8

Page 9

SM5852DS

XBS Gain Characteristics

DB/DS = HIGH

L ch. = R ch. = -35dB same phase data input

20

10

0

MOD1=L,MOD2=H

-10

-20

-30

Attenuation (dB)

-40

-50

-60

10 100 1K 10K 20K20

50 200 500 2K 5K

MOD1=L,MOD2=L

DB/DS = LOW

L ch. = R ch. = -35dB same phase data input

20

MOD1=H,MOD2=L

MOD1=H,MOD2=H

Frequency

(Hz)

10

0

-10

-20

-30

Attenuation (dB)

-40

-50

-60

10 100 1K 10K 20K20 50 200 500 2K 5K

MOD1=L,MOD2=L

MOD1=H,MOD2=H

MOD1=H,MOD2=L

MOD1=L,MOD2=H

Frequency

(Hz)

NIPPON PRECISION CIRCUITS—9

Page 10

XBS frequency response (DB/DS = HIGH)

0

-10

SM5852DS

-20

-30

MOD1=L,MOD2=H

MOD1=L,MOD2=L

-40

-50

Ooutput (dB)

-60

-70

-80

-90

-90 -80 -70 -60 -50 -40 -30 -20 -10 0

Input (dB)

XBS + LIVE frequency response (DB/DS = LOW)

0

MOD1=H,MOD2=H

MOD1=H,MOD2=L

-10

-20

-30

MOD1=H,MOD2=L

MOD1=L,MOD2=L

-40

-50

Ooutput (dB)

-60

-70

MOD1=H,MOD2=H

MOD1=L,MOD2=H

-80

-90

-90 -80 -70 -60 -50 -40 -30 -20 -10 0

Input (dB)

NIPPON PRECISION CIRCUITS—10

Page 11

FUNCTIONAL DESCRIPTION

Signal Flow

SM5852DS

Lch. IN

ASC

LIVE

Rch. IN

ASC Function

The ASC (train position) function uses a 7 kHz bandlimited filter to cut-off sound leakage from

headphones. The ASC function is OFF when OPT is

HIGH, and ON when OPT is LOW.

LIVE Function

The LIVE (pseudo-sound field) function emphasizes

the extent of the sound field by adding an inverse

phase component from the opposite channel of the

input signal. When used with the XBS function, lowfrequency components of the spectrum are further

emphasized.

The LIVE function is OFF when DB/DS is HIGH,

and ON when DB/DS is LOW. Note that the function

is also OFF when both MOD1 and MOD2 are HIGH.

XBS Function

The XBS (extra bass system) function emphasizes

the low-frequency end of the spectrum by changing

the gain for low-frequency components of the input

signal. The XBS gain is set by the states of MOD1

and MOD2. Note that the gain changes when the

XBS function is used together with the LIVE

function.

DB/DS MOD1 MOD2 Maximum gain Mode

LOW LOW LOW +13 dB XBS + LIVE

LOW LOW HIGH 0 dB LIVE

LOW HIGH LOW +4 dB XBS + LIVE

LOW HIGH HIGH 0 dB Off

HIGH LOW LOW +10 dB XBS

HIGH LOW HIGH +13 dB X BS

HIGH HIGH LOW +6 dB X B S

HIGH HIGH HIGH 0 dB Off

Soft Mute

Lch. OUT

XBS

Soft MuteASC

Soft Muting

Soft muting is active when MUTEN is LOW. When

MUTEN is LOW, the attenuation changes smoothly

from 0 to −∞ dB in 1024/fs, or approximately 23.2

ms.

When MUTEN goes HIGH, soft muting is released

and the attenuation changes smoothly from −∞ to 0

dB, again taking approximately 23.2 ms.

Also, if a MUTEN transition occurs while the

attenuation is changing, the attenuation then changes

smoothly in the direction specified by the new level

of MUTEN.

DB/DS, OPT Switching Shock Noise

The soft muting function is also activated to

eliminate switching shock noise when DB/DS or

OPT change state. When DB/DS or OPT change

state, the attenuation changes to −∞ dB, the internal

circuit settings are activated and then soft muting is

released. Therefore, a maximum time of

approximately 46.4 ms is required to change the

compression mode. Of course, if the attenuation is

already −∞ dB after soft muting using MUTEN, then

no time is required to change compression mode.

Reset Initialization

RSTN should be set LOW at power-ON and after

reacquiring synchronization. Note that if RSTN is

LOW for longer than 1 µs, a through-current flows in

the LSI’s internal dynamic circuits because the

internal clock is stopped. The through-current has no

rated value, so the reset pulse should be kept as short

as possible at all times other than at power-ON.

When RSTN goes from LOW to HIGH, initialization

hold is released and the initialization routine first

resets the internal data over an interval of 4fs. During

the initialization routine, the output data is forcibly

muted so that there is no output signal.

Rch. OUT

NIPPON PRECISION CIRCUITS—11

Page 12

SM5852DS

INPUT/OUTPUT TIMING

Input Timing

LRCI

BCKI

MSB

Lch

LSB

MSB

Rch

LSB

DI

There must be a minimum of 16 BCKI clock cycles to read in a single word of data.

Data on DI is input in sync with the falling edge of BCKI in 16-bit serial, MSB first, 2s complement format.

Output Timing

LRCO

BCKO

MSB

Lch Rch

DOUT

Shaded areas represent intervals of invalid data.

LSB

MSB

LSB

NIPPON PRECISION CIRCUITS—12

Page 13

APPLICATON CIRCUIT

SM5852DS

X'tal(16.9344 MHz)

XTI XTO

SRCK

Matsushita

MN6617

SRDATA

SEL IPSEL

X1

R / L

LRCI

BCKI

DI

SM5852DS

CLK

RSTN

TESTN

MUTEN

DB/DS

MOD2

MOD1

OPT

LRCO

BCKO

DOUT

CKO

SM5840

LRCI

BCKI

DIN

Microcontroller

NIPPON PRECISION CIRCUITS—13

Page 14

SM5852DS

NIPPON PRECISION CIRCUITS INC. reserves the right to make changes to the products described in this data sheet in order to

improve the design or performance and to supply the best possible products. Nippon Precision Circuits Inc. assumes no responsibility for

the use of any circuits shown in this data sheet, conveys no license under any patent or other rights, and makes no claim that the circuits

are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision

Circuits Inc. makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification.

The products described in this data sheet are not intended to use for the apparatus which influence human lives due to the failure or

malfunction of the products. Customers are requested to comply with applicable laws and regulations in effect now and hereinafter,

including compliance with export controls on the distribution or dissemination of the products. Customers shall not export, directly or

indirectly, any products without first obtaining required licenses and approvals from appropriate government agencies.

NIPPON PRECISION CIRCUITS INC.

4-3, Fukuzumi 2 chome

Koto-ku, Tokyo 135-8430, Japan

NIPPON PRECISION CIRCUITS INC.

Telephone: 03-3642-6661

Facsimile: 03-3642-6698

NC9624AE 1997.03

NIPPON PRECISION CIRCUITS—14

Loading...

Loading...