Page 1

SM5842AP/APT

NIPPON PRECISION CIRCUITS INC.

High-Class Audio Multi-function Digital Filter

OVERVIEW

The SM5842AP/APT is a multi-function digital filter

IC, fabricated using NPC’s Molybdenum-gate

CMOS process, for digital audio reproduction equipment. It features 8-times oversampling (interpolation), independent left and right-channel digital

deemphasis, and soft muting functions. It accepts 16,

18, 20 or 24-bit input data, and outputs data in 18,

20, 22 or 24-bit format. It operates using either a

384fs or 256fs system clock at sampling frequencies

up to 48 kHz + 10% (384fs SM5842AP, 384/256fs

SM5842APT).

FEATURES

Functions

L/R 2-channel processing

■

8-times oversampling (interpolation)

■

• ≤ ±0.00002 dB passband ripple

• ≥ 117 dB stopband attenuation

Digital deemphasis

■

• 32/44.1/48 kHz sampling frequency (fs)

• 2-channel independent ON/OFF control

Soft muting

■

• 2-channel independent ON/OFF control

Input data format

■

• 2s complement, MSB first

- LR alternating, 16/18/20/24-bit serial, trailing data

- LR alternating, 24-bit serial, leading data

- LR simultaneous, 24-bit serial, leading data

Output data format

■

• 2s complement, MSB first, LR simultaneous

• 18/20/22/24-bit serial

• BCKO burst (NPC format)

Dither round-up processing

■

• ON (dither rounding)/OFF (normal rounding)

control

25-bit internal data length

■

Jitter-free function for correct operation in the

■

presence of jitter between the system clock and

LRCI clock

• ON (jitter-free mode)/OFF (sync mode) control

256fs/384fs system clock selectable

■

• 384fs

- 21.2 MHz maximum frequency (at maximum

fs = 55.2 kHz)

• 256fs

- 13 MHz maximum frequency (at maximum

fs = 50.7 kHz, SM5842AP)

- 14.2 MHz maximum frequency (at maximum

fs = 55.2 kHz, SM5842APT)

■

Crystal oscillator circuit built-in

■

TTL-compatible input/outputs

■

5.0 ± 0.25 V supply

■

Molybdenum-gate CMOS process

■

28-pin plastic DIP

Filter Configuration

■

Linear phase 3-stage FIR interpolation filter

• 169-tap 1st stage (fs to 2fs)

• 29-tap 2nd stage (2fs to 4fs)

• 17-tap 3rd stage (4fs to 8fs)

■

Deemphasis filter

- IIR filter configuration for accurate gain and

phase characteristics

■

26 × 24-bit parallel multiplier/32-bit accumulator

for high precision

■

Overflow limiter built-in

APPLICATIONS

■

CD players

■

DAT players

■

PCM systems

PINOUT

DI / INF2N

BCKI

CKSLN

INF1N

IW1N / DIL

XTI

XTO

VSS

CKO

IW2N / DIR

OW1N

OW2N

SYNCN

RSTN

1

SM5842AP/APT

14

LRCI

28

DG

BCKO

WCKO

DOL

DOR

VDD

DITHN

MUTEL

MUTER

FSEL2

FSEL1

DEMPL

DEMPR

15

NIPPON PRECISION CIRCUITS—1

Page 2

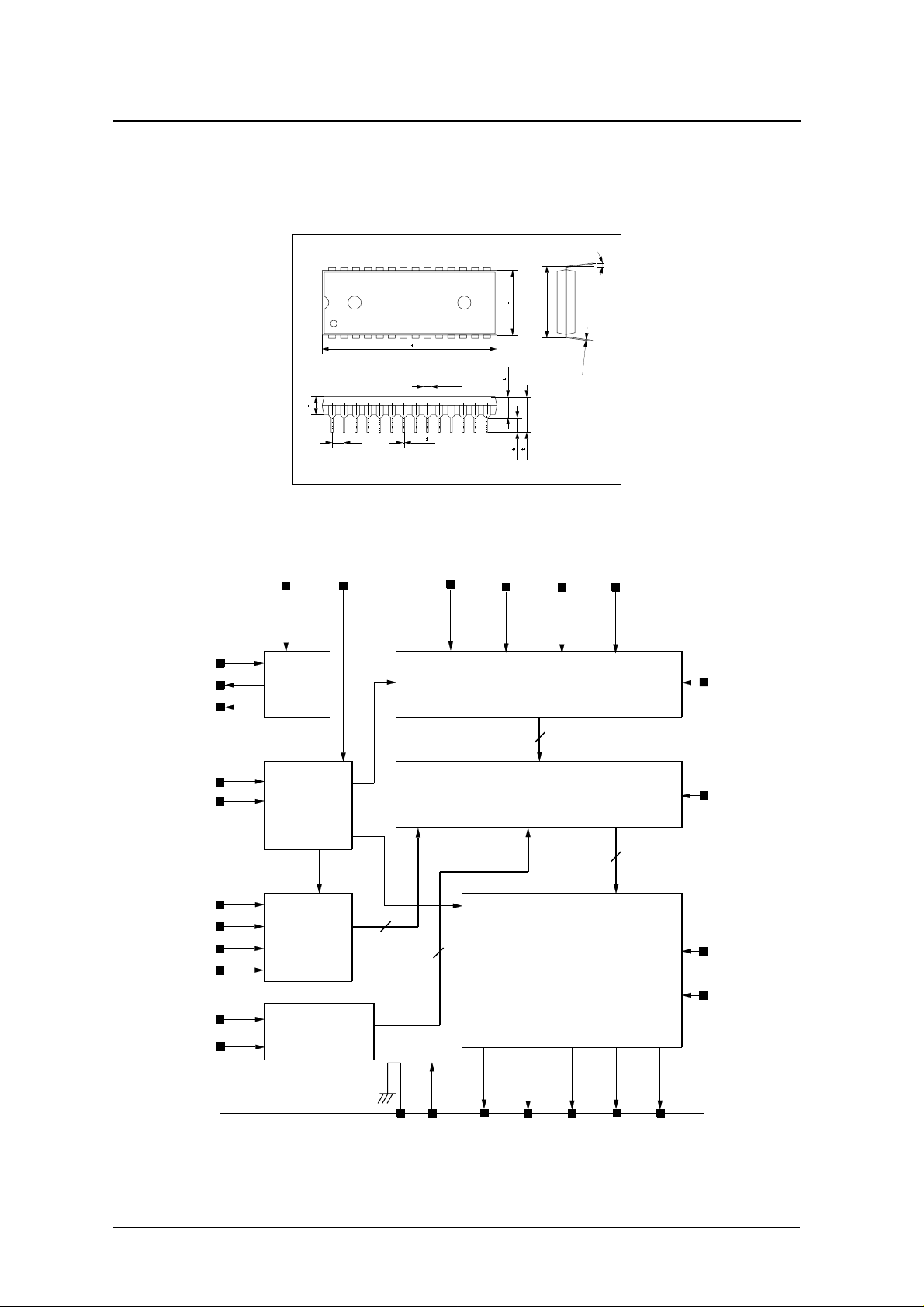

PACKAGE DIMENSIONS

Unit: mm

28-pin plastic DIP

SM5842AP/APT

13.8 0.2

0° to 15°

15.2

BLOCK DIAGRAM

XTI

XTO

CKO

RSTN

SYNCN

3.8 0.1

CKSLN LRCI

System

Clock

Timing

Controller

37.3 0.3

+

0.3

1.5

0.05

−

2.54

0.45 0.1

DI

/ INF2N

4.5 0.3

BCKI

3.2 0.2

3.2 0.2

7.7 0.5

Input Data Interface

Filter and Attenuation Arithmetic block

IW1N

/ DIL

0.10

0.05

+

−

0.25

IW2N

/ DIR

INF1N

DITHN

DEMPL

DEMPR

FSEL1

FSEL2

MUTEL

MUTER

Deemphasis

Control

Mute Control

BCKO WCKO DGDORDOL

V

DDVSS

OW1N

Output Data Interface

OW2N

NIPPON PRECISION CIRCUITS—2

Page 3

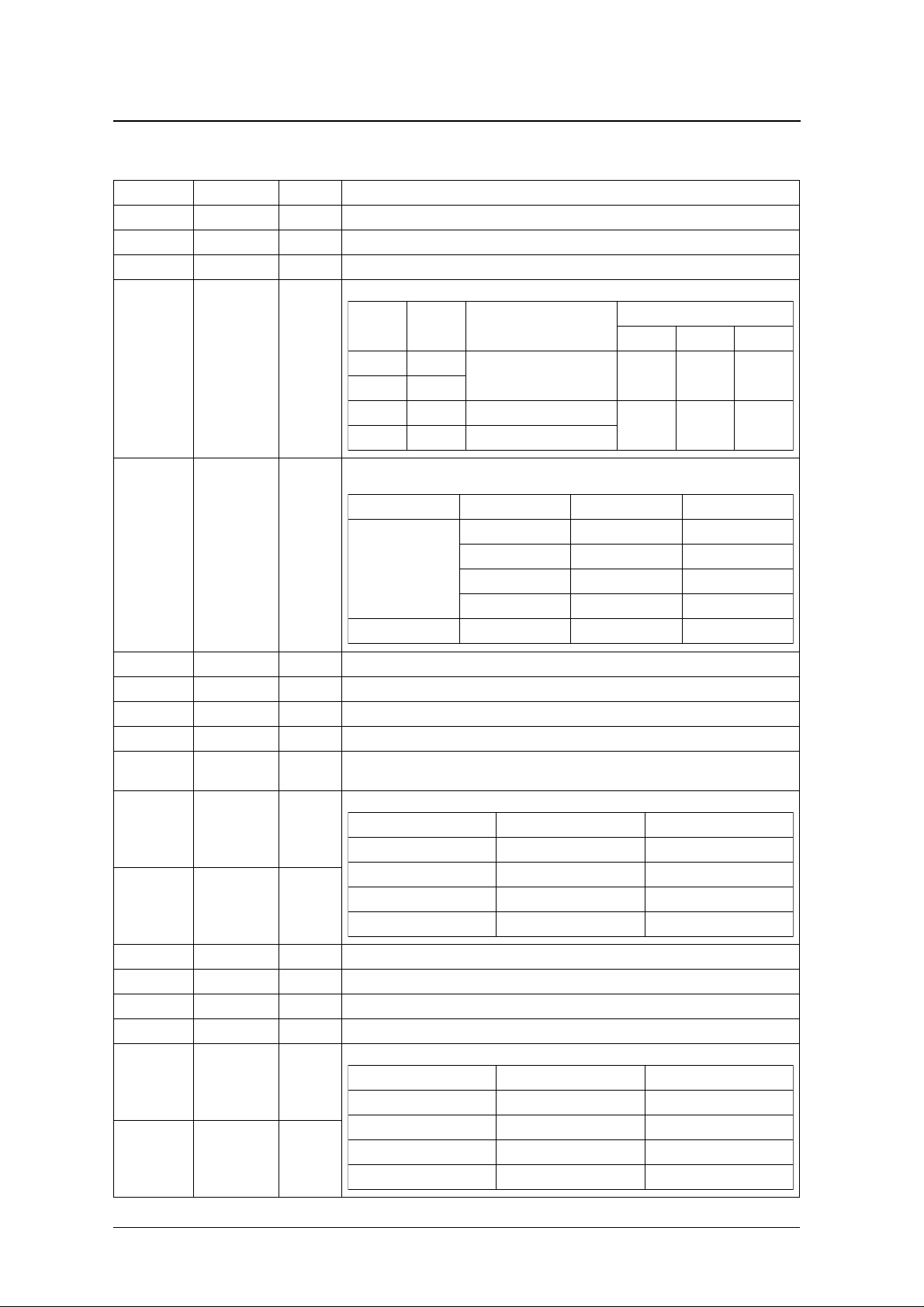

PIN DESCRIPTION

SM5842AP/APT

Number Name I/O

1 DI/INF2N Ip Data input when INF1N is LOW, and input format select pin 2 when INF1N is HIGH.

2 BCKI Ip Input bit clock

3 CKSLN Ip Oscillator and system clock select input. 384fs when HIGH, and 256fs when LOW.

4 INF1N Ip

5 IW1N/DIL Ip

1

Input format select pin 1. INF1N and INF2N select the pin functions below.

INF1N DI/INF2N Input format

LOW LOW

LR alternating, trailing data DI IW1N IW2N

LOW HIGH

HIGH LOW LR alternating, leading data

HIGH HIGH LR simultaneous, leading data

Input bit length select pin 1 when INF1N is LOW, and left-channel data input when INF1N is HIGH.

IW1N and IW2N select the input data length.

INF1N IW2N/DIL IW1N/DIR Input bit length

LOW

HIGH ××24 bits

Description

Pin function selection

DI/INF2N IW1N/DIL IW2N/DIR

INF2N DIL DIR

LOW LOW 24 bits

LOW HIGH 20 bits

HIGH LOW 18 bits

HIGH HIGH 16 bits

6 XTI I Oscillator input connection

7 XTO O Oscillator output connection

8 VSS – Ground

9 CKO O Oscillator output clock. Same frequency as XTI.

10 IW2N/DIR Ip

11 OW1N Ip

12 OW2N Ip

13 SYNCN Ip Sync mode select pin. Normal sync mode when LOW, and jitter-free mode when HIGH.

14 RSTN Ip System reset. Reset operation when LOW, and normal operation when HIGH.

15 DEMPR Ip Right-channel deemphasis control signal. OFF when LOW, and ON when HIGH.

16 DEMPR Ip Left-channel deemphasis control signal. OFF when LOW, and ON when HIGH.

17 FSEL1 Ip

18 FSEL2 Ip

Input bit length select pin 2 when INF2N is LOW , and right-channel data input when INF2N is HIGH.

IW1N and IW2N select the input data length as shown in the table for pin 5.

Output length select bits.

OW2N OW1N Output bit length

LOW LOW 24 bits

LOW HIGH 22 bits

HIGH LOW 20 bits

HIGH HIGH 18 bits

Deemphasis filter select inputs

FSEL1 FSEL2 Sampling frequency (fs)

LOW LOW 44.1 kHz

LOW HIGH 48 kHz

HIGH LOW Invalid setting

HIGH HIGH 32 kHz

NIPPON PRECISION CIRCUITS—3

Page 4

SM5842AP/APT

Number Name I/O

19 MUTER Ip Right-channel mute signal. Muting when HIGH, and normal output when LOW.

20 MUTEL Ip Left-channel mute signal. Muting when HIGH, and normal output when LOW.

21 DITHN Ip Dither processing control. ON when LOW, and OFF when HIGH.

22 VDD – 5 V supply

23 DOR O Right-channel data output

24 DOL O Left-channel data output

25 WCKO O Output word clock

26 BCKO O Output bit clock

27 DG O Deglitched output

28 LRCI Ip Input data sample rate (fs) clock

1. I = input, Ip = Input with pull-up resistor, O = output

1

Description

NIPPON PRECISION CIRCUITS—4

Page 5

SM5842AP/APT

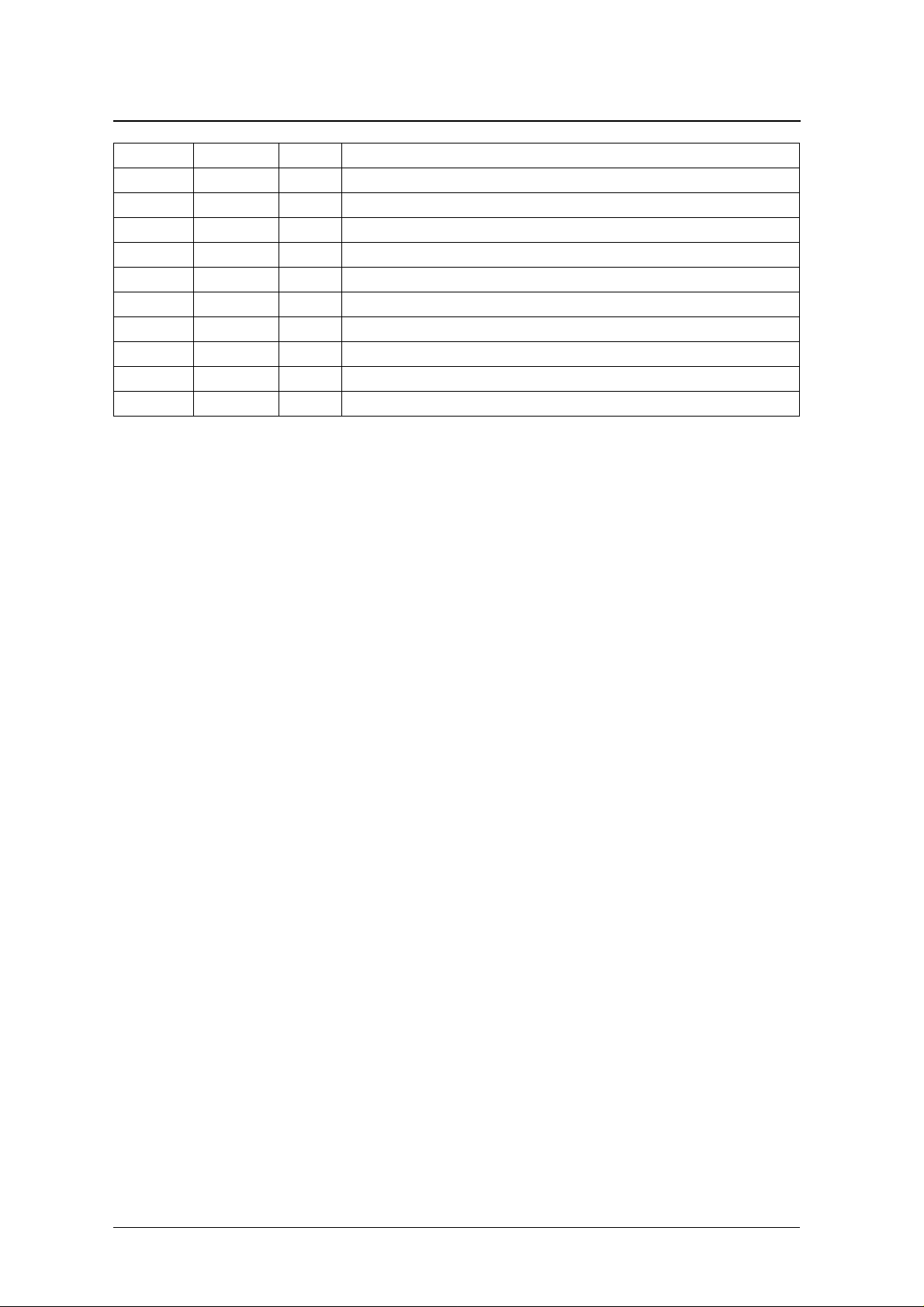

SPECIFICATIONS

Absolute Maximum Ratings

V

= 0 V

SS

Parameter Symbol Rating Unit

Supply voltage range V

Input voltage range V

Storage temperature range T

Power dissipation P

Soldering temperature T

Soldering time t

Recommended Operating Conditions

−

−

−

DD

IN

stg

D

sld

sld

0.3 to 7.0 V

0.3 to V

+ 0.3 V

DD

40 to 125

550 mW

255

10 s

° C

° C

V

= 0 V

SS

Parameter Symbol Condition Rating Unit

Supply voltage range V

Operating temperature range T

DD

SM5842AP

opr

SM5842APT

4.75 to 5.25 V

− 20 to 80

° C

− 20 to 70

DC Electrical Characteristics

V

= 4.75 to 5.25 V, V

DD

Parameter Symbol Condition

Current consumption I

XTI HIGH-level input voltage V

XTI LOW-level input voltage V

HIGH-level input voltage

LOW-level input voltage

2

2

HIGH-level output voltage

LOW-level output voltage

XTO HIGH-level output voltage V

XTO LOW-level output voltage V

XTI HIGH-level input current I

XTI LOW-level input current I

LOW-level input current

Input leakage current

1. f

= 256fs = 14.2 MHz (CKSLN = LOW), no output load

SYS

2. Pins DI/INF2N, BCKI, CKSLN, INF1N, IW1N/DIL, IW2N/DIR, OW1N, OW2N, SYNCN, RSTN, DEMPR, DEMPL, FSEL1, FSEL2, MUTER, MUTEL,

2

2

DITHN, LRCI

3. Pins CKO, DOL, DOR, BCKO, WCKO, DG

= 0 V, T

SS

= − 20 to 80 ° C

a

Rating

Unit

min typ max

DD

IH1

IL1

V

IH2

V

IL2

3

3

V

OH1

V

OL1

OH2

OL2

LH

LL1

I

LL2

I

IH

V

I

OH

I

OL

I

OH

I

OL

V

V

V

V

1

= 5.0 V

DD

= − 0.4 mA 2.5 – – V

= 1.6 mA – – 0.4 V

= − 1.0 mA V

= 1.0 mA – – 0.4 V

= V

IN

DD

= 0 V – 10 20 µA

IN

= 0 V – 10 20 µA

IN

= V

IN

DD

–6080mA

0.7V

DD

– – 0.3V

––V

DD

V

2.4 – – V

– – 0.5 V

− 0.5 – – V

DD

–1020µA

– – 1.0 µA

NIPPON PRECISION CIRCUITS—5

Page 6

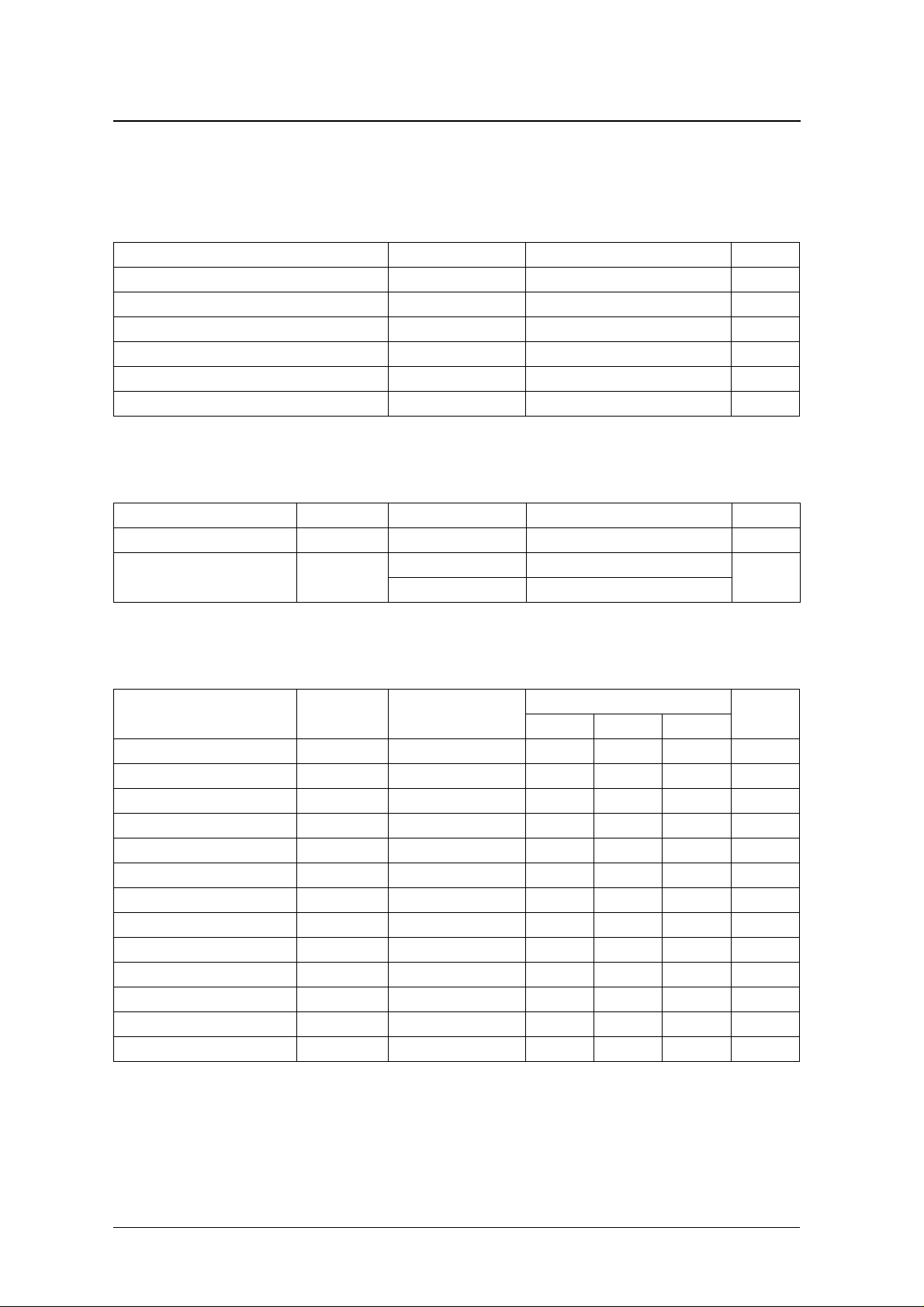

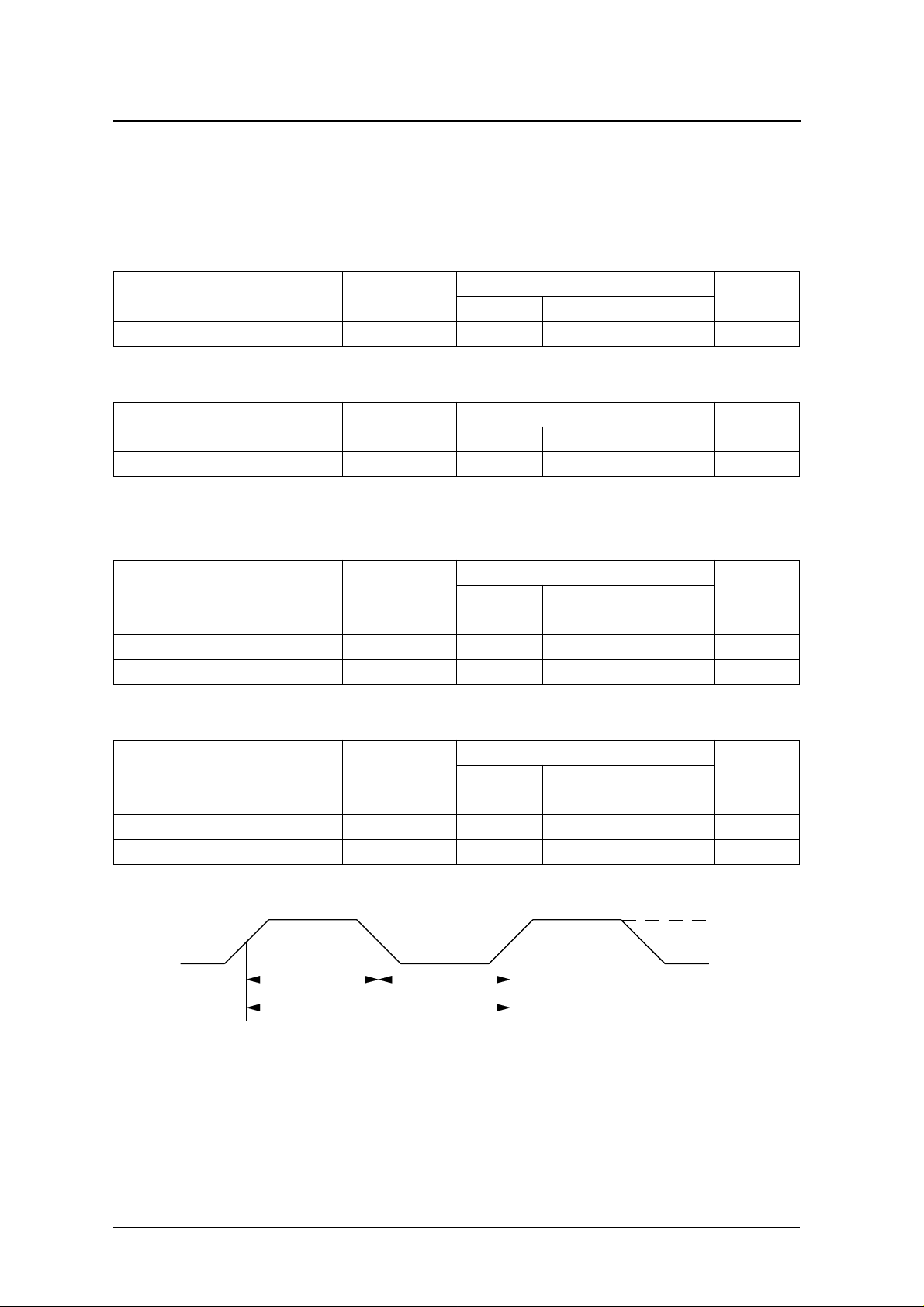

AC Electrical Characteristics

Input Clock (XTI: SM5842AP)

Crystal oscillator

SM5842AP/APT

fs = 384fs (CKSLN = HIGH): V

Parameter Symbol

Oscillator frequency f

fs = 256fs (CKSLN = LOW): V

Parameter Symbol

Oscillator frequency f

= 4.75 to 5.25 V, V

DD

= 4.75 to 5.25 V, V

DD

External clock input

fs = 384fs (CKSLN = HIGH): V

Parameter Symbol

Clock HIGH-level pulsewidth t

Clock LOW-level pulsewidth t

Clock pulse cycle time t

= 4.75 to 5.25 V, V

DD

OSC

OSC

CWH

CWL

XI

= 0 V, T

SS

= 0 V, T

SS

= 0 V, T

SS

= − 20 to 80 ° C

a

Rating

min typ max

2.0 – 21.2 MHz

= − 20 to 80 ° C

a

Rating

min typ max

1.0 – 13.0 MHz

= − 20 to 80 ° C

a

Rating

min typ max

20 – 250 ns

20 – 250 ns

47 – 500 ns

Unit

Unit

Unit

fs = 256fs (CKSLN = LOW): V

Parameter Symbol

Clock HIGH-level pulsewidth t

Clock LOW-level pulsewidth t

Clock pulse cycle time t

= 4.75 to 5.25 V, V

DD

XTI

tCWH tCWL

tXI

CWH

CWL

XI

= 0 V, T

SS

= − 20 to 80 ° C

a

Rating

min typ max

35 – 500 ns

35 – 500 ns

76 – 1000 ns

VIH1

0.5V

VIL1

Unit

DD

NIPPON PRECISION CIRCUITS—6

Page 7

SM5842AP/APT

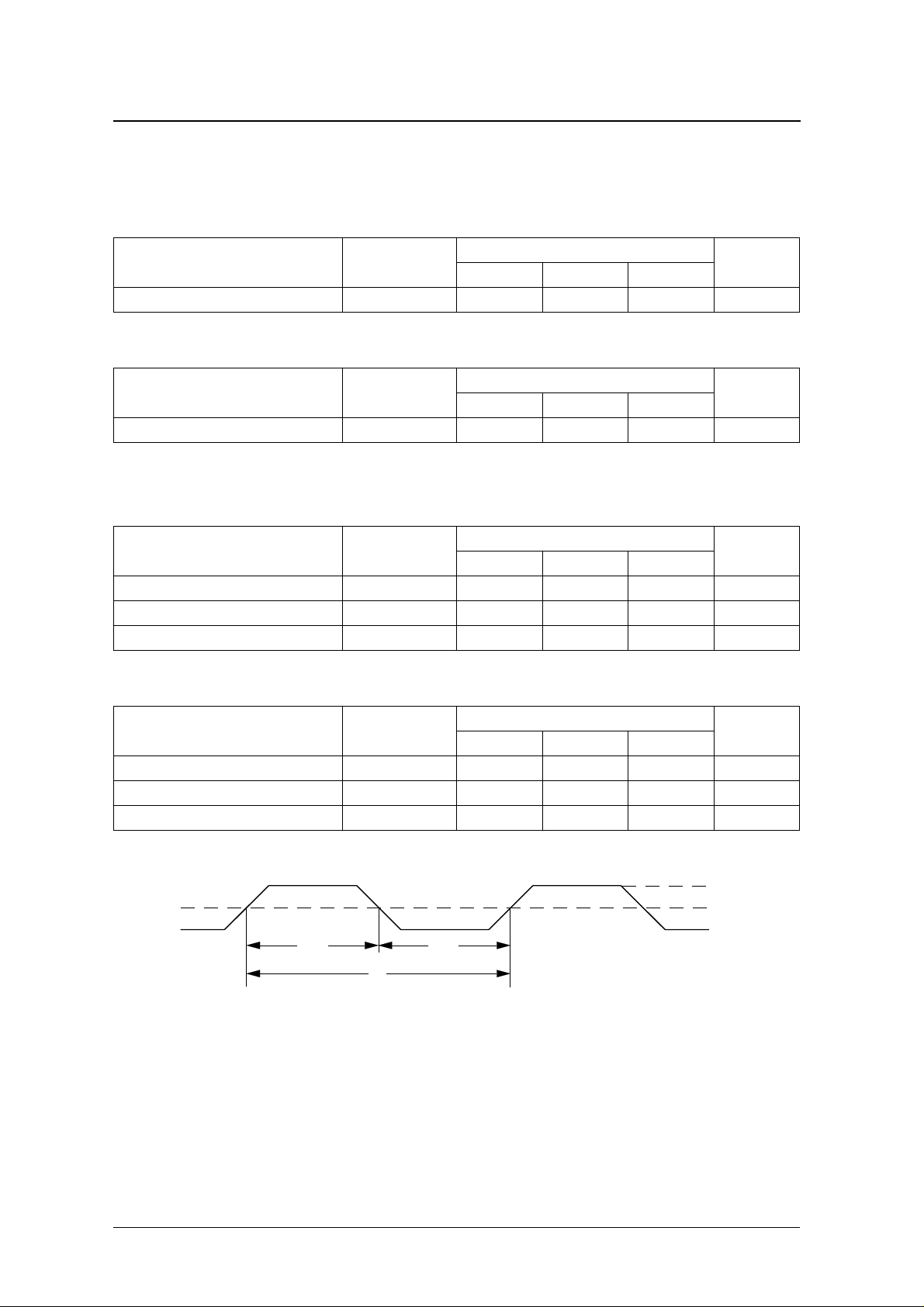

Input Clock (XTI: SM5842APT)

Crystal oscillator

fs = 384fs (CKSLN = HIGH): VDD = 4.75 to 5.25 V, VSS = 0 V, Ta = −20 to 70 °C

Parameter Symbol

Oscillator frequency f

OSC

min typ max

2.0 – 21.2 MHz

Rating

fs = 256fs (CKSLN = LOW): VDD = 4.75 to 5.25 V, VSS = 0 V, Ta = −20 to 70 °C

Parameter Symbol

Oscillator frequency f

External clock input

OSC

min typ max

1.0 – 14.2 MHz

Rating

fs = 384fs (CKSLN = HIGH): VDD = 4.75 to 5.25 V, VSS = 0 V, Ta = −20 to 70 °C

Parameter Symbol

Clock HIGH-level pulsewidth t

Clock LOW-level pulsewidth t

Clock pulse cycle time t

CWH

CWL

XI

min typ max

20 – 250 ns

20 – 250 ns

47 – 500 ns

Rating

fs = 256fs (CKSLN = LOW): VDD = 4.75 to 5.25 V, VSS = 0 V, Ta = −20 to 70 °C

Unit

Unit

Unit

Parameter Symbol

Clock HIGH-level pulsewidth t

Clock LOW-level pulsewidth t

Clock pulse cycle time t

XTI

tCWH tCWL

tXI

CWH

CWL

XI

Rating

min typ max

30 – 500 ns

30 – 500 ns

70 – 1000 ns

VIH1

0.5V

DD

VIL1

Unit

NIPPON PRECISION CIRCUITS—7

Page 8

SM5842AP/APT

Serial input timing (BCKI, DI, DIL, DIR, LRCI)

SM5842AP: VDD = 4.75 to 5.25 V, VSS = 0 V, Ta = −20 to 80 °C

SM5842APT: VDD = 4.75 to 5.25 V, VSS = 0 V, Ta = −20 to 70 °C

Parameter Symbol

BCKI HIGH-level pulsewidth t

BCKI LOW-level pulsewidth t

BCKI pulse cycle t

DIN setup time t

DIN hold time t

Last BCKI rising edge to LRCI edge t

LRCI edge to first BCKI rising edge t

BCKI

tDS

DI

DIL

DIR

BCWH

BCWL

BCY

DS

DH

BL

LB

Rating

min typ max

50 – – ns

50 – – ns

100 – – ns

50 – – ns

50 – – ns

50 – – ns

50 – – ns

tBCY

tBCWH tBCWL

1.5V

tDH

1.5V

Unit

tBL

LRCI

Reset timing (RSTN)

SM5842AP: VDD = 4.75 to 5.25 V, VSS = 0 V, Ta = −20 to 80 °C

SM5842APT: VDD = 4.75 to 5.25 V, VSS = 0 V, Ta = −20 to 70 °C

Parameter Symbol Condition

RST LOW-level reset pulsewidth t

RST

At power-ON 1 – – µs

At all other times 50 – – ns

tLB

1.5V

Rating

Unit

min typ max

NIPPON PRECISION CIRCUITS—8

Page 9

SM5842AP/APT

Output timing

SM5842AP: VDD = 4.75 to 5.25 V, VSS = 0 V, Ta = −20 to 80 °C, CL = 15 pF

SM5842APT: VDD = 4.75 to 5.25 V, VSS = 0 V, Ta = −20 to 70 °C, CL = 15 pF

Parameter Symbol Condition

XTI to XTO delay t

XTI to CKO delay t

XTI to BCKO delay (CKSLN = HIGH)

XTI to BCKO delay (CKSLN = LOW)

BCKO to DOL, DOR, WCKO delay

CKO to DOL, DOR, WCKO, DG delay

XTO to DOL, DOR, WCKO, DG delay

XTI

(CKSLN = H)

XTO

CKO

t

t

t

t

t

t

t

t

t

t

sbH

sbL

sbH

sbL

bdH

bdL

cdH

cdL

xdH

xdL

XTI fall to XTO rise 3 – 15 ns

XTI fall to CKO fall 10 – 35 ns

XTI fall to BCKO rise 20 – 65

XTI fall to BCKO fall 20 – 65

XTI fall to BCKO rise 20 – 65

XTI fall to BCKO fall 20 – 65

BCKO fall to output rise −5–10

BCKO fall to output fall −5–10

CKO fall to output rise 12 – 45

CKO fall to output fall 12 – 45

XTO rise to output rise 15 – 50

XTO rise to output fall 15 – 50

Tsys Tsys

Rating

min typ max

V

DD / 2

Unit

ns

ns

ns

ns

ns

XTI

(CKSLN = L)

CXO

(CKSLN = H)

CKO

(CKSLN = L)

BCKO

DOL

DOR

DG

WCKO

Tsys

tCKO

tsbLtsbH

tcdL

tbdL

tcdH

tbdH

V

DD / 2

1.5V

1.5V

1.5V

1.5V

1.5V

NIPPON PRECISION CIRCUITS—9

Page 10

SM5842AP/APT

Filter Characteristics

8-times interpolation filter

Parameter Rating

Passband 0 to 0.4535fs

Stopband 0.5465fs to 7.4535fs

Passband ripple ≤ ±0.00002 dB

Stopband attenuation ≥ 117 dB

Group delay Fixed

8fs filter response with deemphasis OFF

0

20

40

(dB)

60

80

Attenuation

100

120

140

0.0 1.0 2.0 4.0 5.0 6.0 7.0 8.0

3.0

8fs filter passband response with deemphasis OFF

−0.00008

−0.00004

(dB)

0.00000

0.00004

Attenuation

0.00008

0.000 0.125 0.250 0.375 0.500

Frequency (×fs)

8fs filter transition response with deemphasis OFF

0

20

40

60

Frequency (×fs)

80

100

Attenuation (dB)

120

140

0.440 0.465 0.490 0.515 0.540 0.565 0.590 0.615 0.640

Frequency

(×Fs)

NIPPON PRECISION CIRCUITS—10

Page 11

Deemphasis filter

SM5842AP/APT

Parameter

Sampling frequency (fs)

32 kHz 44.1 kHz 48 kHz

Passband bandwidth (kHz) 0 to 14.5 0 to 20.0 0 to 21.7

Attenuation ≤ ±0.001 dB

Deviation from ideal characteristic

Phase, θ 0 to 1.5°

Passband response with deemphasis ON (logarithmic frequency axis)

44.1kHz

48kHz

[Hz]

0

-20

-40

-60

Phase (degrees)

0

2

4

6

8

Attenuation (dB)

10

10 100 1k 10k 20 50 200 500 2k 5k 20k

32kHz

Phase

32kHz

44.1kHz

48kHz

Frequency (Hz)

NIPPON PRECISION CIRCUITS—11

Page 12

SM5842AP/APT

FUNCTIONAL DESCRIPTION

The basic arithmetic block is shown in figure 1, and

the function of each block is described in the following sections.

Input

2-times interpolator

1st FIR, 169-tap

2-times interpolator

2nd FIR, 29-tap

4fs

Deemphasis OFF

fs

2fs

Deemphasis IIR filter

Deemphasis ON

4fs

Soft mute

4fs

2-times interpolator

3rd FIR, 17-tap

8fs

Output

Figure 1. Arithmetic block diagram

8-times Oversampling (Interpolation)

The interpolation arithmetic block is comprised of 3

cascaded, 2-times FIR interpolation filters, as shown

in figure 1.

The input signal is sampled at rate fs, and then 8times oversampling data is output. Sampling noise in

the 0.5465fs to 7.4535fs stopband is removed by the

interpolation filter.

Digital Deemphasis

The digital deemphasis filter has the same construction as analog filters. It is implemented as an IIR filter to faithfully reproduce the gain and phase

characteristics of standard analog deemphasis filters.

The three sets of filter coefficients for the three fs =

32.0/44.1/48.0 kHz sampling frequencies are

selected by FSEL1 and FSEL2 when the sampling

frequency is specified, as shown in table 1. Independent deemphasis for the left and right channel is controlled independently by DEMPL and DEMPR,

respectively. Digital deemphasis is ON when

DEMPL/DEMPR is HIGH, and OFF when

DEMPL/DEMPR is LOW.

Table 1. Sampling frequency select

FSEL1 FSEL2 Sampling frequency (fs)

LOW LOW 44.1 kHz

LOW HIGH 48 kHz

HIGH LOW Invalid setting

HIGH HIGH 32 kHz

NIPPON PRECISION CIRCUITS—12

Page 13

SM5842AP/APT

Soft Muting

Muting of the left and right channel is controlled

independently by MUTEL and MUTER, respectively. Muting is ON when MUTEL/MUTER is

HIGH, muting is OFF when MUTEL/MUTER is

LOW.

When MUTEL/MUTER goes HIGH, the attenuation

changes smoothly from 0 to −∞ dB in 512/fs, or

System Clock (XTI, XTO, CKO, CKSLN)

Two system clock frequencies, 384fs and 256fs, can

be used. An external clock source can be input on

XTI, or a crystal oscillator can be constructed by

connecting a crystal between XTI and XTO. The

system clock is also buffered and then output on

CKO. The system clock frequency selection and the

internal clock frequency are shown in table 2.

CKSLN

approximately 11.6 ms when fs = 44.1 kHz. When

MUTEL/MUTER goes LOW, muting is released and

the attenuation changes smoothly from −∞ to 0 dB,

again taking approximately 11.6 ms.

When RSTN goes LOW, the DOL and DOR outputs

go LOW, immediately muting the output signal.

Muting is released and timing is synchronized when

RSTN goes HIGH.

Table 2. System clock frequency select

Parameter

XTI input clock frequency (fXI = 1/tXI) 384fs 256fs

CKO clock frequency 384fs 256fs

Internal clock frequency (t

To timing controller

)2 × t

SYS

CKSLN

HIGH LOW

XI

t

XI

XTI

XTO

CKO

1 / 2

Internal system clock

(192fs or 256fs)

Figure 2. Clock generator circuit

NIPPON PRECISION CIRCUITS—13

Page 14

SM5842AP/APT

Audio Data Input (INF1N, INF2N, IW1N, IW2N, DI, DIL, DIR, BCKI, LRCI)

The input data format and several input pin functions

are selected by the state of INF1N and INF2N as

shown in table 3.

Table 3. Pin function select

INF1N DI/INF2N Input format

LOW LOW

LOW HIGH

HIGH LOW LR alternating, leading data

HIGH HIGH LR simultaneous2, leading data

1. Alternating left-channel and right-channel data input on a single input DI.

2. Simultaneous left-channel and right-channel data input on two inputs, DIL and DIR, respectively.

The input data word length is selected by the state of

IW1N and IW2N when INF1N is LOW. 24-bit is

LR alternating1, trailing data DI IW1N IW2N

resynchronized and all functions continue to operate

normally.

selected when INF1N is HIGH.

Sync mode (SYNCN = LOW)

Table 4. Input word length

INF1N IW2N/DIL IW1N/DIR Input word length

LOW LOW 24 bits

LOW HIGH 22 bits

LOW

HIGH LOW 18 bits

HIGH HIGH 16 bits

HIGH ×× 24 bits

When SYNCN is LOW, the timing error value is ±1

× (system clock period), which is a much smaller

timing error tolerance than in jitter-free mode. In this

mode, the internal timing is guaranteed to follow the

LRCI clock timing within this tolerance, making this

mode useful for systems constructed from a multiple

number of SM5842AP/APT devices.

Note that resynchronization affects the internal operation and can generate a momentary click noise output.

Pin function selection

DI/INF2N IW1N/DIL IW2N/DIR

INF2N DIL DIR

Jitter-free Function (SYNCN)

The arithmetic circuit and output control timing is

derived from the system clock, and is therefore independent of the input LRCI and BCKI clocks.

Accordingly, any jitter in the data input clock (LRCI

and BCKI) does not cause jitter in the output.

Generally, the internal timing is synchronized to the

LRCI input timing after a system reset release, when

RSTN goes from LOW to HIGH, on the first LRCI

clock start edge. If the input timing and LRCI start

edge timing subsequently drift, the input timing is

automatically resynchronized when the timing error

exceeds a certain value. There are 2 timing error values at which resynchronization occurs, selected by

the state of SYNCN.

Jitter-free mode (SYNCN = HIGH)

When SYNCN is HIGH, the timing error value is

±3/8 × (LRCI clock period). When the difference

between the input timing and LRCI start edge position do not exceed this value, internal timing is not

NIPPON PRECISION CIRCUITS—14

Page 15

SM5842AP/APT

Audio Data Output (DOL, DOR, BCKO,

WCKO, OW20N)

The output data is in serial, simultaneous left and

right-channel, 2s complement, MSB first, BCKO

burst (NPC format) format. The output data word

length is selected by the state of OW1N and OW2N

as shown in table 5.

Table 5. Output word length select

OW1N OW2N Output word length

LOW LOW 24 bits

LOW HIGH 22 bits

HIGH LOW 20 bits

HIGH HIGH 18 bits

8fs serial data is output in sync with the falling edge

of the internal system clock and BCKO clock. The

output timing is determined by CKSLN and the output word length. When CKSLN is LOW, the output

timing is the same for different output word lengths.

Only the number of BCKO bit clock pulses word

changes depending on the output word length

selected. When CKSLN is HIGH, however, the output timing for 24-bit output mode starts 1 bit earlier

than for 18/20/22-bit output mode.

Table 6. Output timing

Parameter Symbol CKSLN = HIGH CKSLN = LOW

Bit clock rate t

Data word length t

B

DW

1/192fs 1/256fs

24t

SYS

32t

SYS

NIPPON PRECISION CIRCUITS—15

Page 16

System Reset (RSTN)

SM5842AP/APT

Under normal operating conditions, the

SM5842AP/APT does not need to be reset. However,

it can be reset when you want to synchronize the

LRCI clock and internal operation timing in jitterfree mode.

The system is reset by applying a LOW-level pulse

on RSTN.

The arithmetic and output timing counters are reset

on the first LRCI start edge after reset is released, as

long as the XTI clock has already stabilized. The

LRCI start edge is determined by the state of INF1N

and INF2N. When INF1N is LOW or when both

INF1N and INF2N are HIGH, the start edge is the

RSTN

1 2

LRCI

Internal reset

WCKO

rising edge. When INF1N is HIGH and INF2N is

LOW, the start edge is the falling edge.

When RSTN is LOW, the DOL and DOR outputs are

LOW, muting the output signal to an attenuation

level of −∞.

The power-ON reset pulse can be applied by a

microcontroller or, for systems where XTI and LRCI

are stable at power-ON, by connecting a capacitor of

about 300 pF between RSTN and VSS. For systems

that do not use a microcontroller, the capacitor must

be chosen such that the XTI and LRCI clocks fully

stabilize before RSTN goes from LOW to HIGH.

DOL

DOR

Figure 3. System reset timing and output muting

NIPPON PRECISION CIRCUITS—16

Page 17

SM5842AP/APT

TIMING DIAGRAMS

Input Timing Examples (DIN, BCKI, LRCI)

Lch DATA Rch DATA

(MSB)

DI

BCKI

LRCI

INF1N = LOW, IW1N = IW2N = HIGH

(MSB) (LSB)

DIL

123

1 2 14 15 16 1 2 14 15 16

Figure 4. LR alternating, trailing data, 16-bit input

Lch DATA

23 24

1 / fs

(LSB) (MSB) (LSB)

1 / fs

1

DIR

BCKI

LRCI

INF1N HIGH, INF2N = LOW.

Data following LSB is ignored. Requires minimum 24 BCKI clock pulses.

Figure 5. LR alternating, leading data, 24-bit input

DIL

DIR

(MSB)

123 1

(MSB)

12314

Lch DATA

456

Rch DATA

5

6

BCKI

LRCI

Rch DATA

(MSB) (LSB)

123

1 / fs

23 24

(LSB)

23 24

(LSB)

23 24

INF1N = INF2N = HIGH.

Data following LSB is ignored. Requires minimum 24 BCKI clock pulses.

Figure 6. LR simultaneous, leading data, 20-bit input

NIPPON PRECISION CIRCUITS—17

Page 18

SM5842AP/APT

Output Timing Examples (DOL, DOR, BCKO, WCKO, DG)

24TB(TDW)

System

Clock

DOL

or

DOR

BCKO

T

WCKO

DG

The number of output bits is determined by the output bit length selected.

1234 18 1917 20

B TB

12TB

10TB

Figure 7. 18/20/22-bit output (CKSLN = HIGH)

24TB(TDW)

System

Clock

DOL

or

DOR

BCKO

1234

24 23 24

B

T

.............................

........................

16 21 22

12TB

12TB 2TB

21 22

(*)

12

12

3

WCKO

12TB

DG

10TB

The number of output bits is determined by the output bit length selected.

Figure 8. 24-bit output (CKSLN = HIGH)

32TB(TDW)

System

Clock

DOL

or

DOR

BCKO

T

WCKO

DG

The number of output bits is determined by the output bit length selected.

123 18 1917

B TB

16TB

14TB

12TB

12TB

......

16TB 2TB

16TB

24

(*)

2TB

12

Figure 9. 24-bit output (CKSLN = LOW)

NIPPON PRECISION CIRCUITS—18

Page 19

Data Input to Output Delay Timing

SM5842AP/APT

This is the digital filter arithmetic computation time from the completion of data input at rate fs (t

rising edge of LRCI to the start of data output at rate 8fs (t

Table 7. Output delay

CKSLN SYNCN Mode t

LOW After reset + sync mode 48.625/fs

LOW (256fs)

HIGH Jitter-free mode 48.25/fs − 49.0/fs

LOW After reset + sync mode 48.75/fs

HIGH (384fs)

HIGH Jitter-free mode 48.375/fs − 49.125/fs

OUTPUT

) on the falling edge of WCKO.

OUTPUT

1/fs

LRCI

Serial data Input

tINPUT

48/fs

WCKO

(256fs)

tOUTPUT

Serial data output

WCKO

(384fs)

INPUT

− t

INPUT

) on the

tINPUT

Figure 10. Delay timing 1

tOUTPUT − tINPUT

Figure 11. Delay timing 2

tOUTPUT

Serial data output

tOUTPUT

NIPPON PRECISION CIRCUITS—19

Page 20

APPLICATION CIRCUITS

Input Interface Circuits

CD decoder (CXD2500Q) connection

SM5842AP/APT

(SONY)

CD

DECODER

CXD2500Q

PSSL

(SONY)

CD

DECODER

CXD2500Q

XTSL

PSSL

C16M

LRCK

DA16

DA15

EMPH

XTAI

LRCK

DA16

DA15

EMPH

16.9344MHz

44.1kHz

2.1168MHz

X'tal(16.9344MHz)

16.9344MHz

44.1kHz

2.1168MHz

XTI

LRCI

DI

BCKI

DEMPL

DEMPR

IW1N

IW2N

INF1N

CKSLN

CKI

LRCI

DI

BCKI

DEMPL

DEMPR

IW1N

IW2N

INF1N

CKSLN

SM5842

MUTEL

MUTER

XTI

SM5842

MUTEL

MUTER

MUTE

FSEL1

FSEL2

XTO

MUTE

FSEL1

FSEL2

Digital audio interface receiver (YM3623B) connection

(YAMAHA)

DIR

YM3623B

S2

S1

L / R

DO

BCO

DEF

384fs (16.9344MHz)

A

fs (44.1kHz)

XTI

LRCI

DI

BCKI

DEMPL

DEMPR

IW1N

IW2N

INF1N

CKSLN

SM5842

MUTEL

MUTER

FSEL1

FSEL2

NIPPON PRECISION CIRCUITS—20

MUTE

Page 21

SM5842AP/APT

Output Interface Circuits

20-bit input Σ∆ DAC (SM5864AP) connection 1

384fs

to SIGNAL

PROCESSOR

(CD DECODER)

512fs

to SIGNAL

PROCESSOR

(CD DECODER)

256fs

256fs

384fs

CKO

OW2N

OW1N

CKO

SM5842

(20bit OUT)

OW2N

OW1N

CKSLN

SM5842

(20bit OUT)

CKSLN

BCKO

WCKO

XTI

BCKO

WCKO

DOL

DOR

XTI

DOL

DOR

256fs

8fs

384fs

8fs

1 / 2

X'tal 384fs

XDIVN

CKO

BCKI

WCKI

DINL

(ΣDECO)

DINR

COMPN

X3SL

X'tal 512fs

XDIVN

CKO

BCKI

WCKI

DINL

DINR

COMPN

X3SL

NPC

Σ∆DAC

SM5864

NPC

Σ∆DAC

SM5864

(ΣDECO)

74HCU04

XTI

LOA

LOBN

ROA

ROBN

74HCU04

XTI

LOBN

ROBN

LOA

ROA

Analog

LPF

Analog

LPF

Analog

LPF

Analog

LPF

Lch OUT

Rch OUT

Lch OUT

Rch OUT

NIPPON PRECISION CIRCUITS—21

Page 22

SM5842AP/APT

20-bit input Σ∆ DAC (SM5864AP) connection 2

L/R-channel independent complementary PWM output

to SIGNAL

PROCESSOR

(CD DECODER)

384fs

CKSLN

CKO

SM5842

(20bit OUT)

XTI

BCKO

WCKO

DOL

DOR

384fs

8fs

XDIVN

CKO

BCKI

WCKI

DINL

Σ∆DAC

SM5864

(ΣDECO)

LOA

LOBN

ROA

ROBNDINR

Analog

LPF

Lch OUT

OW2N

OW1N

74HCU04

X'tal 384fs

20-bit input R − 2R DAC (PCM63P) connection

L/R-channel independent

SM5842

(20bit OUT)

BCKO

WCKO

DOL

DOR

8fs

X3SL

COMPN

XDIVN

BCKI

WCKI

DINL

DINR

X3SL

COMPN

XTI

Σ∆DAC

SM5864

(ΣDECO)

(BURR − BROWN)

PCM63P

CLOCK

LE

DATA

BPO

Iout

LOA

LOBN

ROA

ROBN

Analog

LPF

Analog

LPF

Rch OUT

Lch OUT

OW2N

OW1N

(BURR − BROWN)

PCM63P

CLOCK

L. E

DATA

BPO

Iout

NIPPON PRECISION CIRCUITS—22

Analog

LPF

Rch OUT

Page 23

SM5842AP/APT

NIPPON PRECISION CIRCUITS INC. reserves the right to make changes to the products described in this data sheet in order to

improve the design or performance and to supply the best possible products. Nippon Precision Circuits Inc. assumes no responsibility for

the use of any circuits shown in this data sheet, conveys no license under any patent or other rights, and makes no claim that the circuits

are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision

Circuits Inc. makes no claim or warr anty that such applications will be suitab le for the use specified without further testing or modification.

The products described in this data sheet are not intended to use for the apparatus which influence human lives due to the failure or

malfunction of the products. Customers are requested to comply with applicable laws and regulations in effect now and hereinafter,

including compliance with export controls on the distribution or dissemination of the products. Customers shall not expor t, directly or

indirectly, any products without first obtaining required licenses and approvals from appropriate government agencies.

NIPPON PRECISION CIRCUITS INC.

4-3, Fukuzumi 2-chome

Koto-ku, Tokyo 135-8430, Japan

NIPPON PRECISION CIRCUITS INC.

Telephone: 03-3642-6661

Facsimile: 03-3642-6698

NC9714AE 1998.2

NIPPON PRECISION CIRCUITS—23

Loading...

Loading...