Page 1

www.vishay.com

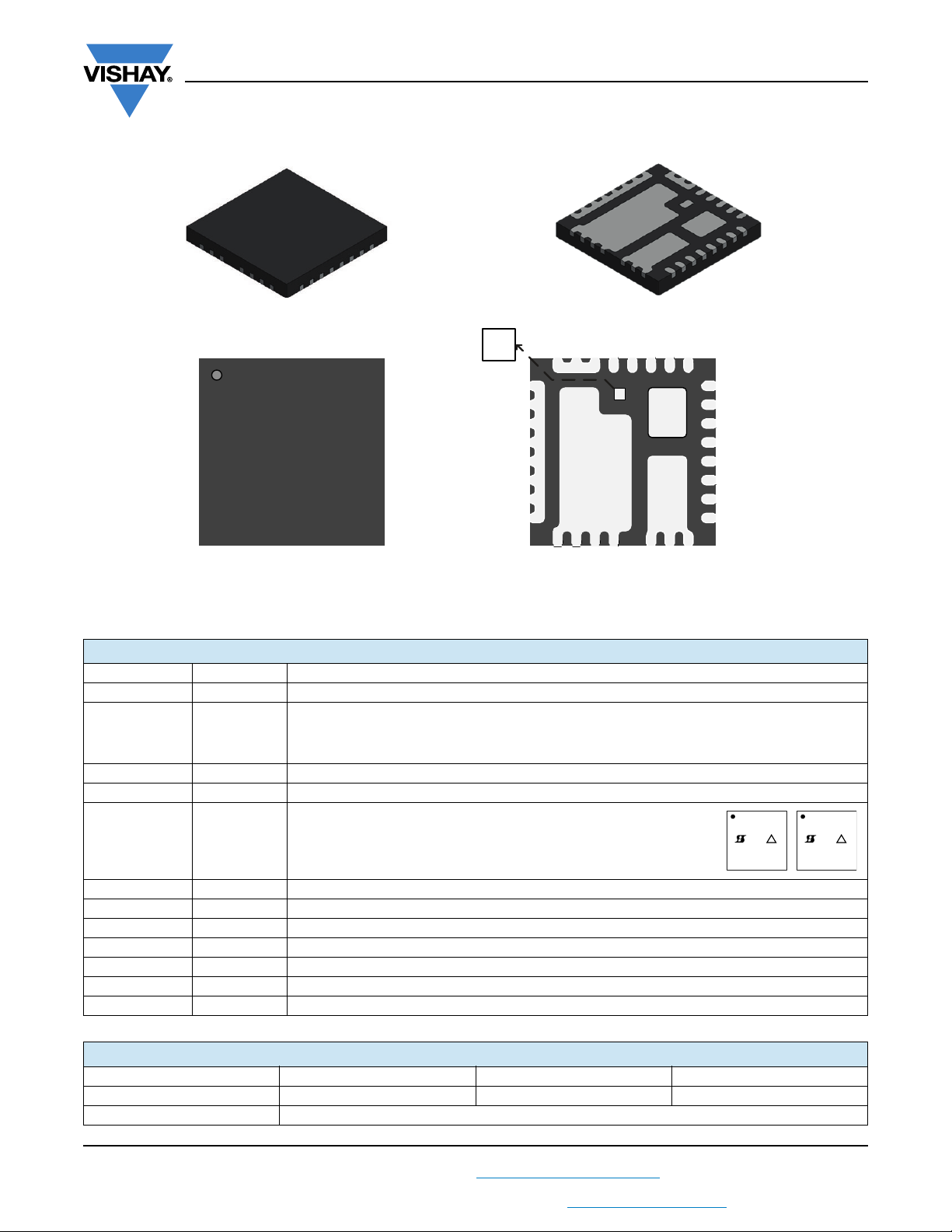

50 A VRPower® Integrated Power Stage

SiC634

Vishay Siliconix

DESCRIPTION

The SiC634 is integrated power stage solutions optimized

for synchronous buck applications to offer high current, high

efficiency, and high power density performance. Packaged

in Vishay’s proprietary

5 mm x 5 mm

enables voltage regulator designs to deliver up to 50 A

continuous current per phase.

The internal power MOSFETs utilizes Vishay’s

state-of-the-art Gen IV TrenchFET® technology that delivers

industry benchmark performance to significantly reduce

switching and conduction losses.

The SiC634 incorporates an advanced MOSFET gate driver

IC that features high current driving capability, adaptive

dead-time control, an integrated bootstrap Schottky diode,

and zero current detection to improve light load efficiency.

The driver is also compatible with a wide range of PWM

controllers, supports tri-state PWM, and 5 V PWM logic.

A user selectable diode emulation mode (ZCD_EN#) is

included to improve the light load performance. The device

also supports PS4 mode to reduce power consumption

when system operates in standby state.

MLP package, SiC634

FEATURES

• Thermally enhanced PowerPAK® MLP55-31L

package

• Vishay’s Gen IV MOSFET technology and a

low-side MOSFET with integrated Schottky

diode

• Delivers in excess of 50 A continuous current, 55 A at

10 ms peak current

• High efficiency performance

• High frequency operation up to 2 MHz

• Power MOSFETs optimized for 19 V input stage

• 5 V PWM logic with tri-state and hold-off

• Supports PS4 mode light load requirement for IMVP8 with

low shutdown supply current (5 V, 3 μA)

• Under voltage lockout for V

CIN

• Material categorization: for definitions of compliance

please see www.vishay.com/doc?99912

APPLICATIONS

• Multi-phase VRDs for computing, graphics card and

memory

• Intel IMVP-8 VRPower delivery

- V

- V

• Up to 24 V rail input DC/DC VR modules

CORE

, V

GRAPHICS

, V

platforms

for Apollo Lake platforms

CCGI

SYSTEM AGENT

Skylake, Kabylake

TYPICAL APPLICATION DIAGRAM

5V V

V

DRV

V

CIN

ZCD_EN#

PWM

controller

S20-0485-Rev. C, 29-Jun-2020

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

PWM

Fig. 1 - SiC634 Typical Application Diagram

For technical questions, contact: powerictechsupport@vishay.com

Gate

driver

GL

C

GND

V

IN

BOOT

PHASE

V

SWH

P

GND

1

Document Number: 76784

IN

V

OUT

Page 2

www.vishay.com

P

GND

N.C.

BOOT

PHASE

V

IN

P

GNDPGNDPGNDPGND

VINVINV

IN

N.C.

GL

V

DRV

N.C.

N.C.

PWM

ZCD_EN#

V

CIN

PGND

VIN

CGND

GL

P

GND

N.C.

BOOT

PHASE

V

IN

P

GND

P

GND

P

GNDPGND

VINVINV

IN

N.C.

GL

V

DRV

N.C.

N.C.

PWM

ZCD_EN#

V

CIN

35

P

GND

34

V

IN

32

C

GND

GL

2

1

4

3

6

5

8

7

2425262728293031

1514131211109

2

1

4

3

6

5

8

7

15 14 13 12 11 10 9

24 25 26 27 28 29 30 31

V

SWH

23

V

SWHVSWHVSWH

V

SWHVSWH

V

SWH

33

GL

V

SWH

22

V

SWH

21

V

SWH

20

V

SWH

19

V

SWH

18

V

SWH

17

V

SWH

16

23 V

SWH

22 V

SWH

21 V

SWH

20 V

SWH

19 V

SWH

16 V

SWH

18 V

SWH

17 V

SWH

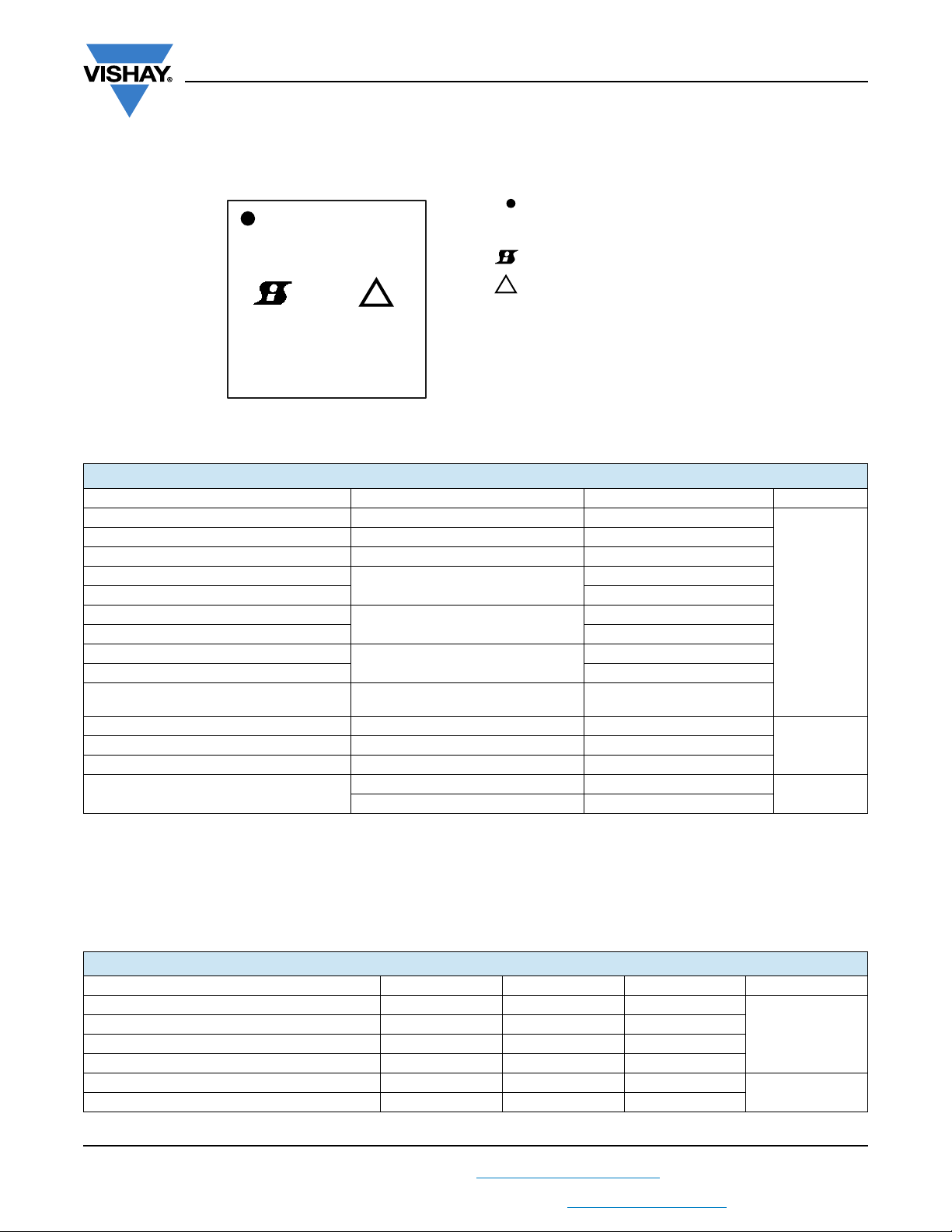

PINOUT CONFIGURATION

SiC634

Vishay Siliconix

Fig. 2 - SiC634 Pin Configuration

PIN CONFIGURATION

PIN NUMBER NAME FUNCTION

1 PWM PWM input logic

The ZCD_EN# pin enables or disables diode emulation. When ZCD_EN# is LOW, diode emulation is

2 ZCD_EN#

3V

CIN

5 BOOT High-side driver bootstrap voltage

4, 6, 30, 31 N.C.

7 PHASE Return path of high-side gate driver

8 to 11, 34 V

12 to 15, 28, 35 P

27, 33 GL Low-side MOSFET gate signal

16 to 26 V

29 V

S20-0485-Rev. C, 29-Jun-2020

32 C

ORDERING INFORMATION

PART NUMBER PACKAGE MARKING CODE OPTION

SiC634CD-T1-GE3 PowerPAK MLP55-31L SiC634 5 V PWM optimized

SiC634DB Reference board

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

IN

GND

SWH

DRV

GND

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

allowed. When ZCD_EN# is HIGH, continuous conduction mode is forced.

ZCD_EN# can also be put in a high impedance mode by floating the pin. If both ZCD_EN# and PWM

are floating, the device shuts down and consumes typically 3 μA (9 μA max.) current

Supply voltage for internal logic circuitry

Pin 4 can be either left floating or connected to C

connected to GND or not internally connected depending on manufacturing

location.

Factory code “G” on line 3, pin 4 = C

Factory code “T” on line 3, pin 4 = not internally connected

GND

. Internally it is either

GND

P/N

LL

G Y W W

Power stage input voltage. Drain of high-side MOSFET

Power ground

Phase node of the power stage

Supply voltage for internal gate driver

Signal ground

2

Document Number: 76784

For technical questions, contact: powerictechsupport@vishay.com

P/N

LL

T Y W W

Page 3

SiC634

www.vishay.com

PART MARKING INFORMATION

= pin 1 indicator

= part number code

P/N

P/N

LL

F Y W W

= Siliconix logo

= ESD symbol

= assembly factory code

F

= year code

Y

WW

= week code

LL

= lot code

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL PARAMETER CONDITIONS LIMIT UNIT

Input voltage V

Control logic supply voltage V

Drive supply voltage V

Switch node (DC voltage)

Switch node (AC voltage)

BOOT voltage (DC voltage)

BOOT voltage (AC voltage)

BOOT to PHASE (DC voltage)

BOOT to PHASE (AC voltage)

All lo gic i npu ts an d o utpu ts

(PWM, ZCD_EN#)

Max. operating junction temperature T

Storage temperature T

Electrostatic discharge protection

Notes

• Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the

specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

(1)

The specification values indicated “AC” is V

(2)

The specification value indicates “AC voltage” is V

(3)

The specification value indicates “AC voltage” is V

(1)

(2)

(3)

Human body model, JESD22-A114 2000

Charged device model, JESD22-C101 1000

to P

SWH

-8 V (< 20 ns, 10 μJ), min. and 35 V (< 50 ns), max.

GND

to P

BOOT

to V

BOOT

IN

CIN

DRV

V

SWH

V

BOOT

V

BOOT-PHASE

J

A

stg

, 40 V (< 50 ns) max.

GND

, 8 V (< 50 ns) max.

PHASE

-0.3 to +28

-0.3 to +7

-0.3 to +7

-0.3 to +28

-7 to +35

-0.3 to +7

-0.3 to +8

-0.3 to V

150

-40 to +125

-65 to +150

Vishay Siliconix

33

40

+0.3

CIN

V

°CAmbient temperature T

V

RECOMMENDED OPERATING RANGE

ELECTRICAL PARAMETER MINIMUM TYPICAL MAXIMUM UNIT

Input voltage (V

Drive supply voltage (V

Control logic supply voltage (V

BOOT to PHASE (V

Thermal resistance from junction to ambient - 10.6 -

Thermal resistance from junction to case - 1.6 -

S20-0485-Rev. C, 29-Jun-2020

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

)4.5-24

IN

) 4.555.5

DRV

) 4.555.5

CIN

BOOT-PHASE

, DC voltage) 4 4.5 5.5

3

For technical questions, contact: powerictechsupport@vishay.com

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Document Number: 76784

V

°C/W

Page 4

www.vishay.com

Vishay Siliconix

ELECTRICAL SPECIFICATIONS

(ZCD_EN# = 5 V, V

PARAMETER SYMBOL TEST CONDITION

POWER SUPPLY

Control logic supply current I

Drive supply current I

PS4 mode supply current I

BOOTSTRAP SUPPLY

Bootstrap diode forward voltage V

PWM CONTROL INPUT

Rising threshold V

Falling threshold V

Tri-state voltage V

Tri-state rising threshold V

Tri-state falling threshold V

Tri-state rising threshold hysteresis V

Tri-state falling threshold hysteresis V

PWM input current I

ZCD_EN# CONTROL INPUT

Rising threshold V

Falling threshold V

Tri-state voltage V

Tri-state rising threshold V

Tri-state falling threshold V

Tri-state rising threshold hysteresis V

Tri-state falling threshold hysteresis V

ZCD_EN# input current I

PS4 exit latency t

TIMING SPECIFICATIONS

Tri-state to GH/GL rising

propagation delay

Tri-state hold-off time t

GH - turn off propagation delay t

GH - turn on propagation delay

(dead time rising)

GL - turn off propagation delay t

GL - turn on propagation delay

(dead time falling)

PWM minimum on-time t

PROTECTION

Under voltage lockout V

Under voltage lockout hysteresis V

Notes

(1)

Typical limits are established by characterization and are not production tested

(2)

Guaranteed by design

S20-0485-Rev. C, 29-Jun-2020

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

= 12 V, V

IN

DRV

and V

= 5 V, TA = 25 °C, unless otherwise stated)

CIN

LIMITS

MIN. TYP. MAX.

V

= FLOAT - 80 -

PWM

VCIN

VDRV

+ I

VCIN

VDRV

F

TH_PWM_R

TH_PWM_F

TRI

TRI_TH_R

TRI_TH_F

HYS_TRI_R

HYS_TRI_F

PWM

TH_ZCD_EN#_R

TH_ZCD_EN#_F

TRI_ZCD_EN#

TRI_ZCD_EN#_R

TRI_ZCD_EN#_F

HYS_TRI_ZCD#_R

HYS_TRI_ZCD#_F

ZCD_EN#

PS4EXIT

t

PD_TRI_R

TSHO

PD_OFF_GH

t

PD_ON_GH

PD_OFF_GL

t

PD_ON_GL

PWM_ON_MIN.

UVLO

UVLO_HYST

= FLOAT, V

PWM

f

= 300 kHz, D = 0.1 - 300 -

S

fS = 300 kHz, D = 0.1 - 10 20

= 1 MHz, D = 0.1 - 30 -

f

S

V

= V

PWM

ZCD_EN#

T

= -10 °C to +100 °C

A

IF = 2 mA - - 0.65 V

V

= FLOAT - 2.5 -

PWM

V

= 5 V - - 350

PWM

= 0 V - - -350

V

PWM

V

= FLOAT - 2.5 -

ZCD_EN#

V

ZCD_EN#

V

ZCD_EN#

No load, see Fig. 4

V

rising, on threshold - 3.4 3.9

CIN

falling, off threshold 2.4 2.9 -

V

CIN

= 0 V - 120 -

ZCD_EN#

= FLOAT,

-39μA

3.6 3.9 4.2

0.72 1 1.3

1.11.351.6

3.4 3.7 4

- 325 -

- 250 -

3.3 3.6 3.9

1.1 1.4 1.7

1.5 1.8 2.1

2.93.153.4

- 375 -

- 450 -

= 5 V - - 100

= 0 V - - -100

--5μs

-20-

- 150 -

-20-

-15-

-20-

-20-

30 - -

- 500 - mV

4

For technical questions, contact: powerictechsupport@vishay.com

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Document Number: 76784

SiC634

UNIT

μAV

mA

V

mV

μA

V

mV

μA

ns

V

Page 5

www.vishay.com

DETAILED OPERATIONAL DESCRIPTION

PWM Input with Tri-State Function

The PWM input receives the PWM control signal from the VR

controller IC. The PWM input is designed to be compatible

with standard controllers using two state logic (H and L) and

advanced controllers that incorporate tri-state logic (H, L

and tri-state) on the PWM output. For two state logic, the

PWM input operates as follows. When PWM is driven above

V

PWM_TH_R

turned on. When PWM input is driven below V

high-side is turned off and the low-side is turned on. For

tri-state logic, the PWM input operates as previously stated

for driving the MOSFETs when PWM is logic high and logic

low. However, there is an third state that is entered as the

PWM output of tri-state compatible controller enters its high

impedance state during shut-down. The high impedance

state of the controller’s PWM output allows the SiC634 to

pull the PWM input into the tri-state region (see definition of

PWM logic and tri-state, Fig. 4). If the PWM input stays in

this region for the tri-state hold-off period, t

high-side and low-side MOSFETs are turned off. The

function allows the VR phase to be disabled without

negative output voltage swing caused by inductor ringing

and saves a Schottky diode clamp. The PWM and tri-state

regions are separated by hysteresis to prevent false

triggering. The SiC634 incorporates PWM voltage

thresholds that are compatible with 5 V.

Diode Emulation Mode and PS4 Mode (ZCD_EN#)

The ZCD_EN# pin enables or disables diode emulation

mode. When ZCD_EN# is driven below V

emulation is allowed. When ZCD_EN# is driven above

V

TH_ZCD_EN#_R

Diode emulation mode allows for higher converter efficiency

under light load situations. With diode emulation active, the

SiC634 will detect the zero current crossing of the output

inductor and turn off the low-side MOSFET. This ensures

that discontinuous conduction mode (DCM) is achieved.

Diode emulation is asynchronous to the PWM signal,

therefore, the SiC634 will respond to the ZCD_EN# input

immediately after it changes state.

The ZCD_EN# pin can be floated resulting in a high

impedance state. High impedance on the input of ZCD_EN#

combined with a tri-stated PWM output will shut down the

SiC634, reducing current consumption to typically 5 μA.

This is an important feature in achieving the low standby

current requirements required in the PS4 state in ultrabooks

and notebooks.

Voltage Input (V

This is the power input to the drain of the high-side power

MOSFET. This pin is connected to the high power

intermediate BUS rail.

the low-side is turned on and the high-side is

TSHO

the

, both

, diode

PWM_TH_F

TH_ZCD_EN#_F

, continuous conduction mode is forced.

)

IN

SiC634

Vishay Siliconix

Switch Node (V

The switch node, V

This is the output applied to the power inductor and output

filter to deliver the output for the buck converter. The PHASE

pin is internally connected to the switch node V

is to be used exclusively as the return pin for the BOOT

capacitor.

Ground Connections (C

P

(power ground) should be externally connected

GND

to C

(control signal ground). The layout of the printed

GND

circuit board should be such that the inductance separating

and P

C

GND

GND

inductance effects between these two pins should not

exceed 0.5 V

Control and Drive Supply Voltage Input (V

V

is the bias supply for the gate drive control IC. V

CIN

the bias supply for the gate drivers. It is recommended to

separate these pins through a resistor. This creates a low

pass filtering effect to avoid coupling of high frequency gate

drive noise into the IC.

Bootstrap Circuit (BOOT)

The internal bootstrap diode and an external bootstrap

capacitor form a charge pump that supplies voltage to the

BOOT pin. An integrated bootstrap diode is incorporated so

that only an external capacitor is necessary to complete the

bootstrap circuit. Connect a boot strap capacitor with one

leg tied to BOOT pin and the other tied to PHASE pin.

Shoot-Through Protection and Adaptive Dead Time

The SiC634 has an internal adaptive logic to avoid shoot

through and optimize dead time. The shoot through

protection ensures that both high-side and low-side

MOSFETs are not turned on at the same time. The adaptive

dead time control operates as follows. The high-side and

low-side gate voltages are monitored to prevent the one

turning on from tuning on until the other's gate voltage is

sufficiently low (< 1 V). Built in delays also ensure that one

power MOS is completely off, before the other can be turned

on. This feature helps to adjust dead time as gate transitions

change with respect to output current and temperature.

Under Voltage Lockout (UVLO)

During the start up cycle, the UVLO disables the gate

drive holding high-side and low-side MOSFET gates low

until the supply voltage rail has reached a point at which

the logic circuitry can be safely activated. The SiC634 also

incorporates logic to clamp the gate drive signals to zero

when the UVLO falling edge triggers the shutdown of the

device.

and PHASE)

SWH

, is the circuit power stage output.

SWH

. This pin

SWH

GND

and P

GND

)

is minimized. Transient differences due to

, V

CIN

)

DRV

DRV

is

S20-0485-Rev. C, 29-Jun-2020

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

5

Document Number: 76784

Page 6

www.vishay.com

ZCD_EN#

V

SWH

GL

+

-

GL

+

-

UVLO

V

CIN

PWM logic

control &

state

machine

Anti-cross

conduction

control

logic

BOOT

V

IN

PWM

C

GND

V

CIN

P

GND

PHASE

V

DRV

V

DRV

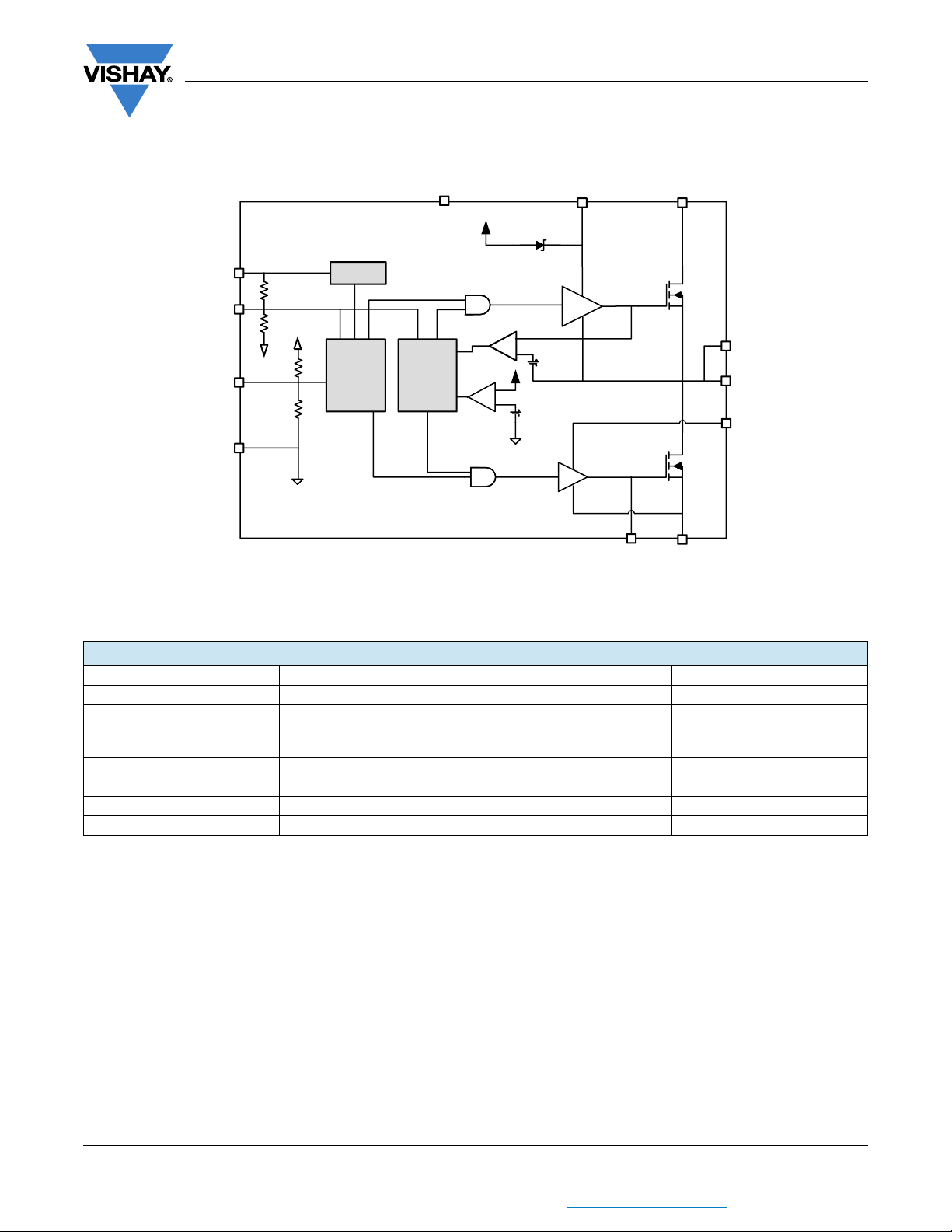

FUNCTIONAL BLOCK DIAGRAM

SiC634

Vishay Siliconix

Fig. 3 - SiC634 Functional Block Diagram

DEVICE TRUTH TABLE

ZCD_EN# PWM GH GL

Tri-state X L L

LLL

LHHL

L Tri-state L L

HLLH

HHHL

H Tri-state L L

S20-0485-Rev. C, 29-Jun-2020

6

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

H, I

L, I

Document Number: 76784

> 0 A

L

< 0 A

L

Page 7

www.vishay.com

V

PWM TIMING DIAGRAM

SiC634

Vishay Siliconix

VTH_PWM_R

VTH_PWM_F

PWM

t

PD_OFF _GL

VTH_TRI_F

VTH_TRI_R

GL

t

PD_ON_GH

GH

ZCD_EN# - PS4 EXIT TIMING

PWM

t

TSHO

t

PD_ON_GL

t

PD_OFF _GH

t

PD_TRI_R

Fig. 4 - Definition of PWM Logic and Tri-State

t

PS4EXIT

t

PD_TRI_R

t

TSHO

5

V

V

SWH

5

ZCD_EN#

2.5 V

Fig. 5 - ZCD_EN# - PS4 Exit Timing

S20-0485-Rev. C, 29-Jun-2020

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

7

Document Number: 76784

Page 8

www.vishay.com

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

5.0

200 300 400 500 600 700 800 900 1000 1100

Power Loss, P

L

(W)

Switching Frequency, fS (kHz)

I

OUT

= 25 A

62

66

70

74

78

82

86

90

94

98

0 5 10 15 20 25 30 35 40 45 50

Efciency (%)

Output Current, I

OUT

(A)

Complete converter efciency

P

IN

= [(VINx IIN) + 5 V x (I

VDRV

+ I

VCIN

)]

P

OUT

= V

OUT

x I

OUT

, measured at output capacitor

1 MHz

750 kHz

500 kHz

15

20

25

30

35

40

45

50

55

60

0 153045607590105120135150

Output Current, I

OUT

(A)

PCB Temperature, T

PCB

(°C)

1 MHz

500 kHz

0.0

2.0

4.0

6.0

8.0

10.0

12.0

14.0

16.0

0 5 10 15 20 25 30 35 40 45 50

Power Loss, P

L

(W)

Output Current, I

OUT

(A)

750 kHz

1MHz

500 kHz

Vishay Siliconix

ELECTRICAL CHARACTERISTICS

Test condition: VIN = 13 V (unless otherwise stated), V

natural convection cooling (All power loss and normalized power loss curves show SiC634 losses only unless otherwise stated)

94

90

DRV

= V

= 5 V, ZCD_EN# = 5 V, V

CIN

OUT

= 1 V, L

= 250 nH (DCR = 0.32 m), TA = 25 °C,

OUT

SiC634

86

500 kHz

82

78

Efciency (%)

74

750 kHz

1 MHz

70

Complete converter efciency

P

66

62

= [(VINx IIN) + 5 V x (I

IN

P

= V

x I

OUT

, measured at output capacitor

OUT

OUT

0 5 10 15 20 25 30 35 40 45 50

Output Current, I

VDRV

OUT

+ I

)]

VCIN

(A)

Fig. 6 - Efficiency vs. Output Current (V

= 12.6 V)

IN

Fig. 9 - Safe Operating Area (V

= 12.6 V)

IN

Fig. 7 - Power Loss vs. Switching Frequency (V

Fig. 8 - Efficiency vs. Output Current (V

S20-0485-Rev. C, 29-Jun-2020

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

= 12.6 V)

IN

Fig. 10 - Power Loss vs. Output Current (V

94

500 kHz

90

86

82

750 kHz

78

Efciency (%)

74

70

Complete converter efciency

P

66

62

= [(VINx IIN) + 5 V x (I

IN

P

= V

OUT

x I

OUT

OUT

0 5 10 15 20 25 30 35 40 45 50

Output Current, I

= 9 V)

IN

Fig. 11 - Efficiency vs. Output Current (V

8

For technical questions, contact: powerictechsupport@vishay.com

= 12.6 V)

IN

1 MHz

+ I

OUT

VCIN

(A)

)]

= 19 V)

IN

VDRV

, measured at output capacitor

Document Number: 76784

Page 9

www.vishay.com

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

5.0

5.5

6.0

-60 -40 -20 0 20 40 60 80 100 120 140

PS4 Mode Current, I

VDRV

& I

VCIN

(uA)

Temperature (°C)

V

PWM

= V

ZCD_EN #

= FLOAT

Vishay Siliconix

ELECTRICAL CHARACTERISTICS

Test condition: VIN = 13 V (unless otherwise stated), V

natural convection cooling (All power loss and normalized power loss curves show SiC634 losses only unless otherwise stated)

DRV

= V

= 5 V, ZCD_EN# = 5 V, V

CIN

OUT

= 1 V, L

= 250 nH (DCR = 0.32 m), TA = 25 °C,

OUT

SiC634

4.2

4.0

(V)

CIN

3.8

3.6

V

UVLO_RISING

3.4

3.2

V

3.0

2.8

Control Logic Supply Voltage, V

UVLO_FALLING

2.6

-60 -40 -20 0 20 40 60 80 100 120 140

Temperature (°C)

Fig. 12 - UVLO Threshold vs. Temperature

4.8

(V)

PWM

4.2

3.6

V

TH_PWM_R

V

TRI_TH_F

3.0

2.4

1.8

V

TRI

V

TRI_TH_R

1.2

PWM Threshold Voltage, V

0.6

V

TH_PWM_F

0.0

-60 -40 -20 0 20 40 60 80 100 120 140

Temperature (°C)

Fig. 13 - PWM Threshold vs. Temperature

0.80

0.75

(V)

F

IF= 2 mA

0.70

0.65

0.60

0.55

0.50

BOOT Diode Forward Voltage, V

0.45

0.40

-60 -40 -20 0 20 40 60 80 100 120 140

Temperature (°C)

Fig. 15 - BOOT Diode Forward Voltage vs. Temperature

4.8

(V)

4.2

V

ZCD_EN#

3.6

3.0

TH_ZCD_EN#_R

V

TRI_ZCD_EN#_ F

2.4

V

TRI_ZCD_EN#_R

1.8

1.2

0.6

ZCD_EN# Threshold Voltage, V

V

TH_ZCD_EN#_F

0.0

-60 -40 -20 0 20 40 60 80 100 120 140

Temperature (°C)

Fig. 16 - ZCD_EN# Threshold vs. Temperature

1.8

1.6

PS4EXIT

1.4

1.2

1.0

0.8

0.6

0.4

Normalized PS4 Exit Latency, t

0.2

-60 -40 -20 0 20 40 60 80 100 120 140

Temperature (°C)

Fig. 14 - PS4 Exit Latency vs. Temperature

S20-0485-Rev. C, 29-Jun-2020

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Fig. 17 - PS4 Mode Current vs. Temperature

9

For technical questions, contact: powerictechsupport@vishay.com

Document Number: 76784

Page 10

www.vishay.com

V

IN

V

SWH

P

GND

V

IN

plane

P

GND

plane

PGND Plane

VSWH

Snubber

V

SWH

P

GND

plane

C

GND

C

VCIN

C

VDRV

P

G

N

D

PCB LAYOUT RECOMMENDATIONS

Step 1: VIN/GND Planes and Decoupling

Step 3: V

CIN/VDRV

SiC634

Vishay Siliconix

Input Filter

1. Layout VIN and P

planes as shown above

GND

2. Ceramic capacitors should be placed directly between

VIN and P

, and close to the device for best

GND

decoupling effect

3. Different values / packages of ceramic capacitors should

be used to cover entire decoupling spectrum e.g. 1210,

0805, 0603, and 0402

4. Smaller capacitance values, closer to device V

pin(s),

IN

- results in better high frequency noise absorbing

Step 2: V

SWH

Plane

1. The V

CIN/VDRV

input filter ceramic capacitors should be

placed close to IC. It is recommended to connect two

caps separately

2. V

capacitor should be placed between pin 3 (V

CIN

and pin 4 (C

of driver IC) to achieve best noise

GND

filtering

3. V

capacitor should be placed between pin 28 (P

DRV

of driver IC) and pin 29 (V

) to provide maximum

DRV

instantaneous driver current for low-side MOSFET

during switching cycle

4. It is recommended to use a large plane analog ground,

, plane to reduce parasitic inductance

C

GND

Step 4: BOOT Resistor and Capacitor Placement

Cboot

Rboot

CIN

GND

)

1. Connect output inductor to DrMOS with large plane to

lower resistance

2. If a snubber network is required, place the components

as shown above, the network can be placed at bottom

S20-0485-Rev. C, 29-Jun-2020

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

For technical questions, contact: powerictechsupport@vishay.com

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

1. The components should be placed close to IC, directly

between PHASE (pin 7) and BOOT (pin 5)

2. To reduce parasitic inductance, chip size 0402 can be

used

10

Document Number: 76784

Page 11

www.vishay.com

VIN plane

P

GND

plane

V

SWH

P

GND

V

IN

C

GND

V

SWH

P

GND

C

GND

SiC634

Vishay Siliconix

Step 5: Signal Routing

C

GND

C

GND

P

GND

1. Route the PWM / ZCD_EN# signal traces out of the top

left corner, next to DrMOS pin 1

2. PWM is an important signal, both signal and return

traces should not cross any power nodes on any layer

3. It is best to “shield” traces form power switching nodes,

e.g. V

, to improve signal integrity

SWH

4. GL (pin 27) has been connected with GL pad internally

and does not need to connect externally

Step 6: Adding Thermal Relief Vias

1. Thermal relief vias can be added on the VIN and P

pads to utilize inner layers for high-current and thermal

dissipation

2. To achieve better thermal performance, additional vias

can be added to VIN and P

3. V

pad is a noise source and not recommended to put

SWH

GND

planes

vias on this plane

4. 8 mil vias for pads and 10 mils vias for planes are the

optimal via sizes. Vias on pads may drain solder during

assembly and cause assembly issue. Please consult

with the assembly house for guideline

Step 7: Ground Connection

1. It is recommended to make a single connection between

C

GND

and P

, this connection can be done on top

GND

layer

2. It is recommended to make the entire first inner layer

(next to top layer) a ground plane and separate it into

C

GND

and P

GND

plane

3. These ground planes provide shielding between noise

sources on top layer and signal traces on bottom layer

GND

S20-0485-Rev. C, 29-Jun-2020

11

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Document Number: 76784

Page 12

SiC634

www.vishay.com

Multi-Phases VRPower PCB Layout

The following is an example of 6 phase layout. As can be seen, all the VRPower stages are lined in X-direction compactly with

decoupling capacitors next to them. The inductors are placed as close as possible to the SiC634 to minimize the PCB copper

loss. Vias are applied on all PADs (VIN, P

optimized. Large copper planes are used for all high current loops, such as VIN, V

duplicated in other layers to minimize the inductance and resistance. All the control signals are routed from the SiC634 to a

controller placed to the north of the power stage through inner layers to avoid the overlap of high current loops. This achieves

a compact design with the output from the inductors feeding a load located to the south of the design as shown in the figure.

V

IN

P

GND

GND

, C

) of the SiC634 to ensure that both electrical and thermal performance are

GND

SWH

, V

OUT

and P

Vishay Siliconix

. These copper planes are

GND

V

P

V

IN

GND

OUT

V

Fig. 18 - Multi-Phase VRPower Layout Top View

OUT

Fig. 19 - Multi-Phase VRPower Layout Bottom View

S20-0485-Rev. C, 29-Jun-2020

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

12

Document Number: 76784

Page 13

www.vishay.com

PRODUCT SUMMARY

Part number SiC634

Description 50 A power stage, 4.5 V

Input voltage min. (V) 4.5

Input voltage max. (V) 24

Continuous current rating max. (A) 50

Switch frequency max. (kHz) 2000

Enable (yes / no) No

Monitoring features -

Protection UVLO, THDN

Light load mode ZCD, PS4

Pulse-width modulation (V) 5

Package type PowerPAK MLP55-31L

Package size (W, L, H) (mm) 5.0 x 5.0 x 0.75

Status code 2

Product type VRPower (DrMOS)

Applications Computer, industrial, networking

to 24 VIN, 5 V PWM with ZCD, PS4 mode

IN

SiC634

Vishay Siliconix

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon

Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package / tape drawings, part marking, and

reliability data, see www.vishay.com/ppg?76784

S20-0485-Rev. C, 29-Jun-2020

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

.

13

For technical questions, contact: powerictechsupport@vishay.com

Document Number: 76784

Page 14

www.vishay.com

by marking

E

Pin 1 dot

Top view

D

MLP55-31L

(5 mm x 5 mm)

E2- 1

Bottom view

Side view

D2- 3 D2- 2

E2- 2

A

0.10 C A

2x

0.10 C B

2x

0.08 C

C

A

A2

A1

B

K7

56

D2- 1

E2- 3

D2-4

E2-4

K8

L

K3

K10

K1

K2

K4

K5

K6

K9

D2-5

K11

K12

F1

F2

K13

8x

1

8

1

16

23

31

24

15

9

8

0.10 C

3

0.10

M

CAB

0.05 C

F3

e/25x

b

31x

b1

31x

e3e2

e1/3x

M

PowerPAK® MLP55-31L Case Outline

Package Information

Vishay Siliconix

DIM.

D2-1 0.98 1.03 1.08 0.039 0.041 0.043

D2-2 0.98 1.03 1.08 0.039 0.041 0.043

D2-3 1.87 1.92 1.97 0.074 0.076 0.078

D2-4 0.30 BSC 0.012 BSC

D2-5 1.05 1.10 1.15 0.041 0.043 0.045

E2-1 1.27 1.32 1.37 0.050 0.052 0.054

E2-2 1.93 1.98 2.03 0.076 0.078 0.080

E2-3 3.75 3.80 3.85 0.148 0.150 0.152

E2-4 0.45 BSC 0.018 BSC

Revision: 21-Aug-17

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

MILLIMETERS INCHES

MIN. NOM. MAX. MIN. NOM. MAX.

A 0.70 0.75 0.80 0.027 0.029 0.031

A1 0.00 - 0.05 0.000 - 0.002

A2 0.20 ref. 0.008 ref.

b 0.20 0.25 0.30 0.078 0.098 0.011

b1 0.15 0.20 0.25 0.006 0.008 0.010

D 4.90 5.00 5.10 0.193 0.196 0.200

e 0.50 BSC 0.019 BSC

e1 3.50 BSC 0.138 BSC

e2 1.50 BSC 0.060 BSC

e3 1.00 BSC 0.040 BSC

E 4.90 5.00 5.10 0.193 0.196 0.200

L 0.35 0.40 0.45 0.013 0.015 0.017

F1 0.15 0.20 0.25 0.006 0.008 0.010

F2 0.20 ref. 0.008 ref.

F3 0.15 ref. 0.006 ref.

For technical questions, contact: powerictechsupport@vishay.com

1

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Document Number: 64909

Page 15

www.vishay.com

Package Information

Vishay Siliconix

DIM.

K1 0.67 BSC 0.026 BSC

K2 0.22 BSC 0.008 BSC

K3 1.25 BSC 0.049 BSC

K4 0.10 BSC 0.004 BSC

K5 0.38 BSC 0.015 BSC

K6 0.12 BSC 0.005 BSC

K7 0.40 BSC 0.016 BSC

K8 0.40 BSC 0.016 BSC

K9 0.40 BSC 0.016 BSC

K10 0.85 BSC 0.033 BSC

K11 0.40 BSC 0.016 BSC

K12 0.40 BSC 0.016 BSC

K13 0.75 BSC 0.030 BSC

ECN: T17-0423-Rev. F, 21-Aug-17

DWG: 6025

Notes

1. Use millimeters as the primary measurement

2. Dimensioning and tolerances conform to ASME Y14.5M. - 1994

3. Dimension b applies to plated terminal and is measured between 0.20 mm and 0.25 mm from terminal tip

4. The pin #1 identifier must be existed on the top surface of the package by using indentation mark or other feature of package body

5. Exact shape and size of this feature is optional

6. Package warpage max. 0.08 mm

7. Applied only for terminals

MIN. NOM. MAX. MIN. NOM. MAX.

MILLIMETERS INCHES

Revision: 21-Aug-17

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

2

Document Number: 64909

Page 16

1.32

(E2-2)

1.98

(E2-3)

(L)

0.4

www.vishay.com

Top side transparent view

(not bottom view)

(D2-4)

1.03

1.03

(E3)

3.4

0.45

1

0.5 (e)

8

31

9

(D2-1)

(D2-2)

Recommended Land Pattern

®

MLP55-31L

1

0.35

0.15

5

8

0.58 0.5

0.3

0.35

0.75

(D2-5)

1.05

(D3) 0.3

(K2) 0.22

(K1) 0.67

(D2-3)

1.92

PowerPAK

24

23

4.2

(E2-1)

(b)

0.25

16

15

(L)

0.4

PAD Patte rn

Vishay Siliconix

Land pattern for MLP55-31L

5

1.35

1.6

0.85

2.02

3.05

1.75

0.5

1.15

0.18

1

24

15

31

1.42

0.42.08

9

0.5

1.13

0.3

0.35

0.33

0.07

0.5

2.15

0.35

0.65

0.57

0.75

0.3

0.75

0.33

23

0.3

3.5

16

0.65

0.3

All dimensions in millimeters

31

1

32

33

8

9

33

24

23

35

16

15

Component for MLP55-31L

Land pattern for MLP55-31L

Revision: 18-Oct-2019

1

Document Number: 66944

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Page 17

Legal Disclaimer Notice

www.vishay.com

Vishay

Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE

RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,

“Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other

disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or

the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all

liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special,

consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular

purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical

requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements

about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product

with the properties described in the product specification is suitable for use in a particular application. Parameters provided in

datasheets and / or specifications may vary in different applications and performance may vary over time. All operating

parameters, including typical parameters, must be validated for each customer application by the customer's technical experts.

Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited

to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and

for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of

any of the products, services or opinions of the corporation, organization or individual associated with the third-party website.

Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website

or for that of subsequent links.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining

applications or for any other application in which the failure of the Vishay product could result in personal injury or death.

Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please

contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by

any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

© 2022 VISHAY INTERTECHNOLOGY, INC. ALL RIGHTS RESERVED

Revision: 01-Jan-2022

1

Document Number: 91000

Loading...

Loading...