Page 1

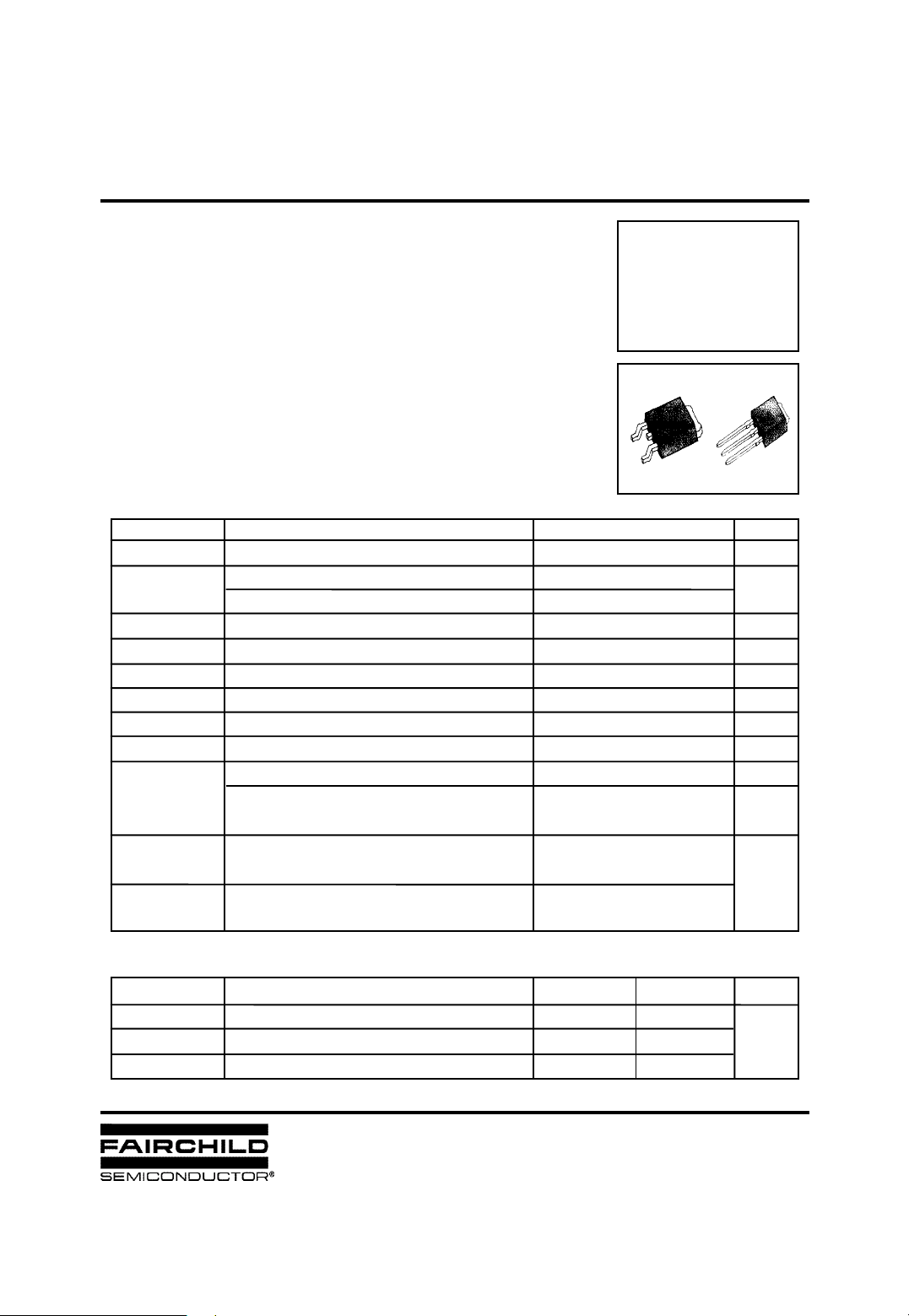

Advanced Power MOSFET

SFW/I9530

FEATURES

n Avalanche Rugged Technology

n Rugged Gate Oxide Technology

n Lower Input Capacitance

n Improved Gate Charge

n Extended Safe Operating Area

o

n 175

C Operating Temperature

n Lower Leakage Current : 10 µA(Max.) @ V

n Low R

: 0.225 Ω (Typ.)

DS(ON)

Absolute Maximum Ratings

Characteristic Value UnitsSymbol

Drain-to-Source Voltage

Continuous Drain Current (T

Continuous Drain Current (T

=25oC)

C

=100oC)

C

Drain Current-Pulsed

Gate-to-Source Voltage

Single Pulsed Avalanche Energy

Avalanche Current

Repetitive Avalanche Energy

Peak Diode Recovery dv/dt

Total Power Dissipation (T

Total Power Dissipation (T

=25oC)

A

=25oC)

C

Linear Derating Factor

Operating Junction and

Storage Temperature Range

Maximum Lead Temp. for Soldering

Purposes, 1/8” from case for 5-seconds

T

V

DSS

I

I

DM

V

E

I

AR

E

dv/dt

P

, T

J

T

D

GS

AS

AR

D

STG

L

= -100V

DS

*

O

O

O

O

O

BV

R

DS(on)

DSS

= -100 V

= 0.3

Ω

ID= -10.5 A

D2-PAK

1

3

1. Gate 2. Drain 3. Source

-100

-10.5

-7.5

1

2

1

1

3

-42

±30

368

-10.5

6.6

-6.5

3.8

66

0.44

- 55 to +175

300

2

1

I2-PAK

2

3

V

A

A

V

mJ

A

mJ

V/ns

W

W

W/

o

C

o

C

Thermal Resistance

Characteristic Max. UnitsSymbol Typ.

R

θJC

R

θJA

R

θJA

When mounted on the mi nimum pad size recommended (PCB Mount).

*

Junction-to-Case

Junction-to-Ambient

Junction-to-Ambient

*

--

--

--

2.27

40

62.5

o

C/W

Rev. C

Page 2

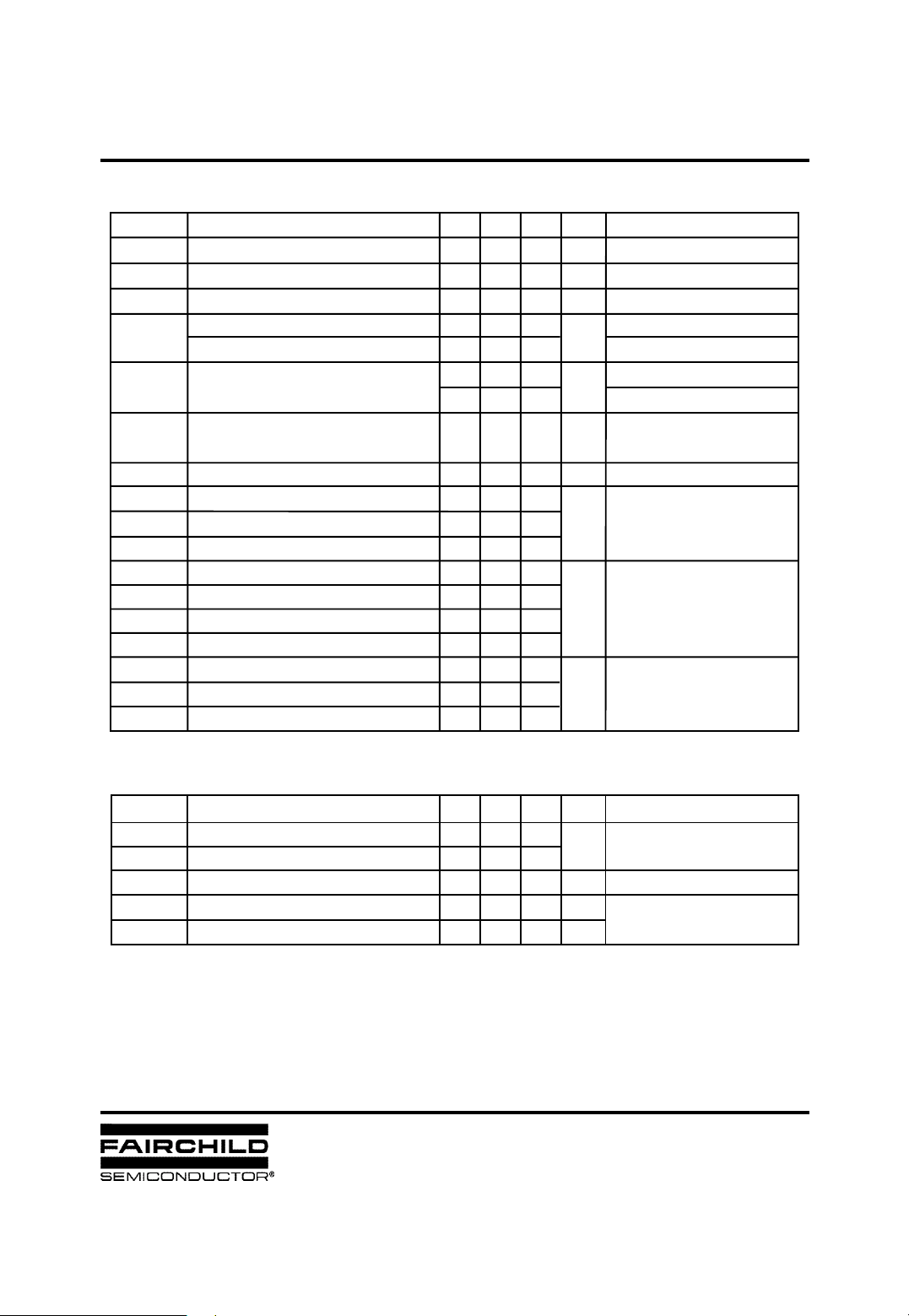

SFW/I9530

P-CHANNEL

POWER MOSFET

Electrical Characteristics

CharacteristicSymbol

BV

∆BV/∆T

V

GS(th)

I

GSS

I

DSS

R

DS(on)

g

C

C

C

t

d(on)

t

d(off)

Q

Q

Q

Drain-Source Breakdown Voltage

DSS

Breakdown Voltage Temp. Coeff.

J

Gate Threshold Voltage

Gate-Source Leakage , Forward

Gate-Source Leakage , Reverse

Drain-to-Source Leakage Current

Static Drain-Source

On-State Resistance

Forward Transconductance

fs

Input Capacitance

iss

Output Capacitance

oss

Reverse Transfer Capacitance

rss

Turn-On Delay Time

t

Rise Time

r

Turn-Off Delay Time

t

Fall Time

f

Total Gate Charge

g

Gate-Source Charge

gs

Gate-Drain(“Miller”) Charge

gd

(TC=25oC unless otherwise specified)

Max. UnitsTyp.Min. Test Condition

V

-100

--

-2.0

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

-0.1

--

--

--

--

--

--

5.5

800

160

60

13

22

45

25

30

5.4

12.2

--

--

-4.0

-100

100

-10

-100

0.3

--

1035

240

90

35

55

100

60

38

--

--

V

V/oC

V

nA

µA

Ω

S

pF

ns

nC

=0V,ID=-250µA

GS

I

=-250µA See Fig 7

D

V

=-5V,ID=-250µA

DS

V

=-20V

GS

V

=20V

GS

VDS=-100V

V

=-80V,TC=150oC

DS

=-10V,ID=-5.3A

V

GS

VDS=-40V,ID=-5.3A

VGS=0V,VDS=-25V,f =1MHz

=-50V,ID=-10.5A,

V

DD

R

=12

G

See Fig 13

V

=-80V,VGS=-10V,

DS

I

=-10.5A

D

See Fig 6 & Fig 12

See Fig 5

Ω

O

4

O

4

O

4

5

O

4

O5O

Source-Drain Diode Ratings and Characteristics

CharacteristicSymbol Max. UnitsTyp.Min. Test Condition

I

I

SM

V

t

Q

Notes ;

1

Repetitive Rating : Pulse Wi dt h Limi t ed by Maximum Junction Temperature

O

2

L=5.0mH, I

O

3

I

O

SD

4

Pulse Test : Pulse Width = 250µs, Duty Cycle 2%

O

5

Essentially Independent of Operating Temperature

O

Continuous Source Current

S

Pulsed-Source Current

Diode Forward Voltage

SD

Reverse Recovery Time

rr

Reverse Recovery Charge

rr

=-10.5A, VDD=-25V, RG=27Ω*, Starting TJ =25oC

AS

_

<

-10.5A, di/dt 400A/µs, V

_

<

_

<

DD BVDSS

--

1

--

O

4

--

O

120

--

0.53

--

, Starting TJ =25oC

_

<

-10.5

--

--

--

-42

-4.0

--

--

A

V

ns

µC

Integral reverse pn-diode

in the MOSFET

T

=25oC,IS=-10.5A,VGS=0V

J

T

=25oC,IF=-10.5A

J

di

/dt=100A/µs

F

O

4

Page 3

P-CHANNEL

POWER MOSFET

Fig 1. Output Characteristics Fig 2. Transfer Characteristics

V

GS

Top : - 1 5 V

- 10 V

- 8.0 V

1

- 7.0 V

10

- 6.0 V

- 5.5 V

- 5.0 V

Bott om : - 4.5 V

0

10

, Drain Current [A]

D

-I

-1

10

-1

10

-VDS , Drain-Source Voltage [V]

@ Notes :

1. 250 µs Pulse Test

2. TC = 25 oC

0

10

SFW/I9530

1

10

175 oC

0

10

25 oC

, Drain Current [A ]

D

-I

-1

1

10

10

246810

- 55 oC

-VGS , Gate-Source Vo ltage [V]

@ Notes :

1. V

2. V

3. 250

= 0 V

GS

= -40 V

DS

s Pulse Test

µ

1.0

0.8

]

Ω

, [

0.6

DS(on)

R

0.4

Drain-Source On-Resistance

0.2

0.0

0 7 14 21 28 35 42

VGS = -10 V

VGS = -20 V

@ Note : TJ = 25 oC

-ID , Drain Current [A ]

1500

C

1000

500

Capacitance [pF]

iss

C

oss

C

rss

0

0

10

C

= Cgs+ Cgd ( Cds= shorted )

iss

= Cds+ C

C

oss

gd

C

= C

rss

gd

1

10

-VDS , Drain-Source Voltage [V]

@ Notes :

1. V

= 0 V

GS

2. f = 1 MHz

Fig 4. Source-Drain Diode Forward VoltageFig 3. On-Resistance vs. Drain Current

1

10

0

10

175 oC

@ Notes :

1. V

, Reverse Dr ain Current [A]

DR

-I

-1

10

25 oC

0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

2. 250

= 0 V

GS

s Pulse Test

µ

-VSD , Source-Dra in Voltage [V]

Fig 6. Gate Charge vs. Gate-Source VoltageFig 5. Capacitance vs. Drain-Source Voltage

10

5

, Gate-Source Voltage [V]

GS

-V

0

0 5 10 15 20 25 30 35

VDS = -20 V

VDS = -50 V

VDS = -80 V

@ Notes : ID =-10.5 A

QG , Total Gate Charge [nC]

Page 4

SFW/I9530

Fig 7. Breakdown Voltage vs. Temperature Fig 8. On-Resistance vs. Temperature

1.2

2.5

POWER MOSFET

P-CHANNEL

1.1

1.0

, (Normalized)

DSS

-BV

0.9

Drain-Source Breakdown Voltage

0.8

-75 -50 -25 0 25 50 75 100 125 150 175 200

@ Notes :

1. V

2. I

TJ , Junction Temperature [oC]

0

10

Operation in This Area

is Limited by R

@ Notes :

1. T

= 25 oC

C

= 175 oC

2. T

J

3. Single P ulse

DS(on)

0.1 ms

1 ms

10 ms

DC

1

10

2

10

1

10

, Drain Current [A]

D

-I

0

10

-1

10

-VDS , Drain-Source Voltage [V]

= 0 V

GS

= -250 µA

D

10

2.0

1.5

1.0

, (Normalized)

DS(on)

R

0.5

Drain-Source On-Resistance

0.0

-75 -50 -25 0 25 50 75 100 125 150 175 200

@ Notes :

1. V

2. I

= -10 V

GS

= -5.3 A

D

TJ , Junction Temperature [oC]

Fig 10. Max. Drain Current vs. Case TemperatureFig 9. Max. Safe Operating Area

12

10

8

6

4

, Drain Current [A ]

D

-I

2

2

0

25 50 75 100 125 150 175

Tc , Case Temperature [oC]

Fig 11. Thermal Response

D=0.5

0

10

0.2

0.1

0.05

-1

10

0.02

0.01

(t) , Thermal Response

JC

θ

Z

-5

10

single pulse

-4

10

-3

10

10

@ Notes :

1. Z

2. Duty Factor, D=t1/t

3. TJM-TC=PDM*Z

-2

JC

θ

P

DM

.

-1

10

(t)=2.27 oC/W Max.

2

(t)

JC

θ

t

1.

t

2.

0

10

1

10

t1 , Square Wave Pulse Durati on [sec]

Page 5

P-CHANNEL

POWER MOSFET

SFW/I9530

Fig 12. Gate Charge Test Circuit & Waveform

12V

-10V

“ Current Regulator

200nF

-3mA

V

R

G

”

50K

Ω

300nF

V

GS

R

1

Current Sampling (IG)

Resistor

Fig 13. Resistive Switching Test Circuit & Waveforms

V

out

in

DUT

Same Type

as DUT

DUT

R

2

Current Sampling (ID)

Resistor

R

L

V

DD

( 0.5 rated V

V

GS

Q

-10V

V

DS

Q

gs

g

Q

gd

Charge

t

on

t

d(on)tr

)

DS

V

in

10%

90%

V

out

t

d(off)

t

off

t

f

Vary tpto obtain

required peak I

-10V

Fig 14. Unclamped Inductive Switching Test Circuit & Waveforms

BV

L

V

DS

D

R

G

L

I

D

V

DD

C

V

DD

E

=LL I

AS

----

1

2

AS

t

p

I

(t)

D

2

-------------------BV

DSS

DSS

-- V

DD

Time

V

(t)

DS

DUT

I

AS

t

p

BV

DSS

Page 6

SFW/I9530

Fig 15. Peak Diode Recovery dv/dt Test Circuit & Waveforms

DUT

P-CHANNEL

POWER MOSFET

+

V

DS

--

I

S

L

V

GS

( Driver )

I

S

( DUT )

V

DS

( DUT )

V

GS

V

GS

Driver

R

G

D =

IFM, Body Diode Forward Current

Comp liment of DU T

Gate Pulse Width

-------------------------Gate Pulse Period

Body Diode

Forward Voltage Drop

(N-Channel)

• dv/dt controlled by “RG”

•I

controlled by Duty Factor “D”

S

Body Diode Reverse Current

I

RM

V

f

di/dt

V

DD

10V

V

DD

Body Diode Recovery dv/dt

Page 7

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is

not intended to be an exhaustive list of all such trademarks.

ACEx

ActiveArray

Bottomless

CoolFET

CROSSVOL T

DOME

EcoSPARK

E2CMOS

EnSigna

TM

TM

FACT

FACT Quiet Series

â

FAST

FASTr

FRFET

GlobalOptoisolator

GTO

HiSeC

I2C

Across the board. Around the world.

The Power Franchise

Programmable Active Droop

ImpliedDisconnect

ISOPLANAR

LittleFET

MicroFET

MicroPak

MICROWIRE

MSX

MSXPro

OCX

OCXPro

OPTOLOGIC

â

OPTOPLANAR

PACMAN

POP

Power247

PowerTrench

â

QFET

QS

QT Optoelectronics

Quiet Series

RapidConfigure

RapidConnect

SILENT SWITCHER

SMART START

SPM

Stealth

SuperSOT-3

SuperSOT-6

SuperSOT-8

SyncFET

TinyLogic

TruTranslation

UHC

UltraFET

â

VCX

â

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER

NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD

DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT

OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT

RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or

systems which, (a) are intended for surgical implant into

the body, or (b) support or sustain life, or (c) whose

failure to perform when properly used in accordance

with instructions for use provided in the labeling, can be

reasonably expected to result in significant injury to the

user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information

Preliminary

No Identification Needed

Formative or

In Design

First Production

Full Production

2. A critical component is any component of a life

support device or system whose failure to perform can

be reasonably expected to cause the failure of the life

support device or system, or to affect its safety or

effectiveness.

This datasheet contains the design specifications for

product development. Specifications may change in

any manner without notice.

This datasheet contains preliminary data, and

supplementary data will be published at a later date.

Fairchild Semiconductor reserves the right to make

changes at any time without notice in order to improve

design.

This datasheet contains final specifications. Fairchild

Semiconductor reserves the right to make changes at

any time without notice in order to improve design.

Obsolete

Not In Production

This datasheet contains specifications on a product

that has been discontinued by Fairchild semiconductor.

The datasheet is printed for reference information only.

Rev. I1

Loading...

Loading...