Page 1

USER’S MANUAL

M2

SDA 6000

Teletext Decoder

with Embedded

16-bit Controller

Edition March 1, 2001

6251-557-1

Page 2

SDA 6000

Revision History: Current Version: 2000-06-15

Previous Version: 08.99

Page Subjects (major changes since last revision)

Complete Update of Controller & Peripheral Spec --> Detailed Version

ASC: Autobaud Detection Feature included

IC: New Description

GPT: New Description

IIC changed to I

2

C

For questions on technology, delivery and prices please contact the Micronas Offices in Germany

or the Micronas GmbH Companies and Representatives worldwide:

see our webpage at http://www.micronas.com

Page 3

Contents

Overview

Page 4

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

1Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 3

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 7

1.2 Logic Symbol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 9

2 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 - 3

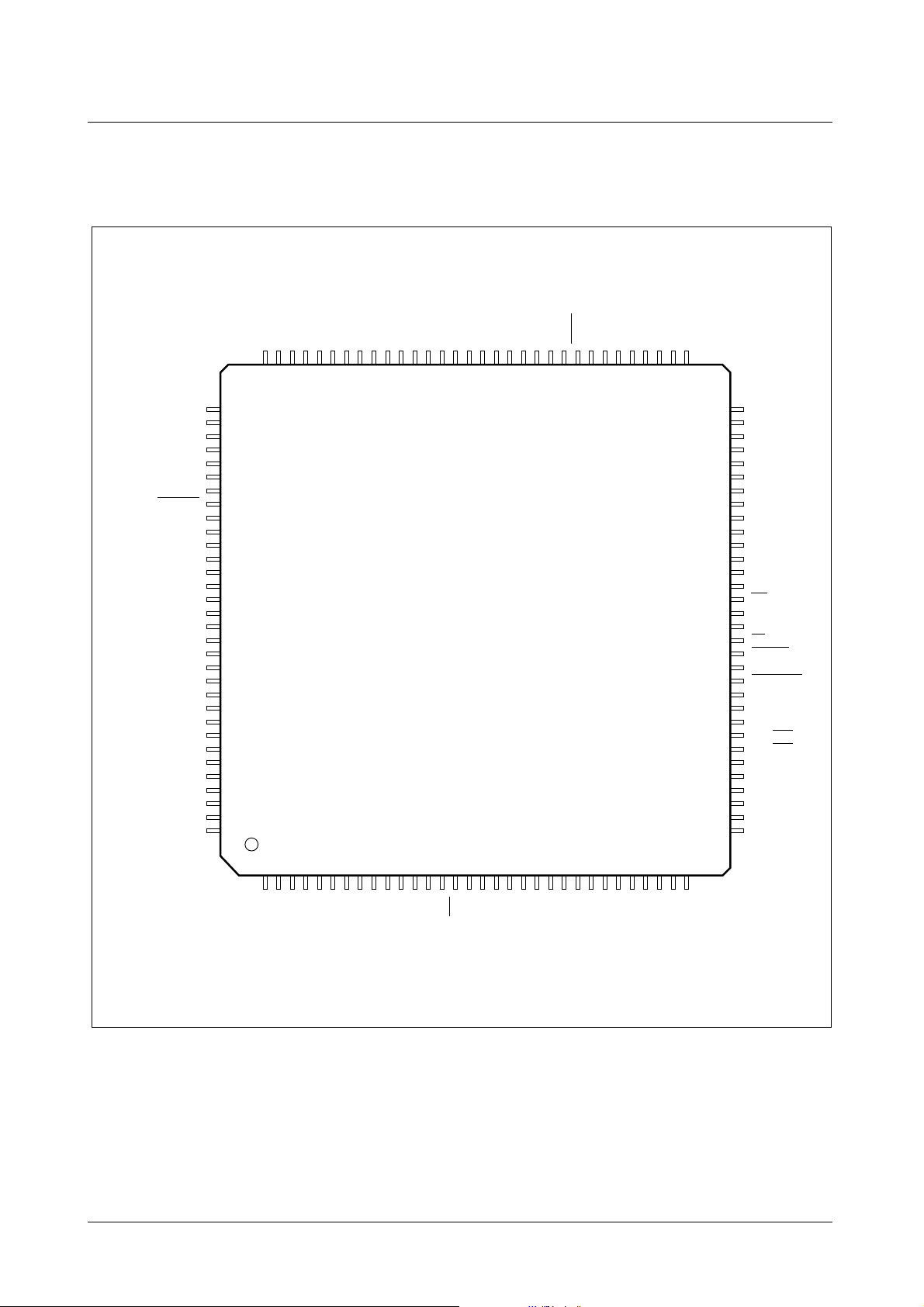

2.1 Pin Diagram (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 - 3

2.2 Pin Definitions and Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 - 4

3 Architectural Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 - 3

4 C16X Microcontroller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 3

4.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 3

4.2 Memory Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 5

4.3 On-Chip Microcontroller RAM and SFR Area . . . . . . . . . . . . . . . . . . . . 4 - 7

4.3.1 System Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 9

4.3.2 General Purpose Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 9

4.3.3 PEC Source and Destination Pointers . . . . . . . . . . . . . . . . . . . . . . . 4 - 10

4.3.4 Special Function Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 11

4.4 External Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 12

4.4.1 SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 13

4.4.2 External Static Memory Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 13

4.5 External Bus Interface (EBI). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 13

4.5.1 Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 16

4.5.2 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 19

4.5.3 Crossing Memory Boundaries . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 23

4.6 Central Processing Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 24

4.6.1 Instruction Pipelining . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 26

4.6.2 Bit-Handling and Bit-Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 32

4.6.3 Instruction State Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 33

4.6.4 CPU Special Function Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 34

5 Interrupt and Trap Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 - 3

5.1 Interrupt System Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 - 3

5.1.1 Interrupt Allocation Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 - 4

5.1.2 Hardware Traps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 - 6

5.2 Operation of the PEC Channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 - 13

5.2.1 Prioritization of Interrupt and PEC Service Requests . . . . . . . . . . . 5 - 20

5.2.2 Saving the Status during Interrupt Service . . . . . . . . . . . . . . . . . . . 5 - 22

5.2.3 Interrupt Response Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 - 23

5.2.4 PEC Response Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 - 25

5.2.5 Fast Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 - 27

5.3 Trap Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 - 28

5.3.1 External Interrupt Source Control . . . . . . . . . . . . . . . . . . . . . . . . . . 5 - 33

6 System Control & Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 3

A-3 Micronas

Page 5

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

6.1 System Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 3

6.1.1 Behavior of I/Os during Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 5

6.1.2 Reset Values for the Controller Core Registers . . . . . . . . . . . . . . . . . 6 - 5

6.1.3 The Internal RAM after Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 5

6.2 System Start-up Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 5

6.3 Register Write Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 8

6.4 Power Reduction Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 12

6.5 Dedicated Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 15

6.6 XBUS Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 17

6.7 Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 17

6.8 Bootstrap Loader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 21

6.9 Identification Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 23

6.9.1 System Identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 23

6.9.2 CPU Identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 26

6.10 Parallel Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 27

7 Peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 3

7.1 General Purpose Timer Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 3

7.1.1 Functional Description of Timer Block 1 . . . . . . . . . . . . . . . . . . . . . . 7 - 3

7.1.1.1 Timer Concatenation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 14

7.1.2 Functional Description of Timer Block 2 . . . . . . . . . . . . . . . . . . . . . 7 - 19

7.1.2.1 Core Timer T6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 20

7.1.2.2 Auxiliary Timer T5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 21

7.1.2.3 Timer Concatenation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 22

7.1.3 GPT Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 26

7.1.4 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 37

7.2 Real-time Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 39

7.2.1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 39

7.2.2 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 41

7.3 Asynchronous/Synchronous Serial Interface . . . . . . . . . . . . . . . . . . . . 7 - 46

7.3.1 Asynchronous Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 49

7.3.1.1 Asynchronous Data Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 51

7.3.1.2 Asynchronous Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 53

7.3.1.3 Asynchronous Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 54

7.3.2 Synchronous Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 56

7.3.2.1 Synchronous Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 57

7.3.2.2 Synchronous Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 58

7.3.2.3 Synchronous Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 58

7.3.3 Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 59

7.3.3.1 Baud Rates in Asynchronous Mode . . . . . . . . . . . . . . . . . . . . . . 7 - 60

7.3.3.2 Baud Rates in Synchronous Mode . . . . . . . . . . . . . . . . . . . . . . . 7 - 63

7.3.4 Autobaud Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 63

7.3.4.1 Serial Frames for Autobaud Detection . . . . . . . . . . . . . . . . . . . . . 7 - 64

A-4 Micronas

Page 6

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

7.3.4.2 Baud Rate Selection and Calculation . . . . . . . . . . . . . . . . . . . . . 7 - 67

7.3.4.3 Overwriting Registers on Successful Autobaud Detection . . . . . 7 - 69

7.3.5 ASC Hardware Error Detection Capabilities . . . . . . . . . . . . . . . . . . 7 - 70

7.3.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 71

7.3.7 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 72

7.4 High Speed Synchronous Serial Interface . . . . . . . . . . . . . . . . . . . . . . 7 - 82

7.4.1 Full-Duplex Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 86

7.4.2 Half Duplex Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 89

7.4.3 Continuous Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 90

7.4.4 Port Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 91

7.4.5 Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 91

7.4.6 Error Detection Mechanisms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 92

7.4.7 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 95

7.5 I2C-Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 99

7.5.1 Operational Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 100

2

7.5.2 The Physical I

7.5.3 Functional Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 103

7.5.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 105

7.6 Analog Digital Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 118

7.6.1 Power Down and Wake Up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 119

7.6.2 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 119

C-Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 100

8 Clock System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 - 3

8.1 General Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 - 3

8.2 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 - 4

9 Sync System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 - 3

9.1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 - 3

9.1.1 Screen Resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 - 3

9.1.2 Sync Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 - 5

9.2 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 - 6

10 Display Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 3

10.1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 3

10.2 Screen Alignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 3

10.3 Layer Concept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 5

10.3.1 Overlapped Layers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 6

10.3.2 Embedded Layers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 8

10.3.3 Transparency in Screen Background Area . . . . . . . . . . . . . . . . . . . 10 - 9

10.4 Input and Output Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 11

10.4.1 Input Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 12

10.4.2 Output Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 13

10.5 Initialization of Memory Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 17

10.5.1 Transfer Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 17

A-5 Micronas

Page 7

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

10.5.2 Transfer Areas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 20

10.5.3 Italic Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 25

10.6 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 27

10.6.1 Special Function Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 27

10.7 Description of Graphic Accelerator Instructions . . . . . . . . . . . . . . . . . 10 - 30

10.7.1 Screen Attributes (SAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 32

10.7.2 Startaddress of Layer 1 (FBR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 35

10.7.3 Size of Layer 1 (FSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 35

10.7.4 Startaddress of Layer 2 (DBR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 36

10.7.5 Size of Layer 2 (DSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 36

10.7.6 Display Coordinates of Layer 2 (DCR) . . . . . . . . . . . . . . . . . . . . . 10 - 37

10.7.7 Contents of CLUT (CLR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 38

10.7.8 Clipping Coordinates (CUR and CBR) . . . . . . . . . . . . . . . . . . . . . . 10 - 38

10.7.9 Source Descriptor for Data Transfer (SDR) . . . . . . . . . . . . . . . . . . 10 - 40

10.7.10 Source Size of Transferred Memory Area (TSR) . . . . . . . . . . . . . . 10 - 41

10.7.11 Destination Size of Transferred Memory Area (TDR) . . . . . . . . . . 10 - 42

10.7.12 Offset of Transferred Memory Area (TOR) . . . . . . . . . . . . . . . . . . 10 - 43

10.7.13 Attributes of Transfer (TAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 44

11 D/A Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 - 3

11.1 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 - 3

12 Slicer and Acquisition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 3

12.1 General Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 3

12.2 Slicer Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 3

12.2.1 Distortion Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 5

12.2.2 Data Separation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 6

12.3 H/V-Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 6

12.4 Acquisition Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 6

12.4.1 FC-Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 7

12.4.2 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 8

12.4.3 VBI Buffer and Memory Organization . . . . . . . . . . . . . . . . . . . . . . . 12 - 8

12.5 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 9

12.5.1 RAM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 12

12.5.2 Recommended Parameter Settings . . . . . . . . . . . . . . . . . . . . . . . . 12 - 25

13 Register Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 - 3

13.1 Register Description Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 - 3

13.2 CPU General Purpose Registers (GPRs) . . . . . . . . . . . . . . . . . . . . . 13 - 4

13.3 Registers ordered by Context . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 - 5

13.4 Registers Ordered by Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 - 13

13.4.1 Registers in SFR Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 - 14

13.4.2 Registers in ESFR Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 - 15

14 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 - 3

A-6 Micronas

Page 8

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

14.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 - 3

14.2 Operating Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 - 3

14.3 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 - 4

14.4 Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 - 10

14.5 Package Outlines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 - 11

A-7 Micronas

Page 9

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

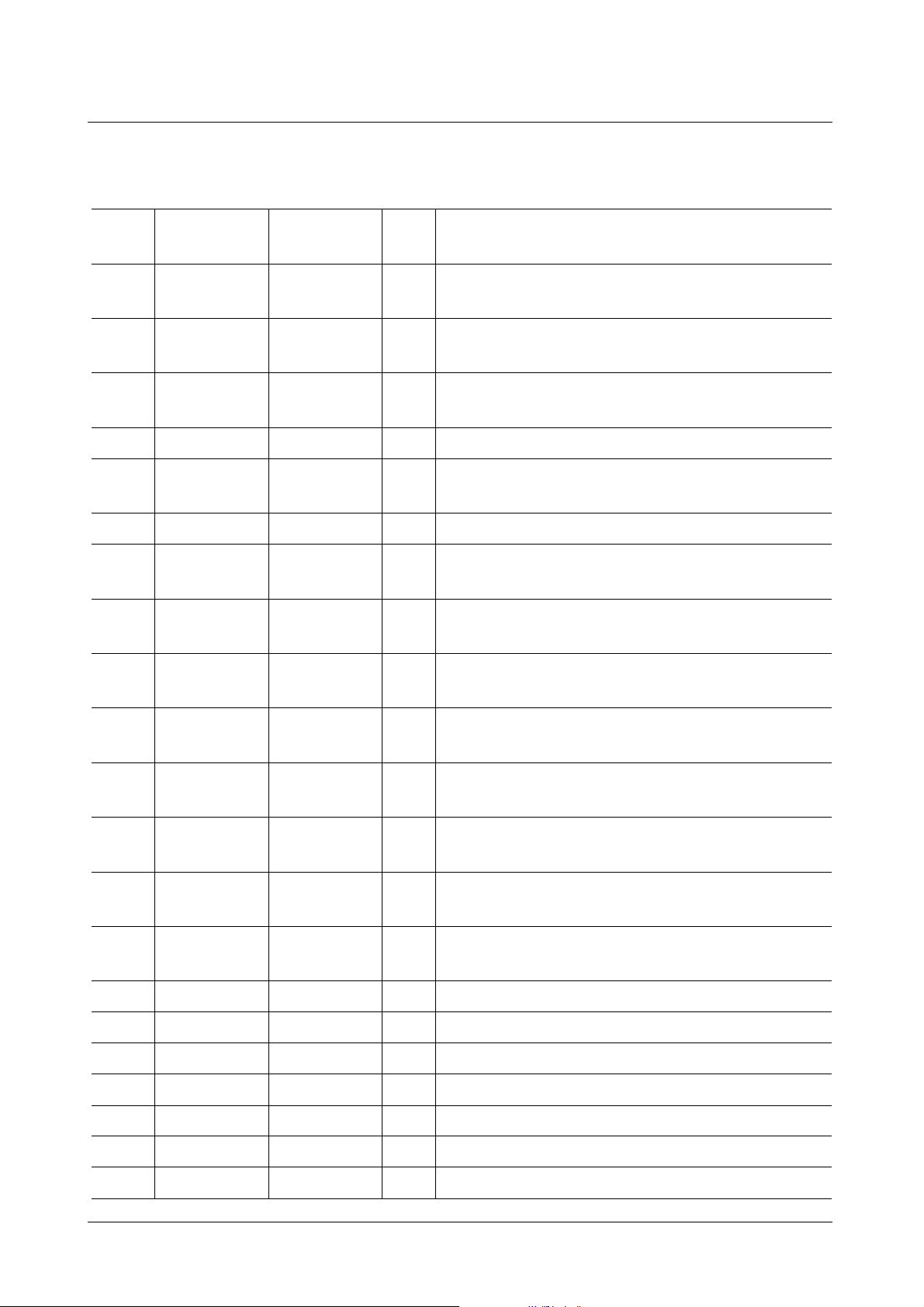

Figure 1-1 M2 Tool Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 5

Figure 1-2 Logic Symbol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 9

Figure 2-1 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 - 3

Figure 3-1 M2 Top Level Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 - 3

Figure 4-1 M2 Memory Path Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 6

Figure 4-2 Storage of Words, Byte and Bits in a Byte Organized Memory . . . . 4 - 7

Figure 4-3 Internal RAM Areas and SFR Areas . . . . . . . . . . . . . . . . . . . . . . . . 4 - 8

Figure 4-4 Location of the PEC Pointers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 11

Figure 4-5 External Memory Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 14

Figure 4-6 Interlocked Access Cycles to ROM and SDRAM . . . . . . . . . . . . . . 4 - 15

Figure 4-7 Interlocked Access Cycles to two SDRAM Banks . . . . . . . . . . . . . 4 - 16

Figure 4-8 Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 17

Figure 4-9 Four-Phase Handshake . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 21

Figure 4-10 CPU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 25

Figure 4-11 Sequential Instruction Pipelining . . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 28

Figure 4-12 Standard Branch Instruction Pipelining . . . . . . . . . . . . . . . . . . . . . 4 - 28

Figure 4-13 Cache Jump Instruction Pipelining . . . . . . . . . . . . . . . . . . . . . . . . . 4 - 29

Figure 4-14 Addressing via the Code Segment Pointer . . . . . . . . . . . . . . . . . . 4 - 42

Figure 4-15 Addressing via the Data Page Pointers . . . . . . . . . . . . . . . . . . . . . 4 - 44

Figure 4-16 Register Bank Selection via Register CP. . . . . . . . . . . . . . . . . . . . 4 - 45

Figure 4-17 Implicit CP Use by Short GPR Addressing Modes . . . . . . . . . . . . 4 - 46

Figure 5-1 Priority Levels and PEC Channels. . . . . . . . . . . . . . . . . . . . . . . . . 5 - 10

Figure 5-2 Mapping of PEC Offset Pointers into the Internal RAM . . . . . . . . . 5 - 19

Figure 5-3 Task Status Saved on the System Stack . . . . . . . . . . . . . . . . . . . . 5 - 22

Figure 5-4 Pipeline Diagram for Interrupt Response Time . . . . . . . . . . . . . . . 5 - 23

Figure 5-5 Pipeline Diagram for PEC Response Time . . . . . . . . . . . . . . . . . . 5 - 26

Figure 6-1 State Machine for Security Level Switching . . . . . . . . . . . . . . . . . . 6 - 11

Figure 6-2 Transitions between Idle Mode and Active Mode . . . . . . . . . . . . . 6 - 14

Figure 6-3 WDT Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 18

Figure 6-4 Bootstrap Loader Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 22

Figure 6-5 Portlogic Register Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 - 27

Figure 7-1 Structure of Timer Block 1 Core Timer T3 . . . . . . . . . . . . . . . . . . . . 7 - 4

Figure 7-2 Block Diagram of Core Timer T3 in Timer Mode . . . . . . . . . . . . . . . 7 - 7

Figure 7-3 Block Diagram of Core Timer T3 in Gated Timer Mode. . . . . . . . . . 7 - 7

Figure 7-4 Block Diagram of Core Timer T3 in Counter Mode . . . . . . . . . . . . . 7 - 8

Figure 7-5 Block Diagram of Core Timer T3 in Incremental Interface Mode. . . 7 - 9

Figure 7-6 Interfacing the Encoder to the Microcontroller . . . . . . . . . . . . . . . . 7 - 10

Figure 7-7 Evaluation of the Incremental Encoder Signals . . . . . . . . . . . . . . . 7 - 11

Figure 7-8 Evaluation of the Incremental Encoder Signals . . . . . . . . . . . . . . . 7 - 12

Figure 7-9 Block Diagram of an Auxiliary Timer in Counter Mode . . . . . . . . . 7 - 13

Figure 7-10 Concatenation of Core Timer T3 and an Auxiliary Timer. . . . . . . . 7 - 15

Figure 7-11 GPT1 Auxiliary Timer in Reload Mode. . . . . . . . . . . . . . . . . . . . . . 7 - 16

Figure 7-12 GPT1 Timer Reload Configuration for PWM Generation . . . . . . . . 7 - 17

B-1 Micronas

Page 10

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Figure 7-13 Auxiliary Timer of Timer Block 1 in Capture Mode. . . . . . . . . . . . . 7 - 18

Figure 7-14 Structure of Timer Block 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 19

Figure 7-15 Block Diagram of Core Timer T6 in Timer Mode . . . . . . . . . . . . . . 7 - 21

Figure 7-16 Concatenation of Core Timer T6 and Auxiliary Timer T5. . . . . . . . 7 - 22

Figure 7-17 Timer Block 2 Register CAPREL in Capture Mode . . . . . . . . . . . . 7 - 23

Figure 7-18 Timer Block 2 Register CAPREL in Reload Mode . . . . . . . . . . . . . 7 - 24

Figure 7-19 Timer Block 2 Register CAPREL in Capture-And-Reload Mode . . 7 - 25

Figure 7-20 RTC Register Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 39

Figure 7-21 RTC Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 40

Figure 7-22 Block Diagram of the ASC0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 47

Figure 7-23 ASC Register Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 48

Figure 7-24 Asynchronous Mode of Serial Channel ASC0 . . . . . . . . . . . . . . . . 7 - 50

Figure 7-25 Asynchronous 8-Bit Frames. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 51

Figure 7-26 Asynchronous 9-Bit Frames. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 52

Figure 7-27 IrDA Frame Encoding/Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 53

Figure 7-28 Fixed IrDA Pulse Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 55

Figure 7-29 RXD/TXD Data Path in Asynchronous Modes. . . . . . . . . . . . . . . . 7 - 56

Figure 7-30 Synchronous Mode of Serial Channel ASC0 . . . . . . . . . . . . . . . . . 7 - 57

Figure 7-31 ASC0 Synchronous Mode Waveforms . . . . . . . . . . . . . . . . . . . . . 7 - 59

Figure 7-32 ASC0 Baud Rate Generator Circuitry in Asynchronous Modes. . . 7 - 61

Figure 7-33 ASC0 Baud Rate Generator Circuitry in Synchronous Mode . . . . 7 - 63

Figure 7-34 ASC_P3 Asynchronous Mode Block Diagram . . . . . . . . . . . . . . . . 7 - 64

Figure 7-35 Two-Byte Serial Frames with ASCII ‘at’ . . . . . . . . . . . . . . . . . . . . . 7 - 65

Figure 7-36 Two-Byte Serial Frames with ASCII ‘AT’ . . . . . . . . . . . . . . . . . . . . 7 - 66

Figure 7-37 ASC0 Interrupt Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 72

Figure 7-38 SFRs and Port Pins Associated with the SSC0 . . . . . . . . . . . . . . . 7 - 83

Figure 7-39 Synchronous Serial Channel SSC0 Block Diagram. . . . . . . . . . . . 7 - 84

Figure 7-40 Serial Clock Phase and Polarity Options . . . . . . . . . . . . . . . . . . . . 7 - 86

Figure 7-41 SSC0 Full Duplex Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 87

Figure 7-42 SSC Half Duplex Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 90

Figure 7-43 SSC0 Baud Rate Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 91

Figure 7-44 SSC0 Error Interrupt Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 93

2

Figure 7-45 I

Figure 7-46 Physical Bus Configuration Example . . . . . . . . . . . . . . . . . . . . . . 7 - 102

Figure 7-47 SFRs and Port Pins Associated with the A/D Converter . . . . . . . 7 - 118

Figure 8-1 Clock System in M2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 - 3

Figure 9-1 M2’s Display Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 - 4

Figure 9-2 Priority of Clamp Phase, Screen Background

Figure 10-1 Display Regions and Alignments . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 4

C Bus Line Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 - 100

and Pixel Layer Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 - 11

B-2 Micronas

Page 11

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Figure 10-2 Behavior of Blank Pin for Consecutive Frames

in ‘Meshed’ Regions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 5

Figure 10-3 Priority of Layers in Overlapped Layer Mode. . . . . . . . . . . . . . . . . 10 - 6

Figure 10-4 Priority of Layers in Embedded Layer Mode . . . . . . . . . . . . . . . . . 10 - 9

Figure 10-5 Format of 1-bitplane Bitmap. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 12

Figure 10-6 Format of 2-bitplane Bitmap. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 12

Figure 10-7 Format of 4-bitplane Bitmap. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 12

Figure 10-8 Format of 8-bitplane Bitmap. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 13

Figure 10-9 Overview on SRU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 13

Figure 10-10 2-bit Pixel Format for Use in Frame Buffer . . . . . . . . . . . . . . . . . 10 - 14

Figure 10-11 8-bit Pixel Format for Use in Frame Buffer . . . . . . . . . . . . . . . . . 10 - 14

Figure 10-12 16-bit Pixel Format (4:4:4:2/TTX) for Use in Frame Buffer . . . . . 10 - 15

Figure 10-13 Internally Generated Flash Signals in Different Flash Phases. . . 10 - 16

Figure 10-14 16-bit Pixel Format (5:6:5) for Use in Frame Buffer . . . . . . . . . . . 10 - 16

Figure 10-15 Overview of GA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 17

Figure 10-16 Use of Register Settings to Specify Source Area . . . . . . . . . . . . 10 - 22

Figure 10-17 Use of Register Settings to Specify Destination

and Clipping Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 25

Figure 10-18 Result for a Non-italic Transferred Memory Area

in Frame Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 25

Figure 10-19 Result for a Italic Transferred Memory Area in Frame Buffer . . . 10 - 26

Figure 10-20 Result for an Italic Transferred Memory Area

at D/A Converter Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 26

Figure 10-21 Organization of GAIs in the External SDRAM . . . . . . . . . . . . . . . 10 - 30

Figure 10-22 GAI Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 - 31

Figure 12-1 Block Diagram of Digital Slicer and Acquisition Interface . . . . . . . 12 - 4

Figure 12-2 VBI Buffer: General Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 9

Figure 14-1 H/V - Sync-Timing (Sync-master mode) . . . . . . . . . . . . . . . . . . . 14 - 10

Figure 14-2 VCS -Timing (Sync-master mode) . . . . . . . . . . . . . . . . . . . . . . . . 14 - 10

B-3 Micronas

Page 12

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Preface

M2 is a 16-bit controller based on Infineon’s C16x core with embedded teletext and

graphic controller functions. M2 can be used for a wide range of TV and OSD

applications. This document provides complete reference information on the hardware

of M2.

Organization of this Document

This Users Manual is divided into 14 chapters. It is organized as follows:

• Chapter 1, Overview

Gives a general description of the product and lists the key features.

• Chapter 2, Pin Description

Lists pin locations with associated signals, categorizes signals according to function,

and describes signals.

• Chapter 3, Architectural Overview

Gives an overview on the hardware architecture and explains the dataflow within M2.

• Chapter 4, C16X Microcontroller

Gives a detailed explanation of the 16-bit

• Chapter 5, Interrupt and Trap Functions,

Explains the powerful C166 Interrupt facilities.

• Chapter 6, System Control & Configuration

Describes how to configure and control the complete

Management Unit.

• Chapter 7, Peripherals

Describes the peripherals (serial buses and timers modules) of the micro.

• Chapter 8 & 9, Clock System & Sync System

Describes how clocks & syncs for the display generator are generated.

• Chapter 10 & 11, Display Generator and D/A Converter

Explains the architecture and programming possibilities of the unit which generates

the RGB signals.

• Chapter 12, Acquisition and Slicer

Describes features and functionality of the data caption unit.

• Chapter 13, Register Overview

Summarizes all HW-registers of M2.

• Chapter 14, Electrical Characteristics

Lists all important AC and DC values and the maximum operating conditions of M2.

←C architecture.

←C system and the Power

C-1 Micronas

Page 13

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Related Documentation

For easier understanding of this specification it is recommended to read the

documentation listed in the following table. Moreover it gives an overview of the software

drivers which are available for M2.

Document Name Document Purpose

Appl. Note “Initialization and

Bootstraploader of M2”

System integration support

C-2 Micronas

Page 14

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Overview

1Overview

M2 is designed to provide absolute top performance for a wide spectrum of teletext and

graphic applications in standard and high end TV-sets and VCRs. M2 contains a data

caption unit, a display unit and a high performance Infineon C16x based microcontroller

(so that M2 becomes a one chip TV-controller) an up to level 3.5 teletext decoder and

display processor with enhanced graphic accelerator capabilities. It is not only optimized

for teletext usage but also, due to its extremely efficient architecture, can be used as a

universal graphic engine.

M2 is able to support a wide range of standards like PAL, NTSC or applications like

Teletext, VPS, WSS, Chinatext, Closed Caption and EPG (Electronic Program Guide).

With the support of a huge number of variable character sets and graphic capabilities a

wide range of OSD applications are also open for M2.

A new flexible data caption system enables M2 to slice most data, making the IC an

universal data decoder. The digital slicer concept contains measurement circuitries that

help identify bad signal conditions and therefore support the automatic compensation of

the most common signal disturbances. M2’s enhanced data caption control logic allows

individual programming, which means that every line can carry an individual service to

be sliced and stored in the memory.

The display generation of M2 is based on frame buffer technology. A frame buffer

concept displays information which is individually stored for each pixel, allowing greater

flexibility with screen menus. Proportional fonts, asian characters and even HTML

browsers are just some examples of applications that can now be supported.

Thus, with the M2, the process of generation and display of on-screen graphics is split

up into two independent tasks. The generation of the image in the frame buffer is

supported by a hardware graphics accelerator which frees the CPU from power intensive

address calculations. The graphics accelerator ‘prints’ the characters, at the desired

‘screen’ position, into the frame buffer memory based on a display list provided by the

software.

The second part of the display generator (the screen refresh unit) then reads the frame

buffer according to the programmed display mode and screen refresh rate and converts

the pixel information into an analog RGB signal.

Furthermore, M2 has implemented an RGB-DAC for a maximum color resolution of

state-of-the-art up to 65536 colors, so that the complete graphic functionality is

implemented as a system on chip. The screen resolution is programmable up to SVGA,

to cover today’s and tomorrow’s applications, only limited by the available memory

(64 Mbit) and the maximum pixel clock frequency (50 MHz).

The memory architecture is based on the concept of a unified memory - placing program

code, variables, application data, bitmaps and data captured from the analog TV signal’s

vertical blanking interval (VBI) in the same physical memory. M2’s external bus interface

1 - 3 Micronas

Page 15

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

supports SDRAMs as well as ROMs or FLASH ROMs. The organization of the memory

is linear, so that it is easy to program the chip for graphic purposes.

The SW development environment “MATE” is available to simplify and speed up the

development of the software and displayed information. MATE stands for: M2 Advanced

Tool Environment. Using MATE, two primary goals are achieved: shorter Time-to-Market

and improved SW qualitiy. In detail:

• Re-usability

• Target independent development

• Verification and validation before targeting

• General test concept

• Documentation

• Graphical interface design for non-programmers

• Modular and open tool chain, configurable by customer

MATE uses available C166 microcontroller family standard tools as well as a

dedicated M2 tools.

Overview

1 - 4 Micronas

Page 16

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

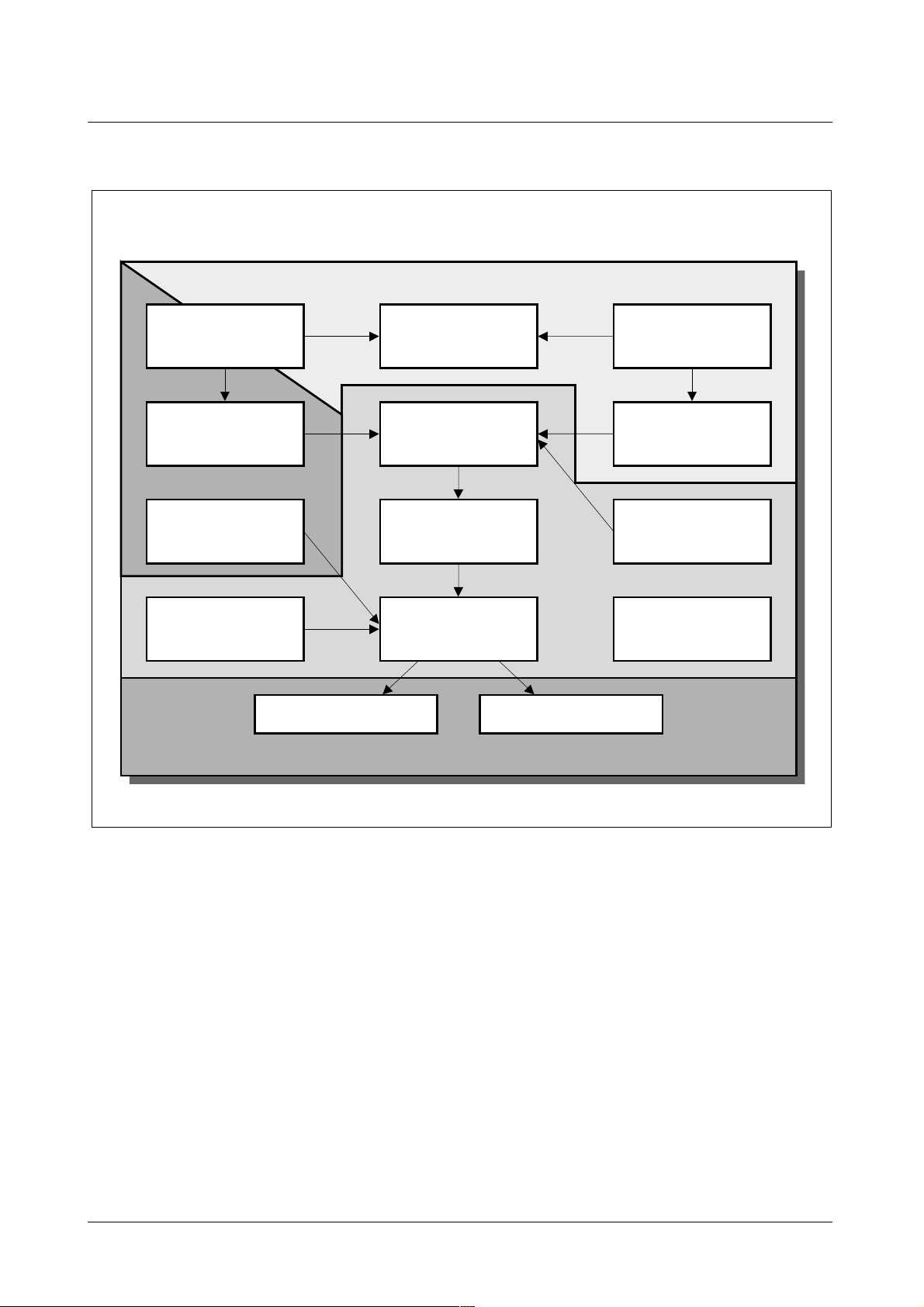

SIE-MATE Tool Concept:

Fast Prototyping on the PC

User Interface

Object Editor

Converter Display data

info M2 formatted data,

Object Library Manager

Dedicated

M2 Libraries

New Tool Generation

User Interface

Simulator

C Compiler

Object Code

C166-Available

Overview

Events and

Action Editor

C Code

Generator

C Sources

RTOS

Embedded System M2

M2 - the 16 Bit MC, TTX/EPG/TeleWeb, High End OSD Engine

Figure 1-1 M2 Tool Flow

Linker/Locator

PC Simulator + EVA Board

Debugging

UEB11114

1 - 5 Micronas

Page 17

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Standard Tool Chain

For the M2 software development (documentation, coding, debugging and test) the

Infineon C166 microcontroller family standard tools can be used: These are ASCII editor,

structogram editor, compiler, assembler, linker. Debugging is supported by low-priced

ROM-Monitor debuggers or the OCDS (On Chip Debug Support) debugger.

M2 Dedicated Tools

Special tools are primarily available for platform independent M2 software development

and secondly to generate data and control code for the M2 graphical user interface (GDI)

without having knowledge of M2 hardware. These are:

• Display Generator Simulator

• Teletext Data Slicer Simulator

• GDI (Graphical Device Interface)

• Teletext Decoder and Display Software for Level 1.5 and Level 2.5

• Mate Display Builder for management, editing, handling and generation of all

necessary data to display OSD’s

• Evaluation Board Simulator to connect a C166 EVA Board to the M2 simulation

Overview

The M2 software is written in ANSI-C to fulfil the platform independent development. The

ported software is code and runtime optimized. The layers of the modular architecture

are separated by application program interfaces which ensure independent handling of

the modules.

1 - 6 Micronas

Page 18

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Overview

Teletext Decoder with Embedded 16-bit Controller

M2

Version 2.1 CMOS

1.1 Features

General

• Level 1.5, 2.5, 3.5 WST Display Compatible

• Fast External Bus Interface for SDRAM (Up to

8 MByte) and ROM or Flash-ROM (Up to 4 MByte)

• Embedded General Purpose 16 Bit CPU (Also used

as TV-System Controller, C16x Compatible)

• Display Generation Based on Pixel Memory

• Program Code also Executable From External

SDRAM

• Embedded Refresh Controller for External SDRAM

• Enhanced Programmable Low Power Modes

• Single 6 MHz Crystal Oscillator

• Multinorm H/V-Display Synchronization in Master or Slave Mode

• Free Programmable Pixel Clock from 10 MHz to 50 MHz

• Pixel Clock Independent from CPU Clock

⌠ 6 Bits RGB-DACs On-Chip

• 3

• Supply Voltage 2.5 and 3.3 V

• P-MQFP-128 Package

P-MQFP-128-2

Microcontroller Features

• 16-bit C166-CPU Kernel (C16x Compatible)

• 60 ns Instruction Cycle Time

• 2 KBytes Dual Ported IRAM

• 2 KBytes XRAM On-chip

• General Purpose Timer Units (GPT1 and GPT2).

• Asynchronous/Synchronous Serial Interface (ASC0) with IrDA Support. Full-duplex

Asynchronous Up To 2 MBaud or Half-duplex Synchronous up to 4.1 MBaud.

Type Package

SDA 6000 P-MQFP-128-2

1 - 7 Micronas

Page 19

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Overview

• High-speed Synchronous Serial Interface (SSC). Full- and Half-duplex synchronous

up to 16.5 Mbaud

2

• 3 Independent, HW-supported Multi Master/Slave I

C Channels at 400 Kbit/s

• 16-Bit Watchdog Timer (WDT)

• Real Time Clock (RTC)

• On Chip Debug Support (OCDS)

• 4-Channel 8-bit A/D Converter

• 42 Multiple Purpose Ports

• 8 External Interrupts

• 33 Interrupt Nodes

Display Features

• OSD size from 0 to 2046 (0 to 1023) pixels in horizontal (vertical) direction

• Frame Buffer Based Display

• 2 HW Display Layers

• Support of Double Page Level 2.5 TTX in 100 Hz Systems

• Support of Transparency for both Layers Pixel by Pixel

• User Programmable Pixel Frequency from 10.0 MHz to 50 MHz

• Up to 65536 Displayable Colors in one Frame

• DMA Functionality

• Graphic Accelerator Functions (Draw Lines, Draw and Fill Rectangle, etc.)

• 1, 2, 4 or 8-bit Bitmaps (up to 256 out of 4096 colors)

• 12 bit/16 bit RGB Mode for Display of up to 65535 Colors

• HW-support for Proportional Characters

• HW-support for Italic Characters

• User Definable Character Fonts

• Fast Blanking and Contrast Reduction Output

Acquisition Features

• Two Independent Data Slicers (One Multistandard Slicer + one WSS-only Slicer)

• Parallel Multi-norm Slicing (TTX, VPS, WSS, CC, G+)

• Four Different Framing Codes Available

• Data Caption only Limited by available Memory

• Programmable VBI-buffer

• Full Channel Data Slicing Supported

• Fully Digital Signal Processing

• Noise Measurement and Controlled Noise Compensation

• Attenuation Measurement and Compensation

• Group Delay Measurement and Compensation

• Exact Decoding of Echo Disturbed Signals

1 - 8 Micronas

Page 20

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

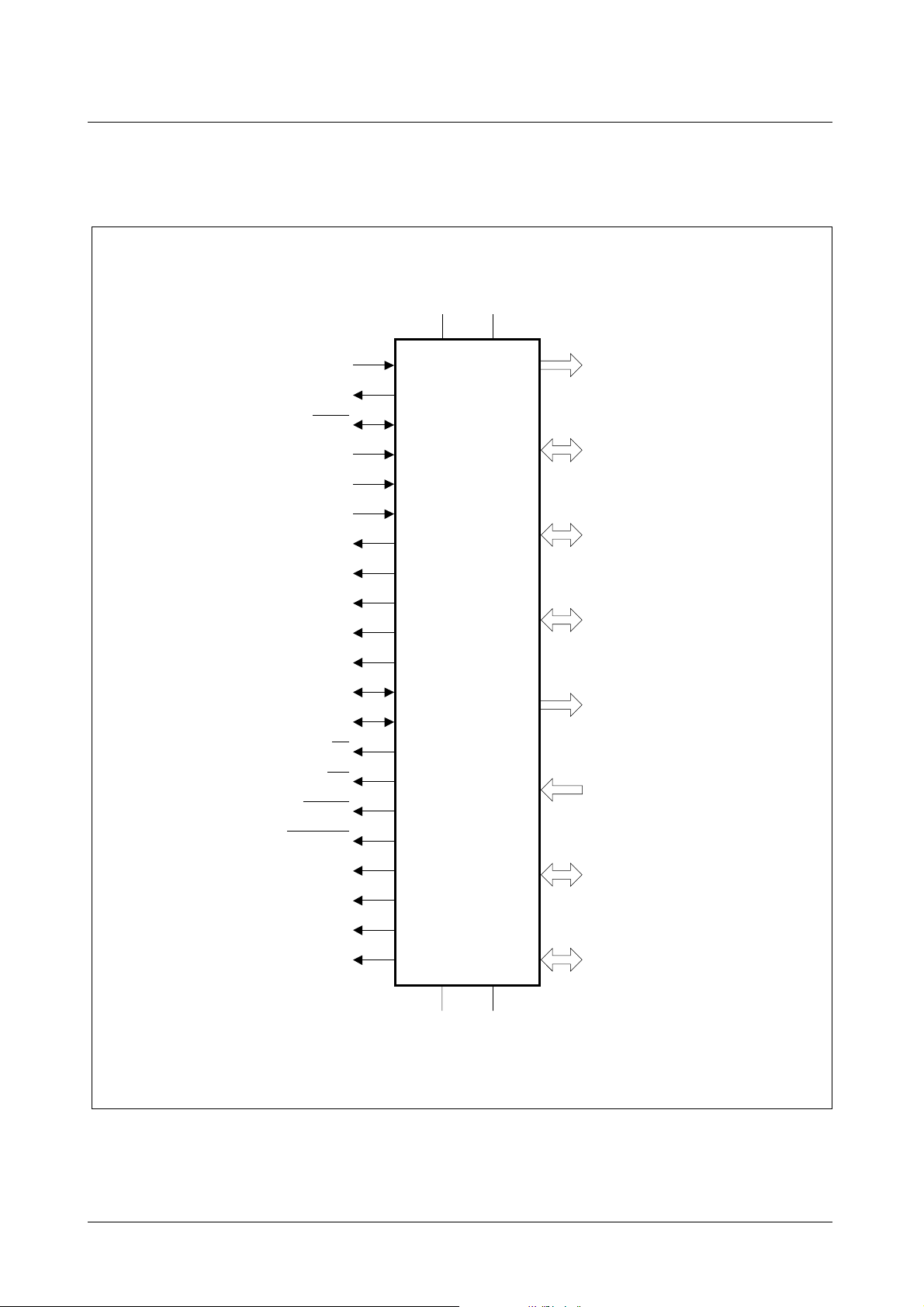

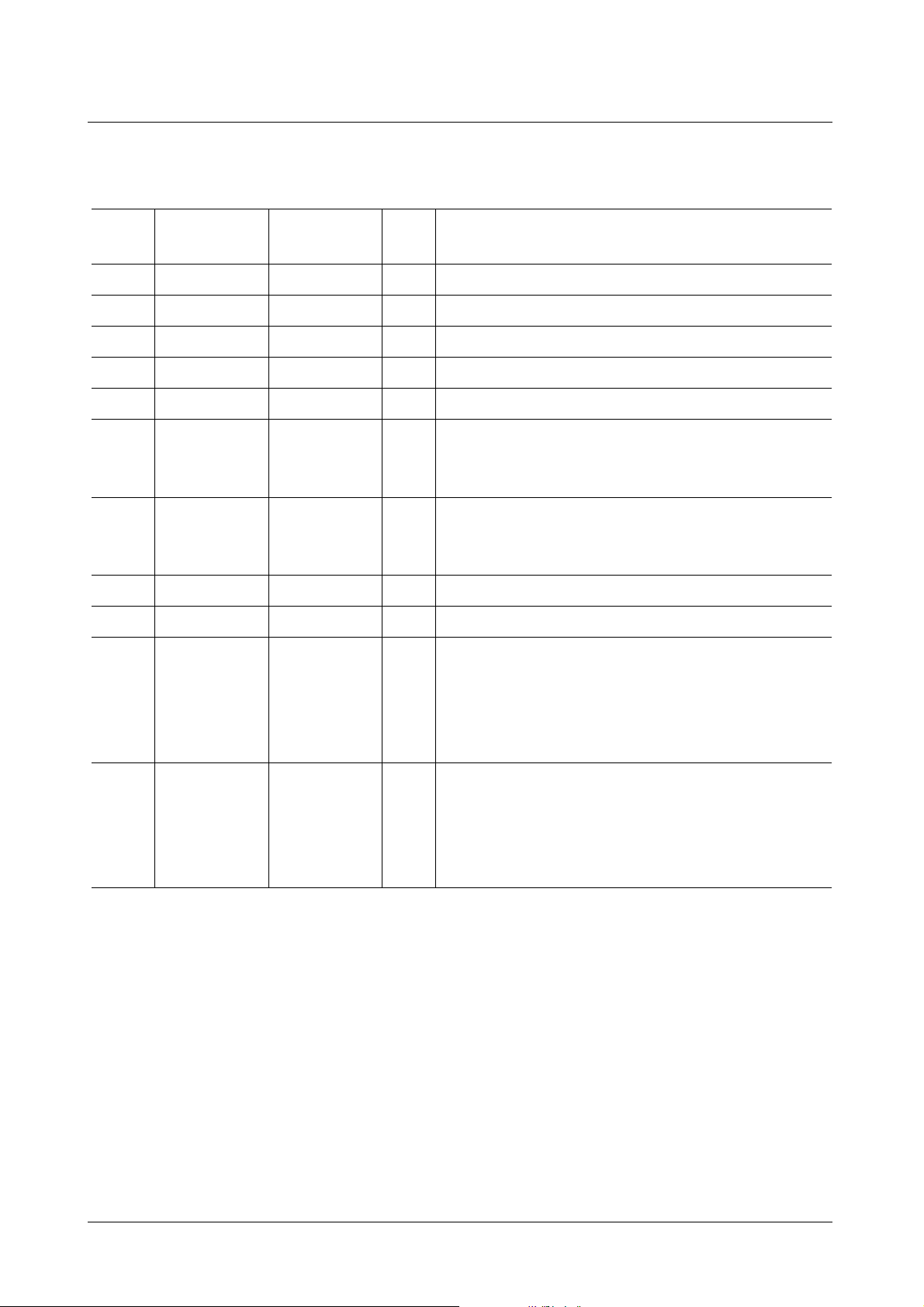

1.2 Logic Symbol

XTAL1

XTAL2

RSTIN

CVBS1A

CVBS1B

CVBS2

Overview

V

R

G

SS

V

DD(3.3 V)

Address

16 Bit

Data

16 Bit

Port 2

8 Bit

B

COR

BLANK

HSYNC

VSYNC

RD

WR

CSROM

CSSDRAM

MEMCLK

UDQM

LDQM

CLKEN

Port 3

15 Bit

M2

Port 4

6 Bit

Port 5

6 Bit

Port 6

7 Bit

JTAG

4 Bit

V

SS

V

DD(2.5 V)

UEL11115

Figure 1-2 Logic Symbol

1 - 9 Micronas

Page 21

Pin Description

Page 22

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

2 Pin Descriptions

Pin Descriptions

2 - 3 Micronas

Page 23

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

2.1 Pin Diagram (top view)

P-MQFP-128-2

DD25-2

P3.10

P3.11

P3.12

P3.13

P3.15

P5.14

P5.15

P6.0

P6.1

91

92

95

96

93

94

97 64

P6.2

98

P6.3

99 62

P6.4

100 61

P6.5

101 60

P6.6

VSYNC

HSYNC

COR/RSTOUT

BLANK/CORBLA

V

DD33-8

V

SS33-8

XTAL1

XTAL2

V

V

V

V

CVBS2

V

V

CVBS1B

CVBS1A

V

V

TMODE A4

102 59

103 58

104 57

105 56

106 55

107 54

108

109 52

110 51

SSA-1

111 50

DDA-1

112 49

R

113 48

G

114 47

B

115 46

SSA-2

116 45

DDA-2

117 44

118

SSA-3

119 42

DDA-3

120 41

121 40

122 39

SSA-4

123 38

DDA-4

124 37

P5.0

125 36

P5.1

126 35

P5.2

127 34

P5.3 A3

128

90

89

88

V

87

SS33-7

DD33-7

SS25-2

V

V

85

86

V

84

P3.9

83

P3.8

82

P3.7

81

P-MQFP-128-2

M2

P3.5

P3.6

79

80

P3.3

P3.4

78

77

P3.2

76

P3.0

P3.1

75

74

D11

RSTIN

72

73

D3

71

D4

70

Pin Descriptions

SS33-6

DD33-6

D12

D10

D2

V

V

68

67

66

65

63

53

43

33

69

D5

D9

D13

V

DD33-5

V

SS33-5

D1

D6

D8

D14

D0

D7

V

DD33-4

V

SS33-4

D15

WR

LDQM

UDQM

RD

CSROM

CLKEN

CSSDRAM

MEMCLK

V

DD33-3

V

SS33-3

A15/CAS

A14/RAS

A13

A0

A1

A2

2345678

1

TDI

TCK

TMS

P2.8

TDO

P2.9

P2.10

9

101112131415161718

SS33-1

P2.15

P2.14

V

DD33-1

V

P2.12

P2.11

P2.13

P4.3/A19

P4.2/A18

P4.4/A20

P4.5/CS3

20212223242526272829303132

19

A5

A9

A8

A6

SS25-1

DD25-1

V

V

P4.1/A17

A7

P4.0/A16

A10

A11

A12

SS33-2

V

V

DD33-2

UEP11116

Figure 2-1 Pin Configuration

2 - 4 Micronas

Page 24

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Pin Descriptions

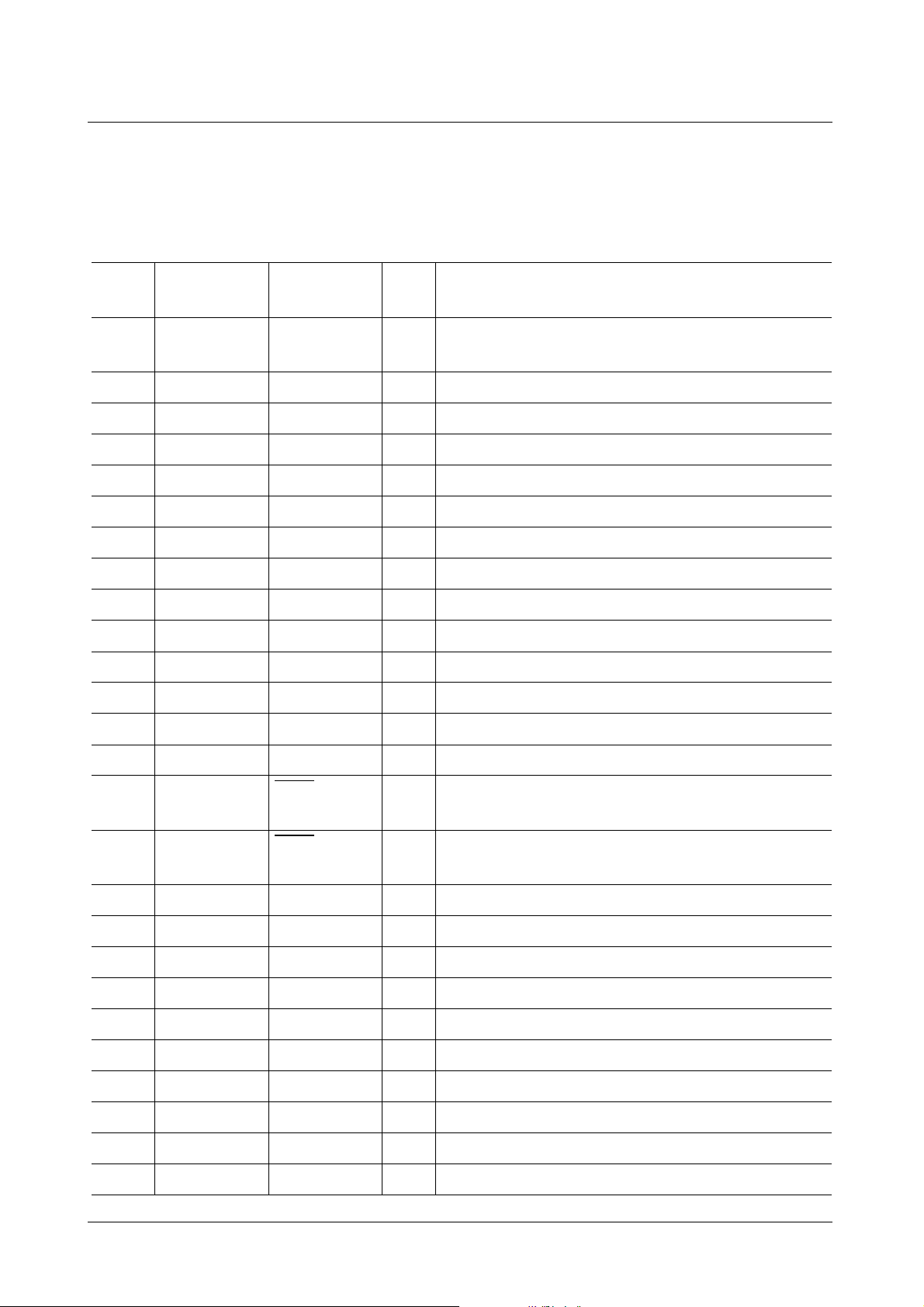

2.2 Pin Definitions and Functions

Table 2-1 Pin Definition and Functions

Pin

No.

37 A0 R0/C0 O Address bit (All addresses are word

36 A1 R1/C1 O Address bit/SDRAM address bit

35 A2 R2/C2 O Address bit/SDRAM address bit

34 A3 R3/C3 O Address bit/SDRAM address bit

33 A4 R4/C4 O Address bit/SDRAM address bit

27 A5 R5/C5 O Address bit/SDRAM address bit

26 A6 R6/C6 O Address bit/SDRAM address bit

24 A7 R7/C7 O Address bit/SDRAM address bit

Pin Name Second

Function

Dir. Function

addresses)/SDRAM Address bit

23 A8 R8 O Address bit/SDRAM address bit

25 A9 R9 O Address bit/SDRAM address bit

28 A10 R10 O Address bit/SDRAM address bit

29 A11 R11 O Address bit/SDRAM address bit

30 A12 R12 O Address bit/SDRAM address bit

38 A13 R13 O Address bit/SDRAM address bit

39 A14 RAS

40 A15 CAS

55 D0 – I/O Data bit

59 D1 – I/O Data bit

65 D2 – I/O Data bit

71 D3 – I/O Data bit

70 D4 – I/O Data bit

O Address bit/

Row address strobe for SDRAM access

O Address bit/

Column address strobe for SDRAM access

64 D5 – I/O Data bit

58 D6 – I/O Data bit

54 D7 – I/O Data bit

57 D8 – I/O Data bit

63 D9 – I/O Data bit

2 - 5 Micronas

Page 25

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Table 2-1 Pin Definition and Functions (cont’d)

Pin

No.

67 D10 – I/O Data bit

72 D11 – I/O Data bit

66 D12 – I/O Data bit

62 D13 – I/O Data bit

56 D14 – I/O Data bit

51 D15 – I/O Data bit

47 RD

46 CSROM

44 CSSDRAM

Pin Name Second

Function

– O External memory read strobe for ROM. RD is

– O Chip select signal for ROM device

– O Chip select signal for SDRAM device

Dir. Function

activated for every external instruction or data

read access.

Pin Descriptions

43 MEMCLK – O Clock for SDRAM

45 CLKEN – O Enable for memory clock

50 WR

22 P4.0 A16 O General purpose output port/Address bit

19 P4.1 A17 O General purpose output port/Address bit

18 P4.2 A18 O General purpose output port/Address bit

17 P4.3 A19 O General purpose output port/Address bit

16 P4.4 A20 O General purpose output port/Address bit

15 P4.5 CS3 O General purpose output port/Chip select

49 LDQM – O Write disable for low byte

48 UDQM – O Write disable for high byte

109 XTAL2 – O Output of the oscillator amplifier circuit

108 XTAL1 – I Input of the oscillator amplifier circuit

73 RSTIN

– O Memory write strobe

signal for second external static memory

– I Reset input pin

121 CVBS1A – I CVBS signal inputs for full service data slicing

120 CVBS1B – I Ground for CVBS1A (differential input)

117 CVBS2 – I CVBS signal inputs for WSS data slicing

112 R – O Analog output for red channel

2 - 6 Micronas

Page 26

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Pin Descriptions

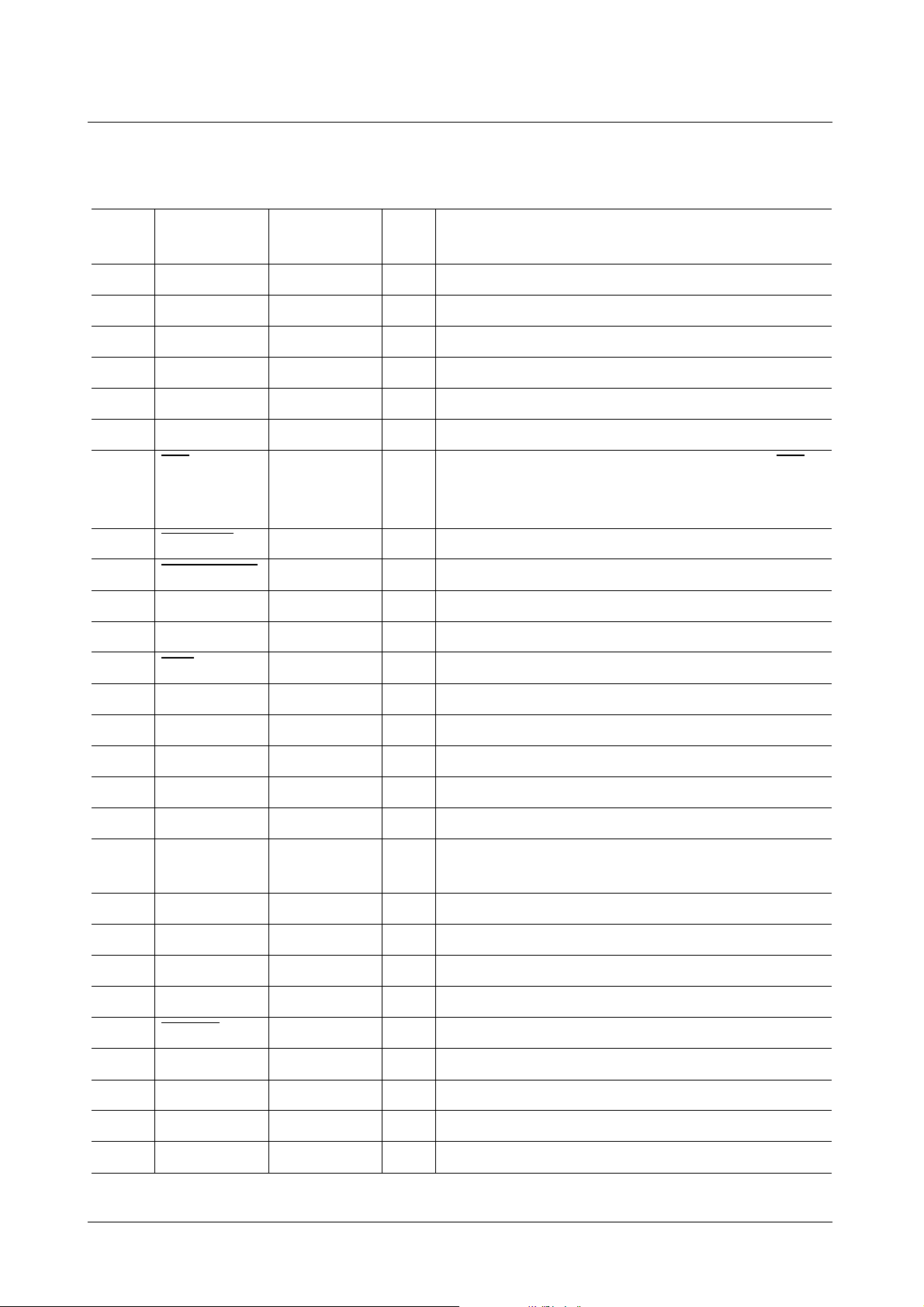

Table 2-1 Pin Definition and Functions (cont’d)

Pin

No.

Pin Name Second

Function

Dir. Function

113 G – O Analog output for green channel

114 B – O Analog output for blue channel

104 COR RSTOUT O Output for contrast reduction/Reset output

105 BLANK CORBLA O Fast blanking signal/Three-level signal for

contrast reduction + fast blanking

103 HSYNC – I/O Horizontal sync In/output

102 VSYNC VCS I/O Vertical sync In/output/Composite sync output

5 P2.8 EX0IN I/O General purpose I/O port/External interrupt 0

6 P2.9 EX1IN I/O General purpose I/O port/External interrupt 1

7 P2.10 EX2IN I/O General purpose I/O port/External interrupt 2

8 P2.11 EX3IN I/O General purpose I/O port/External interrupt 3

9 P2.12 EX4IN I/O General purpose I/O port/External interrupt 4

10 P2.13 EX5IN I/O General purpose I/O port/External interrupt 5

11 P2.14 EX6IN I/O General purpose I/O port/External interrupt 6

12 P2.15 EX7IN I/O General purpose I/O port/External interrupt 7

2

74 P3.0 SCL0 I/O General purpose I/O port/I

75 P3.1 SDA0 I/O General purpose I/O port/I

C Bus clock line 0

2

C Bus data line 0

76 P3.2 CAPIN I/O General purpose I/O port/GPT2 register

CAPREL

77 P3.3 T3OUT I/O General purpose I/O port/GPT1 timer T3

toggle

78 P3.4 T3EUD I/O General purpose I/O port/GPT1 timer T3 ext.

up/down

79 P3.5 T4IN I/O General purpose I/O port/GPT1 timer T4 input

for count/gate/reload/capture

80 P3.6 T3IN I/O General purpose I/O port/GPT1 timer T3

count/gate input

81 P3.7 T2IN I/O General purpose I/O port/GPT1 timer T2 input

for count/gate/reload/capture

82 P3.8 MRST I/O General purpose I/O port/SSC master-

receiver/slave-transmit I/O

2 - 7 Micronas

Page 27

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

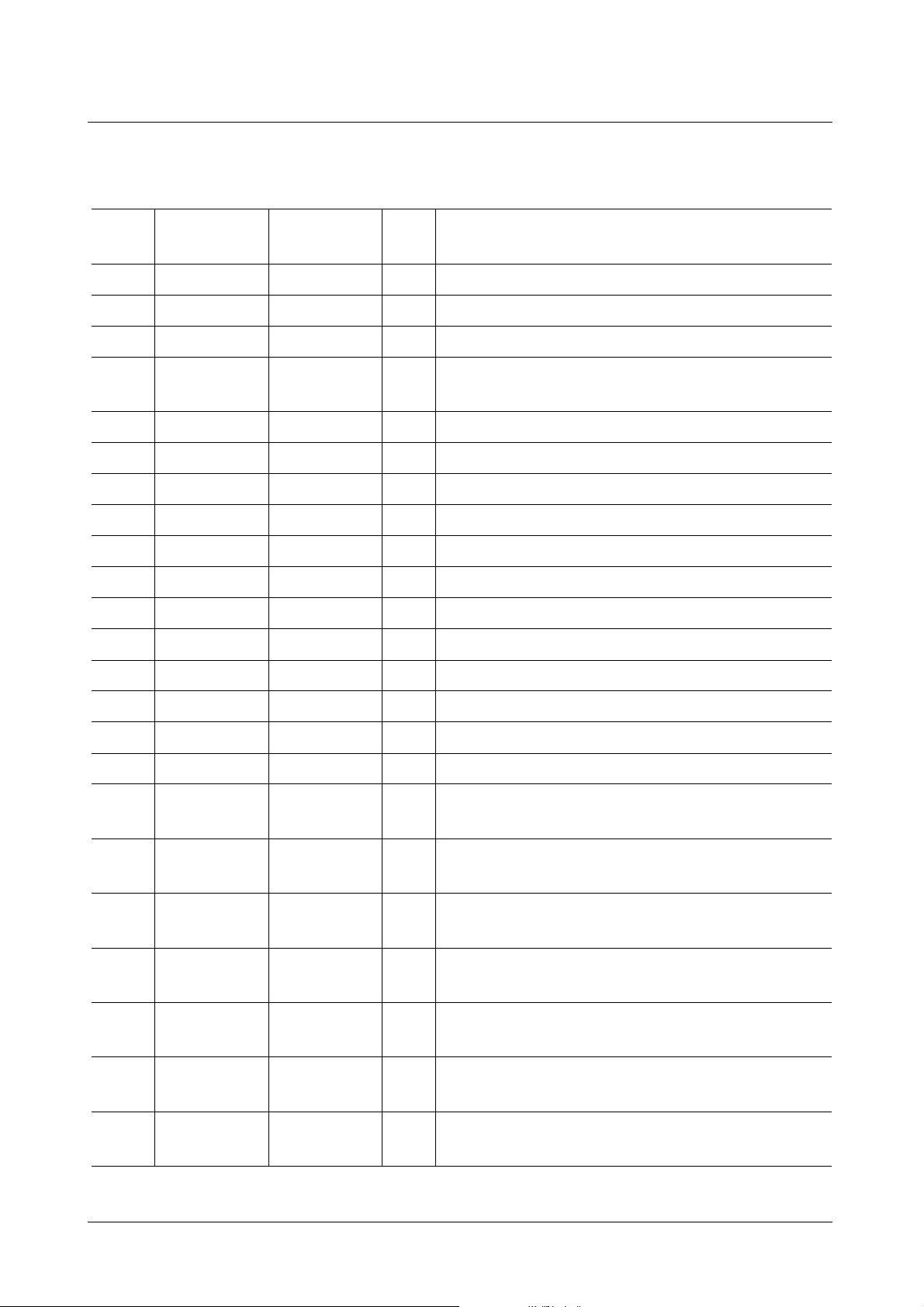

Pin Descriptions

Table 2-1 Pin Definition and Functions (cont’d)

Pin

No.

Pin Name Second

Function

Dir. Function

83 P3.9 MTSR I/O General purpose I/O port/SSC master-

transmit/slave-receiver O/I

88 P3.10 TxD0 I/O General purpose I/O port/ASC0 clock/data

output

89 P3.11 RxD0 I/O General purpose I/O port/ASC0 data input

(asynchronous) or I/O (synchronous.)

90 P3.12 – I/O General purpose I/O port

91 P3.13 SCLK I/O General purpose I/O port/SSC master clock

output/slave clock input

92 P3.15 – I/O General purpose I/O port

124 P5.0 AN.0 I General purpose I/O port/Analog input for

A/D-converter

125 P5.1 AN.1 I General purpose I/O port/Analog input for

A/D-converter

126 P5.2 AN.2 I General purpose I/O port/Analog input for

A/D-converter

127 P5.3 AN.3 I General purpose I/O port/Analog input for

A/D-converter

93 P5.14 T4EUD I/O General purpose I/O port/GPT1 timer T4

ext.up/down ctrl. input

94 P5.15 T2EUD I/O General purpose I/O port/GPT1 timer T2

ext.up/down ctrl. input

95 P6.0 TRIG_IN I/O General purpose I/O port/Trigger input-signal

for ‘On Chip Debug System’ (OCDS)

96 P6.1 TRIG_OUT I/O General purpose I/O port/Trigger output-

signal for ‘On Chip Debug System’ (OCDS)

97 P6.2 – I/O General purpose I/O port

2

98 P6.3 SCL1 I/O General purpose I/O port/I

99 P6.4 SDA1 I/O General purpose I/O port/I

C bus clock line 1

2

C bus data line 1

100 P6.5 – I/O General purpose I/O port

2

101 P6.6 SDA2 I/O General purpose I/O port/I

C bus data line 2

1TCK – I Clock for JTAG interface

3TDI – I Data input for JTAG interface

2 - 8 Micronas

Page 28

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Pin Descriptions

Table 2-1 Pin Definition and Functions (cont’d)

Pin

No.

Pin Name Second

Function

Dir. Function

4TDO – O Data output for JTAG interface

2TMS – I Control signal for JTAG interface

128 TMODE – I Testmode pin

110 V

111

115,

SSA-1

V

DDA-1

V

SSA2-4

– S Analog ground

– S Analog power (for PLL and DAC) (2.5 V)

– S Analog ground

1)

118,

122

116,

V

DDA2-4

– S Analog power (for ADCs) (2.5 V)

119,

123

20, 86

21, 87

V

SS25 1-2

V

DD25 1-2

– S Digital ground (for digital core)

– S Digital power (for digital core) (2.5 V)

13, 31,

V

SS33 1-8

– S Digital ground for pads

41, 52,

60, 68,

84,

107

14, 32,

V

DD33 1-8

– S Digital power (for pads) (3.3 V)

42, 53,

61, 69,

85,

106

1)

(Must be kept to “0” in application.)

2 - 9 Micronas

Page 29

Architectural Overview

Page 30

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

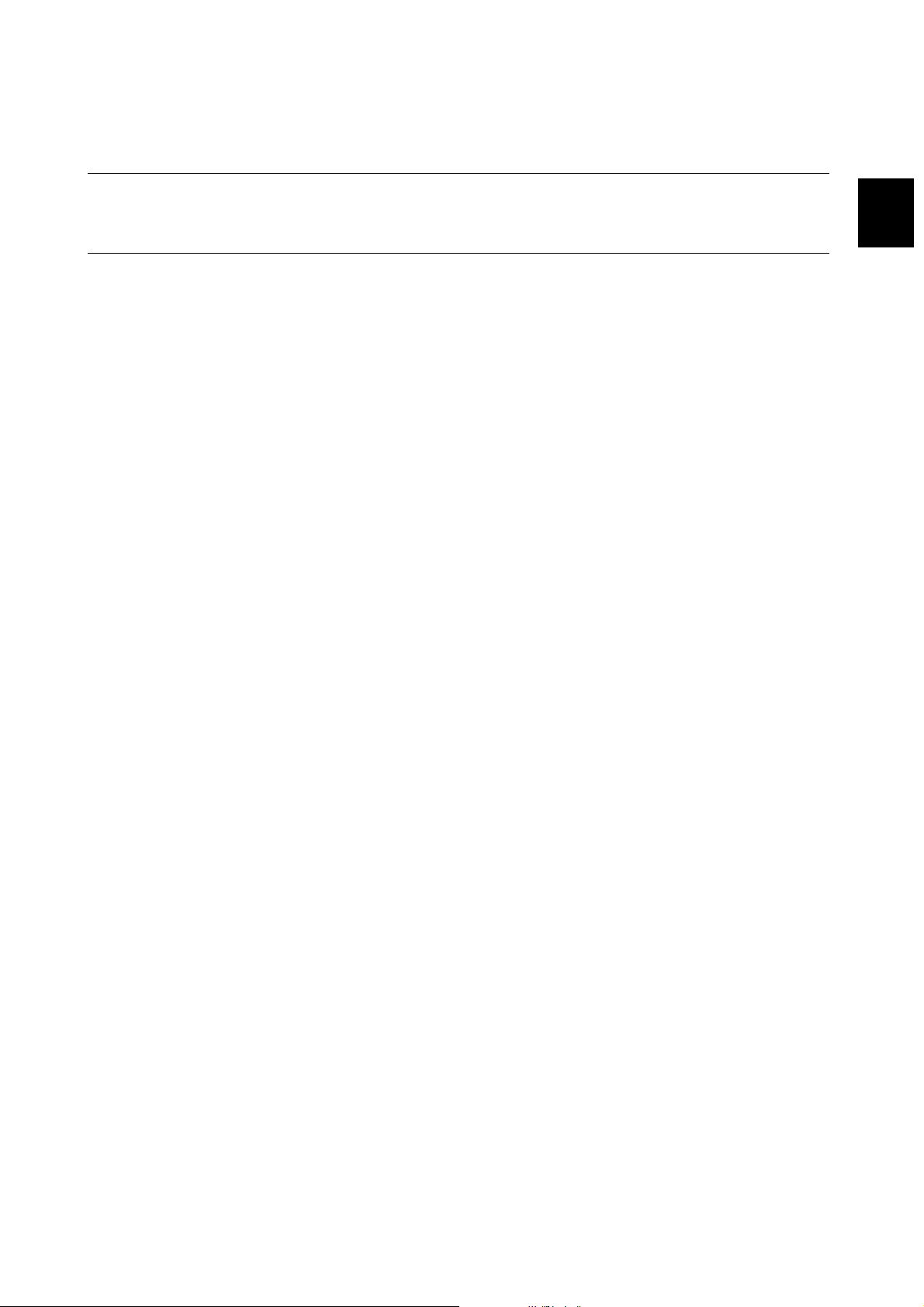

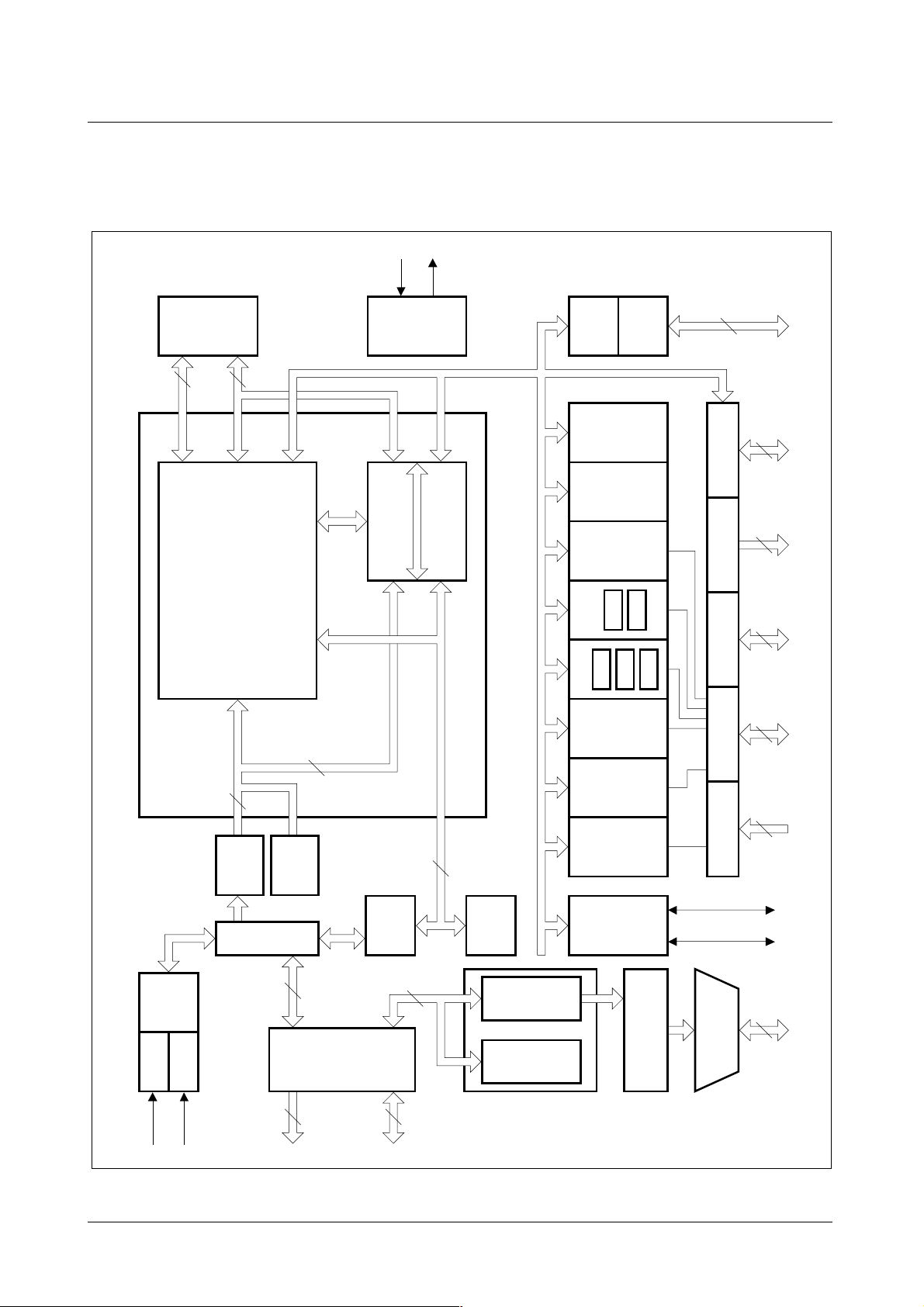

3 Architectural Overview

XTAL

OSC

(6 MHz)

PEC

Interrupt Controller

16

Data

RAM

Internal

2 Kbyte

16

DataInstr./Data32

C166

CPU-Core

36 nodes (8 ext.)

Architectural Overview

4

OCDS

GPT2

JTAG

RTC Watchdog

C

2

Ι

T5

T6

7

Port 6

UEB10716

ACQ

Slicer1

CVBS1

CVBS2

Slicer2

-Cache

Ι

AMI

Boot

ROM

16

16...21

16

External

Addr.

Bus

Interface

D-Cache

16

16

Data

16 X-BUS Instr./Data

XRAM

2 Kbyte

SRUGA

T2

GPT1

4-

T3

T4

SPI

ASC SSC

USART

7-bit

ADC

Channel

D-Sync

FIFO

Port 5 Port 3 Port 2 Port 4

DAC

3 x 6 Bit

6 15 8 8

HV

3

Figure 3-1 M2 Top Level Block Diagram

3 - 3 Micronas

Page 31

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

The architecture of M2 comprises of a 16-bit microcontroller which is derived from the

well known Infineon Technologies C16x controller family. Due to the core philosophy of

M2, the architecture of the CPU core is the same as described in other Infineon

Technologies C16x derivatives.

The CPU, with its peripherals, can be used on one hand to perform all TV controlling

tasks, and on the other hand to process the data, sliced by the slicer, and the acquisition

unit according to the TTX standard. Furthermore it is used to generate an “instruction list”

for the graphic accelerator which supports the CPU by generating the display.

M2 has integrated two digital slicers for two independent CVBS signals. One slicer is

used to capture the data (e.g. Teletext or EPG) from the main channel, the other slicer

can be used to slice the WSS information from a different channel, which is helpful e.g.

to support PIP applications in 16:9 TVs. Both slicers separate the data from the analog

signal and perform the bit synchronization and framing code selection before the data is

stored in a programmable VBI buffer in the external RAM. Capturing and storing the raw

data in the RAM does not need any CPU power.

M2’s display concept has improved in comparison to the common known state of the art

Teletext-ICs. The display concept is based on a pixel orientated attribute definition

instead of the former character orientated attribute definition.

Architectural Overview

For the processing of this new pixel based attribute definition the display generator

architecture is divided in two subblocks: the graphic accelerator (GA) and the screen

refresh unit (SRU).

The graphic accelerator is used to modify the frame buffer. From an abstract point of

view, the graphic accelerator is a DMA which is optimized for OSD functionality, so e.g.

bitmaps can be copied to the frame buffer. The graphic accelerator is used to draw

rectangles, parallelograms, horizontal, vertical and diagonal lines. The user does not

need to access the graphic accelerator directly, thanks to an easy to handle SW-GDI

function which is available with the M2 hardware.

The DMA functionality of the display generator (DG) supports the pixel transfer between

any address of entire external memory. The teletext and graphic capabilities can be used

simultaneously, so that M2 can combine teletext information with e.g. background

images and advanced high resolution OSD graphics.

M2 uses the frame buffer located in external memory so every bitmap can be placed at

any location on the screen. The contents of the frame buffer does not have to be set up

in real time. The duration of the set up of the screen depends on the contents of the

displayed information.

M2 supports two hardware display layers. To refresh the screen the M2 reads and mixes

two independent pixel sources simultaneously.

Different formats of the pixels which are part of different applications (e.g. Teletext

formats, 12-bit RGB or 16-bit RGB values) can be stored in the same frame buffer at the

same time.

3 - 4 Micronas

Page 32

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

Architectural Overview

The screen refresh unit is used to read the frame buffer pixel by pixel in real time and to

process the transparency and RGB data. A color look up table (CLUT) can be used to

get the RGB data of the current pixel. Afterwards the RGB data is transferred to the D/A

converter. The blank signal and contrast reduction signal (COR) is also processed for

each pixel by the SRU and transferred to the corresponding output pins.

The pixel, line and field frequencies are widely programmable so that the sync system

can be used from low end 50 Hz to high end 100 HZ TV applications as well as for any

other standard.

The on chip clock system provides the M2 with its basic clock signals. Independent

clock domains are provided for the embedded controller, the bus interface and the

display system. The pixel clock can vary between 10 MHz and 50 MHz.

Due to the unified memory architecture of M2, a new bus concept is implemented. An

arbiter handles the bus requests from the different request sources. These are:

• Slicer 1 requests (normally used as a TTX slicer)

• Slicer 2 requests (used as a WSS slicer)

• Graphic accelerator requests

• Screen refresh unit requests

• Data requests from the CPU via XBUS

• Instruction requests via the CPU program bus

For exploiting the full computational power of the controller core the code of time critical

routines can be stored in one bank of the external SDRAM separated from all display

information (frame buffer, character set etc.). An instruction cache (I-CACHE) is used

for buffering instruction words in order to minimize the probability of wait states to occur

when the microcontroller is interfering with the display generator (DG) for access rights

to the external memory devices. The data cache (D-CACHE) serves for operand reads

and writes via the XBUS from/to external memory devices.

The external bus interface (EBI) features interleaved access cycles to one or two static

external memory devices (ROM, Flash-ROM or SRAM) with a total maximum size of

4 MByte and one PC100 compliant (Intel standard) SDRAM device (16 MBit organized

as 2 memory banks or 64 MBit organized as 4 memory banks).

2

For TV controlling tasks M2 provides three serial interfaces (I

C, ASC, SSC), two general

purpose timers, (GPT1, GPT2), a real time clock (RTC), a watch dog timer (WDT), an A/

D converter and eight external interrupts.

3 - 5 Micronas

Page 33

C16X Microcontroller

Page 34

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

4 C16X Microcontroller

C16X Microcontroller

4 - 3 Micronas

Page 35

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

C16X Microcontroller

4.1 Overview

M2’s microcontroller and its peripherals are based on a Cell-Based Core (CBC) which is

compatible to the well known C166 architecture.

In M2, the CPU and its peripherals are generally clocked with 33.33 MHz which results

in an instruction cycle time of 60 ns. The implementation of the microcontroller within M2

deviates from other known C16x derivates since the controller’s XBUS is not used as the

external bus. All external access cycles of the microcontroller, the display generator and

the acquisition unit are performed via a high performance time interlocking SDRAM bus.

The external bus interface (EBI) manages the arbitration procedure for access cycles to

the external synchronous DRAM in parallel to an external static memory (ROM or

FLASH; for more details refer to Chapter 4.4).

Due to the realtime critical bus bandwidth requirements of the display generator,

unpredictable wait-states for the controller may occur. These wait-states do not destroy

the overall average system performance, because they are mostly buffered by the CPU

related instruction and data buffers. Nevertheless they can influence, for example, the

worst disconnection response time.

Emulation is now performed by an on-chip debug module which can be accessed by a

JTAG interface.

The following microcontroller peripherals are implemented:

• 2 KByte IRAM (System RAM)

• 2 KByte XRAM (XBUS located)

• 32 Interrupt Nodes

• General Purpose Timer Units (GPT1 and GPT2)

• Real Time Clock (RTC)

• Asynchronous/Synchronous Serial Interface (ASC0)

• High-Speed Synchronous Serial Interface (SSC)

2

C Bus Interface (I2C)

• I

• 4-Channel 8-bit A/D Converter (ADC)

• Watchdog Timer (WDT)

• On-Chip Debug Support Module (OCDS)

• 42 Multiple Purpose Ports

Central Processing Unit

The CPU executes the C166 instruction set (with the extensions of the C167 products).

Its main features are the following:

• 4-stage pipeline (Fetch, Decode, Execute and Write-Back).

• 16

⌠ 16-bit General Purpose Registers

• 16-bit Arithmetic and Logic Unit

• Barrel shifter

• Bit processing capability

4 - 4 Micronas

Page 36

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

• Hardware support for multiply and divide instructions

Internal RAM (IRAM)

The internal dual-port RAM is the physical support for the General Purpose Registers,

the system stack and the PEC pointers. Due to its close connections with the CPU, the

internal RAM provides fast access to these resources. As the GPR bank can be mapped

anywhere in the internal RAM through a base pointer (Context Pointer CP), fast context

switching is allowed. The internal RAM is mapped in the memory space of the CPU and

can be used also to store user variables or code.

Interrupt Controller

Up to 32 interrupt sources can be managed by the Interrupt Controller through a multiple

priority system which provides the user with the ability to customize the interrupt

handling.

The interrupt system of M2 includes a Peripheral Event Controller (PEC). This processor

performs single-cycle interrupt-driven byte or word transfers between any two locations

in the entire memory space of M2.

C16X Microcontroller

In M2, the PEC functionalities are extended by the External PEC which allows an

external device to trigger a PEC transfer while providing the source and destination

pointers. New features also include the packet transfer mode and the channel link mode.

Besides user interrupts, the Interrupt Controller provides mechanisms to process

exceptions or error conditions, so-called “hardware traps”, that arise during program

execution.

System Control Unit

M2’s System Control Unit (CSCU) is used to control system specific tasks such as reset

control or power management within an on-chip system built around the core. The power

management features of the CSCU provide effective means to realize standby

conditions for the system with an optimum balance between power reduction, peripheral

operation and system functionality. The CSCU also provides an interface to the Clock

Generation Unit (CGU) and is able to control the operation of the Real Time Clock (RTC).

The CSCU includes the following functions:

• System configuration control

• Reset sequence control

• External interrupt and frequency output control

• Watchdog timer module

• General XBUS peripherals control

• Power management additional to the standard Idle and Power Down modes

• Control interface for Clock Generation Unit

• Identification register block for chip and CSCU identification

4 - 5 Micronas

Page 37

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

OCDS

The On-Chip Debug System allows the detection of specific events during user program

execution through software and hardware breakpoints. An additional communication

module allows communication between the OCDS and an external debugger, through a

standard JTAG port. This communication is performed in parallel to program execution.

C16X Microcontroller

4 - 6 Micronas

Page 38

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

C16X Microcontroller

4.2 Memory Organization

In normal operation mode the memory space of the CPU is configured in a “Von

Neumann” architecture. This means that code and data are accessed within the same

memory areas, i. e. external memory, internal controller memory (IRAM), the address

2

areas for integrated XBUS peripherals (I

special function register areas (SFR, ESFR) are mapped into one common address

space of 16 MBytes. This address space is arranged as 256 segments of 64 KBytes

each and each segment is again subdivided into four data pages of 16 KBytes each.

All internal memory areas and the address space of the integrated XBUS peripherals are

mapped to segment 0. Code and data may be stored in any part of the memory, except

for the SFR blocks, which can not be used for instructions. Despite this equivalence of

code and data, proper partitioning is necessary to make use of the full bandwidth of the

memory system.

The integrated C16x controller communicates via 2 busses with the memory interface.

In normal operation mode access to segments 00H to 41H (excluding internal memory

areas) is mapped to the read only program memory bus (PMBUS), whereas access to

segments 42

to FFH is mapped to the XBUS. In bootstrap loader mode (BSLMode)

H

instruction fetches to external memory areas via PMBUS are redirected to the internal

bootstrap loader ROM (BSLROM). Operand (data) accesses remain unchanged.

C, internal XBUS memory (XRAM)) and the

The PMBUS is connected to the instruction cache (ICACHE) which operates as readahead FIFO (see Figure 4-1). The data cache (DCACHE) which is connected to the

XBUS holds a maximum of 4 words corresponding to one SDRAM burst. Accesses of

DCACHE, ICACHE and the acquisition unit (ACQ) are joined within the acquisition

memory interface (AMI) and directed to the external bus interface (EBI). Redirections via

ESFR REDIR (instruction fetches only) and ESFR REDIR1 are done in the AMI (see

Chapter 4.5.1). The EBI joins AMI and display generator (DG) accesses and reads data

from or writes data to the external static and dynamic memory devices (see Chapter 4.5

for further information). In case of cache miss wait states are inserted until the data is

ready. IRAM, XRAM and the special function register areas can be accessed without

wait states.

4 - 7 Micronas

Page 39

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

External M2

Memory

DG

SDRAM

Boot ROM

ROM1

ROM2

EBI

AMI

ICACHE

DCACHE

ACQ

C16X Microcontroller

PMBUS

C16X

XBUS

UED11214

Figure 4-1 M2 Memory Path Block Diagram

All memory locations are byte and word readable. The internal memories (IRAM, XRAM)

and the external dynamic memory (SDRAM) are byte and word writable, but external

static memory is only word writable. Bytes are stored at even or odd byte addresses.

Words are stored in ascending memory locations, with the low byte at an even byte

address being followed by the high byte at the next odd byte address. Double words

(instructions only) are stored in ascending memory locations as two subsequent words.

Single bits are always stored in the specific bit position at a word address. Bit position 0

is the least significant bit of the byte at an even byte address and bit position 15 is the

most significant bit of the byte at the next odd byte address. Bit addressing is supported

by a part of the special function registers, a part of the IRAM and the general purpose

registers (GPRs).

4 - 8 Micronas

Page 40

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

C16X Microcontroller

Figure 4-2 Storage of Words, Byte and Bits in a Byte Organized Memory

Note: Byte units forming a single word or a double word must always be stored within

the same physical (internal, external, ROM, RAM) and organizational (page,

segment) memory area.

4 - 9 Micronas

Page 41

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

C16X Microcontroller

4.3 On-Chip Microcontroller RAM and SFR Area

The IRAM/SFR area is located within data page 3, and provides access to 2 KByte of

dual ported IRAM and two 512 Byte blocks of Special Function Registers (SFRs).

The internal RAM (IRAM) serves several purposes:

• System Stack (Programmable Size)

• General Purpose Register Banks (GPRs)

• Source and Destination Pointers for the Peripheral Event Controller (PEC)

• Variable and other data storage, or

• Code storage

Segment 0

64 Kbytes

RAM / SFR Area

2

Ι

C

XRAM

00’FFFF

00’F000

00’E800

00’E000

H

H

H

Page 3

H

RAM / SFR Area

4 Kbytes

SFR Area

00’FFFF

00’FE00

H

H

00’C000

00’8000

00’4000

H

H

H

Page 2

Page 1

Page 0

2 Kbyte

IRAM

Reserved

00’FA00

00’F600

00’F200

H

H

H

ESFR Area

00’0000

H

00’F000

UED11213

H

Figure 4-3 Internal RAM Areas and SFR Areas

Note: The upper 256 bytes of SFR area, ESFR area and IRAM are bit-addressable (see

shaded blocks in Figure 4-3).

4 - 10 Micronas

Page 42

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

C16X Microcontroller

Code accesses are always made through even byte addresses. The highest possible

code storage location in the IRAM is either 00’FDFE

00’FDFC

for double word instructions. The respective location must contain a branch

H

for single word instructions, or

H

instruction (unconditional), because sequential boundary crossings from IRAM to the

SFR area are not supported and cause erroneous results.

Any word and byte data in the IRAM can be accessed via indirect or long 16-bit

addressing modes if the selected DPP register points to page 3. Any word data access

is made through an even byte address. The highest possible word data storage location

in the IRAM is 00’FDFE

. For PEC data transfers, the IRAM can be accessed

H

independent of the contents of the DPP registers via the PEC source and destination

pointers.

The upper 256 Byte of the IRAM (00’FD00

through 00’FDFFH) and the GPRs of the

H

current bank are provided for single bit storage, and thus they are bit addressable.

4.3.1 System Stack

The system stack may be defined within the IRAM. The size of the system stack is

controlled by bit field STKSZ in the SYSCON register (see table below).

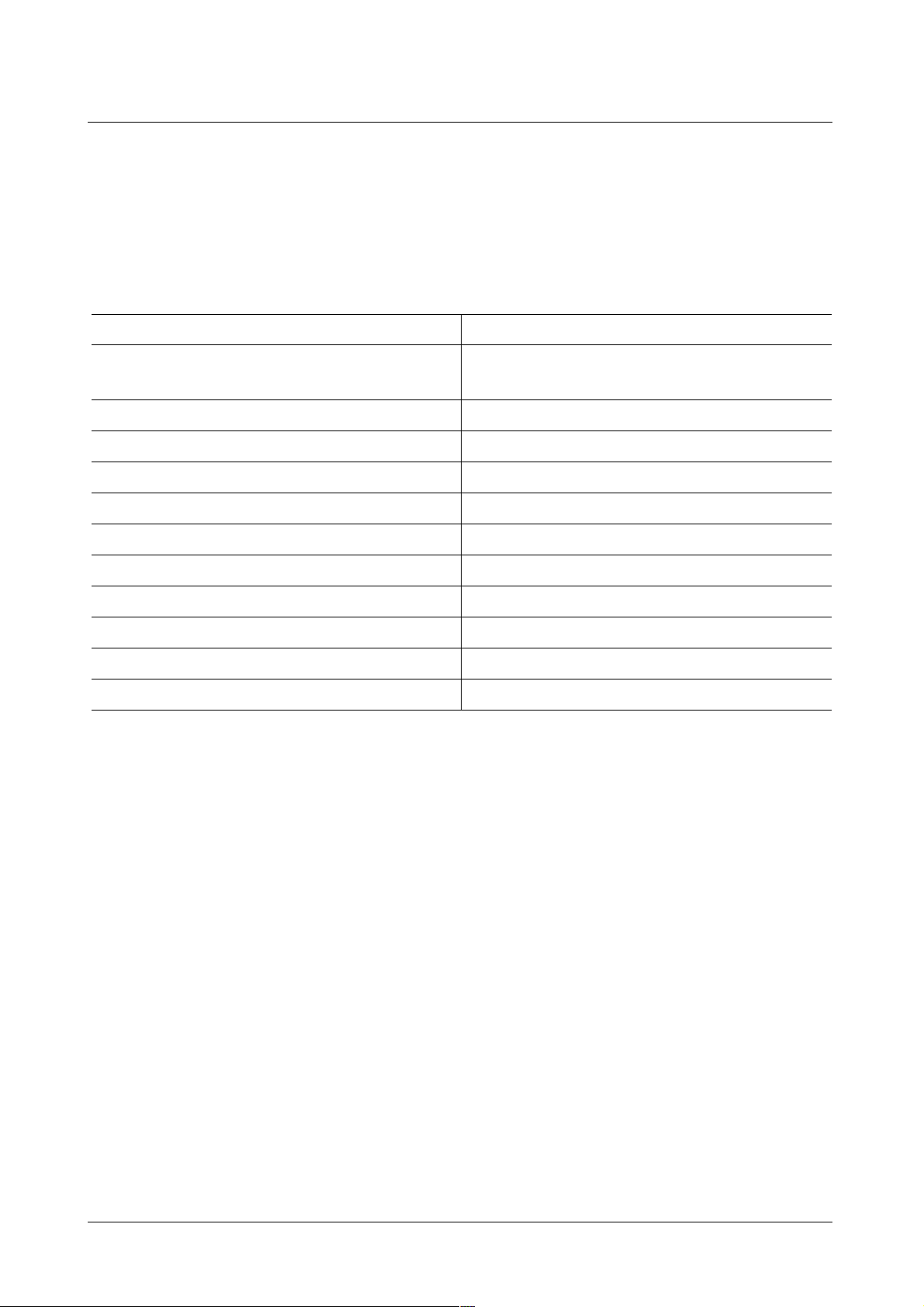

<STKSZ> Stack Size

Internal RAM Addresses (Words)

(Words)

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

B

B

B

B

B

B

B

B

256 00’FBFEH… 00’FA00H (Default after Reset)

128 00’FBFEH… 00’FB00

64 00’FBFEH… 00’FB80

32 00’FBFEH… 00’FBC0

512 00’FBFEH… 00’F800

H

H

H

H

– Reserved. Do not use this combination.

– Reserved. Do not use this combination.

1024 00’FDFEH… 00’F600H (Note: No circular stack)

For all system stack operations, the IRAM is accessed via the Stack Pointer (SP)

register. The stack grows downward from higher to lower RAM address locations. Only

word accesses are supported by the system stack. A stack overflow (STKOV) and a

stack underflow (STKUN) register are provided to control the lower and upper limits of

the selected stack area. These two stack boundary registers can be used not only for

protection against data destruction, but also to implement flushing and filling a circular

stack with a hardware supported system stack (except for option ‘111’).

4 - 11 Micronas

Page 43

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

C16X Microcontroller

4.3.2 General Purpose Registers

The General Purpose Registers (GPRs) use a block of 16 consecutive words within the

IRAM. The Context Pointer (CP) register determines the base address of the currently

active register bank. This register bank may consist of up to 16 word GPRs (R0, R1, …,

R15) and/or of up to 16 byte GPRs (RL0, RH0, …, RL7, RH7). The sixteen byte GPRs

are mapped onto the first eight word GPRs (see Table 4-1).

In contrast to the system stack, a register bank grows from lower towards higher address

locations and occupies a maximum space of 32 Byte. The GPRs are accessed via short

2-, 4- or 8-bit addressing modes using the Context Pointer (CP) register as a base

address (independent of the current DPP register contents). In addition, each bit in the

currently active register bank can be accessed individually.

Table 4-1 Mapping of General Purpose Registers to RAM Addresses

Internal RAM

Address

<CP> + 1E

<CP> + 1C

<CP> + 1A

H

H

H

Byte Registers Word Register

– R15

– R14

– R13

<CP> + 18

<CP> + 16

<CP> + 14

<CP> + 12

<CP> + 10

<CP> + 0E

<CP> + 0C

<CP> + 0A

<CP> + 08

<CP> + 06

<CP> + 04

<CP> + 02

<CP> + 00

H

H

H

H

H

H

H

H

H

H

H

H

H

– R12

– R11

– R10

– R9

– R8

RH7 RL7 R7

RH6 RL6 R6

RH5 RL5 R5

RH4 RL4 R4

RH3 RL3 R3

RH2 RL2 R2

RH1 RL1 R1

RH0 RL0 R0

M2 supports fast register bank (context) switching. Multiple register banks can physically

exist within the IRAM at the same time. However, only the register bank selected by the

Context Pointer register (CP) is active at a given time. Selecting a new active register

bank is simply done by updating the CP register. A particular Switch Context (SCXT)

instruction performs register bank switching and automatically saves the previous

4 - 12 Micronas

Page 44

SDA 6000 PRELIMINARY DATA SHEET

Version 2.1

C16X Microcontroller