Page 1

Silan

1

2

Semiconductors

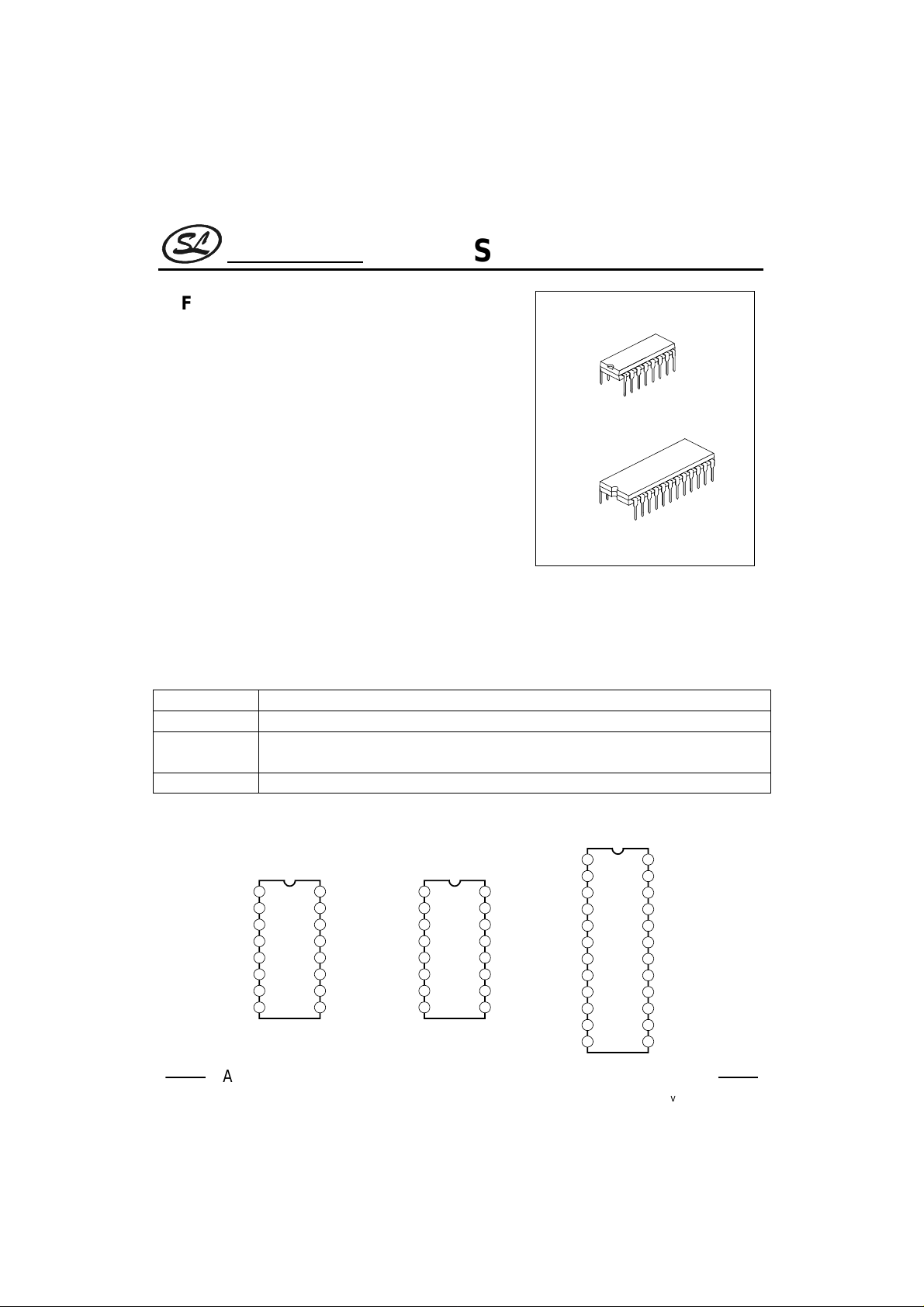

SC9149A/SC9150A

INFRARED REMOTE CONTROL

RECEIVER

DESCRIPTION

The SC9149A/SC9150A are CMOS LSIs designed for use on the

infrared remote control receiver, and when this LSI is used in

combination with SC9148A for transmitter, the remote control

system can be constructed. The SC9149A is DIPcapable of controlling 10 functions, while the SC9150A is DIPtype and is capable of controlling 18 functions.

FEATURES

* Able to output parallel multiple keying signals sent from the

transmitter (The SC9149A is able to output parallel up to 5

functions, while the SC9150A is able to output parallel up to 6

functions.)

* Output for single pulse, hold pulse and cyclic pulse are provided.

(cyclic pulse is available only for SC9150A)

* A single terminal type oscillator by means of CR is provided.

* Code detection circuit provided for code check with the

transmitter prevents inter-ferences from various types of

machines and apparatus.

ORDERING INFORMATION

SC9149A

SC9149AL

SC9149AHN

SC9150A

Advanced version DIP-16 package

Advanced Dependent cyclic (toggle) Outputs

Inversed Rxin input

Output format same as “L”, except that when HP1 or HP2 is active, it will clear CP1.

Advanced version DIP-24 package

PIN CONFIGURATION

GND

1

Rx IN

2

HP1

3

HP2

4

HP3

5

HP4

6

HP5

7

8

SP5 SP4

SC9149A

16

15

14

13

12

11

10

9

VDD

OSC

CODE 2

CODE 3

SP1

SP2

SP3

GND

Rx IN

HP1

HP2

HP3

HP4

HP5

CP2 CP1

6typeandis

1

2

3

4

SC9149AL/

9149AHN

5

6

7

8

16

15

14

13

12

11

10

VDD

OSC

CODE 2

CODE 3

SP1

SP2

SP3

9

DIP-16

SC9149A

4

DIP-24

SC9150A

GND

1

Rx IN

2

HP1

3

HP2

4

HP3

5

HP4

6

SC9150A

HP5

7

8

HP6

9

CP2

10

CP1

11

SP10

12 13

SP9 SP8

VDD

24

OSC

23

CODE 1

22

CODE 2

21

SP1

20

SP2

19

SP3

18

17

SP4

16

SP5

15

SP6

14

SP7

HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD

Rev: 1.0 2000.12.31

1

Page 2

Silan

Semiconductors

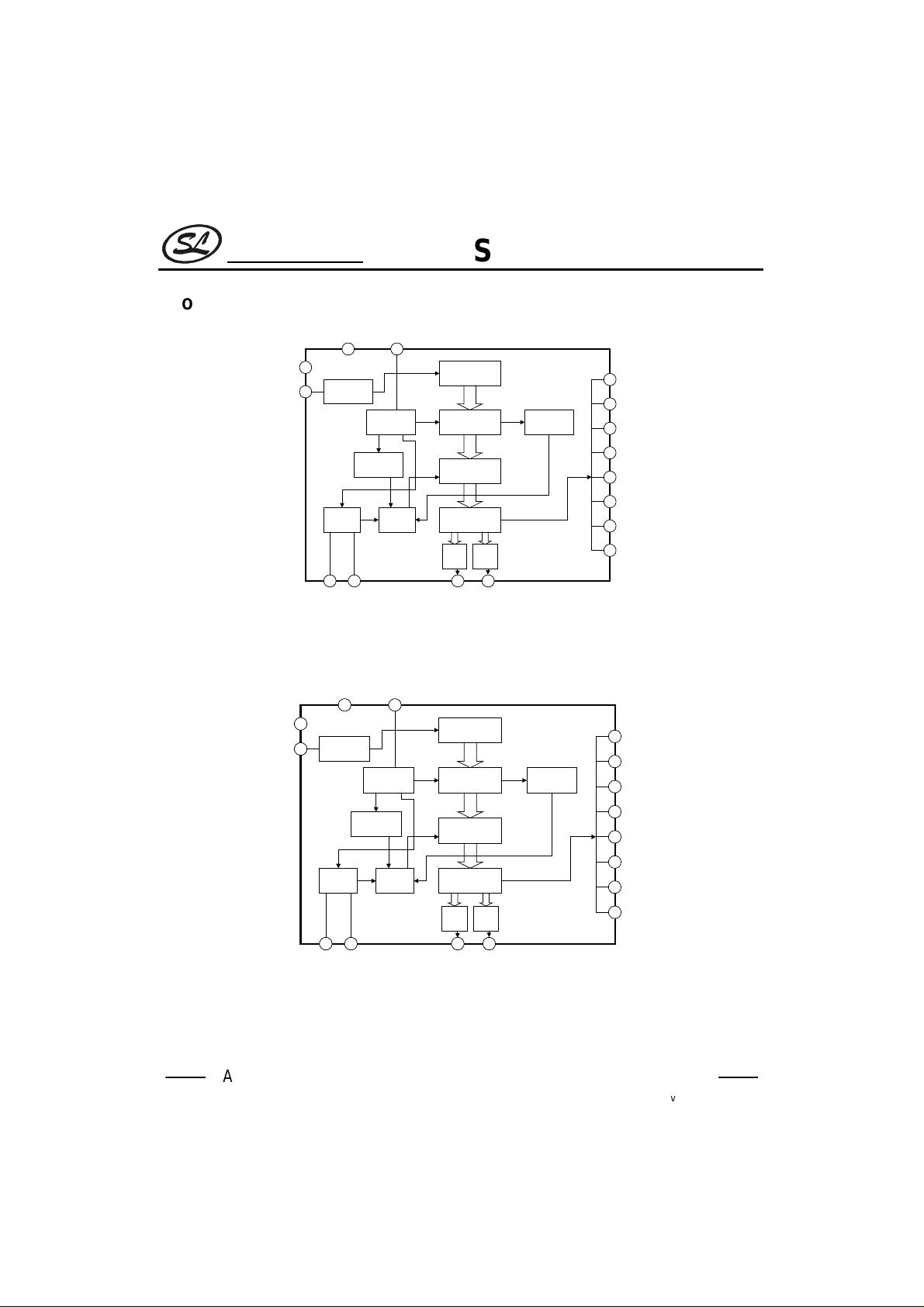

BLOCK DIAGRAM

SC9149A/SC9150A

GND Rx IN

16

VDD

OSC

OSC

15

Code

Check

CODE 2 CODE 3 SP1 SP2

Input shift

register

Input Pulse

counter

Detection

Error

21

Up Counter

Shift register Data Check

Latch Circuit

Output Buffer

F/F F/F

11121314

HP1

3

HP2

4

HP3

5

HP4

6

HP5

7

8

SP5

9

SP4

10

SP3

SC9149A Block Diagram

GND Rx IN

16

VDD

OSC

15

OSC

Code

Check

CODE 2 CODE 3 SP1 SP2

Input shift

register

Input Pulse

counter

Detection

Error

21

Up Counter

Shift register Data Check

Latch Circuit

Output Buffer

F/F F/F

11121314

HP1

3

4

HP2

5

HP3

6

HP4

7

HP5

8

CP2

9

CP1

10

SP3

SC9149AL/9149AHN Block Diagram

HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD

Rev: 1.0 2000.12.31

2

Page 3

Silan

Semiconductors

VDD

OSC

CODE 1

CODE 2

24

23

22

21

GND Rx IN

OSC

Code

Check

21

Input shift

register

Input Pulse

counter

Error

Detection

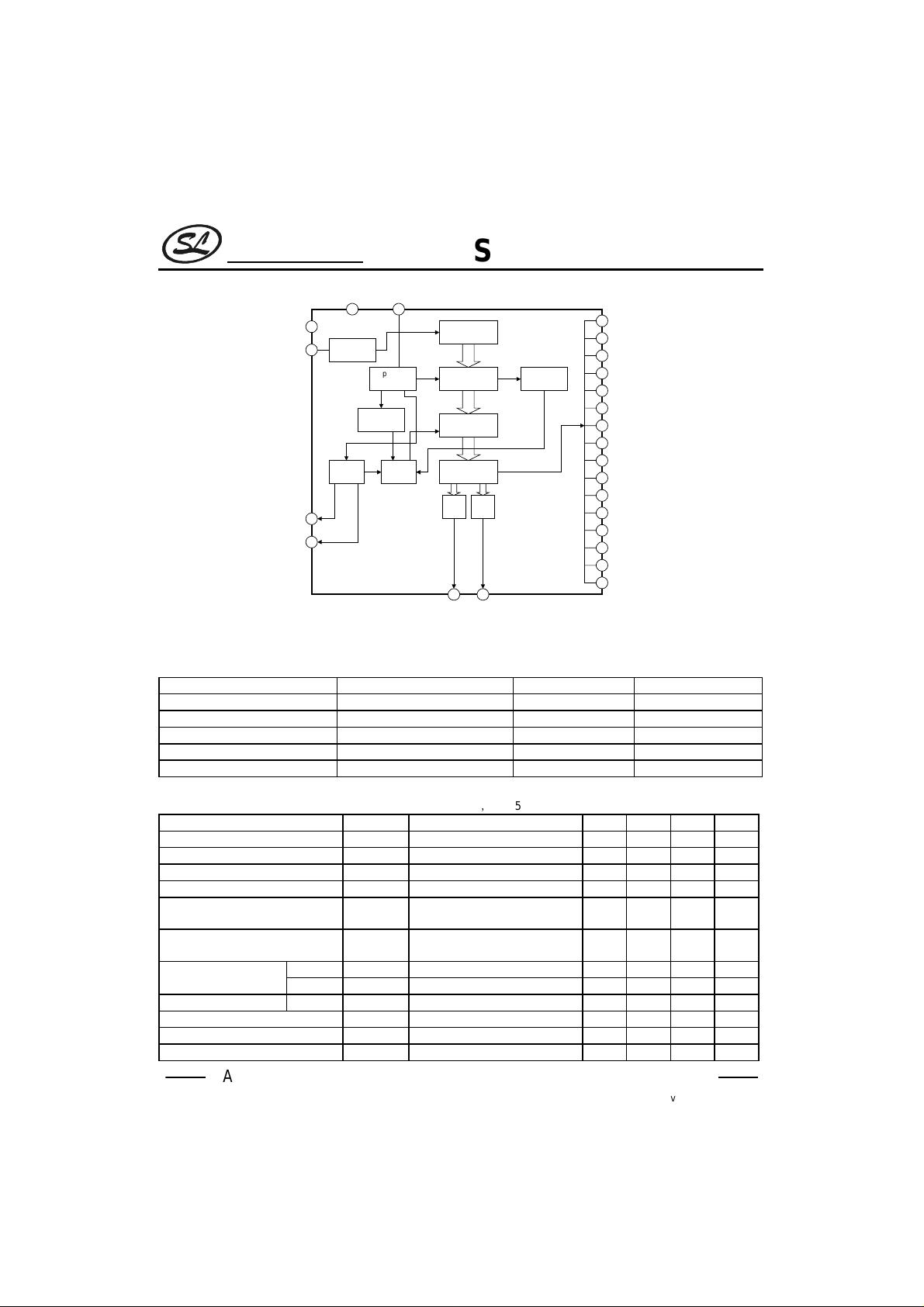

SC9150A Block Diagram

ABSOLUTE MAXIMUM RATINGS

Characteristic Symbol Value Unit

Supply Voltage V

Input / Output Voltage VIN,V

PowerDissipation P

Operating Temperature Tamb -20 ~ +75

Storage Temperature Tstg -55 ~ +125

(Ta=25°C)

DD

D

ELECTRICAL CHARACTERISTICS

Parameter Symbol Test Conditions Min Typ Max Unit

Operating Supply Voltage V

Operating Supply Current I

Standard OSC Frequency Sfosc 38 kHz

Oscillation Frequency fosc 27 57 kHz

Variance Of Oscillation Frequency

By VDD

Variance Of Oscillation Frequency

By Temperature

Output Current

“H” Level I

“L” Level I

Input Current “H” Level I

Pull-Up Resistor Rup CODE Terminal 10 20 40

Input Circuit Threshold Voltage V

Hysteresis Width V

∆V

∆T

(Tamb=25°CVDD=5.0V,Unless otherwise specified)

Ta=25 ~ 75°C

DD

Output without Load 1.0 mA

DD

fosc V

DD

Ta=-30~+75°C

fosc

All output, VOH=4.0V -1.0 mA

OH

All Output, VOL=1V 1.0 mA

OL

CODE Terminal, VIH=5.0V -1.0 1.0

IH

Rx Terminal 2.0 2.5 3.0 V

IN

Rx Terminal 0.8 V

HIS

HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD

SC9149A/SC9150A

HP1

Up Counter

Shift register Data Check

Latch Circuit

Output Buffer

F/F F/F

20 19

SP1 SP2

OUT

Vss-0.3V ~ VDD+0.3V V

=4.5~5.5V -5 5 %

3

3

HP2

4

HP3

5

6

HP4

7

HP5

8

HP6

9

CP2

10

CP1

SP10

11

SP9

12

SP8

13

14

SP7

15

SP6

16

SP5

17

SP4

18

SP3

0~6.0 V

200 mW

°C

°C

4.5 5.5 V

-5 5 %

Rev: 1.0 2000.12.31

µA

kΩ

Page 4

Silan

Semiconductors

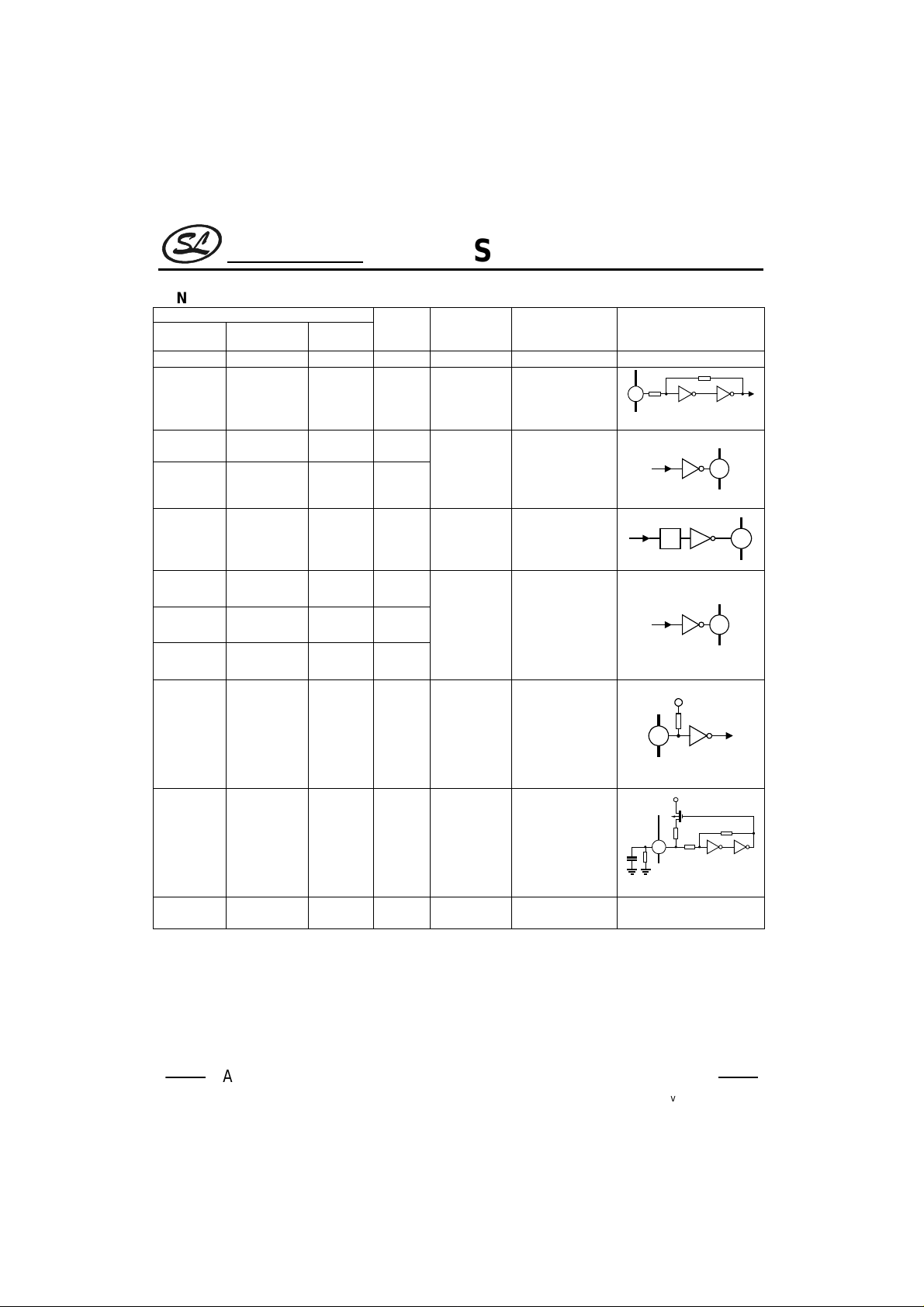

PIN DESCRIPTION

Pin No.

SC9149A

111GNDGND

222RxIN

3~7 3~7 --

-- -- 3~8

-- 9~8 9~10

-- 12~10 --

8~12 -- --

-- -- 11~20

13,14 13~14 21~22 CODE Code input

15 15 23 OSC

16 16 24 V

SC9149AL

/9149AHN

SC9150A

Symbol Terminal

Receiving

signal input

HP1

~HP5

HP1

~HP6

CP1

~CP2

SP1

~SP3

SP1

~SP5

SP1

~SP10

DD

Continuous

signal

output

Cyclic

signal

output

Single-shot

signal

output

Timing

oscillation

Power

supply

SC9149A/SC9150A

Function

/operation

Instruction signal

with carrier

signal eliminated

is input.

As long as

receiving signal

is input, this

output is held at

“H” level

When receiving

signal is input,

output is

reversed.

When receiving

signal is input,

output is placed

at “H” level only

for a fixed

time.(about

107msec)

Transmitter code

is compared with

a code set at

this terminal and

if they agree

each other, input

is accepted.

A resistor and a

capacitor are

parallel

connected

between this

terminal and

GND.

Input/output

configuration

F/F

V

DD

Built-in pull-up resistor.

V

DD

HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD

Rev: 1.0 2000.12.31

4

Page 5

Silan

Semiconductors

FUNCTIONAL DESCRIPTION

1. OSCILLATION CIRCUIT

Timing with transmitter signal and internal operating clock are all decided by this oscillator.

osc

RC

The oscillator has been so far constructed through a combination of a linear amplifier by means of CMOS

inverter in IC and 455kHz ceramic resonator ;however , when SC9149A/SC9150A series are used , a stable

oscillator can be constructed by parallel connecting C and R between the oscillator and GND by a single terminal

oscillator . Oscillation frequency is about 38KHz±5 kHz at R=39kΩ and C=1000pF. (Refer to SCILLATION

Frequency Characteristic below )

Oscillator frequency vs. resistor and capacitor

70

SC9149A/SC9150A

V

DD

70

60

50

40

30

Oscillator frequency (kHz)

20

700 900 1100 1300

Capacitor (pF)

VDD=5V

R=39kΩ

2. RECEIVING SIGNAL INPUT CIRCUIT

Vcc

HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD

60

50

40

30

Oscillator frequency (kHz)

20

26 34 42 50 58

VDD=5V

C=1000pF

Resistor (kΩ

Det.Amp.

Rx

Rev: 1.0 2000.12.31

5

Page 6

Silan

Semiconductors

Signal received by the light receiving element is sent through the amplifier to the detector where 38 kHz carrier

wave is eliminated and is input into the receiving signal input circuit . The receiving signal input circuit (Rx IN ) has

a built-in Schmitt circuit for shaping receiving signal waveform to eliminate rounding .

3. RECEIVING SIGNAL CHECK

The receiving signal check is to check 2 cycle transmitting signal sent from the transmitter to determine if it is

normal signal .

12 BITS 12 BITS

RECEIVING

SIGNAL

FIRST DATA SECOND DATA

First , the first data is stored in the 12-bits shift register. Then, when the second data is put into the shift

register , data is forced out of the shift register by one bit , where the first data has been stored .

Now , pushed out data and incoming data to see if they are same . If an error is caused in the receiving data

12-bits check , the system is reset at that point of time . Conversely , when all receiving data are OK , output is

raised from "L" level to "H" level .

Reader DATA "1" DATA "0"Reader

RECEIVEING

DATA

0.42ms 0.84ms

SC9149A/SC9150A

SHIFT PULSE

CHECK PULSE

The status of receiving data , shift pulse and check pulse is shown above . Shift pulse is provided in the data

center by taking frequency margins of the transmitter and the receiver into consideration .

4.Code Comparison

To prevent interference with other models , C1, C2 and C3 code bits are provided for checking whether the

transmitter and receiver codes agree each other .

Only when both codes agreed , internal latch strobe pulse is generated to latch receiving data and output is

raised from 'L" level . if both codes do not agree , no latch strobe pulse is generated and output remains at "L"

level .

Code bits used differ depending upon receiver as shown below :

CODE BIT

C1 C2

C3 C2

10

01

11

C2,C3 are used for

SC9149A/9149AL/9149AHN

C1,C2 are used for SC9150A.

Code bit “0”, “0” can not be used.

HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD

Rev: 1.0 2000.12.31

6

Page 7

Silan

Semiconductors

5.INITIALIZATION

In order to initialize the internal status at time of power ON, it is necessary to perform the initialization.

The initialization is carried out when a capacitor is connected to the code bit terminal.

V

DD

NOTE: * In case of SC9149A series, connect a capacitor to C1 and C2.

* A capacitor for initialization is unnecessary for the terminal for which code bit “0” is selected. However,

code bit “0”, “0” can not be used. Either one terminal must be set at “H”.

6. EXPLANATION OF OUTPUT PULSE SP,HP,CP

6-1. SP1~SP5 (SINGLE PULSE)

SINGLE-SHOT

KEY ON

Tx OUT

LATCH STROBE

PULSE

12Bits 12Bits

V

C2 C3

SC9149A/SC9150A

INITIALIZE

DD

Rup=20kΩ Typical)

C=0.001µF~0.022µF

RupRup

CC

SINGLE PULSE

OUTPUT

About 107msec

After checking 12-bits receiving data, if data agree and OK, single pulse is output.

Output is raised from “L” level to “H” level and returned again to “L” level after about 107msec.

6-2. HP1~HP5 (Hold pulse)

CONTINUOUS

KEY ON

Tx OUT

LATCH STROBE

PULSE

HOLD PULSE

OUTPUT

12Bits 12B its 12Bits 12B its

About

160msec

Hold pulse is output by the first latch strobe pulse after key ON. Output is kept at “H” level as long as continuous

signal is Input. When the key is released and continuous signal is stopped, about 160msec later, output is reversed

to “L” by the last latch strobe pulse. Further, HP1~HP5 are able to parallely and simultaneously maximum sextet

outputs at “H” level by continuous signal sent from the transmitter.

These outputs are optimum as outputs of REC-PLAY,REC-PAUSE, and CUE/REVIEW of tape deck.

HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD

Rev: 1.0 2000.12.31

7

Page 8

Silan

Semiconductors

6-3. CP1,CP2 ( Cyclic Pulse)

KEY ON

TX OUT

LATCH STROBE

PULSE

12Bits 12Bits 12Bits 12Bits

SC9149A/SC9150A

CYCLIC OUTPUT

When single-shot signal received, cyclic pulse output is reversed. This cyclic pulse is used for power ON/OFF,

MUTE etc.

7.CODE ALLOCATION (KEY NO. IS FOR SC9148A)

Key No.

SC9149AL/9149AHN is able to use KEY1~5 and KEY 7~9, KEY 17~18 only for 10 commands.

H S1 S2 K1 K2 K3 K4 K5 K6

1 1 0 0 1 0 0 0 0 0 Continuous Signal HP1

2 1 0 0 0 1 0 0 0 0 Continuous Signal HP2

3 1 0 0 0 0 1 0 0 0 Continuous Signal HP3

4 1 0 0 0 0 0 1 0 0 Continuous Signal HP4

5 1 0 0 0 0 0 0 1 0 Continuous Signal HP5

6 1 0 0 0 0 0 0 0 1 Continuous Signal HP6

7 0 1 0 1 0 0 0 0 0 Single-shot signal SP1

8 0 1 0 0 1 0 0 0 0 Single-shot signal SP2

9 0 1 0 0 0 1 0 0 0 Single-shot signal SP3

10 0 1 0 0 0 0 1 0 0 Single-shot signal SP4

11 0 1 0 0 0 0 0 1 0 Single-shot signal SP5

12 0 1 0 0 0 0 0 0 1 Single-shot signal SP6

13 0 0 1 1 0 0 0 0 0 Single-shot signal SP7

14 0 0 1 0 1 0 0 0 0 Single-shot signal SP8

15 0 0 1 0 0 1 0 0 0 Single-shot signal SP9

16 0 0 1 0 0 0 1 0 0 Single-shot signal SP10

17 0 0 1 0 0 0 0 1 0 Cyclic Signal CP1

18 0 0 1 0 0 0 0 0 1 Cyclic Signal CP2

C1~C3 code bits are available in addition to the above data bits for optional selection.

SC9150A can use all keys, but SC9149A is able to use KEY1~5 and KEY 7~11 only for 10 commands.

DATA BIT

FUNCTION OF INSTRUCTION

HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD

Rev: 1.0 2000.12.31

8

Page 9

Silan

Semiconductors

TYPICAL APPLICATION CIRCUIT

1. SC9149A CIRCUIT

V

DD

10µF

CR

1516 1314 1112 910

SC9149A/SC9150A

Control signal

1000pF

1000pF

SP4SP3SP2SP1C3C2OSCVDD

SC9149A

GND Rx IN

HP1 HP2 HP3 HP4 HP5 SP5

21 43 65 87

10kΩ

Rx

Input

Control signal

R should be 38kΩ±5%

C should be polypropylene film capacitor having good temperature characteristics 1000pF±5%.

2. SC9149AL/9149AHN CIRCUIT

Control signal

CP1SP3SP2SP1C3C2OSCVDD

10µF

CR

1000pF

1000pF

1516 1314 1112 910

V

DD

SC9149AL/

9149AHN

GND Rx IN

HP1 HP2 HP3 HP4 HP5 CP2

21 43 65 87

10kΩ

Rx

Input

R should be 38kΩ±5%

C should be polypropylene film capacitor having good temperature characteristics 1000pF±5%.

Control signal

HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD

Rev: 1.0 2000.12.31

9

Page 10

Silan

Semiconductors

3. SC9150A CIRCUIT

V

DD

CR

1000pF

10µF

2324 2122 20

SC9149A/SC9150A

Control signal

1000pF

1819 1617 15 14 13

SP1 SP2 SP3 SP4 SP5 SP6 SP7 SP8C2C1OSCVDD

SC9150A

GND Rx IN

21 43

10kΩ

Rx

Input

HP5HP1 HP2 HP3 HP4 HP6 CP2 CP1 SP10 SP9

65 87 9 1110 12

Control signal

R should be 38kΩ±5%.

C should be polypropylene film capacitor having good temperature characteristics 1000pF±5%.

NOTE FOR APPLICATION CIRCUIT

1. COMBINATION OF SC9148A/SC9149A / AL / AHN CODE BITS

SC9148A

CODE

13 12 11 10

VDD

VDD

SC9149A / AL / AHN

T3

(C3)T2(C2)T1(C1)

141516

Code2

OSC

(C2)

13

Code3

(C3)

K1~K5

SP1~SP5

Code:

C1=C2=1,C3=0

Code:

C2=1,C3=0

The combination of code bits of SC9148A and SC9149A is shown in the following table.

Example 1 (C2=1 and C3=0)

SC9148A SC9149A / AL / AHN

C1 C2 C3 C2 C3

110 1 0

101 0 1

111 1 1

HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD

Rev: 1.0 2000.12.31

10

Page 11

Silan

Semiconductors

To make code bit to “1” on SC9148A, connect diode to CODE terminal from T1~T3 terminal. To set Code bit

“0” , open the circuit.

SC9149A has C2 and C3 code terminal. Code bit of C1 has been pulled up in IC and C1 is always kept at “1”

status.

Therefore, on transmitter SC9148A it is necessary to keep C1 code bit at “1” . Example 1 is the external circuit

diagram when Code bit C2=1 and C3=0.

2. COMBINATION OF SC9148A/SC9150A CODE BITS

SC9148A

T3

CODE

(C3)T2(C2)T1(C1)

13 12 11 10

VDD

SC9149A/SC9150A

Code:

K1~K10

C1=C3=1,C2=0

VDD

OSC

221516

Code1

(C1)

21

Code2

(C2)

SP1~SP10

Code:

C1=1,C2=0

SC9150A

Example 2 (C1=1 and C2=0)

The combination of code bits of SC9148A and SC9150A is shown in the following table.

SC9148A SC9150A

C1 C2 C3 C2 C3

10110

01101

11111

On SC9150A, C3 code has been pulled up in IC and always kept at “1” status. Therefore , it is necessary to

keep Code Bit C3 of transmitter SC9148A at “1”. To keep Code Bit C3 at “1”, connect a diode to CODE terminal

from T3 terminal.

4. Note for Input Signal

If input voltage above VDD+0.3V may possibly be applied to Rx Input Terminal(2 Pin), connect resistor of about

10kΩ in series to Rx Input terminal in order to prevent latch-up.

HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD

Rev: 1.0 2000.12.31

11

Page 12

Silan

Semiconductors

PACKAGE OUTLINE

DIP-16-300-2.54 UNIT:mm

SC9149A/SC9150A

2.54

0.25

6.40

3.51

19.4

1.50

0.46

7.62

15 degree

5.083.30

DIP-24-600-2.54 UNIT:mm

2.54

0.25

13.60

15.24

32.04

3.85

1.50

5.083.30

0.46

15 degree

HANGZHOU SILAN MICROELECTRONICS JOINT-STOCK CO.,LTD

Rev: 1.0 2000.12.31

12

Loading...

Loading...