Page 1

INTEGRATED CIRCUITS

DATA SH EET

SAB9079HS

Multistandard Picture-In-Picture

(PIP) controller

Preliminary specification

File under Integrated Circuits, IC02

2000 Jan 13

Page 2

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

FEATURES

• Suitable for single PIP, double window and multi PIP

applications

• Data formats 4 : 1 : 1 (all modes) and 4:2:2(most

modes)

• Sample rate of 14 MHz, 720 Y*-pixels/line

• Horizontal reduction factors1⁄

• Vertical reduction factors1⁄1,1⁄2,1⁄3and1⁄

• PIP OSD for the sub channels displayed

• Detection of PAL/NTSC with overrule bit

• CTE/LTE like circuits in display part

• Replay with definable auto increment, picture sample

rate and picture number auto wrap

• Programmable Y*UV to RGB conversion matrix with

independent coefficients for NTSC and PAL sources

• Display clock and synchronisation are derived from the

main PLL

• Three 8-bit Digital-to-Analog Converters (DACs)

• Three 8-bit Analog-to-Digital Converters (ADCs)

(7-bit performance) with clamp circuit for each

acquisition channel

• Main and sub can write to the same VDRAM address

spaces under certain conditions; the reduction factors

should be the same

• Y* and UV pedestals on the acquisition sides

• Independent vertical filtering with 1 : 1 for UV and Y* at

the display part.

3

⁄4,2⁄3,1⁄2,1⁄3,1⁄4and1⁄

1

4

SAB9079HS

GENERAL DESCRIPTION

6

The SAB9079HS is a PIP controller for a multistandard

application environment in combination with a

multistandard decoder such as for example TDA8310,

TDA9143 or TDA9321H.

The SAB9079HSinserts one or two live video signals with

reduced sizes into the main/display video signal. All video

signals are expected to be analog baseband signals. The

analog signals are stripped signals without sync.

Therefore the luminance signal is referred to as Y*. The

conversion into the digital environment and back is done

on-chip as well as the internal clock generation.

The SAB9079HS is suitablefor single PIP, double window

and multi PIP applications.

ORDERING INFORMATION

TYPE

NUMBER

SAB9079HS SQFP128 plastic shrink quad flat package; 128 leads (lead length 1.6 mm);

2000 Jan 13 2

NAME DESCRIPTION VERSION

body 14 × 20 × 2.72 mm

PACKAGE

SOT387-3

Page 3

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

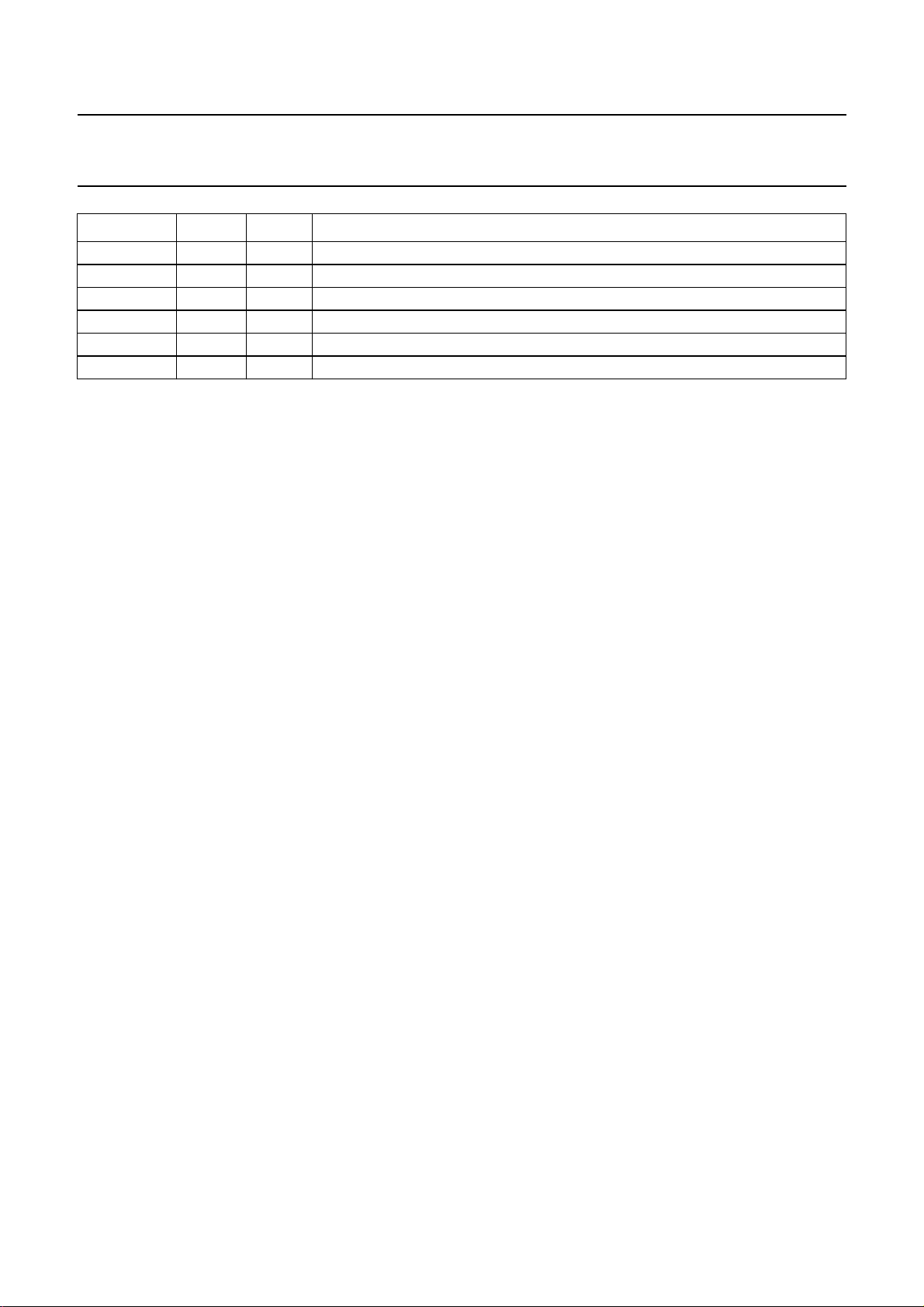

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supplies

V

DDD(C)

V

DDD(P)

V

DDA

I

DDD(C)

I

DDD(P)

I

DDA

PLL

f

osc

f

sys

B

loop

t

jitter

ζ damping factor − 0.7 −

digital supply voltage for the core 3.0 3.3 3.6 V

digital supply voltage for the

4.5 5.0 5.5 V

periphery

analog supply voltage 3.0 3.3 3.6 V

digital supply current for the core tbf 115 tbf mA

digital supply current for the

tbf 10 tbf mA

periphery

analog supply current − 170 210 mA

oscillator frequency 3584 × HSYNC − 56 − MHz

system frequency 1792 × HSYNC − 28 − MHz

896 × HSYNC − 14 − MHz

448 × HSYNC − 7 − MHz

loop bandwidth − 4 − kHz

short term stability jitter during 64 µs −−4ns

2000 Jan 13 3

Page 4

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

2000 Jan 13 4

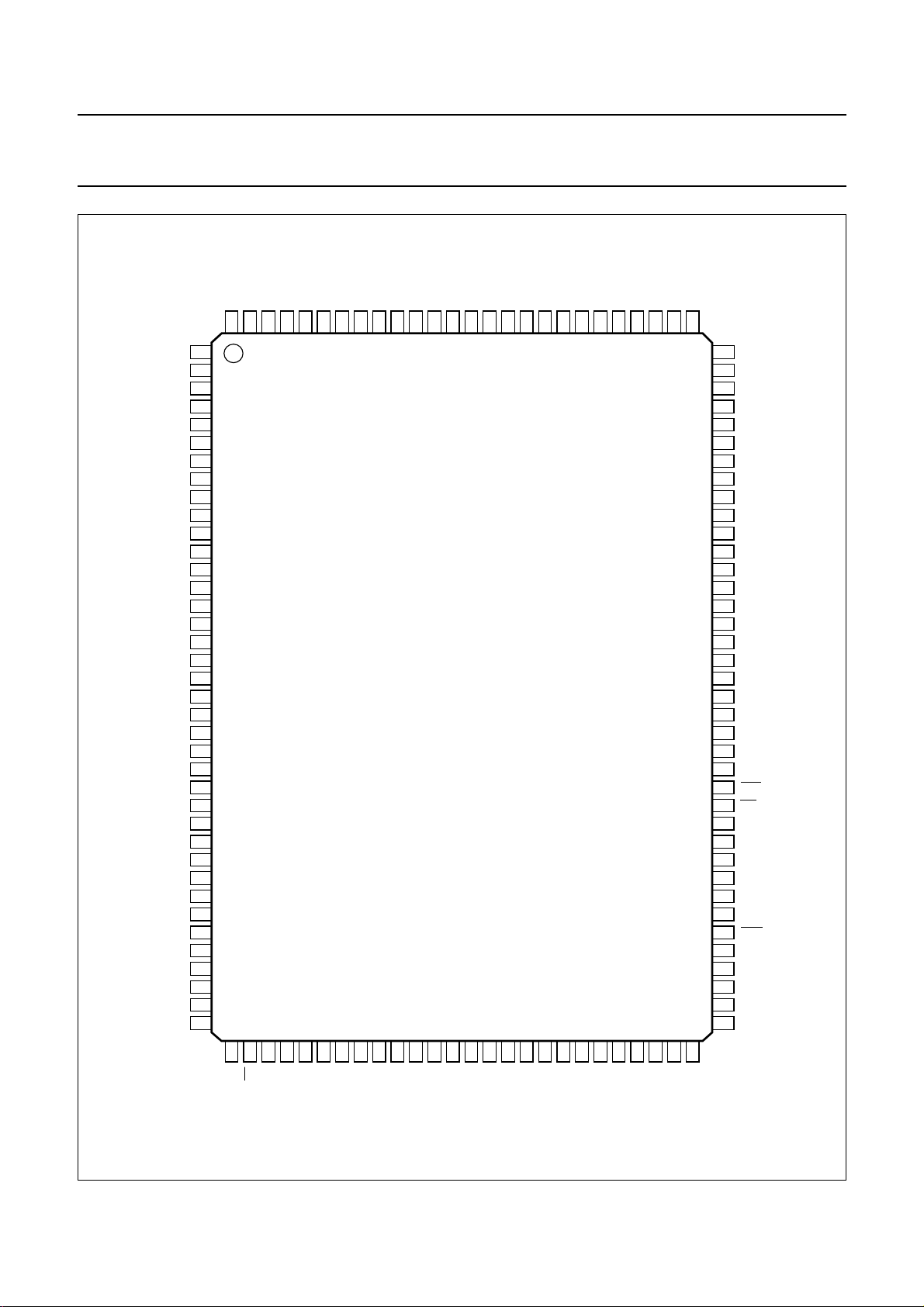

handbook, full pagewidth

BLOCK DIAGRAM

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

V

bias(SA)

V

ref(T)(SA)

V

ref(B)(SA)

SHSYNC

SVSYNC

V

bias(MA)

V

ref(T)(MA)

V

ref(B)(MA)

MHSYNC

MVSYNC

V

DDA(MF)

SY

SU

SV

MY

MU

MV

V

SSA(MA)

1

105

103

101

104

107

106

94

95

126

128

2

127

124

125

9

8

V

DDA(MA)

V

V

DDA(MP)

3

4

CLAMP AND ADC

PLL AND CLOCK

GENERATOR

CLAMP AND ADC

PLL AND CLOCK

GENERATOR

V

DDA(MH)

SSA(MP)

10

11

V

V

DDA(SA)

12

V

DDA(SF)

SSA(SA)

99

100

HORIZONTAL

VERTICAL

LINE MEMORY

HORIZONTAL

VERTICAL

LINE MEMORY

V

DDA(SH)

102

AND

FILTER

AND

FILTER

V

SSA(SP)

91

V

DDA(SP)

92

93

RAS

78

CAS

WE

70 77 40 51

TEST

CONTROL

AD8

DT

to AD0

SC

79 to 83,

74 to 71

VDRAM CONTROL

AND

(RE-)FORMATTING

SAB9079HS

I2C-BUS

CONTROL

DAO0

to DAO15

41 to 46,

49, 50, 69,

67, 65, 61,

59, 57, 55, 53

DAI0

to DAI15

39 to 32,

68, 66, 64,

60, 58, 56,

54, 52

V

DDA(DA)

V

SSA(DA)

30

DAC

AND

BUFFER

DISPLAY

CONTROL

LINE MEMORY

PLL AND CLOCK

GENERATOR

V

DDD(P)

31

113

24

DY

27

DU

29

DV

28

V

bias(DA)

26

V

ref(B)(DA)

25

V

ref(T)(DA)

19

DFB

84

n.c.

21

DVSYNC

20

DHSYNC

V

DDD(C1)

to

V

DDD(C7)

15, 18, 22,

85, 88,

109, 122

V

V

16, 17, 23,

86, 87,

108, 123

SSD(C1)

to

SSD(C7)

V

SSD(P1)

to

V

SSD(P5)

13,

47, 63,

75, 90

V

DDD(P1)

to

V

DDD(P5)

14,

48, 62,

76, 89

98

TSEXT

111 114

TCBD

TCBR A0

TCBC SCL

Fig.1 Block diagram.

97112 116

110 115

TSMSB POR

SDA

117

TMMSB

6

TMEXT

5

TSCLK

121

96

120

TM0

TM2

TM1

119

118

TC

7

TMCLK

MGS386

SAB9079HS

Page 5

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

PINNING

SYMBOL PIN I/O DESCRIPTION

V

DDA(MF)

MV 2 I analog V input of main channel

V

SSA(MA)

V

DDA(MA)

TMEXT 5 I set main PLL input for external mode (CMOS levels)

TMMSB 6 O test main MSB output of PLL counter (CMOS levels)

TMCLK 7 I test clock main input (CMOS levels)

MVSYNC 8 I vertical sync input for main channel (CMOS levels with hysteresis)

MHSYNC 9 I horizontal sync input for main channel (CMOS levels with hysteresis)

V

DDA(MP)

V

SSA(MP)

V

DDA(MH)

V

SSD(P1)

V

DDD(P1)

V

DDD(C1)

V

SSD(C1)

V

SSD(C2)

V

DDD(C2)

DFB 19 O fast blanking control output (CMOS levels)

DHSYNC 20 O horizontal sync output (CMOS levels)

DVSYNC 21 O vertical sync output (CMOS levels)

V

DDD(C3)

V

SSD(C3)

DY 24 O analog Y* output of DAC

V

ref(T)(DA)

V

ref(B)(DA)

DU 27 O analog U output of DAC

V

bias(DA)

DV 29 O analog Voutput of DAC

V

SSA(DA)

V

DDA(DA)

DAI7 32 I memory input data bit 7 (CMOS levels)

DAI6 33 I memory input data bit 6 (CMOS levels)

DAI5 34 I memory input data bit 5 (CMOS levels)

DAI4 35 I memory input data bit 4 (CMOS levels)

DAI3 36 I memory input data bit 3 (CMOS levels)

DAI2 37 I memory input data bit 2 (CMOS levels)

DAI1 38 I memory input data bit 1 (CMOS levels)

DAI0 39 I memory input data bit 0 (CMOS levels)

DT 40 O memory data transfer (CMOS levels)

1 S analog supply voltage for main channel front-end (3.3 V)

3 S analog ground for main channel ADCs

4 S analog supply voltage for main channel ADCs (3.3 V)

10 S analog supply voltage for main channel PLL (3.3 V)

11 S analog ground for main channel PLL

12 S supply of main HSYNC input (5.0 V)

13 S digital ground 1 for periphery; note 1

14 S digital supply voltage 1 for periphery (5.0 V); note 2

15 S digital supply voltage 1 for core (3.3 V); note 3

16 S digital ground 1 for core; note 4

17 S digital ground 2 for core; note 4

18 S digital supply voltage 2 for core (3.3 V); note 3

22 S digital supply voltage 3 for core (3.3 V); note 3

23 S digital ground 3 for core; note 4

25 I/O analog top reference for DACs

26 I/O analog bottom reference for DACs

28 I/O analog voltage reference DACs

30 S analog ground for DACs

31 S analog supply voltage for DACs (3.3 V)

2000 Jan 13 5

Page 6

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

SYMBOL PIN I/O DESCRIPTION

DAO0 41 O memory output data bit 0 (CMOS levels)

DAO1 42 O memory output data bit 1 (CMOS levels)

DAO2 43 O memory output data bit 2 (CMOS levels)

DAO3 44 O memory output data bit 3 (CMOS levels)

DAO4 45 O memory output data bit 4 (CMOS levels)

DAO5 46 O memory output data bit 5 (CMOS levels)

V

SSD(P2)

V

DDD(P2)

DAO6 49 O memory output data bit 6 (CMOS levels)

DAO7 50 O memory output data bit 7 (CMOS levels)

SC 51 O memory shift clock output (CMOS levels)

DAI15 52 I memory input data bit 15 (CMOS levels)

DAO15 53 O memory output data bit 15 (CMOS levels)

DAI14 54 I memory input data bit 14 (CMOS levels)

DAO14 55 O memory output data bit 14 (CMOS levels)

DAI13 56 I memory input data bit 13 (CMOS levels)

DAO13 57 O memory output data bit 13 (CMOS levels)

DAI12 58 I memory input data bit 12 (CMOS levels)

DAO12 59 O memory output data bit 12 (CMOS levels)

DAI11 60 I memory input data bit 11 (CMOS levels)

DAO11 61 O memory output data bit 11 (CMOS levels)

V

DDD(P3)

V

SSD(P3)

DAI10 64 I memory input data bit 10 (CMOS levels)

DAO10 65 O memory output data bit 10 (CMOS levels)

DAI9 66 I memory input data bit 9 (CMOS levels)

DAO9 67 O memory output data bit 9 (CMOS levels)

DAI8 68 I memory input data bit 8 (CMOS levels)

DAO8 69 O memory output data bit 8 (CMOS levels)

CAS 70 O memory column address strobe output (CMOS levels)

AD0 71 O memory address output bit 0 (CMOS levels)

AD1 72 O memory address output bit 1 (CMOS levels)

AD2 73 O memory address output bit 2 (CMOS levels)

AD3 74 O memory address output bit 3 (CMOS levels)

V

SSD(P4)

V

DDD(P4)

WE 77 O memory write enable output (CMOS levels)

RAS 78 O memory row address strobe output (CMOS levels)

AD8 79 O memory address output bit 8 (CMOS levels)

AD7 80 O memory address output bit 7 (CMOS levels)

AD6 81 O memory address output bit 6 (CMOS levels)

47 S digital ground 2 for periphery; note 1

48 S digital supply voltage 2 for periphery (5.0 V); note 2

62 S digital supply voltage 3 for periphery (5.0 V); note 2

63 S digital ground 3 for periphery; note 1

75 S digital ground 4 for periphery; note 1

76 S digital supply voltage 4 for periphery (5.0 V); note 2

SAB9079HS

2000 Jan 13 6

Page 7

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

SYMBOL PIN I/O DESCRIPTION

AD5 82 O memory address output bit 5 (CMOS levels)

AD4 83 O memory address output bit 4 (CMOS levels)

n.c. 84 − not used in application

V

DDD(C4)

V

SSD(C4)

V

SSD(C5)

V

DDD(C5)

V

DDD(P5)

V

SSD(P5)

V

DDA(SH)

V

SSA(SP)

V

DDA(SP)

SHSYNC 94 I horizontal sync input for sub channel (CMOS levels with hysteresis)

SVSYNC 95 I vertical sync input for sub channel (CMOS levels with hysteresis)

TSCLK 96 I test clock input for sub (CMOS levels)

TSMSB 97 O test sub MSB output for PLL counter (CMOS levels)

TSEXT 98 I set sub PLL input for external mode (CMOS levels)

V

DDA(SA)

V

SSA(SA)

SV 101 I analog V input of sub channel

V

DDA(SF)

SU 103 I analog U input of sub channel

V

bias(SA)

SY 105 I analog Y* input of sub channel

V

ref(B)(SA)

V

ref(T)(SA)

V

SSD(C6)

V

DDD(C6)

TCBC 110 I test control block clock input (CMOS levels)

TCBD 111 I test control block data input (CMOS levels)

TCBR 112 I test control block reset input (CMOS levels)

V

DDD(P)

A0 114 I address select pin input (I

SDA 115 I/O serial input data/ACK output (I

SCL 116 I serial clock input (I

POR 117 I power-on reset input (CMOS levels with hysteresis and pull-up resistor to V

TC 118 I test control input (CMOS levels)

TM1 119 I/O test mode input/output (CMOS levels with hysteresis and pull-up resistor to V

TM2 120 I/O test mode input/output (CMOS levels with hysteresis and pull-up resistor to V

TM0 121 I test mode input (CMOS levels)

V

DDD(C7)

85 S digital supply voltage 4 for core (3.3 V); note 3

86 S digital ground 4 for core; note 4

87 S digital ground 5 for core; note 4

88 S digital supply voltage 5 for core (3.3 V); note 3

89 S digital supply voltage 5 for periphery (5.0 V); note 2

90 S digital ground 5 for periphery; note 1

91 S supply of sub HSYNC input (5.0 V)

92 S analog ground for sub channel PLL

93 S analog supply voltage for sub channel PLL (3.3 V)

99 S analog supply voltage for sub channel ADCs (3.3 V)

100 S analog ground for sub channel ADCs

102 S analog supply voltage for sub channel frontend (3.3 V)

104 I/O analog bias reference input for sub channel ADCs

106 I/O analog bottom reference for sub channel ADCs

107 I/O analog top reference for sub channel ADCs

108 S digital ground 6 for core; note 4

109 S digital supply voltage 6 for core (3.3 V); note 3

113 S digital supply voltage for periphery (5.0 V); note 5

2

C-bus) (CMOS levels)

2

C-bus) (CMOS input levels)

2

C-bus) (CMOS levels)

122 S digital supply voltage 7 for core (3.3 V); note 3

DD

DD

DD

)

)

)

2000 Jan 13 7

Page 8

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

SYMBOL PIN I/O DESCRIPTION

V

SSD(C7)

V

ref(T)(MA)

V

ref(B)(MA)

MY 126 I analog Y* input for main channel

V

bias(MA)

MU 128 I analog U input for main channel

Notes

1. All periphery V

2. All periphery V

3. All core V

4. All core V

5. This pin is NOT connected to the other periphery V

123 S digital ground 7 for core; note 4

124 I/O analog top reference for main channel ADCs

125 I/O analog bottom reference for main channel ADCs

127 I/O analog bias reference for main channel ADCs

are internally connected to each other, unless otherwise specified.

SS(P)

are internally connected to each other, unless otherwise specified.

DD(P)

are internally connected to each other.

DD(C)

are internally connected to each other.

SS(C)

.

DD(P)

SAB9079HS

2000 Jan 13 8

Page 9

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

handbook, full pagewidth

bias(MA)

ref(B)(MA)

ref(T)(MA)

V

125

SSD(C7)VDDD(C7)

V

V

124

123

122

TM0

121

TM2

TM1TCPOR

120

119

118

V

DDA(MF)

V

SSA(MA)

V

DDA(MA)

TMEXT

TMMSB

TMCLK

MVSYNC

MHSYNC

V

DDA(MP)

V

SSA(MP)

V

DDA(MH)

V

SSD(P1)

V

DDD(P1)

V

DDD(C1)

V

SSD(C1)

V

SSD(C2)

V

DDD(C2)

DHSYNC

DVSYNC

V

DDD(C3)

V

SSD(C3)

V

ref(T)(DA)

V

ref(B)(DA)

V

bias(DA)

V

SSA(DA)

V

DDA(DA)

MV

DFB

DY

DU

DV

DAI7

DAI6

DAI5

DAI4

DAI3

DAI2

DAI1

V

MU

MY

127

128

126

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

SCL

SDAA0V

117

116

115

SAB9079HS

114

DDD(P)

TCBR

113

112

TCBD

111

DDD(C6)VSSD(C6)Vref(T)(SA)Vref(B)(SA)

TCBC

V

110

109

108

107

106

SAB9079HS

bias(SA)

SY

V

SU

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

V

DDA(SF)

SV

V

SSA(SA)

V

DDA(SA)

TSEXT

TSMSB

TSCLK

SVSYNC

SHSYNC

V

DDA(SP)

V

SSA(SP)

V

DDA(SH)

V

SSD(P5)

V

DDD(P5)

V

DDD(C5)

V

SSD(C5)

V

SSD(C4)

V

DDD(C4)

n.c.

AD4

AD5

AD6

AD7

AD8

RAS

WE

V

DDD(P4)

V

SSD(P4)

AD3

AD2

AD1

AD0

CAS

DAO8

DAI8

DAO9

DAI9

DAO10

40394142434445464748495051525354555657585960616263

DT

DAI0

DAO0

DAO1

DAO2

DAO3

DAO4

DAO5

SSD(P2)

DDD(P2)

V

V

DAO6

DAO7

Fig.2 Pin configuration.

2000 Jan 13 9

SC

DAI15

DAO15

DAI14

DAO14

DAI13

DAO13

DAI12

DAI11

DAO12

DAO11

DDD(P3)

V

64

DAI10

SSD(P3)

V

MGS387

Page 10

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

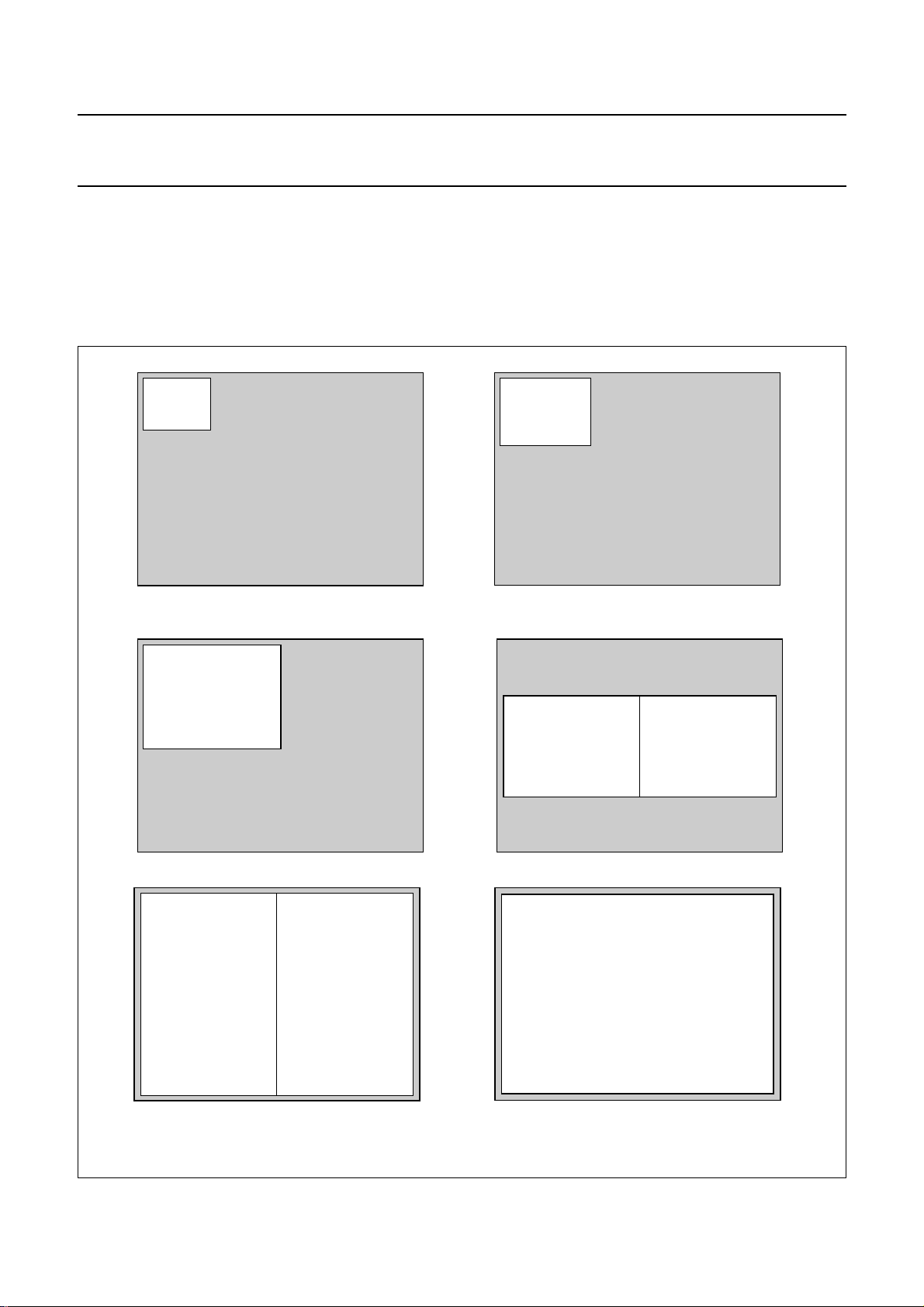

SYSTEM DESCRIPTION

PIP modes

An overview of the general PIP modes is given in Figs 3, 4 and 5. These pictures do not refer to all possible modes the

device can handle. These modes are guaranteed only when sufficient memory is available and enough time is available

to fetch all data from the memory.

handbook, halfpage

handbook, halfpage

handbook, halfpage

handbook, halfpage

SP-Small

SP-Large

MGD594

MGD596

handbook, halfpage

handbook, halfpage

SP-Medium

DP

MGD595

MGD597

Twin-PIP

MGD598

Fig.3 PIP modes.

2000 Jan 13 10

Full Field Still

Full Field Live

MGD587

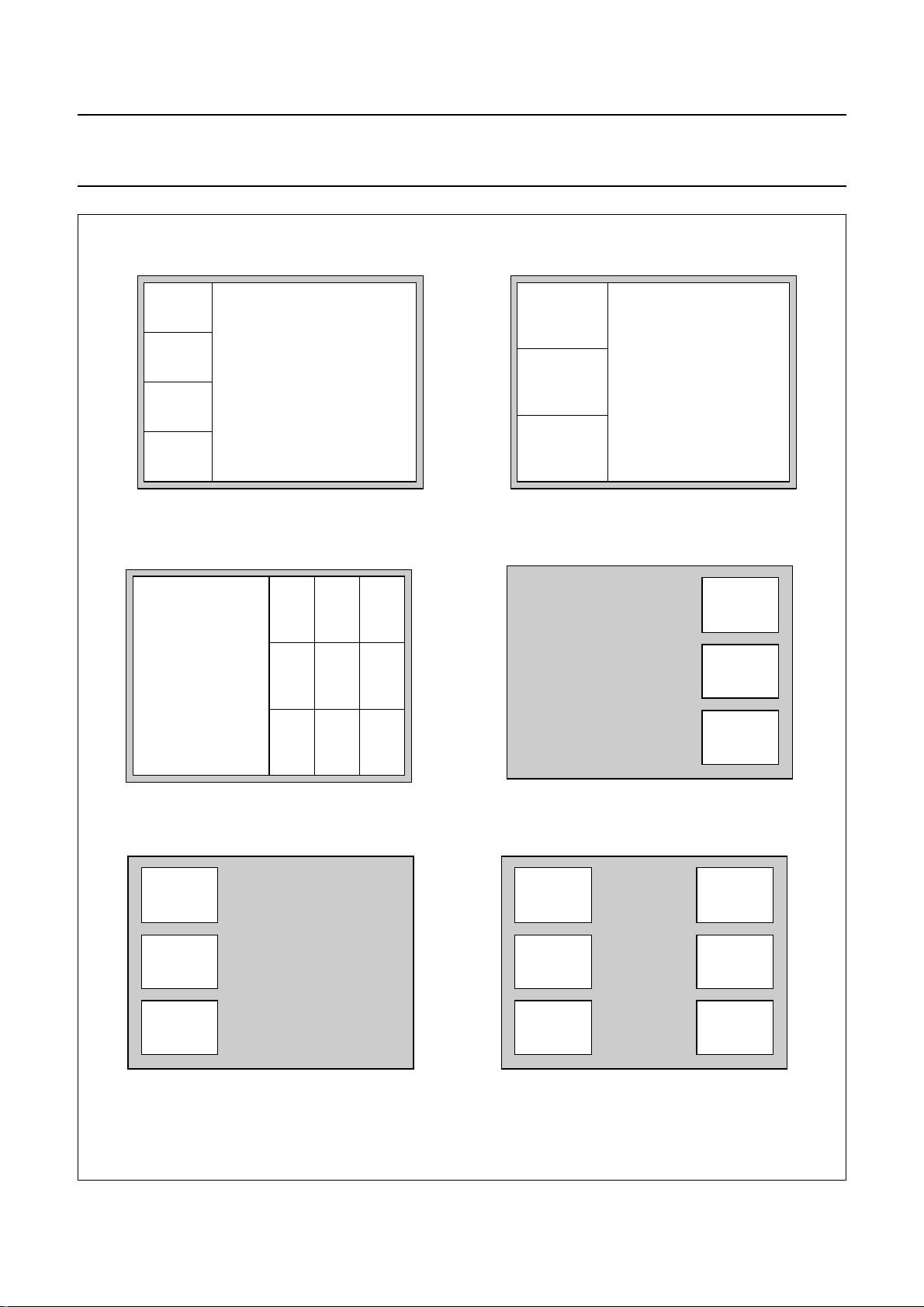

Page 11

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

handbook, halfpage

MGS388

handbook, halfpage

SAB9079HS

handbook, halfpage

MGS389

handbook, halfpage

MGS390

handbook, halfpage

POP-Left

MGD588

Fig.4 PIP modes (continued).

2000 Jan 13 11

handbook, halfpage

POP-Right

POP-Double

MGD589

MGD590

Page 12

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

handbook, halfpage

MP7

handbook, halfpage

MGD591

handbook, halfpage

handbook, halfpage

MP8

SAB9079HS

MGD592

Quatro

handbook, halfpage

MP16

MGD584

MGD586

Fig.5 PIP modes (continued).

2000 Jan 13 12

handbook, halfpage

MP9

MP13

MGD585

MGL925

Page 13

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

Acquisition window

The acquisition window is 720 pixels. This is related to a

whole line of 896 pixels. So for PAL will be

acquired from the active video. For NTSC this will be

slightly less .

720

--------- 896

63.5 µs×

The vertical acquisition window is 228 lines for NTSC and

276 lines for PAL. Data will be acquired in a 4 :2:2

format. The acquisition clock is 896 × HSYNC.

Acquisition fine positioning

2

C-bus settings relate to the incoming HSYNC,

All I

whether this is a real HSYNC or a burstkey for horizontal

positioning. The same applys for the incoming VSYNC for

vertical positioning. The relationships between the

acquisition window and the internal clamp pulse are

illustrated in Fig.6. In an application the clamp pulse must

be positioned, by the I2C-bus, between the HSYNC and

the start of the active video of the incoming signal.

720

--------- 896

64 µs×

SAB9079HS

Display window

The display window available for PIP pictures is also

720 pixels wide, related to a 896 pixels line. The vertical

display window is 228 lines for NTSC and 276 lines for

PAL.

Background window

The origin of the display window is referenced to the origin

of the background window. The background area is

768 pixels wide. Vertically it is 238 lines for NTSC and

286 lines for PAL.

Display fine positioning

The I2C-bus defined fine positioning has relationships to

the internal HSYNC and VSYNC as illustrated in Fig.7.

handbook, full pagewidth

The grey area depicts the background.

MAHFP

CIPER

CIDEL

MAVFP

228/276 lines

720 pixels

MGS391

Fig.6 Acquisition fine positioning.

2000 Jan 13 13

Page 14

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

handbook, full pagewidth

BGHFP

BGVFP

MDVFP

MDHFP

MAIN CHANNEL

768 pixels

SDHFP

SAB9079HS

SDVFP

SUB CHANNEL

238/286 lines

MGS392

The grey area depicts the background.

Fig.7 Display fine positioning.

YUV to RGB conversion matrix

A YUV to RGB conversion matrix is available. The nine

matrixcoefficientvaluescanbe set by I2C-buscommands.

Two sets can be defined; one for PAL and one for NTSC.

The matrix must be switched on, otherwise a 1 : 1

conversion takes place and Y*, U and V will be

unmodified.

Theconversionmatrix is based on the following equations.

All results (R, G and B) fall in the range from 0 to 1. Any

results outside of this range will be clipped to the nearest

end value. It should be noted that gamma correction is not

applied as is common practice. The end of this section

contains an example.

Normalised Y, U and V (indicated by subscript ‘a’) are

given by the following four equations:

1. Ya=x×Ra+y×Ga+z×B

a

2. x+y+z=1

3. Ua=Ba−Y

4. Va=Ra−Y

a

a

Absolute or discrete (indicated by subscript ‘d’) values

for Y, U and V are given by the following three equations:

1. Yd= 255 × Ya(V), Yanormalised (range 0 to 1)

U

2. ,

3. ,

128 127

U

d

normalised (range −1 to +1)

U

a

128 127

V

d

V

normalised (range −1 to +1)

a

×+=

×+=

a

----------- 1z–

V

a

----------- 1x–

2000 Jan 13 14

Page 15

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

Absolute or discrete (indicated by subscript ‘d’) values for R, G and B are given by the following three equations:

RdY

1.

GdY

2.

B

3.

d

The implementation of a matrix with 9 coefficients is shown in Table 1.

Table 1 Matrix coefficients

YUV TO RGB MATRIX

COEFFICIENTS

R ry=1 ru=0

Ggy=1

B by=1 bv=0

255

--------- -

d

127

255

--------- -

d

127

255

Y

--------- -

d

127

V

d

x

-- -

y

U

d

128–()1x–()××+=

128–()1z–()××+=

1x–()× V

d

Y

COFACTOR: Y

255

128–()××–

--------- 127

d

z

1z–()× Ud128–()××–=

-- -

y

U

d

d

COFACTOR:2 × (Ud− 128) COFACTOR: 2 × (Vd− 128)

rv

255

gu

bu

255

--------- 254

--------- 254

z

1z–()××–= gv

-- y

1z–()×=

255

--------- 254

255

--------- 254

V

d

1x–()×=

x

× 1x–()×–=

-- y

So, for example;

R=ry×Y

+ru×2×(Ud− 128) + rv × 2 × (Vd− 128)

d

Table 2 shows how the coefficients can be calculated for a specific case where x = 0.299, y = 0.587 and z = 0.114.

Calculation of xv:y* 128 (rounded to the nearest integer), translates to a binary value. Calculation of xu:xv: translates to

a binary value with the coefficients for the binary bits: −1,1⁄

1

⁄4,1⁄8,1⁄16,1⁄32,1⁄

2

1

⁄

(LSB).

64

128

Table 2 Coefficient calculation

COEFFICIENT EXPRESSION DECIMAL VALUE BINARY VALUE

ry 1 1 10000000

ru 0 0 00000000

rv 0.704 01011010

255

--------- 254

1x–()×

gy 1 1 10000000

gu −0.173 11101010

gv −0.358 11010010

255

--------- 254

255

--------- 254

z

× 1z–()×–

-- y

x

× 1x–()×–

-- y

by 1 1 10000000

bu 0.889 01110010

255

--------- 254

1z–()×

bv 0 0 00000000

2000 Jan 13 15

Page 16

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

PLL phase shift compensation for VCR

When a VCR is applied as source for the main channel, a

large phase jump can appear when the VCR head

switches to another field. Since this phenomenon occurs

around the VSYNC, its effects can be compensated.

A prediction mechanism generates a compensation

window around the VSYNC. This window can be

manipulated with two parameters; VsPre and VsPost.

• VsPre sets the number of lines before the predicted

VSYNC, where the compensation window will start

• VsPostsets the number of linesafter the actual VSYNC,

where the compensation window will end.

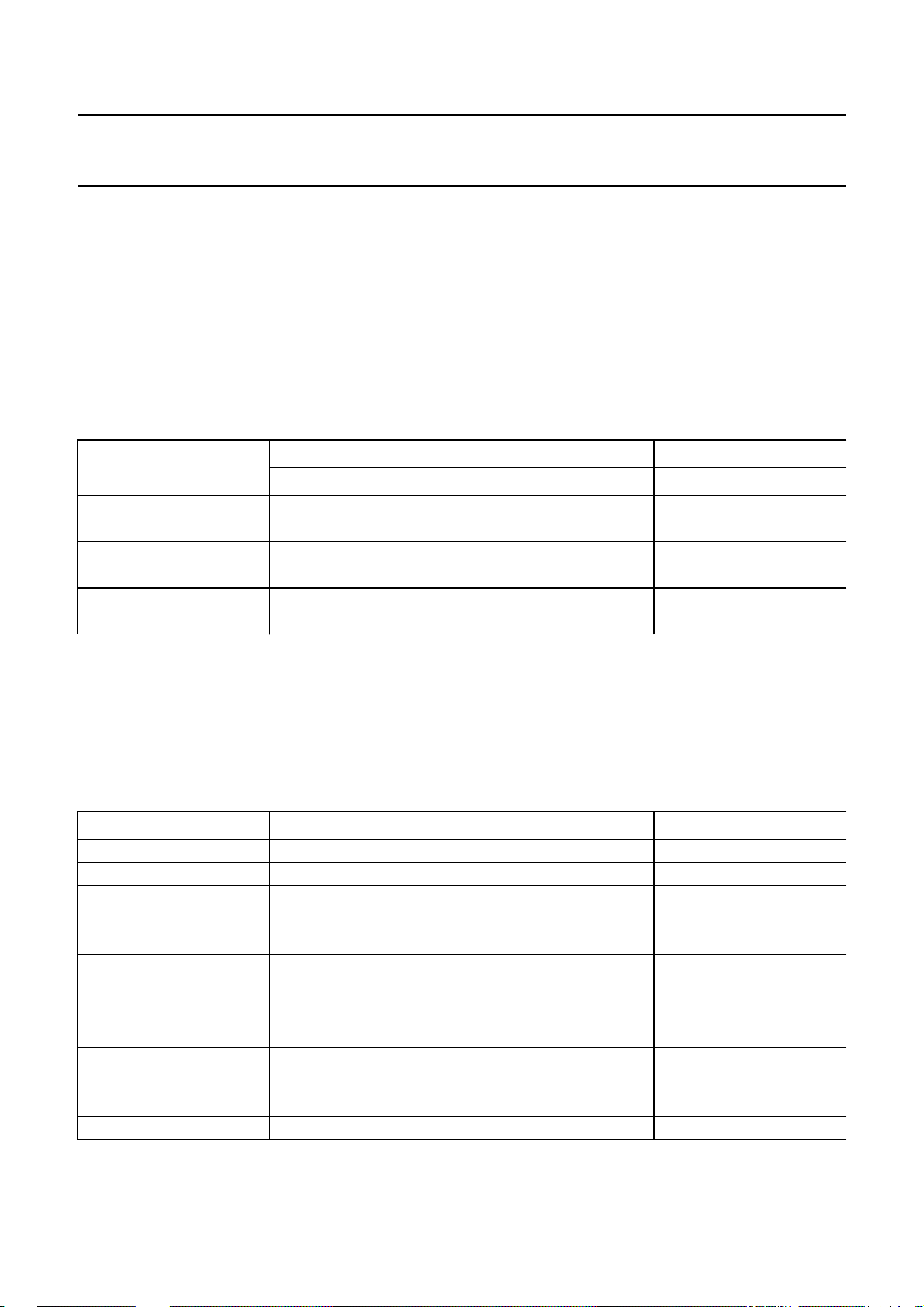

Table 3 I

Table 4 Description of Table 3

S START condition

A acknowledge bit (generated by SAB9079HS)

P STOP condition

SLAVE slave address; the data transmission starts with the slave address byte SLV (2CH or 2EH);

SUB sub address byte; the SUB byte indicates the sub address which has to be written; if more than

DATA data byte; the data byte is the actual data written to the sub address; the functions of each sub

2

C-bus slave receiver protocol

S SLAVE A SUB A DATA A DATA A P

SYMBOL DESCRIPTION

the LSB of the SLV byte is the R/

one data byte is send (as above) the internal sub address counter is automatically incremented

after each data byte

address are explained in the following Sections

W bit which is logic 0 in slave receiver mode

2

C-bus

I

2

C-BUS CONTROL

I

The SAB9079HS is a slave receiver/transmitter. The

protocols are given in Tables 3 and 5.

2

Table 5 I

Table 6 Description of Table 5

S START condition

A acknowledge bit; after the SLV generated by the SAB9079HS; after the DATA generated by the

N acknowledge not bit; given by the master after the last data byte

P STOP condition

SLAVE slave address; the data transmission starts with the slave address byte SLV (2DH or 2FH);

DATA data byte; this is put on the bus by SAB9079HS in an auto increment mode; if the master gives an

2000 Jan 13 16

C-bus slave transmitter protocol

SSLAVEADATAADATAADATAN P

SYMBOL DESCRIPTION

master

the LSB of the SLV byte is the R/

acknowledge the next data byte is sent; if the SAB9079HS has sent all its data it starts again with

the first data byte and the sequence is repeated; this continues until an acknowledge not is given

by the master

W bit which is logic 1 in slave transmitter mode

Page 17

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

The SAB9079HS has 8 read/status registers. The last 7 registers are reserved for future purposes. Reading a reserved

register will return zero values.

The SAB9079HS has 192 write registers. Writing to a reserved register is not allowed.

An overview of all write registers is given in Table 7.

Table 7 Description of write registers

SUB ADDRESS RANGE PURPOSE

00H to 04H display

05H to 11H positioning and sizing of PIPs

12H to 17H decoder settings

18H to 1FH acquisition control

20H to 25H decoder and PLL settings

26H to 28H reserved

29H to 2AH decoder and PLL settings

2BH to 2FH replay settings

30H to 37H border and colour settings

38H to 3CH OSD controls

3DH to 4EH YUV to RGB conversion matrix settings

4FH to 5FH extra decoder settings

60H to 7FH reserved

80H to DFH OSD characters

E0H to FFH reserved

2

I

C-BUS READ REGISTERS

The SAB9079HS has 8 read/status registers. The register currently used are listed in Table 8. The remaining 7 are

reserved for future purposes. Reading a reserved register will return zero values.

Table 8 I

ADDRESS

2

C-bus read registers

SUB

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

00H SNonInt Mask ID RepChano

01H reserved

02H reserved

03H reserved

04H reserved

05H reserved

06H reserved

07H reserved

DATA BYTES

2000 Jan 13 17

Page 18

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

SNonInt

This bit indicates the internal interface status of the sub

channel. A logic 0 indicates that the channel is in

interlaced mode, a logic 1 indicates that the channel is

non-interlaced.

Mask ID

This bit gives the version number of the chip. A logic 0

indicates that a SAB9079N1 is used, a logic 1 indicates

that a SAB9079N2 is used.

RepChano

These bits indicate the present picture number, counting

from 0, where replay acquisition is writing.

2

C-BUS DISPLAY SETTING REGISTERS

I

MPIPON and SPIPON

If MPIPON is set to logic 1 (see Table 10) the main PIP is

on. If itis set to logic 0 the main PIP is off. If SPIPON is set

to logic 1 the sub PIPs are on, in accordance with the

scheme of the PIPG bits (see Section “Positioning and

sizing of PIPs”). If SPIPON is set to logic 0 all the sub PIPs

are off. This can also be achieved by setting all PIPG bits

to zero.

SAB9079HS

• BGHfp, BGVfp, MDHfp, MDVfp, SDHfp and SDVfp

• MHPic, MVPic, SHPic, SVPic, SHDis and SVDis

• PIPG

• MHRed, MVRed, SHRed, SVRed, MLSel,

• OSDHfp, OSDVfp, OSDHDis and OSDVDis.

FillSet and FillOff

The FillSet bit sets the colour of all sub PIPs immediately

to a 30% grey value if is set to logic 1. If FillSet is set to

logic 0 then the 30% grey PIPs stay until the data in the

VDRAM is updated (unfrozen). This bit should be used in

the event that a new PIP mode is made in which the

VDRAM data becomes invalid. FillOff works the opposite

to FillSet. If this bit is set all the VDRAM data is made

visible in the PIPs and no PIP has a grey content. This bit

is generally not used.

MiS

If the MiS bit is set to logic 0 the main and sub channels

have their own independent memory spaces. If set to

logic 1 the main and sub channels share the same

memory space, this is only valid if the main and sub

channels have the same reduction factors.

c,r

SLSel and SBSel

MFreeze and SFreeze

MFreeze and SFreeze control the writing of data to the

VDRAM. If set to logic 0 the writing to the VDRAM is

disabled after the next VSYNC. If set to logic 1 the writing

is enabled after the next VSYNC.

I2CHold

The I2C-bus hold bit is set to logic 0 (default). This means

that all I2C-bus data is directly clocked into the internal

registers. A part of the I2C-bus data will be clocked in on

thenext VSYNC (e.g. thereduction factors and thedisplay

positioning). If the I2CHold bit is logic 1 that part of the

I2C-buswillnot be clocked in on the next VSYNC.Tomake

the data available the I2CHold bit should be set to logic 0

again. This function is useful when much data has to be

sent and a screenupdate is notallowed when sendingthis

data. A list of I2C-bus registers which are clocked in on a

VSYNC is given below:

• MPIPON and SPIPON

• MFreeze, SFreeze and FillSet

• DNonInt, MNonInt and SNonInt

• PRIO

YUVFilter

These bits control the vertical filtering of 1 : 1 for both the

Y* and UV channels independently. Several display filter

modes can be set with these bits. An overview is given in

Table 9. The Y filter should not be used in vertical1⁄

modes.

Table 9 Display filter modes

MODE YUV FILTER

No filter 00H

UV 1 : 1 vertical filter 01H

Y1:1 vertical filter 10H

YUV1:1 vertical filter 11H

1

CTE and LTE

ColourTransient Enhancement (CTE) canbe set on or off.

Luminance Transient Enhancement (LTE) is controllable

via a scale, setting the scale value to 0H means that LTE

is off.

2000 Jan 13 18

Page 19

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

MFld and SFld

The number of fields stored in the VDRAM can be set with

the MFld and SFld bits. There is a limit of 4 Mbits which

can be stored. It is best to set these bits so that 3 fields

are stored for the sub channel and 2 forthe main channel,

but this is not possiblein all cases (large PIPs). Therefore,

the number of fields stored can be reduced. This can

result in some performance loss, e.g. if the sub channel is

set to 1 field joint line errors can appear.

IntOff, DNonInt, MNonInt and SNonInt

In automatic interlace mode (IntOff is logic 0) the device

calculateswhetherinterlaced or non-interlaced signals are

applied and acts accordingly. This can be overruled by

setting bit IntOff to logic 1. Bits DNonInt, MNonint and

SNonInt then determine the interlace. If the xNonInt bits

are set to logic 0 the device is put in interlaced mode, if

they are set to logic 1 the main, sub and/or display

channels are put in non-interlaced mode. DNonint

overrules MNonint (main and display channels are

coupled).

PalOff, DPal, MPal and SPal

In automatic mode (PalOff is logic 0) the device calculates

what type of signal is applied, PAL or NTSC. In the event

that the number of lines in a field is less than 287 it is

assumed to be NTSC, otherwise it is assumed to be PAL.

This can be overruled by setting PalOff to logic 1.

SAB9079HS

The xPal bits then determine the mode of the device. A

logic 0 sets the device in NTSC mode, a logic 1 to PAL

mode. DPAL overrules MPAL (main and display channels

are coupled).

PRIO, NipCoff, Fmt411, DFilt and Yth

The PRIO bit sets the priority between the main and sub

channels. A logic 0 gives priority to the sub channel which

meansthat the sub channel PIPs, if present,are placed on

top of the main PIP. A logic 1 places the main PIP on top

of the sub PIPs. The NiPCoff bit determines whether a

grey bar is inserted in case a NTSC PIP is displayed in a

PIP with PAL PIP size. The missing lines are equally

dividedbetweenthe top part and the bottom partofthePIP

window and made 30% grey. If this bit is logic 0 the grey

bar is displayed, if this bit is logic 1 the grey bar is omitted

and the PIP data is shifted up. The Fmt411 bit sets the

YUV format. If this bit is logic 0 then the device is in

4:2:2YUVmode, if this bit is logic 1then the device is in

4:1:1 YUV mode. If the 4:2:2 format is used the

memory use is larger, so some modes are not available

and the length of a read/write cycle is larger. The Dfilt bit

controls an interpolating filter to expand the internal

720 pixels data rate to the output data rate of 2 × 720

pixels in 1FH mode. If DFilt is logic 1 then the filter is on.

The Yth

Y value is less then Yth × 16 then the fast blanking is

switched off, and the original live background will be

visible. This feature can be used to pick up sub-titles and

display them as OSD anywhere on the screen.

bits control the video output. If the current

(3 : 0)

2

Table 10 overview of the I

SUB

ADDRESS

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

00H MPIPON SPIPON MFreeze SFreeze I

01H −−−− MFld

02H YUVFilter

C-bus sub addresses

(1 : 0)

−−CTE LTE

DATA BYTES

2

CHold FillSet FillOff MiS

(1 : 0)

SFld

(2 : 0)

03H IntOff DNonInt MNonInt SNonInt Paloff DPal MPal SPal

04H PRIO NipCoff Fmt411 DFilt Yth

(3 : 0)

2000 Jan 13 19

(1 : 0)

Page 20

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

POSITIONING AND SIZING OF PIPS

Thebasic principle is the same as inthe SAB9076/77. The

only difference is that the main channel can only display

1 PIP. The algorithm for the sub channel is similar. The

difference for the sub channel is that the number of PIPs

for each row and the offset of the first PIP is replaced by

grid bits. In the matrix of 16 PIPs every PIP can be put on

or off. The I2C-bus registers are given in Table 11.

BGHfp and BGVfp

The BGHfp and BGVfp bits control the horizontal

(4 pixels/step) and vertical (2 line/field/step) background

positioning (upper left corner).

SDHfp and SDVfp

The SDHfp and SDVfp bits control the horizontal

(4 pixels/step) and vertical (1 line/field/step) sub display

positioning (upper left corner).

SHPic and SVPic

Bit SHPic controls the horizontal size of the sub PIP in

steps of 4 pixels (minimum is 8 pixels). Bit SVPic controls

the vertical size of the sub PIP in steps of 1 line/field for

NTSC or 2 lines/field for PAL.

SAB9079HS

SHDis and SVDis

Bit SHDis controls the horizontal distance between the left

sides of the sub PIPs on a row in steps of 4 pixels. Bit

SVDis controls the vertical distance between the top lines

of sub PIPs in steps of 1 line (both Pal and NTSC). The

distancesshouldalwaysbeequal or larger than the picture

sizesso that the PIPsof one channel donot overlap. In the

event of single PIP modes SHDis should be set to

maximum.

MDHfp and MDVfp

The MDHfp and MDVfp bits control the horizontal and

vertical main display positioning.

MHPic and MVPic

Bit MHPic controls the horizontal size of the main PIP in

steps of 4 pixels (minimum is 24 pixels). Bit MVPic

controls the vertical size of the main PIP in steps of

1 line/field for NTSC or 2 lines/field for PAL.

PIPG

row,col

The PIPG

PIP on or off in a multi PIP mode. PIPs are numbered

according to Table 12. Rows are numbered from top to

bottom, columns are numbered from left to right.

bits make it possible to set each individual

row,col

2

Table 11 I

C-bus registers for PIP

SUB

ADDRESS

05H BGHfp

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

(3 : 0)

06H SDHfp

07H SDVfp

08H SHPic

09H SVPic

0AH SHDis

0BH SVDis

0CH MDHfp

0DH MDVfp

0EH MHPic

0FH MVPic

10H PIPG

11H PIPG

1,3

3,3

PIPG

PIPG

1,2

3,2

PIPG

PIPG

1,1

3,1

PIPG

PIPG

DATA BYTES

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

1,0

3,0

PIPG

PIPG

0,3

2,3

PIPG

PIPG

BGVfp

0,2

2,2

(3 : 0)

PIPG

PIPG

0,1

2,1

PIPG

PIPG

0,0

2,0

2000 Jan 13 20

Page 21

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

Table 12 PIP numbering

ROW COLUMN 0 COLUMN 1 COLUMN 2 COLUMN 3

0 PIPG

1 PIPG

2 PIPG

3 PIPG

ACQUISITION CONTROL

Acquisition control sets the reduction factors, the

acquisition fine positioning and the channel selection bits

are given in Table 13.

SHRed, SVRed, MHRed and MVRed

The reduction factors can be set in accordance with

Table 14.

SAHfp and SAVfp

The SAHfp and SAVfp bits control the horizontal

(2 pixels/step) and vertical (1 line/field/step) sub

acquisition positioning (upper left corner). When SAHfp is

set to logic 0, the sub channel will enter the freeze mode.

0,0

1,0

2,0

3,0

SAB9079HS

PIPG

0,1

PIPG

1,1

PIPG

2,1

PIPG

3,1

SLSel and MLSel

Bits SLSel and MLSel select which PIP is updated.

A maximum of 16 PIPs can be displayed for the sub

channel. The number counting is done fromthe left toright

and from top to bottom.

If all PIPs are on (see Table 12) 16 PIPs are displayed.

If PIPs are put off the maximum number is limited to the

number of PIPs displayed. In the PIP mode where the

mainand sub channel have thesame reduction factors the

main channel can write in sub VDRAM address spaces

accordingtothesamenumbering. In all other cases MLSel

is inoperative and should be set to 0H. For replay and

other trick modes morePIPs can bestored and addressed

via the higher numbers (17 to 60). The numbers

61, 62 and 63 are not valid.

PIPG

PIPG

PIPG

PIPG

0,2

1,2

2,2

3,2

PIPG

PIPG

PIPG

PIPG

0,3

1,3

2,3

3,3

MAHfp and MAVfp

The MAHfp and MAVfp bits control the horizontal

(2 pixels/step) and vertical (1 line/field/step) main

acquisition positioning (upper left corner). When MAHfp is

set to logic 0, the main channel will enter the freeze mode.

Table 13 Acquisition and channel selection bits

SUB

ADDRESS

18H − SVRed

19H − MVRed

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

(2 : 0)

(2 : 0)

1AH SAHfp

1BH SAVfp

1CH MAHfp

1DH MAVfp

DATA BYTES

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

1EH −− SLSel

1FH −− MLSel

− SHRed

− MHRed

(5 : 0)

(5 : 0)

(2 : 0)

(2 : 0)

2000 Jan 13 21

Page 22

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

Table 14 Reduction factors

BITS

MAIN SUB MAIN SUB

0H not valid not valid not valid not valid

1H

2H

3H

4H

5H

6H

7H

DECODER AND PLL SETTINGS

SYClRef, SUClRef, SVClRef, MYClRef, MUClRef and

MVClRef

The clamp reference level can be set separately for each

of the 6 analog inputs; it acts as a wide range pedestal.

Under normal conditions SYClRef will be set to 0 and

SUVClRef will be set to 128.

DHsel, FidOn, VFilt, UVPol, VSPol, FPol and CCON

HORIZONTAL VERTICAL

1

⁄

1

1

⁄

2

1

⁄

3

1

⁄

4

2

⁄

3

1

⁄

6

3

⁄

4

SAB9079HS

1

⁄

1

1

⁄

2

1

⁄

3

1

⁄

4

not valid not valid not valid

1

⁄

6

not valid not valid not valid

IntCoff, FbDel and YDel

BitIntCoffsetstheinterlacecorrection.Interlacecorrection

isput off if this bit issetto logic 1. FbDel

fast blank delay in 8 steps of a1⁄228 MHz clock cycle

(−4 to +3); 0H is mid-scale. YDel adjusts the Y delay with

respect to the UV delay; 0H is mid-scale from −4to+3

pixels. YDel is done on the display side and therefore both

channels,mainand sub channels, will have anequaldelay

in the luminance.

1

⁄

1

1

⁄

2

1

⁄

3

1

⁄

4

1

⁄

1

1

⁄

2

1

⁄

3

1

⁄

4

not valid not valid

canadjust the

(2 : 0)

• DHsel determines the timing of the HSYNC pulse

(burstkey = 0 or HSYNC = 1), for the display part

• FidOn enables the field identification position fine

tuning; FidOn = 1 takes the value of registers

4FH or 57H; FidOn = 0 takes a hard wired default value

• VFilt enhances the vertical reduction filter for vertical

reduction modes1⁄3and1⁄

4

• SUVPol and MUVPol invert the UV polarity of the YUV

data

• DUVPol inverts the UV polarity of the border colours

• VSPol determines the active edge of the VSYNC

(positive edge is logic 0 and negative edge is logic 1)

• FPol can invert the field ID of the incoming fields

• CCON enables the clamp correction circuit.

Pedestals

Onthe acquisition sides YUV can begivenan offset during

the clamp. Using this mechanism minor offsets in the

matricescanbe adjusted. The steps are from −8 to +7with

a resolution of 1 LSB of the ADC.

VSPre and VSPost

VSPre is the number of lines before a VSYNC where the

PLL is put in free-running mode. VSPost is the number of

lines after the VSYNC where the PLL is still free-running.

Outside this area the PLL is in normal mode.

2000 Jan 13 22

Page 23

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

Table 15 Decoder and PLL settings

SUB

ADDRESS

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

12H SYClRef

13H SUClRef

14H SVClRef

15H MYClRef

16H MUClRef

17H MVClRef

20H −−SFidOn SVFilt SUVPol SVSPol SFPol SCCON

21H DHsel − MFidOn MVFilt MUVPol MVSPol MFPol MCCON

22H IntCOff FbDel

23H SPedestY

24H SPedestU

25H SPedestV

(2 : 0)

(3 : 0)

(3 : 0)

(3 : 0)

29H −− VSPre

2AH −− VSPost

DATA BYTES

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

DUVPol YDel

MPedestY

MPedestU

MPedestV

(2 : 0)

(3 : 0)

(3 : 0)

(3 : 0)

REPLAY SETTINGS

DChaOff

DChaOff is the channel offset for the display. It can be

used in trick modes or software replay as the channel

number to be displayed.

DChaDis

DChaDis is the number of internal VSYNCs between two

stored and/or displayed fields.

RepMax

RepMaxis the maximum number of different fields that will

be stored in the memory during replay.

RepInc

Repinc is the auto increment used during replay

acquisition/display.

RepAcq, RepDisp, RepCont, DCha+ and DCha

−

Bit RepAcq enables the replay acquisition loop, in which

pictures are stored with DChaDis as time distance. Bit

RepDisp enables the display of stored pictures. When bit

RepCont = 1 it enables a continuous looping during

display, when bit RepCont = 0 it enables the step function.

Bit DCha+ enables one step forward (next picture), bit

DCha− enables one step back in time (previous picture). It

should be noted that if bits RepAcq and RepDisp are both

logic 1atthesametime,theinternaldisplay number will be

the present acquisition number minus 1.

2000 Jan 13 23

Page 24

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

Table 16 Replay settings

SUB

ADDRESS

2BH −− DChaOff

2CH DChaDis

2DH −− RepMax

2EH DCha+ DCha− RepAcq RepDisp RepCont −−RGBOn

2FH −− RepInc

Note

1. RGBOn enables the YUV to RGB matrix. It is not related to the replay registers.

BORDER AND COLOUR SETTINGS

Several border and colour settings are given in Table 17.

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

BHSize and BVSize

Bits BHSize and BVSize control thehorizontal and vertical

border size in steps of 2 pixels and 1 line.

OUVPol

Bit OUVPol sets the UV polarity for all the OSD related

colours.

FBLON

If bit FBLON is set to logic 1 the FBL pin is made HIGH

under the condition that standard signals are applied.

If PAL signals are applied, this functionis overruled for the

SAB9078HS.

Shade

Bit Shade gives the OSD characters a shade.

OSDBLK

DATA BYTES

(5 : 0)

(7 : 0)

(5 : 0)

(5 : 0)

Colour registers

The colour registers are all built-up in a similar way:

• Bit 6 is the on bit which determines whether the border

(or OSD) is visible

• Bits 5 and 4 determine the brightness level ofthe colour

(see Table 18)

• Bits 2, 1 and 0 determine the colour type (see Table 18)

• SB = Sub Border

• SBS = Sub Border Select (which PIP has a different

border colour)

• MB = Main Border

• BG = Back Ground

• OSD is the OSD character

• OSDS = the background ofthe selected OSD character.

SBSel

The SBSel bits select which sub PIPhas a differentborder

colour, if SBSON is set to logic 1. The colour type can be

set with SBSBrt and SBSCol.

(1)

Bit OSDBLK blanks all OSD characters but retains their

values in memory.

2000 Jan 13 24

Page 25

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

Table 17 border and colour settings

SUB

ADDRESS

30H BHSize

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

(3 : 0)

31H − SBON SBBrt

32H − SBSON SBSBrt

33H − MBON MBBrt

34H FBLON BGON BGBrt

35H OUVPol OSDON OSDBrt

36H Shade OSDBLK OSDSBrt

37H −−−− SBSel

Table 18 Colour registers

COLOUR TYPE BRIGHTNESS LEVELS

COLOUR VALUE 0H 1H 2H 3H

White (low) 0H 0% 10% 30% 50%

Blue 1H 30% 50% 70% 100%

Red 2H 30% 50% 70% 100%

Magenta 3H 30% 50% 70% 100%

Green 4H 30% 50% 70% 100%

Cyan 5H 30% 50% 70% 100%

Yellow 6H 30% 50% 70% 100%

White (high) 7H 60% 70% 80% 100%

DATA BYTES

(1 : 0)

(1 : 0)

(1 : 0)

(1 : 0)

(1 : 0)

(1 : 0)

BVSize

− SBCol

(3 : 0)

(2 : 0)

− SBSCol

− MBCol

− BGCol

− OSDCol

− OSDSCol

(3 : 0)

(2 : 0)

(2 : 0)

(2 : 0)

(2 : 0)

(2 : 0)

OSD CONTROLS

OSD can be placed on the screen in 4 rows of 4 strings.

Each string can hold up to 6 characters. They can be

placedontop of the sub PIPs. Finepositioningisdone with

the OSDHfp and OSDVfp bits. The OSDHDis bits

determine the distance between the strings and OSDVdis

determine the distance between the rows (see Table 19).

OSDHfp and OSDVfp

Bits OSDHfp and OSDVfp control the fine positioning of

the OSD text in steps of 4 pixels and 1 line.

OSDHDis and OSDVDis

Bit OSDHDis determines the distance between the strings

(in steps of 4 pixels) and bit OSDVdis determines the

distance between the rows (in steps of 1 line).

2000 Jan 13 25

OSDEXP

It is possible to expand the OSD characters. 0xH is

standard, 10H doubles the size and 11H quadruples the

size.

OSDBG and OSDTR

BitOSDBGsetsthe OSD background. Bit OSDTR sets the

transparency of the OSD background; the options are

given in Table 20.

OSDHRep and OSDVRep

Bit OSDHRep (see Table 21) sets the actual number of

strings per row (a maximum of 4). Bit OSDVRep sets the

actual number of rows (a maximum of 4).

Page 26

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

Table 19 OSD control registers

SUB

ADDRESS

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

38H OSDHfp

39H OSDVfp

3AH OSDHDis

3BH OSDVDis

3CH OSDEXP OSDBG OSDTR OSDHRep

Table 20 OSD background

MODE OSDBG OSDTR NOTE

Only OSD 0 x PIP (BG)

OSD with BG 1 0 30% white

Transparent 1 1 50% PIP/30% white

Table 21 Row and string settings

DATA BYTES

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(1 : 0)

OSDVRep

(1 : 0)

OSDXRep VALUE OSDHRep NR. OF STRINGS OSDVRep NR. OF ROWS

00B 1 1

01B 2 2

10B 3 3

11B 4 4

OSD CHARACTERS

The OSD characters can be written to I2C-bus sub address 80H and higher (see Table 22). Theindex OSDCHR

pos,row,col

indicates the character position in the string, the row number and the column number of the string.

Table 22 OSD write register

SUB

ADDRESS

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

80H OSDChr

81H OSDChr

82H OSDChr

83H OSDChr

84H OSDChr

85H OSDChr

86H OSDChr

86H OSDChr

DATA BYTES

0,0,0

0,0,1

0,0,2

0,0,3

0,1,0

0,1,1

0,1,2

0,1,3

||

DEH OSDChr

DFH OSDChr

5,3,2

5,3,3

2000 Jan 13 26

Page 27

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

OSDChr

The OSDChr byte is divided into groups. The lower 7 bits OSDChr

to the character ROM table. Bit 7 indicates whether the character is selected, e.g. to change the background of that

character. Selecting the first character of a string selects the whole string; selecting any other character has no effect.

Table 23 Character ROM table; see also Fig.8

UPPER

3 BITS

0H 1H 2H 3H 4H 5H 6H 7H 8H 9H AH BH CH DH EH FH

LOWER 4 BITS

0H

2

1

1

1H

3

⁄

⁄

4

⁄

3

6

1

⁄

⁄

4

3

2H !”#$%&’()*+,-./

3H 0123456789: ;<=>?

4H @ABCDEFGHI JKLMNO

5H PQRSTUVWXYZ [ \ ] ^ _

6H `abcdefghi jklmno

7Hpqrstuvwxyz{|}~

contain the character to be displayed according

(6 : 0)

1

1

⁄

⁄

2

1

Note

1. Rows 0H and 1H are not completely represented because of their graphical contents (e.g. a smiley).

2000 Jan 13 27

Page 28

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

handbook, full pagewidth

UPPER

3 BITS

0H

1H

2H

3H

0H 1H 2H 3H 4H 5H 6H 7H 8H 9H AH BH CH DH EH FH

SAB9079HS

LOWER 4 BITS

4H

5H

6H

7H

MGS828

Fig.8 OSD character set.

2000 Jan 13 28

Page 29

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

YUV TO RGB CONVERSION MATRIX SETTINGS

RGBOn

RGBOn enables the YUV to RGB matrix.

XXCoefn (all coefficients)

The YUV to RGB conversion matrix has the following 3 equations:

1. R = RYCoef × Yd+ RUCoef × 2 × (Ud− 128) + RVCoef × 2 × (Vd− 128)

2. G = GYCoef × Yd+ GUCoef × 2 × (Ud− 128) + GVCoef × 2 × (Vd− 128)

3. B = BYCoef × Yd+ BUCoef × 2 × (Ud− 128) + BVCoef × 2 × (Vd− 128)

In this equation Yd is normalised for the range 0 to 255, Udand Vd for the range −128 to 128. The UV coefficients are

twos complement in the range −1 ≤ coef < 1. The Y coefficients are positives in the range 0 ≤ coef < 2. For PAL pictures

the coef1 values are used, for NTSC the coef2 values.

Table 24 Conversion settings

SUB

ADDRESS

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

2EH DCha+ DCha− RepAcq RepDisp RepCont −−RGBOn

3DH RYCoef1

3EH RUCoef1

3FH RVCoef1

40H GYCoef1

41H GUCoef1

42H GVCoef1

43H BYCoef1

44H BUCoef1

45H BVCoef1

46H RYCoef2

47H RUCoef2

48H RVCoef2

49H GYCoef2

4AH GUCoef2

4BH GVCoef2

4CH BYCoef2

4DH BUCoef2

4EH BVCoef2

DATA BYTES

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

Note

1. DCha+, DCha−, RepAcq, RepDisp and RepCont are used for replay settings. They are not related to the conversion

matrix.

2000 Jan 13 29

Page 30

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

controller

EXTRA DECODER SETTINGS

ClDel and ClPer

XXClDel sets the delay from the rising edge of the

HSYNC/burstkey to the beginning of the internally

generated clamp pulse for signal XX in steps of 1 pixel.

XXClPer sets the pulse width of the internally generated

clamp pulse in steps of 1 pixel.

FidPos

Bit Fidpos defines the position of the field identification

window. The purpose is to set it so that the incoming

VSYNC is halfway up the window. This allows a spread of

1

⁄4line for the VSYNC (VCR and/or less sophisticated

decoder types) in steps of 2 pixels.

VGate

XVGate disables the detection of a next VSYNC for a

number of lines, after detecting an initial one in steps of

1 line.

SAB9079HS

SmlPal

If this bit is set to logic 1, the vertical acquisition and

display window for PAL is decreased from 276 lines to

258 lines

TGAct1, TGAct2, TColBar, TGenY, TGenU and TGenV

For test purposes, a built-in colour bar/ramp generator is

available which replaces the ADC digital output data. This

test generator is enabled if TGAct1 and TGAct2 are both

setto logic 1, and isdisabled when TGAct2 is setto logic 0

(it is recommended to set TGAct1 to logic 1). The test

pattern (common for main and sub channels) is set to

colour bar if TColBar is set to logic 1 and set to a ramp if

TColBar is set to logic 0. Both patterns start at a HSYNC

pulse. By use of bit(s) TGenX (active logic 1) the

Y, U and V of the pattern can be controlled independently.

Table 25 Extra decoder settings

SUB

ADDRESS

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

4FH SYClDel

50H SUClDel

51H SVClDel

52H −− SYClPer

53H −− SUClPer

54H −− SVClPer

55H SFidPos

56H −− SVGATE

57H MYClDel

58H MUClDel

59H MVClDel

5AH −− MYClPer

5BH −− MUClPer

5CH −− MVClPer

5DH MFidPos

5EH −− MVGATE

DATA BYTES

(7 : 0)

(7 : 0)

(7 : 0)

(5 : 0)

(5 : 0)

(5 : 0)

(7 : 0)

(5 : 0)

(7 : 0)

(7 : 0)

(7 : 0)

(5 : 0)

(5 : 0)

(5 : 0)

(7 : 0)

(5 : 0)

5FH SmlPal − TGAct1 TGAct2 TColBar TGenY TGenU TGenV

2000 Jan 13 30

Page 31

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

DACs

These are 8-bit DACs. The maximum output sample

frequency is 28 MHz.

Acquisition channel ADCs and clamping

Theanalog input signals are convertedto digital signals by

means of three ADCs. The resolution of the ADCs is 8-bit

(DNL is 7-bit, INL is 6-bit) and the sampling is done at the

system frequency of 14 MHz. The inputs should be

AC-coupled and an internal clamp circuit will clamp the

input to V

V

ref(T)(SA/MA)Vref(B)(SA/MA)

---------------------------------------------------------------------- -

ref(B)(SA/MA)

for the luminance channels and to

+

2

+

LSB

---------- 2

for the chrominance channels.

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DDD(P)

V

DDD(C)

V

DDA

P

max

T

stg

T

amb

V

ESD

digital supply voltage for the peripheral −0.5 +6.0 V

digital supply voltage for the core −0.5 +4.0 V

analog supply voltage −0.5 +4.0 V

maximum power dissipation − 1.5 W

storage temperature −25 +150 °C

ambient temperature 0 70 °C

electrostatic handling note 1 − 3000 V

The clamping starts at the active edge of the internally

generated clamp period signal. The clamp period signal,

generated from the HSYNC pulse, has a delay adjusted

with the XXCICel bits with respect to the HSYNC. Internal

video buffers amplify the standard input signals

Y*, U and V to the correct ADC levels. The bandwidth of

the input signals should be limited to 4.5 MHz for the

Y input and 1.125 MHz for the U and V inputs.

PLL

The PLL generates, from the HSYNC, an internal system

clock of 3584 HSYNC which is approximately 56 MHz.

The other system clocks are derived from this clock. They

are in the range 3584, 1792, 896 or 448 × HSYNC.

note 2 − 300 V

Notes

1. Human body model; see

2. Machine model; see

“UZW-B0/FQ-B302”

“UZW-B0/FQ-A302”

.

.

QUALITY SPECIFICATION

According to

the

“Quality Reference Handbook”

“SNW-FQ-611 Part E”

, dated 14 december 1992. The numbers of the quality specification can be found in

. The handbook can be ordered using the code 9397 750 00192.

THERMAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS VALUE UNIT

R

th(j-a)

thermal resistance from junction to ambient in free air 37 K/W

2000 Jan 13 31

Page 32

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

ANALOG CHARACTERISTICS

V

DDD(P)

= 5.0 V; V

DDD(C)

= 3.3 V; T

=25°C; unless otherwise specified.

amb

SYMBOL PARAMETER CONDITIONS MIN. TYPE MAX. UNIT

Supplies

V

DDD(P)n

all digital supply voltages for

4.5 5.0 5.5 V

the peripheral

V

DDD(C)n

all digital supply voltages for

3.0 3.3 3.6 V

the core

V

V

∆V

DDA

SS(n)

DD(max)

analog supply voltages 3.0 3.3 3.6 V

all ground voltages − 0 − V

maximum difference

− 0 100 mV

between supply voltages

∆V

SS(max)

maximum difference

− 0 100 mV

between ground voltages

I

DDD(q)

quiescent current of digital

note 1 − 050µA

supply voltages

I

VDDA(MP)

main PLL analog supply

− 0.4 − mA

current

I

VDDA(SP)

sub PLL analog supply

− 0.4 − mA

current

I

VDDA(MA)

I

VDDA(SA)

I

VDDA(DA)

I

DDA(tot)

I

DDD(tot)

main ADCs supply current note 2 − 78 96 mA

sub ADCs supply current note 2 − 78 96 mA

DACs supply current note 3 − 10 17 mA

total analog supply current − 170 210 mA

total digital supply current − 115 − mA

Analog-to-digital converter and clamping

V

Vref(T)(SA/MA)

V

Vref(B)(SA/MA)

V

iY(p-p)

top reference voltage note 4 2.65 2.82 2.95 V

bottom reference voltage note 4 0.95 1.08 1.20 V

input signal amplitude

note 5 − 1.00 1.04 V

(peak-to-peak value)

V

iV(p-p)

input signal amplitude

note 5 − 1.05 1.10 V

(peak-to-peak value)

V

iU(p-p)

input signal amplitude

note 5 − 1.33 1.38 V

(peak-to-peak value)

I

i

input current clamping off − 0.1 −µA

clamping on; note 2 − 55 −µA

C

i

f

s

input capacitance − 5 − pF

sample frequency note 6 − 896xHSYNC − kHz

RES resolution note 2 8 8 8 bit

DNL differential non-linearity note 2 −1.4 − +1.4 LSB

INL integral non-linearity note 2 −2.0 − +2.0 LSB

α

cs

channel separation − 48 − dB

PSRR power supply rejection ratio − 48 − dB

2000 Jan 13 32

Page 33

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

SYMBOL PARAMETER CONDITIONS MIN. TYPE MAX. UNIT

V

clamp(Y)

V

clamp(UV)

Digital-to-analog converter and output stage

V

Vref(T)(DA)

V

Vref(B)(DA)

R

L

C

L

f

s

RES resolution 8 8 8 bit

DNL differential non-linearity note 3 −1.0 − +1.0 LSB

INL integral non-linearity note 3 −1.0 − +1.0 LSB

α

cs

PSRR power supply rejection ratio note 3 − 48 − dB

Main PLL and clock generation

f

i(PLL)(main)

Sub PLL and clock generation

f

i(PLL)(sub)

Notes

1. Digital clocks are silent, POR connected to VDD.

2. Load resistance of V

3. The load resistance of DAC outputs is 1 kΩ.

4. The V

formulae:

clamping voltage level Y note 7 1.25 1.35 1.45 V

clamping voltage level UV note 8 1.80 1.95 2.10 V

top reference voltage 1.10 1.20 1.30 V

bottom reference voltage 0.15 0.22 0.30 V

load resistance 1 − 1000 kΩ

load capacitance 0 − 50 pF

sample frequency 1FH; note 6 − 1792HSYNC − kHz

2FH; note 6 − 896HSYNC − kHz

channel separation note 3 − 48 − dB

input frequency 1FH note 6 14 15.75 18 kHz

input frequency note 6 14 15.75 18 kHz

is 39 kΩ.

are made by a resistor division of V

. They can be calculated with the

DDA

Vref(T)(SA/MA)

bias(MA)/Vbias(SA)

and V

Vref(B)(SA/MA)

2V

a)

b)

V

V

Vref(T)(SA/MA)

Vref(B)(SA/MA)

V

DDA

V

DDA

5. The input signal is amplified to meet an internal peak-to-peak voltage level of V

ref(T)(nom)

-----------------------------V

DDA(nom)

V

ref(B)(nom)

-------------------------- V

DDA(nom)

V×=

V×=

Vref(T)(SA/MA)

− V

Vref(B)(SA/MA)

6. The internal system frequencies are 3584, 1792, 896 and 448 times the HSYNC input frequency.

7. The Y* channel is clamped to the V

Vref(B)(SA/MA)

8. The UV channels are clamped to 0.5 × (V

of the ADCs, which is derived from pin V

Vref(T)(SA/MA)+VVref(B)(SA/MA)+VLSB

). Where V

ref(B)(SA)

is one step of the ADC.

LSB

2000 Jan 13 33

and pin V

.

ref(B)(MA)

.

Page 34

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

COLOUR PATH CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

G

(conv)(MY)

G

(conv)(SY)

G

(conv)(MU)

G

(conv)(SU)

G

(conv)(MV)

G

(conv)(SV)

G

(conv)(DY)

G

(conv)(DU)

G

(conv)(DV)

MM

ADC(Y)

MM

ADC(U)

MM

ADC(V)

MM

ADC(YUV)

analog Y* input ADC conversion

gain for main channel

analog Y* input ADC conversion

gain for sub channel

analog U input ADC conversion

gain for main channel

analog U input ADC conversion

gain for sub channel

analog V input ADC conversion

gain for main channel

analog V input ADC conversion

gain for sub channel

analog Youtput ADC conversion

gain

analog U output ADC conversion

gain

analog Voutput ADC conversion

gain

analog YADC mismatch note 1 − 05%

analog U ADC mismatch note 1 − 05%

analog VADC mismatch note 1 − 05%

analog YUVADC mismatch note 1 − 05%

0.20 0.22 0.24 LSB/mV

0.20 0.22 0.24 LSB/mV

0.15 0.17 0.19 LSB/mV

0.15 0.17 0.19 LSB/mV

0.19 0.21 0.23 LSB/mV

0.19 0.21 0.23 LSB/mV

6.0 6.8 7.5 LSB/mV

6.0 6.8 7.5 LSB/mV

6.0 6.8 7.5 LSB/mV

Note

1. Mismatch = (max − min)/average.

2000 Jan 13 34

Page 35

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

DIGITAL CHARACTERISTICS

All V

DC characteristics

V

IH

V

IL

V

hys

V

OH

V

OL

I

LI

I

OZ

R

pu

AC characteristics

f

sys

t

r

t

f

pins = 3.0 to 3.6 V; T

DDD(C)

=0to70°C; unless otherwise specified.

amb

SYMBOL PARAMETER CONDITIONS MIN. TYPE MAX. UNIT

HIGH-level input voltage 70 −−%V

LOW-level input voltage −−30 %V

hysteresis voltage − 30 − %V

HIGH-level output voltage V

− 0.4 −−V

DDD(P)

LOW-level output voltage −−0.4 V

input leakage current V

3-state input leakage

= 3.6 V − 0.1 1 µA

DDD

V

= 3.6 V − 0.2 1 µA

DDD

current

internal pull-up resistor 23 50 80 kΩ

system frequency note 1 − 3584xHSYNC kHz

rise time − 625ns

fall time − 625ns

DDD

DDD

DDD

Note

1. The internal system frequencies are 3584, 1792, 896 and 448 times the HSYNC input frequency.

TEST AND APPLICATION INFORMATION

TV application with insertion before 100 Hz feature box (double window)

In the 100 Hz application the deflection circuit operates at 100 Hz. The PIP data is inserted into the main decoder output

stream and fed to the feature box. The double window feature is made at 1Fh and the field rate is doubled in the feature

box. The internal synchronization is illustrated in Fig.9.

handbook, full pagewidth

DECODER

DECODER

Y*UV

HV

HV

Y*UV

HV

SUB

MAIN AND

DISPLAY

Y*UV/RGB

FBL

SWITCH

FEATURE

BOX

MGS829

Y*UV

HV

Fig.9 1Fh/1Fv application with insertion before the feature box.

2000 Jan 13 35

Page 36

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

SLAVE 2FH GENERAL DESCRIPTION

In the slave mode the main and display channel has to

follow an external 2Fh, xFv signal. The main acquisition

cannot handle such a source, the main/display PLL can.

Thus no main channel PIP is available, only the

upconverted sub channel can be inserted. The following

functions are available in 4:1:1 only unless otherwise

indicated:

• Suitable for single PIP, multi PIP, replay and channel

overview applications

• Data formats 4 : 1 : 1 (all modes) and 4 :2:2 (some

modes)

• PIP OSD for the sub channels displayed

• Detection of PAL/NTSC with overrule bit

2FH,1FV ALGORITHMS

Table 26 Available 2Fh and 1Fv algorithms

ALGORITHM FORMAT 4 : 1 : 1 FORMAT 4 : 2 : 2 REMARKS

progressive scan yes no; note 1 proscan (median filtering)

line doubling yes yes note 2

• CTE and LTE like circuits in display part

• Replay with definable auto increment, picture sample

rate and picture number auto wrap

• Programmable Y*UV to RGB conversion matrix with

independent coefficients for NTSC and PAL sources

• Display clock and synchronization are derived from the

main channel PLL.

The following features are only available for the sub

channel:

• Sample rate of 14 Mhz, 720 Y* pixels/line

• Horizontal reduction factors1⁄

• Vertical reduction factors1⁄1,1⁄2,1⁄3and1⁄4.

1

⁄2,1⁄3,1⁄4and1⁄

1

6

Notes

1. Median filtering in 4:2:2 mode is allowed for single PIP (no main channel) and reduction factors not greater than

1

⁄2 for both horizontal and vertical

2. The performance of the line doubling algorithm is dependent on the picture content. Line (based interlace) flickering

will remain in this mode.

2FH,2FV ALGORITHMS

Table 27 Available 2Fh and 2Fv algorithms

ALGORITHM FORMAT 4 : 1 : 1 FORMAT 4 : 2 : 2 REMARKS

AABB field doubling yes yes

ABAB field doubling yes yes

AB’A’B fields interpolation

via median filtering

AB’A’B+ field interpolation

via median filtering and

averaging with original

fields

Note

1. Median filtering in 4:2:2 mode is allowed for single PIP (no main channel) and reduction factors not greater than

1

⁄2 for both horizontal and vertical

yes no; note 1 digital scan

yes no; note 1 digital scan plus

2000 Jan 13 36

Page 37

Philips Semiconductors Preliminary specification

Multistandard Picture-In-Picture (PIP)

SAB9079HS

controller

SLAVE 2FH AND XFV RELATED I2C-BUS REGISTERS

Table 28 Overview of the I2C-bus registers and their subaddresses

SUB

ADDRESS

01H D2FH D2FV −− MFld

02H YUVFilter

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

(1:0)

ABMode

D2FH and D2FV

These bits control the display mode with respect to 2Fh or 100 Hz features. If D2FH is set to logic 1 the number of lines

is doubled and/or if D2FV is set to logic 1 the number of fields is doubled.

ABMode

These bits select the different algorithms for 2Fh modes; see Table 29.

Algorithm selection

Several display algorithms can be set with these bits; an overview is given in Table 29.

DATA BYTES

(1:0)

(1:0)

CTE LTE

(2:0)

SFld

(1:0)

Note: BGVfp

The resolution of the MAVfp bits changes in 2Fh and xFv modes. In 2Fh and 1Fv modes the vertical resolution is