Page 1

LOW POWER DTMF RECEIVER S5T3170

INTRODUCTION

The S5T3170 is a complete Dual Tone Multiple Frequency (DTMF)

receiver that is fabricated by low power CMOS and the SwitchedCapacitor Filter technology. This LSI consists of band split filters,

which separates counting section which verifies the frequency and

duration of the received tones before passing the corresponding code

to the output bus. It decodes all 16 DTMF tone pairs into a 4bits digital

code. The externally required components are minimized by on chip

provision of a differential input AMP, clock oscillator and latched three

state interface. The on chip clock generator requires only a low cost

TV crystal as an external component.

FEATURES

• Detects all 16 standard tones.

• Low power consumption: 15mW (Typ)

• Single power supply: 5V

• Uses inexpensive 3.58MHz crystal

• Three state outputs for microprocessor interface

• Good quality and performance for using in exchange system

18−DIP−300A

20−SOP−375

• Power down mode/input inhibit

ORDERING INFORMATION

Device Package Operating

S5T3170X01-D0B0 18−DIP−300A

S5T3170X01-S0B0 20−SOP−375

− 25°C — + 75°C

APPLICATIONS

• PABX • Key Phone System

• Central Office • Answering Phone

• Paging Systems • Home Automation System

• Remote Control • Mobile Radio

• Credit Card Systems • Remote Data Entry

1

Page 2

S5T3170 LOW POWER DTMF RECEIVER

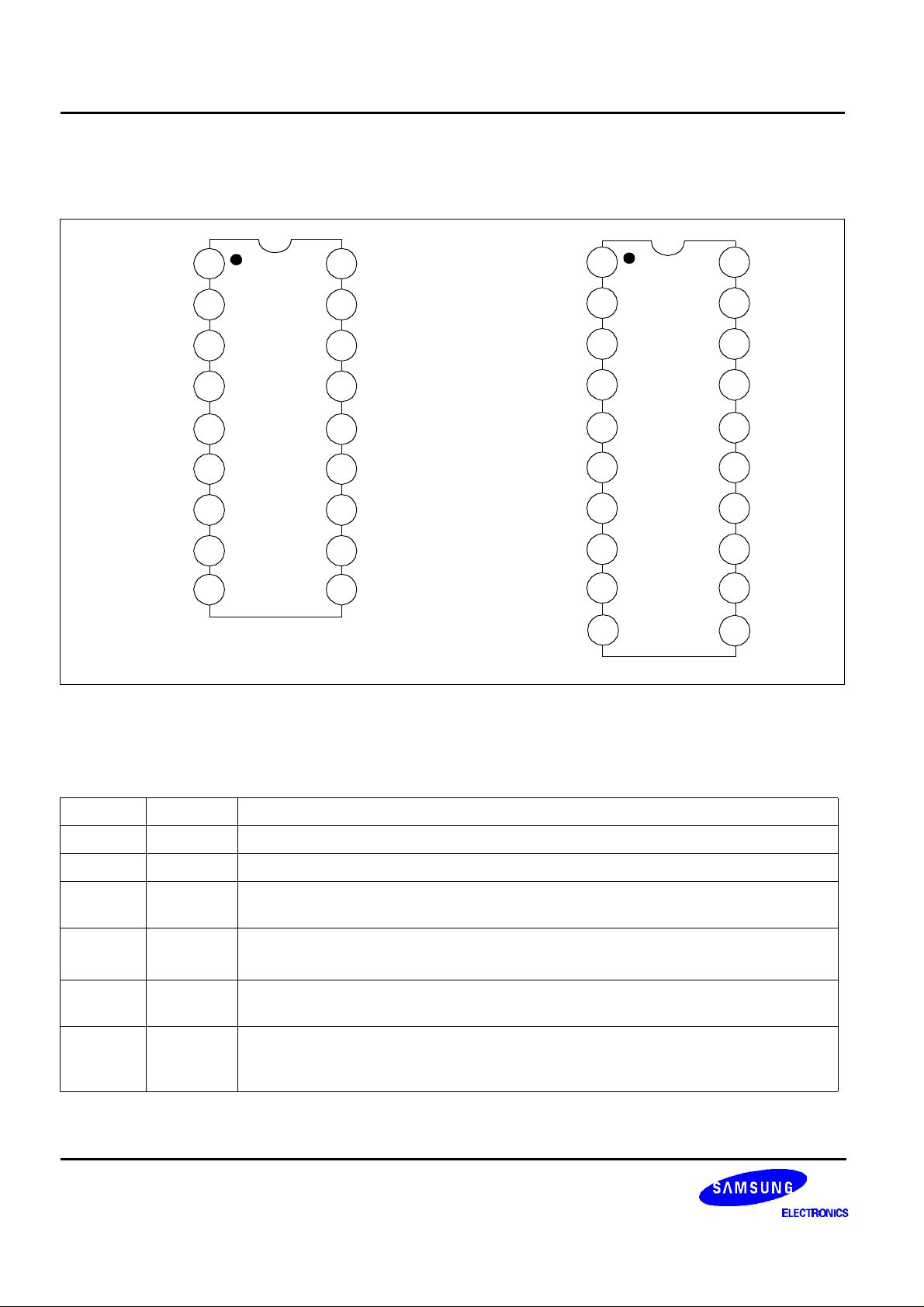

PIN CONFIGURATION

IN+

IN-

GS

V

REF

PDN

OSC1

OSC2

GND

1

2

3

4

I

IN

5

S5T3170

6

7

8

9 10

(18-DIP)

18

17

16

15

14

13

12

11

V

DD

SI/GTO

ESO

DSO

Q4

Q3

Q2

Q1

OE

IN+

IN-

GS

V

REF

PDN

NC

OSC1

OSC2

GND

1

2

3

4

I

IN

5

S5T3170

6

7

8

9 12

10

(20-SOP)

20

19

18

17

16

15

14

13

11

V

DD

SI/GTO

ESO

DSO

NC

Q4

Q3

Q2

Q1

OE

PIN DESCRIPTION

Pin No Symbol Description

1 IN + Non inverting input of the internal amp.

2 IN − Inverting input of the internal amp.

3 GS Gain Select.

The output used for gain adjustment of analog input signal with a feedback resistor.

4 V

5 I

REF

IN

6 PDN Control input for the stand-by power down mode.

Reference Voltage output (VDD/2, Typ) can be used to bias the internal amp input of

VDD/2.

Input inhibit.

High input states inhibits the detection of tones. This pin is pulled down internally.

Power down occurs when the signal on this input is in high states. This pin is pulled

down internally.

2

Page 3

LOW POWER DTMF RECEIVER S5T3170

PIN DESCRIPTION (Continued)

Pin No Symbol Description

7, 8 OSC1

OSC2

Clock input/output.

A inexpensive 3.579545MHz crystal connected between these pins completes internal

oscillator. Also, external clock can be used.

9 GND Ground pin.

10 OE Output Enable input.

Outputs Q1-Q4 are CMOS push-pull when OE is High and open circuited (High

impedance) when disabled by pulling OE low. Internal pull up resistor built in.

11 - 14 Q1 - Q4 Three state data output.

When enabled by OE, these digital outputs provide the hexadecimal code

corresponding to the last valid tone pair received.

15 DSO Delayed Steering Output.

Indicates that valid frequencies have been present for the required guard time, thus

constituting a valid signal. Presents a logic high when a received tone pair has been

registered and the output latch is updated.

Returns to logic low when the voltage on SI/GTO falls below VTH.

16 ESO Early Steering Outputs.

Indicates detection of valid tone output a logic high immediately when the digital

algorithm detects a recognizable tone pair.

Any momentary loss of signal condition will cause ESO to return to low.

17 SI/GTO Steering Input/Guard Time Output.

A voltage greater the V

detected at SI causes the device to register the detected

TS

tone pair and update the output latch. A voltage less than VTS frees the device to

accept a new tone pair. The GTO output acts to reset the external steering time

constant, and its state is a function of ESO and the voltage on SI

18 V

DD

Power Supply (+5V, Typ)

ABSOLUTE MAXIMUM RATINGS

Characteristics Symbol Value Unit

Power Supply Voltage V

Analog Input Voltage Range V

Digital Input Voltage Range V

Output Voltage Range V

Current On Any Pin I

Operating Temperature T

Storage Temperature T

DD

I (A)

I (D)

O

I

OPR

STG

6 V

− 0.3 — VDD + 0.3 V

− 0.3 — VDD + 0.3 V

− 0.3 — VDD + 0.3 V

10 V

− 40 — + 85 mA

− 60 — + 150 °C

3

Page 4

S5T3170 LOW POWER DTMF RECEIVER

ELECTRICAL CHARACTERISTICS

(VDD = 5V, Ta = 25°C, unless otherwise noted)

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Operating Voltage V

Operating Current I

Power Dissipation P

Input Voltage Low V

Input Voltage High V

Input Leakage Current I

I (LKG)

Pull Up Current On OE Pin I

Analog Input Impedance R

Steering Input Threshold Voltage V

Output Voltage Low V

V

Output Current (Sinking) I

Output Current (Sourcing) I

V

Output Voltage V

REF

V

Output Resistance R

REF

O (SINK)

O (SOURCE)VOH

O (REF)

O (REF)

Analog Input Offset Voltage V

DD

DD

PU

TH

OL

OH

IH

IO

D

IL

VIN = GND or V

OE = GND − 7.5 15 µA

I

fIN = 1KHz 8 10 − MΩ

No Load − − 0.03 V

No Load 4.97 − − V

VOL = 0.4V 1 2.5 − mA

− 4.75 − 5.25 V

− − 3.0 9.0 mA

− − 15 45 mW

− − − 1.5 V

− 3.5 − − V

DD

− 2.2 − 2.5 V

= 4.6V 0.4 0.8 − mA

− 2.4 − 2.8 V

− − 10 − KΩ

− − 25 − mV

Power Supply Rejection Ratio PSRR Gain Setting Amp at

1KHz

− 0.1 − m

− 60 − dB

Common Mode Rejection Ratio CMRR − 3.0V < VIN < 3.0V − 60 − dB

Open Loop Voltage Gain G

V

Gain Setting Amp at

− 65 − dB

1KHz

Open Loop Unit Gain Bandwidth BW − − 1.5 − MHz

Analog Output Voltage Swing V

O (P-P)

Acceptable Capacitive Load C

Acceptable Resistive Load R

Analog Input Common Mode

V

L

L

CM

RL = 100K − 4.5 − V

P-P

GS − 100 − pF

GS − 50 − KΩ

No Load − 3.0 − V

P-P

Voltage Range

Valid Input Signal Range

V

I(VAL)

− −29 − 1.0 dBm

(each tone of composite signal)

Dual Tone Twist Accept TW − − ±10 − dB

Acceptable Frequency Deviation ∆f − − − ±1.5%

−

± 2Hz

Frequency Deviation Reject ∆f

R

− ±3.5% − − −

4

Page 5

LOW POWER DTMF RECEIVER S5T3170

ELECTRICAL CHARACTERISTICS (Continued)

(VDD = 5V, Ta = 25°C, unless otherwise noted)

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Third Tone Tolerance T3rd − −25 −16 − dB

Noise Tolerance TN − − −12 − dB

Dial Tone Tolerance DT − 18 22 − dB

Crystal Clock Frequency f

Maximum Clock Input Rise Time t

Maximum Clock Input Fall Time t

R(MAX)

F(MAX)

Acceptable Clock Input Duty Cycle D

Acceptable Capacitive Load D

Tone Present Detect Time t

Tone Absent Detect Time t

Minimum Tone Duration Accept t

Minimum Tone Duration Reject t

Acceptable Interdigit Pause t

Rejectable Interdigit Pause t

Propagation Delay Time SI to Q t

Propagation Delay Time SI to DSO t

DET(P)

DET(A)

TDA(MIN)

TDR(MAX)

IDP(A)

IDP(R)

D(SI-Q)

D(SI-D)

Output Data Setup Q to DSO t

Propagation Delay Time OE to Q

t

D(QE-Q)EN

(Enable)

Propagation Delay Time OE to Q

t

D(QE-Q)DIS

(Disable)

CK

CK

SU

− 3.5759 3.5795 3.5831 MHz

External Clock − − 110 nS

External Clock − − 110 nS

External Clock 40 50 60 %

L

OSC2 PIN − − 30 pF

− 5 11 14 mS

− 0.5 4 8.5 mS

User Adjustable − − 40 mS

User Adjustable 20 − − mS

User Adjustable − − 40 mS

User Adjustable 20 − − mS

OE = High − 8 11 µS

OE = High − 12 16 µS

OE = High − 3.4 − µS

RL = 10K, CL = 50pF − 50 60 nS

RL = 10K, CL = 50pF − 300 − nS

NOTES:

1. Digit sequence consists of all 16 DTMF tones.

2. Tone duration = 40mS, Tone pause = 40mS.

3. Nominal DTMF frequencies are used.

4. Both tones in the composite signal have an equal amplitude.

5. Tone pair is deviated by ± 1.5% ± 2Hz.

6. Bandwidth limited (3KHz) Gaussian Noise.

7. The precise dial tone frequencies are (350Hz and 440Hz) ± 2%.

8. For an error rate of better than 1 in 10000.

9. Referenced to lowest level frequency component in DTMF signal.

10. Minimum signal acceptance level is measured with specified maximum frequency deviation.

11. This item also applies to a third tone injected onto the power supply.

12. Referenced to Fig. 1 Input DTMF tone level at -28dBm.

5

Page 6

S5T3170 LOW POWER DTMF RECEIVER

TEST CIRCUIT

9

8

6

5

4

3

15

R1

100K

2

16

17

181

100K

R2

X - tal 1

4 5 6

7 8 9

*

0

#

321

V

CC

7

KS58006

S5T5820C

10

11

12

13

14

0.1µF

X - tal 2

Fig. 2

8

7

9 10

S5T3170

12

11

7

5

6

6

KT3170

13

4

4

5

15

14

LED

2

3

1

2

3

18

17

16

300K

1

V

CC

R3

C1

HL74HCTLS02

14

12

11

8

GND

8

9

6

5

7

ABI

d

4

RDO

13

3

1102

b

c

LT

V

CC

V

CC

HL74LS47

V

g

a

c

d

13

12

11

10

9

R9

R8

R7

R6

R5

R4

CC

f

16

15

14

R10

V

CC

10

a

1

2 3

V

CC

comd

4 5

c dp

g

f

com

a b

9 8 7 6

LTS542R

Figure 1. Test Circuit

6

Page 7

LOW POWER DTMF RECEIVER S5T3170

TIMING DIAGRAM

t

TDR (MAX)

t

TDA (MIN)

t

IDP (A)

t

IDP (R)

DTMF

INPUT

ESO

SI/GTO

Q1 - Q4

DSO

DECODED TONE # (n - 1)

t

DET (P)

t

D (SI-D)

DTMF #n DTMF #n + 1

t

DET (A)

t

PGT

t

SU

t

AGT

DTMF #n + 1

V

TH

OE

Figure 2. Timing Diagram

t

D (OE-Q) EN

t

D (OE-Q) DIS

7

Page 8

S5T3170 LOW POWER DTMF RECEIVER

DIGITAL OUTPUT

Outputs Q1-Q4 are CMOS push pull when enabled (EO = High) and open circuited (high impedance) when

disabled by pulling EO = Low. These digital outputs provide the hexadecimal code corresponding to the DTMF

signals. The table below describes the hexadecimal.

NO Low Frequency High Frequency OE Q4 Q3 Q2 Q1

1 697 1209 H 0 0 0 1

2 697 1336 H 0 0 1 0

3 697 1477 H 0 0 1 1

4 770 1209 H 0 1 0 0

5 770 1336 H 0 1 0 1

6 770 1477 H 0 1 1 0

7 852 1209 H 0 1 1 1

8 852 1336 H 1 0 0 0

9 852 1477 H 1 0 0 1

0 941 1336 H 1 0 1 0

* 941 1209 H 1 0 1 1

# 941 1477 H 1 1 0 0

A 697 1633 H 1 1 0 1

B 770 1633 H 1 1 1 0

C 852 1633 H 1 1 1 1

D 941 1633 H 0 0 0 0

ANY - - L Z Z Z Z

NOTE:

Z : High Impedance

H : High Logic Level

L : Low Logic Level

8

Page 9

LOW POWER DTMF RECEIVER S5T3170

APPLICATION CIRCUIT

+5V

0.1uF

100K

100K

3.58MHz

IN+

IN-

GS

V

REF

I

IN

PDN

OSC1

OSC2

GND

V

DD

SI/GTO

ESO

DSO

Q4

Q3

Q2

Q1

OE

300K

All resistors are 1% tolerance

All capacitors are 5% tolerance

Figure 3. Single Ended Input Configuration

0.1uF

10nF

C1 R1

10nF

C2 R2

100K

100K

R3

37.5K

R2

60K

R5

100K

V

IN+

INGS

REF

R3 = R2R5/(R2+R5), VOLTAGE GAIN = R5/R1

2

INPUT IMPEDANCE : + (1/wC)

2

R

1

All resistors are 1% tolerance

All resistors are 1% tolerance

All capacitors are 5% tolerance

1

+

_

2

3

S5T3170

4

2

Figure 4. Differential Ended Input Configuration

9

Page 10

S5T3170 LOW POWER DTMF RECEIVER

V

DD

SI/GTO

R1

ESO

t

= (R1C) In (VDD/VDD-VTH)

PGT

t

= (RPC) In (VDD/V

AGT

RP = R1R2/(R1 + R2)

Decreasing t

AGT

(t

PGT

C

R2

)

TST

> t

)

AGT

Figure 5. Guard Time Adjustment

S5T3170

OSC1

OSC2

30pF

OSC1

3.579545MHz

OSC2

SI/GTO

R1

ESO

t

= (RPC) In (VDD/VDD-VTH)

PGT

t

= (R1C) In (VDD/VTH)

AGT

RP = R1R2 (R1 + R2)

Decreasing t

S5T3170

PGT

(t

PGT

R2

< t

C

AGT

)

10

TO OSC1 of next S5T3170

Figure 6. Oscillator Connection

Loading...

Loading...