Page 1

TV SOUND MPX FOR TWO CARRIER SYSTEM S1A0688C01

INTRODUCTION

32−SDIP−400

The S1A0688C01 is a monolithic integrated circuit designed for

demodulating two carrier TV-MPX broadcast.

FEATURES

• 1st & 2nd Sound IF

• Double-PLL FM Detection

• AGC for CCA part

• Matrix for Multi-Sound Broadcasts

• Pilot Detector

• External Control Interface

• ID Indicators (Stereo, Bilingual)

• Available for Korea standard

• Non-clipping Output up to 400% modulation with AGC

• Available in DC control, Normal microcontroler control or IIC bus control systems

• ID output: Direct LED drive or IIC serial data output

• Non-adjust

ORDERING INFORMATION

Device Package Operating Temperature

S1A0688C01-A0B0 32−SDIP−400 −10 to + 70 °C

1

Page 2

S1A0688C01 TV SOUND MPX FOR TWO CARRIER SYSTEM

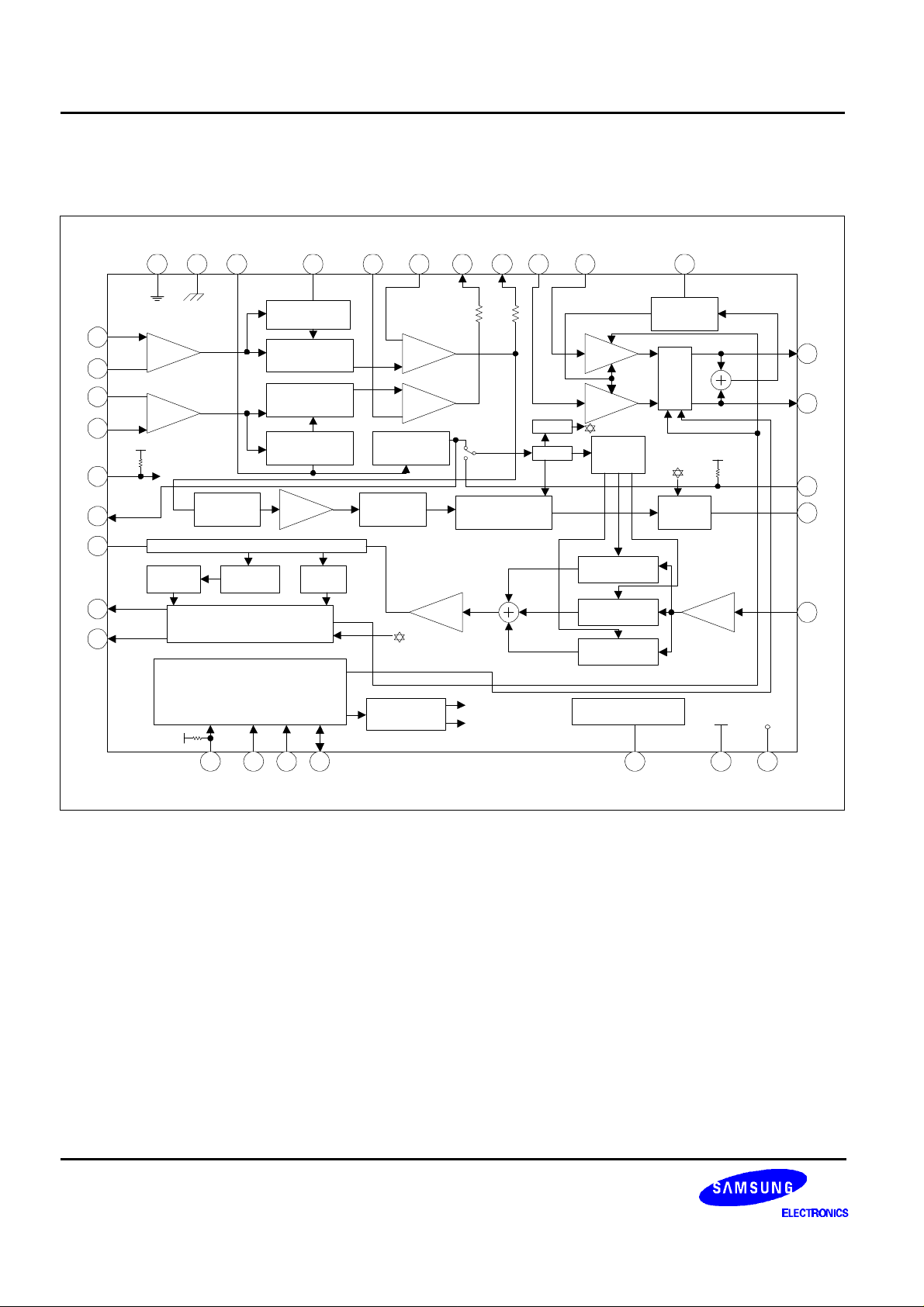

BLOCK DIAGRAM

1 19 7 6 8 9 10 12 11 13 14

31

30

17

23

24

GND VSS

2

IF

3

4

IF

5

S1

4.72MHz

1st PLL

4.72MHz

2nd PLL

4.5MHz

2nd PLL

4.5MHz

1st PLL

4.3MHz

VCO

A

A

1/39

S1

1/2

CCA

CCA

1/100

1/370

1/200

AGC

AMP

MATRIX

18

15

29

30KHz

HPF

OFFSET CANCELLER

DN

CUT COMP

DIGITAL FREQUENCY

DETECTOR

CONTROL TYPE

AUTO DETECT

U-COM INTERFACE

(DC/3-LINE U-COM/IIC-BUS)

X20

MN

DET

100KHz

LPF

ZAPPING

BLOCK

55.1KHz

SC BPF AM DET

150Hz

SC BPF

X3

CCA

PLL

276Hz

SC BPF

390Hz

SC BPF

VOLTAGE

REFERENCE

X8

VCC VDD

26

27

28 22 21 20 32 16 25

2

Page 3

TV SOUND MPX FOR TWO CARRIER SYSTEM S1A0688C01

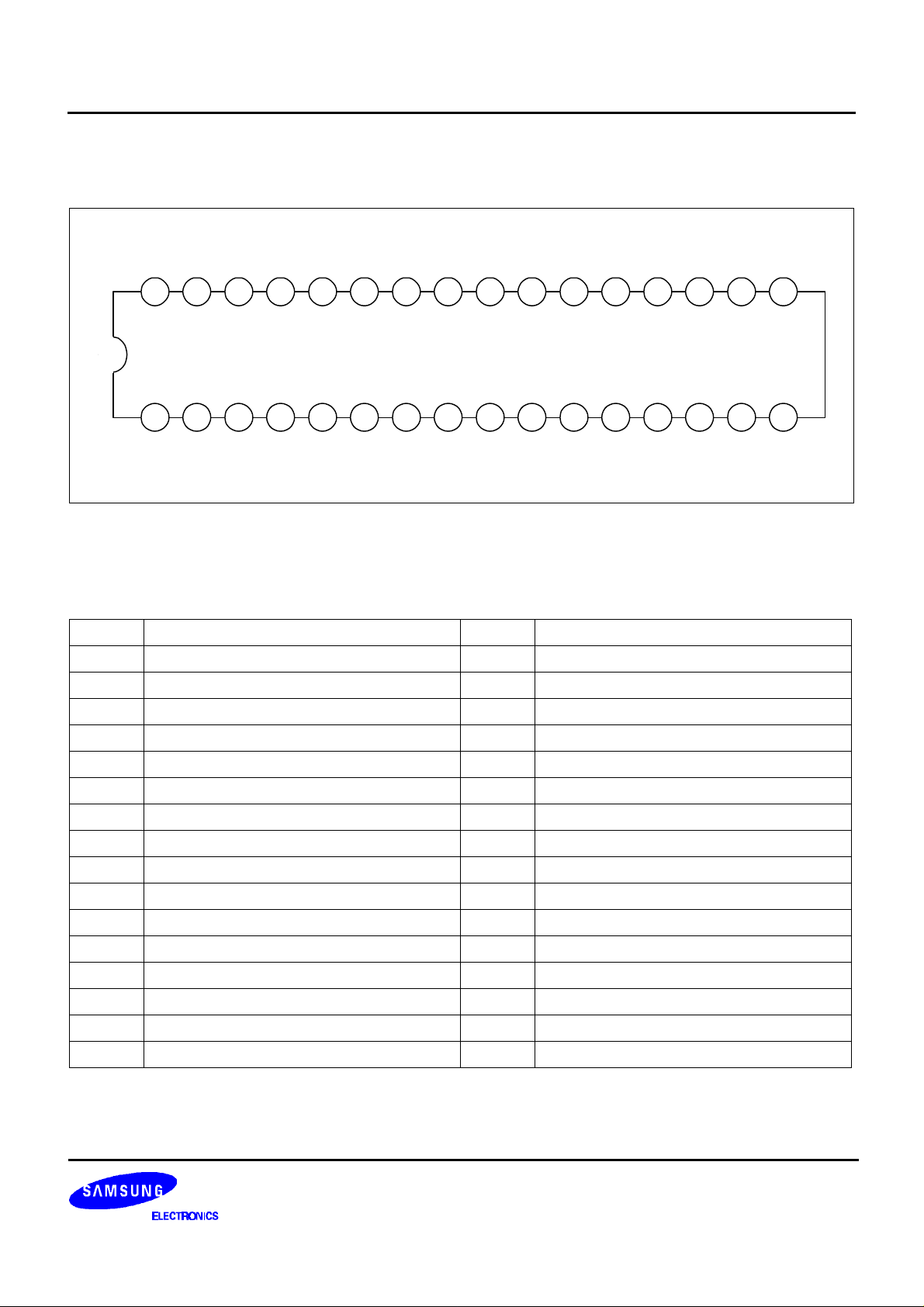

PIN CONFIGURATION

RC TMS RCM ECI SCC FDI ADO VDD BIB STB EN SCL VSSSDA RO OFC

26 2528 2730 2932 31

S1A0688C01

GND

IF2 BP2 BP1 IF1 LPC2 LPC1 AC1 AC2 S1O S1I S2O AGCS2I LO VCC

24 23 22 21 20 19 18 17

161514131 2 3 4 5 6 7 8 9 10 11 12

PIN DESCRIPTION

Pin No. Description Pin No. Description

1 Analog GND 17 ID Filter Offset Canceling Cap.

2 SIF 2 Input 18 R Output

3 SIF 2 Bypass 19 Digital VSS

4 SIF 1 Bypass 20 Data Input / Output (SDA)

5 SIF 1 Input 21 Clock Input (SCL)

6 SIF 2 LPF Capacitor 22 Enable Input (EN)

7 SIF 1 LPF Capacitor 23 ID Indicator (Stereo)

8 SIF 1 Amplifier Capacitor 24 ID Indicator (Bilingual)

9 SIF 2 Amplifier Capacitor 25 Digital VDD

10 SIF 1 DET Output 26 AM DET Output

11 SIF 1 CCA Input 27 Frequency DET Input

12 SIF 2 DET Output 28 Slave Custom Code

13 SIF 2 CCA Input 29 External Clock In

14 AGC Detect Capacitor 30 Reference Clock Monitor

15 L output 31 Test Mode Switch

16 Analog VCC 32 Voltage Reference Capacitor

3

Page 4

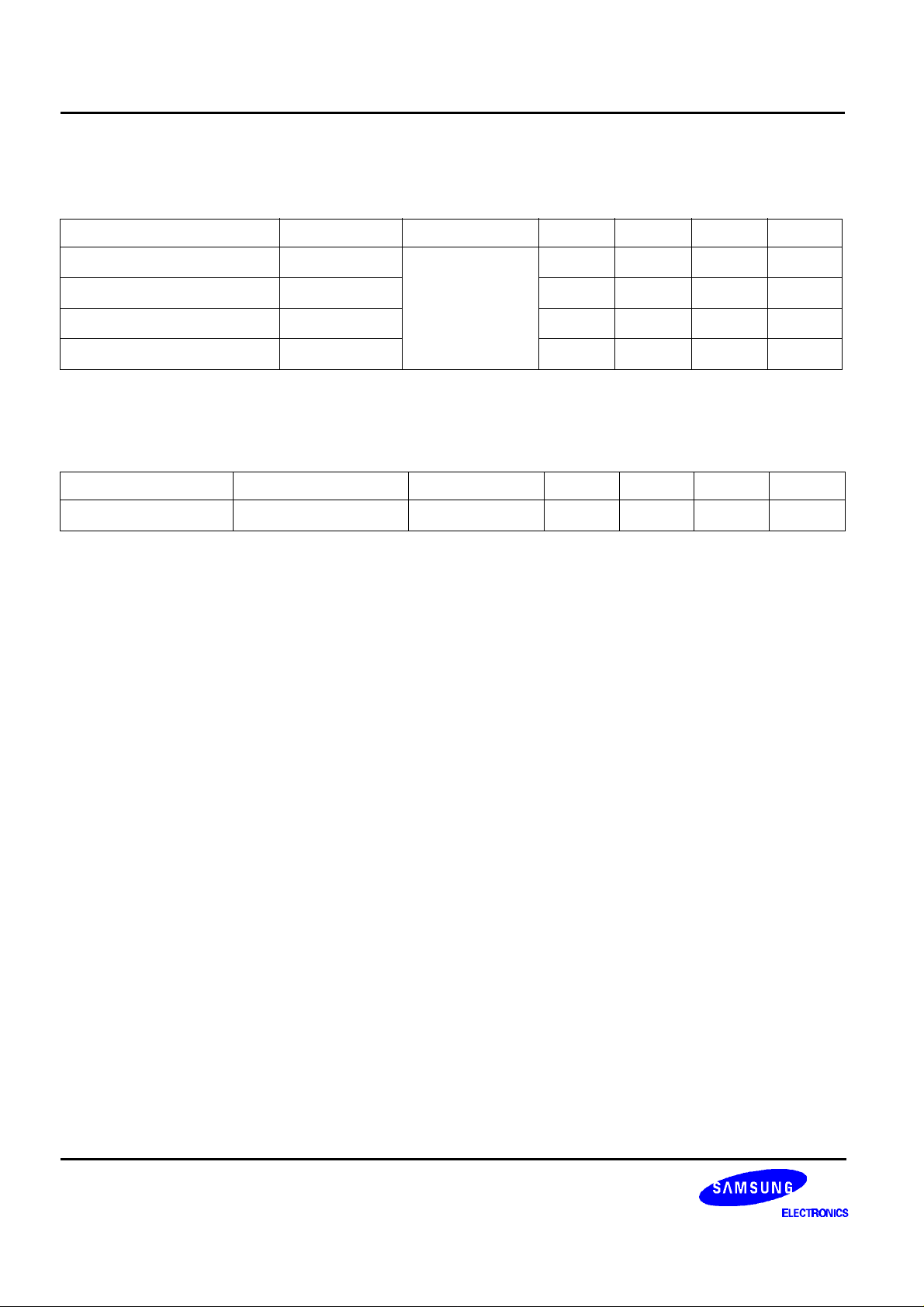

S1A0688C01 TV SOUND MPX FOR TWO CARRIER SYSTEM

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Condition Min. Typ. Max. Unit

Maximum Supply voltage VCC

Power Dissipation P

Operating temperature T

Storage temperature T

D

OPR

STG

max

Ta = 25 °C

VI = 0

RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Condition Min. Typ. Max. Unit

Operating Voltage V

OPR

− − 6 V

− − 1000 mW

− 10 − 70 °C

− 40 − 125 °C

− 4.7 5 5.5 V

4

Page 5

TV SOUND MPX FOR TWO CARRIER SYSTEM S1A0688C01

ELECTRICAL CHARACTERISTICS

DC Electrical Characteristics

(Ta = 25°C, VCC = VDD = 5V, fm = 1kHz, VI = 80dBµ, ∆f = ± 25kHz, unless otherwise specified)

Parameter Symbol Condition Min. Typ. Max. Unit

ICC Vi = 0 35 60 85 mA

IDD Vi = 0 − − 2.0 mA

SIF Input Limiting Voltage Vlim − − − 50 dBµ

AM Rejection Ratio AMRR AM 30% Mod 40 55 − dB

Input Impedance Zin − − 1 − Kohm

PILOT*Pilot Input Sensitivity Vps − − − 50 dBµ

ID ON time Ton MONO → ST, BI − 1.0 1.5 SEC

ID OFF time Toff ST, BI → MONO − − 0.3 SEC

Output level Vo − 320 420 520 mVrms

Matrix Matrix THD THDm1 − − 0.2 1.0 %

THDm2 ∆ f = ± 100kHz − 0.5 5.0 %

Noise Output (RF off) Voff Carrier OFF − − 400 mVrms

Output Impedance Zout − − − 50 ohm

Separation Ratio SEPtyp non-adjust 25 − − dB

SEPadj IIC Bus adjust 40 45 − dB

Cross Talk CT ∆ f = ± 25kHz 50 55 − dB

Matrix S/N Ratio S/N ∆ f = ± 25kHz 55 60 − dB

S/N(st) ∆ f = ± 25kHz (ST) 50 55 − dB

MUTE Attenuation

Ratio

* : Pilot signal FM deviation is ± 2.5kHz after 50% AM modulation.

Amute ∆ f = ± 25kHz − −66 −55 dB

5

Page 6

S1A0688C01 TV SOUND MPX FOR TWO CARRIER SYSTEM

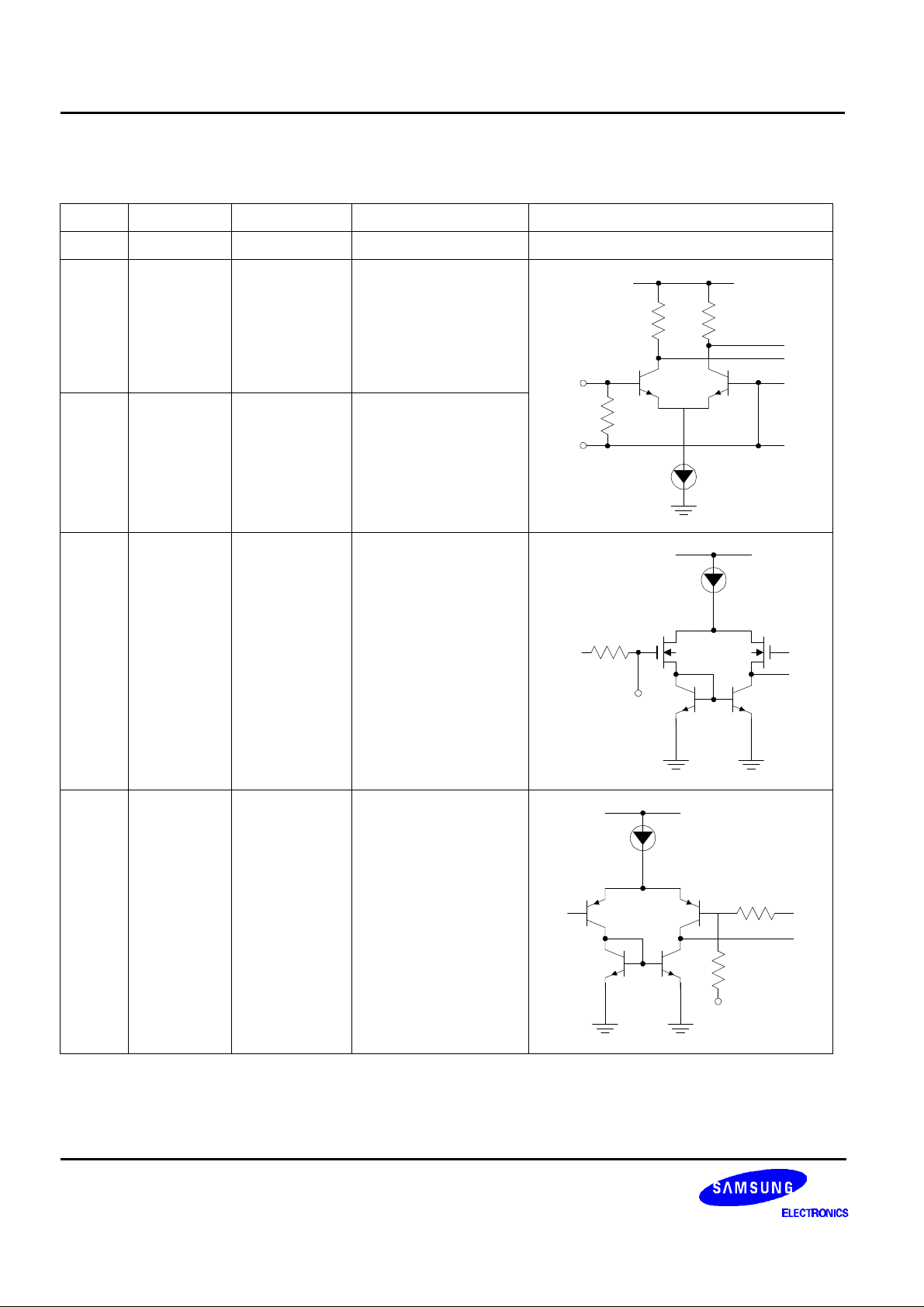

PIN DESCRIPTION

Pin No. Symbol Pin Name Description Internal Equivalence Circuit

1 GND Analog ground − −

2, 5 SIF2, SIF1 SIF input pin SIF signal input through

a SIF filter

IF1

(IF2)

3, 4 BP2, BP1 IF bypass pin IF Bypass pin is

grounded with a

capacitor

6, 7 LPC2, LPC1 PLL LPF pin The external capacitor

extracts DC level from

the 1st PLL output of

FM DET.

BP1

(BP2)

8, 9 AC1, AC2 DET AMP NF

pin

LPC1

(LPC2)

Negative feedback pin

of FM DET amplifier

Grounded with a

capacitor

AC1

(AC2)

6

Page 7

TV SOUND MPX FOR TWO CARRIER SYSTEM S1A0688C01

PIN DESCRIPTION (Continued)

Pin No. Symbol Pin Name Description Internal Equivalence Circuit

10, 12 S1O, S2O FM DET output FM DET output pin

connected with a deemphasis circuit

S1O

(S2O)

11, 13 S1I, S2I FM detected

signal input pin

Input pin of current

control amplifier (CCA).

FM detected output

signal is added to this

pin.

14 AGC AGC DET pin AGC detect pin is

grounded through a

capacitor. If the signal

level is over the

predetermined value,

this terminal voltage will

be raised. AGC function

can be deactivated by

connect this terminal to

GND.

S1I

(S2I)

BIAS

AGC

7

Page 8

S1A0688C01 TV SOUND MPX FOR TWO CARRIER SYSTEM

PIN DESCRIPTION (Continued)

Pin No. Symbol Pin Name Description Internal Equivalence Circuit

15, 18 LO, RO Matrix output

pin

Audio output signal is

provided from this pin.

16 VCC Analog power − −

17 OFC ID BPF offset

cancel pin

The external capacitor

is used to eliminate

offset of ID filter

OFC

LO

(RO)

19 VSS Digital ground – –

20 SDA Serial data

input and

output

It is the data

communication line of

IIC bus used to

exchange the MICOM

SDA

data and IC internal

data.

21 SCL Clock signal CLOCK line of IIC bus.

SCL

8

Page 9

TV SOUND MPX FOR TWO CARRIER SYSTEM S1A0688C01

PIN DESCRIPTION (Continued)

Pin No. Symbol Pin Name Description Internal Equivalence Circuit

22 EN Enable select

pin

23 STB Stereo

indicator pin

24 BIB Bilingual

indicator pin

25 VDD Power supply

(Digital)

26 ADO AM DET output

pin

It is always “H” in DC

control system, always

“L” in IIC bus system,

and used as strobe port

in normal MICOM

system.

When ID is detected as

STEREO, this pin will

remain “L” (OPEN

DRAIN).

When ID is detected as

Bilingual, this pin will

remain “L” (OPEN

DRAIN).

− −

AM detected signal will

output from this

terminal.

EN

STB

BIB

27 FDI Frequency

DET input pin

ADO

AM detected signal

goes into this terminal

coupled with a

capacitor to remove DC

offset.

FDI

9

Page 10

S1A0688C01 TV SOUND MPX FOR TWO CARRIER SYSTEM

PIN DESCRIPTION (Continued)

Pin No. Symbol Pin Name Description Internal Equivalence Circuit

28 SCC Slave custom

code

29 ECI External clock

input pin

30 RCM Reference

clock monitor

When Open:

Slave Address =

84H (Write), 85 (Read)

When connect to VSS:

Slave Address =

86H (Write), 87 (Read)

Normal is open.

It can be used as high

speed test for IC maker.

Internal Reference

Clock Monitor IC maker

test option

SCC

ECI

RCM

31 TMS Test mode

Switch

32 RC Voltage

Reference

Capacitor pin

Normal State: Open

Test State: VSS

IC maker test option

TMS

Connect to capacitor to

stabilize the reference

voltage

RC

10

Page 11

TV SOUND MPX FOR TWO CARRIER SYSTEM S1A0688C01

OPERATION DESCRIPTION

SYSTEM

S1A0688C01 consists of IF AMP, FM DET, AGC, MATRIX, U-COM Control INTERFACE and ID DET blocks. All

blocks are operable and available without adjust for Korea standard broadcast system.

IF AMP BLOCK

This block amplifies the provided IF signal to a detectable level of FM DET. Total gain is over 60dB and bandwidth

is about 3 − 10MHz.

FM DET

S1A0688C01 adopts non-adjust double-PLL type FM detection circuits. First PLL has a role of chasing FM carrier

frequency with wide holding range (for example, hold range is 2MHz) and second PLL does actual FM detection

with narrow holding range (about 300kHz), The free running frequency of 2nd PLL is same as the lock frequency of

1 st. PLL, and free running frequency of 1 st. PLL is determined by internal Resistor and Capacitor. The free run-

ning frequency can be varied by the variation of resistor and capacitor.

AGC

The AGC block comprises AGC detector part and CCA part (Current control Amplifier). The MATRIX output signal

level is set to 400mVrms when applied 100% modulated FM signal and supply voltage is 5V. As the gain of CCA is

about 6 dB and the gain of matrix is 6dB, so the output signal level of CCA is 200 mVrms and the matrix output is

400 mVrms. If over- modulated (over 200%) FM signal is added to S1A0688C01 input port, the output will be

clipped by supply voltage dynamic limitation range (The linear amplify range is limited lower than 800 mVrms).

To prevent this problem, In S1A0688C01 we use AGC circuit to reduce the gain of CCA part when the over- modulated FM signal has been applied, AGC circuit is deactivated until the modulation is over 200%. If AGC is activated,

the THD and separation characteristics of output signal would be deteriorated because the gain of CCA is varied

according to modulation ratio.

11

Page 12

S1A0688C01 TV SOUND MPX FOR TWO CARRIER SYSTEM

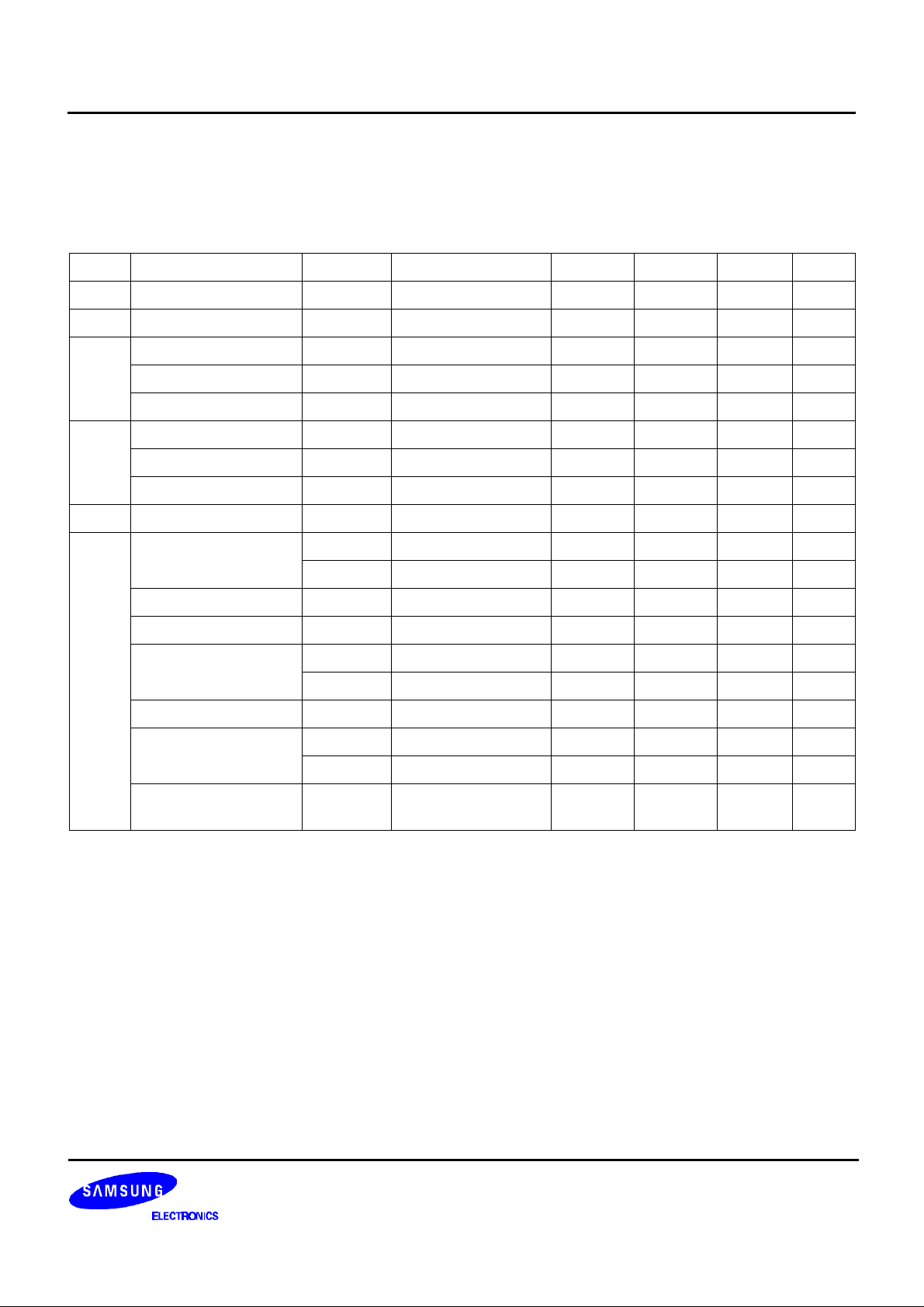

MATRIX

MATRIX part separates provided FM detected signal into MONO, STEREO, BILINGUAL, and SUB according to

broadcast status and end users setting, it mainly consists of analog switches and operational amplifiers. The input

and output signal format of MATRIX is shown as follows.

Broadcast Mode

S1 S2 Remark

Stereo L+R L−R −

Bilingual Main Sub −

Mono Main None * * can be main

User Select Output

Stereo Bilingual Sub Mono

Broadcast Mode LOUT ROUT LOUT ROUT LOUT ROUT LOUT ROUT

Stereo 2L 2R L+R L+R L+R L+R L+R L+R

Bilingual Main Main Main Sub Sub Sub Main Main

Input

Mono Main Main Main Main Main Main Main Main

12

Page 13

TV SOUND MPX FOR TWO CARRIER SYSTEM S1A0688C01

ID DET

ID signal is FM modulated to second carrier (SIF2) with a 2.5kHz FM modulation after AM modulated to 55kHz

PILOT sub-carrier with a 50% AM modulation. ID DET part consists of 3 blocks: that is filter block for extracting pilot

carrier, AM detector block for AM detection of ID signal and digital block for detecting the frequency of provided ID

signal logically. In the filter block, audio signal is removed by HPF and pilot signal is extracted by the automatically

adjusted switch - capacitor BPF (band pass filter) with a center frequency of 55kHz. ID signal is extracted from the

pilot carrier in the AM detector block, then Digital block detects the frequency of ID signal, The ID signal can be

detected in the range shown as follow:

ID Low Off Low On High On High Off

Stereo (150 Hz) 125 Hz 140 Hz 160 Hz 176 Hz

Bilingual (276 Hz) 237 Hz 255 Hz 300 Hz 312 Hz

This block’s circuit is configured to reduce the blinking of the ID, and consequently has the following characteristics: typ 1 sec and Max 1.5 sec delay when converting from Mono to Stereo, or to Bilingual. 0.3 sec delay when

converting from Stereo or Bilingual to Mono. Therefore, when changing the channels on your TV set, a minimum of

1.5 sec is needed for ID Detect Time.

Broadcast

S1A0688C01

Set MICOM

Mono

Mono

Mono

T1

T2

Stereo or Bilingual

Stereo or Bilingual

Stereo or Bilingual

T1: S1A0688C01’s ID Detect Time typ 1 sec, Max 1.5 sec

T2: When changing channels, set MICOM’s ID Detect Delay Time to a minimum of 1.5 sec.

Figure 1. Timing Diagram for Changing Channels from Mono to stereo or Bilingual

The ID Detect Block of the S1A0688C01 can momentarily malfunction if the signal is weak. Hence, we recommend

that you delay for at least 1 sec at Set MICOM before detecting the ID, if the ID changes at a fixed channel.

Broadcast

S1A0688C01

Set MICOM

Mono

Mono

Mono

T3

T1

T3

Stereo or Bilingual

Stereo or Bilingual

Stereo or Bilingual

Malfunction Skip

T1: S1A0688C01’s ID Detect Time typ 1 sec, Max 1.5 sec

T3: When the channel is fixed, set MICOM’s ID Detect Delay Time to a minimum of 1 sec.

Figure 2. Timing Diagram when Channel is Fixed

13

Page 14

S1A0688C01 TV SOUND MPX FOR TWO CARRIER SYSTEM

MICOM

S1A0688C01 is available in DC control, normal microcontroller control, and IIC BUS microcontroller control system,

and it can distinguish the control type automatically by monitoring PIN 22 (EN) status. The relation of control source

type and PIN 22 status is shown as follows.

IIC Bus Normal MICOM DC Control

EN (Pin 22) always “L” MICOM strobe always “H”

Protocol of IIC BUS microcontroller control (PIN 22: L)

The S1A0688C01 can be controlled via the 2-line IIC BUS by the microcontroller. The two lines (SDA-serial data.

SCL-serial clock) exchange information between the devices connected to the IIC bus. SDA is bidirectional line

which is connected to a positive supply voltage via a pull up resistor. When the bus is free both lined are HIGH. The

data on the SDA line must be stable during the High-powered of the clock. The HIGH or LOW data can only

change when the clock signal line is LOW. A HIGH -to -LOW transition of the SDA line while SCL is HIGH is

defined as a start condition. A LOW- to -HIGH transition of the SDA line while SCL is HIGH is defined as a stop

condition. The bus receiver will be reset by the reception of a start condition and is considered to be busy after the

start condition. After a stop condition the bus is considered as free again.

SDA

321 25 26 27

SCL

1 − 7th bit Chip select code (1000010B)

1st Byte

8th bit R/W

9th, 18th, 27th bit Acknowledge

2nd Byte 10th − 17th bit SUB address (function)

3rd Byte 197th − 26th bit Data (D1 − D8)

Data transmitted to the S1A0688C01 starts with the module address as follows:

MSB LSB

1 0 0 0 0 1 0 R/W ACK

MSB First.

14

Page 15

TV SOUND MPX FOR TWO CARRIER SYSTEM S1A0688C01

Protocol of normal microcontroller control (PIN 22: STROBE)

SDA

321 22 23 24

SCL

STROBE

(EN)

1st Byte 1 − 7th bit Chip select code (1000010B)

8th bit Not use (don’t care)

2nd Type 9th − 16th bit Function assignment

3rd Type 17th − 24th bit Data (D1 − D8)

The module address of S1A0688C01 in normal microcontroller control mode is as follows:

.

MSB LSB

1 0 0 0 0 1 0 D

MSB First.

The maximum STROBE pulse width in normal microcontroller control mode should be under 6.0 msec. If the

STROBE pulse width excess the limit, S1A0688C01 will be changed to DC control mode.

Control Item in Each Control Mode

In each control mode, control items is limited as follows:

Control Mode Change Mute Preset Pre-adjust set

Data

Transmission

Receive

Acknowledge

IIC Bus O O O O O O

Normal MICOM O O O × × ×

DC Control × × × × × ×

NOTES:

1. PRE-SET: When power is ON, MICOM initials the status of S1A0688C01 to preset status.

(All IC has same preset status data)

2. PRE-ADJUST SET: When power is ON, MICOM initials the status of S1A0688C01 to pre-measured and stored status.

(Different each IC)

3. DATA TRANSMISSION: Transmit stored data to MICOM when MICOM requests.

4. RECEIVE ACKNOWLEDGE: Return acknowledge signal to MICOM after DATA receipt.

15

Page 16

S1A0688C01 TV SOUND MPX FOR TWO CARRIER SYSTEM

MICOM control map

In IIC BUS mode, SLAVE Address = WRITE: 84H, READ: 85H

In normal MICOM mode, chip select code = 1000010B

SUB ADDRESS

(2nd BYTE)

(MSB<->LSB)

MSB LSB

D1 D2 D3 D4 D5 D6 D7 D8

0 0 X X X X X X Mono

DATA (3rd BYTE)

FUNCTION REMARK

000XXXXX

(Mode Control)

1 0 X X X X X X Stereo

0 1 X X X X X X Bilingual

1 1 X X X X X X Sub

001XXXXX

(Mute Control)

010XXXXX

(Test Mode Control)

0 X X X X X X X Mute Off

1 X X X X X X X Mute

0 X X X X X X X Normal mode

1 X X X X X X X Test mode

0 0 X X X X X X Default

011XXXXX

(Free Run Frequency

Control)

1 0 X X X X X X Frequency down

0 1 X X X X X X Default zap

1 1 X X X X X X Frequency down zap

100XXXXX D1 D2 D3 D4 D5 X X X

101XXXXX

S1U S1D S2U S2D

X X X X Pin DC cont.

0 0 X X X X X X Operating

110XXXXX

(Test Mode)

1 0 X X X X X X Slave zap

0 1 X X X X X X Master zap

Separation adjust

(3)

End user

control

Ic maker

test

Set maker

IC maker

test

1 1 X X X X X X External clock

111XXXXX X X X X X X X X Not use

NOTES:

1. MSB first

2. When power is ON, all latch data are “0”, S1A0688B is set to MONO OFF, MUTE OFF, SEPARATION

ADJUST DEFAULT (00001XXX).

3. Separation Adjust Data

D1 D2 D3 D4 D5 D1 D2 D3 D4 D5 D1 D2 D3 D4 D5

0 0 0 0 0 (MIN) <--- 1 0 0 0 0 (TYP) ----> 1 1 1 1 1 (MAX)

16

Page 17

TV SOUND MPX FOR TWO CARRIER SYSTEM S1A0688C01

Control Function Description

• MODE CONTROL: Control the MATRIX structure according to broadcast status and end user’s setting.

S1A0688C01 has 4 modes (MONO, STEREO, BILINGUAL and SUB)

• MUTE CONTROL: When MUTE CONTROL is on, the audio output of S1A0688C01 is off.

• SEP. ADJUST: The separation characteristic of S1A0688C01 in STEREO mode can be controlled by IIC BUS.

This option controls S2 FM demodulated output signal level so as to make the separation characteristic in best

status.

• TEST MODE: IC makers test item.

DC Control Map (PIN22: H)

DC (Logic) Input

Function

SCL SDA

0 0 Mono

1 0 Stereo

0 1 Bilingual

1 1 Sub

READ Mode in IIC BUS MICOM Control Mode

S1A0688C01 can transmit the data which is registered inside IC to the MICOM in IIC BUS control system.

If the 8th bit of module address is ‘H’, it means MICOM requests the data stored in the IC and S1A0688C01 enter

data transmission mode. During the read mode, S1A0688C01 ignores the data the data of 2nd type (SUB address)

and transmits the internal data within the period of 3rd byte. The SDA line of MICOM should be maintain H to

accept transmitted data from IC. The format of read data is as follows.no

Bit of 3rd Byte 1 2 3 4

5 6 7 8

Read Mode

Transmit Data BI ST BI ST ZC ZC 0 1

0 0 1 1 Mono

1 0 0 1 Bilingual

0 1 1 0 Stereo

Option for IC maker

(ZC: IC test option)

Others Transmission error

17

Page 18

S1A0688C01 TV SOUND MPX FOR TWO CARRIER SYSTEM

Others

In IIC BUS control system, if the SLAVE address is correct, the acknowledge signal will be generated by

S1A0688C01 no matter the sub address is right or wrong, When sub address is wrong IC will do nothing.

NOTES:

1. The characteristic of SIF Filter should be suitable to MPX sound system.

We suggest to use MURATA Co. products: SFSH4.5MCB and SFSH4.72MCB.

2. If you need to use two chip in one set (e.g. TVCR), You should separate the chips by select pin 28 voltage.

When it is high or open, Write =84H, Read = 85H.

When pin 28 is connected to ground, Write =86H, Read = 87H.

3. Program control method:

1. Under window 95 environment, extract kb22688b.zip

2. Install: setup.exe

3. Run kb22688b.exe

4. PC parallel port pin description:

PIN 1 2 3 19

SIGNAL SDA SCL EN GND

18

Page 19

TV SOUND MPX FOR TWO CARRIER SYSTEM S1A0688C01

VCC

TEST CIRCUIT

100µF

VDD

SDASCLEN

R-OUT

M

ST

BI

M M

17

4.7µF 10µF

47kΩ

47kΩ

47kΩ

47kΩ

47kΩ

20 19 18

22 2124 23

16

L- OUT

4.7µF

M

10µF

1MΩ

4.7µF

4.7µF

0.039µF 0.039µF

9 10 11 12 151413

25

10µF

1µF

S1A0688C01

8

1µF 1µF 10µF 10µF

TCLK

SM

RCM

S2 S1

28 27 26

0.1µF 0.1µF

30 2932 31

0.1µF

5 6

0.047µF 0.047µF

SIF1 SIF2

0.047µF 0.047µF

S S

1 2 3 4 7

19

Page 20

S1A0688C01 TV SOUND MPX FOR TWO CARRIER SYSTEM

L- OUT

APPLICATION CIRCUIT

100µF

VDD

R-OUT

SDASCLENST

17

4.7µF 10µF

47kΩ

47kΩ

47kΩ

20 19 18

16

VCC

4.7µF

10µF

1MΩ

4.7µF

22 2124 23

470Ω

470Ω

0.039µF 0.039µF

9 10 11 12 151413

100µF

25

8

S1A0688C01

F

µ

1

1µF

1µF 1µF 10µF 10µF 4.7µF

20

F

µ

0.1

N.C N.C N.C

N.C

28 27 26

30 2932 31

5 6

3pF

1 2 3 4 7

F

µ

F 0.047

µ

0.047

4.5MHz

4.72MHz

Loading...

Loading...