Page 1

®

REF200

REF200

REF200

DUAL CURRENT SOURCE/CURRENT SINK

FEATURES

● COMPLETELY FLOATING:

No Power Supply or Ground Connections

● HIGH ACCURACY: 100

µA ±0.5%

● LOW TEMPERATURE COEFFICIENT:

±25ppm/°C

● WIDE VOLTAGE COMPLIANCE:

2.5V to 40V

● ALSO INCLUDES CURRENT MIRROR

DESCRIPTION

The REF200 combines three circuit building-blocks

on a single monolithic chip—two 100µA current

sources and a current mirror. The sections are

dielectrically isolated, making them completely

independent. Also, since the current sources are twoterminal devices, they can be used equally well as

current sinks. The performance of each section is

individually measured and laser-trimmed to achieve

high accuracy at low cost.

The sections can be pin-strapped for currents of 50µA,

100µA, 200µA, 300µA or 400µA. External circuitry

can be used to obtain virtually any current. These and

many other circuit techniques are shown in the

Applications section of this Data Sheet.

The REF200 is available in plastic 8-pin mini-DIP

and SOIC packages.

APPLICATIONS

● SENSOR EXCITATION

● BIASING CIRCUITRY

● OFFSETTING CURRENT LOOPS

● LOW VOLTAGE REFERENCES

● CHARGE-PUMP CIRCUITRY

● HYBRID MICROCIRCUITS

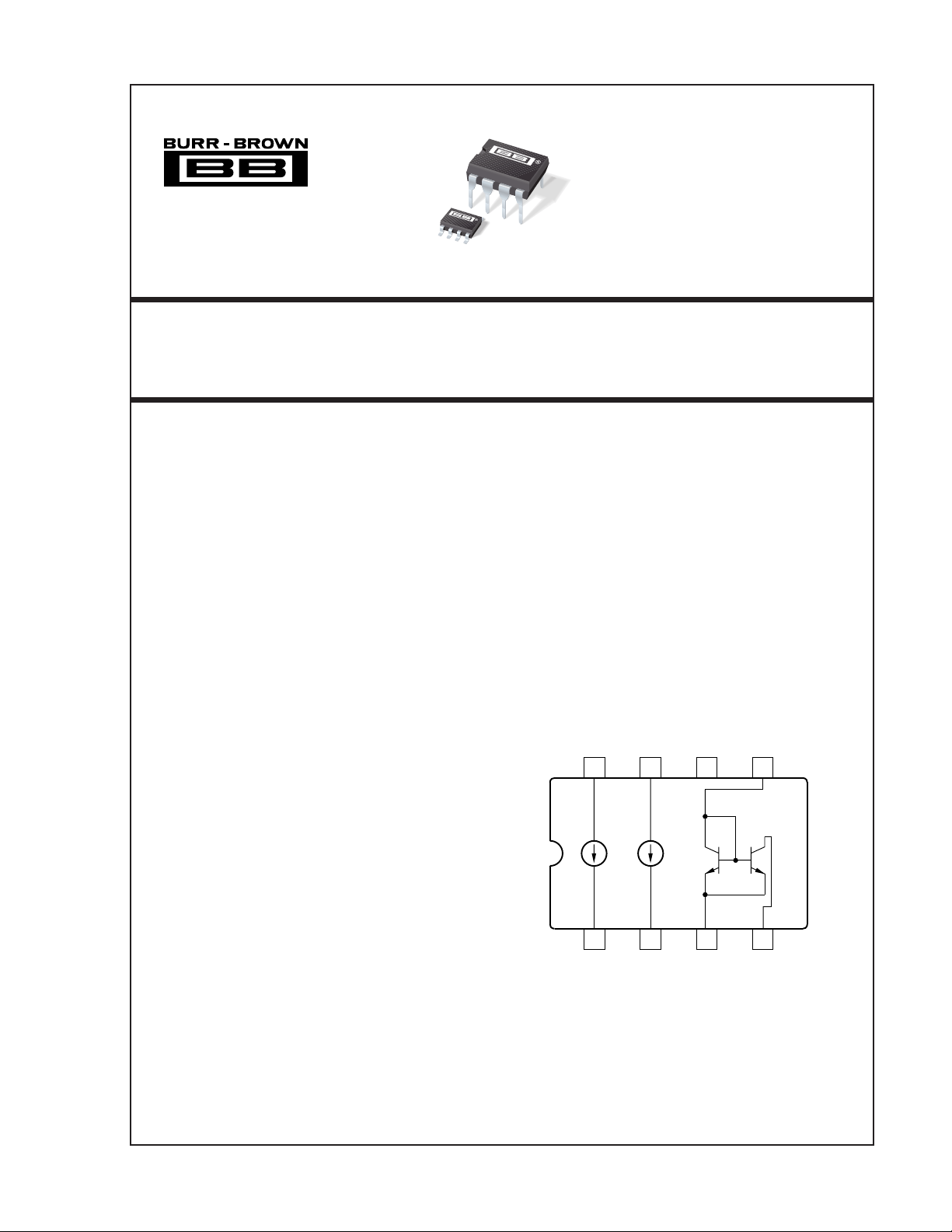

I

1

High

8765

1234

I

1

Low

I

2

High

100µA 100µA

I

2

Low

Substrate

Mirror

Common

Mirror

Mirror

In

Out

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111

Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

© 1988 Burr-Brown Corporation PDS-851D Printed in U.S.A. October, 1993

Page 2

SPECIFICATIONS

ELECTRICAL

At TA = +25°C, VS = 15V, unless otherwise noted.

REF200AP, AU

PARAMETER CONDITION MIN TYP MAX UNITS

CURRENT SOURCES

Current Accuracy ±0.25 ±1%

Current Match ±0.25 ±1%

Temperature Drift Specified Temp Range 25 ppm/°C

Output Impedance 2.5V to 40V 20 100 MΩ

Noise BW = 0.1Hz to 10Hz 1 nAp-p

Voltage Compliance (1%) T

Capacitance 10 pF

CURRENT MIRROR I = 100µA Unless

Gain 0.995 1 1.005

Temperature Drift 25 ppm/°C

Impedance (output) 2V to 40V 40 100 MΩ

Nonlinearity I = 0µA to 250µA 0.05 %

Input Voltage 1.4 V

Output Compliance Voltage See Curves

Frequency Response (–3dB) Transfer 5 MHz

TEMPERATURE RANGE

Specification –25 +85 °C

Operating –40 +85 °C

Storage –40 +125 °C

3.5V to 30V 200 500 MΩ

f = 10kHz 20 pA/√Hz

to T

MIN

MAX

Otherwise Noted

See Curves

PIN CONFIGURATION

Top View DIP/SOIC

I

Low

1

I

Low

2

Mirror Common

Mirror Output

1

2

3

4

8

7

6

5

I

High

1

I

High

2

Substrate

Mirror Input

ELECTROSTATIC

DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown

recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling

and installation procedures can cause damage.

ESD damage can range from subtle performance degradation

to complete device failure. Precision integrated circuits may

be more susceptible to damage because very small parametric

changes could cause the device not to meet its published

specifications.

ABSOLUTE MAXIMUM RATINGS

Applied Voltage .....................................................................–6V to +40V

Reverse Current ........................................................................... –350µA

Voltage Between Any Two Sections................................................. ±80V

Operating Temperature ................................................... –40°C to +85°C

Storage Temperature .....................................................–40°C to +125°C

Lead Temperature (soldering, 10s) .............................................. +300°C

(SOIC 3s)........................................................+260°C

PACKAGE/ORDERING INFORMATION

PACKAGE

DRAWING TEMPERATURE

PRODUCT PACKAGE NUMBER

REF200AP 8-Pin Plastic DIP 006 –25°C to +85°C

REF200AU 8-Pin SOIC 182 –25°C to +85°C

NOTE: (1) For detailed drawing and dimension table, please see end of data

sheet, or Appendix C of Burr-Brown IC Data Book. (2) Grade designation “A”

may not be marked. Absence of grade designation indicates A grade.

(1)

RANGE

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes

no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change

without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant

any BURR-BROWN product for use in life support devices and/or systems.

®

REF200

2

Page 3

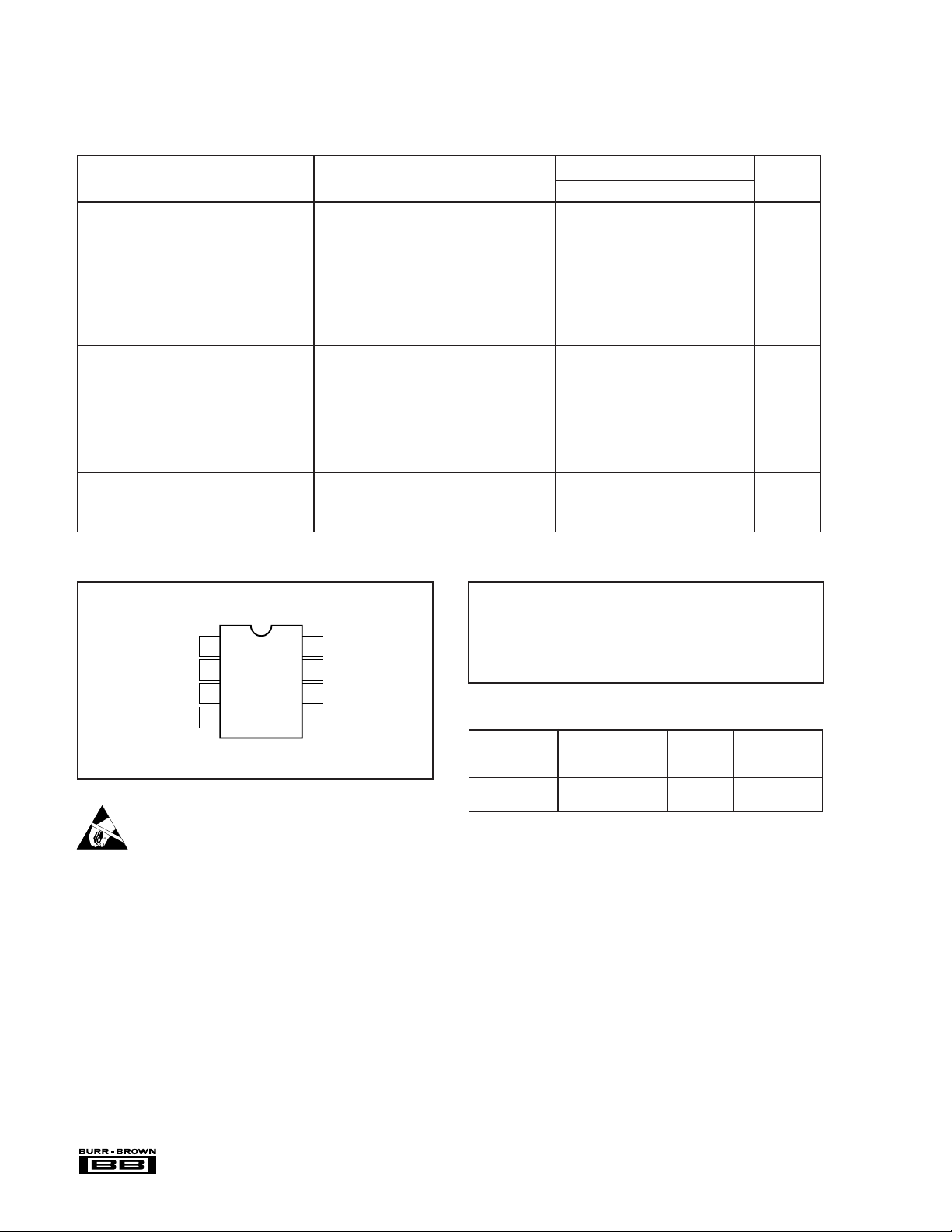

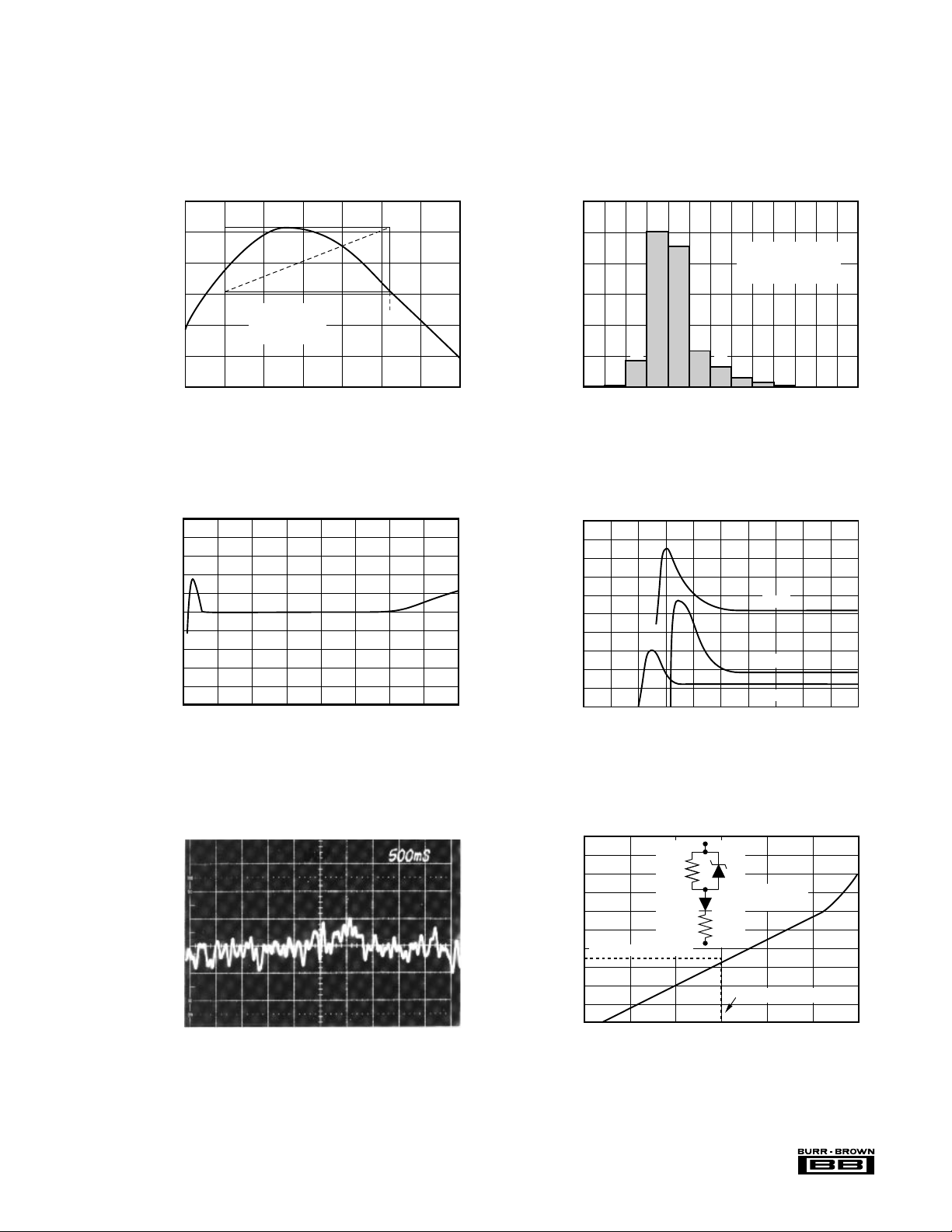

TYPICAL PERFORMANCE CURVES

600

500

400

300

200

100

0

5010

Temperature Drift (ppm/°C)

Quantity (Units)

Distribution of three

production lots —

1284 Current Sources.

2015 25 3530 40 5045 55 6560

2

5

117

30

15

6

0

11

501

454

86

66

CURRENT SOURCE

TEMPERATURE DRIFT DISTRIBUTION

1000

900

800

700

600

500

400

300

200

100

Reverse Current (µA)

0

0–2–4–6–8

–10

–12

Reverse Voltage (V)

CURRENT SOURCE

REVERSE CURRENT vs REVERSE VOLTAGE

Reverse Voltage

Circuit Model

12kΩ

7V

5kΩ

Safe Reverse Current

Safe Reverse Voltage

)

At TA = +25°C, VS = +15V, unless otherwise noted.

CURRENT SOURCE

100.1

100

99.9

TYPICAL DRIFT vs TEMPERATURE

99.8

Current (µA)

99.7

99.6

99.5

101

100.8

100.6

100.4

100.2

100

99.8

Current (µA)

99.6

99.4

99.2

99

0 5 10 15 20 25 30 35 40

Drift specified by

“box method”

(See text)

–25–50 25 7550 1251000

Temperature (°C)

CURRENT SOURCE

OUTPUT CURRENT vs VOLTAGE

Voltage (V)

85°C

100.5

100.4

100.3

100.2

100.1

100

99.9

Current (µA)

99.8

99.7

99.6

99.5

0

CURRENT SOURCE

OUTPUT CURRENT vs VOLTAGE

25°C

–55°C

125°C

12345

Voltage (V)

Output Current (500pA/div)

CURRENT SOURCE

CURRENT NOISE (0.1Hz to 10Hz)

Time (500ms/div

®

3

REF200

Page 4

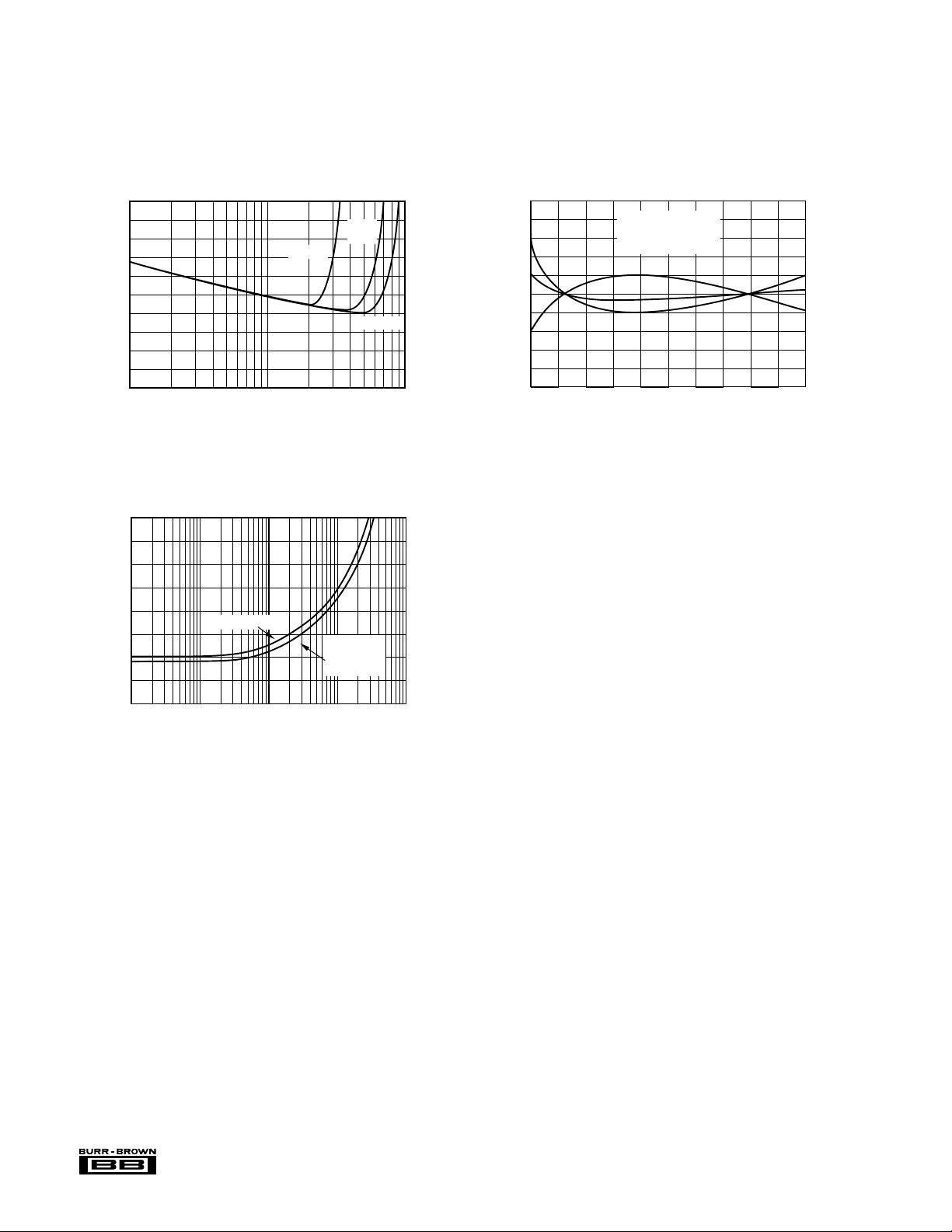

TYPICAL PERFORMANCE CURVES (CONT)

At TA = +25°C, VS = +15V, unless otherwise noted.

5

4

3

2

1

0

Error (%)

–1

–2

–3

–4

–5

10µA 100µA 1mA

4

3

2

Input Voltage (V)

1

MIRROR GAIN ERROR vs CURRENT

V = 1V

O

Mirror Current (A)

MIRROR INPUT VOTAGE/OUTPUT

COMPLIANCE VOLTAGE vs CURRENT

Input Voltage

Output

Compliance

Voltage

V =

O

1.25V

V = 1.5V

O

0.1

0.08

0.06

0.04

0.02

0

–0.02

–0.04

Nonlinearity (% of 250µA)

–0.06

–0.08

–0.01

0

MIRROR TRANSFER NONLINEARITY

50 100 150 200 250

Data from Three

Representative Units

(Least-square fit)

Current (µA)

0

1µA 10µA 100µA

Current

®

REF200

1mA

10mA

4

Page 5

(Substrate)

Current

Source

(1 of 2)

4kΩ

8X

8,7

5kΩ

1kΩ

1,2

6

3

54

1kΩ

12kΩ

Current

Mirror

APPLICATIONS INFORMATION

The three circuit sections of the REF200 are electrically

isolated from one another using a dielectrically isolated

fabrication process. A substrate connection is provided (pin

6), which is isolated from all circuitry. This pin should be

connected to a defined circuit potential to assure rated DC

performance. The preferred connection is to the most negative constant potential in your system. In most analog

systems this would be –V

pin 6 open and leave unused sections unconnected.

Drift performance is specified by the “box method,” as

illustrated in the Current vs Temperature plot of the typical

performance curves. The upper and lower current extremes

measured over temperature define the top and bottom of the

box. The sides are determined by the specified temperature

range of the device. The drift of the unit is the slope of the

diagonal—typically 25ppm/°C from –25°C to +85°C.

If the current sources are subjected to reverse voltage, a

protection diode may be required. A reverse voltage circuit

model of the REF200 is shown in the Reverse Current vs

Reverse Voltage curve. If reverse voltage is limited to less

than 6V or reverse current is limited to less than 350µA, no

protection circuitry is required. A parallel diode (Figure 2a)

will protect the device by limiting the reverse voltage across

the current source to approximately 0.7V. In some applications, a series diode may be preferable (Figure 2b) because

it allows no reverse current. This will, however, reduce the

compliance voltage range by one diode drop.

Applications for the REF200 are limitless. Application Bulletin AB-165 shows additional REF200 circuits as well as

other related current source techniques. A collection of

circuits is shown to illustrate some techniques. Also, see

AB-165A.

. For best AC performance, leave

S

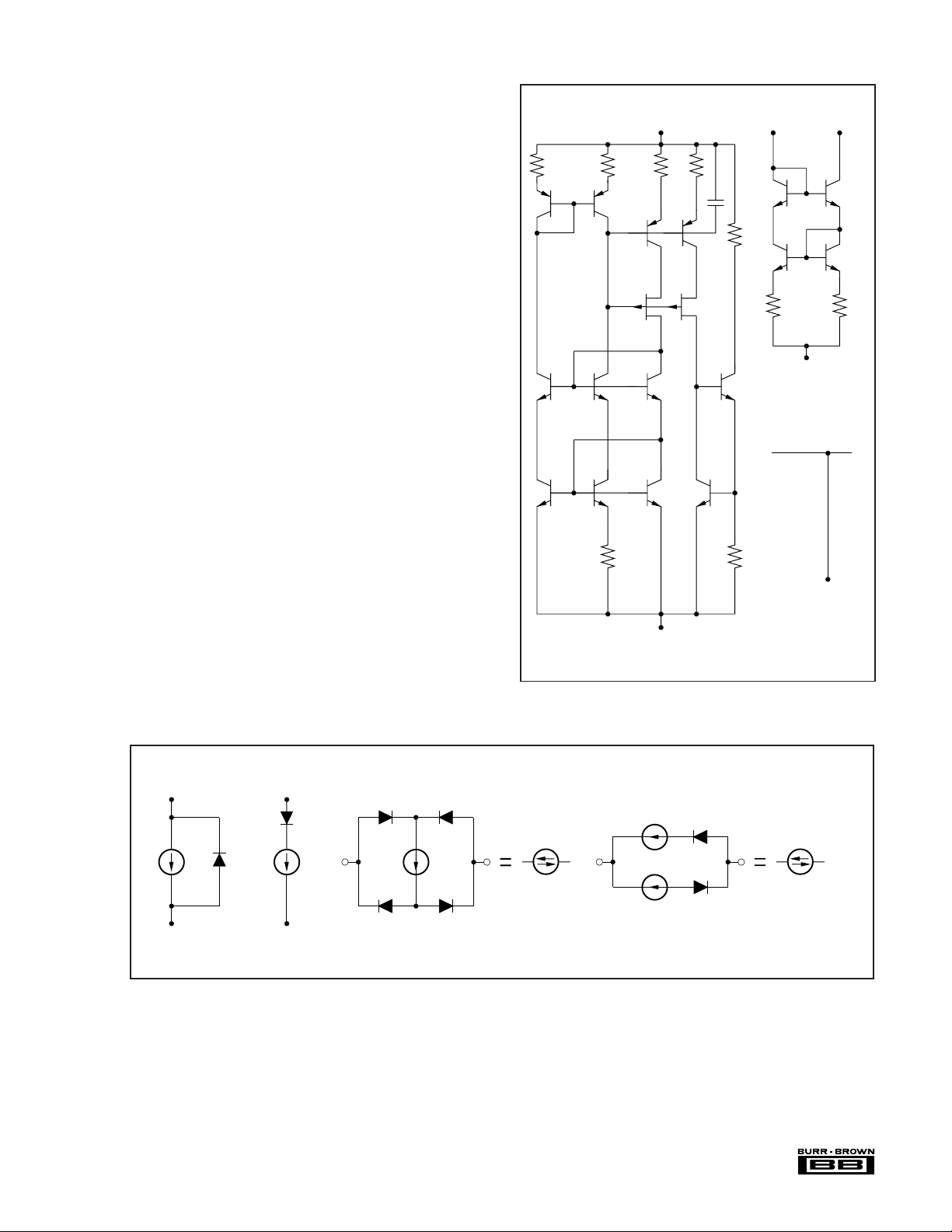

FIGURE 1. Simplified Circuit Diagram.

(a) (b) (c) (d)

FIGURE 2. Reverse Voltage Protection.

NOTE: All diodes = 1N4148.

DD

D

4

31

100µA

D

2

Bidirectional

Current Source

5

100µA

100µA

D

1

D

2

REF200

Bidirectional

Current Source

®

Page 6

FIGURE 3. 50µA Current Source.

(b)

(c)

(a)

+V

In Out

Mirror

Com

3

100µA

–V

S

S

45

100µA

50µA

I

OUT

200µA

100µA

100µA 100µA

100µA

In Out

Com

Compliance = 4V

(a)

FIGURE 4. 200µA, 300µA, and 400µA Floating Current Sources.

Compliance to

Ground

In Out

Mirror

Com

3

100µA

50µA

45

0.01µF

100µA

100kΩ

+V

S

In Out

Mirror

3

(b)

Compliance to

Mirror

Com

3

300µA

45

–V + 5V

S

50µA

45

100µA

100µA

Compliance = 4V

5.1V

1N4689

100µA

In Out

Mirror

Com

3

(c)

+V

S

27kΩ

In Out

400µA

45

Compliance to

–V + 5.1V

S

45

Mirror

Com

3

100µA

50µA

–V

S

FIGURE 5. 50µA Current Sinks.

®

REF200

–V

S

–V

S

6

Page 7

+V

(2)

S

101

SERIES-CONNECTED CURRENT SOURCES

CURRENT vs APPLIED VOLTAGE

High

100µA

100µA100µA

100µA/200µA

100

100µA

Low

Current (µA)

45

In Out

Mirror

Com

3

99

0 1020304050607080

Applied Voltage (V)

–V

Compliance to –V + 1.5V

S

S

Provides 2X Higher Compliance Voltage

FIGURE 6. Improved Low-Voltage Compliance. FIGURE 7. 100µA Current Source—80V Compliance.

+V

S

+V

S

100µA

L

o

a

d

–V

S

(a) Compliance approximate

to Gnd. HV compliance

limited by FET breakdown.

High

100µA

0.01µF

40kΩ

40kΩ

0.01µF

100µA

+V

5.1V

1N4689

27kΩ

–V

S

L

o

a

d

100µA

0.01µF

0.01µF

S

100µA

33kΩ

100µA

–V

S

(b) Compliance to +V – 5V.

L

o

a

d

S

(c)

100µA

1N41481N4148

40kΩ

± ±

0.01µF

40kΩ

100µA

Low

(d) Floating 200µA cascoded

current source.

NOTES: (1) FET cascoded current sources offer improved output impedance and high frequency operation. Circuit in (b)

also provides improved PSRR.

FIGURE 8. FET Cascode Circuits.

1N41481N4148

(e) Bidirectional 200µA

cascoded current source.

For current sinks (Circuits (a) and (b) only), invert circuits and use “N” channel JFETS.

7

REF200

®

Page 8

+V

S

Using Standard Potentiometer

V

IN

R

A

R

B

+V

S

Using Bourns Op Amp Trimpot

V

IN

R

A

®

R

B

100µA

51Ω

To

Other

Amps

2kΩ Linear

51Ω

–V

100µA

S

V = V (–R /R )

IN B A

OUT

Offset Adjustment Range = ±5mV

NOTE: (1) For N Op Amps, use Potentiometer Resistance = N • 100Ω.

FIGURE 9. Op Amp Offset Adjustment Circuits.

Op Amp

100µA

V

OUT

V

OUT

Op Amp

(1)

To

–V

Other

Amps

100µA

Offset Adjustment Range = ±5mV

S

(1)

100Ω

Bourns Trimpot

V = –V (R /R )

OUT

®

IN B A

®

REF200

8

Page 9

R

2

+V

S

I = N • 100µA

OUT

0.01µF

+V

S

®

OPA602 or OPA128

R

I

2

OUT

Use OPA128

I = N • 100µA

OUT

(1)

R

1

(N • R )

NOTE: (1) Burr Brown

EXAMPLES

R

1

100Ω 10MΩ 1nA

2

10kΩ 1MΩ 1µA

10kΩ 1kΩ 1mA

0.01µF

100µA

–V

S

(a) (b)

FEATURES:

(1) Zero volts shunt compliance.

(2) Adjustable only to values above

reference value.

NOTE:

Current source/sink swing to the

“Load Return” rail is limited only

100µA

by the op amp's input common

mode range and output swing

capability. Voltage drop across “R”

can be tailored for any amplifier to

0.01µF

allow swing to zero volts from rail.

OPA602

EXAMPLES

RNRI

OUT

1kΩ 4kΩ 500µA

1kΩ 9kΩ 1mA

NR

R

100kΩ 9.9kΩ 10mA

I = (N +1) 100µA

O

100µA

Reference

I = (N +1) 100µA

O

NR

OPA602

–V

S

(d)(c)

100µA

0.01µF

(N • R )

(1)

R

1

2

R

2

R

FIGURE 10. Adjustable Current Sources.

0.01µF

100µA

NR

OPA602

I = (N +1) 100µA

O

10pF

(e)

9

IO = 100µA (N + 1). Compliance ≈ 3.5V

with 0.1V across R. Max I

For I

= 1A, R = 0.1Ω, NR = 1kΩ.

O

R

limited by FET.

O

REF200

®

Page 10

RTD

Cable Shield

R

OFFSET

INA110

Instrumentation Amplifier

V = Gain • 200µA • ∆ RTD

OUT

200µA

Reference

Current

+V

S

865

7

I

O

AB

234

1

–V

C

S

200µA

Compensation

Current

REF200

FIGURE 11. RTD Excitation With Three Wire Lead Resistance Compensation.

Triangle Output

OPA602

C

2Vp-p

R

10kΩ

Frequency = 1/4RC (Hz)

Frequency = 25/C (Hz)

(C is in µF and R = 10kΩ)

1/2

REF200

FIGURE 12. Precision Triangle Waveform Generator.

®

REF200

Square Output

1N41481N4148

1N41481N4148

2Vp-p

Bidirectional

Current Source

10

Page 11

–15V

100µA

0.1µF

Siliconix

J109

50kΩ

I

OUT

For current source,

invert circuitry and

use P-Channel FET.

50kΩ

0.1µF

100µA

V

IN

–10V ≤ V ≤ +10V

IN

100kΩ

1/4

OPA404

V = +10V: 100% Duty CycleV = +10V: 100% Duty Cycle

IN

V = 0V: 50% Duty Cycle

IN

V = –10V: 0% Duty Cycle

IN

FIGURE 13. Precision Duty-Cycle Modulator.

For current source,

invert circuitry and

use P-Channel FET.

I

OUT

100µA + Bridge

(See Figure 12)

OPA404

100µA + Bridge

(See Figure 12)

C

1/4

1/4

OPA404

12Vp-p

Duty Cycle Out

60kΩ

Siliconix

J109

0.1µF

50kΩ

100µA

–15V

FIGURE 14. Low Noise Current Sink. FIGURE 15. Low Noise Current Sink with Compliance

Below Ground.

11

®

REF200

Page 12

High

300µA

High

400µA

100µA

20kΩ

0.01µF

100µA

2N5116

2N4340

0.01µF

27kΩ

5 4

In Out

Mirror

100µA

Com

3

300µA

Low

(a) Regulation (15V to 30V = 0.00003%/V (10G(a) Regulation (15V to 30V = 0.00003%/V (10GΩ)

FIGURE 16. Floating 300µA and 400µA Cascoded Current Sources.

+V

S

100µA

10kΩ

100µA

20kΩ

0.01µF

2N5116

2N4340

5 4

In Out

Mirror

Com

3

400µA

Low

(a) Regulation (15V to 30V = 0.000025%/V (10G(a) Regulation (15V to 30V = 0.000025%/V (10GΩ)

High

Compliance

4V to 30V

25mA

10kΩ

V

I

Diodes: 1N4148

or PWS740-3

Diode Bridge for

reduced V .

OS

–V

100µA

S

FIGURE 17. Rate Limiter.

C

OPA602

V Rate Limit = 100µA/C

O

V = –V

100Ω

I

O

100µA

100Ω

+V

S

–V

S

100Ω

100Ω

40.2Ω10kΩ

NOTE: Each amplifier 1/4 LM324.

Low

Op amp power supplies are derived

within the circuitry, and this quiescent

current is included in the 25mA.

FIGURE 18. 25mA Floating Current Source.

®

REF200

12

Page 13

+15V

V

R

(50kΩ)

V

I

100µA

1N4148

R

(50kΩ)

–10 –5 +5 +10

O

+10

+5

V

I

R

(50kΩ)

V

I

100µA

–15V

FIGURE 19. Dead-Band Circuit.

+15V

R

(50kΩ)

100µA

10pF

OPA602

1N4148

10pF

OPA602

1N4148

R

(50kΩ)

R

(50kΩ)

1N4148

1N4148

–5

For V > –5V: V = 0

V

O

–10

V

O

+10

I

For V < –5V: V = –V – 5V

I I

(Dead to 100µA • R)

O

O

+5

–10 –5 +5 +10

V

I

V

O

–5

–10

For V < 5V: V = 0

For V > 5V: V = 5V – V

(Dead to –100µA • R)

V

O

+10

O

I

O

I I

+5

–10 –5 +5 +10

V

I

10pF

OPA602

V

I

R

(50kΩ)

(50kΩ)

1N4148

100µA

10pF

–15V

OPA602

FIGURE 20. Double Dead-Band Circuit.

–5

For V > 5V: V = V – 5V

I

1N4148

10kΩ

–10

For V < –5V: V = V + 5V

(Dead to ±100µA • R)

OOI

I I

10kΩ

10kΩ

V

R

OPA602

O

1N4148

®

13

REF200

Page 14

+V

+V

S

S

100µA

100µA

V = 100µV

O

OPA602

V = 1V

O

1Ω

0.01µF

10kΩ

FIGURE 22. Voltage Reference.FIGURE 21. Low-Voltage Reference.

V

O

1kΩ

+10

100µF

OPA121

V

O

–10 –5 +5 +10

+5

OPA121

V

I

100µA

with bridge

(See Figure 2)

R

(50kΩ)

V = V (–5V < V < 5V)

O

I I

V = 5V (V > 5V)

V = –5V (V < –5V)

(Bound = 100µA • R)

I

O

O

I

–2.5V (R = 25kΩ)

+5V (R = 50kΩ)

+7.5V (R = 75kΩ)

–5

–10

+7.5V (R = 75kΩ)

+5V (R = 50kΩ)

+2.5V (R = 25kΩ)

V

I

FIGURE 23. Bipolar Limiting Circuit.

1kΩ

100µF

1N4148

OPA121

V

I

100µA

FIGURE 24. Limiting Circuit.

OPA121

R

(50kΩ)

V

O

V = V (V < 5V)

OOI I

V = 5V (V > 5V)

(V = 100µA • R)

I

LIMIT

V

O

+10

+5

+7.5V (R = 75kΩ)

+5V (R = 50kΩ)

+2.5V (R = 25kΩ)

–10 –5 +5 +10

–5

–10

V

I

®

REF200

14

Page 15

100µA

(1)

0.01µF

(2)

V

CENTER

(1)

0.01µF

V

I

100µA

FIGURE 25. Window Comparator.

+V

–V

S

+5V

V

1kΩ

1/2

LM393

(3)

R

V

O

(3)

R

1/2

LM393

NOTES: (1) Capacitors optional to reduce noise and switching time.

S

(2) Programs center of threshold voltage. (3) Programs window voltage.

O

The

W

V

CENTER

W

Window

(2)

5V

0

–V W+V

–V , +V = 100µA • R

W

V

I

100µA

+In

1/2

OPA1013

1/2

OPA1013

100µA

PMI

MAT03

INA105

+V

–In

S

–V

S

V = +In – (–In)

O

FIGURE 26. Instrumentation Amplifier with Compliance to –VS.

15

®

REF200

Loading...

Loading...