Page 1

SBSLITE™ Telecom Standard Product Data Sheet

PM8611

Preliminary

SBSLITE

Telecom Standard Product

Data Sheet

Preliminary

Issue 2: May 2001

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

Document ID: PMC-2010883, Issue 2

Page 2

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Legal Information

Copyright

© 2001 PMC-Sierra, Inc.

The information is proprietary and confidential to PMC-Sierra, Inc., and for its customers’

internal use. In any event, you cannot reproduce any part of this document, in any form, without

the express written consent of PMC-Sierra, Inc.

PMC-2010883 (P1)

Disclaimer

None of the information contained in this document constitutes an express or implied warranty by

PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such

information or the fitness, or suitability for a particular purpose, merchantability, performance,

compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any

portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all

representations and warranties of any kind regarding the contents or use of the information,

including, but not limited to, express and implied warranties of accuracy, completeness,

merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or

consequential damages, including, but not limited to, lost profits, lost business or lost data

resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has

been advised of the possibility of such damage.

Trademarks

SBSLITE, NSE-20G, NSE-8G, SBI, SPECTRA, TEMUX-84, AAL1gator-32, and FREEDM-336

are trademarks of PMC-Sierra, Inc. S/UNI is a registered trademark of PMC-Sierra.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 1

Document ID: PMC-2010883, Issue 2

Page 3

SBSLITE™ Telecom Standard Product Data Sheet

Contacting PMC-Sierra

PMC-Sierra

8555 Baxter Place Burnaby, BC

Canada V5A 4V7

Tel: (604) 415-6000

Fax: (604) 415-6200

Document Information: document@pmc-sierra.com

Corporate Information: info@pmc-sierra.com

Technical Support: apps@pmc-sierra.com

Web Si te: http://www.pmc-sierra.com

Preliminary

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 2

Document ID: PMC-2010883, Issue 2

Page 4

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Table of Contents

1 Features.......................................................................................................................9

2 Applications ............................................................................................................... 11

3 References ................................................................................................................12

4 Application Examples ................................................................................................ 13

5 Block Diagram ...........................................................................................................15

6 Loopback Configurations ...........................................................................................16

7 Description.................................................................................................................17

8 Pin Diagram ...............................................................................................................19

9 Pin Description........................................................................................................... 20

10 Functional Description ...............................................................................................34

10.1 SBI Bus Data Formats ......................................................................................34

10.2 Incoming SBI336 Timing Adapter......................................................................52

10.3 CAS Expanders................................................................................................. 52

10.4 Memory Switch Units ........................................................................................53

10.5 CAS Merging.....................................................................................................54

10.6 Incoming SBI336 Tributary Translator............................................................... 54

10.7 PRBS Processors .............................................................................................54

10.8 Transmit 8B/10B Encoders ...............................................................................55

10.9 Transmit Serializer ............................................................................................58

10.10 LVDS Transmitters ............................................................................................58

10.11 Clock Synthesis Unit .........................................................................................58

10.12 Transmit Reference Generator .........................................................................58

10.13 LVDS Receivers ................................................................................................ 59

10.14 Data Recovery Units .........................................................................................59

10.15 Receive 8B/10B Decoders................................................................................59

10.16 Outgoing SBI336S Tributary Translator ............................................................62

10.17 Outgoing SBI336 Timing Adapter......................................................................63

10.18 In-band Link Controller...................................................................................... 63

10.19 Microprocessor Interface ..................................................................................66

11 Normal Mode Register Description............................................................................71

12 Test Features Description........................................................................................240

12.1 Master Test and Test Configuration Registers ................................................240

12.2 JTAG Test Port ................................................................................................242

13 Operation .................................................................................................................254

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 3

Document ID: PMC-2010883, Issue 2

Page 5

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

13.1 “C1” Synchronization.......................................................................................254

13.2 Synchronized Control Setting Changes .......................................................... 255

13.3 Switch Setting Algorithm .................................................................................260

13.4 JTAG Support..................................................................................................267

14 Functional Timing.....................................................................................................272

14.1 Incoming SBI336 Bus Functional Timing ........................................................ 272

14.2 Incoming 77 MHz TelecomBus Functional Timing..........................................273

14.3 Transmit Serial LVDS Functional Timing ........................................................274

14.4 Receive Serial LVDS Functional Timing .........................................................275

14.5 Outgoing 77.76 MHz TelecomBus Functional Timing .....................................277

14.6 Outgoing SBI336 Functional Timing ...............................................................277

15 Absolute Maximum Ratings ..................................................................................... 279

16 D. C. Characteristics................................................................................................280

17 Microprocessor Interface Timing Characteristics ....................................................281

18 A.C. Timing Characteristics .....................................................................................284

18.1 SBSLITE Incoming Bus Timing.......................................................................284

18.2 SBSLITE Receive Bus Timing ........................................................................285

18.3 SBSLITE Outgoing Bus Timing.......................................................................286

18.4 SBSLITE Transmit Bus Timing........................................................................287

18.5 JTAG Port Interface.........................................................................................288

19 Ordering and Thermal Information ..........................................................................289

19.1 Ordering Information .......................................................................................289

19.2 Thermal Information ........................................................................................289

20 Mechanical Information ........................................................................................... 290

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 4

Document ID: PMC-2010883, Issue 2

Page 6

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

List of Figures

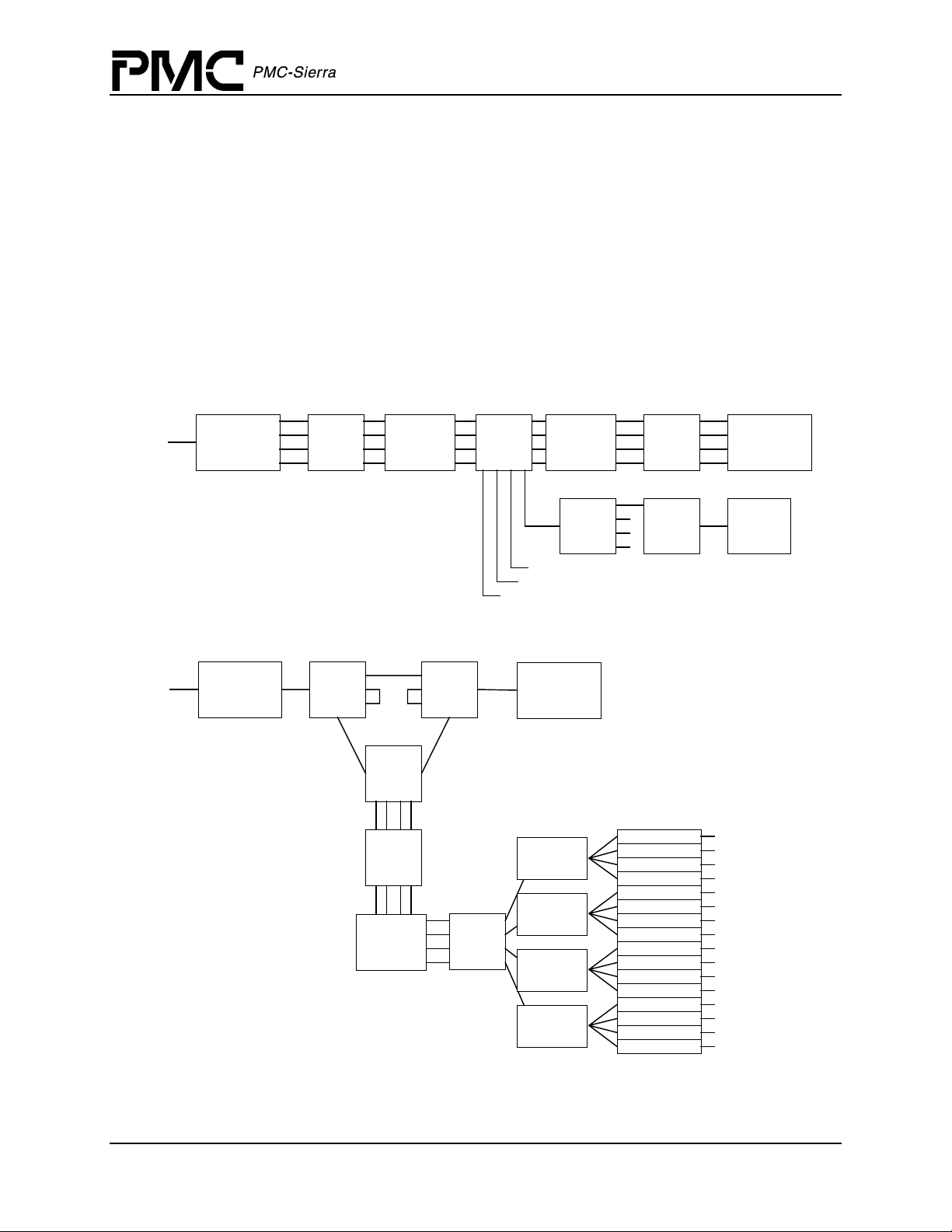

Figure 1 OC-48 T1/E1 ADM (Individually Drop/Add any T1/E1 in STS-48)....................13

Figure 2 OC-48 T1/E1 ADM (Drop/Add up to STS-48 at STS-1 Granularity) ................. 13

Figure 3 Any-Service-Any-Port NxDS0 TDM Access Solution........................................14

Figure 4 Any-Service-Any-Port T1/E1 Channelized PHY Card.......................................14

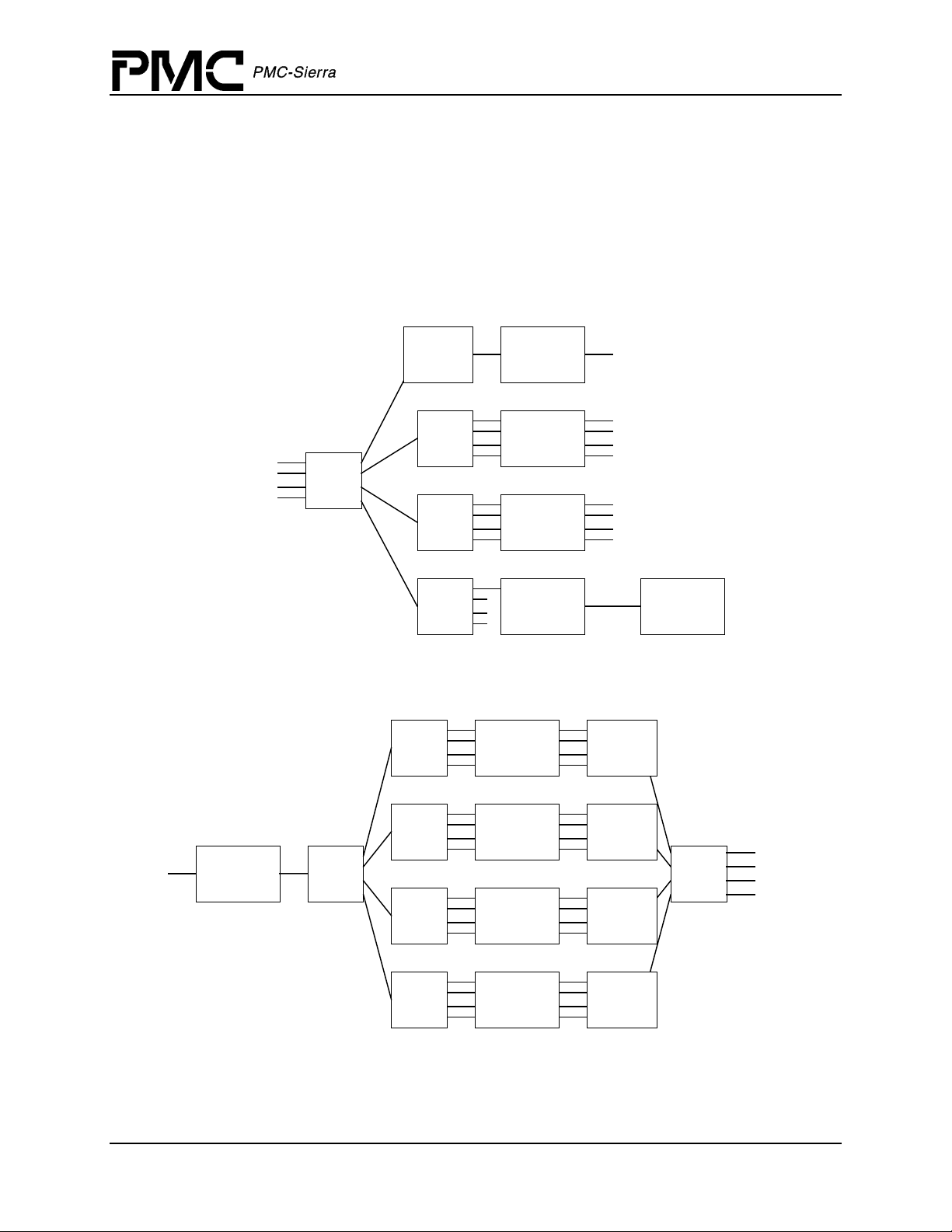

Figure 5 SBSLITE Block Diagram ...................................................................................15

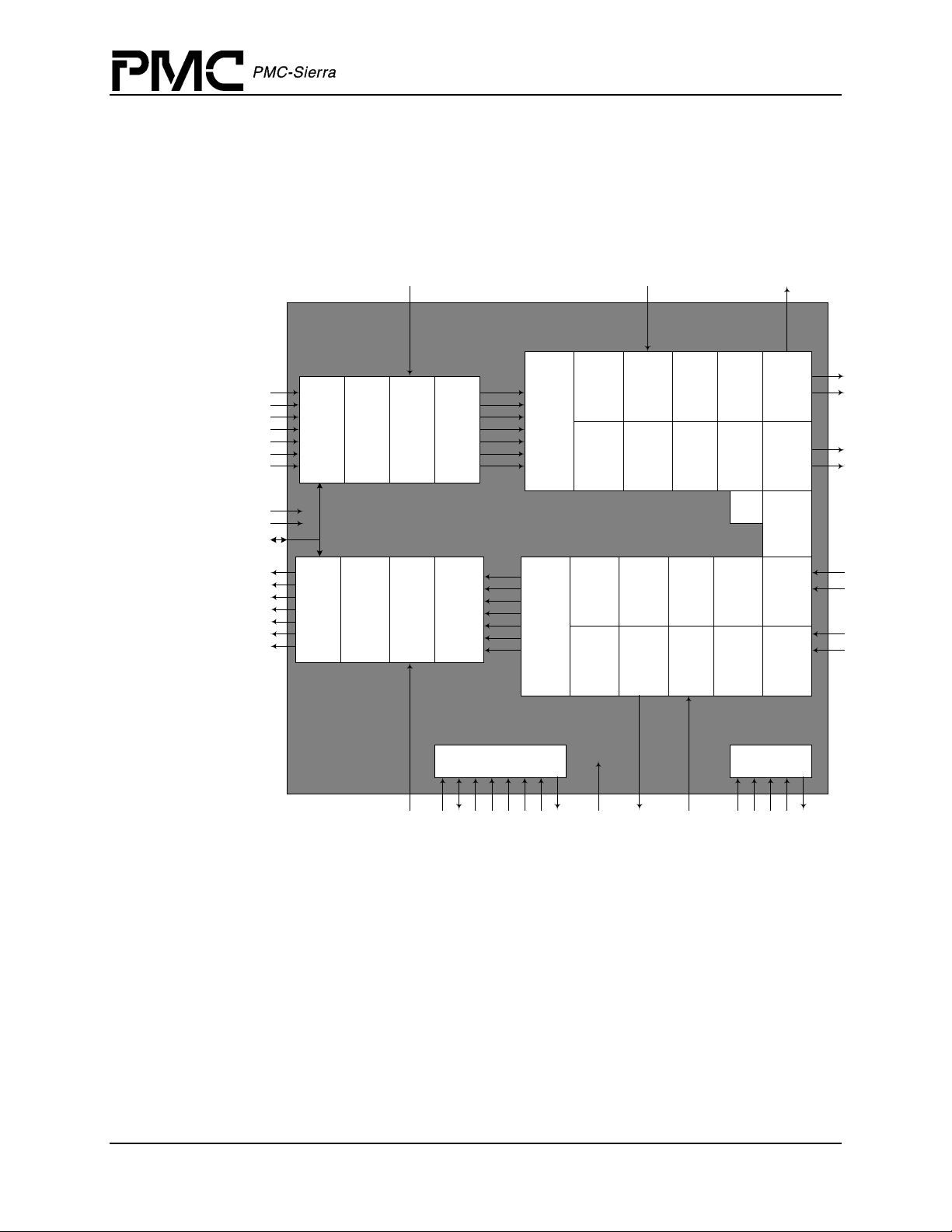

Figure 6 Loopback Block Diagram .................................................................................. 16

Figure 7 Pin Diagram (Bottom View)...............................................................................19

Figure 8 Character Alignment State Machine .................................................................60

Figure 9 Frame Alignment State Machine.......................................................................62

Figure 10 In-Band Signaling Channel Message Format .................................................64

Figure 11 In-Band Signaling Channel Header Format....................................................65

Figure 12 Input Observation Cell (IN_CELL) ................................................................252

Figure 13 Output Cell (OUT_CELL) ..............................................................................252

Figure 14 Bidirectional Cell (IO_CELL) .........................................................................253

Figure 15 Layout of Output Enable and Bidirectional Cells...........................................253

Figure 16 “C1” Synchronization Control........................................................................255

Figure 17 TEMUX-84™/SBSLITE™/NSE/SBSLITE™/AAL1gator-32™ system

DS0 Switching with CAS...............................................................................256

Figure 18 CAS Multiframe Timing .................................................................................257

Figure 19 Switch Timing DSOs with CAS .....................................................................257

Figure 20 TEMUX-84/SBSLITE/NSE/SBSLITE/FREEDM-336 System DS0

Switching no CAS .........................................................................................258

Figure 21 Switch Timing - DSOs without CAS ..............................................................259

Figure 22 Non DS0 Switch Timing ................................................................................260

Figure 23 Example Graph .............................................................................................262

Figure 24 Time:Space:Time Switching in one NSE-20G and four Single-Ported

SBSs .............................................................................................................263

Figure 25 Example Graph .............................................................................................264

Figure 26 Example Problem..........................................................................................265

Figure 27 Merged Graph ...............................................................................................265

Figure 28 Relabeled Graph ........................................................................................... 266

Figure 29 Boundary Scan Architecture .........................................................................268

Figure 30 TAP Controller Finite State Machine.............................................................269

Figure 31 Incoming SBI336 Functional Timing .............................................................272

Figure 32 Incoming 77 MHz TelecomBus Functional Timing .......................................274

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 5

Document ID: PMC-2010883, Issue 2

Page 7

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Figure 33 Incoming TelecomBus to LVDS Functional Timing ......................................274

Figure 34 Incoming SBI Bus to LVDS Timing with DS0 Switching ...............................275

Figure 35 Receive LVDS Link Timing ...........................................................................276

Figure 36 Outgoing Synchronization Timing .................................................................276

Figure 37 Outgoing 77.76 MHz TelecomBus Functional Timing ..................................277

Figure 38 Outgoing SBI336 Functional Timing .............................................................278

Figure 39 Microprocessor Interface Read Timing .........................................................281

Figure 40 Microprocessor Interface Write Timing .........................................................283

Figure 41 SBSLITE Incoming Timing ............................................................................ 285

Figure 42 SBSLITE Receive Timing..............................................................................286

Figure 43 SBSLITE Outgoing Timing ............................................................................ 287

Figure 44 SBSLITE Transmit Timing.............................................................................287

Figure 45 JTAG Port Interface Timing...........................................................................288

Figure 46 160 Pin PBGA 15 x 15 mm Body .................................................................. 290

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 6

Document ID: PMC-2010883, Issue 2

Page 8

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

List of Tables

Table 1 Structure for Carrying Multiplexed Links ............................................................35

Table 2 T1/TVT1.5 Tributary Column Numbering ........................................................... 35

Table 3 E1/TVT2 Tributary Column Numbering .............................................................. 36

Table 4 T1/E1 Link Rate Information...............................................................................37

Table 5 T1/E1 Clock Rate Encoding ...............................................................................37

Table 6 DS3/E3 Link Rate Information............................................................................38

Table 7 DS3/E3 Clock Rate Encoding ............................................................................38

Table 8 T1 Framing Format.............................................................................................39

Table 9 T1 Channel Associated Signaling Bits ...............................................................41

Table 10 E1 Framing Format ..........................................................................................42

Table 11 E1 Channel Associated Signaling Bits ............................................................. 44

Table 12 DS3 Framing Format........................................................................................45

Table 13 DS3 Block Format ............................................................................................ 45

Table 14 DS3 Multi-frame Stuffing Format......................................................................45

Table 15 E3 Framing Format ..........................................................................................46

Table 16 E3 Frame Stuffing Format ................................................................................47

Table 17 Transparent VT1.5/TU11 Format .....................................................................48

Table 18 Transparent VT2/TU12 Format ........................................................................49

Table 19 Fractional Rate Format.....................................................................................51

Table 20 Structure for Carrying Multiplexed Links in SBI336..........................................52

Table 21 SBI336S Character Encoding ..........................................................................55

Table 22 Serial TelecomBus Character Encoding ..........................................................57

Table 23 In-band Message Header Fields ...................................................................... 65

Table 24 Test Mode Register Memory Map .................................................................. 240

Table 25 Instruction Register (Length - 3 bits) ..............................................................242

Table 26 Identification Register.....................................................................................243

Table 27 Boundary Scan Register ................................................................................244

Table 28 Absolute Maximum Ratings............................................................................279

Table 29 D.C Characteristics ........................................................................................280

Table 30 Microprocessor Interface Read Access (Figure 39).......................................281

Table 31 Microprocessor Interface Write Access (Figure 40) .......................................283

Table 32 SBSLITE Incoming Timing (Figure 41) ..........................................................284

Table 33 SBSLITE Receive Timing (Figure 42) ............................................................285

Table 34 SBSLITE Outgoing Timing (Figure 43) ..........................................................286

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 7

Document ID: PMC-2010883, Issue 2

Page 9

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Table 35 SBSLITE Transmit Timing (Figure 44) ...........................................................287

Table 36 JTAG Port Interface (Figure 45) ..................................................................... 288

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 8

Document ID: PMC-2010883, Issue 2

Page 10

1 Features

• The PM8611 SBI336 Bus Serializer (SBSLITE™) is a:

° Scalable Bandwidth Interconnect (SBI™) converter and Time Division Multiplexer

(TDM) SBI switch.

° Byte-wide 77.76 MHz SBI336 bus to 777.6 MHz serial SBI336S converter.

° DS0, NxDS0, T1, E1, TVT1.5, TVT2, DS3 and E3 granular SBI336 to serial SBI336S

switch. Supports subrate link switching with the restriction that subrate links must be

symmetric in both the transmit and receive directions.

° Byte-wide 77.76 MHz TelecomBus to serial 777.6 MHz TelecomBus converter. This

requires the TelecomBus J1 byte to be in a fixed location corresponding to a value of 0 or

522 which is immediately following the C1 octets:

° VT1.5, VT2, STS-1 77.76 MHz TelecomBus to serial TelecomBus switch.

• Can be used with the Narrowband Switch Elements, NSE-20G, to implement a DS0

granularity SBI Memory:Space:Memory switch scalable to 20 Gbit/s and NSE-8G, to

implement a switch scalable to 8 Gbit/s. In TelecomBus mode, a 20 Gbit/s VT1.5/VT2

granularity Memory:Space:Memory switch can be implemented.

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

• Integrates two independent DS0 granularity Memory Switches. One switch is placed

between the incoming 77.76 MHz byte-wide SBI336 bus and the transmit working and

protect Serial SBI336S link. The transmit working and protect links transmit the same data.

The other switch is placed between the receive working or protect Serial SBI336S link and

the outgoing 77.76 MHz byte-wide SBI336 bus.

• Provides 125 µS nominal latency in DS0 mode. Channel Associated Signaling (CAS) latency

through the SBSLITE in DS0 mode is two T1 multiframe (6 mS) or two E1 multiframe (4

mS).

• Provides less than 16 µS nominal latency in TelecomBus mode or SBI mode without DS0

level switching.

• Permits any receive or incoming byte from an input port to be mapped to any outgoing or

transmit byte, respectively, on the associated output port through the Memory switch.

• Supports redundant working and protect serial SBI336S links in support of a redundant

Memory:Space:Memory switch with the NSE.

• Encodes and decodes byte-wide SBI336 bus control signals for all SBI supported link types

and clock modes for transport over the serial SBI336S interface.

• Encodes data from the Incoming SBI336 bus or TelecomBus stream to a working and protect

777.6 Mbit/s LVDS serial links with 8B/10B-based encoding.

• Decodes data from a working and protect 777.6 MHz low voltage differential serializer

(LVDS) serial links with 8B/10B-based encoding to the Outgoing SBI336 bus or TelecomBus

stream.

• In SBI mode, switches CAS bits with all DS0 data.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 9

Document ID: PMC-2010883, Issue 2

Page 11

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

• Uses 8B/10B-based line coding protocol on the serial links to provide transition density

guarantee and DC balance and to offer a greater control character vocabulary than the

standard 8B/10B protocol.

• Provides optional pseudo-random bit sequence (PRBS) generation for each outgoing LVDS

serial data link for off-line link verification. PRBS can be inserted with STS-1 granularity.

• Provides PRBS detection for each incoming LVDS serial link for off-line link verification.

PRBS is verified with STS-1 granularity.

• Provides pins to coordinate updating of the connection map of the memory switch blocks in

the local device, peer SBSLITE devices and companion NSE switch device.

• Can communicate with the NSE switch device over an in-band communications channel in

the LVDS links. This channel includes mechanisms for central control and configuration.

• Derives all internal timing from a single 77.76 MHz system clock to a system frame pulse.

• Implemented in 1.8 V/3.3 V 0.18 µm CMOS and packaged in a 160 ball 15 mm x 15 mm

PBGA.

• Consumes low power at 1.4 W.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 10

Document ID: PMC-2010883, Issue 2

Page 12

2 Applications

• T1/E1 SONET/SDH Cross-connects

• T1/E1 SONET/SDH Add-Drop Multiplexers

• OC-48 Multiservice Access Multiplexers

• Channelized OC-12/OC-48 Any Service Any Port Switches

• Serial Backplane Board Interconnect

• Shelf to Shelf Cabled Serial Interconnect

• Voice Gateways

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 11

Document ID: PMC-2010883, Issue 2

Page 13

3 References

1. IEEE 802.3, “Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access

Method and Physical Layer Specifications”, Section 36.2, 1998.

2. A.X. Widmer and P.A. Franaszek, “A DC-Balanced, Partitioned-Block, 8B/10B Transmission

Code,” IBM Journal of Research and Development, Vol. 27, No 5, September 1983, pp 440-

451.

3. U.S. Patent No. 4,486,739, P.A. Franaszek and A.X. Widmer, “Byte Oriented DC Balanced

(0,4) 8B/10B Partitioned Block Transmission Code,” December 4, 1984.

4. Telcordia - SONET Transport Systems: Common Generic Criteria, GR-253-CORE, Issue 2,

Revision 2, January 1999.

5. ITU, Recommendation G.707 - "Digital Transmission Systems – Terminal equipments -

General", March 1996.

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

6. ITU, Recommendation O.151 – “Error Performance Measuring Equipment Operating at the

Primary Rate and Above", October 1992.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 12

Document ID: PMC-2010883, Issue 2

Page 14

4 Application Examples

Figure 1 and Figure 2 show a PM8611 SBI336 Bus Serializer-lite (SBSLITE) connected to a

TelecomBus to implement a T1 or E1 Add/Drop function. When connected to the TelecomBus,

the SBSLITE with a PM8620 or PM8621 Narrowband Switching Element (NSE-8G™ or NSE20G™) implements a T1/E1 Memory:Space:Memory switch. The SBSLITE requires all path

pointer justifications to be translated into tributary pointer movements so that J1 is fixed to the

location following C1 or H3. In both examples J1 alignment is performed with the TUPP-622.

Switching within the SBSLITE and NSE is utilizing the Transparent Virtual Tributary, TVT,

mapping across the serial SBI336S LVDS links.

Figure 1 OC-48 T1/E1 ADM (Individually Drop/Add any T1/E1 in STS-48)

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

SPECTRA-

2488

4 X

TUPP-

622

4 X

SBSLITE

NSE

4 X

SBSLITE

SBS

4 X

TUPP-

622

1 X

TEMAP

-84

Figure 2 OC-48 T1/E1 ADM (Drop/Add up to STS-48 at STS-1 Granularity)

SPECTRA-

2488

TBS TBS

TBS

4 X

TUPP-

622

4 X

SBSLITE

NSE

SPECTRA-

2488

4 X

SBSLITE

4 X

SBSLITE

4 X

SBSLITE

4 X

SBSLITE

TEMUX84

TEMUX84

TEMUX84

TEMUX84

TEMUX84

TEMUX84

TEMUX84

TEMUX84

TEMUX84

TEMUX84

TEMUX84

TEMUX84

TEMUX84

TEMUX84

TEMUX84

TEMUX84

SPECTRA-

2488

11 X

OCTLIU

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 13

Document ID: PMC-2010883, Issue 2

Page 15

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Figure 3 and Figure 4 show examples of the SBS and SBSLITE when used to implement high

density T1/E1 Channelized Physical Interface cards and NxDS0 Multiservice access cards also

using SBS and NSE devices. DS0, NxDS0, T1, E1, Transparent VTs, E3, DS3 and subrate rate

links can be switched between the physical layer and layer 2 devices using the SBS, SBSLITE

and NSE devices.

Figure 3 Any-Service-Any-Port NxDS0 TDM Access Solution

4 X

SBSLITE

SBS

NSE

SBS

SBS

FREEDM-

336

4 X

IMA-84

12 X

AAL1gator-

32

11 X

OCTLIU

Serial

Clock and

Data

Figure 4 Any-Service-Any-Port T1/E1 Channelized PHY Card

TBS

4 X

TEMUX-84

SBSLITE

4 X

Any-PHY

(Packet)

Any-PHY

(Cell)

Any-PHY

(Cell)

Processors

DSP

SPECTRA-

2488

TBS

TBS

TBS

TBS

4 X

TEMUX-84

4 X

TEMUX-84

4 X

TEMUX-84

4 X

SBSLITE

NSE

4 X

SBSLITE

4 X

SBSLITE

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 14

Document ID: PMC-2010883, Issue 2

Page 16

5 Block Diagram

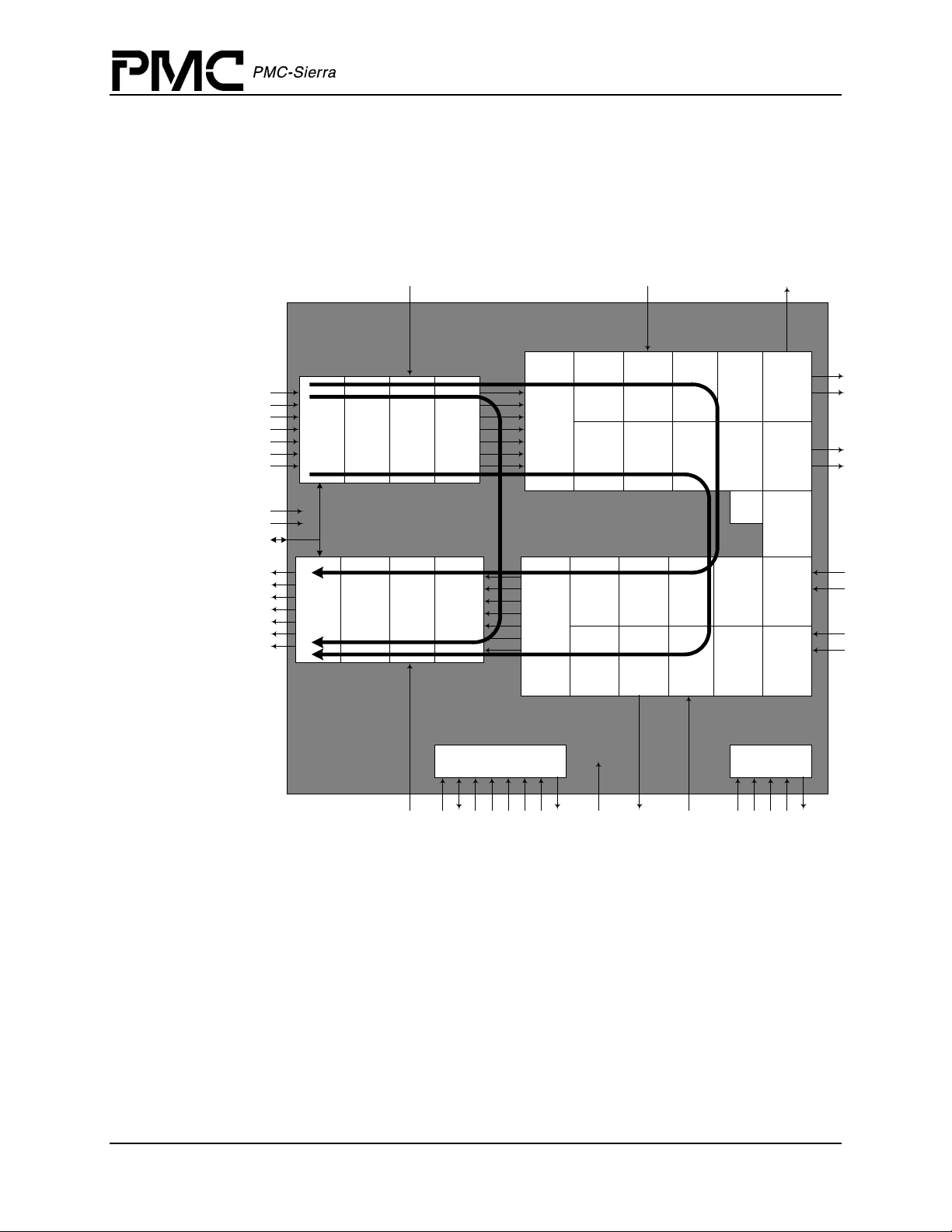

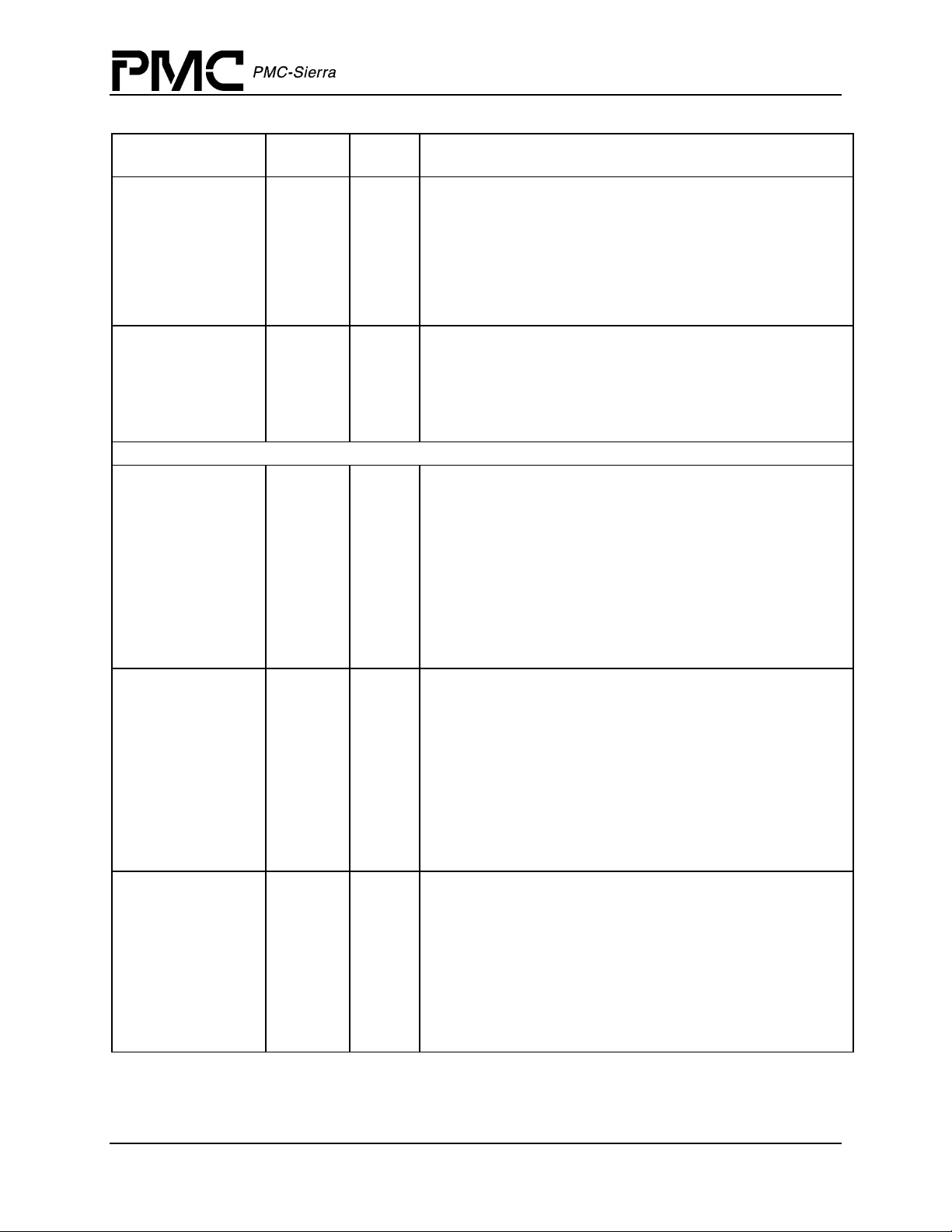

Figure 5 SBSLITE Block Diagram

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

IDATA[7:0]

IDP

IPL

IV5

IC1FP

ITPL

ITAIS

SREFCLK

SYSCLK

JUST_REQ

ODATA[7:0]

ODP

OPL

OV5

OC1FP

OTPL

OTAIS

Incoming

SBI336

Timing

Adaptor

(ISTA)

Outgoing

SBI336

Timing

Adaptor

(OSTA)

Incoming

CAS

Expand

(ICASE)

Outgoing

CAS

Merge

(OCASM)

ICMP

Incoming

Memory

Switch

Unit

(IMSU)

Outgoing

Memory

Switch

Unit

(OMSU)

Incoming

CAS

Merge

(ICASM)

Outgoing

CAS

Expand

(OCASE)

Incoming

SBI

Tributary

Translator

(ISTT)

Outgoing

SBI

Tributary

Translator

(OSTT)

1/2

Working

PRBS

Processor

(WPP)

1/2

Protect

PRBS

Processor

(PPP)

1/2

Working

PRBS

Processor

(WPP)

1/2

Protect

PRBS

Processor

(PPP)

IUSER

1/2

Working

In-Band

Link

Controller

(WILC)

1/2

Protect

In-Band

Link

Controller

(PILC)

1/2

Working

In-Band

Link

Controller

(WILC)

1/2

Protect

In-Band

Link

Controller

(PILC)

Transmit

Working

8B/10B

Encoder

(TW8E)

Transmit

Protect

8B/10B

Encoder

(TP8E)

Receive

Working

8B/10B

Decoder

(RW8D)

Receive

Protect

8B/10B

Decoder

(RP8D)

Transmit

Working

Serializer

(TWPS)

Transmit

Protect

Serializer

(TPPS)

Tx

Ref

Working

Data

Recovery

Unit

(WDRU)

Protect

Data

Recovery

Unit

(PDRU)

TC1FP

Transmit

Working

LVDS

Interface

(TWLV)

Transmit

Protect

LVDS

Interface

(TPLV)

Clock

Synthesis

Unit

Receive

Working

LVDS

Interface

(RWLV)

Receive

Protect

LVDS

Interface

(RPLV)

TPWRK

TNWRK

TPPROT

TNPROT

RPWRK

RNWRK

RPPROT

RNPROT

Microprocessor Interface

A[8:0]

OCMP

D[15:0]

WRB

RDB

ALE

INTB

OUSER

RWSEL

RC1FP

CSB

RSTB

JTAG

TDI

TCK

TMS

TRSTB

TDO

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 15

Document ID: PMC-2010883, Issue 2

Page 17

6 Loopback Configurations

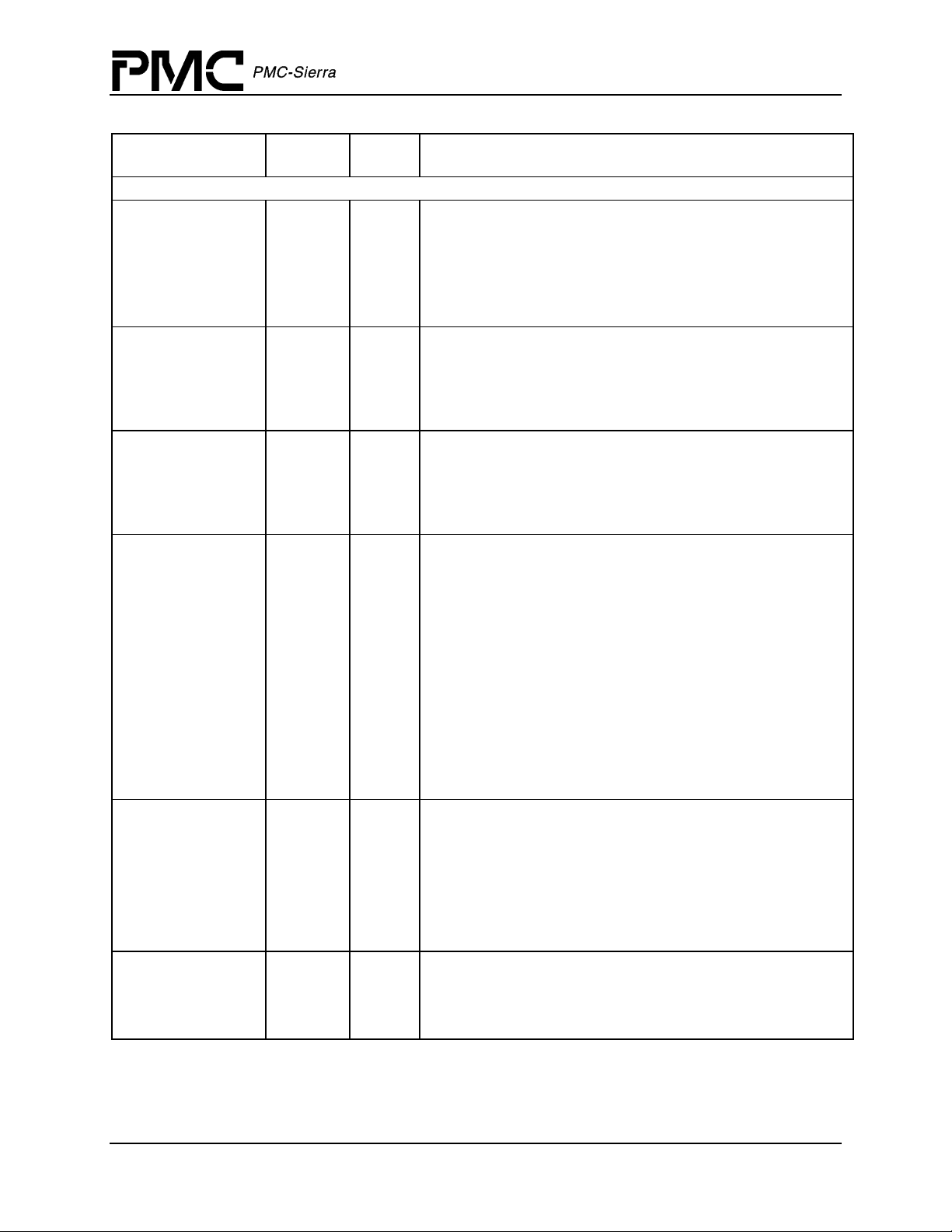

Figure 6 Loopback Block Diagram

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

IDATA[7:0]

IDP

IPL

IV5

IC1FP

ITPL

ITAIS

SREFCLK

SYSCLK

JUST_REQ

ODATA[7:0]

ODP

OPL

OV5

OC1FP

OTPL

OTAIS

Incoming

SBI336

Timing

Adaptor

(ISTA)

Outgoing

SBI336

Timing

Adaptor

(OSTA)

Incoming

CAS

Expand

(ICASE)

Outgoing

CAS

Merge

(OCASM)

ICMP

Incoming

Memory

Switch

Unit

(IMSU)

Outgoing

Memory

Switch

Unit

(OMSU)

Incoming

CAS

Merge

(ICASM)

Outgoing

CAS

Expand

(OCASE)

Incoming

SBI

Tributary

Translator

(ISTT)

Outgoing

SBI

Tributary

Translator

(OSTT)

1/2

Working

PRBS

Processor

(WPP)

1/2

Protect

PRBS

Processor

(PPP)

1/2

Working

PRBS

Processor

(WPP)

1/2

Protect

PRBS

Processor

(PPP)

IUSER

1/2

Working

In-Band

Link

Controller

(WILC)

1/2

Protect

In-Band

Link

Controller

(PILC)

1/2

Working

In-Band

Link

Controller

(WILC)

1/2

Protect

In-Band

Link

Controller

(PILC)

Transmit

Working

8B/10B

Encoder

(TW8E)

Transmit

Protect

8B/10B

Encoder

(TP8E)

Receive

Working

8B/10B

Decoder

(RW8D)

Receive

Protect

8B/10B

Decoder

(RP8D)

Transmit

Working

Serializer

(TWPS)

Transmit

Protect

Serializer

(TPPS)

Tx

Ref

Working

Data

Recovery

Unit

(WDRU)

Protect

Data

Recovery

Unit

(PDRU)

TC1FP

Transmit

Working

LVDS

Interface

(TWLV)

Transmit

Protect

LVDS

Interface

(TPLV)

Clock

Synthesis

Unit

Receive

Working

LVDS

Interface

(RWLV)

Receive

Protect

LVDS

Interface

(RPLV)

TPWRK

TNWRK

TPPROT

TNPROT

RPWRK

RNWRK

RPPROT

RNPROT

Microprocessor Interface

A[8:0]

OCMP

D[15:0]

WRB

RDB

ALE

INTB

OUSER

RWSEL

RC1FP

CSB

RSTB

JTAG

TDI

TCK

TMS

TRSTB

TDO

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 16

Document ID: PMC-2010883, Issue 2

Page 18

7 Description

The PM8611 SBI336 Bus Serializer, SBSLITE, is a monolithic integrated circuit that implements

conversion between a byte-serial 77.76 MHz SBI336 bus and redundant 777.6 Mbit/s bit-serial

8B/10B-base SBI336S bus. In TelecomBus mode, the SBSLITE implements conversion between

a 77.76 MHz TelecomBus format and a redundant 777.6 Mbit/s bit-serial 8B/10B-base serial

TelecomBus format. In line with the bus conversion is a DS0 granular switch allowing any input

DS0 to be output on any output DS0.

The SBSLITE can be used to connect and switch high density T1/E1 framer devices supporting

an SBI bus with link layer devices supporting an SBI bus over a serial backplane. Putting a

Narrowband Switch Element (NSE) between the framer and link layer devices allows

construction of up to 20 Gbit/s NxDS0 switches.

In the ingress direction, the SBSLITE connects an incoming 77.76 MHz SBI336 stream to a pair

of redundant serial SBI336S LVDS links through a DS0 memory switch. In TelecomBus mode,

an incoming 77.76 MHz TelecomBus that has the J1 path fixed and all high order pointer

justifications converted to tributary pointer justifications can be switched through a VT granular

switch to a pair of redundant serial LVDS TelecomBus format links. The incoming data is

encoded into an extended set of 8B/10B characters and transferred onto two redundant 777.6

Mbit/s serial LVDS links. SBI or TelecomBus frame boundaries, pointer justification events and

master timing controls are marked by 8B/10B control characters. Incoming synchronized payload

envelopes (SPEs) may be optionally overwritten with the locally generated X

pattern for diagnosis of downstream equipment. The PRBS processor is configurable to handle

any combination of SPEs and can be inserted independently into either of the redundant LVDS

links. A DS0 memory switch provides arbitrary mapping of streams on the incoming SBI336 bus

stream to the working and protect LVDS links at DS0 granularity. In TelecomBus mode, a

VT1.5/VT2 memory switch provides arbitrary mapping of tributaries on the incoming

TelecomBus stream to the working and protect LVDS links. Multi-cast is supported.

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

23

+ X18 + 1 PRBS

In the egress direction, the SBSLITE connects two independent 777.6 Mbit/s serial LVDS links to

an outgoing SBI336 Bus. Each link contains a constituent SBI336S stream. Bytes on the links

are carried as 8B/10B characters. The SBSLITE decodes the characters into data and control

signals for a single 77.76 MHz SBI336 bus. Alternatively the SBSLITE decodes two independent

777.6 Mbit/s TelecomBus formatted serial LVDS links characters into a single 77.76 MHz

TelecomBus. A PRBS processor is provided to monitor the decoded payload for the X

23

+ X18 + 1

pattern in each SPE. The PRBS processor is configurable to handle any combination of

synchronized payload envelopes (SPEs) in the serial LVDS link. Data on the outgoing SBI336

bus stream may be sourced from either of the LVDS links.

An In-band signaling link over the serial LVDS links allows this device to be controlled by a

companion switching device, the Narrowband Switching Element, PM8620 NSE-20G. This link

can be used as communication link between a central processor and the local microprocessor.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 17

Document ID: PMC-2010883, Issue 2

Page 19

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Two loopbacks are provided on the SBSLITE. The transmit 8B/10B-to-receive 8B/10B loopback

allows data entering on the incoming bus to be looped back from the output of the TW8E and

TP8E to the input of the RW8D and RP8D, respectively. Only the data looped back on the active

link (working or protection) will make it back to the outgoing bus. The transmit-to-receive

loopback allows data entering on the incoming bus to be looped back from the output of the

ICASM to the input of the OCASE and then returned to the outgoing bus.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 18

Document ID: PMC-2010883, Issue 2

Page 20

SBSLITE™ Telecom Standard Product Data Sheet

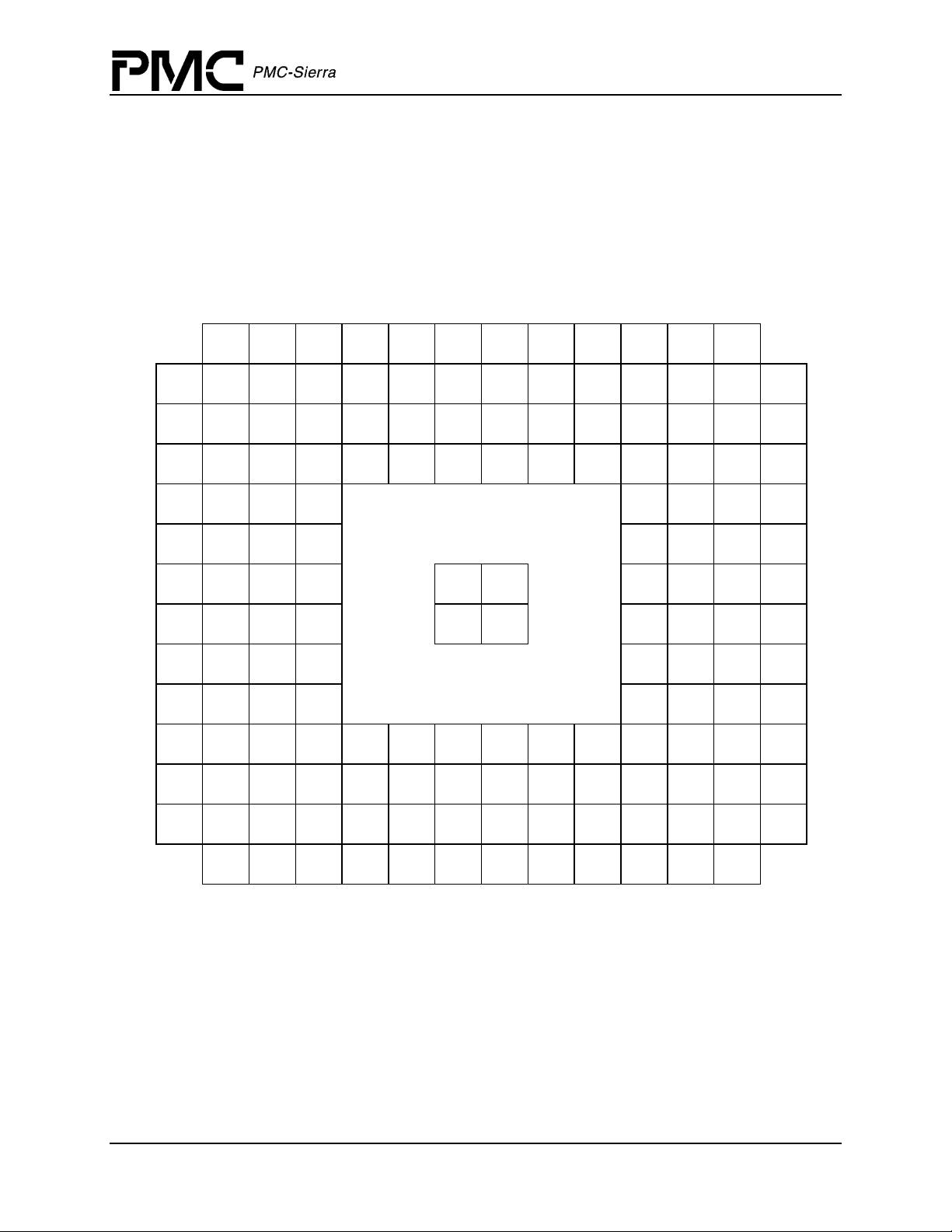

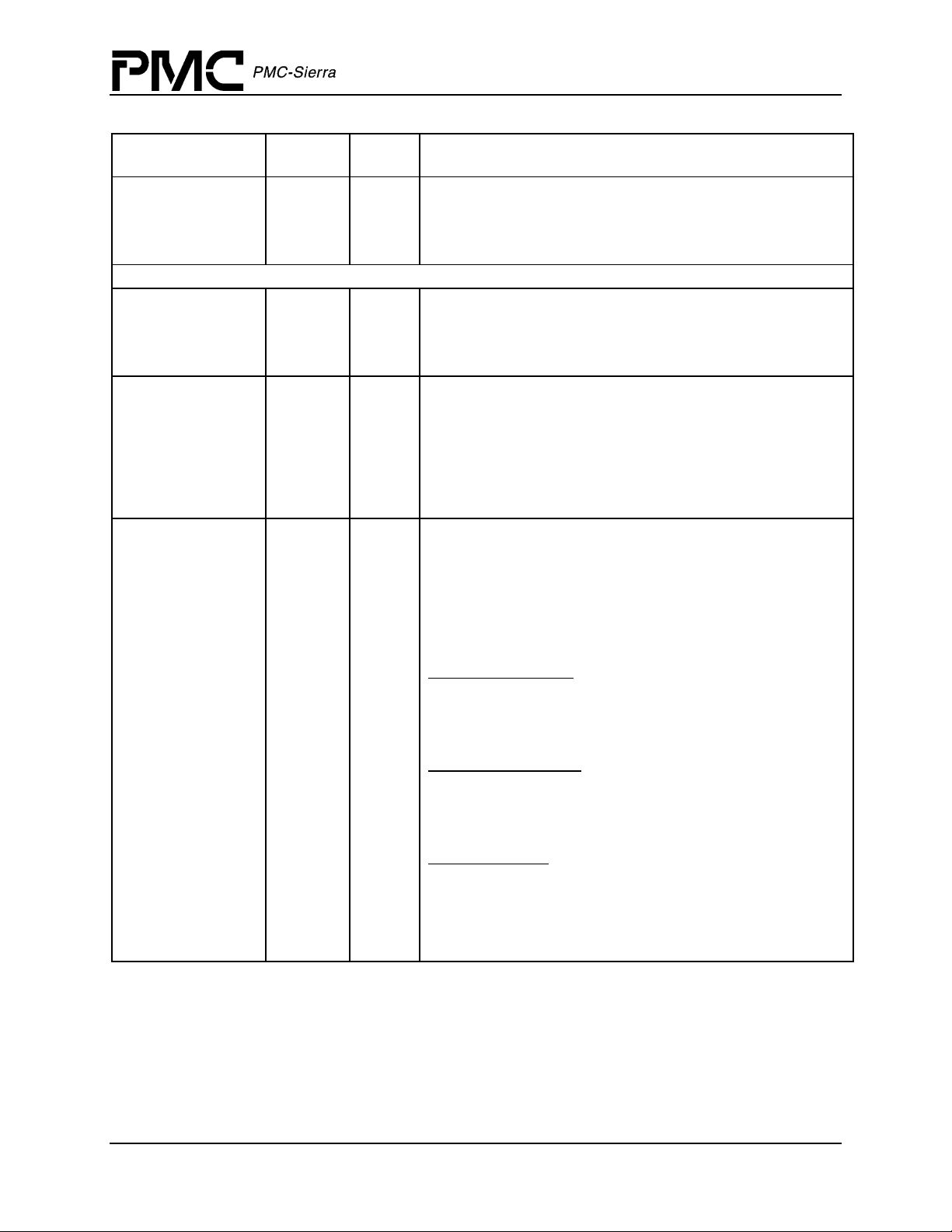

8 Pin Diagram

The SBSLITE is packaged in a 160-pin PBGA package having a body size of 15 mm by 15 mm

and a ball pitch of 1 mm.

Figure 7 Pin Diagram (Bottom View)

14 13 12 11 10 9 8 7 6 5 4 3 2 1

Preliminary

A

B

C

D

E

F

G

H

J

K

L

M

DVDDO SYSCLK DVDDI VSS DVDDO OTPL VSS ODATA[4] DVDDI ODATA[0] DVDDO DVDDO

IDATA[0] VSS SREFCLK VSS ICMP VSS OV5 ODATA[6] VSS ODATA[2] VSS VSS RESK VSS

IDATA[3] IDATA[1] IDATA[2] VSS DVDDQ OC1FP DVDDO ODATA[7] DVDDO VSS ODP TC1FP RES AVDH

IDATA[6] IDATA[4] IDATA[5] OCMP VSS OPL OTAIS ODATA[5] ODATA[3] ODATA[1] AVDH VSS TNPROT TPPROT

IDP DVDDO VSS IDATA[7] VSS AVDH TPWRK TNWRK

IPL IV5 IC1FP ITPL ATB0 ATB1 RPWRK RNWRK

VSS DVDDI INTB ITAIS GND GND AVDL VSS RPPROT RNPROT

DVDDO TCK TDO VSS GND GND AVDL AVDQ VSS CSU_AVD

TDI DVDDQ TRSTB TMS AVDL AVDL VSS VSS

OUSER2 NC JUST_REQVSS VSS VSS DVDDI VSS

A[1] DVDDI VSS A[0] D[2] D[6] VSS VSS D[10] IUSER2 D[15] VSS ALE DVDDI

A[2] A[3] A[6] D[0] D[4] VSS D[8] VSS D[11] VSS DVDDO WRB CSB RDB

A

B

C

D

E

F

G

H

H

J

K

L

M

A[4] A[5] VSS A[8] D[3] DVDDO D[7] D[9] D[13] D[14] RC1FP RWSEL DVDDO DVDDO

N

P

DVDDO A[7] D[1] D[5] DVDDI DVDDQ DVDDO D[12] DVDDI VSS RSTB VS S

N

P

14 13 12 11 10 9 8 7 6 5 4 3 2 1

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 19

Document ID: PMC-2010883, Issue 2

Page 21

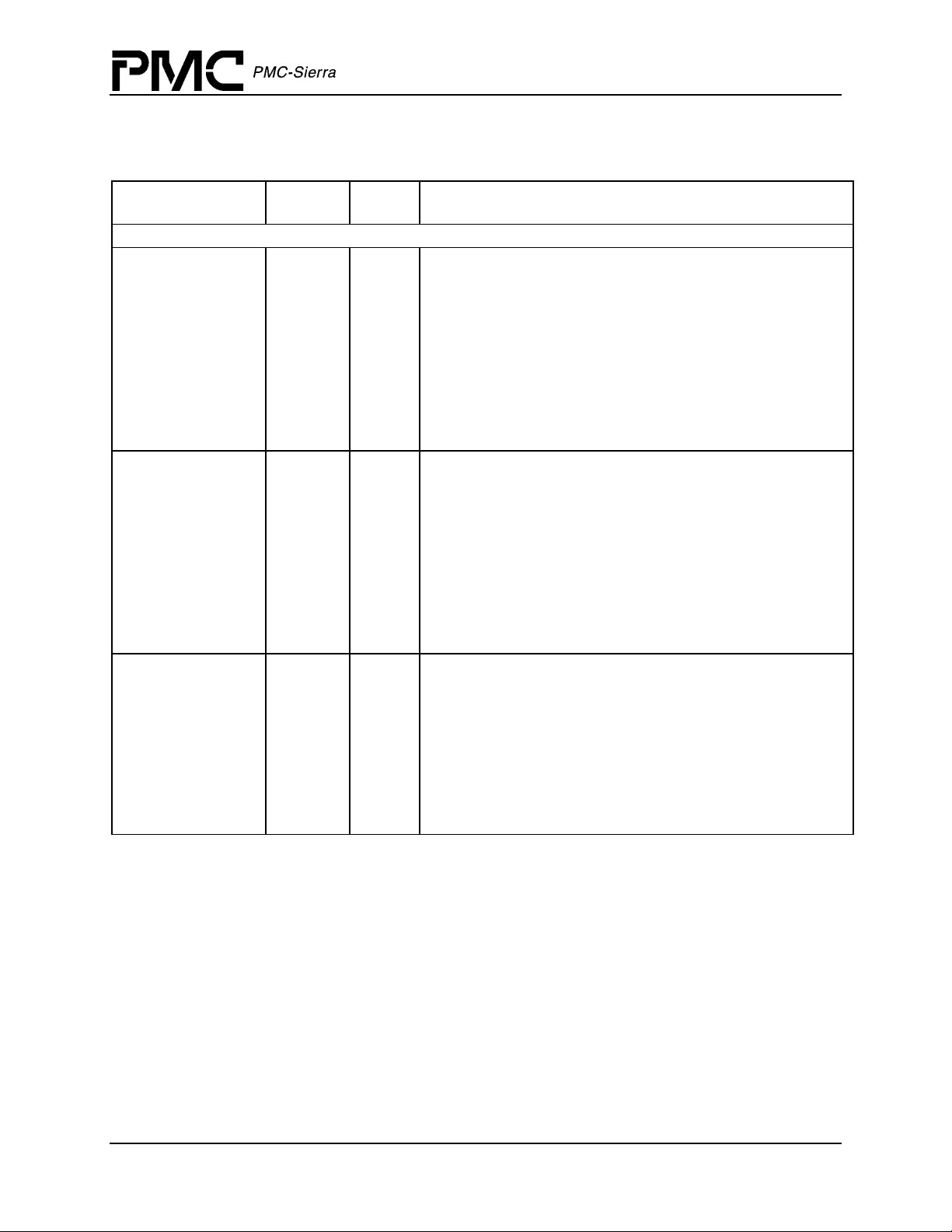

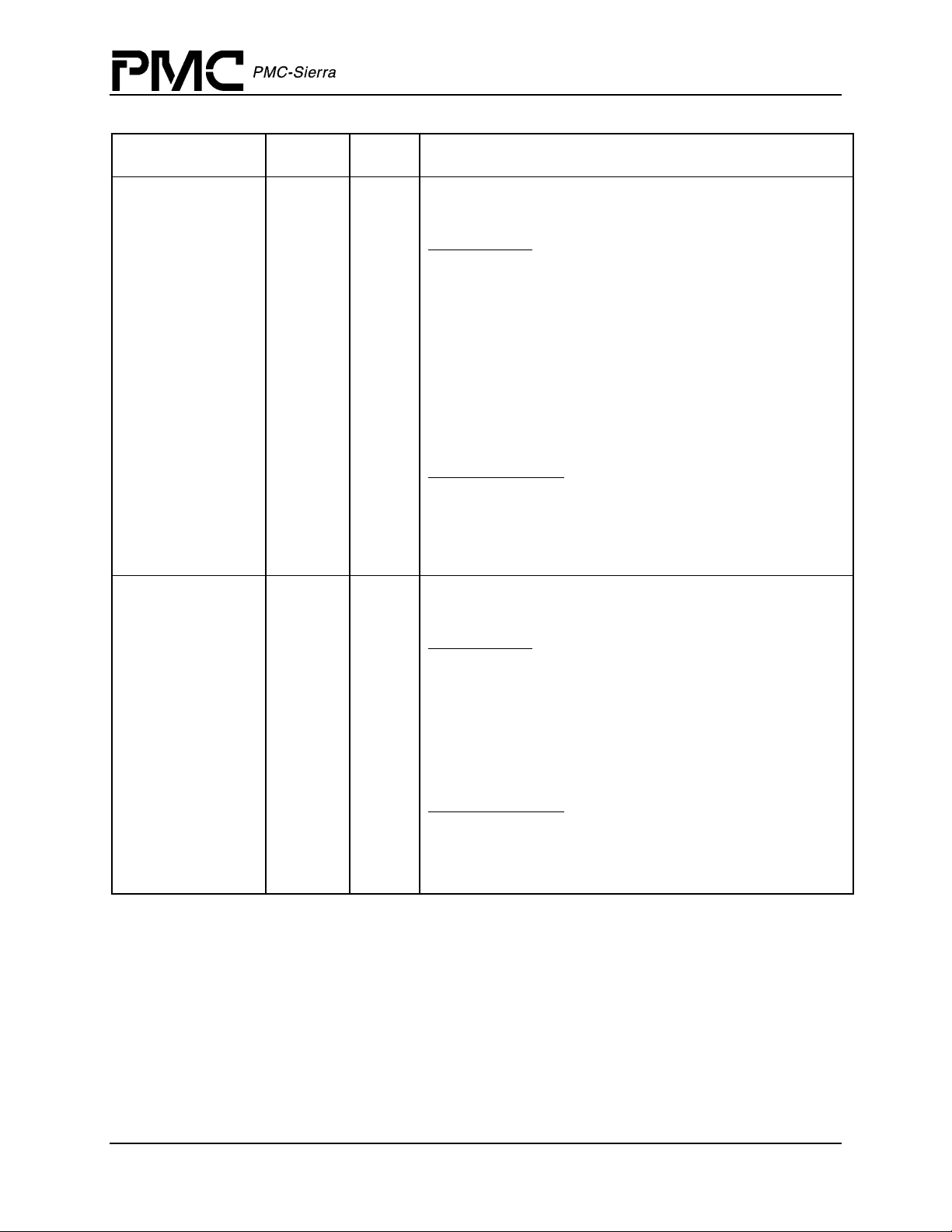

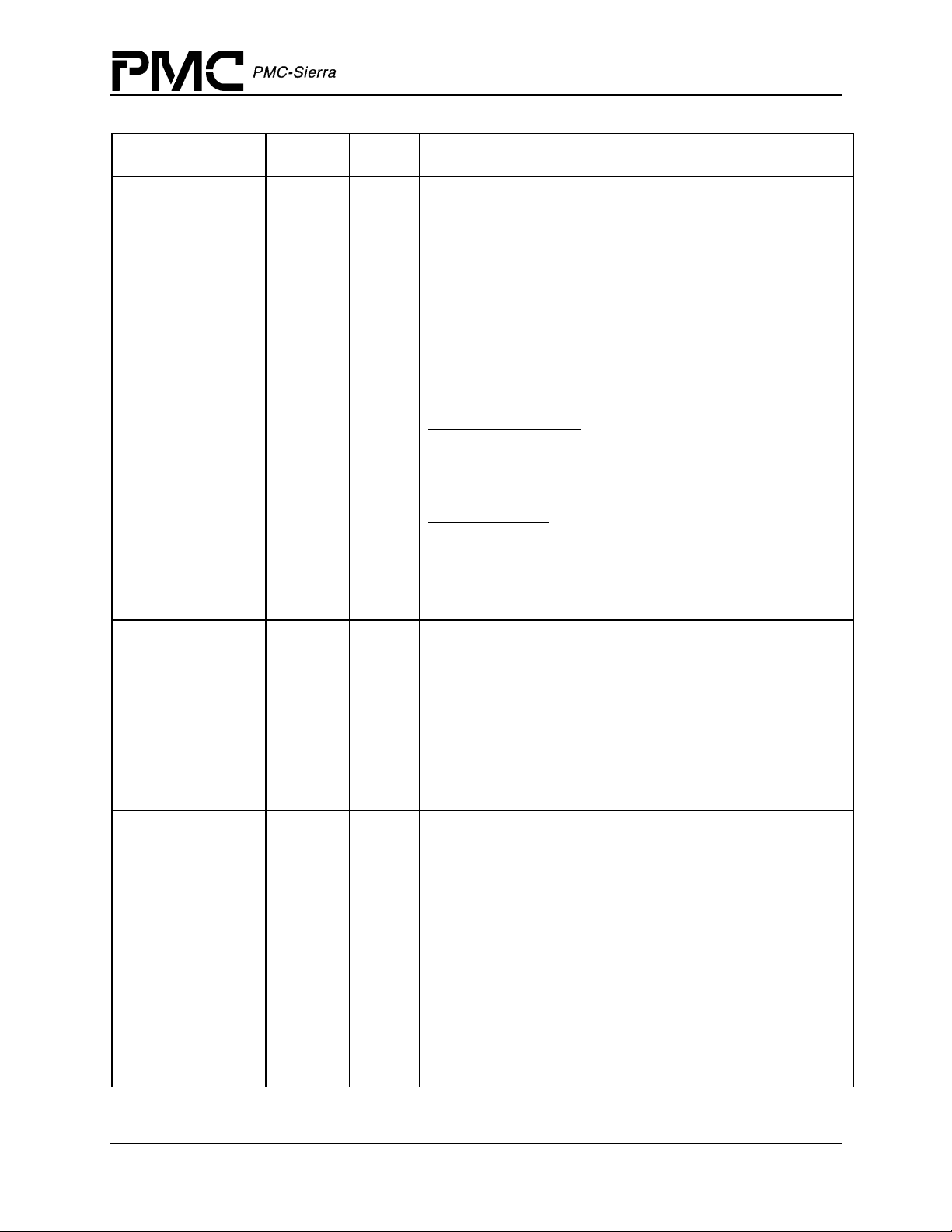

9 Pin Description

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type Pin

No.

Receive Serial Data Interface (5 Signals)

RPWRK

RNWRK

RPPROT

RNPROT

RC1FP Input N4

Analog

LVDS

Input

Analog

LVDS

Input

F2

F1

G2

G1

Function

Receive Working Serial Data. In SBI336 mode, the differential

receive working serial data link (RPWRK/RNWRK) carries the

receive 77.76 MHz SBI336 data from an upstream working source,

in bit serial format, SBI336S.

In TelecomBus mode, RPWRK/RNWRK carries the receive 77.76

MHz TelecomBus from an upstream working source, in bit serial

format.

Data on RPWRK/RNWRK is encoded in an 8B/10B format

extended from IEEE Std. 802.3. The 8B/10B character bit ‘a’ is

transmitted first and the bit ‘j’ is transmitted last.

RPWRK/RNWRK are nominally 777.6 Mbit/s data streams.

Receive Protect Serial Data. In SBI336 mode, the differential

receive protect serial data link (RPPROT/RNPROT) carries the

receive 77.76 MHz SBI336 data from an upstream protect source,

in bit serial format, SBI336S.

In TelecomBus mode, RPPROT/RNPROT carries the receive

77.76 MHz TelecomBus from an upstream protection source, in bit

serial format.

Data on RPPROT/RNPROT is encoded in an 8B/10B format

extended from IEEE Std. 802.3. The 8B/10B character bit ‘a’ is

transmitted first and the bit ‘j’ is transmitted last.

RPPROT/RNPROT are nominally 777.6 Mbit/s data streams.

Receive Serial Frame Pulse. The receive serial SBI336S frame

pulse signal (RC1FP) provides system timing of the receive serial

interface.

When using the receive serial interface, RC1FP is set high once

every multiframe (4 frames for SBI without CAS, 48 frames for SBI

with CAS, and 4 frames for TelecomBus), or multiple thereof. The

RC1FP_DLY[13:0] bits (register 007H) are used to align the C1

frame boundary 8B/10B character on the receive serial interface

(RPWRK/RNWRK and RPPROT/RNPROT) with RC1FP.

RC1FP is sampled on the rising edge of SYSCLK.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 20

Document ID: PMC-2010883, Issue 2

Page 22

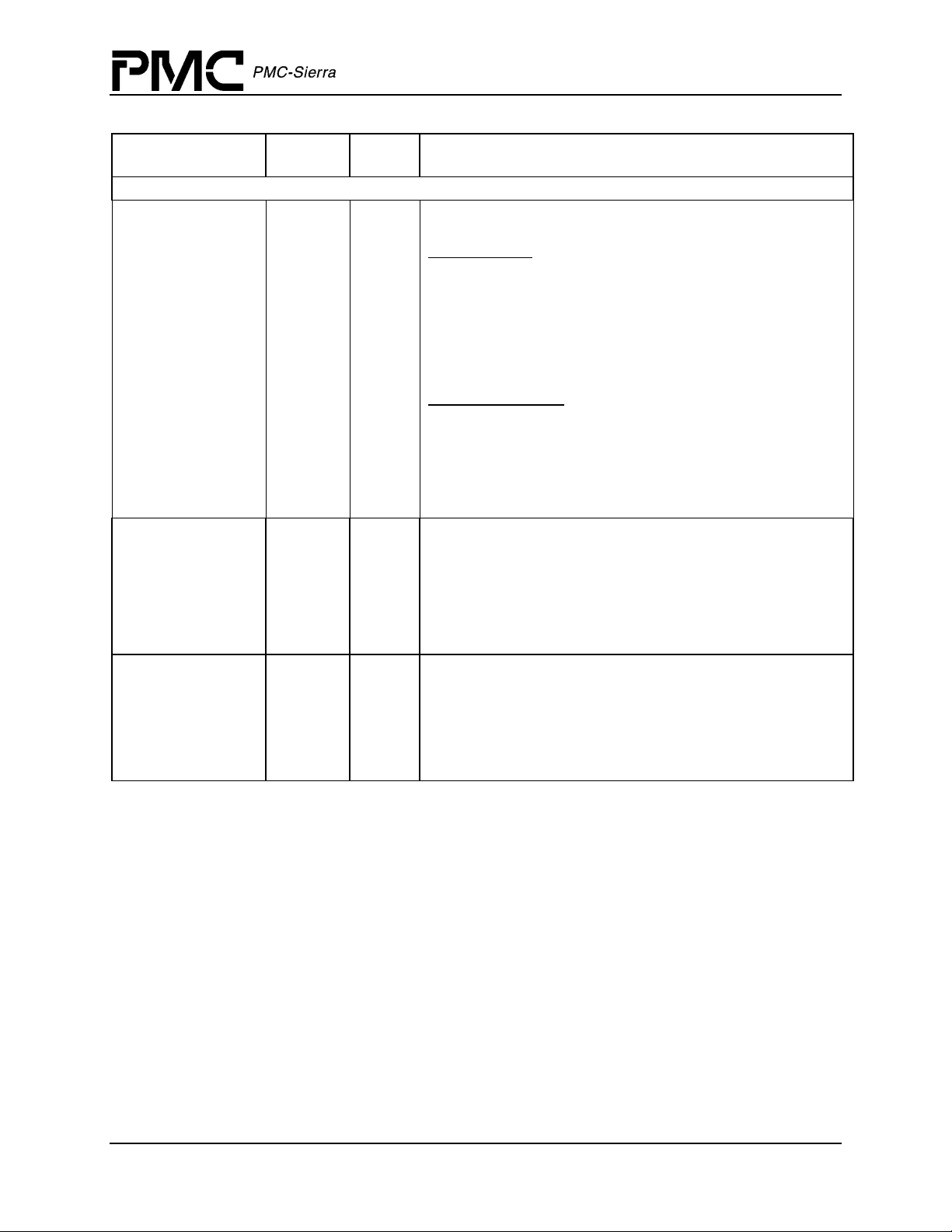

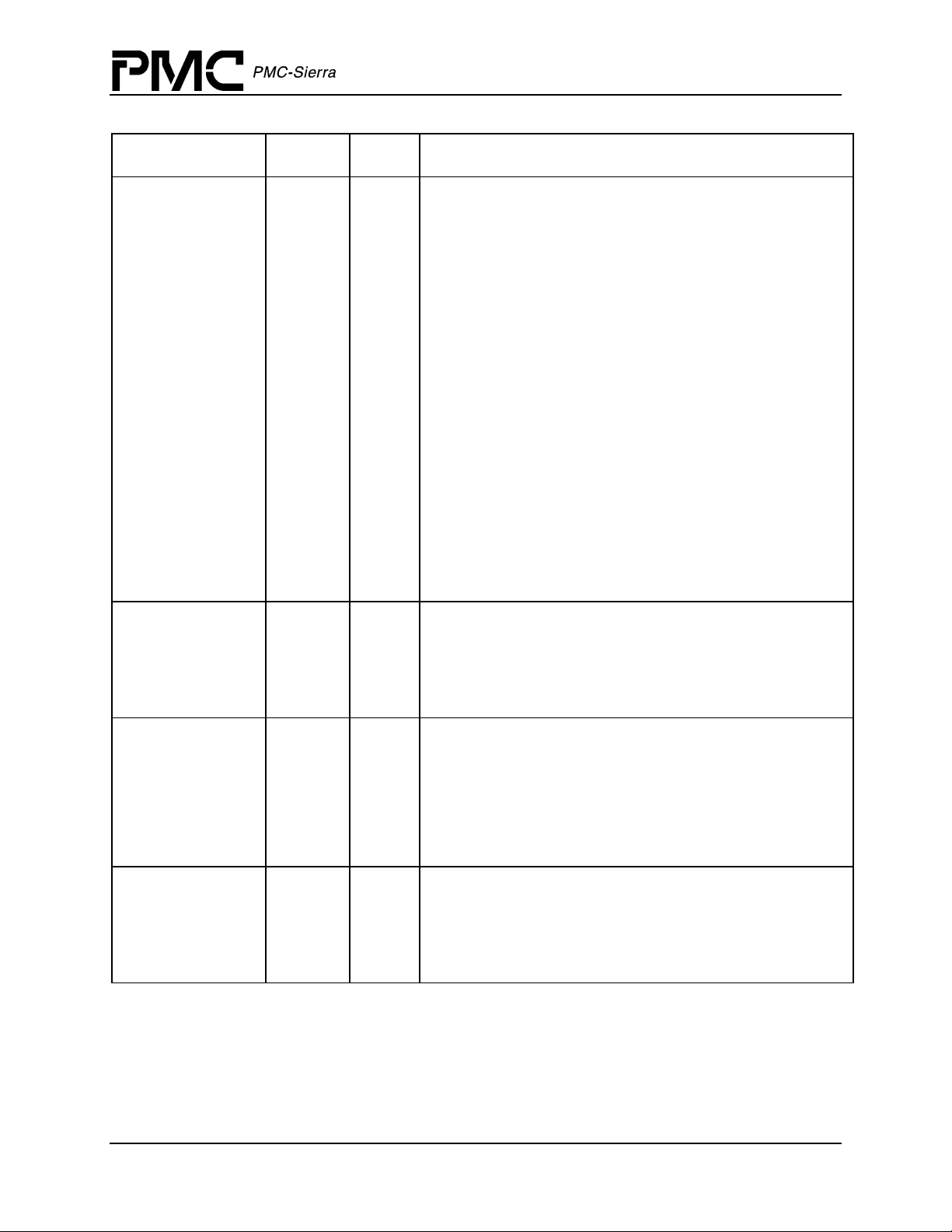

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type

Outgoing SBI Bus (68 Signals)

OC1FP Tristate

Output

ODATA[7]

ODATA[6]

ODATA[5]

ODATA[4]

ODATA[3]

ODATA[2]

ODATA[1]

ODATA[0]

ODP Tristate

Tristate

Output

Output

Pin

No.

C9

C7

B7

D7

A6

D6

B5

D5

A4

C4

Function

Outgoing C1 Frame Pulse (OC1FP). This signal indicates the first

C1 octet on the outgoing SBI or TelecomBus.

In SBI336 mode:

This signal also indicates multiframe alignment which occurs every

4 frames, therefore this signal is pulsed every fourth C1 octet to

produce a 2 KHz multiframe signal.

When using the SBI bus in synchronous mode the OC1FP signal

indicates T1 and E1 signaling multiframe alignment by pulsing on

48 SBI frame boundaries. This must be done if CAS is to be

switched along with the data.

In TelecomBus mode:

This signal may also be pulsed to indicate the J1 byte position and

the byte following J1. The J1 byte position is locked to an offset of

either 0 or 522. The byte following J1 is used to indicate

multiframe alignment and is only pulsed once every 4 frames

marking the frame with the V1s.

OC1FP is updated on the rising edge of SREFCLK.

Outgoing Data (ODATA[7:0]). The Outgoing Data buse,

ODATA[7:0], is a time division multiplexed buses which transport

tributaries by assigning them to fixed octets within the SBI or

TelecomBus structure.

ODATA[7:0] are updated on the rising edge of SREFCLK.

Outgoing Bus Data Parity (ODP). The outgoing data parity signal

carries the even or odd parity for the outgoing bus. In SBI336

modes, the parity calculation for ODP encompasses the

ODATA[7:0], OPL and OV5 signals. In TelecomBus mode, the

parity calculation encompasses the ODATA[7:0] and optionally the

OC1FP and OPL signals.

ODP is updated on the rising edge of SREFCLK.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 21

Document ID: PMC-2010883, Issue 2

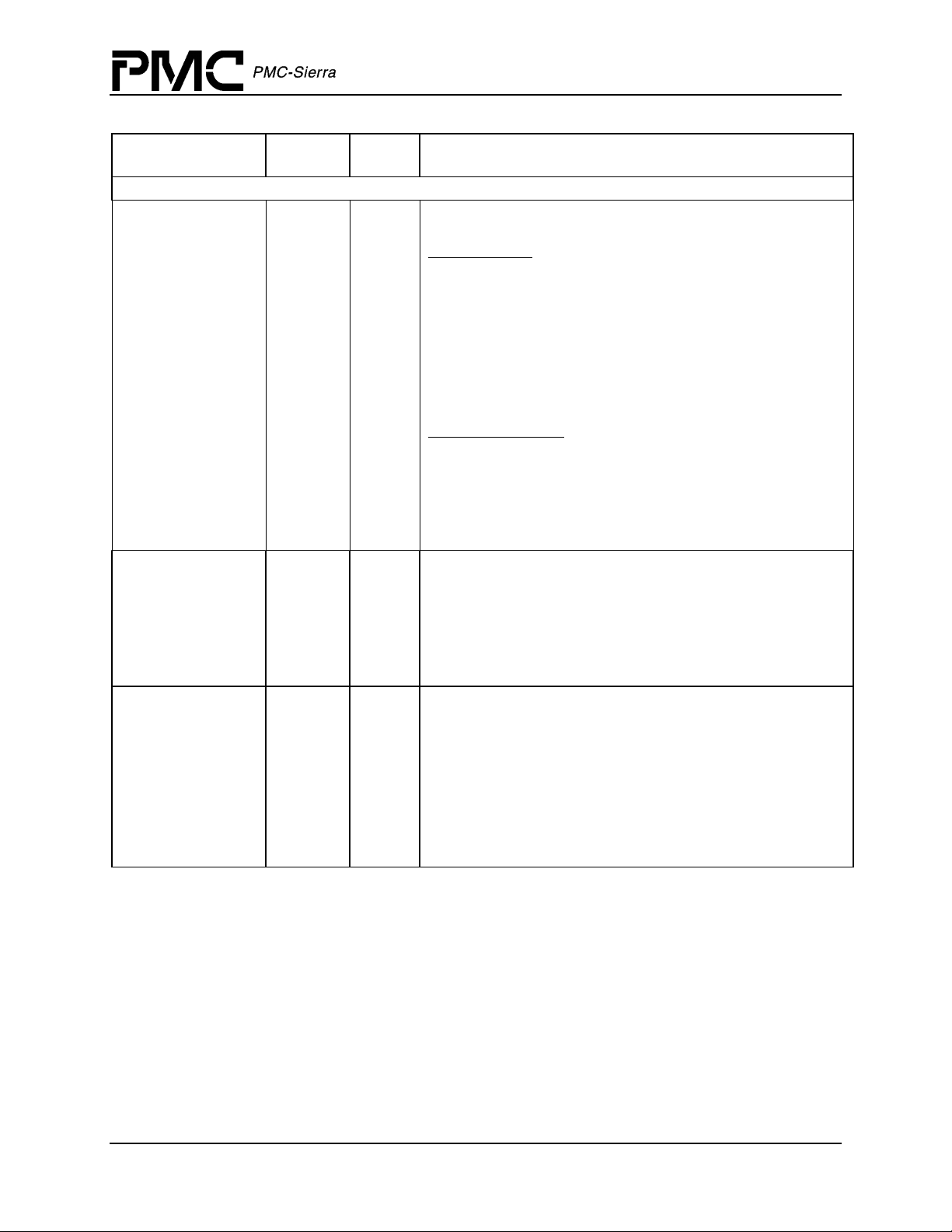

Page 23

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type

OPL Tristate

Output

OV5 Tristate

Output

Pin

No.

D9

B8

Function

Outgoing Bus Payload (OPL). The outgoing payload signal, OPL,

indicates valid tributary data within the SBI bus. In TelecomBus

mode, this signal indicates valid path payload.

In SBI336 mode:

This active high signal is asserted during all octets making up a

tributary which includes all octets shaded grey in the framing

format tables. This signal goes high during the V3 or H3 octet

within a tributary to accommodate negative timing adjustments

between the tributary rate and the fixed SBI bus structure. This

signal goes low during the octet after the V3 or H3 octet within a

tributary to accommodate positive timing adjustments between the

tributary rate and the fixed SBI bus structure. For fractional rate

links this signal indicates that the current octet is carrying valid data

when high.

In locked TVT mode, this signal must be driven in the same

manner as for floating TVTs.

In TelecomBus mode:

This signal distinguishes between transport overhead bytes and

synchronous payload bytes. OPL is set high to mark each payload

byte on ODATA[7:0] and is set low to mark each transport

overhead byte.

OPL is updated on the rising edge of SREFCLK.

Outgoing Bus Payload Indicator (OV5). The active high signal,

OV5, locates the position of the floating payload for each tributary

within the outgoing SBI336 or TelecomBuses.

In SBI336 mode:

This active high signal locates the position of the floating payloads

for each tributary within the SBI336 structure. Timing differences

between the port timing and the bus timing are indicated by

adjustments of this payload indicator relative to the fixed bus

structure. All movements indicated by this signal must be

accompanied by appropriate adjustments in the OPL signal.

In locked TVT mode or fractional rate link mode this signal may be

driven but must be ignored by the receiving device.

In TelecomBus mode:

This signal identifies tributary payload frame boundaries on the

outgoing data bus. OV5 is set high to mark the V5 bytes on the

bus.

OV5 is updated on the rising edge of SREFCLK.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 22

Document ID: PMC-2010883, Issue 2

Page 24

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type

Pin

No.

JUST_REQ Bidir K12

JUST_REQ[1]

(continued)

OTPL Tristate

Output

OTAIS

Tristate

Output

A8

D8

Function

Shared Bus Justification Request (JUST_REQ). The SBI Bus

Justification Request signal, JUST_REQ, is used to speed up, slow

down or maintain the minimal rate of a slave timed SBI device.

When the SBSLITE is configured to be connected to a physical

layer device, JUST_REQ is an input aligned with the incoming bus.

When the SBSLITE is configured to be connected to a link layer

device, JUST_REQ is an output aligned with the outgoing bus.

This active high signal, JUST_REQ, indicates negative timing

adjustments on the SBI bus when asserted high during the V3 or

H3 octet, depending on the tributary type. In response to this the

slave timed SBI device should send an extra byte in the V3 or H3

octet of the next frame along with a valid payload signal indicating

a negative justification.

This signal indicates positive timing adjustments on the

corresponding SBI bus when asserted high during the octet

following the V3 or H3 octet, depending on the tributary type. The

slave timed SBI device should respond to this by not sending an

octet during the V3 or H3 octet of the next frame along with a valid

payload signal indicating a positive justification.

For fractional rate links this signal is asserted high during any

available information byte to indicate to the slave timed SBI device

that the timing master device is able to accept another byte of data.

For every byte that this signal is asserted high the slave device is

expected to send a valid byte of data.

All timing adjustments from the slave timed device in response to

the justification request must still set the payload and payload

indicators appropriately for timing adjustments.

JUST_REQ is not used when configured for TelecomBus mode.

JUST_REQ is asserted or sampled on the rising edge of

SREFCLK.

Outgoing Tributary Payload (OTPL). This signal is used to

indicate tributary payload when configured for TelecomBus and is

held low when configured for an SBI336 bus.

OTPL is set high during valid VC11 and VC12 bytes of the

Outgoing bus. OTPL is set low for all transport overhead bytes,

high order path overhead bytes, fixed stuff column bytes and

tributary transport overhead bytes (V1,V2,V3,V4).

OTPL is updated on the rising edge of SREFCLK.

Outgoing Tributary Alarm Indication Signal (OTAIS). This signal

indicates tributaries in low order path AIS state for the Outgoing

TelecomBus and is held low when configured for an SBI336 bus.

OTAIS is set high when the tributary on the Outgoing bus is in AIS

state and is set low when the tributary is out of AIS state.

OTAIS is updated on the rising edge of SREFCLK.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 23

Document ID: PMC-2010883, Issue 2

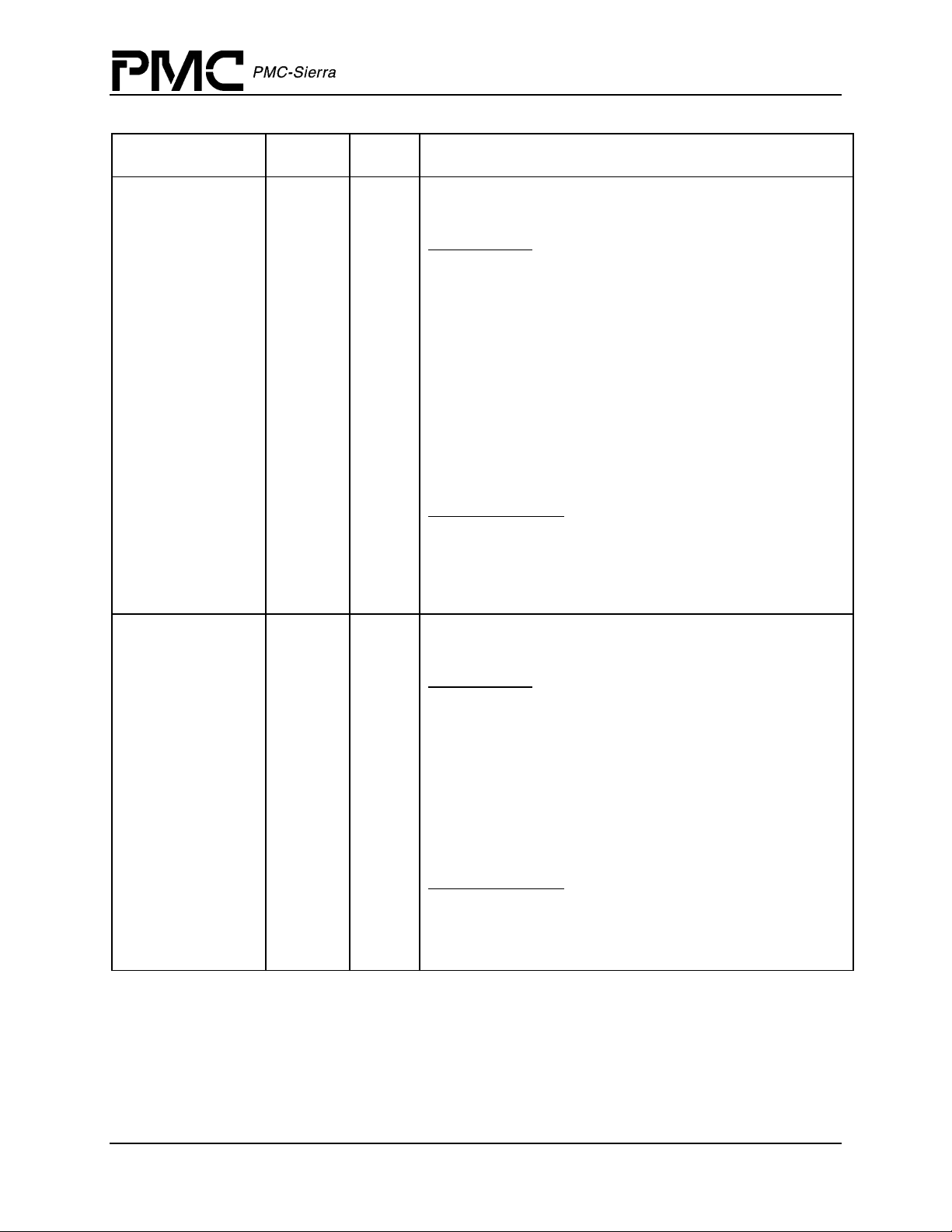

Page 25

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type

Pin

No.

Incoming SBI Bus (56 Signals)

IC1FP Input F12

IDATA[7]

IDATA[6]

IDATA[5]

IDATA[4]

IDATA[3]

IDATA[2]

IDATA[1]

IDATA[0]

IDP Input E14

Input E11

D14

D12

D13

C14

C12

C13

B14

Function

Incoming C1 Frame Pulse (IC1FP). This signal indicates the first

C1 octet on the incoming SBI336 or TelecomBus.

In SBI336 mode:

This signal also indicates multiframe alignment which occurs every

4 frames, therefore this signal is pulsed every fourth C1 octet to

produce a 2 KHz multiframe signal. The frame pulse does not

need to be repeated every 2 KHz as the SBSLITE will flywheel in

its absence.

When using the SBI bus in synchronous mode the IC1FP signal

can be used to indicate T1 and E1 multiframe alignment by pulsing

on 48 SBI frame boundaries. This must be done if CAS is to be

switched along with the data.

In TelecomBus mode:

This signal may also be pulsed to indicate the J1 byte position and

the byte following J1. The J1 byte position must be locked to an

offset of either 0 or 522. The byte following J1 is used to indicate

multiframe alignment and should only pulse once every 4 frames

marking the frame with the V1s.

IC1FP is sampled on the rising edge of SREFCLK.

Incoming Bus Data (IDATA[7:0]). The Incoming data bus,

IDATA[7:0], is a time division multiplexed buses which transports

tributaries by assigning them to fixed octets within the SBI336 or

TelecomBus structure.

Multiple SBI336 devices can drive this bus at uniquely assigned

tributary columns within the SBI/SBI336 bus structure.

IDATA[7:0] is sampled on the rising edge of SREFCLK.

Incoming Bus Data Parity (IDP). The Incoming data parity signal

carries the even or odd parity for the Incoming bus. In SBI336

modes, the parity calculation encompasses the IDATA[7:0], IPL

and IV5 signals. In TelecomBus mode, the parity calculation

encompasses the IDATA[7:0] and optionally the IC1FP and IPL

signals.

Multiple SBI336 devices can drive this signal at uniquely assigned

tributary columns within the SBI336 bus structure. This parity signal

is intended to detect multiple sources in the column assignment.

IDP is sampled on the rising edge of SREFCLK.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 24

Document ID: PMC-2010883, Issue 2

Page 26

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type

Pin

No.

IPL Input F14

IV5 Input F13

Function

Incoming Bus Payload (IPL). The IPL signal indicates valid

tributary data within the SBI336 bus. In TelecomBus mode, this

signal indicates valid path payload.

In SBI336 mode:

This active high signal is asserted during all octets making up a

tributary which includes all octets shaded grey in the framing

format tables. This signal goes high during the V3 or H3 octet

within a tributary to accommodate negative timing adjustments

between the tributary rate and the fixed SBI336 structure. This

signal goes low during the octet following the V3 or H3 octet within

a tributary to accommodate positive timing adjustments between

the tributary rate and the fixed SBI336 structure. For fractional rate

links this signal indicates that the current octet is carrying valid data

when high.

Multiple SBI336 devices can drive this signal at uniquely assigned

tributary columns within the SBI336 structure.

For locked TVTs, this signal must be driven in the same manner as

for floating TVTs.

In TelecomBus mode:

This signal distinguishes between transport overhead bytes and

the synchronous payload bytes. IPL is set high to mark each

payload byte on IDATA[7:0] and is set low to mark each transport

overhead byte..

IPL is sampled on the rising edge of SREFCLK.

Incoming Bus Payload Indicator (IV5). This signal locates the

position of the floating payload for each tributary of the incoming

SBI336 or TelecomBuses.

In SBI336 mode:

This active high signal locates the position of the floating payloads

for each tributary within the SBI336 structure. Timing differences

between the port timing and the bus timing are indicated by

adjustments of this payload indicator relative to the fixed bus

structure. All movements indicated by this signal must be

accompanied by appropriate adjustments in the IPL signal.

Multiple SBI336 devices can drive this signal at uniquely assigned

tributary columns within the SBI336 structure.

For locked TVTs, this signal must either be driven in the same

manner as for floating TVTs or held low.

In TelecomBus mode:

This signal identifies tributary payload frame boundaries on the

incoming data bus. IV5 is set high to mark the V5 bytes on the

bus.

IV5 is sampled on the rising edge of SREFCLK.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 25

Document ID: PMC-2010883, Issue 2

Page 27

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type

Pin

No.

ITPL Input F11

ITAIS Input G11

Transmit Serial Data Interface (5 Signals)

TPWRK

TNWRK

TPPROT

TNPROT

TC1FP Output C3

Analog

LVDS

Output

Analog

LVDS

Output

E2

E1

D1

D2

Function

Incoming Tributary Payload (ITPL). This signal is used to

indicate tributary payload when configured for TelecomBus and is

unused when configured for an SBI336 bus.

ITPL is set high during valid VC11 and VC12 bytes of the Incoming

bus. ITPL is set low for all transport overhead bytes, high order

path overhead bytes, fixed stuff column bytes and tributary

transport overhead bytes (V1,V2,V3,V4).

ITPL is sampled on the rising edge of SREFCLK.

Incoming Tributary Alarm Indication Signal (ITAIS). This signal

indicates tributaries in low order path AIS state for the Incoming

TelecomBus and is unused when configured for an SBI336 bus.

ITAIS is set high when the tributary on the Incoming bus is in AIS

state and is set low when the tributary is out of AIS state.

ITAIS is sampled on the rising edge of SREFCLK.

Transmit Working Serial Data. In SBI336 mode, the differential

transmit working serial data link (TPWRK/TNWRK) carries a

transmit 77.76 MHz SBI336 data stream to a downstream working

sink, in bit serial format, SBI336S.

In TelecomBus mode, TPWRK/TNWRK carries the transmit 77.76

MHz TelecomBus data stream to a downstream working sink, in bit

serial format.

Data on TPWRK/TNWRK is encoded in an 8B/10B format

extended from IEEE Std. 802.3. The 8B/10B character bit ‘a’ is

transmitted first and the bit ‘j’ is transmitted last.

TPWRK/TNWRK are nominally 777.6 Mbit/s data streams.

Transmit Protect Serial Data. In SBI336 mode, the differential

transmit protect serial data link (TPPROT/TNPROT) carries a

transmit 77.76 MHz SBI336 data stream to a downstream protect

sink, in bit serial format, SBI336S.

In TelecomBus mode, TPPROT/TNPROT carries the transmit

77.76 MHz TelecomBus data stream to a downstream protection

sink, in bit serial format.

Data on TPPROT/TNPROT is encoded in an 8B/10B format

extended from IEEE Std. 802.3. The 8B/10B character bit ‘a’ is

transmitted first and the bit ‘j’ is transmitted last.

TPPROT/TNPROT are nominally 777.6 Mbit/s data streams.

Transmit Serial SBI Frame Pulse. The transmit serial SBI frame

pulse signal (TC1FP) provides system timing of the transmit serial

interface.

TC1FP is set high to indicate that the C1 frame boundary 8B/10B

character has been serialized out on the transmit working serial

data link (TPWRK/TNWRK) and the transmit protection serial data

link (TPPROT/ TNPROT). TC1FP is output every 4 frame for SBI

mode without CAS and for TelecomBus mode. TC1FP is output

every 48 frames for SBI mode with CAS.

TC1FP is updated on the rising edge of SYSCLK.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 26

Document ID: PMC-2010883, Issue 2

Page 28

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type

Pin

No.

Microprocessor Interface (30 Signals)

CSB Input M2

RDB Input M1

WRB Input M3

D[15]

D[14]

D[13]

D[12]

D[11]

D[10]

D[9]

D[8]

D[7]

D[6]

D[5]

D[4]

D[3]

D[2]

D[1]

D[0]

A[8]/TRS

A[7]

A[6]

A[5]

A[4]

A[3]

A[2]

A[1]

A[0]

ALE Input L2

I/O L4

N5

N6

P6

M6

L6

N7

M8

N8

L9

P10

M10

N10

L10

P11

M11

Input

N11

P12

M12

N13

N14

M13

M14

L14

L11

Function

Chip Select Bar. The active low chip select signal (CSB) controls

microprocessor access to registers in the SBSLITE device. CSB is

set low during SBSLITE Microprocessor Interface Port register

accesses. CSB is set high to disable microprocessor accesses.

If CSB is not required (i.e. register accesses controlled using RDB

and WRB signals only), CSB should be connected to an inverted

version of the RSTB input.

Read Enable Bar. The active low read enable bar signal (RDB)

controls microprocessor read accesses to registers in the SBSLITE

device. RDB is set low and CSB is also set low during SBSLITE

Microprocessor Interface Port register read accesses. The

SBSLITE drives the D[15:0] bus with the contents of the addressed

register while RDB and CSB are low.

Write Enable Bar. The active low write enable bar signal (WRB)

controls microprocessor write accesses to registers in the SBSLITE

device. WRB is set low and CSB is also set low during SBSLITE

Microprocessor Interface Port register write accesses. The

contents of D[15:0] are clocked into the addressed register on the

rising edge of WRB while CSB is low.

Microprocessor Data Bus. The bi-directional data bus, D[15:0] is

used during SBSLITE Microprocessor Interface Port register reads

and write accesses. D[15] is the most significant bit of the data

words and D[0] is the least significant bit.

Microprocessor Address Bus. The microprocessor address bus

(A[8:0]) selects specific Microprocessor Interface Port registers

during SBSLITE register accesses.

A[8] is also the Test Register Select (TRS) address pin and selects

between normal and test mode register accesses. TRS is set high

during test mode register accesses, and is set low during normal

mode register accesses.

Address Latch Enable. The address latch enable signal (ALE) is

active high and latches the address bus (A[11:0]) when it is set low.

The internal address latches are transparent when ALE is set high.

ALE allows the SBSLITE to interface to a multiplexed address/data

bus. ALE has an integral pull up resistor.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 27

Document ID: PMC-2010883, Issue 2

Page 29

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type

Pin

No.

INTB Open

Drain

Output

General Function (9 Signals)

SYSCLK Input A12

SREFCLK Input B12

ICMP Input B10

G12

Function

Interrupt Request Bar. The active low interrupt enable signal

(INTB) output goes low when an SBSLITE interrupt source is active

and that source is unmasked. INTB returns high when the interrupt

is acknowledged via an appropriate register access. INTB is an

open drain output.

SBI System Clock. The 77 MHz SBI reference clock signal,

SYSCLK, is the master clock for the SBSLITE device. SYSCLK is

a 77.76 MHz clock, with a nominal 50% duty cycle. RC1FP,

OCMP and RWSEL are sampled on the rising edge of SYSCLK.

TC1FP is updated on the rising edge of SYSCLK.

SBI Reference Clock. The SBI reference clock, SREFCLK, is a

reference for the incoming and outgoing SBI bus and TelecomBus

interfaces. SREFCLK is a 77.76 MHz clock with a nominal 50%

duty cycle. IC1FP, IDATA[7:0], IDP, IPL, IV5, ITPL, ITAIS,

JUST_REQ and ICMP are sampled on the rising edge of

SREFCLK. OC1FP, ODATA[7:0], ODP, OPL, OV5, OTPL, OTAIS

and JUST_REQ are updated on the rising edge of SYSCLK.

This signal should be tied to SYSCLK.

Incoming Connection Memory Page. The incoming connection

memory page select signal, ICMP, controls the selection of the

connection memory page in the Incoming Memory Switch Unit,

IMSU. When ICMP is set high, connection memory page 1 is

selected. When ICMP is set low, connection memory page 0 is

selected.

The byte location during which ICMP is sampled is dependant on

the mode of operation.

4-Frame SBI336 mode:

ICMP is sampled at the C1 byte position of the incoming bus on the

first frame of the 4-frame multiframe (marked by IC1FP). Changes

to the connection memory page selection is synchronized to the

frame boundary of the next four frame multiframe.

48-Frame SBI336 mode:

ICMP is sampled at the C1 byte position of the incoming bus on the

first frame of the 48-frame multiframe (marked by IC1FP).

Changes to the connection memory page selection is synchronized

to the frame boundary of the next 48-frame multiframe.

TelecomBus mode:

ICMP is sampled at the C1 byte position of every frame on the

incoming bus (marked by IC1FP). Changes to the connection

memory pate selection are synchronized to the frame boundary of

the next frame.

CMP is sampled on the rising edge of SREFCLK.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 28

Document ID: PMC-2010883, Issue 2

Page 30

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type

Pin

No.

OCMP Input D11

RWSEL Input N3

IUSER2 Input L5

OUSER2 Output K14

RSTB Input P3

Function

Outgoing Connection Memory Page. The outgoing connection

memory page select signal, OCMP, controls the selection of the

connection memory page in the Outgoing Memory Switch Unit,

OMSU. When OCMP is set high, connection memory page 1 is

selected. When OCMP is set low, connection memory page 0 is

selected.

The byte location during which OCMP is sampled is dependant on

the mode of operation.

4-Frame SBI336 mode:

OCMP is sampled at the C1 byte position of the receive bus on the

first frame of the 4-frame multiframe (marked by RC1FP).

Changes to the connection memory page selection is synchronized

to the frame boundary of the next four frame multiframe.

48-Frame SBI336 mode:

OCMP is sampled at the C1 byte position of the receive bus on the

first frame of the 48-frame multiframe (marked by RC1FP).

Changes to the connection memory page selection is synchronized

to the frame boundary of the next 48-frame multiframe.

TelecomBus mode:

OCMP is sampled at the C1 byte position of every frame on the

receive bus (marked by RC1FP). Changes to the connection

memory pate selection are synchronized to the frame boundary of

the next frame.

OCMP is sampled on the rising edge of SYSCLK.

Receive Working Serial Data Select. The receive working serial

data select signal, RWSEL, selects between sourcing outgoing

data, ODATA[7:0], from the receive working serial data link,

RPWRK/RNWRK, or the receive protect serial data link,

RPPROT/RNPROT. When RWSEL is set high, the working serial

bus is selected. When RWSEL is set low, the protect serial bus is

selected. RWSEL is sampled at the C1 byte location as defined by

the receive serial interface frame pulse signal, RC1FP. Changes

to the selection of the working and protect serial streams are

synchronized to the SBI frame boundary of the next frame.

RWSEL is sampled on the rising edge of SYSCLK.

Input In-band Link User Signal. The input in-band link user

signal, IUSER2, provides external control over one of the bits in the

in-band link. The USER[2] bit in the header of the in-band

signaling channel of both the working and protection serial links will

reflect the state of this input.

IUSER2 an asynchronous signal and is internally synchronized to

SYSCLK.

Output In-Band Link User Signal. The output in-band link user

signal, OUSER2, reflects the state of the USER[2] bit in the header

of the in-band signaling channel of either the working or the

protection serial link, whichever is active.

OUSER2 is an asynchronous output.

Reset Enable Bar. The active low reset signal, RSTB, provides an

asynchronous SBSLITE reset. RSTB is a Schmitt triggered input

with an integral pull-up resistor.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 29

Document ID: PMC-2010883, Issue 2

Page 31

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type

Pin

No.

JTAG Interface (5 Signals)

TCK Input H13

TMS Input J11

TDI Input J14

TDO Tristate H12

TRSTB Input J12

Analog Reference Resistors (2 Signals)

RES

RESK Analog

Analog Test Bus (2 Signals)

ATB0 Analog F4

Analog

Input

Input

C2

B2

Function

Test Clock. The JTAG test clock signal, TCK, provides timing for

test operations that are carried out using the IEEE P1149.1 test

access port.

Test Mode Select. The JTAG test mode select signal, TMS,

controls the test operations that are carried out using the IEEE

P1149.1 test access port. TMS is sampled on the rising edge of

TCK. TMS has an integral pull-up resistor.

Test Data Input. The JTAG test data input signal, TDI, carries test

data into the SBSLITE via the IEEE P1149.1 test access port. TDI

is sampled on the rising edge of TCK. TDI has an integral pull-up

resistor.

Test Data Output. The JTAG test data output signal, TDO, carries

test data out of the SBSLITE via the IEEE P1149.1 test access

port. TDO is updated on the falling edge of TCK. TDO is a tri-state

output which is inactive except when scanning of data is in

progress.

Test Reset Bar. The active low JTAG test reset signal, TRSTB,

provides an asynchronous SBSLITE test access port reset via the

IEEE P1149.1 test access port. TRSTB is a Schmitt triggered input

with an integral pull-up resistor.

Note that when TRSTB is not being used, it must be connected to

the RSTB input.

Reference Resistor Connection (RES). An off-chip 3.16kΩ ±1%

resistor is connected between this positive resistor reference pin

and a Kelvin ground pin, RESK. An on-chip negative feedback path

will force the 0.8V VREF Voltage onto RES, therefore forcing

252uA of current to flow through the resistor.

Reference Resistor Connection (RESK). An off-chip 3.16kΩ ±1%

resistor is connected between the positive resistor reference pin,

RESK, and this Kelvin ground pin. An on-chip negative feedback

path will force the 0.8V VREF Voltage onto RESK, therefore forcing

252uA of current to flow through the resistor.

Analog test pin (ATB0). This pin is used for PMC-Sierra validation

and testing. This pin must be grounded.

ATB1 Analog F3

Analog High Voltage Power (5 Signals)

CSU_AVDH Power H1

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 30

Document ID: PMC-2010883, Issue 2

Analog test pin (ATB1). This pin is used for PMC-Sierra validation

and testing. This pin must be grounded.

CSU Analog Power (CSU_AVDH). This pin should be connected

to a well-decoupled +3.3 V DC supply.

Page 32

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type

Pin

No.

AVDH[2]

AVDH[1]

AVDH[0]

AVDQ Power H3

Analog Low Voltage Power (4 Signals)

AVDL[3]

AVDL[2]

AVDL[1]

AVDL[0]

Digital Core Power (8 Signals)

DVDDI[7]

DVDDI[6]

DVDDI[5]

DVDDI[4]

DVDDI[3]

DVDDI[2]

DVDDI[1]

DVDDI[0]

Digital I/O Power (14 Signals)

DVDDO[13]

DVDDO[12]

DVDDO[11]

DVDDO[10]

DVDDO[9]

DVDDO[8]

DVDDO[7]

DVDDO[6]

DVDDO[5]

DVDDO[4]

DVDDO[3]

DVDDO[2]

DVDDO[1]

DVDDO[0]

Digital I/O Quiet Power (3 Signals)

DVDDQ[2:0] Power P8

Power C1

D4

E3

Power

Power K2

Power N1

G4

H4

J3

J4

L1

P5

P9

L13

G13

A11

A5

N2

M4

P7

N9

P13

H14

E13

A13

A9

C8

C6

A3

A2

J13

C10

Function

Analog Power (AVDH[2:0]). These pins should be connected to a

well-decoupled +3.3 V DC supply.

Analog Quiet Power (AVDQ). This pin should be connected to a

well decoupled +3.3 V DC supply.

Analog Power (AVDL[3:0]). These pins should be connected to a

well-decoupled +1.8 V DC supply. Each AVDL pin requires

individual filtering.

Digital Core Power (DVDDI[7:0]). The digital core power pins

should be connected to a well-decoupled +1.8 V DC supply.

Digital I/O Power (DVDDO[13:0]). The digital I/O power pins

should be connected to a well-decoupled +3.3 V DC supply.

Digital I/O Quite Power (DVDDQ[2:0]). The digital I/O quite power

pins should be connected to a well-decoupled +3.3 V DC supply.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 31

Document ID: PMC-2010883, Issue 2

Page 33

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

Pin Name Type

Pin

Function

No.

Ground (35 Signals)

VSS[34]

VSS[33]

VSS[32]

VSS[31]

VSS[30]

VSS[29]

VSS[28]

VSS[27]

VSS[26]

VSS[25]

VSS[24]

VSS[23]

VSS[22]

VSS[21]

VSS[20]

VSS[19]

VSS[18]

VSS[17]

VSS[16]

VSS[15]

VSS[14]

VSS[13]

VSS[12]

VSS[11]

VSS[10]

VSS[9]

VSS[8]

VSS[7]

VSS[6]

VSS[5]

VSS[4]

VSS[3]

VSS[2]

VSS[1]

VSS[0]

GND Thermal

NC No Connect K13 The No Connect pin must be left floating.

Notes on Pin Description

1. All SBSLITE inputs and bi-directionals except the LVDS links present minimum capacitive loading and

operate at TTL (Vdd reference) logic levels.

2. Inputs RSTB, ALE, TMS, TDI and TRSTB have internal pull-up resistors.

3. All SBSLITE outputs have 8 mA drive capability.

4. The DVDDI and AVDL power pins are not internally connected to each other. Failure to connect these

pins externally may cause malfunction or damage to the SBSLITE.

5. The AVDH, AVDQ, CSU_AVDH, DVDDO and DVDDQ power pins are not internally connected to each

other. Failure to connect these pins externally may cause malfunction or damage to the SBSLITE.

6. The DVDDI, DVDDO, DVDDQ, AVDH, AVDQ, CSU_AVDH and AVDL power pins all share a common

ground.

Ground B1

D3

E4

G3

H2

J1

J2

K1

K3

K4

L3

P2

P4

M5

L7

M7

L8

M9

N12

L12

K11

H11

G14

E12

B13

B11

C11

A10

D10

B9

A7

B6

C5

B4

B3

G7

Vias

G8

H7

H8

Ground (VSS[34:0]). The ground pins, VSS[34:0], should be

connected to GND.

The Thermal Vias (GND) pins are used to improve thermal

conductance of the device package. They should be connected to

the PCB ground plane. The GND pins are not electrically

connected to the other ground pins of the package.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 32

Document ID: PMC-2010883, Issue 2

Page 34

SBSLITE™ Telecom Standard Product Data Sheet

Preliminary

7. To prevent damage to the SBSLITE and to ensure proper operation, power must be applied

simultaneously to all 3.3 V power pins followed by power to all the 1.8 V power pins followed by input

pins driven by signals.

8. To prevent damage to the SBSLITE, power must first be removed from input pins followed by the

removal of power from all the 1.8 V power supply pins followed by the simultaneous removal of power

from all the 3.3 V power pins.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use 33

Document ID: PMC-2010883, Issue 2

Page 35

10 Functional Description

10.1 SBI Bus Data Formats