Page 1

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

PM8313

D3MX

M13 MULTIPLEXER

ISSUE 5: JULY 1998

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

Page 2

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

Page 3

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

CONTENTS

1 FEATURES ........................................................................................................................1

2 APPLICATIONS .................................................................................................................6

3 STANDARD REFERENCES..............................................................................................7

4 APPLICATION EXAMPLE..................................................................................................9

5 BLOCK DIAGRAM...........................................................................................................10

6 PIN DIAGRAM.................................................................................................................13

7 PIN DESCRIPTION .........................................................................................................14

8 FUNCTIONAL DESCRIPTION ........................................................................................34

8.1 DS3 FRAMER.....................................................................................................34

8.2 DS3 PERFORMANCE MONITOR......................................................................36

8.3 PATH MAINTENANCE DATA LINK RECEIVER ..................................................37

8.4 ALARM AND CONTROL CHANNEL BIT ORIENTED CODE DETECTOR........37

8.5 DS3 TRANSMITTER...........................................................................................38

8.6 PATH MAINTENANCE DATA LINK TRANSMITTER ...........................................38

8.7 ALARM AND CONTROL CHANNEL BIT ORIENTED CODE TRANSMITTER..39

8.8 M23 MULTIPLEXER ...........................................................................................39

8.9 DS2 FRAMER.....................................................................................................40

8.10 M12 MULTIPLEXER ...........................................................................................42

8.11 LOOPBACK MODES..........................................................................................43

8.12 MICROPROCESSOR INTERFACE....................................................................46

9 REGISTER MEMORY MAP.............................................................................................47

10 NORMAL MODE REGISTER DESCRIPTION.................................................................51

10.1 DS3 PMON REGISTERS ...................................................................................75

i

Page 4

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

11 TEST FEATURES DESCRIPTION ................................................................................132

11.1 TEST MODE REGISTER MEMORY MAP........................................................132

11.2 TEST MODE 0..................................................................................................137

12 OPERATION ..................................................................................................................141

12.1 USING THE INTERNAL DATA LINK TRANSMITTER.......................................141

12.2 USING THE INTERNAL DATA LINK RECEIVER..............................................142

12.2.1 KEY USED ON SUBSEQUENT DIAGRAMS: .....................................145

13 FUNCTIONAL TIMING...................................................................................................150

14 ABSOLUTE MAXIMUM RATINGS.................................................................................158

15 D.C. CHARACTERISTICS..............................................................................................159

16 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS...............................161

17 D3MX TIMING CHARACTERISTICS.............................................................................166

18 ORDERING AND THERMAL INFORMATION...............................................................179

19 MECHANICAL INFORMATION......................................................................................180

ii

Page 5

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

LIST OF REGISTERS

REGISTER 00H: MASTER RESET / CLOCK STATUS.................................................................52

REGISTER 01H: REVISION/GLOBAL PMON UPDATE...............................................................54

REGISTER 02H: MASTER BYPASS CONFIGURATION..............................................................55

REGISTER 03H: MASTER HDLC CONFIGURATION..................................................................57

REGISTER 04H: MASTER LOOPBACK CONFIGURATION........................................................59

REGISTER 05H: MASTER INTERFACE CONFIGURATION .......................................................61

REGISTER 06H: MASTER ALARM ENABLE/NETWORK REQUIREMENT BIT.........................63

REGISTER 07H: MASTER TEST .................................................................................................66

REGISTER 08H: MASTER INTERRUPT SOURCE #1 ................................................................68

REGISTER 09H: MASTER INTERRUPT SOURCE #2 ................................................................70

REGISTER 0AH: MASTER INTERRUPT SOURCE #3................................................................71

REGISTER 0CH:DS3 TRAN CONFIGURATION..........................................................................72

REGISTER 0DH:DS3 TRAN DIAGNOSTIC .................................................................................74

REGISTER 11H: DS3 PMON INTERRUPT ENABLE/STATUS.....................................................76

REGISTER 14H: DS3 LCV COUNT LSB......................................................................................77

REGISTER 15H: DS3 LCV COUNT MSB.....................................................................................77

REGISTER 16H: DS3 FERR COUNT LSB...................................................................................78

REGISTER 17H: DS3 FERR COUNT MSB..................................................................................78

REGISTER 18H: DS3 EXZS COUNT LSB...................................................................................79

REGISTER 19H: DS3 EXZS COUNT MSB..................................................................................79

REGISTER 1AH: DS3 PERR COUNT LSB..................................................................................80

REGISTER 1BH: DS3 PERR COUNT MSB.................................................................................80

REGISTER 1CH: DS3 CPERR COUNT LSB...............................................................................81

iii

Page 6

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

REGISTER 1DH: DS3 CPERR COUNT MSB..............................................................................81

REGISTER 1EH: DS3 FEBE COUNT LSB...................................................................................82

REGISTER 1FH: DS3 FEBE COUNT MSB..................................................................................82

REGISTER 20H: XFDL TSB CONFIGURATION ..........................................................................83

REGISTER 21H: XFDL TSB INTERRUPT STATUS......................................................................85

REGISTER 22H: XFDL TSB TRANSMIT DATA.............................................................................86

REGISTER 24H: RFDL TSB CONFIGURATION ..........................................................................87

REGISTER 25H: RFDL TSB INTERRUPT CONTROL/STATUS...................................................88

REGISTER 26H: RFDL TSB STATUS...........................................................................................90

REGISTER 27H: RFDL TSB RECEIVE DATA...............................................................................92

REGISTER 28H: MX23 CONFIGURATION..................................................................................93

REGISTER 29H: MX23 DEMUX AIS INSERT REGISTER...........................................................95

REGISTER 2AH: MX23 MUX AIS INSERT REGISTER ...............................................................96

REGISTER 2BH: MX23 LOOPBACK ACTIVATE REGISTER.......................................................97

REGISTER 2CH: MX23 LOOPBACK REQUEST INSERT REGISTER........................................98

REGISTER 2DH: MX23 LOOPBACK REQUEST DETECT REGISTER ......................................99

REGISTER 2EH: MX23 LOOPBACK REQUEST INTERRUPT REGISTER ..............................100

REGISTER 31H: FEAC XBOC TSB CODE ................................................................................101

REGISTER 32H: RBOC CONFIGURATION/INTERRUPT ENABLE ..........................................102

REGISTER 33H: RBOC INTERRUPT STATUS ..........................................................................103

REGISTER 34H: DS3 FRMR CONFIGURATION.......................................................................103

REGISTER 35H: DS3 FRMR INTERRUPT ENABLE (ACE=0) ..................................................106

REGISTER 35H: DS3 FRMR ADDITIONAL CONFIGURATION REGISTER (ACE=1)..............108

REGISTER 36H: DS3 FRMR INTERRUPT STATUS ..................................................................111

iv

Page 7

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

REGISTER 37H: DS3 FRMR STATUS........................................................................................113

REGISTERS 40H, 50H, 60H, 70H, 80H, 90H AND A0H: DS2 FRMR CONFIGURATION.........115

REGISTERS 41H, 51H, 61H, 71H, 81H, 91H AND A1H: DS2 FRMR INTERRUPT ENABLE ...117

REGISTERS 42H, 52H, 62H, 72H, 82H, 92H AND A2H: DS2 FRMR INTERRUPT STATUS ....118

REGISTERS 43H, 53H, 63H, 73H, 83H, 93H AND A3H: DS2 FRMR STATUS..........................119

REGISTERS 44H, 54H, 64H, 74H, 84H, 94H AND A4H: DS2 FRMR MONITOR INTERRUPT

ENABLE/STATUS...........................................................................................................121

REGISTERS 45H, 55H, 65H, 75H, 85H, 95H AND A5H: DS2 FRMR FERR COUNT...............123

REGISTERS 46H, 56H, 66H, 76H, 86H, 96H AND A6H: DS2 FRMR PERR COUNT (LSB).....124

REGISTERS 47H, 57H, 67H, 77H, 87H, 97H AND A7H: DS2 FRMR PERR COUNT (MSB)....124

REGISTERS 48H, 58H, 68H, 78H, 88H, 98H AND A8H: MX12 CONFIGURATION AND

CONTROL .....................................................................................................................125

REGISTERS 49H, 59H, 69H, 79H, 89H, 99H AND A9H: MX12 LOOPBACK CODE SELECT

REGISTER.....................................................................................................................127

REGISTERS 4AH, 5AH, 6AH, 7AH, 8AH, 9AH AND AAH: MX12 AIS INSERT REGISTER......129

REGISTERS 4BH, 5BH, 6BH, 7BH, 8BH, 9BH AND ABH: MX12 LOOPBACK ACTIVATE

REGISTER.....................................................................................................................130

REGISTERS 4CH, 5CH, 6CH, 7CH, 8CH, 9CH AND ACH: MX12 LOOPBACK INTERRUPT

REGISTER.....................................................................................................................131

v

Page 8

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

LIST OF FIGURES

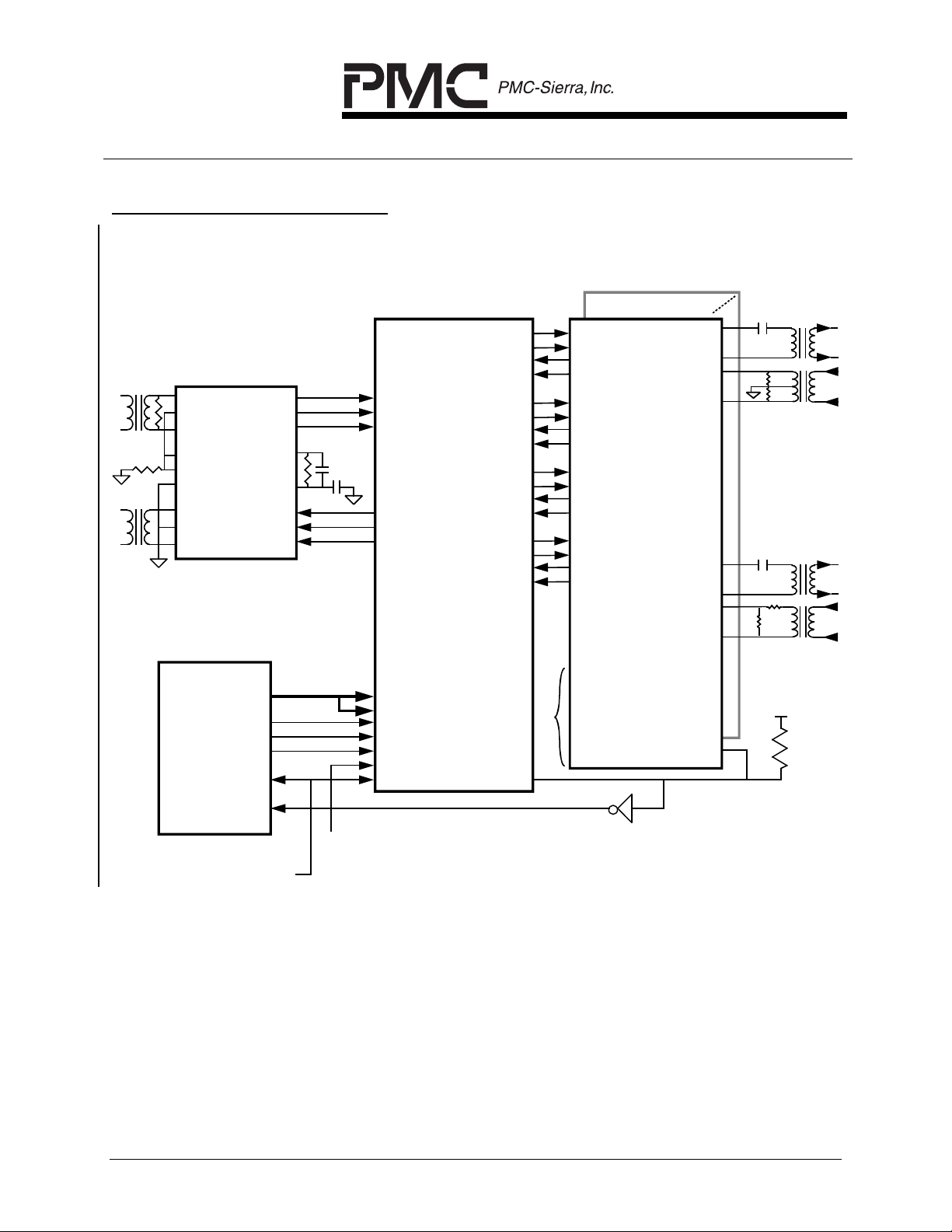

FIGURE 1 - M1-3 MULTIPLEXER/DEMULTIPLEXER...............................................................9

FIGURE 2 - DS3 DIAGNOSTIC LOOPBACK..........................................................................44

FIGURE 3 - DS3 LINE LOOPBACK ........................................................................................45

FIGURE 4 - DS2/G.747 DEMULTIPLEX LOOPBACK.............................................................45

FIGURE 5 - DS1/E1 DEMULTIPLEX LOOPBACK..................................................................46

FIGURE 6 - TYPICAL DATA FRAME.....................................................................................145

FIGURE 7 - RFDL NORMAL DATA AND ABORT SEQUENCE.............................................146

FIGURE 8 - RFDL FIFO OVERRUN......................................................................................147

FIGURE 9 - XFDL NORMAL DATA SEQUENCE...................................................................148

FIGURE 10 - XFDL UNDERRUN SEQUENCE.......................................................................149

FIGURE 11 - RECEIVE DS3 HIGH SPEED OUTPUT TIMING...............................................150

FIGURE 12 - RECEIVE DS3 LOW SPEED TIMING................................................................151

FIGURE 13 - TRANSMIT DS3 TIMING ...................................................................................152

FIGURE 14 - TDLINT TIMING - NORMAL DATA TRANSMISSION.........................................153

FIGURE 15 - TDLEOMI TIMING - WITH REMOVAL OF TDLEOMI BEFORE COMPLETION OF

FCS TRANSMISSION....................................................................................................154

FIGURE 16 - TDLEOMI TIMING - WITH REMOVAL OF TDLEOMI AFTER COMPLETION OF

FCS TRANSMISSION....................................................................................................155

FIGURE 17 - INPUT DS3 OVERHEAD SERIAL STREAM.....................................................156

FIGURE 18 - OUTPUT DS3 OVERHEAD SERIAL STREAM.................................................157

FIGURE 19 - MICROPROCESSOR READ ACCESS TIMING................................................162

FIGURE 20 - MICROPROCESSOR WRITE ACCESS TIMING...............................................164

FIGURE 21 - RECEIVE DS3 INPUT TIMING..........................................................................166

FIGURE 22 - TRANSMIT DS3 INPUT TIMING........................................................................167

vi

Page 9

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

FIGURE 23 - TRANSMIT OVERHEAD INPUT TIMING...........................................................168

FIGURE 24 - TRANSMIT TRIBUT AR Y INPUT TIMING...........................................................169

FIGURE 25 - TRANSMIT DATA LINK INPUT TIMING.............................................................170

FIGURE 26 - TRANSMIT DATA LINK EOM INPUT TIMING....................................................171

FIGURE 27 - TRANSMIT DS3 OUTPUT TIMING....................................................................172

FIGURE 28 - RECEIVE DS3 OUTPUT TIMING......................................................................174

FIGURE 29 - RECEIVE OVERHEAD OUTPUT TIMING.........................................................176

FIGURE 30 - TRANSMIT OVERHEAD OUTPUT TIMING.......................................................177

FIGURE 31 - RECEIVE TRIBUTARY OUTPUT TIMING .........................................................177

FIGURE 32 - RECEIVE DATA LINK OUTPUT TIMING............................................................178

FIGURE 33 - 208 PIN COPPER LEADFRAME PLASTIC QUAD FLAT PACK (R SUFFIX):...180

vii

Page 10

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

LIST OF TABLES

TABLE 1 - TEST MODE ADDRESS LOCATIONS – READ FROM INPUTS.......................138

TABLE 2 - TEST MODE ADDRESS LOCATIONS – WRITE TO OUTPUTS......................138

TABLE 3 - TRANSMITT OVERHEAD FORMAT..................................................................156

TABLE 4 - RECEIVE OVERHEAD FORMAT.......................................................................157

TABLE 5 - D3MX ABSOLUTE MAXIMUM RATINGS..........................................................158

TABLE 6 - D3MX D.C. CHARACTERISTICS.......................................................................159

TABLE 7 - MICROPROCESSOR READ ACCESS (FIGURE 19) .......................................161

TABLE 8 - MICROPROCESSOR WRITE ACCESS (FIGURE 20)......................................163

TABLE 9 - D3MX RECEIVE DS3 INPUT (FIGURE 21) ......................................................166

TABLE 10 - D3MX TRANSMIT DS3 INPUT (FIGURE 22)....................................................167

TABLE 11 - D3MX TRANSMIT OVERHEAD INPUT (FIGURE 23).......................................168

TABLE 12 - D3MX TRANSMIT TRIBUTARY INPUT (FIGURE 24) .......................................169

TABLE 13 - D3MX TRANSMIT DATA LINK INPUT (FIGURE 25)..........................................170

TABLE 14 - D3MX TRANSMIT DATA LINK EOM INPUT (FIGURE 26) ................................171

TABLE 15 - D3MX TRANSMIT DS3 OUTPUT (FIGURE 27)................................................172

TABLE 16 - D3MX RECEIVE DS3 OUTPUT (FIGURE 28) ..................................................173

TABLE 17 - D3MX RECEIVE OVERHEAD OUTPUT (FIGURE 29).....................................175

TABLE 18 - D3MX TRANSMIT OVERHEAD OUTPUT (FIGURE 30)...................................176

TABLE 19 - D3MX RECEIVE TRIBUTARY OUTPUT (FIGURE 31)......................................177

TABLE 20 - D3MX RECEIVE DATA LINK OUTPUT (FIGURE 32)........................................177

TABLE 21 - D3MX ORDERING INFORMATION...................................................................179

TABLE 22 - D3MX THERMAL INFORMATION .....................................................................179

viii

Page 11

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

1

FEATURES

Integrates a full featured M13 multiplexer and DS-3 framer in a single

•

monolithic device.

Supports the M23 or C-bit parity DS3 formats.

•

Supports the M12 or G.747 formats allowing DS1 or E1 signals to be

•

multiplexed into a DS3 signal.

• Allows the M12 stages to be bypassed allowing direct input of DS2 signals

•

into the M23 multiplexer stage.

Provides a generic microprocessor interface for configuration, control, and

•

status monitoring.

Low power CMOS technology.

•

Packaged in a 208 pin Plastic Quad Flat Pack (PQFP) package.

•

Each DS3 framer/performance monitor section:

Frames to a DS3 signal with a maximum average reframe time of less than

•

1.5 ms (as required by TR-TSY-000009 Section 4.1.2 and TR-TSY-000191

Section 5.2).

Decodes a B3ZS-encoded signal and indicates line code violations. The

•

definition of line code violation is software selectable.

Detects and accumulates occurrences of excessive zeros and loss of signal.

•

Provides indication of M-frame and M-subframe boundaries, and overhead bit

•

positions in the DS3 stream.

Detects the DS3 alarm indication signal (AIS) and idle signal. Detection

•

algorithms operate correctly in the presence of a 10-3 bit error rate.

Extracts valid X-bits and indicates far end receive failure. Accumulates up to

•

65,535 line code violation (LCV) events per second, 16,383 P-bit parity error

events per second, 1023 F-bit or M-bit (framing bit) events per second,

65,535 excessive zero (EXZ) events per second, and when enabled for C-bit

1

Page 12

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

parity mode operation, up to 16,383 C-bit parity error events per second, and

16,383 far end block error (FEBE) events per second.

• Detects and validates bit-oriented codes in the C-bit parity far end alarm and

control channel.

• Terminates the C-bit parity path maintenance data link with an integral HDLC

receiver having a 4-byte deep FIFO buffer. Supports polled, interrupt-driven

or DMA access.

• Optionally extracts the C-bit parity mode path maintenance data link signal

and serializes it at 28.2 kbit/s.

• Extracts the X, P, M, F, C and stuff opportunity bits and serializes them at

526 kbit/s on a time division multiplex signal.

Each DS3 transmit framer section:

• Provides the overhead bit insertion for a DS3 stream.

• Provides a bit serial clock and data interface, and allows the M-frame

boundary and/or the overhead bit positions to be located via an external

interface

• Provides optional insertion of the X, P, M, F, C, and stuff opportunity bits via a

526 kbit/s serial interface.

• Provides B3ZS encoding.

• Inserts far end receive failure (FERF), the DS3 alarm indication signal (AIS)

and the idle signal when enabled by external inputs, or internal register bits.

• Provides diagnostic features to allow the generation of line code violation

error events, parity error events, framing bit error events, and when enabled

for the C-bit parity application, C-bit parity error events, and far end block

error events.

• Inserts bit-oriented codes in the C-bit parity far end alarm and control

channel.

• Optionally inserts the C-bit parity path maintenance data link with an integral

HDLC transmitter. Supports polled, interrupt-driven, or DMA access.

2

Page 13

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Optionally inserts the C-bit parity mode path maintenance data link signal

•

from a 28.2 kbit/s serial input.

Each M23 multiplexer section:

Multiplexes 7 DS2 bit streams into a single M23 format DS3 bit stream.

•

Performs required bit stuffing including generation of C-bits.

•

Includes required FIFO buffers for rate adaptation in the multiplex path.

•

Allows insertion of per DS2 payload loopback requests encoded in the

•

transmitted C-bits to be activated or cleared under microprocessor control.

Provides generated DS2 clock for use in integrated M13 or C-bit parity

•

multiplex applications.

Demultiplexes a single M23 format DS3 bit stream into 7 DS2 bit streams.

•

Performs required bit destuffing including interpretation of C-bits.

•

Detects per DS2 payload loopback requests encoded in the received C-bits.

•

Allows per DS2 payload loopback to be activated or cleared under

•

microprocessor control.

Allows per DS2 alarm indication signal (AIS) to be activated or cleared for

•

either direction under microprocessor control.

Allows DS2 alarm indication signal (AIS) to be activated or cleared in the

•

demultiplex direction automatically upon loss of DS3 frame alignment or

signal.

Supports C-bit parity DS3 format.

•

Each DS2 framer and M12 multiplexer section:

Supports two asynchronous multiplexing standards: the combination of four

•

DS1 bit streams into a single M12 format DS2 bit stream and the combination

of three 2048 kbit/s tributaries into a 6312 kbit/s high speed signal according

to CCITT Recommendation G.747.

Frames to either a DS2 or G.747 signal.

•

3

Page 14

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Maximum average reframe time of less than 7 ms (as required by TR-TSY-

•

000009 Section 4.1.2 and TR-TSY-000191 Section 5.2) for DS2 format and 1

ms for G.747 format.

Allows forcing of reframe via an internal register.

•

Detects the alarm indication signal in 9.9 ms in the presence of a 10-3 bit

•

error rate.

Extracts the DS2 X-bit or G.747 remote alarm bit and indicates far end

•

receive failure.

Accumulates error events over consecutive accumulation intervals as defined

•

by writes to internal registers.

Accumulates up to 255 DS2 M-bit or F-bit error events per second.

•

Accumulates up to 255 G.747 framing bit or word (selectable) error events

per second.

Accumulates up to 8191 G.747 parity error events per second.

•

Optionally generates interrupts when various events or status changes occur.

•

Performs required bit stuffing including generation of C-bits.

•

Performs required bit destuffing including interpretation of C-bits.

•

Includes required FIFO buffers for rate adaptation in the multiplex path.

•

Allows per tributary alarm indication signal (AIS) to be activated or cleared for

•

either direction under microprocessor control.

DS2 Functionality

Multiplexes four DS1 bit streams into a single M12 format DS2 bit stream.

•

Performs required inversion of second and fourth multiplexed DS1 streams as

•

required by ANSI T1.107 Section 7.2.

Allows insertion of per DS1 payload loopback requests encoded in the

•

transmitted C-bits to be activated or cleared under microprocessor control.

Inserts X, F, and M bits into transmitted DS2 bit stream.

•

4

Page 15

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Allows transmission of far end receive failure (FERF) and alarm indication

•

signal (AIS) under microprocessor control.

Allows inversion of inserted F or M bits for diagnostic purposes.

•

Demultiplexes a single M12 format DS2 bit stream into four DS1 bit streams.

•

Detects per DS1 payload loopback requests encoded in the received C-bits.

•

Allows per DS1 payload loopback to be activated or cleared under

•

microprocessor control.

Performs required inversion of second and fourth demultiplexed DS1 streams.

•

E1 Functionality

Multiplexes three 2048 kbit/s bit streams into a single G.747 format 6312

•

kbit/s bit stream.

Inserts frame alignment signal and parity bit into transmitted 6312 kbit/s bit

•

stream.

Allows transmission of remote alarm indication (RAI) and reserved bit (Set II,

•

bit 3) under microprocessor control.

Allows inversion of inserted frame alignment signal for diagnostic purposes.

•

Allows inversion of the C-bits in anticipation of remote loopback

•

recommendations.

Demultiplexes a single G.747 format 6312 kbit/s bit stream into three 2048

•

kbit/s bit streams.

5

Page 16

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

2

APPLICATIONS

M23 Based M13 Multiplexer

•

C-Bit Parity Based M13 Multiplexer

•

M23 Multiplexer

•

M13 Multiplexer Supporting G.747 Tributary Format

•

6

Page 17

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

3

STANDARD REFERENCES

1. American National Standard for Telecommunications, ANSI T1.103-1987 "Digital Hierarchy - Synchronous DS3 Format Specifications".

2. American National Standard for Telecommunications, ANSI T1.107-1988 "Digital Hierarchy - Formats Specifications".

3. American National Standard for Telecommunications, ANSI T1.404-1989 "Customer Installation-to-Network - DS3 Metallic Interface Specification".

4. American National Standard for Telecommunications, ANSI T1.107a-1990 "Digital Hierarchy - Supplement to Formats Specifications (DS3 Format

Applications)".

5. American National Standard for Telecommunications, T1M1.3/91-003R3 - "InService Digital Transmission Performance Monitoring Draft Standard".

6. Bell Communications Research, TR-TSY-000009 - "Asynchronous Digital

Multiplexes Requirements and Objectives," Issue 1, May 1986.

7. Bell Communications Research, TR-TSY-000191 - "Alarm Indication Signal

Requirements and Objectives," Issue 1, May 1986.

8. Bell Communications Research, TR-TSY-000233 - "Wideband and

Broadband Digital Cross-Connect Systems Generic Requirements and

Objectives," Issue 2, September 1990.

9. Bell Communications Research, TR-TSY-000820 - "OTGR: Network

Maintenance Transport Surveillance - Generic Digital Transmission

Surveillance, Section 5.1," Issue 1, June 1990.

10. Bell Communications Research, TR-NWT-000499 - "Transpor t Systems

Generic Requirements (TSGR) - Common Requirements," Issue 4,

November 1991.

11. CCITT Blue Book, Recommendation Q.921 - "ISDN User-Network Interface

Data Link Layer Specification", Volume VI, Fascicle VI.10, 1988.

12. CCITT Blue Book, Recommendation G.747 - "Second Order Digital Multiplex

Equipment Operating at 6312 kbit/s and Multiplexing Three Tributaries at

2048 kbit/s", Volume III, Fascicle III.4, 1988.

7

Page 18

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

13. International Organization for Standardization, ISO 3309:1984 - "High-Level

Data Link Control Procedures -- Frame Structure".

8

Page 19

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

4

APPLICATION EXAMPLE

Figure 1 - M1-3 Multiplexer/Demultiplexer

(7 Quad DSX-1/E1 line interfaces)

•

•

•

•

•

•

•

•

•

1:1.36

1:2

1:1.36

1:2

+5V

LIN+

NC-R

LIN-

RGND

RFO

TGN D

LOUT+

NC-T

LOUT-

P

µ

e

fac

0

0

ter

72

P

In

8

ine

I 7

3 L

SS

DS-

AD[15:0]

ALE

RDB

WRB

RESB

INT

RPOS

RNEG

RCLK

LF1

LF2

TPOS

TNE G

TCLK

RPOS

RNEG

RCLK

TPOS

TNE G

TCLK

TICLK

TOH

TOH EN

TIMFP

TOHCLK

TOHFP

A[7:0]

D[7:0]

ALE

RDB

WRB

CSB

RSTB

RD1DAT1

RD1CLK1

TD1DAT1

TD1CLK1

RD1DAT2

RD1CLK2

TD1DAT2

TD1CLK2

RD1DAT3

RD1CLK3

TD1DAT3

TD1CLK3

MX

D3

RD1DAT4

3

RD1CLK4

TD1DAT4

31

TD1CLK4

PM8

RD1DAT28

RD1CLK28

TD1DAT28

TD1CLK28

INTB

TDD[1]

TCLKI[1]

RDD[1]

RCLKO[1]

TDD[2]

TCLKI[2]

RDD[2]

RCLKO[2]

TDD[3]

TCLKI[3]

RDD[3]

RCLKO[3]

TDD[4]

TCLKI[4]

RDD[4]

RCLKO[4]

•

•

•

•

•

A[8:0]

D[7:0]

ALE

RDB

WRB

from /to µP

CSB

RSTB

TXTIP[1]

TXRING[1]

RXTIP[1]

RXRING[1]

TXTIP[2]

TXRING[2]

RXTIP[2]

RXRING[2]

X

TXTIP[3]

S

TXRING[3]

RXTIP[3]

QD

RXRING[3]

4

1

TXTIP[4]

43

TXRING[4]

PM

RXTIP[4]

RXRING[4]

INTB

From chip select

decode circuitry

From Master

reset circu itry

Note:

Use of the SSI LIU as illustrated requires that TICLK has a duty cycle of 45% min

55% max or better (e.g. using a Connor Winfield S65T3 reference oscillator).

9

Page 20

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

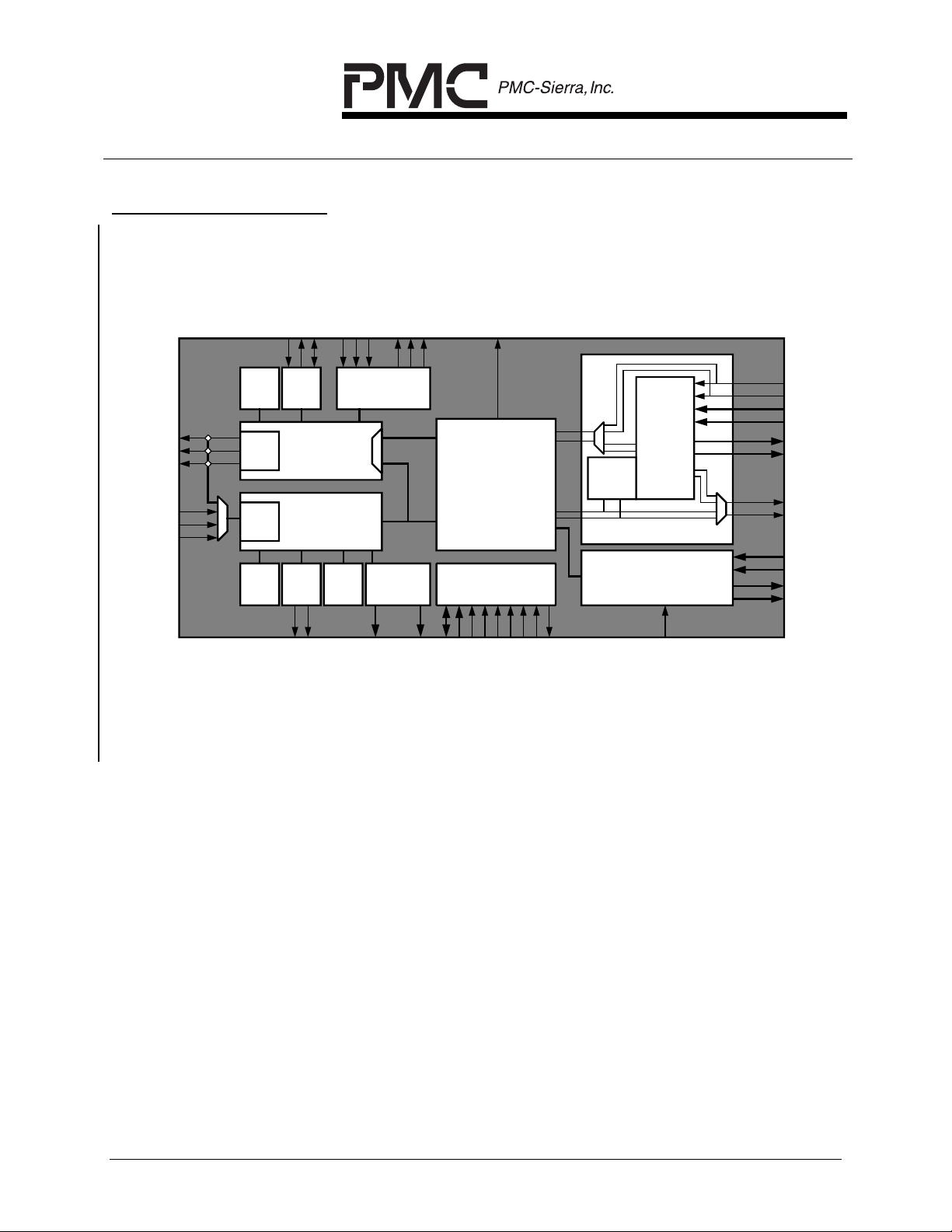

5

TCLK

TPOS/TDAT

TNEG/TMFP

RCLK/VCLK

RPOS/RDAT

RNEG/RLCV

BLOCK DIAGRAM

LINT

TDLEOMI

TDLCLK/TD

XFDL

XBOC

FEAC

B3ZS

Encode

B3ZS

Decode

RBOC

FEAC

Tx

Rx

Tx

HDLC

TRAN

DS3 Transmit

Framer

FRMR

DS3 Receive

Framer

RFDL

Rx

HDLC

RDLCLK/RDLINT

RDLSIG/RDLEOM

TDLSIG/TDLUDR

PMON

Perf.

Monitor

TOH

TOHEN

O/H

Access

RMSFP, ROHP,

ROCLK, RODAT, RMFP,

TOHCLK

Tx

Rx

O/H

Access

ROHCLK,

TIMFP

TOHFP

TICLK

Microprocessor

D[7:0]

RE X Z , RAIS,

ROHFP, ROH, RLOS,

ROOF/RRED, RFERF

GD2CLK

MX23

M23

MUX/DEMUX

I/F

ALE

CSB

A[7:0]

A8/TRS

#1

TD1CLK4

TD1DAT4

MX12

M12 MUX/

DEMUX

DS2

FRMR

Framer

One of seven M12

#2-#7

Remaining Six M12

RDB

WRB

INTB

RSTB

TD2CLK

TD1DAT[3:1 ]

TD1CLK[3:1]

RD1DAT[3:1]

RD1CLK[3:1]

RD1CLK4

RD1DAT4

TD1CLK[28:5]

TD1DAT[28:5]

RD1CLK[28:5]

RD1DAT [28:5]

10

Page 21

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

DESCRIPTION

The PM8313 D3MX M13 Multiplexer supports asynchronous multiplexing and

demultiplexing of 28 DS1s, 21 E1s or 7 DS2s into a DS3 signal. The device

supports ANSI T1.107, Bell Communications Research TR-TSY-000009 and

CCITT Recommendation G.747 standards.

Receive DS3 framing is provided by the DS3 FRMR Framer Block. The FRMR

accepts either a B3ZS encoded bipolar, or a unipolar signal compatible with M23

and C-bit parity applications. The FRMR frames to a DS3 signal with a maximum

average reframe time of 1.5 ms in the presence of a 10

-3

bit error rate. The

FRMR indicates line code violations, loss of signal, framing bit errors, parity

errors, C-bit parity errors, and far end block errors (FEBE). The FRMR detects

far end receive failure (X-bits set to 0), the alarm indication signal (AIS), and the

idle signal. The FRMR is an off-line framer, indicating both out of frame (OOF)

and change of frame alignment (COFA) events. The error events (FER, CBIT

PARITY ERROR, FEBE, etc.) are still indicated while the framer is OOF, based

on the previous frame alignment.

The C-bit parity far end alarm channel (FEAC) and path maintenance data link

are supported. Bit oriented codes in the FEAC channel are detected by the

RBOC Bit-Oriented Code Receiver Block. If enabled, the RBOC generates an

interrupt when a valid code has been received. The path maintenance data link is

terminated using either the RFDL Data Link Receiver Block or an external HDLC

receiver. The RFDL supports polled, interrupt driven, and DMA servicing.

DS3 error event accumulation is provided by the DS3 PMON Performance

Monitor Block. The PMON accumulates framing bit errors, line code violations,

excessive zeros occurrences, parity errors, C-bit parity errors, and far end block

errors. Error accumulation continues even while the off-line framer is indicating

OOF. The counters are intended to be polled once per second, and are sized so

as not to saturate at a 10

-3

bit error rate. Transfer of count values to holding

registers is initiated through the microprocessor interface.

DS3 transmit framing insertion is provided by the DS3 TRAN Transmitter Block. It

outputs either a B3ZS encoded bipolar signal, or a unipolar signal. The DS3

TRAN inserts the X, P, M, C, and F bits into the outgoing DS3 stream. The DS3

TRAN block inserts far end receive failure, AIS, and the idle signal under the

control of external inputs, or internal register bits. Diagnostic features are

provided to allow the generation of line code violation error events, parity error

events, framing bit error events, and when enabled for the C-bit parity

application, C-bit parity error events, and far end block error events. External

11

Page 22

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

inputs allow substitution of the overhead bits or the sourcing of AIS, idle signal or

far end receive failure indication.

When configured for the C-bit parity application, bit oriented codes in the FEAC

channel are inserted by the XBOC Bit-Oriented Code Transmitter Block. The

FEAC code is controlled by an internal register. The path maintenance data link

is inserted using the XFDL Data Link Transmitter Block or an external HDLC

transmitter. The XFDL supports polled, interrupt driven, and DMA servicing.

The demultiplexing and multiplexing of seven 6312 kbit/s data streams into and

out of the DS3 is performed by the MX23 M23 Multiplexer Block. The MX23

contains FIFOs and performs bit stuffing fo r the rate adaptation of the DS2s. The

C-bits are set appropriately, with the option of inserting DS2 loopback requests.

The MX23 may be configured to generate an interrupt upon the detection of

loopback requests in the received DS3. AIS may be inserted in the any of the

6312 kbit/s tributaries in both directions. C-bit parity is supported by sourcing a

6.3062723 MHz clock, which corresponds to a stuffing ratio of 100%.

Framing to the demultiplexed 6312 kbit/s data streams is provided by the DS2

FRMR Framer. It supports both DS2 (ANSI TI.107) and CCITT Recommendation

G.747 frame formats. The maximum average reframe time is 7 ms for DS2 and

1ms for G.747. In DS2 mode, it detects far end receive failure and accumulates

M-bit and F-bit errors. In G.747 mode, it detects remote alarm and accumulates

framing word errors and parity errors. The DS2 FRMR is an off-line framer,

indication both OOF and COFA events. Error events (FERF, MERR, FERR,

PERR, RAI, framing word errors) are still indicated while the DS2 framer is

indicating OOF, based on the previous alignment.

The multiplexing and demultiplexing of the low speed tributaries into and out of a

6312 kbit/s data stream is performed by seven MX12 M12 Multiplexers. Each of

the MX12 blocks may be independently configured to multiplex and demultiplex

four 1544 kbit/s DS1s into and out of a DS2 formatted signal or to multiplex and

demultiplex three 2048 kbit/s signals into and out of a G.747 formatted signal.

Each MX12 may be independently bypassed so an external DS2 may by

multiplexed and demultiplexed directly into and out of the DS3. The MX12

contains FIFOs and performs bit stuffing to accommodate the tributary frequency

deviations. The C-bits are set appropriately, with the option of inserting DS1

loopback requests. The MX12 block may be configured to generate an interrupt

upon the detection of loopback requests in the received DS2. AIS may be

inserted in any of the low speed tributaries in both directions.

12

Page 23

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

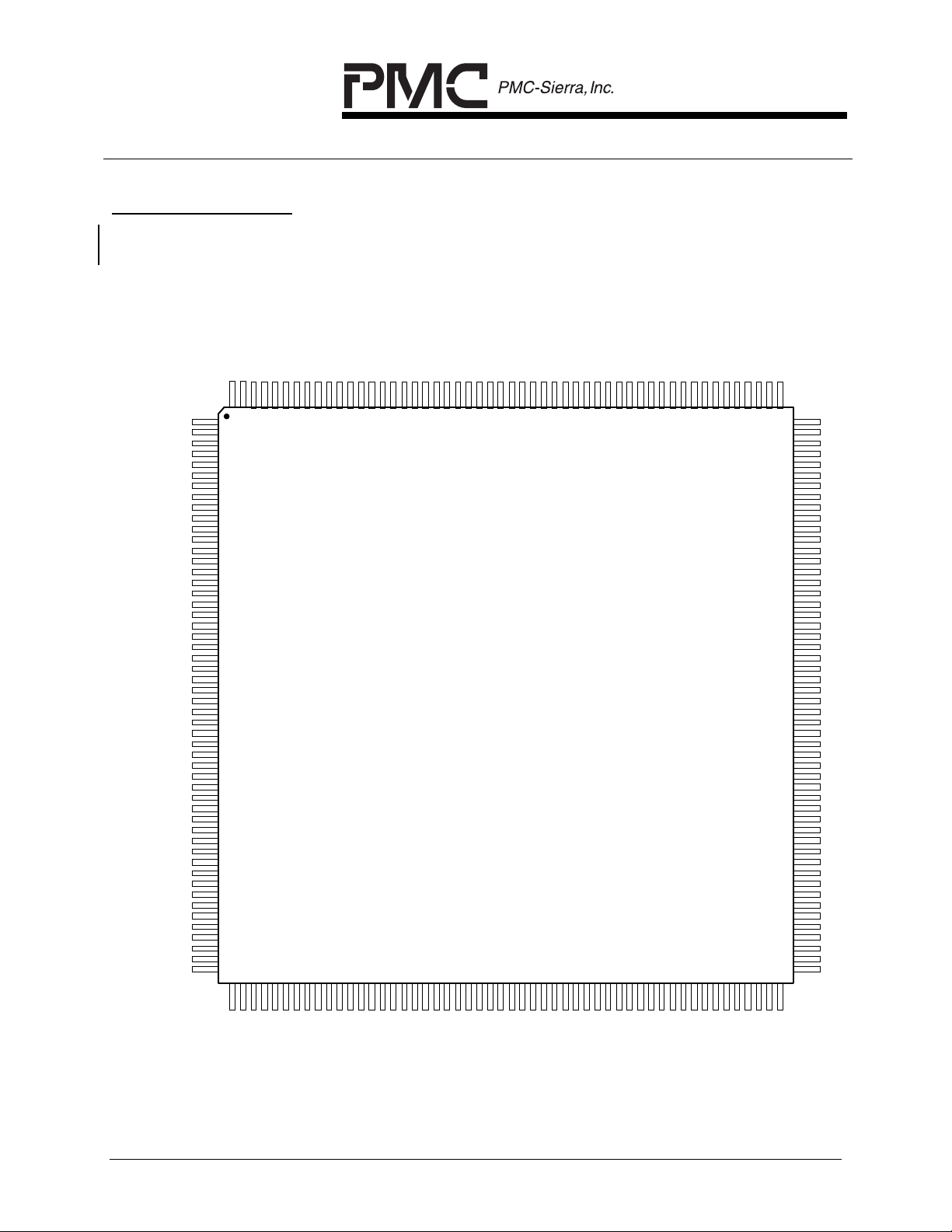

6

PIN DIAGRAM

The D3MX is packaged in a 208 pin PQFP package having a body size of 28 mm by 28

mm and a pin pitch of 0.5 mm.

RD1CLK2

VDDI

RD1DAT3

TD1DAT3

TD1CLK3

RD1CLK3

NC

TD1DAT4

VSSO

PM8313

D3MX

RD1DAT4

TD1CLK4

RD1CLK4

TD1DAT5

NC

RD1DAT5

TD1CLK5

TD1DAT6

RD1CLK5

RD1DAT6

TD1CLK6

NC

TD1DAT7

RD1DAT7

RD1CLK6

TD1CLK7

RD1CLK7

NC

VSSO

VDDO

TD1CLK8

TD1DAT8

RD1DAT8

RD1DAT9

TD1DAT9

RD1CLK8

PIN 157

PIN 1

TICLK

TCLK

TPOS/TDAT

RAIS

TNEG/TMFP

GD2CLK

RODAT

VSSO

VDDO

ROCLK

RMFP

ROHP

NC

TOHCLK

TOHFP

RMSFP

TOH

TOHEN

ROHFP

ROH

ROHCLK

RLOS

RFERF

ROOF/RRED

REXZ

RCLK/VCLK

VSSO

NC

RPOS/RDAT

RNEG/RLCV

RDLCLK/RDLINT

RDLSIG/RDLEOM

INTB

VSSO

NC

VDDO

CSB

ALE

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

PIN 52

TDLCLK/TDLING

TD2CLK

PIN 208

TIMFP

Index

TDLEOMI

TD1DAT1

RD1DAT1

TD1CLK1

TDLSIG/TDLUDR

VSSO

RD1CLK1NCTD1DAT2

VDDO

TD1CLK2

RD1DAT2NCVSSI

PIN 156

TD1CLK9

RD1CLK9

TD1DAT10

RD1DAT10

TD1CLK10

RD1CLK10

TD1DAT11

RD1DAT11

TD1CLK11

NC

RD1CLK11

TD1DAT12

RD1DAT12

TD1CLK12

RD1CLK12

TD1DAT13

NC

RD1DAT13

TD1CLK13

RD1CLK13

TD1DAT14

RD1DAT14

TD1CLK14

RD1CLK14

VSSO

NC

TD1DAT15

RD1DAT15

TD1CLK15

RD1CLK15

TD1DAT16

NC

RD1DAT16

TD1CLK16

RD1CLK16

VDDO

TD1DAT17

NC

RD1DAT17

TD1CLK17

RD1CLK17

TD1DAT18

RD1DAT18

NC

TD1CLK18

VSSO

RD1CLK18

TD1DAT19

RD1DAT19

TD1CLK19

RD1CLK19

TD1DAT20

PIN 105

A7

A6

PIN 53

A8

WRB

RDB

VSSI

RSTB

VDDI

NC

RD1CLK28

TD1CLK28

RD1CLK27

TD1DAT28

RD1DAT28

NC

TD1CLK27

RD1DAT27

TD1CLK26

TD1DAT27

RD1CLK26

NC

RD1DAT26

TD1DAT26

TD1CLK25

RD1CLK25

RD1DAT25NCTD1DAT25

VSSO

NC

TD1CLK24

RD1CLK24

RD1DAT24

TD1CLK23

TD1DAT24

RD1CLK23

TD1CLK22

RD1DAT23

TD1DAT23

RD1CLK22

NC

VDDO

RD1DAT22

VSSO

TD1DAT22

RD1CLK21

TD1CLK21

RD1DAT21

TD1DAT21

RD1CLK20

TD1CLK20

RD1DAT20

PIN 104

13

Page 24

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

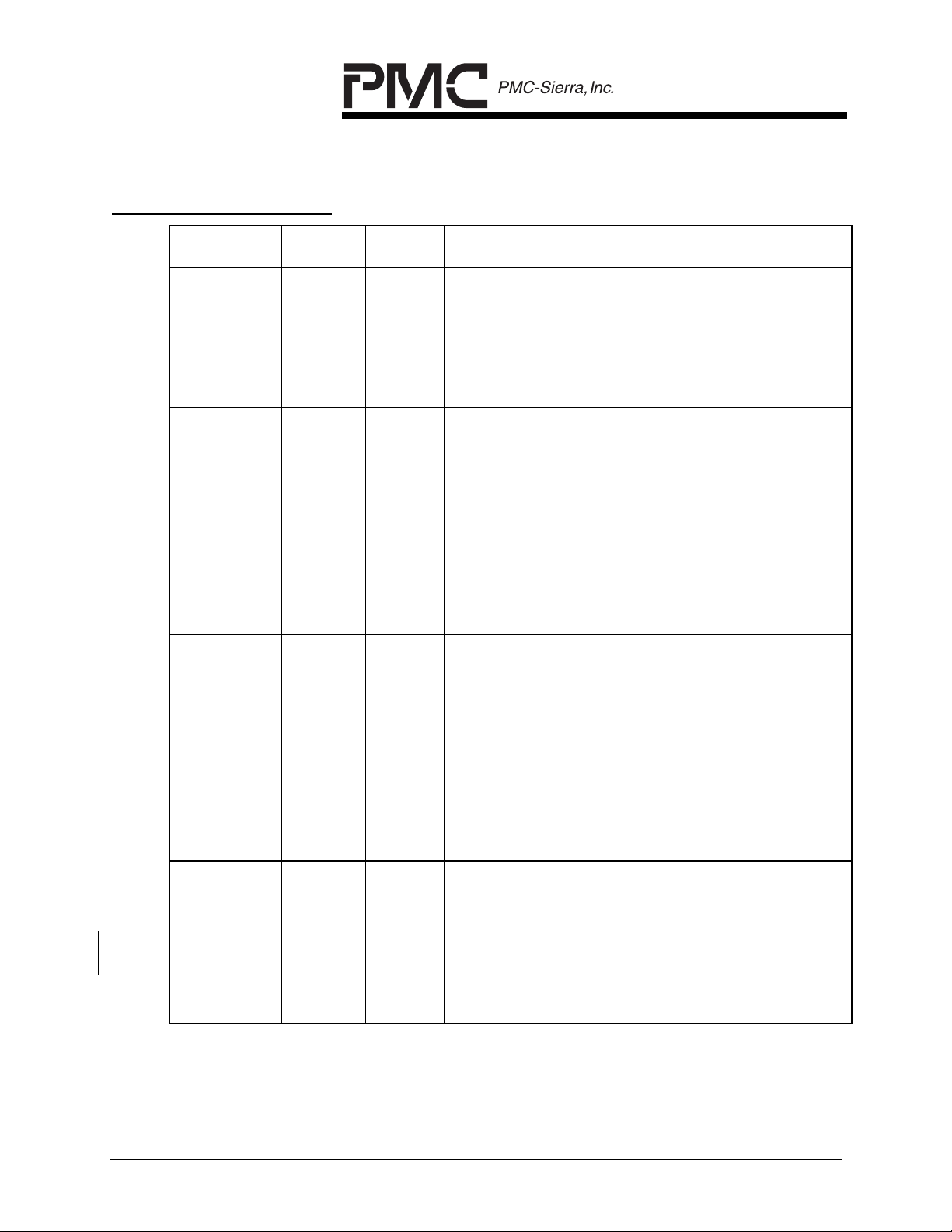

7

PIN DESCRIPTION

Pin Name Type Pin No. Function

RCLK/

VCLK

Input 26 The receive input clock (RCLK) provides timing

for the receive side of the D3MX. RCLK is

nominally a 44.736 MHz, 50% duty cycle clock.

The test vector clock (VCLK) signal is used

during D3MX production testing to verify

internal functionality.

RPOS/

RDAT

Input 29 The positive input pulse (RPOS) signal

represents the positive pulses received on the

B3ZS-encoded line when configured for dual

rail reception. The receive data input (RDAT)

signal represents the unipolar DS3 input

stream when configured for single rail

operation. Both RPOS and RDAT are sampled

on the rising edge of RCLK by default and may

be enabled to be sampled on the falling edge of

RCLK.

RNEG/

RLCV

Input 30 The negative input pulse (RNEG) signal

represents the negative pulses received on the

B3ZS-encoded line when configured for dual

rail reception. Line code violations (LCVs) may

be input on the receive line code violation

(RLCV) signal when configured for single rail

operation. Both RNEG and RLCV are sampled

on the rising edge of RCLK by default and may

be enabled to be sampled on the falling edge of

RCLK.

ROCLK Output 10 The receive output clock (ROCLK) signal

provides timing for downstream processing.

ROCLK is nominally a 44.736 MHz, 50% duty

cycle clock. RODAT, RMFP, RMSFP, RLOS,

REXZ and ROHP are updated on the falling

edge of ROCLK. ROCLK is a buffered version

of RCLK.

14

Page 25

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

RODAT Output 7 The receive data output (RODAT) signal carries

the 44.736 Mbit/s NRZ stream decoded from

the B3ZS line signal. The frame alignment

signals (RMFP, RMSFP, and ROHP) are

aligned to the RODAT stream. RODAT is

updated on the falling edge of ROCLK.

RMFP Output 11 The receive M-frame pulse (RMFP) signal

marks the first bit (X1) in the M-frame of the

DS3 signal on RODAT. When the framer is out-

of-frame, RMFP continues to operate with

timing aligned to the old M-frame position.

When the framer regains frame alignment the

RMFP timing is updated, which may result in a

change of frame alignment. RMFP is updated

on the falling edge of ROCLK.

RMSFP Output 16 The receive M-subframe pulse (RSMFP) signal

marks the first bit (X, P, and M) in each M-

subframe of the received DS3 stream (RODAT)

when the framer is in-frame. When the framer

is out-of-frame, RSMFP continues to operate

with timing aligned to the old M-frame position.

When the framer regains frame alignment the

RMSFP timing is updated, which may result in

a change of frame alignment. RSMFP is

updated on the falling edge of ROCLK.

ROHP Output 12 The receive overhead pulse (ROHP) signal

marks the overhead bit positions (X, P, M, C,

and F) in the received DS3 stream (RODAT)

when the framer is in-frame. When the framer

is out-of-frame, ROHP continues to operate

with timing aligned to the old M-frame position.

When the framer regains frame alignment the

ROHP timing is updated, which may result in a

change of frame alignment. ROHP is updated

on the falling edge of ROCLK.

15

Page 26

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

ROHCLK Output 21 The receive overhead clock (ROHCLK) cycles

once per overhead bit. ROHCLK is nominally a

526 kHz clock. ROOF, RFERF, RAIS, RIDL,

RFERR, ROH, and ROHFP are updated on the

falling edge of ROHCLK.

ROH Output 20 The receive overhead data (ROH) signal

contains the overhead bits (C, F, X, P, and M)

extracted from the received DS3 stream. ROH

is updated on the falling edge of ROHCLK.

ROHFP Output 19 The receive overhead frame position (ROHFP)

signal may be used to locate the individual

overhead bits in the received overhead data

stream, ROH. ROHFP is high during the X1

overhead bit position in the ROH stream.

ROHFP is updated on the falling edge of

ROHCLK.

RLOS Output 22 The receive loss of signal (RLOS) status is set

high when the dual rail NRZ format stream is

selected, and 175 successive zeros are

detected on the RPOS and RNEG inputs.

RLOS is set low when the ones' density is

greater than 33% for 175 ± 1 bit periods on the

RPOS and RNEG inputs. RLOS is updated on

the falling edge of ROCLK.

REXZ Output 25 The receive excessive zero (REXZ) signal

indicates the presence of 3 or more

consecutive zeros in the received DS3 bipolar

stream. REXZ pulses high for one ROCLK

cycle whenever 3 or more consecutive zeros

are detected. When the Receive DS3 interface

is configured to for uni-polar data, the REXZ

output is forced low. REXZ is updated on the

falling edge of ROCLK.

16

Page 27

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

RAIS Output 4 The receive alarm indication signal (RAIS)

indicates the presence of AIS in the received

DS3 stream. RAIS is set high when the AIS

pattern has been received for 2.23 ms or 13.5

ms (software selectable). RAIS is set low when

the AIS pattern has not been received for 2.23

ms or 13.5 ms. RAIS is updated on the falling

edge of ROHCLK.

ROOF/ Output 24 The receive out-of-frame (ROOF) signal is set

high when an out-of-frame condition is

declared. An out-of-frame is declared when 3

out of 16 (default) or 3 out of 8 consecutive F-

bit errors are detected, or when one or more M-

bit errors is detected in 3 out of 4 consecutive

M-frames. ROOF is set low when an in-frame

condition is declared. ROOF is updated on the

falling edge of ROHCLK. This ROOF signal is

available when the REDO bit in the Master

Alarm Enable register is logic 0.

RRED The receive RED Alarm (RRED) signal is

available when the REDO bit in the Master

Alarm Enable register is logic 1. The RRED

output is set high when a DS3 out-of-frame

condition or DS3 loss of signal condition has

been present for either 2.23ms or 13.5 ms. The

RRED output is set low when a DS3 out-of-

frame condition or DS3 loss of signal condition

has been absent for either 2.23ms or 13.5 ms.

RRED is updated on the falling edge of

ROHCLK.

17

Page 28

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

RFERF Output 23 The receive far end receive failure (RFERF)

signal reflects the value of the internal FERF

state buffered by two M-frames. Internally,

FERF is set high when both X-bits (X1 and X2)

are received as logic 0 in the current M-frame;

FERF is set low when both X-bits are received

as logic 1. FERF remains in its previous state

when X1 • X2 in the current M-frame. The

RFERF output latency provides a better than

99.99% chance of freezing (i.e. holding RFERF

in its previous state) upon a valid state value

during the occurrence of an out of frame.

RFERF is updated once per M-frame on the

falling edge of ROHCLK.

18

Page 29

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

RDLCLK/

RDLINT

Output 31 The receive data link clock (RDLCLK) signal is

active when an external HDLC receiver is

selected (the REXHDLC bit in the Master

HDLC Configuration Register is a logic 1). The

RDLCLK signal provides timing for the external

processing of the path maintenance data link

signal extracted by the DS3 FRMR. RDLCLK is

updated on the falling edge of the ROHCLK

signal and cycles 3 times per M-frame.

RDLCLK is nominally a 28.2 kHz clo ck, which

is low for at least 1.9 µs per cycle.

The data link interrupt (RDLINT) signals is

active when the internal HDLC receiver is

selected (the REXHDLC in the Master HDLC

Configuration Register bit is a logic 0). The

RDLINT signal is asserted when an event

occurs which changes the status of the HDLC

receiver. RDLINT is updated on the falling

edge of the ROHCLK signal. RDLINT is

deasserted when the Interrupt Enable/Status

Register is read in the HDLC receiver. By

default RDLINT is an active low open-drain

output, but can be configured as active high.

Typically, RDLINT would be connected to an

external DMA device. If the supervising

microprocessor is desired to service the RFDL,

this output can be wired-ORed with the INTB

output when RDLINT is configured as an

active-low open drain output.

19

Page 30

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

RDLSIG/

RDLEOM

Output 32 The receive data link (RDLSIG) signal is active

when an external HDLC receiver is selected

(the REXHDLC bit in the corresponding Master

HDLC Configuration Register is a logic 1). The

RDLSIG signal carries bits extracted from the

three C-bits in M-subframe #5 by the DS3

framer. RDLSIG is held high when C-bit parity

mode is not enabled. RDLSIG is updated on

the falling edge of the corresponding RDLCLK

signal.

The receive end of message (RDLEOM) signal

is active if the internal HDLC receiver is

selected (the REXHDLC bit in the Master

HDLC Configuration Register is a logic 0). The

RDLEOM signal is asserted when the last byte

of a sequence is read from the HDLC receiver,

or if the receiver's buffer overruns. RDLEOM is

updated on the falling edge of the ROHCLK

signal. RDLEOM is deasserted when the

Interrupt Enable/Status Register is read in the

HDLC Receiver. By default, RDLEOM is an

active low open-drain output, but can be

configured as active high.

Typically, RDLEOM would be connected to the

supervising microprocessor when an external

DMA is used, signaling the microprocessor that

a complete message is ready. In this case the

RDLEOM is configured as an active-low open

drain output and wired-ORed with the INTB

output.

20

Page 31

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

RD1CLK1

RD1CLK2

RD1CLK3

RD1CLK4

RD1CLK5

RD1CLK6

RD1CLK7

RD1CLK8

RD1CLK9

RD1CLK10

RD1CLK11

RD1CLK12

RD1CLK13

RD1CLK14

RD1CLK15

RD1CLK16

RD1CLK17

RD1CLK18

RD1CLK19

RD1CLK20

RD1CLK21

Output 198

193

186

180

175

170

166

159

155

151

146

142

137

133

127

122

116

110

106

102

98

The receive DS1 clock (RD1CLK[28:1]) signals

provide timing for each of the 28 demultiplexed

DS1 streams. The RD1CLK[28:1] signals are

nominally 1.544 MHz clocks, but have

substantial jitter due to the demultiplexing and

destuffing processes. The RD1DAT[28:1]

outputs are updated on the falling edges of the

corresponding RD1CLK[28:1] signals.

When the internal M12 multiplexers are

configured for G.747 multiplexing, every fourth

RD1CLK signal (RD1CLK4, 8, 12, 16, 20, 24,

28) is unused and held low. The remaining

RD1CLK signals are then nominally 2.048 MHz

clocks.

When the internal M12 multiplexers are

bypassed, every fourth RD1CLK signal

(RD1CLK4, 8, 12, 16, 20, 24, 28) may become

a DS2 rate clock operating at nominally 6.312

MHz. The remaining RD1CLK signals for the

particular M12 multiplexer bypassed are then

unused and held low.

The internal M12 multiplexers may be

bypassed or configured for G.747 multiplexing

on an individual basis. Thus the configuration

of each of the seven blocks of four RD1CLK

signals is independently programmable.

RD1CLK22

RD1CLK23

RD1CLK24

RD1CLK25

RD1CLK26

RD1CLK27

RD1CLK28

91

87

82

76

71

66

62

21

Page 32

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

RD1DAT1

RD1DAT2

RD1DAT3

RD1DAT4

RD1DAT5

RD1DAT6

RD1DAT7

RD1DAT8

RD1DAT9

RD1DAT10

RD1DAT11

RD1DAT12

RD1DAT13

RD1DAT14

RD1DAT15

RD1DAT16

RD1DAT17

RD1DAT18

RD1DAT19

Output 202

195

188

182

177

173

168

161

157

153

149

144

139

135

129

124

118

114

108

The receive DS1 data (RD1DAT[28:1]) signals

carry the 28 demultiplexed DS1 streams. The

RD1DAT[28:1] outputs are updated on the

falling edges of the corresponding

RD1CLK[28:1] signals.

When the internal M12 multiplexers are

configured for G.747 multiplexing, every fourth

RD1DAT signal (RD1DAT4, 8, 12, 16, 20, 24,

28) is unused and held low. The remaining

RD1DAT signals are then nominally 2.048

Mbit/s data streams.

When the internal M12 multiplexers are

bypassed, every fourth RD1DAT signal

(RD1DAT4, 8, 12, 16, 20, 24, 28) may become

a DS2 rate data stream operating at nominally

6.312 Mbit/s. The remaining RD1DAT signals

for the particular M12 multiplexer bypassed are

then unused and held low.

The internal M12 multiplexers may be

bypassed or configured for G.747 multiplexing

on an individual basis. Thus the configuration

of each of the seven blocks of four RD1DAT

signals is independently programmable.

RD1DAT20

RD1DAT21

RD1DAT22

RD1DAT23

RD1DAT24

RD1DAT25

RD1DAT26

RD1DAT27

RD1DAT28

104

100

94

89

84

78

74

69

64

22

Page 33

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

TD1CLK1

TD1CLK2

TD1CLK3

TD1CLK4

TD1CLK5

TD1CLK6

TD1CLK7

TD1CLK8

TD1CLK9

TD1CLK10

TD1CLK11

TD1CLK12

TD1CLK13

TD1CLK14

TD1CLK15

TD1CLK16

TD1CLK17

TD1CLK18

TD1CLK19

TD1CLK20

TD1CLK21

Input 201

194

187

181

176

172

167

160

156

152

148

143

138

134

128

123

117

112

107

103

99

The transmit DS1 clock (TD1CLK[28:1]) signals

provide timing for each of the 28 DS1 streams

to be multiplexed. The TD1CLK[28:1] signals

should nominally be 1.544 MHz clocks, and

should have the minimal jitter and wander of a

standard DS1 line signal. The TD1DAT[28:1]

inputs are sampled on the rising edges of the

corresponding TD1CLK[28:1] signals.

When the internal M12 multiplexers are

configured for G.747 multiplexing, every fourth

TD1CLK signal (TD1CLK4, 8, 12, 16, 20, 24,

28) is unused and ignored. The remaining

TD1CLK signals should then nominally be

2.048 MHz clocks.

When the internal M12 multiplexers are

bypassed, every fourth TD1CLK signal

(TD1CLK4, 8, 12, 16, 20, 24, 28) should then

become a DS2 rate clock operating at

nominally 6.312 MHz. The remaining TD1CLK

signals for the particular M12 multiplexer

bypassed are then unused and ignored.

The internal M12 multiplexers may be

bypassed or configured for G.747 multiplexing

on an individual basis. Thus the configuration

of each of the seven blocks of four TD1CLK

signals is independently programmable.

TD1CLK22

TD1CLK23

TD1CLK24

TD1CLK25

TD1CLK26

TD1CLK27

TD1CLK28

92

88

83

77

72

68

63

23

Page 34

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

TD1DAT1

TD1DAT2

TD1DAT3

TD1DAT4

TD1DAT5

TD1DAT6

TD1DAT7

TD1DAT8

TD1DAT9

TD1DAT10

TD1DAT11

TD1DAT12

TD1DAT13

TD1DAT14

TD1DAT15

TD1DAT16

TD1DAT17

TD1DAT18

TD1DAT19

Input 203

196

190

184

179

174

169

162

158

154

150

145

141

136

130

126

120

115

109

The transmit DS1 data (TD1DAT[28:1]) signals

carry the 28 DS1 streams to be multiplexed.

The TD1DAT[28:1] inputs are sampled on the

rising edges of the corresponding

TD1CLK[28:1] signals.

When the internal M12 multiplexers are

configured for G.747 multiplexing, every fourth

TD1DAT signal (TD1DAT4, 8, 12, 16, 20, 24,

28) is unused and ignored. The remaining

TD1DAT signals should then nominally be

2.048 Mbit/s data streams.

When the internal M12 multiplexers are

bypassed, every fourth TD1DAT signal

(TD1DAT4, 8, 12, 16, 20, 24, 28) may become

a DS2 rate data stream operating at nominally

6.312 Mbit/s. The remaining TD1DAT signals

for the particular M12 multiplexer bypassed are

then unused and ignored.

The internal M12 multiplexers may be

bypassed or configured for G.747 multiplexing

on an individual basis. Thus the configuration

of each of the seven blocks of four TD1DAT

signals is independently programmable.

TD1DAT20

TD1DAT21

TD1DAT22

TD1DAT23

TD1DAT24

TD1DAT25

TD1DAT26

TD1DAT27

TD1DAT28

105

101

97

90

86

81

75

70

65

24

Page 35

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

GD2CLK Output 6 The transmit generated DS2 clock (GD2CLK)

signal is provided for use in integrated M13 or

C-bit parity multiplex applications. When

configured for M13 operation, GD2CLK is

nominally a 6.311993 MHz clock, which

corresponds to a stuffing ratio of 39.1%. When

configured for C-bit parity operation, GD2CLK

is nominally a 6.3062723 MHz clock, which

corresponds to a stuffing ratio of 100%. The

GD2CLK may be connected to the TD2CLK

input clock. GD2CLK is updated on the falling

edge of TCLK.

TD2CLK Input 206 The transmit DS2 clock (TD2CLK) signal

provides timing for the multiplex side of all of

the MX12 TSBs. TD2CLK is nominally a 6.312

MHz, 50% duty cycle clock.

25

Page 36

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

TDLSIG/

TDLUDR

I/O 205 The transmit data link (TDLSIG) signal is active

when an external HDLC receiver is selected

(the TEXHDLC bit in the corresponding Master

HDLC Configuration Register is a logic 1). The

TDLSIG signal carries bits to be inserted in the

three C-bits in M-subframe #5 by the DS3

transmitter. TDLSIG is ignored when C-bit

parity mode is not enabled. TDLSIG is

sampled on the rising edge of the TDLCLK

signal.

The transmit data link underrun (TDLUDR)

signal is active when the internal HDLC

receiver is selected (the TEXHDLC bit in the

corresponding Master HDLC Configuration

Register is a logic 0). TDLUDR is asserted

when the internal HDLC transmitter underruns.

TDLUDR is deasserted by writing to the XFDL

Interrupt Status Register. By default TDLUDR

is an active low open-drain output, but can be

configured as active high.

Upon a reset, the TEXHDLC bit a logic 1, thus,

the pin is configured as an input, TDLSIG.

Typically, TDLUDR would be connected to the

supervising microprocessor when an external

DMA is used, signaling the microprocessor that

a severe error has occurred causing the

transmit buffer to underrun. In this case the

TDLUDR is configured as an active-low open

drain output and wired-ORed with the INTB

output.

26

Page 37

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

TDLCLK/

TDLINT

Output 207 The transmit data link clock (TDLCLK) signal is

active when an external HDLC receiver is

selected (the TEXHDLC bit in the Master HDLC

Configuration Register is a logic 1). The

TDLCLK signal provides timing for the external

sourcing of the path maintenance data link

signal inserted by the DS3 TRAN. TDLCLK is

updated on the falling edge of the TOHCLK

signal and cycles 3 times per M-frame.

TDLCLK is nominally a 28.2 kHz clock, which is

low for at least 1.9 µs per cycle.

The transmit data link interrupt (TDLINT) signal

is active when the internal HDLC transmitter is

selected (the TEXHDLC bit in the

corresponding Master HDLC Configuration

Register is a logic 0).TDLINT is asserted when

the last data byte written to the internal HDLC

transmitter has been setup fo r transmission,

and a write is required to the XFDL

Configuration Register, or the XFDL Transmit

Data Register to either end the current

message transmission, or to provide more

data. By default TDLINT is an active low open-

drain output, but can be configured as active

high.

Typically, TDLINT would be connected to an

external DMA device. If the supervising

microprocessor is desired to service the XFDL,

this output can be wired-ORed with the INTB

output when TDLINT is configured as an active-

low open drain output.

27

Page 38

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

TDLEOMI Input 204 The transmit data link end of message input

(TDLEOMI) provides a method for an external

DMA controller to signal the end of the

transmitted message to the HDLC transmitter

without needing to write to the XFDL

Configuration Register. The TDLEOMI input is

active high and must be glitch-free. It internally

sets the corresponding EOM register bit in the

XFDL Configuration register. The TDLEOMI

input may be asserted during or after the write

of the last byte of a packet but before the next

byte would be expected (within 210 µs of the

last assertion of TDLINT or the INT bit in the

XFDL Status Register). TDLEOMI must be

deasserted before the write of the first byte of

the next packet. TDLEOMI is ignored if no data

transmission is pending.

TICLK Input 1 The transmit input clock (TICLK) provides the

transmit direction timing. TICLK is nominally a

44.736 MHz, 50% duty cycle clock. TIMFP is

sampled on the rising edge of TICLK.

TIMFP Input 208 The transmit M-frame pulse input (TIMFP)

signal allows one to control the alignment of the

M-frame of the transmitted DS3 stream (TDAT).

The first bit (X1) of the M-frame on TDAT will

occur within several TICLK cycles and be

identified by the TMFP output signal. TIMFP

may be tied low if such control is not required.

TIMFP is sampled on the rising edge of TICLK.

TOH Input 17 The transmit overhead data (TOH) signal

contains the overhead bits (C, F, X, P, and M)

that may be inserted in the transmitted DS3

stream. TOH is sampled on the rising edge of

TOHCLK.

28

Page 39

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

TOHEN Input 18 The transmit overhead insertion (TOHEN)

signal controls the insertion of DS3 overhead

bits from the TOH input. When TOHEN is high,

the associated overhead bit in the TOH stream

is inserted in the transmitted DS3 frame. When

TOHEN is low, the DS3 overhead bit is

generated and inserted internally. TOHEN is

sampled on the rising edge of TOHCLK.

TOHFP Output 15 The transmit overhead frame position (TOHFP)

signal may be used to align the individual

overhead bits in the transmitted overhead data

stream, TOH, to the DS3 M-frame. TOHFP is

high during the X1 overhead bit position in the

TOH stream. TOHFP is updated on the falling

edge of TOHCLK.

TOHCLK Output 14 The transmit overhead clock (TOHCLK) cycles

once per overhead bit. TOHCLK is nominally a

526 kHz clock. TOHFP is updated on the falling

edge of T OHCLK. T OH, and TOHEN are

sampled on the rising edge of TOHCLK.

TCLK Output 2 The transmit clock (TCLK) provides timing for

circuitry downstream of the DS3 transmitter of

the D3MX. TCLK is nominally a 44.736 MHz,

50% duty cycle clock.

TPOS/

TDAT

Output 3 The transmit positive pulse (TPOS) signal

represents the positive pulses transmitted on

the B3ZS-encoded line when configured for

dual-rail operation. TPOS is updated on the

falling edge of TCLK by default but may be

enabled to be updated on the rising edge of

TCLK.

The transmit data output (TDAT) signal

represents a unipolar DS3 output stream when

configured for single rail operation. TDAT is

updated on the falling edge of TCLK by default

but may be enabled to be updated on the r ising

edge of TCLK.

29

Page 40

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

TNEG/

TMFP

Output 5 The transmit negative pulse (TNEG) signal

represents the negative pulses transmitted on

the B3ZS-encoded line when configured for

dual rail operation. TNEG is updated on the

falling edge of TCLK by default but may be

enabled to be updated on the rising edge of

TCLK.

The transmit multiframe pulse (TMFP) signal

marks the transmit M-frame alignment when

configured for single rail operation. The TMFP

output is high during the first bit (X1) of the

DS3 multiframe presented on TDAT. TMFP is

updated on the falling edge of TCLK by default

but may be enabled to be updated on the r ising

edge of TCLK.

INTB Output 33 The active low interrupt (INTB) signal goes low

when one of the DS3 FRMR, RBOC, DS2

FRMR, MX12, MX23 or PMON TSBs generates

an interrupt, provided that the interrupt source

in question is not masked. INTB goes high

when the Interrupt Enable/Status Register is

read in the corresponding TSB. Note that INTB

will remain low until all active, unmasked

interrupt sources are acknowledged. The INTB

signal is an open drain output.

CSB Input 45 The active low chip select (CSB) signal is low

during D3MX register accesses. CSB mu st go

high at least once after a powerup to clear

internal test modes. If CSB is not used, then it

should be tied to an inverted version of RSTB,

in which case RDB and WRB determine

register accesses

RDB Input 57 The active low read enable (RDB) signal is low

during D3MX register read accesses. The

D3MX drives the D7-D0 bus with the contents

of the addressed register while RDB and CSB

are low.

30

Page 41

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

WRB Input 56 The active low write strobe (WRB) signal is low

during a D3MX register write access. The D7-

D0 bus contents are clocked into the

addressed register on the rising WRB edge

while CSB is low.

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

A6

I/O 34

35

37

38

39

41

42

44

Input 47

48

49

50

51

52

53

The bidirectional data bus (D7-D0) is used

during D3MX register read and write accesses.

The address bus (A8-A0) selects specific

registers during D3MX register accesses.

A7

54

A8/TRS 55 The test register select (TRS) signal

discriminates between normal and test mode

register accesses. TRS is high during test

mode register accesses, and is low during

normal mode register accesses. The TRS input

has an integral pull down resistor.

TRS should be connected to ground for normal

mode register access.

RSTB Input 58 The active low reset (RSTB) signal provides an

asynchronous D3MX reset. RSTB is a Schmitt

triggered input with an integral pull up resistor.

31

Page 42

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Pin Name Type Pin No. Function

ALE Input 46 The address latch enable (ALE) is active high

and latches the address bus (A7-A0) and TRS

when low. When ALE is high, the internal

address latches are transparent. It allows the

D3MX to interface to a multiplexed

address/data bus. The ALE input has an

integral pull up resistor.

VDDI1

VDDI2

VSSI1

VSSI2

VDDO1

VDDO2

VDDO3

VDDO4

VDDO5

VDDO6

VSSO1

VSSO2

VSSO3

VSSO4

VSSO5

Power 60

189

Ground 59

191

Power 199

9

43

95

121

164

Ground 200

8

36

96

111

The core power (VDDI) pins should be

connected to a well decoupled +5 V DC in

common with VDDO.

The core ground (VSSI) pins should be

connected to GND in common with VSSO.

The pad ring power (VDDO) pins should be

connected to a well decoupled +5 V DC in

common with VDDI.

The pad ring ground (VSSO) pins should be

connected to GND in common with VSSI.

VSSO6

VSSO7

VSSO8

VSSO9

VSSO10

163

183

27

80

132

32

Page 43

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

Notes on Pin Description:

All D3MX inputs and bidirectionals present minimum capacitive loading and

operate at TTL logic levels.

All D3MX digital outputs and bidirectionals have 2 mA drive capability, except the

INTB, TPOS/TDAT, TNEG/TMFP, TCLK, ROCLK, RODAT, RMFP, RMSFP, ROHP

outputs and the D7-D0 bidirectionals, which have 4 mA drive capability.

The VSSO and VSSI ground pins are not internally connected together. Failure

to connect these pins externally may cause malfunction or damage the D3MX.

The VDDO and VDDI power pins are not internally connected together. Failure to

connect these pins externally may cause malfunction or damage the D3MX.

208-pin QFP pins # 13, 28, 40, 61, 67, 73, 79, 85, 93, 113, 119, 125, 131, 140,

147, 165, 171, 178, 185, 192, 197 are all "no-connect".

33

Page 44

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

8

FUNCTIONAL DESCRIPTION

8.1 DS3 Framer

The DS3 Framer (FRMR) Block integrates circuitry required for decoding a

B3ZS-encoded signal and framing to the resulting DS3 bit stream. The FRMR is

directly compatible with the M23 and C-bit parity DS3 applications.

The FRMR decodes a B3ZS-encoded signal and provides indications of line

code violations. The B3ZS decoding algorithm and the LCV definition can

independently be chosen via software. Loss of signal is also detected.

The framing algorithm examines five F-bit candidates simultaneously. When at

least one discrepancy has occurred in all the candidates, the algorithm examines

the next set of candidates. When a single F-bit candidate remains in a set, the

first bit in the supposed M-subframe is examined for the M-frame alignment

signal (i.e. the M-bits, M1,M2,M3, are following the 010 pattern). Framing is

declared if the M-bits are correct for three consecutive M-frames while no

discrepancies have occurred in the F-bits. During the examination of the M-bits

the X-bits and P-bits are ignored. The algorithm gives a maximum average

reframe time of less than 1.5 ms.

Once in-frame, the FRMR provides indications of the M-frame and M-subframe

boundaries, and identifies the overhead bit positions in the incoming DS3 signal.

While the FRMR is in-frame, the F-bit and M-bit positions in the DS3 stream are

examined. Out-of-frame is declared when 3 F-bit errors out of 16 consecutive Fbits or 8 consecutive F-bits are observed (selectable by the M3O8 bit), or when

one or more M-bit errors are detected in 3 out of 4 consecutive M-frames. The

M-bit error criteria for OOF can be disabled via the MBDIS bit in the DS3 Framer

configuration register. The 3 out of 8 consecutive F-bits out-of-frame ratio

-

provides more robust operation in the presence of a 10

3

bit error rate than the 3

out of 16 consecutive F-bits ratio (less than one false OOF every minute verses

one false OOF every 6 seconds, respectively); either choice of out-of-frame ratios

allows an out-of-frame to be declared quickly when the M-subframe alignment

patterns or, optionally, when the M-frame alignment is lost.

Also while in-frame, M-bit or F-bit framing bit errors and P-bit parity errors are

indicated. When C-bit parity mode is enabled, both C-bit parity errors and far

end block errors are indicated. These error indications, as well as the line code

violation and excessive zeros indication, may be accumulated over 1 second

intervals with the T3 Performance Monitor (PMON). Note that the framer is an

34

Page 45

PM8313 D3MX

DATA SHEET

PMC-920702 ISSUE 5 M13 MULTIPLEXER

off-line framer, indicating both OOF and COFA events. Even if an OOF is

indicated, the framer will continue indicating performance monitoring information