Page 1

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

PM5313

SPECTRA-622

SONET/SDH PAYLOAD

EXTRACTOR/ALIGNER

FOR 622 MBIT/S

DATA SHEET

PROPRIET A RY AND CONFIDENTIAL

PRODUCTION

ISSUE 6: SEPTEMBER 2000

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

Page 2

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

Issue No. Issue Date Details of Change

Issue 6 Sept 2000

Issue 5 May 2000

• Remove support of in-band G1 reporting on

DROP bus

• Improve RAD Timing diagram (Fig 60)

• Pointer justification not generated in PAIS on

DROP bus

• Specify that the jitter tolerance is according to the

1995 Bellcore spec.

• Remove the K1 and K2 bytes from the RAD.

• Specify that a RESET_PATH command will also

clear the performing monitor counters of the

section/line TSBs.Update AC and DC

Characeristic sections according to its final

report..

• V1 pulse is always outputted on the DROP bus

when the RTAL FIFO is bypassed

• Add the RESET sequence to enable the TX line

interface and the OUTDATA bit in the CRSI.

• Specify TFPO timing in serial mode

• CRU and CSU will track REFCLK while in ROOL

• Describe RX and TX bypass mode limitations

• SDLE and RBYP mode can not be set at the

same time.

• Fix number of bits before a DOOL is declared

from 80 to 96.

• Bit 7 of register 0090H is now X vs 0.

• Write to the PMON c ounter registers will also

trigger a count transfer.

• SS bits are always 00 when the DPGM is in

autonomous mode.

• Add WANS programming section

• Update the RAD and TFPI timing diagrams.

• Update rev of CRU, GPGM and TTOC.

• Update the methodology Tools table.

• Added STM1-CONCAT register bits in RPPS and

TPPS configuration.

• Extend the timing for output pins RSUC, RSOW,

ROH and TDO.

PROPRIETARY AND CONFIDENTIAL i

Page 3

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

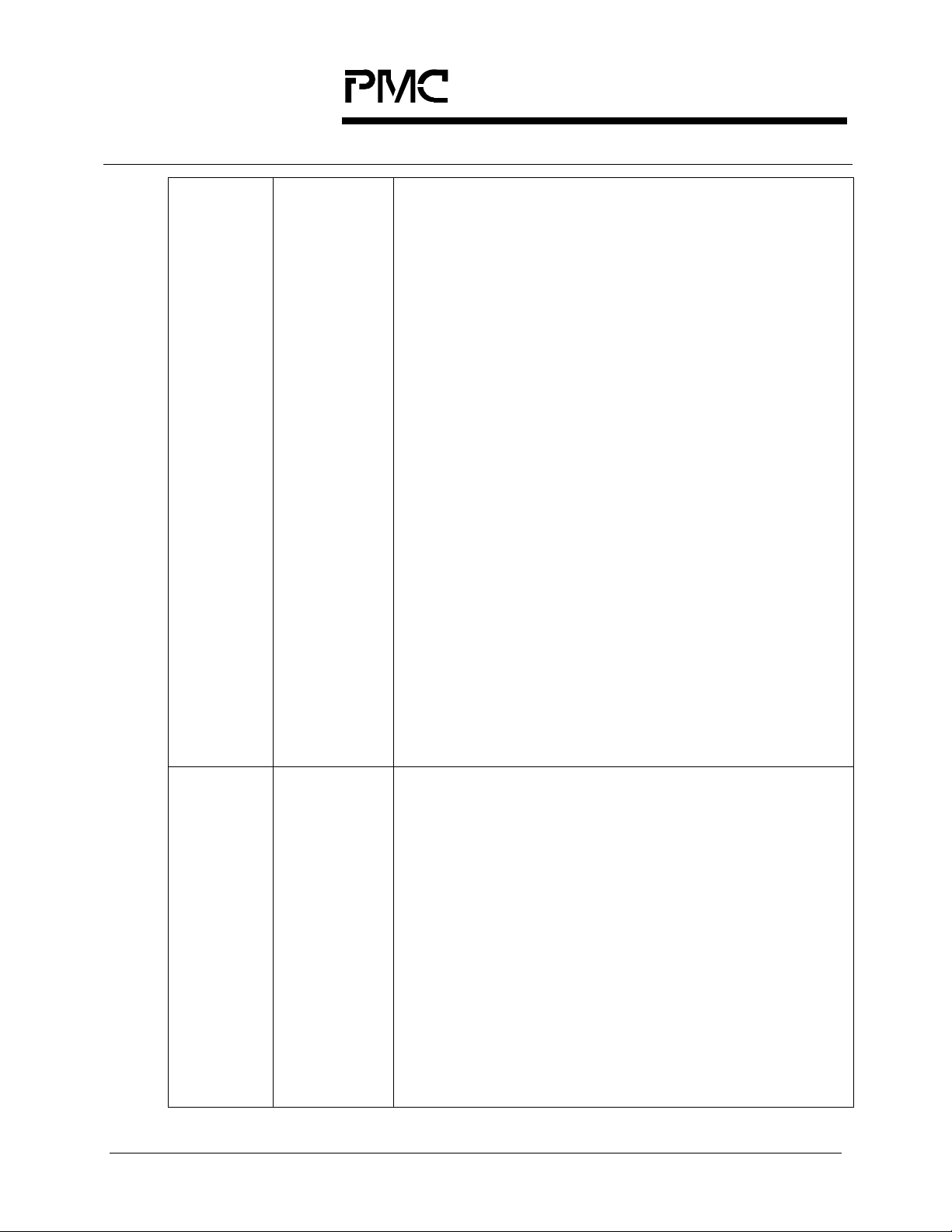

• Remove support for the tandem connection

• Removed RESBYP and TESBYPASS register bits

in RPPS and TPPS configuration. Bypass is no

longer programmable per slice but for all RPPS or

TPPS slices via the RESBYP and TESBYP bits

found in DROP and ADD BUS configuration

registers.

• Fix RASE filtering spec to 8 frames

• Correct DLL, APGM and DPGM register bits

description

• Describe use of ATSI bit in APGM autonomous

mode.

• Remove support of 12c when both autonomous

mode and DTMODE are use.

• Specify that FOOF affect only one frame

• Add TS

DC spec.

TAD

• Add power supply filtering and PECL I/O

diagrams

• Revise RPOH timing diagrams

• Add BYPASS Rx and TX mode description and

limitation. No support for TUAIS, tx dual mode

and pointer generation by STALs.

• Specify that activity on the AC1J1V1, ADP and

APL pins can not be detected if ADP is tied high

or low.

Issue 4

• Revised RPPS alarm bit names, register 0n1C

• Revised National bit description in the TTOC

register 00C1

• Revised signal mapping in register 0009

SPECTRA 622 Section Alarm Control #2

• Added pin description of the Transmit Ring

Control Port

• Fixed polarity for bit 7, register 0102

• Added TPIP is held in reset in DS3 mode only

• Revised TPAIS and DPAIS frame slots to correctly

correspond to slice order

• Clarified precedence of TOH Overhead port over

TSOW , TSUC , and TLOW

• Removed some DLL registers

PROPRIETARY AND CONFIDENTIAL ii

Page 4

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

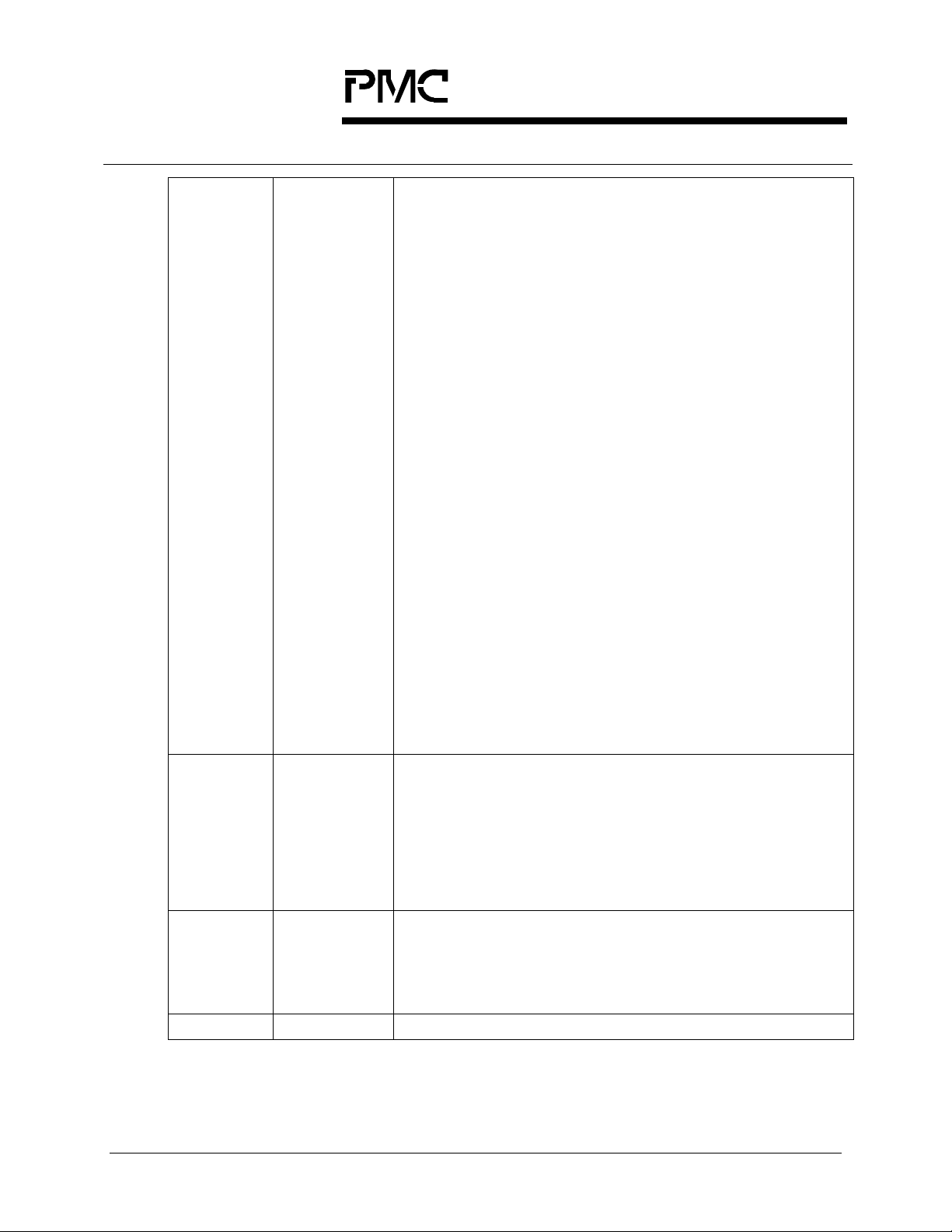

• ADD DLL does not exist

• Clarified description of SSTB/SPTB write trigger

register

• Revised TTOH, TTOHEN set-up time

• Clarified SENB bit description in register 0030

• Clarified bit DC1 description in register 00B4

• Clarified APGM/DPGM register information

• Clarified register 1102 description

• BIP calculation not supported by TPIP

• Added REFCLK required when generating

DS3ROCLK internally

• Added pin description for FPIN and TPL

• Revised RASE description and register definitions

• Revised bit 6 Path Reset description, register

0000

• Clarified Protection Switch Byte Failures detection

description

• Added updates based on preps

• Remove STS-6c/9c support

• Fix register bits definitions

• Fix Tx Ring Control Port definiton

• Remove B3 verification from ADD bus

• Revised Recommended BERM settings

Issue 3 July 1999

• Added FPPOS bit in register 0003

• Added Register 0016

• Added SCPII bit in register 000B

• Uncovered EXT bit in register 1151

• Added pin number

• Added boundary scan chain information

Issue 2 April 1999

• Removed DS-3 framers

• Block diagram updated

• TTOC and RTOC registers added

• Swapped RASE and SSTB register blocks

Issue 1 Sep 1998 Document created

PROPRIETARY AND CONFIDENTIAL iii

Page 5

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

CONTENTS

1 FEATURES.....................................................................................1

1.1 GENERAL............................................................................1

1.2 SONET SECTION AND LINE / SDH REGENERATOR

AND MULTIPLEXER SECTION...........................................2

1.3 SONET PATH / SDH HIGH ORDER PATH...........................3

1.4 SYSTEM SIDE INTERFACES..............................................4

2 APPLICATIONS ..............................................................................6

3 REFERENCES................................................................................7

4 DEFINITIONS................................................................................. 8

5 APPLICATION EXAMPLES ............................................................ 9

6 BLOCK DIAGRAM........................................................................14

7 LOOPBACK MODES....................................................................15

8 DESCRIPTION..............................................................................16

9 PIN DIAGRAMS............................................................................ 18

10 PIN DESCRIPTION (520).............................................................23

10.1 SERIAL LINE SIDE INTERFACE SIGNALS....................... 23

10.2 PARALLEL LINE SIDE INTERFACE SIGNALS.................. 26

10.3 RECEIVE AND TRANSMIT CLOCKS ................................31

10.4 SECTION/LINE STATUS AND ALARMS SIGNALS...........35

10.5 RECEIVE TRANSPORT OVERHEAD EXTRACTION

SIGNALS............................................................................ 42

10.6 TRANSMIT TRANSPORT OVERHEAD INSERTION

SIGNALS............................................................................ 49

PROPRIETARY AND CONFIDENTIAL iv

Page 6

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

10.7 RECEIVE PATH STATUS AND OVERHEAD SIGNAL ....... 57

10.8 TRANSMIT PATH OVERHEAD SIGNALS..........................63

10.9 DROP AND TRANSMIT P A TH AIS CONTROL

SIGNALS............................................................................ 66

10.10 DROP BUS INTERFACE CONFIGURATION..................... 69

10.11 DROP BUS TELECOM INTERFACE SIGNALS.................70

10.12 ADD BUS TELECOM INTERFACE SIGNALS....................81

10.13 DS3 SYSTEM SIDE INTERFACE...................................... 95

10.14 MICROPROCESSOR INTERFACE SIGNALS...................97

10.15 ANALOG MISCELLANEOUS SIGNALS .......................... 100

10.16 JTAG TEST ACCESS PORT (TAP) SIGNALS.................. 101

10.17 POWER AND GROUND...................................................102

11 FUNCTIONAL DESCRIPTION.................................................... 107

11.1 RECEIVE LINE INTERFACE............................................ 107

11.1.1 CLOCK RECOVERY UNIT.................................... 107

11.1.2 SERIAL TO PARALLEL CONVERTER.................. 109

11.2 RECEIVE SECTION OVERHEAD PROCESSOR

(RSOP)............................................................................. 109

11.3 RECEIVE SECTION TRACE BUFFER (SSTB).................110

11.4 RECEIVE LINE OVERHEAD PROCESSOR (RLOP)........ 111

11.5 RECEIVE TRANSPORT OVERHEAD CONTROLLER

(RTOC)..............................................................................113

11.6 RING CONTROL PORT....................................................113

11.7 RECEIVE PATH PROCESSING SLICE (RPPS)...............114

PROPRIETARY AND CONFIDENTIAL v

Page 7

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

11.7.1 RECEIVE PATH OVERHEAD PROCESSOR

(RPOP)...................................................................116

11.7.2 RECEIVE PATH TRACE BUFFER (SPTB)............ 122

1 1.7.3 RECEIVE TELECOMBUS ALIGNER (RTAL)......... 124

11.7.4 DS3 MAPPER DROP SIDE (D3MD) ..................... 129

11.7.5 DROP BUS PRBS GENERATOR AND

MONITOR (DPGM)................................................132

11.8 TRANSMIT PATH PROCESSING SLICE (TPPS)............ 134

11.8.1 ADD BUS PRBS GENERATOR AND

MONITOR (APGM)................................................ 136

11.8.2 DS3 MAPPER ADD SIDE (D3MA).........................136

11.8.3 TRANSMIT POINTER INTERPRETER

PROCESSOR (TPIP) ............................................ 138

1 1.8.4 TRANSMIT TELECOMBUS ALIGNER (TTAL) ......139

11.8.5 TRANSMIT PATH TRACE BUFFER (SPTB) ......... 140

11.8.6 T RANSMIT PATH OVERHEAD PROCESSOR

(TPOP) ..................................................................141

1 1.9 TRANSMIT TRANSPORT OVERHEAD

CONTROLLER (TTOC).................................................... 142

11.10 TRANSMIT LINE OVERHEAD PROCESSOR (TLOP).....144

11.11 TRANSMIT SECTION OVERHEAD PROCESSOR

(TSOP)............................................................................. 145

11.12 TRANSMIT SECTION TRACE BUFFER (SSTB)............. 145

11.13 TRANSMIT LINE INTERFACE.........................................146

11.13.1...................................................CLOCK SYNTHESIS 146

1 1. 13.2........................PARALLEL T O SERIAL CONVERTER 146

11.14 WAN SYNCHRONIZATION CONTROLLER (WANS) ......147

PROPRIETARY AND CONFIDENTIAL vi

Page 8

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

11.15 ADD/DROP BUS TIME-SLOT INTERCHANGE (TSI) ...... 150

11.16 SYSTEM SIDE INTERFACES..........................................151

11.16.1.......................................TELECOMBUS INTERFACE 151

11.16.2........................................... SERIAL DS3 INTERFACE 153

11.17 JTAG TEST ACCESS PORT INTERFACE....................... 153

11.18 MICROPROCESSOR INTERFACE ................................. 154

12 NORMAL MODE REGISTER DESCRIPTION ............................ 166

13 TEST FEATURES DESCRIPTION..............................................474

13.1 MASTER TEST AND TEST CONFIGURA TION

REGISTERS.....................................................................474

13.2 JT AG TEST PORT ...........................................................479

13.2.1BOUNDARY SCAN CELLS................................... 486

14 OPERATION...............................................................................489

14.1 SOFTWARE INITIALIZATION SEQUENCE.....................489

14.2 TRANSPORT AND PATH OVERHEAD BYTES............... 489

14.3 LINE CONFIGURATION OPTIONS ................................. 495

14.3.1 STS-12/12 C (STM-4/AU3/AU4/A U4-XC)

MODE.................................................................... 495

14.4 PATH PROCESSING SLICE CONFIGURATION

OPTIONS......................................................................... 495

14.4.1BASIC CONFIGURATION..................................... 495

14.4.2 ADDITIONAL CONFIGURATION FOR

TRANSMIT CONCATENATED STREAM

SUPPORT............................................................. 498

14.4.3 CONCATENATED AND NON-

CONCATENATED STREAMS DETECTION.......... 498

PROPRIETARY AND CONFIDENTIAL vii

Page 9

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

14.4.4 PRB S GENERATOR/MONITOR

CONFIGURATION FOR CONCATENATED

STREAMS............................................................. 499

14.5 TIME SLOT INTERCHANGE (GROOMING)

CONFIGURATION OPTIONS .......................................... 500

14.6 SYSTEM INTERFACE CONFIGURATION OPTIONS...... 501

14.6.1SINGLE 77.76 MHZ BYTE TELECOM BUS

MODE.................................................................... 501

14.6.2FOUR 19.44 MHZ BYTE TELECOM BUS

MODE.................................................................... 501

14.6.3SERIAL DS3 MODE..............................................502

14.6.4DROP BUS MODE................................................ 502

14.7 BIT ERROR RATE MONITOR.......................................... 503

14.8 CLOCKING OPTIONS ..................................................... 504

14.9 WAN SYNCHRONIZATION PARAMETERS.................... 505

14.9.1PLL GAIN...............................................................506

14.9.2PHASE COMPARATOR ........................................ 507

14.9.3PHASE SAMPLE AVERAGING.............................507

14.9.4IMPLEMENTATION EXAMPLE .............................508

14.10 LOOPBACK OPERATION................................................508

14.11 JTAG SUPPORT.............................................................. 509

14.11.1....................................................TAP CONTROLLER 511

14.11.2.......................................................................STATES 513

14.11.3......................................................... INSTRUCTIONS 514

14.12 BOARD DESIGN RECOMMENDATIONS........................515

14.13 POWER SUPPLIES......................................................... 516

PROPRIETARY AND CONFIDENTIAL viii

Page 10

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

14.14 INTERFACING TO ECL OR PECL DEVICES.................. 519

14.15 CLOCK RECOVERY........................................................ 521

15 FUNCTIONAL TIMING................................................................522

15.1 PARALLEL LINE INTERFACE.......................................... 522

15.2 RECEIVE TRANSPORT OVERHEAD EXTRACTION......525

15.2.1RECEIVE TRANSPORT OVERHEAD (RTOH)

FUNCTIONAL TIMING .......................................... 525

15.2.2 RECEIVE SECTION AND LINE DCC

FUNCTIONAL TIMING .......................................... 526

15.2.3 RECEIVE ORDER WIRE AND USER

CHANNEL FUNCTIONAL OUTPUT TIMING.........528

15.2.4 RE CEIVE OVERHEAD (ROH) FUNCTIONAL

OUTPUT TIMINGS................................................ 530

15.3 TRANSMIT TRANSPORT OVERHEAD INSERTION....... 532

15.3.1TRANSMIT TRANSPORT OVERHEAD

(TTOH) FUNCTIONAL TIMING ............................. 532

15.3.2 TRANSMIT SECTION AND LINE DCC

FUNCTIONAL TIMING .......................................... 533

15.3.3 TRANSMIT ORDER WIRE AND USER

CHANNEL FUNCTIONAL TIMING ........................ 536

15.3.4 TRANSMIT OVERHEAD (TOH) FUNCTIONAL

TIMING.................................................................. 537

15.4 PATH OVERHEAD EXTRACTION AND INSERTION ......540

15.5 MATE SPECTRA-622 INTERFACES............................... 544

15.6 TELECOM BUS SYSTEM SIDE....................................... 549

15.6.1DROP BUS............................................................549

15.6.2ADD BUS ............................................................... 556

PROPRIETARY AND CONFIDENTIAL ix

Page 11

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

15.7 DS3 MODE SYSTEM SIDE..............................................566

15.8 SYSTEM SIDE PATH AND DS3 AIS CONTROL

PORT ............................................................................... 567

16 ABSOLUTE MAXIMUM RATINGS.............................................. 570

17 D.C. CHARACTERISTICS.......................................................... 571

18 MICROPROCESSOR INTERFACE TIMING

CHARACTERISTICS..................................................................575

19 A.C. TIMING CHARACTERISTICS............................................. 582

19.1 SYSTEM RESET TIMING ................................................ 582

19.2 PARALLEL LINE INTERFACE TIMING............................583

19.3 SERIAL LINE INTERFACE TIMING ................................. 586

19.4 RECEIVE TIMING............................................................ 588

19.5 DROP BUS TIMING......................................................... 592

19.6 P A TH AIS INPUT TIMING................................................. 597

19.7 ADD BUS TIMING............................................................ 599

19.8 TRANSMIT TIMING..........................................................602

19.9 JT AG TIMING...................................................................608

20 ORDERING AND THERMAL INFORMATION............................. 610

21 MECHANICAL INFORMATION................................................... 612

PROPRIETARY AND CONFIDENTIAL x

Page 12

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

LIST OF REGISTERS

REGISTER 0000H: SPECTRA-622 RESET, IDENTITY AND

ACCUMULA TION TRIG GER...................................................... 167

REGISTER 0001H: SPECTRA-622 LINE ACTIVITY MONITOR ........... 169

REGISTER 0002H: SPECTRA-622 LINE CONFIGURATION #1 ..........171

REGISTER 0003H: SPECTRA-622 LINE CONFIGURATION #2 ..........174

REGISTER 0004H: SPECTRA-622 CLOCK CONTROL.......................176

REGISTER 0005H: SPECTRA-622 RECEIVE LINE AIS CONTROL ....178

REGISTER 0006H: SPECTRA-622 RING CONTROL ..........................180

REGISTER 0007H: SPECTRA-622 LINE RDI CONTROL.................... 182

REGISTER 0008H: SPECTRA-622 SECTION ALARM OUTPUT

CONTROL #1..............................................................................184

REGISTER 0009H: SPECTRA-622 SECTION ALARM OUTPUT

CONTROL #2..............................................................................186

REGISTER 000BH: SPECTRA-622 SECTION/LINE BLOCK

INTERRUPT STATUS................................................................. 187

REGISTER 000CH: SPECTRA-622 AUXILIARY SECTION/LINE

INTERRUPT ENABLE ................................................................189

REGISTER 000DH: SPECTRA-622 AUXILIARY SECTION/LINE

INTERRUPT STATUS................................................................. 191

REGISTER 000EH: SPECTRA-622 AUXILIARY SIGNAL

INTERRUPT ENABLE ................................................................193

REGISTER 000FH: SPECTRA-622 AUXILIARY SIGNAL

STATUS/INTERRUPT STATUS .................................................. 194

REGISTER 0010H: SPECTRA-622 PATH PROCESSING SLICE

INTERRUPT STATUS #1............................................................ 195

PROPRIETARY AND CONFIDENTIAL xi

Page 13

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

REGISTER 0011H: SPECTRA-622 PATH PROCESSING SLICE

INTERRUPT STATUS #2............................................................ 195

REGISTER 0012H: SPECTRA-622 PATH PROCESSING SLICE

INTERRUPT STATUS #3............................................................ 195

REGISTER 0013H: SPECTRA-622 TRANSMIT TELECOM BUS

CONFIGURATION...................................................................... 197

REGISTER 0014H: SPECTRA-622 SERIAL CONTROL PORT

ST A TUS AND CONTROL............................................................ 199

REGISTER 0015H: SPECTRA-622 SERIAL CONTROL PORT

INTERRUPT ENABLE ................................................................200

REGISTER 0016H: SPECTRA-622 SERIAL CONTROL PORT

INTERRUPT STATUS................................................................. 201

REGISTER 0030H: CRSI CONFIGURATION AND INTERRUPT.......... 202

REGISTER 0031H: CRSI STATUS........................................................ 204

REGISTER 0032H: CRSI CLOCK RECOVERY CONTROL .................. 206

REGISTER 0033H: CRSI CLOCK TRAINING CONFIGURATION ........ 207

REGISTER 0034H: RSOP CONTROL AND INTERRUPT ENABLE......208

REGISTER 0035H: RSOP STATUS AND INTERRUPT ........................ 210

REGISTER 0036H: RSOP SECTION BIP (B1) ERROR COUNT #1.....212

REGISTER 0040H: RLOP CONTROL AND STATUS............................ 213

REGISTER 0041H: RLOP INTERRUPT ENABLE AND STATUS..........216

REGISTER 0042H: RLOP LINE BIP (B2) ERROR COUNT #1 ............. 218

REGISTER 0045H: RLOP REI ERROR COUNT #1.............................. 220

REGISTER 0050H: SSTB SECTION TRACE CONTROL..................... 222

REGISTER 0051H: SSTB SECTION TRACE STATUS......................... 225

REGISTER 0052H: SSTB SECTION TRACE INDIRECT ADDRESS.... 227

PROPRIETARY AND CONFIDENTIAL xii

Page 14

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

REGISTER 0053H: SSTB SECTION TRACE INDIRECT DATA............228

REGISTER 0056H: SSTB SECTION TRACE OPERATION..................229

REGISTER 0060H: RASE INTERRUPT ENABLE................................. 230

REGISTER 0061H: RASE INTERRUPT STATUS ................................. 231

REGISTER 0062H: RASE CONFIGURATION/CONTROL....................233

REGISTER 0063H: RASE SF ACCUMULATION PERIOD.................... 235

REGISTER 0066H: RASE SF SATURATION THRESHOLD.................237

REGISTER 0068H: RASE SF DECLARING THRESHOLD................... 238

REGISTER 006AH: RASE SF CLEARING THRESHOLD..................... 239

REGISTER 006CH: RASE SD ACCUMULATION PERIOD................... 240

REGISTER 006FH: RASE SD SATURATION THRESHOLD.................242

REGISTER 0071H: RASE SD DECLARING THRESHOLD.................. 243

REGISTER 0073H: RASE SD CLEARING THRESHOLD..................... 244

REGISTER 0075H: RASE RECEIVE K1...............................................245

REGISTER 0076H: RASE RECEIVE K2...............................................246

REGISTER 0077H: RASE RECEIVE Z1/S1.......................................... 247

REGISTER 0080H: WANS CONFIGURATION......................................248

REGISTER 0081H: WANS INTERRUPT AND STATUS........................ 249

REGISTER 0082H: WANS PHASE WORD LSB................................... 250

REGISTER 0089H: WANS REFERENCE PERIOD LSB....................... 252

REGISTER 008BH: WANS PHASE COUNTER PERIOD LSB.............. 253

REGISTER 008DH: WANS PHASE AVERAGE PERIOD...................... 254

REGISTER 0090H: RTOC OVERHEAD CONTROL.............................255

PROPRIETARY AND CONFIDENTIAL xiii

Page 15

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

REGISTER 0091H: RTOC AIS CONTROL............................................257

REGISTER 00A2H: TRANSMIT DLL RESET REGISTER..................... 258

REGISTER 00A3H: TRANSMIT DLL CONTROL STATUS....................258

REGISTER 00A4H: DROP BUS DLL CONFIGURATION...................... 259

REGISTER 00A6H: DROP BUS DLL RESET REGISTER.................... 261

REGISTER 00A7H: DROP BUS DLL CONTROL STATUS....................262

REGISTER 00B0H: CSPI CONFIGURATION .......................................264

REGISTER 00B1H: CSPI STATUS........................................................265

REGISTER 00B4H: TSOP CONTROL .................................................. 266

REGISTER 00B5H: TSOP DIAGNOSTIC.............................................. 267

REGISTER 00B8H: TLOP CONTROL................................................... 268

REGISTER 00B9H: TLOP DIAGNOSTIC.............................................. 269

REGISTER 00BAH: TLOP TRANSMIT K1............................................ 270

REGISTER 00BBH: TLOP TRANSMIT K2............................................ 271

REGISTER 00C0H: TTOC TRANSMIT OVERHEAD OUTPUT

CONTROL .................................................................................. 272

REGISTER 00C1H: TT OC TRANSMIT OVERHEAD BYTE

CONTROL .................................................................................. 274

REGISTER 00C2H: TTOC TRANSMIT Z0 ............................................ 277

REGISTER 00C3H: TTOC TRANSMIT S1............................................ 278

REGISTER 0100H: SPECTRA-622 RPPS CONFIGURATION .............279

REGISTER 0102H: SPECTRA-622 RPPS PATH AND DS3

CONFIGURATION...................................................................... 281

REGISTER 0110H: SPECTRA-622 RPPS PATH/DS3 AIS

CONTROL #1..............................................................................283

PROPRIETARY AND CONFIDENTIAL xiv

Page 16

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

REGISTER 0111H: SPECTRA-622 RPPS PATH/DS3 AIS

CONTROL #2..............................................................................285

REGISTER 0114H: SPECTRA-622 RPPS PATH REI/RDI

CONTROL #1..............................................................................287

REGISTER 0115H: SPECTRA-622 RPPS PATH REI/RDI

CONTROL #2..............................................................................289

REGISTER 0118H: SPECTRA-622 RPPS PATH ENHANCED RDI

CONTROL #1..............................................................................291

REGISTER 0119H: SPECTRA-622 RPPS PATH ENHANCED RDI

CONTROL #2..............................................................................294

REGISTER 011CH: SPECTRA-622 RPPS RALM OUTPUT

CONTROL #1..............................................................................296

REGISTER 011DH: SPECTRA-622 RPPS RALM OUTPUT

CONTROL #2..............................................................................298

REGISTER 0128H: SPECTRA-622 RPPS PATH/DS3 INTERRUPT

STATUS ...................................................................................... 300

REGISTER 012CH: SPECTRA-622 RPPS AUXILIARY PATH

INTERRUPT ENABLE #1 ...........................................................302

REGISTER 012DH: SPECTRA-622 RPPS AUXILIARY PATH

INTERRUPT ENABLE #2 ...........................................................304

REGISTER 0130H: SPECTRA-622 RPPS AUXILIARY PATH

INTERRUPT STATUS #1............................................................ 306

REGISTER 0131H: SPECTRA-622 RPPS AUXILIARY PATH

INTERRUPT STATUS #2............................................................ 308

REGISTER 0134H: SPECTRA-622 RPPS AUXILIARY PATH

STATUS ...................................................................................... 310

REGISTER 0150H: RPOP STATUS AND CONTROL (EXTD=0)............311

REGISTER 0150H: RPOP STATUS AND CONTROL (EXTD=1)........... 313

REGISTER 0151H: RPOP ALARM INTERRUPT STATUS

(EXTD=0).................................................................................... 314

PROPRIETARY AND CONFIDENTIAL xv

Page 17

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

REGISTER 0151H: RPOP ALARM INTERRUPT STATUS

(EXTD=1).................................................................................... 316

REGISTER 0152H: RPOP POINTER INTERRUPT STATUS................ 317

REGISTER 0153H: RPOP ALARM INTERRUPT ENABLE

(EXTD=0).................................................................................... 319

REGISTER 0153H: RPOP ALARM INTERRUPT ENABLE

(EXTD=1).................................................................................... 321

REGISTER 0154H: RPOP POINTER INTERRUPT ENABLE ............... 322

REGISTER 0155H: RPOP POINTER LSB............................................ 324

REGISTER 0156H: RPOP POINTER MSB........................................... 325

REGISTER 0157H: RPOP PATH SIGNAL LABEL................................. 327

REGISTER 0158H: RPOP PATH BIP-8 LSB.........................................328

REGISTER 015AH: RPOP PATH REI LSB............................................ 329

REGISTER 015CH: RPOP TRIBUTARY MULTIFRAME STATUS

AND CONTROL..........................................................................330

REGISTER 015DH: RPOP RING CONTROL........................................ 332

REGISTER 0174H: PMON RECEIVE POSITIVE POINTER

JUSTIFICATION COUNT............................................................ 334

REGISTER 0175H: PMON RECEIVE NEGATIVE POINTER

JUSTIFICATION COUNT............................................................ 335

REGISTER 0176H: PMON TRANSMIT POSITIVE POINTER

JUSTIFICATION COUNT............................................................ 336

REGISTER 0177H: PMON TRANSMIT NEGATIVE POINTER

JUSTIFICATION COUNT............................................................ 337

REGISTER 0180H: RTAL CONTROL.................................................... 338

REGISTER 0181H: RTAL INTERRUPT STATUS AND CONTROL ....... 340

REGISTER 0182H: RTAL ALARM AND DIAGNOSTIC CONTROL.......343

PROPRIETARY AND CONFIDENTIAL xvi

Page 18

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

REGISTER 0190H: SPTB CONTROL................................................... 345

REGISTER 0191H: SPTB PATH TRACE IDENTIFIER STATUS........... 348

REGISTER 0192H: SPTB INDIRECT ADDRESS REGISTER .............. 350

REGISTER 0193H: SPTB INDIRECT DATA REGISTER....................... 351

REGISTER 0194H: SPTB EXPECTED PATH SIGNAL LABEL.............352

REGISTER 0195H: SPTB PATH SIGNA L LABEL CONTROL AND

STATUS: .....................................................................................353

REGISTER 0196H: SPTB PATH TRACE OPERATION......................... 355

REGISTER 01B0H: D3MD CONTROL.................................................. 356

REGISTER 01B1H: D3MD INTERRUPT STATUS................................ 357

REGISTER 01B2H: D3MD INTERRUPT ENABLE................................358

REGISTER 01D0H: DPGM GENERATOR CONTROL #1..................... 359

REGISTER 01D1H: DPGM GENERATOR CONTROL #2..................... 361

REGISTER 01D2H: DPGM GENERATOR CONCATENATE

CONTROL .................................................................................. 362

REGISTER 01D3H: DPGM GENERATOR STATUS..............................364

REGISTER 01D8H: DPGM MONITOR CONTROL #1 .......................... 365

REGISTER 01D9H: DPGM MONITOR CONTROL #2 .......................... 367

REGISTER 01DAH: DPGM MONITOR CONCATENATE

CONTROL .................................................................................. 368

REGISTER 01DBH: DPGM MONITOR STATUS................................... 370

REGISTER 01DCH: DPGM MONITOR ERROR COUNT #1................. 372

REGISTER 0D01H: SPECTRA-622 DROP BUS STM-1 #1 AU3 #1

SELECT...................................................................................... 373

REGISTER 0D02H: SPECTRA-622 DROP BUS STM-1 #2 AU3 #1

SELECT...................................................................................... 374

PROPRIETARY AND CONFIDENTIAL xvii

Page 19

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

REGISTER 0D03H: SPECTRA-622 DROP BUS STM-1 #3 AU3 #1

SELECT...................................................................................... 375

REGISTER 0D04H: SPECTRA-622 DROP BUS STM-1 #4 AU3 #1

SELECT...................................................................................... 376

REGISTER 0D05H: SPECTRA-622 DROP BUS STM-1 #1 AU3 #2

SELECT...................................................................................... 377

REGISTER 0D06H: SPECTRA-622 DROP BUS STM-1 #2 AU3 #2

SELECT...................................................................................... 378

REGISTER 0D07H: SPECTRA-622 DROP BUS STM-1 #3 AU3 #2

SELECT...................................................................................... 379

REGISTER 0D08H: SPECTRA-622 DROP BUS STM-1 #4 AU3 #2

SELECT...................................................................................... 380

REGISTER 0D09H: SPECTRA-622 DROP BUS STM-1 #1 AU3 #3

SELECT...................................................................................... 381

REGISTER 0D0AH: SPECTRA-622 DROP BUS STM-1 #2 AU3 #3

SELECT...................................................................................... 382

REGISTER 0D0BH: SPECTRA-622 DROP BUS STM-1 #3 AU3 #3

SELECT...................................................................................... 383

REGISTER 0D0CH: SPECTRA-622 DROP BUS STM-1 #4 AU3 #3

SELECT...................................................................................... 384

REGISTER 0D30H: SPECTRA-622 DROP BUS CONFIGURATION.... 385

REGISTER 1030H: SPECTRA-622 ADD BUS CONFIGURATION........387

REGISTER 1032H: SPECTRA-622 ADD BUS PARITY

INTERRUPT ENABLE ................................................................390

REGISTER 1034H: SPECTRA-622 ADD BUS PARITY

INTERRUPT STATUS................................................................. 391

REGISTER 1036H: SPECTRA-622 SYSTEM SIDE CLOCK

ACTIVITY MONITOR.................................................................. 392

REGISTER 1037H: SPECTRA-622 ADD BUS SIGNAL ACTIVITY

MONITOR................................................................................... 393

PROPRIETARY AND CONFIDENTIAL xviii

Page 20

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

REGISTER 1061H: SPECTRA-622 ADD BUS STM-1 #1 AU3 #1

SELECT...................................................................................... 394

REGISTER 1062H: SPECTRA-622 ADD BUS STM-1 #2 AU3 #1

SELECT...................................................................................... 395

REGISTER 1063H: SPECTRA-622 ADD BUS STM-1 #3 AU3 #1

SELECT...................................................................................... 396

REGISTER 1064H: SPECTRA-622 ADD BUS STM-1 #4 AU3 #1

SELECT...................................................................................... 397

REGISTER 1065H: SPECTRA-622 ADD BUS STM-1 #1 AU3 #2

SELECT...................................................................................... 398

REGISTER 1066H: SPECTRA-622 ADD BUS STM-1 #2 AU3 #2

SELECT...................................................................................... 399

REGISTER 1067H: SPECTRA-622 ADD BUS STM-1 #3 AU3 #2

SELECT...................................................................................... 400

REGISTER 1068H: SPECTRA-622 ADD BUS STM-1 #4 AU3 #2

SELECT...................................................................................... 401

REGISTER 1069H: SPECTRA-622 ADD BUS STM-1 #1 AU3 #3

SELECT...................................................................................... 402

REGISTER 106AH: SPECTRA-622 ADD BUS STM-1 #2 AU3 #3

SELECT...................................................................................... 403

REGISTER 106BH: SPECTRA-622 ADD BUS STM-1 #3 AU3 #3

SELECT...................................................................................... 404

REGISTER 106CH: SPECTRA-622 ADD BUS STM-1 #4 AU3 #3

SELECT...................................................................................... 405

REGISTER 1100H: SPECTRA-622 TPPS CONFIGURATION.............. 406

REGISTER 1102H: SPECTRA-622 TPPS PATH AND DS3

CONFIGURATION...................................................................... 409

REGISTER 1106H: SPECTRA-622 TPPS PATH TRANSMIT

CONTROL ...................................................................................411

PROPRIETARY AND CONFIDENTIAL xix

Page 21

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

REGISTER 1108H: SPECTRA-622 TPPS DS3 ACTIVITY

MONITOR................................................................................... 413

REGISTER 1110H: SPECTRA-622 TPPS PATH AIS CONTROL.......... 414

REGISTER 1128H: SPECTRA-622 TPPS PATH/DS3 INTERRUPT

STATUS ...................................................................................... 416

REGISTER 112CH: SPECTRA-622 TPPS AUXILIARY PATH

INTERRUPT ENABLE ................................................................418

REGISTER 1130H: SPECTRA-622 TPPS AUXILIARY PATH

INTERRUPT STATUS................................................................. 420

REGISTER 1150H: TPOP CONTROL...................................................422

REGISTER 1151H: TPOP POINTER CONTROL.................................. 424

REGISTER 1153H: TPOP CURRENT POINTER LSB...........................425

REGISTER 1155H: TPOP PAYLOAD POINTER LSB............................ 426

REGISTER 1157H: TPOP PATH TRACE...............................................427

REGISTER 1158H: TPOP PATH SIGNAL LABEL ................................. 428

REGISTER 1159H: TPOP PATH STATUS............................................. 429

REGISTER 115AH: TPOP PATH USER CHANNEL.............................. 431

REGISTER 115BH: TPOP PATH GROWTH #1.....................................432

REGISTER 115CH: TPOP PATH GROWTH #2..................................... 433

REGISTER 115DH: TPOP TANDEM CONNECTION

MAINTENANCE..........................................................................434

REGISTER 1180H: TTAL CONTROL .................................................... 435

REGISTER 1181H: TTAL INTERRUPT STATUS AND CONTROL........ 437

REGISTER 1182H: TTAL ALARM AND DIAGNOSTIC CONTROL........ 439

REGISTER 1190H: TPIP STATUS AND CONTROL (EXTD=0).............441

REGISTER 1190H: TPIP STATUS AND CONTROL (EXTD=1).............443

PROPRIETARY AND CONFIDENTIAL xx

Page 22

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

REGISTER 1191H: TPIP ALARM INTERRUPT STATUS (EXTD=0) .....444

REGISTER 1192H: TPIP POINTER INTERRUPT STATUS................... 446

REGISTER 1193H: TPIP ALARM INTERRUPT ENABLE (EXTD=0)..... 448

REGISTER 1194H: TPIP INTERRUPT ENABLE................................... 450

REGISTER 1195H: TPIP POINTER LSB...............................................452

REGISTER 1196H: TPIP POINTER MSB..............................................453

REGISTER 119CH: TPIP TRIBUTARY MULTIFRAME STATUS

AND CONTROL..........................................................................455

REGISTER 11B0H: D3MA CONTROL................................................... 457

REGISTER 11B1H: D3MA INTERRUPT STATUS.................................458

REGISTER 11B2H: D3MA INTERRUPT ENABLE.................................459

REGISTER 11D0H: APGM GENERATOR CONTROL #1......................460

REGISTER 11D1H: APGM GENERATOR CONTROL #2......................462

REGISTER 11D2H: APGM GENERATOR CONCATENATE

CONTROL .................................................................................. 463

REGISTER 11D3H: APGM GENERATOR STATUS .............................. 465

REGISTER 11D8H: APGM MONITOR CONTROL #1........................... 466

REGISTER 11D9H: APGM MONITOR CONTROL #2........................... 468

REGISTER 11DAH: APGM MONITOR CONCATENATE CONTROL.... 469

REGISTER 11DBH: APGM MONITOR STATUS ................................... 471

REGISTER 11DCH: APGM MONITOR ERROR COUNT #1 ................. 473

REGISTER ADDRESS 2000H: MASTER TEST....................................475

REGISTER ADDRESS 2001H: RX ANALOG TEST REGISTER........... 477

REGISTER ADDR ESS 2002H: TX ANAL OG TEST REGISTER........... 478

PROPRIETARY AND CONFIDENTIAL xxi

Page 23

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

REGISTER ADDRESS 2003H: MASTER TEST SLICE SELECT..........479

PROPRIETARY AND CONFIDENTIAL xxii

Page 24

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

LIST OF TABLES

TABLE 1 PATH SIGNAL LABEL MATCH/MISMATCH STATE

TABLE. .......................................................................... 123

TABLE 2 PSL MODE 2 MATCH, MISMATCH AND UNEQUIPPED......124

TABLE 3 - ASYNCHRONOUS DS3 MAPPING TO STS-1 (STM-

0/AU3). ..........................................................................129

TABLE 4 - DS3 AIS FORMAT. .............................................................. 130

TABLE 5 - DS3 DESYNCHRONIZER CLOCK GAPPING

ALGORITHM. ................................................................ 132

TABLE 6 - DS3 SYNCHRONIZER BIT STUFFING ALGORITHM.........138

TABLE 7 -COLUMNS AND STS-1 (STM-0/AU3) STREAMS

ASSOCIATION. .............................................................150

TABLE 8 - SYSTEM SIDE ADD BUS CONFIGURATION OPTIONS.... 152

TABLE 9 - SYSTEM SIDE DROP BUS CONFIGURATION

OPTIONS ...................................................................... 153

TABLE 10-REGISTER MEMORY MAP ................................................. 154

TABLE 11- RECEIVE ESD[1:0] CODEPOINTS.....................................341

TABLE 12- RXSEL[1:0] CODEPOINTS FOR STS-1 AND STS-NC....... 407

TABLE 13-TRANSMIT RDI CONTROL..................................................429

TABLE 14- TRANSMIT ESD[1:0] CODEPOINTS. .................................438

TABLE 15-TEST MODE REGISTER MEMORY MAP............................ 474

TABLE 16- MASTER TEST SLICE SELECT, SLICE_SEL[3:0]

CODE-POINTS.............................................................. 479

TABLE 17-INSTRUCTION REGISTER (LENGTH - 3 BITS)..................480

TABLE 18-IDENTIFICATION REGISTER.............................................. 480

TABLE 19-BOUNDARY SCAN REGISTER LENGTH - 277 BITS.......... 480

PROPRIETARY AND CONFIDENTIAL xxiii

Page 25

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

TABLE 20- SLICE CONFIGURATION FOR SDH STM-4 PATH

PROCESSING............................................................... 496

TABLE 21- SLICE CONFIGURATION FOR SONET STS-12/12C

PATH PROCESSING.....................................................497

TABLE 22- VALID MASTER/SLAVE SLICE CONFIGURATIONS.......... 498

TABLE 23-TELECOM BUS STS-1 (STM-0/AU3) TIME-SLOTS

(STREAMS)................................................................... 500

TABLE 24-RECOMMENDED BERM SETTINGS ..................................504

TABLE 25-ABSOLUTE MAXIMUM RATINGS .......................................570

TABLE 26-D.C CHARACTERISTICS .................................................... 571

TABLE 27- MICROPROCESSOR INTERFACE READ ACCESS.......... 575

TABLE 28- MICROPROCESSOR INTERFACE WRITE ACCESS.........579

TABLE 29-RSTB TIMING ...................................................................... 582

TABLE 30-TRANSMIT PARALLEL LINE INTERFACE TIMING............. 583

TABLE 31-RECEIVE PARALLEL LINE INTERFACE TIMING................ 585

TABLE 32- RECEIVE LINE SIDE INTERFACE TIMING........................ 586

TABLE 33- RECEIVE LINE INPUT INTERFACE TIMING......................586

TABLE 34- RECEIVE LINE OUTPUT TIMING....................................... 588

TABLE 35- RECEIVE PATH OVERHEAD AND ALARM PORT

OUTPUT TIMING .......................................................... 590

TABLE 36- RECEIVE RING CONTROL PORT OUTPUT TIMING......... 592

TABLE 38- TELECOM DROP BUS INPUT TIMING...............................592

TABLE 39- TELECOM DROP BUS OUTPUT TIMING AT 77.76

MHZ DCK...................................................................... 594

TABLE 40- TELECOM DROP BUS OUTPUT TIMING AT 19.44

MHZ DCK...................................................................... 594

PROPRIETARY AND CONFIDENTIAL xxiv

Page 26

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

TABLE 41- DS3 DROP INTERFACE INPUT TIMING............................ 596

TABLE 42- DS3 DROP INTERFACE OUTPUT TIMING........................ 596

TABLE 43- SYSTEM DROP-SIDE PATH ALARM INPUT TIMING.........597

TABLE 44- SYSTEM ADD-SIDE PATH ALARM INPUT TIMING............ 598

TABLE 45- TELECOM ADD BUS INPUT TIMING................................. 599

TABLE 46- DS3 ADD INTERFACE INPUT TIMING...............................601

TABLE 47- TRANSMIT PATH OVERHEAD INPUT TIMING.................. 602

TABLE 48- TRANSMIT ALARM PORT INPUT TIMING......................... 603

TABLE 49- TRANSMIT TRANSPORT OVERHEAD INPUT TIMING ..... 604

TABLE 50- TRANSMIT RING CONTROL PORT INPUT TIMING.......... 606

TABLE 51- TRANSMIT OVERHEAD OUTPUT TIMING........................ 607

TABLE 52- JTAG PORT INTERFACE.................................................... 608

TABLE 53- ORDERING INFORMATION ............................................... 610

TABLE 54- THERMAL INFORMATION – THETA JC ............................. 610

TABLE 55- MAXIMUM JUNCTION TEMPERATURE ............................ 610

TABLE 56- THERMAL INFORMATION – THETA JA VS. AIRFLOW...... 610

PROPRIETARY AND CONFIDENTIAL xxv

Page 27

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

LIST OF FIGURES

FIGURE 1 -STS-12 (STM-4/AU-3), STS-12 (STM-4/AU-4) OR

STS-12C (STM-4-4C) APPLICATION WITH 19.44

MHZ BYTE TELECOMBUS INTERFACE.......................... 9

FIGURE 2 -STS-12 (STM-4/AU-3), STS-12 (STM-4/AU-4) OR

STS-12C (STM-4-4C) APPLICATION WITH 77.76

MHZ BYTE TELECOMBUS INTERFACE........................ 10

FIGURE 3 -STS-48 (STM-16) APPLICATION................................... 11

FIGURE 4 -OC-12 CHANNELISED DS-3 INTERFACE FOR

HIGH SPEED IP SWITCHES/ROUTERS........................ 12

FIGURE 5 -MULT I-SERVICE CHANNELISED OC-12

AGGREGATE INTERFACE FOR HIGH SPEED IP

SWITCHES/ROUTERS...................................................13

FIGURE 6 -FULL VIEW OF SPECTRA-622 DIAGRAM.................... 18

FIGURE 7 -SECTION VIEW OF SPECTRA-622 PIN

DIAGRAM, A1-T17.......................................................... 19

FIGURE 8 -SECTION VIEW OF SPECTRA-622 PIN

DIAGRAM, U1-AL17 ........................................................ 20

FIGURE 9 -SECTION VIEW OF SPECTRA-622 PIN

DIAGRAM, AL18-U31...................................................... 21

FIGURE 10 -SECTION VIEW OF SPECTRA-622 PIN

DIAGRAM, A31-T31........................................................ 22

FIGURE 11 - SPECTRA-622 TYPICAL JITTER TOLERANCE AT

622 MBIT/S.................................................................... 108

FIGURE 12 - POINTER INTERPRETATION STATE DIAGRAM........117

FIGURE 13 - POINTER GENERATION STATE DIAGRAM .............. 127

FIGURE 14 -PHASE COMPARATOR BLOCK DIAGRAM ................ 147

FIGURE 15 -PHASE AVERAGER BLOCK DIAGRAM...................... 149

PROPRIETARY AND CONFIDENTIAL xxvi

Page 28

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

FIGURE 16 -PATH PROCESSING SLICES AND ORDER OF

TRANSMISSION ........................................................... 165

FIGURE 17 -INPUT OBSERVATION CELL (IN_CELL)..................... 487

FIGURE 18 -OUTPUT CELL (OUT_CELL ........................................487

FIGURE 19 -BI-DIRECTIONAL CELL (IO_CELL)............................. 488

FIGURE 20 -CONCEPTUAL CLOCKING STRUCTURE .................. 504

FIGURE 25. DIGITAL PLL BLOCK DIAGRAM.......................................506

FIGURE 26 -BOUNDARY SCAN ARCHITECTURE..........................510

FIGURE 27 -TAP CONTROLLER FINITE STATE MACHINE............ 512

FIGURE 28 -ANALOG POWER SUPPLY FILTERING...................... 517

FIGURE 29 -INTERFACING SPECTRA-622 PECL PINS TO

3.3V DEVICES .............................................................. 520

FIGURE 30 -INTERFACING SPECTRA-622 PECL PINS TO

5.0V DEVICES .............................................................. 520

FIGURE 32 -IN FRAME DECLARATION TIMING.............................522

FIGURE 33 -OUT OF FRAME DECLARATION TIMING................... 522

FIGURE 34 -STS-12 (STM-4/AU3) TRANSMIT TELECOM BUS

TIMING.......................................................................... 523

FIGURE 35 -STS-12C (STM-4-4C) TRANSMIT TELECOM BUS

TIMING.......................................................................... 524

FIGURE 36 -RECEIVE TRANPORT OVERHEAD EXTRACTION.... 525

FIGURE 37 -RX SECTION/LINE AND LINE DCC TIMING

(RX_GAPSEL=0)...........................................................526

FIGURE 38 -RX LINE DCC TIMING (RX_GAPSEL=0)..................... 526

FIGURE 39 -RX SECTION DCC TIMING (RX_GAPSEL=0).............527

FIGURE 40 -RX SECTION/LINE AND LINE DCC TIMING

(RX_GAPSEL=1)...........................................................527

PROPRIETARY AND CONFIDENTIAL xxvii

Page 29

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

FIGURE 41 -RX ORDER WIRE AND USER CHANNEL TIMING

(RX_GAPSEL=0)...........................................................528

FIGURE 42 -RSOW, RLOW AND RSUC ALIGNMENT W.R.T.

RTOHFP (RX_GAPSEL=0) ........................................... 529

FIGURE 43 -RX ORDER WIRE AND USER CHANNEL TIMING

(RX_GAPSEL=1)...........................................................529

FIGURE 44 -RECEIVE OVERHEAD OUTPUT FUNCTIONAL

TIMING (RX_GAPSEL=0)............................................. 530

FIGURE 45 -RECEIVE OVERHEAD OUTPUT FUNCTIONAL

TIMING (RX_GAPSEL=1)............................................. 530

FIGURE 46 -TRANSMIT TRANSPORT OVERHEAD

INSERTION................................................................... 532

FIGURE 47 -TX SECTION/LINE AND LINE DCC TIMING

(TX_GAPSEL=0)...........................................................533

FIGURE 48 -TX LINE DCC OUTPUT TIMING (TX_GAPSEL=0)......534

FIGURE 49 -TX SECTION DCC OUTPUT TIMING

(TX_GAPSEL=0)...........................................................534

FIGURE 50 -TX SECTION/LINE AND LINE DCC TIMING

(TX_GAPSEL=1)...........................................................535

FIGURE 51 -TRANSMIT ORDER WIRE AND USER CHANNEL

TIMING (TX_GAPSEL=0).............................................. 536

FIGURE 52 -TSOW, TLOW AND TSUC ALIGNMENT W. R.T

TTOHFP (TX_GAPSEL=0)............................................536

FIGURE 53 -TRANSMIT ORDER WIRE AND USER CHANNEL

TIMING (TX_GAPSEL=1).............................................. 537

FIGURE 54 -TRANSMIT OVERHEAD FUNCTIONAL TIMING

(TX_GAPSEL=0)...........................................................537

FIGURE 55 -TRANSMIT OVERHEAD FUNCTIONAL TIMING

(TX_GAPSEL=1)...........................................................538

PROPRIETARY AND CONFIDENTIAL xxviii

Page 30

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

FIGURE 56 - RECEIVE PATH OVERHEAD

EXTRACTION/ALARM TIMING..................................... 540

FIGURE 58 -TRANSMIT PATH OVERHEAD INSERTION

TIMING.......................................................................... 542

FIGURE 59 -RECEIVE RING CONTROL PORT...............................544

FIGURE 60 - RECEIVE PATH ALARM PORT TIMING..................... 545

FIGURE 61 - TRANSMIT RING CONTROL PORT........................... 547

FIGURE 62 - TRANSMIT ALARM PORT TIMING ............................. 548

FIGURE 63 - STS-3 (STM-1/AU3) 1 9.44 MHZ BYTE DROP BUS

TIMING.......................................................................... 549

FIGURE 64 - STS-3C (STM-1/AU4) 19.44 MHZ BYTE DROP

BUS TIMING..................................................................550

FIGURE 65 - STS-12C (STM-4-4 C) 19.44 MHZ BYTE DROP

BUS TIMING..................................................................552

FIGURE 66 - STS-12 (STM-4/AU3) 77.76 MHZ BYTE DRO P

BUS TIMING..................................................................554

FIGURE 67 - STS-12C (STM-4-4 C) 77.76 MHZ BYTE DROP

BUS TIMING..................................................................555

FIGURE 68 - STS-3 (STM-1/AU3) 1 9.44 MHZ BYTE ADD BUS

TIMING.......................................................................... 556

FIGURE 69 - STS-3 (STM-1/AU3) 1 9.44 MHZ BYTE ADD BUS

(AFP) TIMING................................................................557

FIGURE 70 - STS-3C (STM-1/AU4) 19.44 MHZ BYTE ADD BUS

TIMING.......................................................................... 558

FIGURE 71 - STS-3C (STM-1/AU4) 19.44 MHZ BYTE ADD BUS

(AFP) TIMING................................................................559

FIGURE 72 - STS-12C (STM-4-4C) 19.44 MHZ BYTE ADD BUS

TIMING.......................................................................... 560

FIGURE 73 -STS-12C (STM-4-4 C) 19.44 MHZ BYTE ADD BUS

(AFP) TIMING................................................................561

PROPRIETARY AND CONFIDENTIAL xxix

Page 31

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

FIGURE 74 - STS-12 (STM-12/AU3) 77.76 MHZ BYTE ADD

BUS TIMING..................................................................562

FIGURE 75 - STS-12 (STM-12/AU3) 77.76 MHZ BYTE ADD

BUS (AFP) TIMING ....................................................... 563

FIGURE 76 - STS-12C (STM-4-4C) 77.76 MHZ BYTE ADD BUS

TIMING.......................................................................... 564

FIGURE 77 - STS-12C (STM-4-4C) 77.76 MHZ BYTE ADD BUS

(AFP) TIMING................................................................565

FIGURE 78 - STS-1 (STM-0/AU3) DS3 DROP INTERFACE

TIMING.......................................................................... 566

FIGURE 79 - STS-1 (STM-0/AU3) DS3 ADD INTERFACE

TIMING.......................................................................... 566

FIGURE 80 - SYSTEM DROP SIDE PATH/DS3 AIS CONTROL

PORT TIMING...............................................................567

FIGURE 81 - SYSTEM ADD SIDE PATH/DS3 AIS CONTROL

PORT TIMING...............................................................568

FIGURE 82 - MICROPROCESSOR INTERFACE READ

ACCESS TIMING (INTEL MODE) ................................. 576

FIGURE 83 - MICROPROCESSOR INTERFACE READ

ACCESS TIMING (MOTOROLA MODE)....................... 577

FIGURE 84 - MICROPROCESSOR INTERFACE WRITE

ACCESS TIMING (INTEL MODE) ................................. 579

FIGURE 85 - MICROPROCESSOR INTERFACE WRITE

ACCESS TIMING (MOTOROLA MODE)....................... 580

FIGURE 86 -RSTB TIMING DIAGRAM.............................................582

FIGURE 87 -TRANSMIT PARALLEL LINE INTERFACE TIMING

DIAGRAM...................................................................... 584

FIGURE 88 -RECEIVE PARALLEL LINE INTERFACE TIMING

DIAGRAM...................................................................... 585

FIGURE 89 - RECEIVE SERIAL LINE SIDE TIMING....................... 586

PROPRIETARY AND CONFIDENTIAL xxx

Page 32

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

FIGURE 90 - SERIAL TRANSMIT INTERFACE TFPI TIMING..........587

FIGURE 91 - RECEIVE LINE OUTPUT TIMING............................... 589

FIGURE 92 - RECEIVE PATH OVERHEAD AND ALARM PORT

OUTPUT TIMING .......................................................... 591

FIGURE 93 - RING CONTROL PORT OUTPUT TIMING ................. 592

FIGURE 95 - TELECOM DROP BUS INPUT TIMING ...................... 593

FIGURE 96 - TELECOM DROP BUS OUTPUT TIMING...................595

FIGURE 97 - DS3 DROP INTERFACE OUTPUT TIMING................596

FIGURE 98 - SYSTEM DROP-SIDE PATH ALARM INPUT

TIMING.......................................................................... 597

FIGURE 99 - SYSTEM ADD-SIDE PATH ALARM INPUT TIMING.... 598

FIGURE 100 - TELECOM ADD BUS INPUT TIMING ......................... 600

FIGURE 101 - DS3 ADD INTERFACE INPUT TIMING

(INTERNAL DS3 FRAMER)...........................................601

FIGURE 102 - TRANSMIT PATH OVERHEAD INPUT TIMING.......... 602

FIGURE 103 - TRANSMIT ALARM PORT INPUT TIMING ................. 603

FIGURE 104 - TRANSMIT TRANSPORT OVERHEAD INPUT

TIMING.......................................................................... 605

FIGURE 105 - TRANSMIT RING CONTROL PORT INPUT

TIMING.......................................................................... 606

FIGURE 106 - TRANSMIT OVERHEAD OUTPUT TIMING................607

FIGURE 107 - JTAG PORT INTERFACE TIMING..............................608

FIGURE 108 - THETA JA VS. AIRFLOW PLOT.................................. 610

FIGURE 109 - MECHANICAL DRAWING 520 PIN SUPER BALL

GRID ARRA Y (SBGA)....................................................612

PROPRIETARY AND CONFIDENTIAL xxxi

Page 33

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

1 FEATURES

1.1 General

• Monolithic SONET/SDH P AYLOAD EXTRACTOR/ALIGNER for use in

STS-12 (STM-4/AU3 or STM-4/AU4) or STS-12c (STM-4-4c) interface

applications, operating at serial interface speeds of up to 622.08 Mbit/s.

• Provides integrated clock and data recovery and clock synthesis for direct

connection to optical modules.

• Supports a duplex byte-serial 77.76 Mbyte/s STS-12 (STM-4/AU3 or

STM-4/AU4) or STS-12c (STM-4-4c) line side interface for use in applications

where by-passing clock recovery, clock synthesis, and serializer-deserializer

functionality is desired.

• Supports clock recovery bypass for use in applications where external clock

recovery is desired.

• Complies with Bellcore GR-253-CORE jitte r tolerance (1995 issue), jitter

transfer and intrinsic jitter criteria.

• Provides control circuitry to comply with Bellcore GR-253-CORE WAN

clocking requirements related to wander transfer, holdover and long term

stability when using an external VCXO.

• Provides termination for SONET Section and Line, SDH Regenerator Section

and Multiplexer Section transport overhead, and path overhead of twelve

STS-1 (STM-0/AU3) paths, four STS-3/3c (STM-1/AU3/AU4) paths or a single

STS-12c (STM-4-4c) path.

• De-multiplexes an STM-4 receive stream to four STM-1 Telecom DROP bus

streams.

• Multiplexes four STM-1 Telecom ADD bus streams to an STM-4 transmit

stream.

• Maps twelve STS-1 (STM-0/AU3) payloads, four STS-3/3c (STM-1/AU3/AU4)

payloads or a single STS-12c (STM-4-4c) payload to system timing reference,

accommodating plesiochronous timing offsets between the references

through pointer processing.

• Maps twelve DS3 bit st reams into an STS-12 (STM-4/AU3) frame.

PROPRIETARY AND CONFIDENTIAL 1

Page 34

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

• Provides Time Slot Interchange (TSI) function at the Telecom ADD and DROP

buses for grooming twelve STS-1 (STM-0/AU3) paths or four STS-3/3c

(STM-1/AU3/AU4) paths.

• Supports line loopback from the line side receive stream to the transmit

stream and diagnostic loopback from a Telecom ADD bus interface to a

Telecom DROP bus interface.

• Supports OC-48(STM-16) applications by providing parallel receive and

transmit line side ports used to connect to front-end OC-48 devices.

• Provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan

board test purposes.

• Provides a generic 8-bit microprocessor bus interface for configuration,

control, and status monitoring .

• Low power 3.3V CMOS with TTL compatible digital inputs and CMOS/TTL

digital outputs. PECL inputs and outputs are 3.3V and 5V compatible.

• Industrial temperature range (-40°C to +85°C).

• 520 pin Super BGA package.

1.2 SONET Section and Line / SDH Regenerator and Multiplexer Section

• Frames to the STS-12 (STM-4) receive stream and inserts the framing bytes

(A1, A2) and the STS identification byte (J0) into the transmit stream;

descrambles the received stream and scrambles the transmit stream.

• Calculates and compares the bit interleaved parity (BIP) error detection codes

(B1, B2) for the receive stream. Calculates and inserts B1 and B2 in the

transmit stream. Accumulates near end errors (B1, B2) and far end errors

(M1) and inserts line remote error indications (REI) into the Z2 (M1) growth

byte based on received B2 errors.

• Detects signal degrade (SD) and signal fail (SF) threshold crossing alarms

based on received B2 errors.

• Extracts and serializes the order wire channels (E1, E2), the data

communication channels (D1-D3, D4-D12) and the section user channel (F1)

from the received stream, and inserts the corresponding signals into the

transmit stream.

PROPRIETARY AND CONFIDENTIAL 2

Page 35

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

• Extracts and serializes the automatic protection switch (APS) channel (K1,

K2) bytes, filtering and extracting them into internal registers for the receive

stream. Inserts the APS channel into the transmit stream.

• Extracts and filters the synchronization status message (Z1/S1) byte into an

internal register for the receive stream. Inserts the synchronization status

message (Z1/S1) byte into the transmit stream.

• Extracts a 64 byte or 16 byte section trace (J0) message using an internal

register bank for the receive stream. Detects an unstable section trace

message or mismatch with an expected message, and optionally inserts Line

and Path AIS on the system DROP side upon either of these conditions.

Inserts a 64 byte or 16 byte section trace (J0) message using an internal

register bank for the transmit stream. Provides access to the accepted

message via the microprocessor port.

• Detects loss of signal (LOS), out of frame (OOF), loss of frame (LOF), line

remote defect indication (RDI), line alarm indication signal (AIS), and

protection switching byte failure alarms on the receive stream. Optionally

returns line RDI in the transmit stream.

• Provides a transmit and receive ring control port, allowing alarm and

maintenance signal control and status to be passed between mate

SPECTRA-622s for ring-based add drop multiplexer and line multiplexer

applications.

• Configurable to force Line AIS in the transmit stream.

1.3 SONET Path / SDH High Order Path

• Accepts a multiplex of twelve STS-1 (STM-0/AU3) streams, four STS-3/3c

(STM-1/AU3/AU4) streams or a single STS-12 c (ST M-4-4c) stream, interprets

the STS (AU) pointer bytes (H1, H2, and H3), extracts the synchronous

payload envelope(s) and processes the path overhead for the receive stream.

• Constructs a byte serial multiplex of twelve STS-1 (STM-0/AU3) streams or

four STS-3/3c (STM-1/AU3/AU4) stream on the transmit side.

• Detects loss of pointer (LO P), loss of tributary multiframe (LOM), path alarm

indication signal (PAIS) and path (auxiliary and enhanced) remote defect

indication (RDI) for the receive stream. Optionally inserts path alarm

indication signal (PAIS) and path remote defect indication (RDI) in the

transmit stream.

PROPRIETARY AND CONFIDENTIAL 3

Page 36

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

• Extracts and serializes the entire path overhead from the twelve STS-1

(STM-0/AU3), four STS-3/3c (STM-1/AU3/AU4) or the single STS-12c

(STM-4-4c) receive streams. Inserts the path overhead bytes in the twelve

STS-1 (STM-0/AU3), four STS-3/3c (STM-1/AU3/AU4) or single STS-12c

(STM-4-4c) stream for the transmit stream. The path overhead bytes may be

sourced from internal registers or from bit serial path overhead input stream.

Path overhead insertion may also be dis abl e d.

• Extracts the received path signal label (C2) byte into an internal register and

detects for path signal label unstable and for signal label mismatch with the

expected signal label that is downloaded by the microprocessor. Inserts the

path signal label (C2) byte from an internal register for the transmit stream.

• Extracts a 64 byte or 16 byte path trace (J1) message using an internal

register bank for the receive stream. Detects an unstable path trace message

or mismatch with an expected message, and inserts Path RAI upon either of

these conditions. Inserts a 64 byte or 16 byte path trace (J1) message using

an internal register bank for the transmit stream. Provides access to the

accepted message via the micropr ocessor por t.

• Detects received path BIP-8 and counts received path BIP-8 errors for

performance monitori ng purp oses. BIP- 8 er ror s are selectable to be treated

on a bit basis or block basis. Optionally calculates and inserts path BIP-8

error detection codes for the transmit stream.

• Counts received path remote error indications (REIs) for performance

monitoring purposes. Optionally inserts the path REI count into the path

status byte (G1) basis on bit or block BIP-8 errors detected in the receive

path. Reporting of BIP-8 errors is on a bit or block bases independent of the

accumulation of BIP-8 errors.

• Maintains the existing tributary multiframe sequence on the H4 byte until a

new phase alignment has been verified.

• Provides a serial alarm port communication of path REI and path RDI alarms

to the transmit stream of a mate SPECTRA-622 in the returning direction.

1.4 System Side Interfaces

• Supports Telecombus interfaces by indicating/accepting the location of the

STS identification byte (C1), optionally the path trace byte(s) (J1), optionally

the first tributary overhead byte(s) (V1), and all synchronous payload

envelope bytes in the byte serial stream.

PROPRIETARY AND CONFIDENTIAL 4

Page 37

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

• Configurable to support four 19.44 MHz byte Telecombus interfaces or a

single 77.76 MHz byte Telecombus interface.

• For Telecombus interface, accommodates phase and frequency differences

between the receive/transmit streams and the DROP/ADD busses via pointer

adjustments.

• Supports bit serial DS3 interfaces for mapping into and out of the 12 possible

STS-1 SPE’s in an STS-12 (STM-4/AU3).

• For the DS3 interface, provides optional insertion of DS3 AIS in both the ADD

and DROP directions.

• Configurable to support a mix of traffic from the DS-3 interface and the

Telecombus interface selectable on an STS-1 basis.

• Provides TSI function to interchange or groom twelve STS-1 (STM-0/AU3)

paths or four STS-3/3c (STM-1/AU3/AU4) paths at the Telecom ADD and

DROP buses. For STS-3 (STM-1/AU3) paths, grooming can be performed at

the STS-1 (STM-0/ AU3) level.

PROPRIETARY AND CONFIDENTIAL 5

Page 38

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

2 APPLICATIONS

• SONET/SDH Add Drop Multiplexers

• SONET/SDH Terminal Multiplexers

• SONET/SDH Line Multiplexers

• SONET/SDH Cross Connects

• SONET/SDH Test Equipment

• Switches and Hubs

• Routers

PROPRIETARY AND CONFIDENTIAL 6

Page 39

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

3 REFERENCES

• American National Standard for Telecommunications - Digital Hierarchy -

Optical Interface Rates and Formats Specification, ANSI T1.105-1995.

• American National Standard for Telecommunications - Layer 1 In-Service

Digital Transmission Performance Monitoring, T1X1.3/93-005R1, April 1993.

• Bell Communications Research - GR-253-CORE “SONET Transport Systems:

Common Generic Criteria”, Issue 2 Revision 2, January, 1999.

• Bell Communications Resea rch - GR-436-CORE “Digital Network

Synchronization Plan”, Issue 1 Revision 1, June 1996.

• ETS 300 417-1-1, "Generic Functional Requirements for Synchronous Digital

Hierarchy (SDH) Equipment", January, 1996.

• ITU-T Recommendation G.703 - "Physical/Electrical Characteristics of

Hierarchical Digital Interfaces", 1991.

• ITU-T Recommendation G.704 - "General Aspects of Digital Tr ansmission

Systems; Terminal Equipment - Synchronous Frame Structures Used At 1544,

6312, 2048, 8488 and 44 736 kbit/s Hierarchical Levels", July, 1995.

• ITU, Recommendation G.707 - "Network Node Interface For The

Synchronous Digital Hierarchy", 1996.

• ITU Recommendation G.781, - “Structure of Recommendations on Equipment

for the Synchronous Digital Hierarchy (SDH)”, January, 1994.

• ITU Recommendation G.783, “Characteristics of Synchronous Digital

Hierarchy (SDH) Equipment Functional Blocks”, 28 October, 1992.

• ITU Recommendation O.151, “Error Performance measuring Equipment

Operating at the Primary Rate and Above”, October, 1992.

• ITU Recommendation I.432, “ISDN User Network Interfaces”, March 93.

PROPRIETARY AND CONFIDENTIAL 7

Page 40

PRODUCTION

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

PM5313 SPECTRA-622

4 DEFINITIONS

The following table defines the abbreviations for the SPECTRA-622.

APGM ADD Bus PRBS Generator/Monitor

CRSI CRU and SIPO

CRU Clock Recovery Unit

CSPI CSU and PISO

CSU Clock Synthesis Unit

DPGM DROP Bus PRBS Generator/Monitor

D3MA DS3 Mapper ADD Side

D3MD DS3 Mapper DROP Side

PISO Parallel to Serial Converter

PRBS Pseudo Random Bit/Byte Sequence

RASE Receive APS, Synchronization Extractor and Bit Error

Monitor

RLOP Receive Line Overhead Processor

RTOC Receive Transport Overhead Controller

RPOP Receive Path Overhead Processor

RSOP Receive Section Overhead Processor

RTAL Receive Telecom Aligner

TSI Timeslot Interchange

SIPO Serial to Parallel Converter

SPTB SONET/SDH Path Trace Buffer

SSTB SONET/SDH Section Trace Buffer

TLOP Transmit Line Overhead Processor

TTOC Transmit Transport Overhead Controller

TPOP Transmit Path Overhead Processor

TSOP Transmit Section Overhead Processor

TT AL Transmit Telecom Aligner

WANS Wide Area Network Synchronization Controller

RPPS Receive Path Processing Slice

TPPS Transmit Path Processing Slice

PROPRIETARY AND CONFIDENTIAL 8

Page 41

PRODUCTION

PMC-Sierra, Inc.

PM5313 SPECTRA-622

DATASHEET

PMC-1981162 ISSUE 6 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

5 APPLICATION EXAMPLES

The SPECTRA-622 can be used in SONET/SDH network elements including

switches, terminal multiplexers, and add-drop multiplexers. In such applications,

the SPECTRA-622 line interface typically interfaces directly to electrical optical

modules. On the system side interface, the SPECTRA-622 connects directly to a

Telecombus. Figure 1 shows how the SPECTRA-622 is used to implement a 622

Mbit/s aggregate interface. In this application, the SPECTRA-622 performs

SONET/SDH section, line and path termination and the PM5362 TUPP-PLUS

performs tributary pointer processing and performance monitoring.

Figure 1 -STS-12 (STM-4/AU-3), STS-12 (STM-4/AU-4) or STS-12c (STM4-4c) Application with 19.44 MHz Byte Telecombus Interface

622 Mbit/s

Optical

Interface

Optical

Transceiver

RXD+/SD

TXD+/-

PM5313

SPECTRA-622

ACK

AD[31:0], ADP[4:1]

AC1J1V1[4:1]

APL[4:1]

DD[31:24], DDP[4]

DC1J1V1[4]

DPL[4]

DCK

DD[23:16], DDP[3]

DC1J1V1[3]

DPL[3]

DCK

DD[15:8], DDP[2]

DC1J1V1[2]

DPL[2]

DCK

DD[7:0], DDP[1]

DC1J1V1[1]

DPL[1]

DCK

ID[7:0], IDP

IC1J1

IPL

SCLK

ID[7:0], IDP

IC1J1

IPL

SCLK

ID[7:0], IDP

IC1J1

IPL

SCLK

ID[7:0], IDP

IC1J1

IPL

SCLK

PM5362

TUPP-PLUS

PM5362

TUPP-PLUS

PM5362

TUPP-PLUS

PM5362

TUPP-PLUS

OD[7:0], ODP

OTV5

OTPL

TPOH

OD[7:0], ODP

OTV5

OTPL

TPOH