Page 1

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM4341A

T1XC

SINGLE DSX-1 TRANSCEIVER DEVICE

DATA SHEET

ISSUE 7: JUNE 1998

Page 2

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

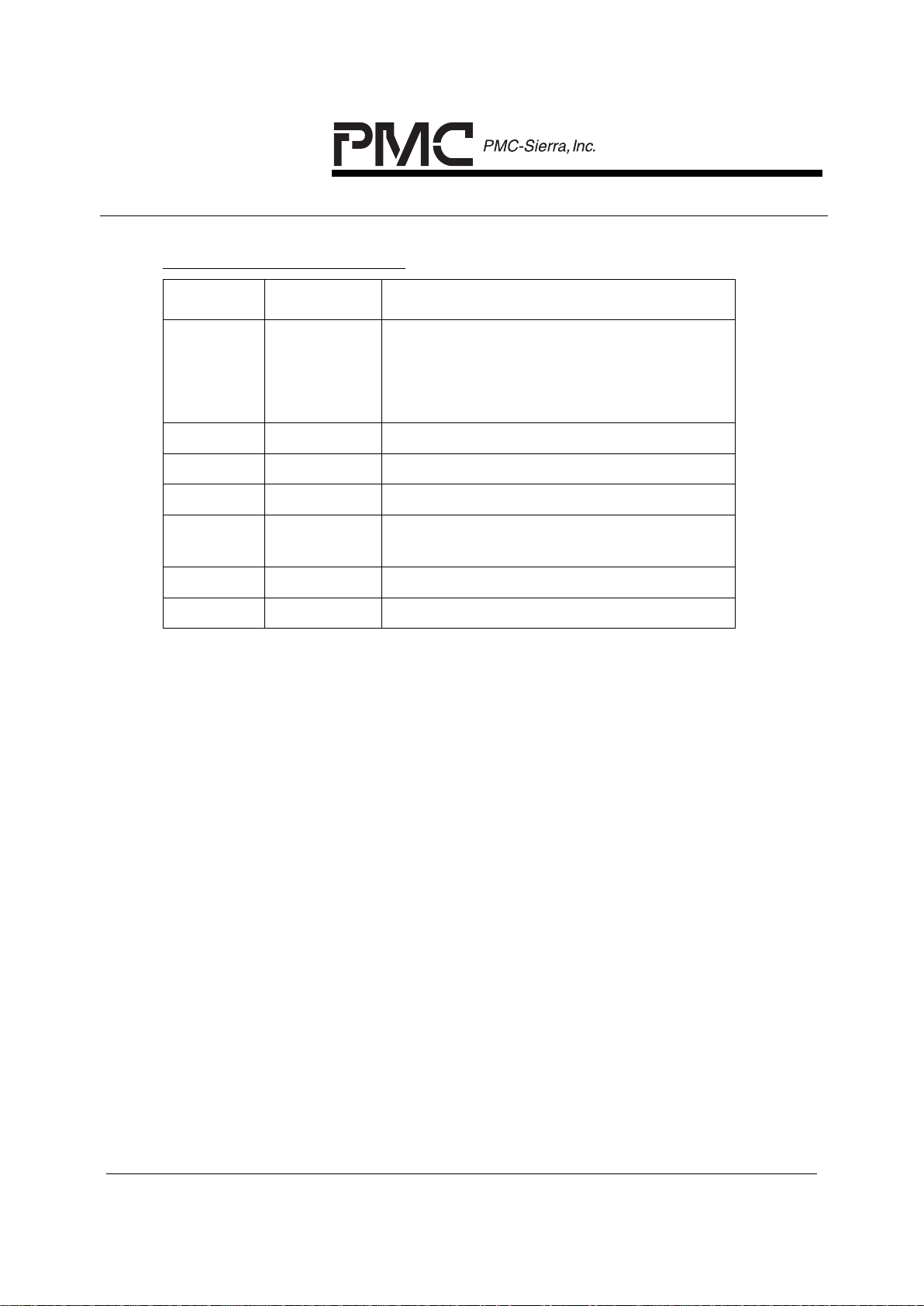

PUBLIC REVISION HISTORY

Issue No. Issue Date Details of Change

7 June 1998 Data Sheet Reformatted — No Change in

Technical Content.

Generated R7 datasheet from PMC-

891007, R11

6 July 1996 Release of Issue 10 of T1XC Eng Doc

5

4

3 February

1996

Release of Issue 9 of T1XC Eng Doc

2

1

Page 3

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

i

CONTENTS

1 FEATURES...............................................................................................1

1.1 APPLICATIONS.............................................................................3

2 REFERENCES.........................................................................................4

3 APPLICATION EXAMPLES......................................................................6

4 BLOCK DIAGRAM..................................................................................10

5 DESCRIPTION.......................................................................................11

6 PIN DIAGRAM........................................................................................13

7 PIN DESCRIPTION................................................................................15

8 FUNCTIONAL DESCRIPTION...............................................................36

8.1 DIGITAL DS-1 RECEIVE INTERFACE (DRIF).............................36

8.2 ANALOG DSX-1 PULSE SLICER (RSLC)...................................36

8.3 CLOCK AND DATA RECOVERY (CDRC)....................................39

8.4 FRAMER (FRMR)........................................................................40

8.5 FRAMER/SLIP BUFFER RAM (FRAM).......................................41

8.6 INBAND LOOPBACK CODE DETECTOR (IBCD).......................41

8.7 PULSE DENSITY VIOLATION DETECTOR (PDVD)....................42

8.8 PERFORMANCE MONITOR COUNTERS (PMON)....................42

8.9 BIT ORIENTED CODE DETECTOR (RBOC)..............................42

8.10 HDLC RECEIVER (RFDL)...........................................................43

8.11 ALARM INTEGRATOR (ALMI).....................................................43

8.12 ELASTIC STORE (ELST)............................................................44

8.13 SIGNALLING EXTRACTOR (SIGX).............................................45

Page 4

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ii

8.14 RECEIVE PER-CHANNEL SERIAL CONTROLLER (RPSC)......46

8.15 SIGNALLING ALIGNER (SIGA)...................................................46

8.16 BACKPLANE RECEIVE INTERFACE (BRIF) ..............................46

8.17 BASIC TRANSMITTER (XBAS)...................................................47

8.18 TRANSMIT PER-CHANNEL SERIAL CONTROLLER (TPSC)....47

8.19 INBAND LOOPBACK CODE GENERATOR (XIBC).....................48

8.20 BIT ORIENTED CODE GENERATOR (XBOC)............................48

8.21 HDLC TRANSMITTER (XFDL) ....................................................48

8.22 PULSE DENSITY ENFORCER (XPDE) ......................................49

8.23 DIGITAL JITTER ATTENUATOR (DJAT).......................................50

8.23.1JITTER CHARACTERISTICS...........................................50

8.23.2JITTER TOLERANCE........................................................51

8.23.3JITTER TRANSFER..........................................................53

8.23.4FREQUENCY RANGE......................................................54

8.24 TIMING OPTIONS (TOPS)..........................................................54

8.25 DIGITAL DS-1 TRANSMIT INTERFACE (DTIF)...........................54

8.26 ANALOG DSX-1 PULSE GENERATOR (XPLS)..........................54

8.27 BACKPLANE TRANSMIT INTERFACE (BTIF) ............................57

8.28 MICROPROCESSOR INTERFACE (MPIF) .................................58

9 REGISTER DESCRIPTION....................................................................59

9.1 NORMAL MODE REGISTER MEMORY MAP.............................59

10 NORMAL MODE REGISTER DESCRIPTION........................................63

10.1 INTERNAL REGISTERS .............................................................63

Page 5

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iii

10.1.1 REGISTERS 4A-4FH: LATCHING PERFORMANCE DATA

........................................................................................166

11 TEST FEATURES DESCRIPTION .......................................................189

11.1 TEST MODE REGISTER MEMORY MAP.................................189

11.2 INTERNAL REGISTERS ...........................................................193

11.3 TEST MODE 0...........................................................................194

12 TIMING DIAGRAMS.............................................................................196

13 OPERATION.........................................................................................209

13.1 CONFIGURING THE T1XC FROM RESET...............................209

13.2 USING THE INTERNAL FDL TRANSMITTER...........................214

13.2.1POLLED MODE..............................................................215

13.2.2INTERRUPT MODE........................................................216

13.2.3DMA-CONTROLLED MODE...........................................216

13.3 USING THE INTERNAL FDL RECEIVER..................................216

13.3.1POLLED MODE..............................................................217

13.3.2INTERRUPT MODE........................................................218

13.3.3DMA- CONTROLLED MODE..........................................219

13.3.4KEY USED ON SUBSEQUENT DIAGRAMS:.................220

13.4 USING THE LOOPBACK MODES.............................................224

13.4.1PAYLOAD LOOPBACK....................................................224

13.4.2LINE LOOPBACK............................................................225

13.4.3DIAGNOSTIC DIGITAL LOOPBACK...............................226

13.4.4DIAGNOSTIC METALLIC LOOPBACK ...........................227

13.5 USING THE PER-CHANNEL SERIAL CONTROLLERS ...........228

Page 6

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iv

13.5.1INITIALIZATION ..............................................................228

13.5.2DIRECT ACCESS MODE ...............................................228

13.5.3INDIRECT ACCESS MODE............................................229

13.6 PROGRAMMING THE XPLS WA VEFORM TEMPLATE ............230

13.7 USING THE DIGITAL JITTER ATTENUATOR............................234

13.7.1DEFAULT APPLICATION.................................................234

13.7.2DATA BURST APPLICATION ..........................................234

13.7.3ELASTIC STORE APPLICATION....................................235

13.7.4ALTERNATE TCLKO REFERENCE APPLICATION ........235

13.8 USING THE PERFORMANCE MONITOR COUNTER VALUES 235

14 ADDITIONAL APPLICATIONS .............................................................241

15 ABSOLUTE MAXIMUM RATINGS........................................................245

16 CAPACITANCE.....................................................................................246

17 D.C. CHARACTERISTICS ...................................................................247

18 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS......249

19 T1XC I/O CHARACTERISTICS............................................................254

20 ANALOG CHARACTERISTICS...........................................................264

21 ORDERING AND THERMAL INFORMATION ......................................266

22 MECHANICAL INFORMATION.............................................................267

Page 7

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

v

LIST OF REGISTERS

REGISTER 00H: T1XC RECEIVE OPTIONS....................................................64

REGISTER 01H: T1XC RECEIVE BACKPLANE OPTIONS .............................66

REGISTER 02H: T1XC DATALINK OPTIONS ...................................................68

REGISTER 03H: T1XC RECEIVE DS1 INTERFACE CONFIGURATION..........71

REGISTER 04H: T1XC TRANSMIT DS1 INTERFACE CONFIGURATION.......73

REGISTER 05H: T1XC TRANSMIT BACKPLANE OPTIONS...........................75

REGISTER 06H: T1XC TRANSMIT FRAMING AND BYPASS OPTIONS.........77

REGISTER 07H: T1XC TRANSMIT TIMING OPTIONS ....................................79

REGISTER 08H: T1XC MASTER INTERRUPT SOURCE #1 ...........................86

REGISTER 09H: T1XC MASTER INTERRUPT SOURCE #2 ...........................87

REGISTER 0AH: T1XC MASTER DIAGNOSTICS............................................88

REGISTER 0BH: T1XC MASTER TEST...........................................................90

REGISTER 0CH: T1XC REVISION/CHIP ID.....................................................92

REGISTER 0DH: T1XC MASTER RESET........................................................93

REGISTER 0EH: T1XC PHASE STATUS WORD (LSB)....................................94

REGISTER 0FH: T1XC PHASE STATUS WORD (MSB)...................................96

REGISTER 10H: CDRC CONFIGURATION......................................................97

REGISTER 11H: CDRC INTERRUPT ENABLE................................................98

REGISTER 12H: CDRC INTERRUPT STATUS.................................................99

REGISTER 14H: XPLS LINE LENGTH CONFIGURATION ............................100

REGISTER 15H: XPLS CONTROL/STATUS...................................................102

REGISTER 16H: XPLS CODE INDIRECT ADDRESS....................................103

Page 8

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vi

REGISTER 17H: XPLS CODE INDIRECT DATA.............................................105

REGISTER 18H: DJAT INTERRUPT STATUS.................................................106

REGISTER 19H: DJAT REFERENCE CLOCK DIVISOR (N1) CONTROL......107

REGISTER 1AH: DJAT OUTPUT CLOCK DIVISOR (N2) CONTROL.............108

REGISTER 1BH: DJAT CONFIGURATION .....................................................109

REGISTER 1CH: ELST CONFIGURATION.....................................................111

REGISTER 1DH: ELST INTERRUPT ENABLE/STATUS.................................112

REGISTER 1EH: ELST TROUBLE CODE......................................................113

REGISTER 20H: FRMR CONFIGURATION....................................................114

REGISTER 21H: FRMR INTERRUPT ENABLE..............................................116

REGISTER 22H: FRMR INTERRUPT STATUS...............................................118

REGISTER 2AH: RBOC ENABLE...................................................................120

REGISTER 2BH: RBOC CODE STATUS ........................................................121

REGISTER 2CH: ALMI CONFIGURATION.....................................................122

REGISTER 2DH: ALMI INTERRUPT ENABLE...............................................124

REGISTER 2EH: ALMI INTERRUPT STATUS ................................................125

REGISTER 2FH: ALMI ALARM DETECTION STATUS...................................126

REGISTER 30H: TPSC CONFIGURATION.....................................................128

REGISTER 31H: TPSC µP ACCESS STATUS................................................129

REGISTER 32H: TPSC CHANNEL INDIRECT ADDRESS/CONTROL...........130

REGISTER 33H: TPSC CHANNEL INDIRECT DATA BUFFER.......................131

TPSC INTERNAL REGISTERS 01-18H: PCM DATA CONTROL BYTE..........133

TPSC INTERNAL REGISTERS 19-30H: IDLE CODE BYTE..........................135

Page 9

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vii

REGISTER 34H: XFDL CONFIGURATION.....................................................137

REGISTER 35H: XFDL INTERRUPT STATUS................................................139

REGISTER 36H: XFDL TRANSMIT DATA.......................................................140

REGISTER 38H: RFDL CONFIGURATION.....................................................141

REGISTER 39H: RFDL INTERRUPT CONTROL/STATUS..............................142

REGISTER 3AH: RFDL STATUS.....................................................................144

REGISTER 3BH: RFDL RECEIVE DATA.........................................................146

REGISTER 3CH: IBCD CONFIGURATION.....................................................147

REGISTER 3DH: IBCD INTERRUPT ENABLE/STATUS.................................148

REGISTER 3EH: IBCD ACTIVATE CODE.......................................................150

REGISTER 3FH: IBCD DEACTIVATE CODE..................................................151

REGISTER 40H: SIGX CONFIGURATION......................................................152

REGISTER 41H: SIGX µP ACCESS STATUS.................................................154

REGISTER 42H: SIGX CHANNEL INDIRECT ADDRESS/CONTROL ...........155

REGISTER 43H: SIGX CHANNEL INDIRECT DATA BUFFER .......................156

SIGX INTERNAL REGISTERS 01-18H: SIGNALLING DATA..........................158

SIGX INTERNAL REGISTERS 21-38H: PER-CHANNEL CONFIGURATION

DATA .....................................................................................................159

REGISTER 44H: XBAS CONFIGURATION.....................................................160

REGISTER 45H: XBAS ALARM TRANSMIT...................................................162

REGISTER 46H: XIBC CONTROL..................................................................163

REGISTER 47H: XIBC LOOPBACK CODE....................................................165

REGISTER 49H: PMON INTERRUPT STATUS...............................................166

REGISTER 4AH: PMON LCV COUNT (LSB)..................................................168

Page 10

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

viii

REGISTER 4BH: PMON LCV COUNT (MSB).................................................169

REGISTER 4CH: PMON BEE COUNT (LSB).................................................170

REGISTER 4DH: PMON BEE COUNT (MSB)................................................171

REGISTER 4EH: PMON FER COUNT............................................................172

REGISTER 4FH: PMON OOF/COFA COUNT.................................................173

REGISTER 50H: RPSC CONFIGURATION....................................................174

REGISTER 51H: RPSC µP ACCESS STATUS................................................175

REGISTER 52H: RPSC CHANNEL INDIRECT ADDRESS/CONTROL..........176

REGISTER 53H: RPSC CHANNEL INDIRECT DATA BUFFER......................177

RPSC INTERNAL REGISTERS 01-18H: PCM DATA CONTROL BYTE .........179

RPSC INTERNAL REGISTERS 19-30H: DATA TRUNK CONDITIONING CODE

BYTE....................................................................................................181

RPSC INTERNAL REGISTERS 31-48H: SIGNALLING TRUNK CONDITIONING

BYTE....................................................................................................182

REGISTER 55H: PDVD INTERRUPT ENABLE/STATUS ................................183

REGISTER 57H: XBOC CODE.......................................................................185

REGISTER 59H: XPDE INTERRUPT ENABLE/STATUS ................................186

REGISTER 5DH: RSLC INTERRUPT ENABLE/STATUS................................188

REGISTER 0BH: T1XC MASTER TEST.........................................................193

Page 11

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ix

LIST OF FIGURES

FIGURE 1 - EXAMPLE 1. T1 OR E1 ATM INTERFACE USING PM7345 .........6

FIGURE 2 - EXAMPLE 2. DSX-1/0 CROSS-CONNECT....................................7

FIGURE 3 - EXAMPLE 3. MULTI-FEATURED, JITTER ATTENUATING CSU...8

FIGURE 4 - 68 PIN PLCC................................................................................13

FIGURE 5 - 80 PIN PQFP................................................................................14

FIGURE 6 - EXTERNAL ANALOG RECEIVE INTERFACE CIRCUIT .............38

FIGURE 7 - CDRC JITTER TOLERANCE.......................................................40

FIGURE 8 - DJAT JITTER TOLERANCE .........................................................52

FIGURE 9 - DJAT MINIMUM JITTER TOLERANCE VS XCLK ACCURACY....53

FIGURE 10- DJAT JITTER TRANSFER............................................................53

FIGURE 11- EXTERNAL ANALOG TRANSMIT INTERFACE CIRCUIT...........56

FIGURE 12- TRANSMIT TIMING OPTIONS.....................................................85

FIGURE 13- SLC®96 TRANSMIT DATALINK INTERFACE.............................196

FIGURE 14- T1DM TRANSMIT DATALINK INTERFACE.................................197

FIGURE 15- ESF 4KBIT/S TRANSMIT DATALINK INTERFACE.....................197

FIGURE 16- ESF 2KBIT/S TRANSMIT DATALINK INTERFACE.....................198

FIGURE 17- SLC®96 RECEIVE DATALINK INTERFACE...............................198

FIGURE 18- T1DM RECEIVE DATALINK INTERFACE...................................199

FIGURE 19- ESF 4KBIT/S RECEIVE DATALINK INTERFACE.......................199

FIGURE 20- ESF 2KBIT/S RECEIVE DATALINK INTERFACE.......................200

FIGURE 21- D-CHANNEL RECEIVE DATALINK INTERFACE........................200

FIGURE 22- D-CHANNEL TRANSMIT DATALINK INTERFACE.....................201

Page 12

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

x

FIGURE 23- 1.544MHZ RECEIVE BACKPLANE INTERFACE.......................201

FIGURE 24- 1.544MHZ RECEIVE LINE DATA INTERFACE...........................202

FIGURE 25- 1.544MHZ TRANSMIT BACKPLANE INTERFACE ....................202

FIGURE 26- 2.048MHZ RECEIVE BACKPLANE INTERFACE.......................203

FIGURE 27- 2.048MHZ TRANSMIT BACKPLANE INTERFACE ....................204

FIGURE 28- 1.544MHZ RECEIVE BACKPLANE INTERFACE - WITHOUT

SIGNALLING ALIGNMENT.............................................................................204

FIGURE 29- 1.544MHZ RECEIVE BACKPLANE INTERFACE - WITH

SIGNALLING ALIGNMENT.............................................................................205

FIGURE 30- 1.544MHZ TRANSMIT BACKPLANE INTERFACE - WITHOUT

SIGNALLING ALIGNMENT.............................................................................205

FIGURE 31- 1.544MHZ TRANSMIT BACKPLANE INTERFACE - WITH

SIGNALLING ALIGNMENT.............................................................................206

FIGURE 32- 1.544MHZ RECEIVE BACKPLANE INTERFACE - WITH ALTFDL...

.....................................................................................................207

FIGURE 33- 1.544MHZ TRANSMIT BACKPLANE INTERFACE - WITH ALTFDL

.....................................................................................................208

FIGURE 34- TYPICAL DATA FRAME..............................................................220

FIGURE 35- RFDL NORMAL DATA AND ABORT SEQUENCE......................221

FIGURE 36- RFDL FIFO OVERRUN ..............................................................222

FIGURE 37- XFDL NORMAL DATA SEQUENCE ...........................................222

FIGURE 38- XFDL UNDERRUN SEQUENCE................................................223

FIGURE 39- PAYLOAD LOOPBACK...............................................................225

FIGURE 40- LINE LOOPBACK.......................................................................226

FIGURE 41- DIAGNOSTIC DIGITAL LOOPBACK..........................................227

FIGURE 42- DIAGNOSTIC METALLIC LOOPBACK.......................................228

Page 13

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xi

FIGURE 43- CODE REGISTER SEQUENCE DURING PULSE GENERATION ...

.....................................................................................................232

FIGURE 44- CODE REGISTER SEQUENCE FOR 0-110 FEET BUILD-OUT233

FIGURE 45- LCV COUNT VS. BER................................................................236

FIGURE 46- FER COUNT VS. BER FOR SF AND T1DM FRAMING FORMATS .

.....................................................................................................237

FIGURE 47- FER COUNT VS. BER FOR SLC®96 FRAMING FORMAT........237

FIGURE 48- FER COUNT VS. BER FOR ESF FRAMING FORMAT ..............238

FIGURE 49- BEE COUNT VS. BER FOR ESF FRAMING FORMAT..............238

FIGURE 50- BEE COUNT VS. BER FOR SF FRAMING FORMAT.................239

FIGURE 51- BEE COUNT VS. BER FOR SLC®96 FRAMING FORMAT........239

FIGURE 52- BEE COUNT VS. BER FOR T1DM FRAMING FORMAT............240

FIGURE 53- EXAMPLE 4. TERMINATING ISDN PRIMARY RATE D-CHANNEL

WITH QFDL.....................................................................................................241

FIGURE 54- EXAMPLE 5. TERMINATING ISDN PRIMARY RATE D-CHANNEL

WITH VL1935..................................................................................................243

FIGURE 55- MICROPROCESSOR READ ACCESS TIMING.........................250

FIGURE 56- MICROPROCESSOR WRITE ACCESS TIMING .......................252

FIGURE 57- BACKPLANE TRANSMIT INPUT TIMING DIAGRAM................254

FIGURE 58- XCLK=37.056MHZ INPUT TIMING............................................255

FIGURE 59- TCLKI INPUT TIMING ................................................................256

FIGURE 60- DIGITAL RECEIVE INTERFACE INPUT TIMING DIAGRAM......257

FIGURE 61- TRANSMIT DATA LINK INPUT TIMING DIAGRAM....................258

FIGURE 62- BACKPLANE RECEIVE INPUT TIMING DIAGRAM...................258

FIGURE 63- RECEIVE DATA LINK OUTPUT TIMING DIAGRAM...................259

Page 14

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xii

FIGURE 64- BACKPLANE RECEIVE OUTPUT TIMING DIAGRAM...............260

FIGURE 65- RECOVERED DATA OUTPUT TIMING DIAGRAM.....................260

FIGURE 66- TRANSMIT INTERFACE OUTPUT TIMING DIAGRAM..............261

FIGURE 67- TRANSMIT DATA LINK DMA INTERFACE OUTPUT TIMING

DIAGRAM .....................................................................................................262

FIGURE 68- RECEIVE DATA LINK DMA INTERFACE OUTPUT TIMING

DIAGRAM .....................................................................................................263

FIGURE 69- ANALOG RECEIVE DATA INPUT TIMING DIAGRAM................264

FIGURE 70- 68 PIN PLASTIC LEADED CHIP CARRIER (Q SUFFIX)...........267

FIGURE 71- 80 PIN COPPER LEADFRAME PLASTIC QUAD FLAT PACK (R

SUFFIX) .....................................................................................................268

Page 15

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xiii

LIST OF TABLES

TABLE 1 - RECOMMENDED RECEIVE NETWORK VALUES......................37

TABLE 2 - TYPICAL CHARACTERISTICS OF RECEIVE TRANSFORMER.38

TABLE 3 - TYPICAL CHARACTERISTICS OF TRANSMIT TRANSFORMER56

TABLE 4 - PLLREF[1:0] OPTIONS................................................................80

TABLE 5 - TRANSMIT CLOCK OPTIONS.....................................................81

TABLE 6 - PHASE STATUS WORD OPERATION .........................................95

TABLE 7 - TRANSMIT LINE LENGTH OPTIONS........................................101

TABLE 8 - XPLS INTERNAL CODE REGISTER MAP................................103

TABLE 9 - FRMR FRAME FORMAT OPTIONS...........................................115

TABLE 10 - ALMI FRAME FORMAT OPTIONS.............................................123

TABLE 11 - TPSC INDIRECT REGISTER MAP............................................132

TABLE 12 - TPSC INVERT AND SIGNINV FUNCTIONS..............................133

TABLE 13 - TPSC ZERO CODE SUPPRESSION OPTIONS........................134

TABLE 14 - RFDL FILL LEVEL INTERRUPT OPTIONS ...............................142

TABLE 15 - IBCD CODE LENGTH OPTIONS...............................................147

TABLE 16 - SIGX FRAME FORMAT OPTIONS.............................................153

TABLE 17 - SIGX INDIRECT REGISTER MAP.............................................157

TABLE 18 - XBAS ZERO CODE SUPPRESSION OPTIONS........................160

TABLE 19 - XBAS FRAME FORMAT OPTIONS............................................161

TABLE 20 - XIBC CODE LENGTH OPTIONS...............................................164

TABLE 21 - RPSC INDIRECT REGISTER MAP ...........................................178

TABLE 22 - RPSC INVERSION OPTIONS....................................................179

Page 16

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xiv

TABLE 23 - TEST MODE 0 PRIMARY INPUT READING MAP.....................194

TABLE 24 - TEST MODE 0 PRIMARY OUTPUT WRITING MAP..................195

TABLE 25 - DEFAULT SETTINGS.................................................................209

TABLE 26 - ESF FRAME FORMAT...............................................................210

TABLE 27 - SLC®96 FRAME FORMAT.........................................................211

TABLE 28 - SF FRAME FORMAT..................................................................212

TABLE 29 - T1DM FRAME FORMAT.............................................................213

TABLE 30 - PMON POLLING SEQUENCE...................................................213

TABLE 31 - ESF FDL PROCESSING............................................................214

TABLE 32 - TYPICAL OUTPUT VOLTAGES FOR XPLS CODES..................230

TABLE 33 - PREPROGRAMMED XPLS CODE SEQUENCES.....................231

TABLE 34 - PMON COUNTER SATURATION CHARACTERISTICS............236

TABLE 35 - SETTING UP T1XC TO PROCESS THE D-CHANNEL ..............242

TABLE 36 - D.C. CHARACTERISTICS..........................................................247

TABLE 37 - MICROPROCESSOR READ ACCESS......................................249

TABLE 38 - MICROPROCESSOR WRITE ACCESS.....................................251

TABLE 39 - BACKPLANE TRANSMIT INPUT TIMING (FIGURE 57)............254

TABLE 40 - XCLK=37.056MHZ INPUT (FIGURE 58)....................................255

TABLE 41 - TCLKI INPUT (FIGURE 59)........................................................256

TABLE 42 - DIGITAL RECEIVE INTERFACE INPUT TIMING (FIGURE 60) .256

TABLE 43 - TRANSMIT DATA LINK INPUT TIMING (FIGURE 61)................258

TABLE 44 - BACKPLANE RECEIVE INPUT TIMING (FIGURE 62) ..............258

TABLE 45 - RECEIVE DATA LINK OUTPUT TIMING (FIGURE 63)..............259

Page 17

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xv

TABLE 46 - BACKPLANE RECEIVE OUTPUT TIMING (FIGURE 64) ..........260

TABLE 47 - RECOVERED DATA OUTPUT TIMING (FIGURE 65).................260

TABLE 48 - TRANSMIT INTERFACE OUTPUT TIMING (FIGURE 66)..........261

TABLE 49 - TRANSMIT DATA LINK DMA INTERFACE OUTPUT TIMING

(FIGURE 67) ...................................................................................................262

TABLE 50 - RECEIVE DATA LINK DMA INTERFACE OUTPUT TIMING

(FIGURE 68) ...................................................................................................263

TABLE 51 - T1 SLICING THRESHOLD VOLTAGE.........................................264

TABLE 52 - ANALOG RECEIVE DATA INPUT TIMING (FIGURE 69) ...........264

TABLE 53 - TAP/TAN OUTPUT RESISTANCE ..............................................265

TABLE 54 - PACKAGING OPTIONS..............................................................266

TABLE 55 - THERMAL PROPERTIES...........................................................266

Page 18

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xvi

Page 19

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

1

1

FEATURES

•

Integrates a full-featured T1 framer and line interface in a single device with

analog circuitry for receiving and transmitting DSX-1 compatible signals and

digital circuitry for terminating the duplex DS-1 signal.

•

Provides an 8-bit microprocessor bus interface for configuration, control, and

status monitoring.

•

Low power CMOS technology

•

Available in either a 68 pin PLCC package, or a high density (14 by 14mm) 80

pin PQFP package.

The receiver section:

•

Provides analog circuitry for receiving a DSX-1 signal up to 655 feet from the

cross-connect. Direct digital inputs are also provided to allow for by-passing

the analog front-end.

•

Recovers clock and data using a digital phase locked loop for high jitter

tolerance. A direct clock input is provided to allow clock recovery to be bypassed.

•

Accepts dual rail or single rail digital PCM inputs.

•

Supports B8ZS or AMI line code.

•

Accepts gapped data streams to support higher rate demultiplexing.

•

Frames to SF, ESF, T1DM (DDS), and SLC®96 format DS1 signals.

•

Provides loss of signal detection, and red, yellow, and AIS alarm detection.

Red, yellow, and AIS alarms are integrated as per industry specifications.

•

Detects violations of the ANSI T1.403 12.5% pulse density rule over a moving

192 bit window.

•

Provides programmable in-band loopback code detection.

•

Supports line and path performance monitoring according to AT&T and ANSI

specifications. Accumulators are provided for counting:

•

ESF CRC-6 errors to 333 per second;

•

Framing bit errors to 31 per second;

•

Line code violations to 4095 per second; and

•

Loss of frame or change of frame alignment events to 7 per

second.

Page 20

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

2

•

Provides ESF bit-oriented code detection, and an HDLC/LAPD interface for

terminating the ESF data link.

•

Supports polled, interrupt-driven, or DMA servicing of the HDLC interface.

•

Extracts the data link in ESF, T1DM (DDS) or SLC®96 modes. Extracts the Dchannel for Primary Rate interfaces.

•

Provides a two-frame elastic store buffer for jitter and wander attenuation that

performs controlled slips and indicates slip occurrence and direction.

•

Provides robbed bit signalling extraction, with optional data inversion,

programmable idle code substitution, digital milliwatt code substitution, bit

fixing, and 2 superframes of signalling debounce on a per-channel basis.

•

Provides trunk conditioning which forces programmable trouble code

substitution and signalling conditioning on all channels or on selected

channels.

•

Optionally provides dual rail digital PCM output signals to allow BPV

transparency. Also supports unframed mode.

•

Supports transfer of received PCM and signalling data to 1.544 Mbit/s

backplane buses or to 2.048 Mbit/s backplane buses.

The transmitter section:

•

Supports transfer of transmitted PCM and signalling data from 1.544 Mbit/s or

2.048 Mbit/s backplane buses.

•

Formats data to SF, ESF, T1DM (DDS), and SLC®96 format DS1 signals.

•

Optionally accepts dual rail digital PCM inputs to allow BPV transparency.

Also supports unframed mode and framing bit, CRC, or data link by-pass.

•

Provides signalling insertion, programmable idle code substitution, digital

milliwatt code substitution, and data inversion on a per channel basis.

•

Provides trunk conditioning which forces programmable trouble code

substitution and signalling conditioning on all channels or on selected

channels.

•

Provides minimum ones density through Bell (bit 7), GTE or DDS zero code

suppression on a per channel basis.

•

Detects violations of the ANSI T1.403 12.5% pulse density rule over a moving

192 bit window or optionally stuffs ones to maintain minimum ones density.

•

Allows insertion of framed or unframed in-band loopback code sequences.

Page 21

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

3

•

Allows insertion of a data link in ESF, T1DM (DDS) or SLC®96 modes. Allows

insertion of the D- channel for Primary Rate interfaces.

•

Supports transmission of the alarm indication signal (AIS) or the yellow alarm

signal in all formats.

•

Provides ESF bit-oriented code generation and an HDLC/LAPD interface for

generating the ESF data link.

•

Supports polled, interrupt-driven, or DMA servicing of the HDLC interface.

•

Provides a digital phase locked loop for generation of a low jitter transmit

clock.

•

Provides a FIFO buffer for jitter attenuation and rate conversion in the

transmitter. FIFO full or empty indication allows for bit-stuffing in higher rate

multiplexing applications.

•

Supports B8ZS or AMI line code.

•

Provides analog circuitry for transmitting a DSX-1 signal. Digitally

programmable line build out is provided. Direct digital outputs are also

provided.

•

Provides dual rail or single rail digital PCM output signals.

1.1 APPLICATIONS

•

T1 Channel Service Units (CSU) and Data Service Units (DSU)

•

T1 Channel Banks (CH BANK) and Multiplexers (CPE MUX)

•

Digital Private Branch Exchanges (DPBX)

•

Digital Access and Cross-Connect Systems (DACS) and Electronic DSX

Cross-Connect Systems (EDSX)

•

T1 Frame Relay Interfaces

•

T1 ATM Interfaces

•

ISDN Primary Rate Interfaces (PRI)

•

SONET Add/Drop Multiplexers (ADM)

•

Test Equipment

Page 22

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

2

REFERENCES

1. American National Standard for Telecommunications, ANSI T1.102-1992 -

"Digital Hierarchy - Electrical Interfaces."

2. American National Standard for Telecommunications - Digital Hierarchy -

Formats Specification, ANSI T1.107-1991

3. American National Standard for Telecommunications - Carrier to Customer

Installation - DS1 Metallic Interface Specification, ANSI T1.403-1989

4. American National Standard for Telecommunications - Integrated Services

Digital Network (ISDN) Primary Rate- Customer Installation Metallic

Interfaces Layer 1 Specification, ANSI T1.408-1990

5. Bell Communications Research - Digital Interface Between The SLC96 Digital

Loop Carrier System And A Local Digital Switch, TR-TSY-000008, Issue 2,

August 1987.

6. Bell Communications Research - DS1 Rate Digital Service Monitoring Unit

Functional Specification, TA-TSY-000147, Issue 1, October, 1987.

7. Bell Communications Research - Digital Cross-Connect System

Requirements And Objectives, TR-TSY-000170, Issue 1, November 1985.

8. Bell Communications Research - Alarm Indication Signal Requirements and

Objectives, TR-TSY-000191 Issue 1, May 1986.

9. Bell Communications Research - The Extended Superframe Format Interface

Specification, TR-TSY-000194 Issue 1, December 1987. (Replaced by TRTSY-000499)

10. Bell Communications Research - Digital Data System (DDS) - T1 Data

Multiplexor (T1DM), TA-TSY-000278, Issue 1, November 1985.

11. Bell Communications Research - Integrated Digital Loop Carrier Generic

Requirements, Objectives, and Interface, TR-TSY-000303, Issue 1,

September, 1986.

12. Bell Communications Research - Functional Criteria for the DS1 Interface

Connector, TR-TSY-000312, Issue 1, March, 1988.

13. Bell Communications Research - Transport Systems Generic Requirements

(TSGR): Common Requirement, TR-TSY-000499, Issue 3, December, 1989.

Page 23

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

5

14. AT&T - Digital Channel Bank - Requirements And Objectives, PUB43801,

November 1982.

15. AT&T - Digital Channel Bank - Requirements And Objectives - Addendum 1,

PUB43801A, January 1985.

16. AT&T - Requirements For Interfacing Digital Terminal Equipment To Services

Employing The Extended Superframe Format, PUB54016, October 1984.

17. AT&T, TR 62411 - Accunet T1.5 - "Service Description and Interface

Specification" December, 1990.

Page 24

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

6

3

APPLICATION EXAMPLES

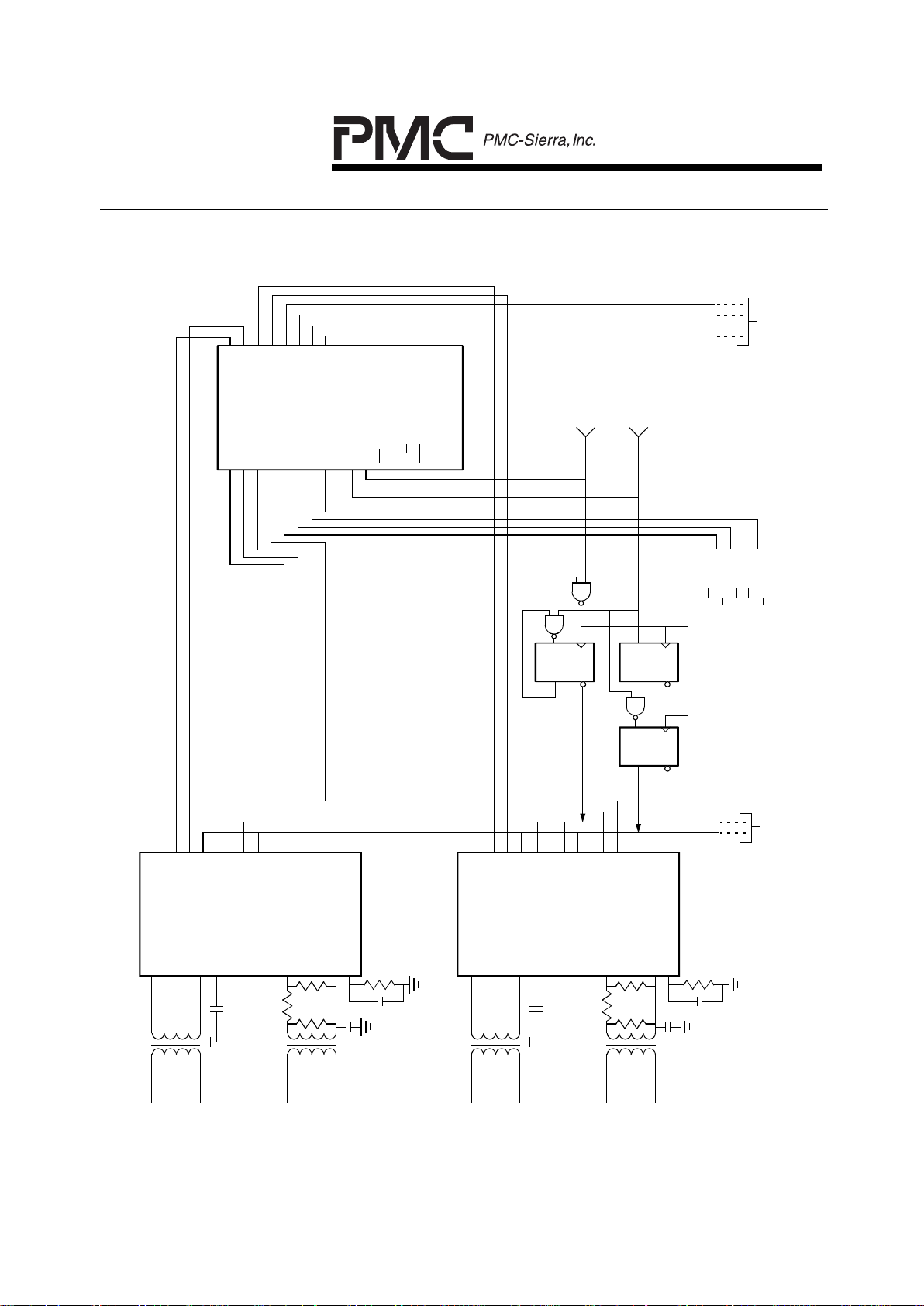

Figure 1 - Example 1. T1 or E1 ATM Interface Using PM7345

+5V

AD[7 :0]

ALE

RDB

WRB

RESB

INT

Inte l/

Motorola

Singl e Chip

µP

RAS

REF

RRC

TC

TAP

TAN

BRPCM

BRFPO

RCLKO

BTPCM

BTFP

BTCLK

TCL KO

TCL K I

PM 4341 A

T1XC T1

Transceiver

PM7345

S/UNI-PDH

SATURN

User-Netw ork

Interface for

PDH

RPOS/RDAT

RNEG/ROHM

RCLK

TIOHM

C13/CADD

TPOS/TDAT

TNEG/TOHM

TCLK

TICLK

From Master

rese t c ircu itry

From chip select

decode circuitry

37.056 MHz

RX

CELL

INTERFA C E

TX

CELL

INTERFA C E

ATM/SMD S

Adaptation

Layer

Processor

(SA R o r

po licin g

fun c tio n s )

RRDENB

FRDB/RFCLK

RSOC

REOH

REOC

FRDATA[7:0]

RFIFOE/RCA

TW REN B

FW RB /TFCLK

TSO C

FW DA TA[7:0]

TFIFO FB/TC A

TPOHC L K

TPO H F P

TPO HINS

TPO H

RPOHCLK

RPOHFP

RPOH

TOHINS

TOH

INTB

A[7:0]

D[7:0]

ALE

RDB

WRB

CSB

RSTB

XCLK

1.544

MHz

A[8:0

]

D[7:0]

ALE

RDB

WRB

CSB

RS

TB

Example 1 shows the PM4341 T1XC or PM6341 E1XC used with a PM7345

Saturn User Network Interface for PDH (S/UNI-PDH™) to implement ATM wide

area user network interfaces (UNI) and network node interfaces (NNI).

In this example, the T1 LIU and framing functions are provided by the PM4341A

T1XC. The combination of the T1XC or E1XC devices with the S/UNI-PDH

™

allows both PLCP formatted DS1/E1 signals and CCITT G.804 compliant

DS1/E1 signals to be processed. The G.804 specification defines ATM cell

mappings for a variety of transmission formats, including the 1.544 Mbit/s DS1

and the 2.048 Mbit/s E1 formats.

Page 25

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

7

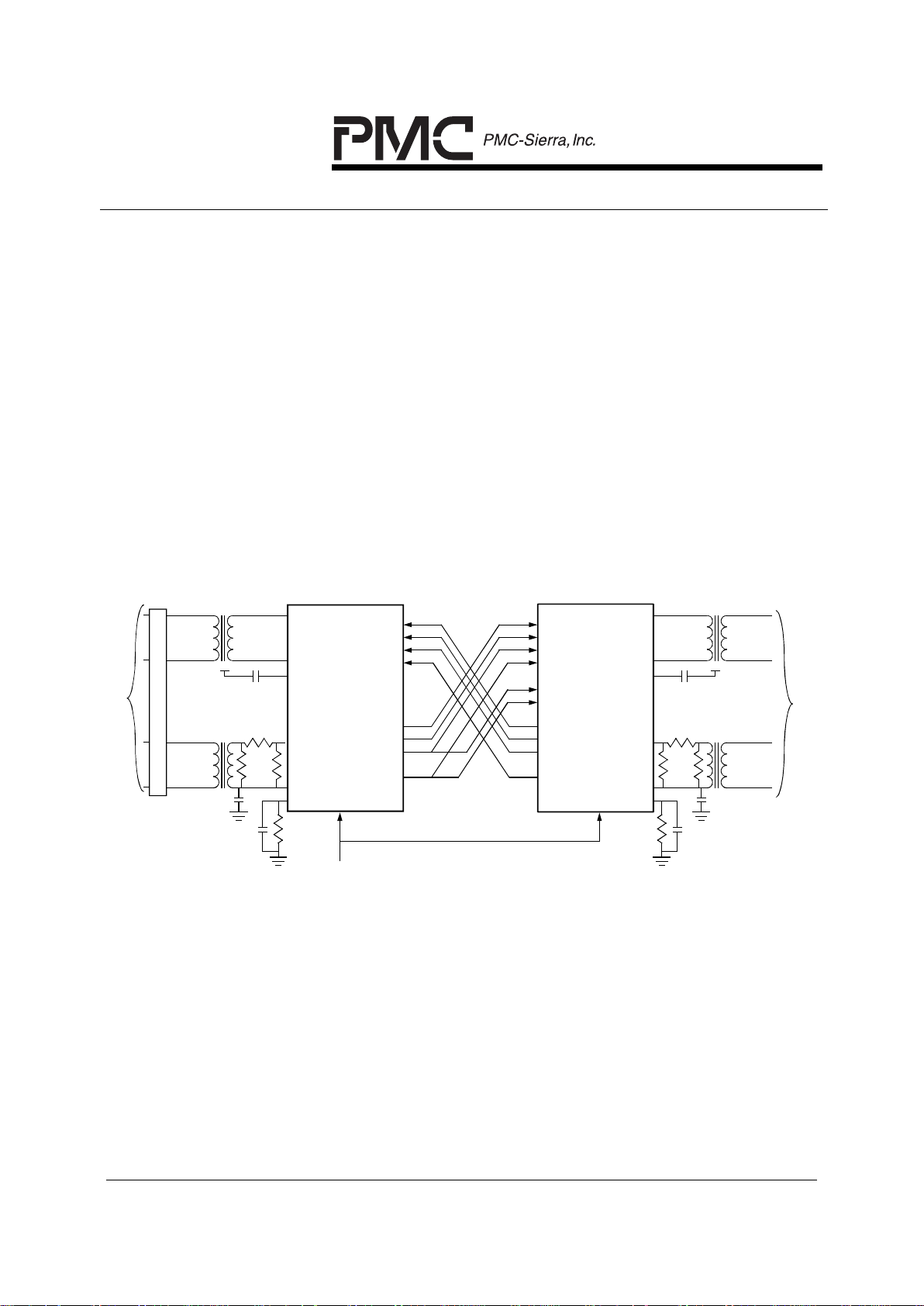

Figure 2 - Example 2. DSX-1/0 Cross-connect

MT8980 DX

PM4341A T1XC

AVS

AVS

4.

0

96

M

H

z

D

AVD

+

to

tr

an

sc

ei

ve

rs

#

3

& 4

to

tr

an

sc

ei

ve

rs

#

3

& 4

#1

fro

m

tr

an

sc

ei

ve

r

#3

fro

m

tr

an

sc

ei

ve

r

#4

PM4341A T1XC

#2

AVS

AVS

AVD

+

D

D

Glu

e

log

ic

ca

n

be

im

pl

eme

nt

ed

us

in

g o

ne

74HCT00 and

one 74HCT

175 pack.

2.048MHz

DSX-1

Tr

an

sm

it

STi

0

STi

1

STi

2

STi

3

STi

4

STi

5

STi

6

STi7F0i

C4i

STo0

STo1

STo2

STo3

STo4

STo5

STo6

STo7

CSTo

ODE

CS

DS

R/W

DTA

A[5:0

]

D[7:0

]

BTPCM

BTS

IG

BTFP

BTCLK

BRCLK

BRFP

I

BRPCM

BRS

IG

BRFPO

TAP

TAN

TC

RAS

REF

RRC

DSX-1

Re

c

e

iv

e

Q

QB

BRPCM

BRS

IG

BRPCM

BRS

IG

BTPCM

BTS

IG

BTFP

BTCLK

BRCLK

BRFP

I

BRPCM

BRS

IG

BRFPO

TAP

TAN

TC

RAS

REF

RRC

DSX-1

Tr

an

sm

it

D

S

X

-1

R

eceive

Sys

te

m

Fr

am

e

Pu

ls

e

Q

QB

Q

QB

Page 26

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

8

Example 2 shows a DSX 1/0 Cross-Connect utilizing four T1XC chips and a Mitel

MT8980 Digital Time/Space Switch to implement a simple 1/0 cross-connect. An

alternate architecture could use two MT8980s, one as a voice switch and the

other as a signalling switch, and 8 T1XCs to cross-connect eight T1s. (Note: a

true implementation would require redundancy in the switch core.)

In this example, the T1XC chips are programmed to receive and generate the

same framing format, using the 2.048 MHz backplane data rate. The "system

frame pulse" signal is stretched through the two D-FF into a pulse of 488ns

duration, which is used to frame align the data out of each transceiver through

the elastic store and to provide frame alignment indication to the transmitters.

The raw system frame pulse signal is used to indicate frame alignment

synchronization to the MT8980. Another D-FF is configured as a toggle to

generate a 2.048MHz clock from the system 4.096MHz clock source,

synchronized to the system frame pulse.

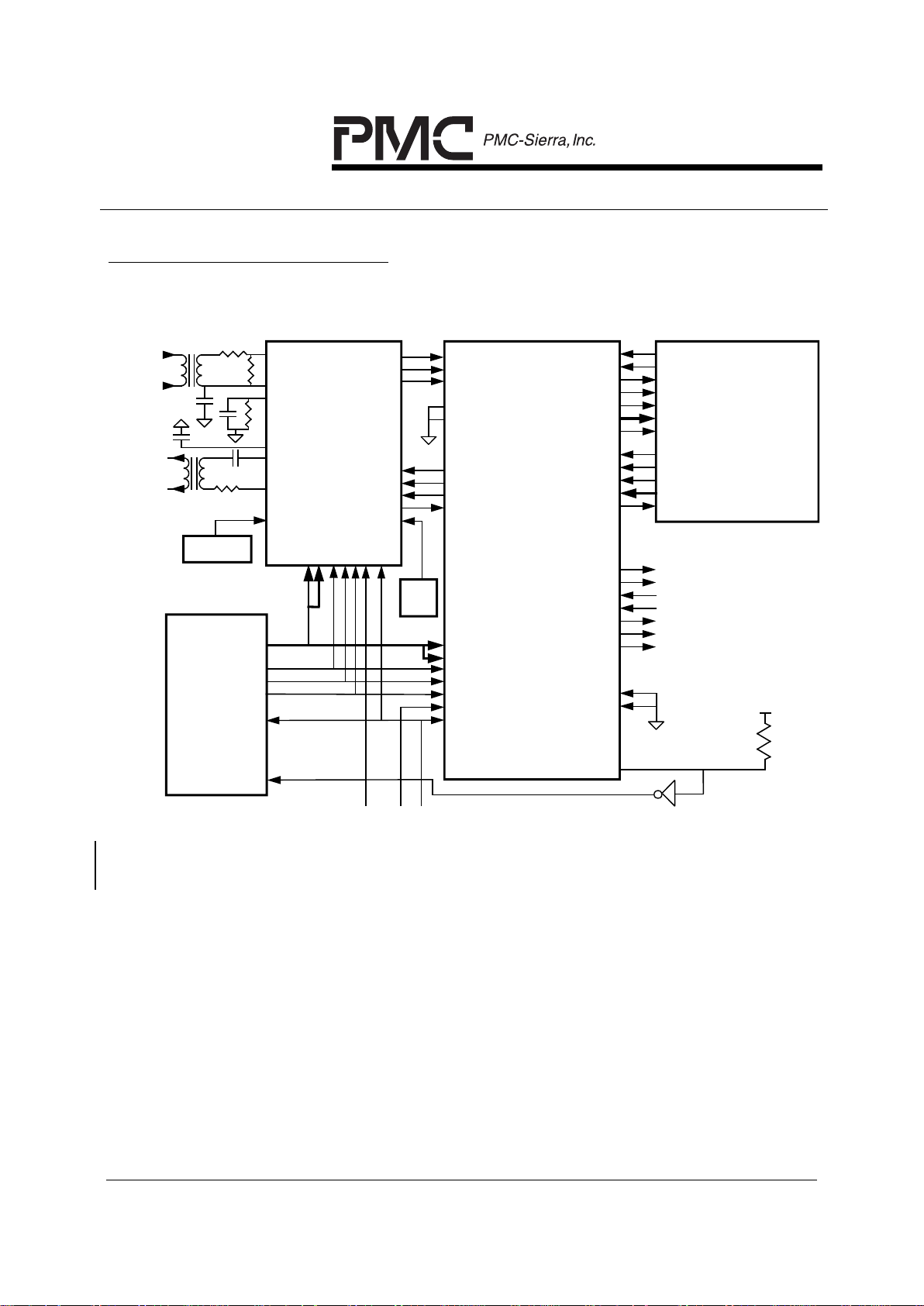

Figure 3 - Example 3. Multi-featured, jitter attenuating CSU

DSX-1

Transmit

PM4

34

1A

T

1XC

BTPCM

BTSIG

BTFP

BTCLK

BRFPI

BRCLK

BRPCM

BRSIG

BRFPO

RCLKO

TAP

TAN

RAS

REF

RRC

DSX-1

Receive

AVS

AVS

AVD

+

#1

DSX-1

Transmit

PM4

34

1A

T

1XC

BTPCM

BTSIG

BTFP

BTCLK

BRFPI

BRCLK

BRPCM

BRSIG

BRFPO

RCLKO

TAP

TAN

RAS

REF

RRC

DSX-1

Receive

AVS

AVS

AVD

+

#2

N

e

t

w

o

r

k

C

u

s

t

o

m

e

r

XCLKXCLK

37.056MHz

Networ

k inte

rface

unit

TC

TC

Example 3 is an application utilizing 2 T1XC chips to implement a multi-featured

Channel Service Unit with jitter attenuation. The T1XCs are programmed to

receive and generate the same framing format, using the 1.544 MHz backplane

data rate with the Elastic Stores bypassed.

T1XC #1's Timing Options Register is programmed to enable jitter attenuation of

the outgoing transmit data to the network, using the backplane transmit clock

(BTCLK= recovered clock from customer interface) as the jitter reference.

Similarly, T1XC #2 is programmed to attenuate the outgoing transmit data jitter to

the customer equipment using its backplane transmit clock (BTCLK= recovered

Page 27

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

9

clock from network interface) as the jitter reference. Also, since T1XC #2's elastic

store is bypassed, the TRSLIP bit in the Receive Options register can be set to

provide a measure of the frequency difference between the network clock and

the customer clock by monitoring the time interval between resulting slip

indications.

This application can be readily modified to provide additional features by simply

changing the T1XC configurations via software. No external wiring changes are

necessary to support framing format conversion or to loop time the network

transmit data to the network receive recovered clock.

For example, to provide format conversion of a customer's SF-based equipment

to an ESF network, T1XC #1 would be programmed to receive and transmit ESF

formatted data, while providing superframe alignment indication on the

backplane frame pulse output (BRFPO). T1XC #2 would be programmed to

receive and transmit SF formatted data, while providing every second

superframe alignment indication on its BRFPO. To provide loop timing of the

network transmit to the network receive clock, T1XC #2 would be programmed to

use the elastic store, thereby providing the slip buffering to handle the frequency

difference between the network and customer equipment clocks. T1XC #1 would

be programmed to use its RCLKO for the transmitter clock instead of the input

BTCLK.

Page 28

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

10

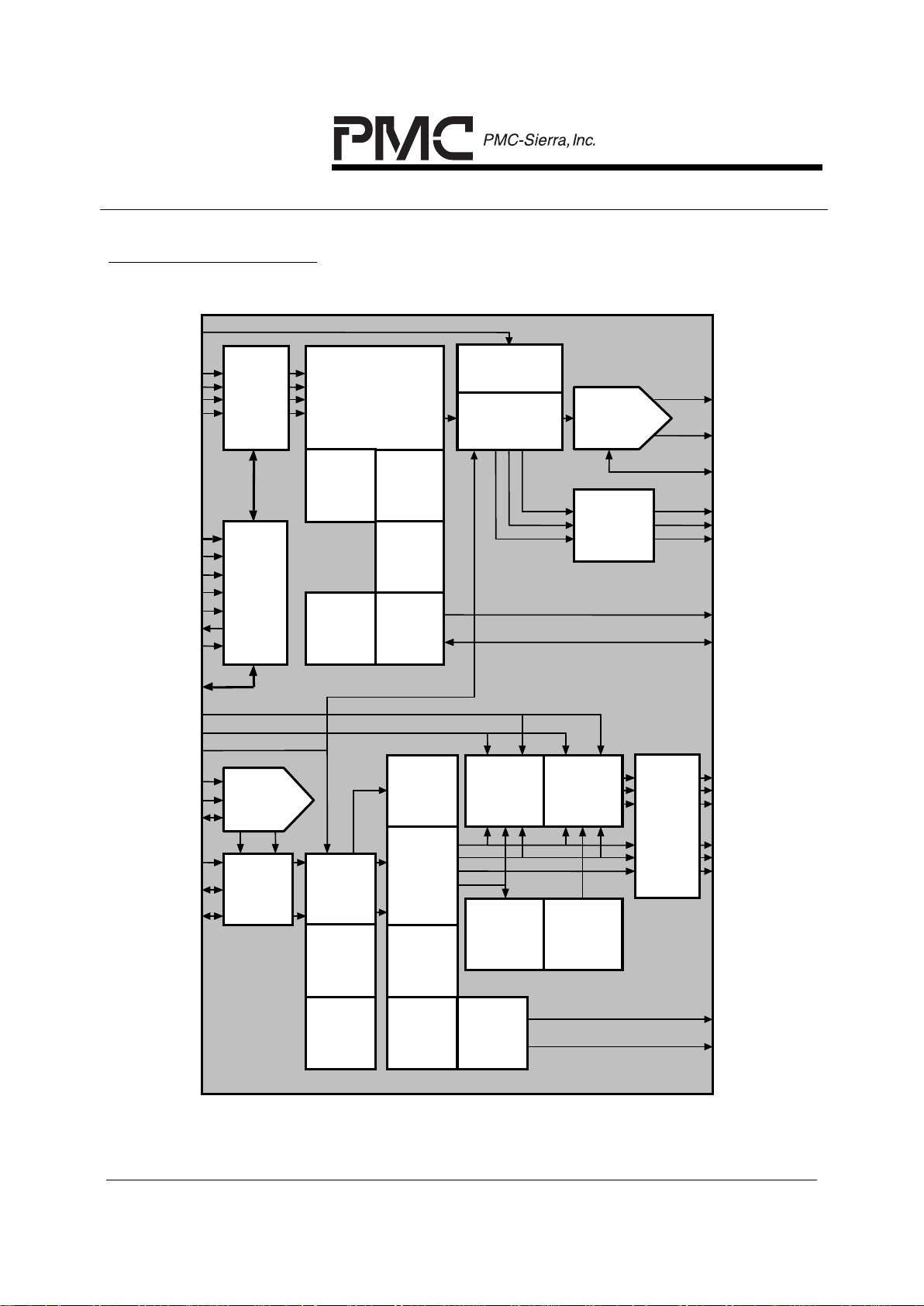

4

BLOCK DIAGRAM

CDRC

CLOCK AND

DATA

RECOVERY

PMON

PER-

FORMANCE

MONITOR

COUNTERS

ALMI

ALARM

INTE-

GRATOR

BRIF

BACK-

PLANE

RECEIVE

INTER-

FACE

BRPCM/BRDP

BRSIG/BRDN

BRFPO

RCLKO

RFP

RDPCM/RPCM

RDLCLK/

RDLEOM

RDLSIG/

RDLINT

TDP/TDD

TCLKO

TDN/TFLG

TAN

TAP

TDLSIG/

TDLINT

TDLCLK/

TDLUDR

TC

TOPS

TIMING

OPTIONS

DJAT

DIGITAL

JITTER

ATTENUATOR

XIBC

IN-BAND

LOOPBACK

CODE

GENERATOR

XBAS

BASICTRANSMITTER:

FRAME GENERATION,

ALARM INSERTION,

TRUNK CONDITIONING

LINE CODING

TPSC

PER-CHAN

CONT:

SIG,IDLE,

ZERO CO NT

DTIF

DIGITAL DS-1

TRANSMIT

INTERFACE

XPLS

ANALOG

DSX-1 PULSE

GENERATOR

XCLK/VCLK

BRFPI

BRCLK

RCLKI

RDP/RDD/

SDP

RDN/RLCV/

SDN/

RAS

REF

RRC

TCLKI

BTPCM/BTDP

BTCLK

BTSIG/BTDN

BTFP

INTB

D(7-0)

A(7-0)

RDB

WRB

CSB

ALE

RSTB

MPIF

MICRO-

PROCESS-

OR

INTERFACE

RECEIVER

TRANSMITTER

XPDE

PULSE

DENSITY

ENFORCER

XFDL

HDLC

TRANSMITTER

XBOC

BIT-

ORIENTED

CODE GEN.

PDVD

PULSE

DENSITY

VIOLATION

DETECTOR

RFDL

HDLC

RECEIVER

RBOC

BIT-

ORIENTED

CODE

DETECTOR

IBCD

IN-BAND

LOOPBACK

CODE

DETECTOR

FRAM

FRAMER/

SLIP BUFFER

RAM

RPSC

PER-CHANNEL

CONTROL:

TRUNK

CONDITION

DRIF

DIGITAL

DS-1 RX

INTER-

FACE

FRMR

FRAMER:

FRAME

ALIGNMENT,

ALARM

EXTRACT

RSLC

ANALOG

DSX-1 PULSE

SLICER

ELST

ELASTIC

STORE

SIGX

SIGNALLING

EXTRACT-

OR

BTIF

BACK-

PLANE

TRANSMIT

INTER-

FACE

TOPS

TIMING

OPTIONS

Page 29

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

11

5

DESCRIPTION

The PM4341A Single T1 Framer/Transceiver (T1XC) is a feature-rich device

suitable for use in many T1 systems with a minimum of external circuitry. The

T1XC is software configurable, allowing feature selection without changes to

external wiring.

On the receive side, the T1XC recovers clock and data and can be configured to

frame to any of the common DS-1 signal formats: SF, ESF, T1DM (DDS), or

SLC®96. Analog circuitry is provided to allow direct reception of a DSX-1

compatible signal up to 655 feet from the cross-connect by using only an external

transformer and passive components. The T1XC also supports detection of

various alarm conditions such as loss of signal, pulse density violation, red

alarm, yellow alarm, and AIS alarm. The T1XC detects and indicates the

presence of yellow and AIS patterns and also integrates yellow, red, and AIS

alarms as per industry specifications.

Performance monitoring with accumulation of CRC-6 errors, framing bit errors,

line code violations, and loss of frame events is provided. The T1XC also detects

the presence of in-band loopback codes, ESF bit oriented codes, and detects

and terminates HDLC messages on the ESF data link. An elastic store for slip

buffering and adaptation to backplane timing is provided, as is a signalling

extractor that supports signalling debounce, signalling freezing, idle code

substitution, digital milliwatt tone substitution, data inversion, and signalling bit

fixing on a per-channel basis. Receive side data and signalling trunk

conditioning is also provided.

On the transmit side, the T1XC generates framing for SF, ESF, T1DM (DDS), and

SLC®96 DS1 formats, or framing can be optionally disabled. Internal analog

circuitry allows direct transmission of a DSX-1 compatible signal using only an

external transformer. Digitally programmable line build out allows transmission of

DSX-1 compatible signals up to 655 feet from the cross-connect. The T1XC also

supports signalling insertion, idle code substitution, digital milliwatt tone

substitution, data inversion, and zero code suppression on a per-channel basis.

The zero code suppression is selectable to Bell (bit 7), GTE, or DDS standards,

and can also be disabled. Transmit side data and signalling trunk conditioning is

provided.

The T1XC can also generate in-band loopback codes, ESF bit oriented codes,

and transmit HDLC messages on the ESF data link. The T1XC can generate a

low jitter transmit clock and provides a FIFO for transmit jitter attenuation. When

not used for jitter attenuation, the full or empty status of this FIFO is made

Page 30

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

12

available to facilitate higher order multiplexing applications by controlling bitstuffing logic.

The T1XC provides both a parallel microprocessor interface for controlling the

operation of the T1XC device, and serial PCM interfaces that allow 1.544 Mbit/s

or 2.048 Mbit/s backplanes to be directly supported. Tolerance of gapped clocks

allows other backplane rates to be supported with a minimum of external logic.

Page 31

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

13

6

PIN DIAGRAM

Figure 4 - 68 Pin PLCC

PM4341A

9 8 7 6 5 4 3 2 1 6867 66656463 6261

XCLK/VCLK

BTPCM/BTDP

BTSIG/BTDN

BTFP

BTCLK

TCLKI

TCLKO

TDP/TDD

VSSO[0]

VDDO[0]

TDN/TFLG

TDLCLK/TDLUDR

TDLSIG/TDLINT

TAVS

TAVD

TAN

VDDO[3]

27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

ALE

BRFPI

BRCLK

RFP

RDLCLK/RDLEOM

RDLSIG/RDLINT

RCLKO

RDPCM/RPCM

VSSO[2]

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

CSB

RSTB

INTB

D[0]

D[1]

D[2]

D[3]

VSSO[1]

VSSI[0]

VDDI[0]

VDDO[1]

D[4]

D[5]

D[6]

D[7]

RDB

WRB

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

VSSO[3]

TC

TAP

RAVD

RAVS

RAS

RRC

REF

VSSI[1]

VDDI[1]

RCLKI

BRFPO

BRPCM/BRDP

BRSIG/BRDN

RDP/RDD/SDP

RDN/RLCV/SDN

VDDO[2]

(TOP VIEW)

Page 32

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

Figure 5 - 80 Pin PQFP

(TOP VIEW)

PM4341A

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

NC

CSB

RSTB

INTB

D[0]

D[1]

D[2]

D[3]

VSSO[1]

VSSI[0]

VDDI[0]

VDDO[1]

D[4]

D[5]

D[6]

D[7]

RDB

WRB

NC

NC

NC

NC

VSSO[3]

TC

TAP

RAVD

RAVS

RAS

RRC

REF

VSSI[1]

VDDI[1]

RCLKI

BRFPO

BRPCM/BRDP

BRSIG/BRDN

RDP/RDD/SDP

RDN/RLCV/SDN

VDDO[2]

NC

22232425262728293031323334353637383940

21

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

ALE

BRFPI

BRCLK

RFP

RDLCLK/RDLEOM

RDLSIG/RDLINT

RCLKO

RDPCM/RPCM

VSSO[2]

NC

NC

NC

79787776757473727170696867666564636261

80

NC

XCLK/VCLK

BTPCM/BTDP

BTSIG/BTDN

BTFP

BTCLK

TCLKI

TCLKO

TDP/TDD

VSSO[0]

VDDO[0]

TDN/TFLG

TDLCLK/TDLUD

R

TDLSIG/TDLINT

TAVS

TAVD

TANNCVDDO[3]

NC

Page 33

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

15

7

PIN DESCRIPTION

Pin Pin No.

Name Type PQFP PLCC Function

RDP/ I/O 44 46 Receive Digital Positive Line Pulse

(RDP). This input is available when the

T1XC is configured to receive dual-rail

formatted data. The RDP input can be

enabled for either RZ or NRZ waveforms.

When enabled for NRZ, this input may

be enabled to be sampled on the rising

or falling edge of RCLKI. When enabled

for RZ, clock is recovered from the RDP

and RDN inputs.

RDD/ Receive Digital DS-1 Signal (RDD).

When the T1XC is configured to receive

single-rail data, this input may be enabled

to be sampled on the rising or falling

edge of RCLKI.

SDP Sliced Positive Line Pulse (SDP). This

pin becomes an output when the receive

analog line interface is powered up. A

positive pulse on the SDP output

corresponds to the sampled positive

pulse excursion on the RAS input.

RDN/ I/O 43 45 Receive Digital Negative Line Pulse

(RDN). This input is available when the

T1XC is configured to receive dual-rail

formatted data. The RDN input can be

enabled for either RZ or NRZ waveforms.

When enabled for NRZ, this input may

be enabled to be sampled on the rising

or falling edge of RCLKI. When enabled

for RZ, clock is recovered from the RDP

and RDN inputs.

Page 34

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

16

Pin Pin No.

Name Type PQFP PLCC Function

RLCV/ I/O 43 45 Receive Line Code Violation Indication

(RLCV). When the T1XC is configured to

receive single-rail data, this input may be

enabled to be sampled on the rising or

falling edge of RCLKI.

SDN Sliced Negative Line Pulse (SDN). This

pin becomes an output when the receive

analog line interface is powered up. A

positive pulse on the SDN output

corresponds to the sampled negative

pulse excursion on the RAS input.

RCLKI Input 48 50 Receive Line Clock Input (RCLKI). This

input is an externally recovered 1.544

MHz line clock that may be enabled to

sample the RDP and RDN inputs on its

rising or falling edge when the input

format is enabled for dual-rail NRZ; or to

sample the RDD and RLCV inputs on its

rising or falling edge when the input

format is enabled for single-rail.

RAS Input 53 55 Receive Analog Signal (RAS). This

analog input samples the AC signal on

an external isolation transformer. It is

connected to the positive lead of the

transformer secondary through a passive

attenuation network.

REF I/O 51 53 Receive Reference (REF). This analog

bidirectional pin provides DC bias to an

external isolation transformer. It is

connected to the negative lead of the

transformer secondary and to a

decoupling capacitor to RAVS.

Page 35

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

17

Pin Pin No.

Name Type PQFP PLCC Function

RRC I/O 52 54 Receive Peak Hold R-C Network (RRC).

This analog bidirectional pin is connected

to an external parallel resistor/capacitor

network to RAVS. This network is

necessary to the operation of the internal

peak detector that tracks the incoming

signal level.

RAVD Power 55 57 Receive Analog Power (RAVD). This pin

provides the +5V supply to the receive

analog line interface. If the receive

analog line interface is not used, the

power consumption of the T1XC can be

reduced by connecting the RAVD pin to

the analog ground pin, RAVS. RAVD

must be connected to a common, well

decoupled +5 VDC supply together with

the VDDO[2:0] and VDDI[1:0] pins. Care

must be taken to avoid coupling noise

induced on the VDDO and VDDI pins into

the RAVD pin.

RAVS Ground 54 56 Receive Analog Ground (RAVS). This pin

provides the ground supply to the receive

analog line interface. RAVS must be

connected to a common ground together

with the VSSO[2:0] and VSSI[1:0] pins.

Care must be taken to avoid coupling

noise induced on the VSSO and VSSI

pins into the RAVS pin.

RCLKO Output 36 41 Recovered PCM Clock Output (RCLKO).

This output signal is the recovered 1.544

MHz clock, synchronized to the XCLK

signal. The RCLKO signal is recovered

from the received analog inputs (if the

interface is powered up), from the RDP

and RDN inputs (if the input format is

dual-rail RZ), or from the RCLKI input (if

the input format is NRZ).

Page 36

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

18

Pin Pin No.

Name Type PQFP PLCC Function

RDPCM/ Output 37 42 Recovered Decoded PCM (RDPCM).

This output is available when the T1XC is

configured for decoded data output. This

NRZ output signal is the recovered data

stream with B8ZS decoding applied, if

B8ZS decoding is enabled. It is updated

on the falling edge of RCLKO. The

RDPCM signal is not meant to be used

when the digital receive interface is

configured for uni-polar operation since

this data should be available at the RDD

input.

RPCM Recovered PCM (RPCM). This output is

available when the T1XC is configured for

raw data output. This NRZ output signal

is the recovered data stream without

optional B8ZS decoding applied. It is

updated on the falling edge of RCLKO.

Page 37

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

19

Pin Pin No.

Name Type PQFP PLCC Function

RFP Output 33 38 Receive Frame Pulse (RFP). When the

T1XC is configured for receive frame

pulse output, RFP pulses high for 1

RCLKO cycle during bit 1 of each 193-bit

frame, indicating the frame alignment of

the RPCM/RDPCM data stream. RFP

does not indicate the frame alignment in

RDPCM when the digital receive

interface is configured for unipolar

operation (i.e. RUNI=1and RDIEN=1 in

Register 03h).

When configured for receive superframe

output, RFP pulses high for 1 RCLKO

cycle during bit 1 of frame 1 of the 12 or

24 frame superframe, indicating the

superframe alignment of the

RPCM/RDPCM data stream.

When configured for receive alternate

superframe output, RFP pulses high for 1

RCLKO cycle during bit 1 of frame 1 of

every second 12 or 24 frame superframe,

indicating the superframe alignment of

the RPCM/RDPCM data stream. This

alternate superframe indication is useful

for performing format conversion from SF

to ESF while maintaining the same

superframe alignment.

RFP is updated on the falling edge of

RCLKO.

Page 38

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

20

Pin Pin No.

Name Type PQFP PLCC Function

RDLSIG/ Output 35 40 Receive Data Link Signal (RDLSIG). The

RDLSIG signal is available on this output

when the internal HDLC receiver (RFDL)

is disabled from use, or, optionally, when

the D-channel of the Primary Rate

interface is extracted. When the T1XC is

configured to receive ESF formatted

data, the RDLSIG contains the data

stream extracted from the facility data

link; when the T1XC is configured to

receive SF formatted data, the RDLSIG

output is held low; when the T1XC is

configured to receive T1DM, RDLSIG

reflects the value of the R-bit in the T1DM

sync word; when the T1XC is configured

for SLC®96, RDLSIG contains the value

of the Fs framing bits. When the Dchannel is enabled for extraction,

RDLSIG contains the contents of channel

24 of each DS-1 frame. RDLSIG is

updated on the falling edge of RDLCLK.

RDLINT Receive Data Link Interrupt (RDLINT).

The RDLINT signal is available on this

output when RFDL is enabled. RDLINT

goes high when an event occurs which

changes the status of the HDLC receiver.

Page 39

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

21

Pin Pin No.

Name Type PQFP PLCC Function

RDLCLK/ Output 34 3 9 Re ceive Data Link Clock (RDLCLK). The

RDLCLK signal is available on this output

when the internal HDLC receiver (RFDL)

is disabled from use, or, optionally, when

the D-channel of the Primary Rate

interface is extracted. RDLCLK is used

to process the data stream contained on

the RDLSIG output. When the T1XC is

configured to receive SF formatted data,

the RDLCLK output is held low. In all

other formats the rising edge of RDLCLK

can be used to sample the data on

RDLSIG.

RDLEOM Receive Data Link End of Message

(RDLEOM). The RDLEOM signal is

available on this output when RFDL is

enabled. RDLEOM goes high when the

last byte of a received sequence is read

from the RFDL FIFO buffer, or when the

FIFO buffer is overrun.

BRPCM/ Output 46 48 Backplane Receive PCM (BRPCM). The

BRPCM signal is available on this output

when the backplane is configured for

single-rail output. BRPCM contains the

recovered data stream passed through

ELST, SIGX, and the RPSC. When the

ELST is not by-passed, the BRPCM

stream is aligned to the backplane timing

and is updated on the falling edge of

BRCLK. When the ELST is by-passed,

BRPCM is aligned to the receive line

timing and is updated on the falling edge

of RCLKO.

Page 40

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

22

Pin Pin No.

Name Type PQFP PLCC Function

BRDP Output 46 48 Backplane Receive Positive Line Pulse

(BRDP). The BRDP signal is available on

this output when the backplane is

configured for dual-rail output. The

BRDP NRZ output represents the RZ

receive digital positive pulse signal

extracted from the input bipolar signal.

BRDP is updated on the falling edge of

RCLKO.

BRSIG/ Output 45 47 Backplane Receive Signalling (BRSIG).

The BRSIG signal is available on this

output when the backplane is configured

for single-rail output. BRSIG contains the

extracted signalling bits for each channel

in the frame, repeated for the entire

superframe. Each channel's signalling

bits are valid in bit locations 5,6,7,8 of the

channel and are channel-aligned with the

BRPCM data stream. When the ELST is

not by-passed, the BRSIG stream is

aligned to the backplane timing and is

updated on the falling edge of BRCLK.

When the ELST is by-passed, BRSIG is

aligned to the receive line timing and is

updated on the falling edge of RCLKO.

BRDN Backplane Receive Negative Line Pulse

(BRDN). The BRDN signal is available

on this output when the backplane is

configured for dual-rail output. The

BRDN NRZ output represents th e RZ

receive digital negative pulse signal

extracted from the input bipolar signal.

BRDN is updated on the falling edge of

RCLKO.

Page 41

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

23

Pin Pin No.

Name Type PQFP PLCC Function

BRFPO Output 47 49 Backplane Frame Pulse Output

(BRFPO). When the T1XC is configured

for backplane receive frame pulse output,

BRFPO pulses high for 1 BRCLK cycle

(or 1 RCLKO cycle if ELST is by-passed)

during bit 1 of each 193-bit frame,

indicating the frame alignment of the

BRPCM data stream.

When configured for backplane receive

superframe output, BRFPO pulses high

for 1 BRCLK cycle (or 1 RCLKO cycle if

ELST is by-passed) during bit 1 of frame

1 of the 12 or 24 frame superframe,

indicating the superframe alignment of

the BRPCM data stream.

When configured for backplane alternate

receive superframe output, BRFPO

pulses high for 1 BRCLK cycle (or 1

RCLKO cycle if ELST is by-passed)

during bit 1 of frame 1 of every second

12 or 24 frame superframe, indicating the

superframe alignment of the BRPCM

data stream. This alternate superframe

indication is useful for performing format

conversion from SF to ESF while

maintaining the same superframe

alignment.

BRFPO is updated on the falling edge of

BRCLK or RCLKO.

BRCLK Input 32 37 Backplane Receive Clock (BRCLK). This

clock should be either 1.544MHz or

2.048MHz with optional gapping for

adaptation to non-uniform backplane

data streams. The T1XC may be

configured to ignore the BRCLK input

and use the RCLKO signal in its place

when the ELST is bypassed.

Page 42

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

24

Pin Pin No.

Name Type PQFP PLCC Function

BRFPI Input 31 36 Backplane Frame Pulse Input (BRFPI).

This input is used to frame align the

received data to the system backplane. If

frame alignment only is required, a pulse

at least 1 BRCLK cycle wide must be

provided on BRFPI every 193 bit times. If

receive signalling alignment is required,

receive signalling alignment must be

enabled, and a pulse at least 1 BRCLK

cycle wide must be provided on BRFPI

every 12 or 24 frame times. BRFPI is

sampled on the rising edge of BRCLK.

BTPCM/ Input 77 8 Backplane Transmit PCM (BTPCM). The

non-return to zero, digital data stream to

be transmitted is input on this pin when

the backplane is configured for single-rail

input. The BTPCM signal is sampled on

the rising edge of BTCLK.

BTDP Backplane Transmit Positive Line Pulse

(BTDP). The positive pulse of the dualrail signal to be transmitted is input on

this pin when the backplane is configured

for dual-rail input. In dual-rail input mode,

the BTDP input by-passes the

transmitter and is fed directly into the

DJAT. BTDP is sampled on the rising

edge of BTCLK.

Page 43

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

25

Pin Pin No.

Name Type PQFP PLCC Function

BTSIG/ Input 76 7 Backplane Transmit Signalling (BTSIG).

The BTSIG input signal contains the

signalling bits for each channel in the

transmit data frame, repeated for the

entire superframe. This signal is input on

the BTSIG pin when the backplane is

configured for single-rail input. Each

channel's signalling bits are in bit

locations 5,6,7,8 of the channel and are

channel-aligned with the BTPCM data

stream. BTSIG is sampled on the rising

edge of BTCLK.

BTDN Backplane Transmit Negative Line Pulse

(BTDN). The negative pulse of dual-rail

signal to be transmitted is input on this

pin when the backplane is configured for

dual-rail input. In dual-rail input mode,

the BTDN input by-passes the

transmitter and is fed directly into the

DJAT. BTDN is sampled on the rising

edge of BTCLK.

BTFP Input 75 6 Backplane Transmit Frame Pulse (BTFP).

This input is used to frame align the

transmitter to the system backplane. If

frame alignment only is required, a pulse

at least 1 BTCLK cycle wide must be

provided on BTFP every 193 bit times. If

superframe alignment is required,

transmit superframe alignment must be

enabled, and a pulse at least 1 BTCLK

cycle wide must be provided on BTFP

every 12 or 24 frame times.

Page 44

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

26

Pin Pin No.

Name Type PQFP PLCC Function

BTCLK Input 74 5 Backplane Transmit Clock (BTCLK). This

clock should be either 1.544MHz or

2.048MHz with optional gapping for

adaptation from non-uniform backplane

data streams. The T1XC may be

configured to ignore the BTCLK input

and use the RCLKO signal in its place.

TDLSIG/ I/O 66 65 Transmit Data Link Signal (TDLSIG). The

TDLSIG signal is input on this pin when

the internal HDLC transmitter (XFDL) is

disabled from use. TDLSIG is the source

for the data stream to be inserted into the

ESF data link. When the T1XC is

configured to transmit SLC®96

formatted data, the TDLSIG input is the

source for the Fs framing bits; when the

T1XC is configured to transmit T1DM

with R-bit replacement, TDLSIG is the

source of the R-bit in the T1DM sync

word. TDLSIG is sampled on the rising

edge of TDLCLK.

TDLINT Transmit Data Link Interrupt (TDLINT).

The TDLINT signal is output on this pin

when XFDL is enabled. TDLINT goes

high when the last data byte written to

the XFDL has been set up for

transmission and processor intervention

is required to either write control

information to end the message, or to

provide more data.

Page 45

PM4341A T1XC

DATA SHEET

PMC-900602 ISSUE 7 T1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

27

Pin Pin No.

Name Type PQFP PLCC Function

TDLCLK/ Output 67 66 Transmit Data Link Clock (TDLCLK). The

TDLCLK signal is available on this output

when the internal HDLC transmitter

(XFDL) is disabled from use. The rising