Datasheet PIC 18F24K50 Datasheet

PIC18(L)F2X/45K50

28/40/44-Pin, Low-Power, High-Performance

Microcontrollers with XLP Technology

Universal Serial Bus Features:

• USB V2.0 Compliant

• Crystal-less Full Speed (12 Mb/s) and Low-Speed

Operation (1.5 Mb/s)

• Supports Control, Interrupt, Isochronous and Bulk

Transfers

• Supports up to 32 Endpoints (16 Bidirectional)

• 1 Kbyte Dual Access RAM for USB

• On-Chip USB Transceiver

Flexible Oscillator Struc ture:

• 3x and 4xPLL Clock Multipliers

• Two External Clock modes, Up to 48 MHz (12

MIPS)

• Internal 31 kHz Oscillator

• Internal Oscillator, 31 kHz to 16 MHz

- Factory calibrated to ± 1%

- Self-tune to ± 0.20% max. from USB or

secondary oscillator

• Secondary Oscillator using Timer1 @ 32 kHz

• Fail-Safe Clock Monitor:

- Allows for safe shutdown if any clock stops

Peripheral Highlights:

• Up to 33 I/O pins plus 3 Input-Only Pins:

- High-current Sink/Source 25 mA/25 mA

- Three programmable external interrupts

- 11 programmable interrupts-on-change

- 9 programmable weak pull-ups

- Programmable slew rate

•SR Latch

• Enhanced Capture/Compare/PWM (ECCP)

module:

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-shutdown and auto-restart

- Pulse steering control

• Capture/Compare/PWM (CCP) module

• Master Synchronous Serial Port (MSSP) module

Supporting 3-Wire SPI (all 4 modes) and I

Master and Slave modes

• Two Analog Comparators with Input Multiplexing

• 10-Bit Analog-to-Digital (A/D) Converter module:

- Up to 25 input channels

- Auto-acquisition capability

- Conversion available during Sleep

2

C™

• Digital-to-Analog Converter (DAC) module:

- Fixed Voltage Reference (FVR) with 1.024V,

2.048V and 4.096V output levels

- 5-bit rail-to-rail resistive DAC with positive

and negative reference selection

• High/Low-Voltage Detect module

• Charge Time Measurement Unit (CTMU):

- Supports capacitive touch sensing for touch

screens and capacitive switches

• Enhanced USART module:

- Supports RS-485, RS-232 and LIN/J2602

- Auto-wake-up on Start bit

- Auto-Baud Detect

Extreme Low-Power Management with XLP:

• Sleep mode: 20 nA, typical

• Watchdog Timer: 300 nA, typical

• Timer1 Oscillator: 800 nA @ 32 kHz

• Peripheral Module Disable

Special Microcontroller Features:

• Low-Power, High-Speed CMOS Flash Technology

• C Compiler Optimized Architecture for Re-Entrant

Code

• Power Management Features:

- Run: CPU on, peripherals on, SRAM on

- Idle: CPU off, peripherals on, SRAM on

- Sleep: CPU off, peripherals off, SRAM on

• Priority Levels for Interrupts

• Self-Programmable under Software Control

• 8 x 8 Single-Cycle Hardware Multiplier

• Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 131s

• Single-Supply In-Circuit Serial Programming™

(ICSP™) via Two Pins

• In-Circuit Debug (ICD) with Three Breakpoints via

Two Pins

• Optional dedicated ICD/ICSP Port (44-pin TQFP

Package Only)

• Wide Operating Voltage Range:

- F devices: 2.3V to 5.5V

- LF devices: 1.8V to 3.6V

• Flash Program Memory of 10,000 Erase/Write

Cycles Minimum and 20-year Data Retention

2012 Microchip Technology Inc. DS30684A-page 1

PIC18(L)F2X/45K50

10

11

2

3

4

5

6

1

8

7

9

12

13

14

15

16

17

18

19

20

23

24

25

26

27

28

22

21

MCLR/VPP/RE3

RA0

RA1

RA2

RA3

RA4

RA5

V

SS

RA7

RA6

RC0

RC1

RC2

V

USB3V3

RB7

RB6

RB5

RB4

RB3

RB2

RB1

RB0

V

DD

VSS

RC7

RC6

D+

D-

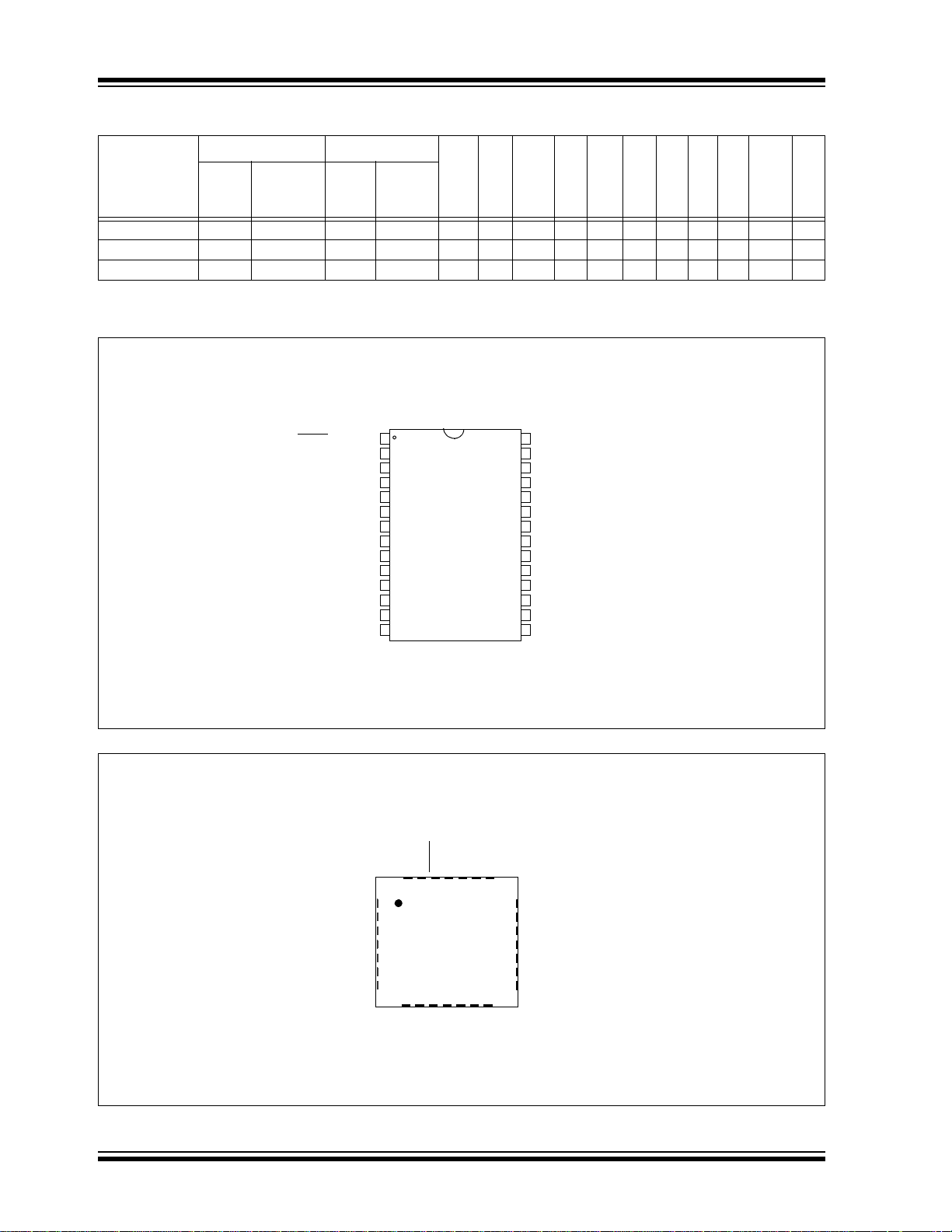

28-PIN PDIP (300 MIL), SOIC, SSOP

PIC18(L)F2XK50

10

11

2

3

6

1

18

19

20

21

27

12

13

14

15

8

7

16

17

26

252423

22

28

9

RC0

5

4

RB7

RB6

RB5

RB4

RB3

RB2

RB1

RB0

V

DD

VSS

RC7

RC6

D+

D-

MCLR

/VPP/RE3

RA0

RA1

RA2

RA3

RA4

RA5

V

SS

RA7

RA6

RC1

RC2

V

USB3V3

PIC18(L)F2XK50

28-PIN QFN

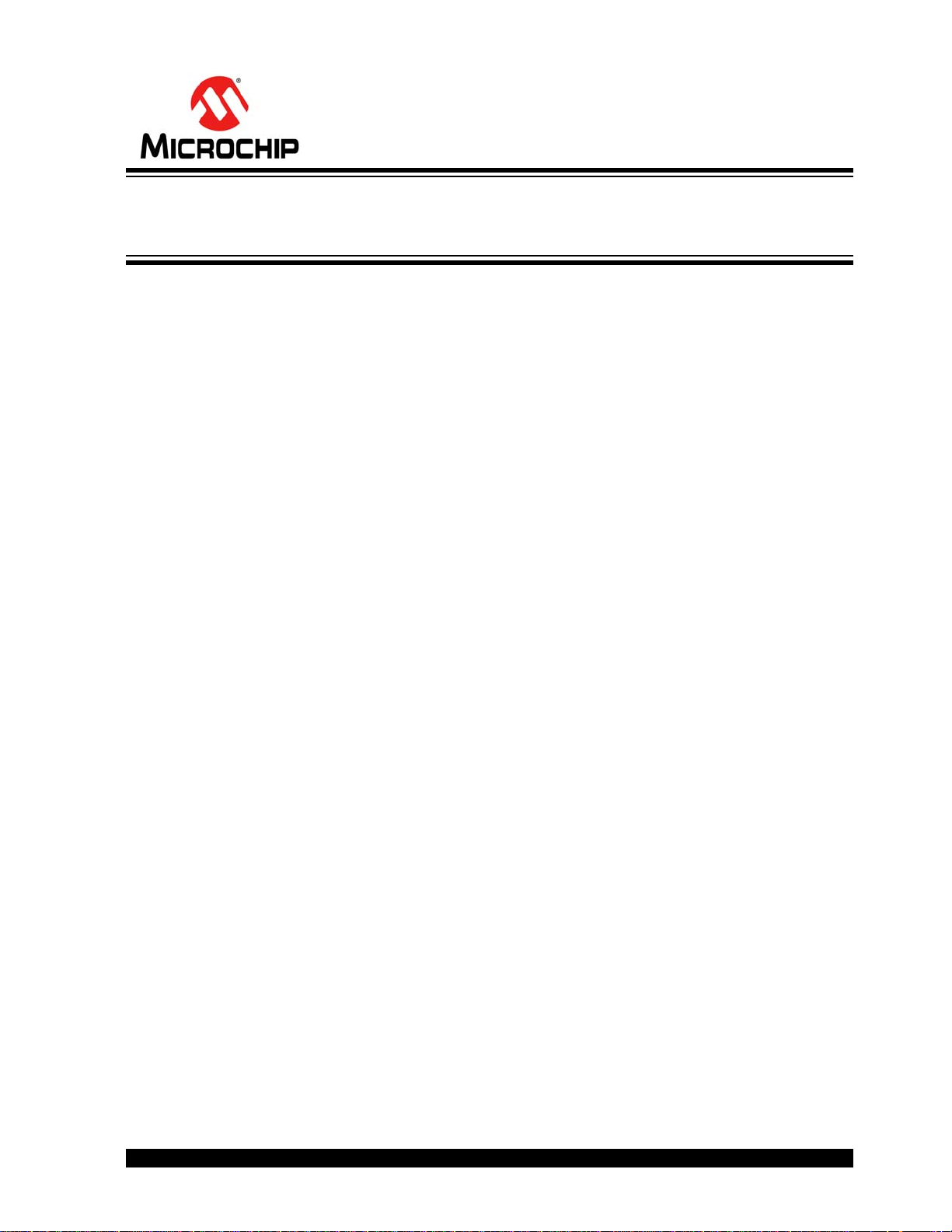

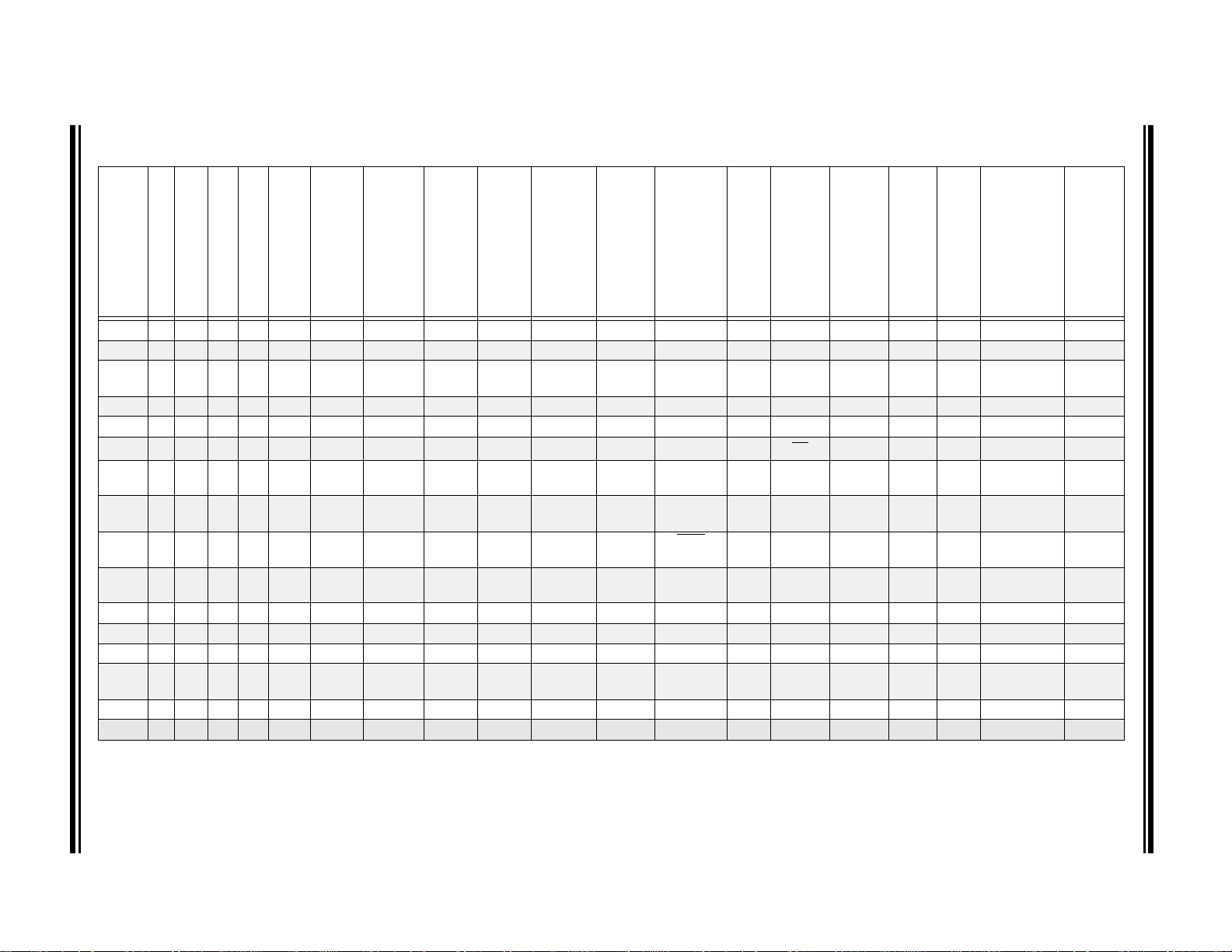

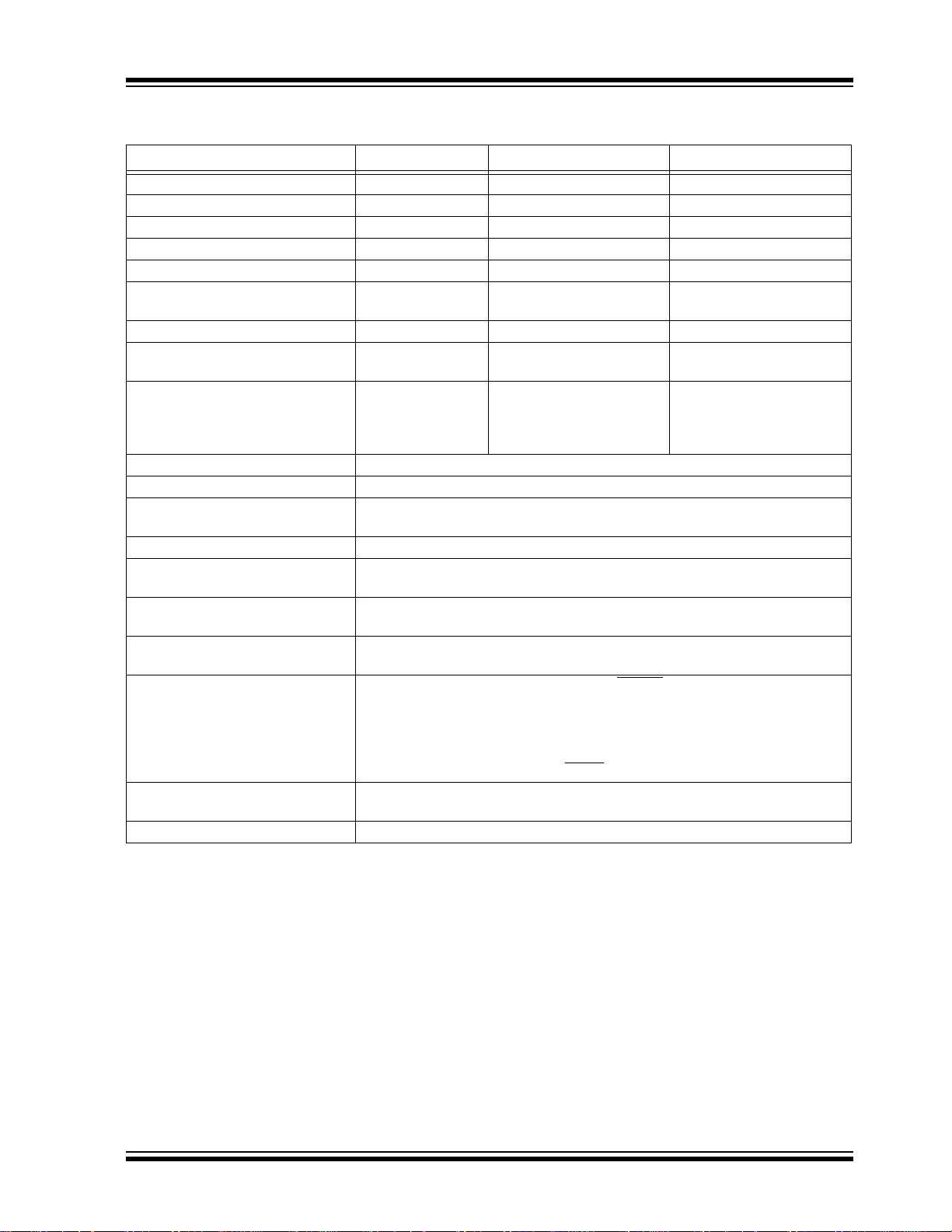

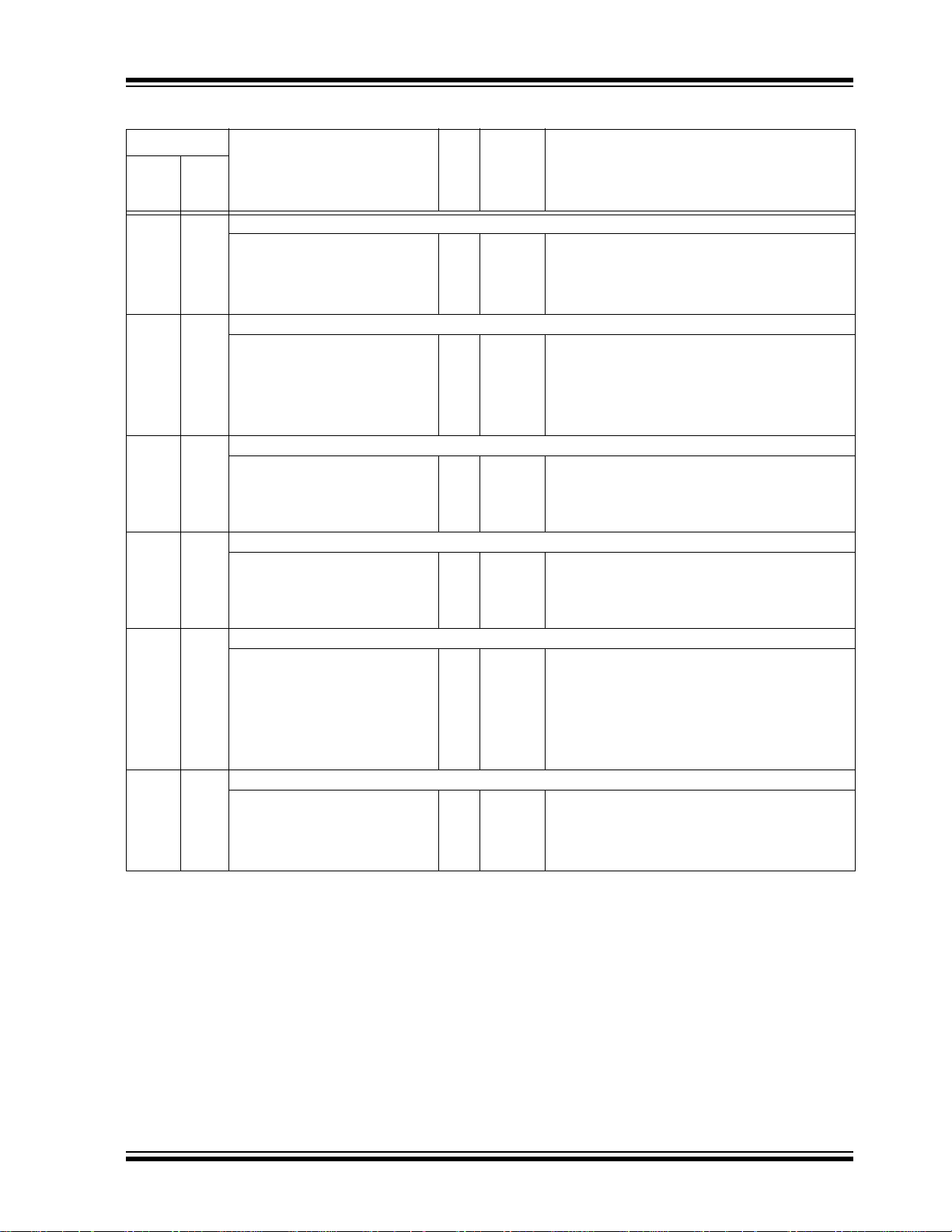

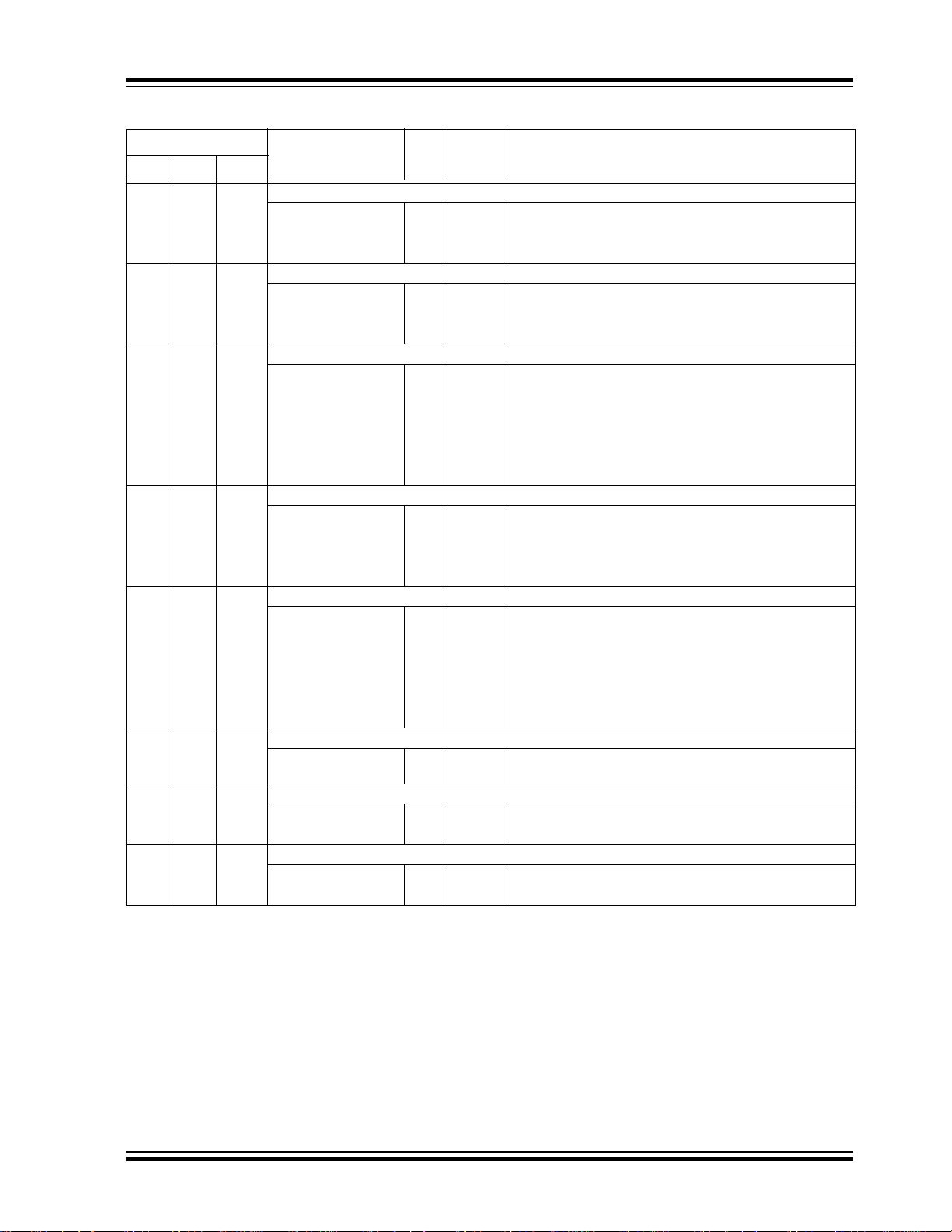

Program Memory Data Memory

Device

Flash

(bytes)

Single-Word

Instructions

SRAM

(bytes)

Data

EEPROM

(bytes)

Pins I/O

CCP/

ECCP

Channels

10-Bit A/D

Comparators

BOR/LVD

CTMU

MSSP

EUSART

Timers

8-bit/16-bit

PIC18(L)F45K50 32K 16384 2048 256 40/44 36 25-ch 2 1/1 Yes Yes 1 1 2/2 Yes

PIC18(L)F25K50 32K 16384 2048 256 28 25 14-ch 2 1/1 Yes Yes 1 1 2/2 Yes

PIC18(L)F24K50 16K 8192 2048 256 28 25 14-ch 2 1/1 Yes Yes 1 1 2/2 Yes

Pin Diagram

USB 2.0

Pin Diagram

DS30684A-page 2 2012 Microchip Technology Inc.

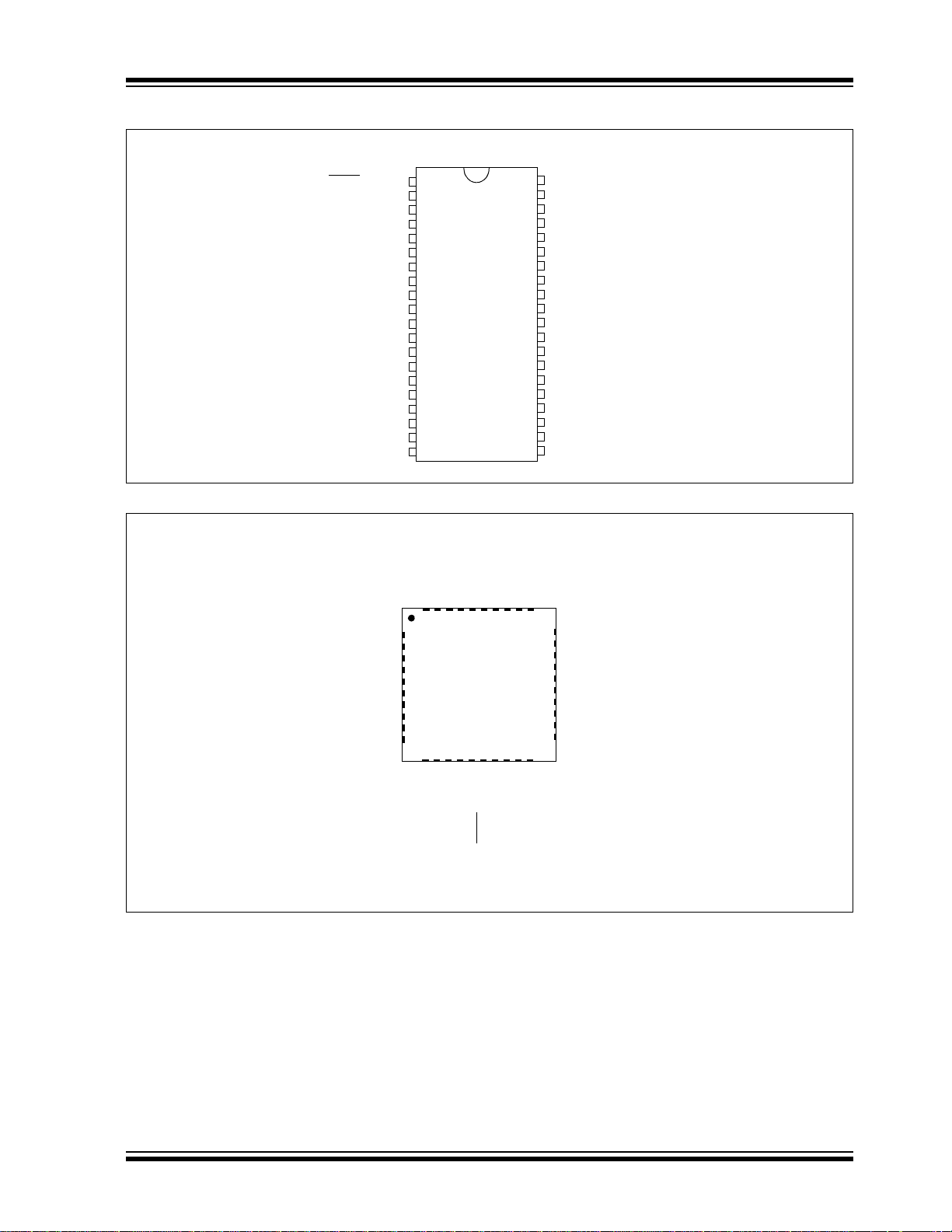

Pin Diagram

RB7

RB6

RB5

RB4

RB3

RB2

RB1

RB0

V

DD

VSS

RD7

RD6

RD5

RD4

RC7

RC6

D+

DRD3

RD2

MCLR/VPP/RE3

RA0

RA1

RA2

RA3

RA4

RA5

RE0

RE1

RE2

V

DD

VSS

RA7

RA6

RC0

RC1

RC2

V

USB3V3

RD0

RD1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

40-PIN PDIP (600 MIL)

PIC18(L)F45K50

10

2

3

4

5

6

1

171819

20

111213

14

34

8

7

4039383736

35

15

16

27

28

29

30

21

22

23

24

25

26

32

31

9

33

RA3

RA2

RA1

RA0

MCLR

/VPP/RE3

RB3

RB7

RB6

RB5

RB4

RC6D+D-

RD3

RD2

RD1

RD0

V

USB3V3

RC2

RC1

RA6

RA7

V

SS

VDD

RE2

RE1

RE0

RA5

RA4

RC7

RD4

RD5

RD6

RD7

V

SS

VDD

RB0

RB1

RB2

40-PIN UQFN

PIC18(L)F45K50

RC0

Pin Diagram

PIC18(L)F2X/45K50

2012 Microchip Technology Inc. DS30684A-page 3

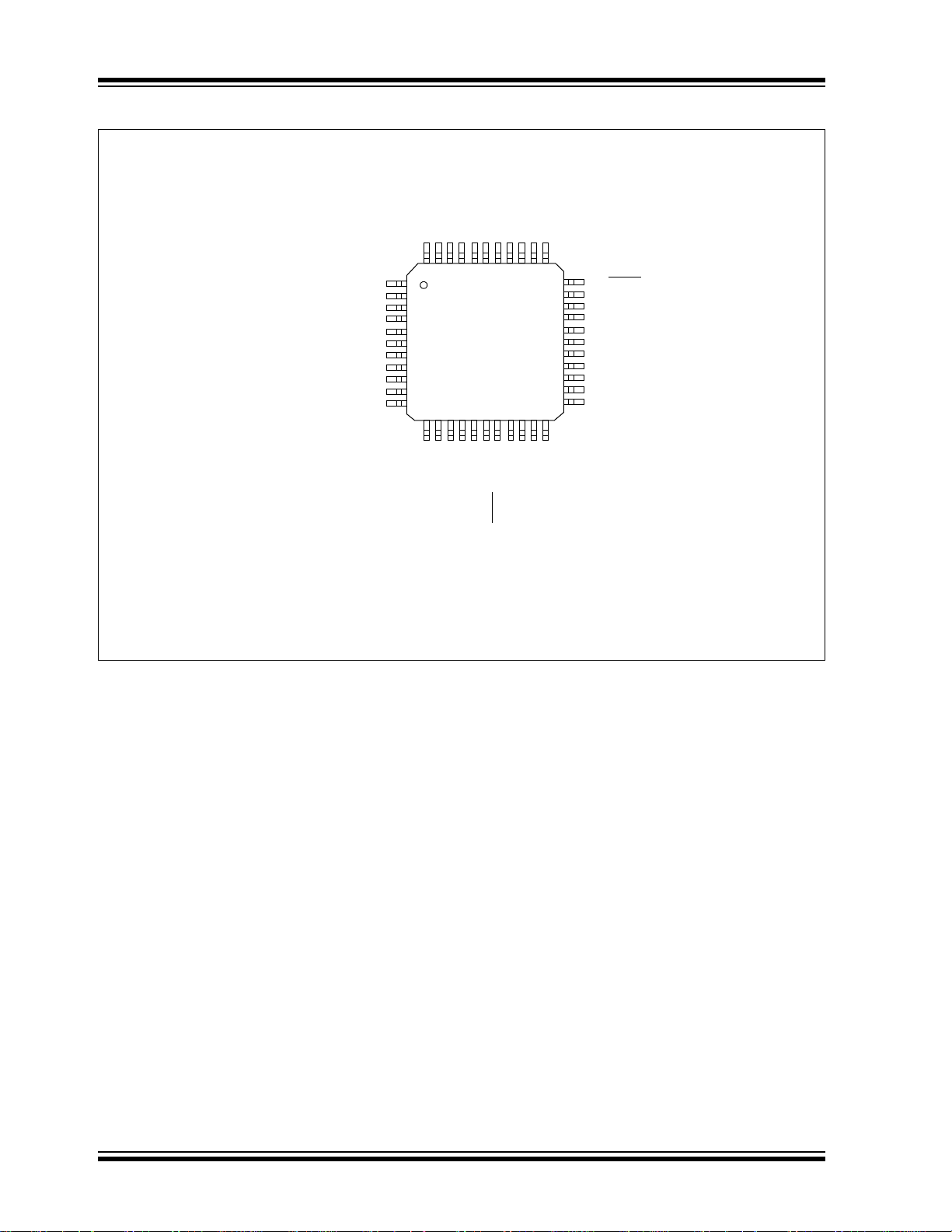

PIC18(L)F2X/45K50

10

11

2

3

6

1

1819202122

121314

15

38

8

7

44

43

42

414039

16

17

29

30

31

32

33

23

24

25

26

27

28

363435

9

37

RA3

RA2

RA1

RA0

MCLR

/VPP/RE3

NC/ICCK

(1)

/ICPGC

(1)

RB7

RB6

RB5

RB4

NC/ICDT

(1)

/ICPGD

(1)

RC6D+D-

RD3

RD2

RD1

RD0

V

USB3V3

RC2

NC

NC/ICRST

(1)

/ICVPP

(1)

RC0

RA6

RA7

V

SS

VDD

RE2

RE1

RE0

RA5

RA4

RC7

RD4

RD5

RD6

V

SS

VDD

RB0

RB1

RB2

RB3

44-PIN TQFP

RD7

5

4

RC1

PIC18(L)F45K50

Note 1: Special ICPORT programming/debug port features available when ICPRT = 1

Pin Diagram

DS30684A-page 4 2012 Microchip Technology Inc.

2012 Microchip Technology Inc. DS30684A-page 5

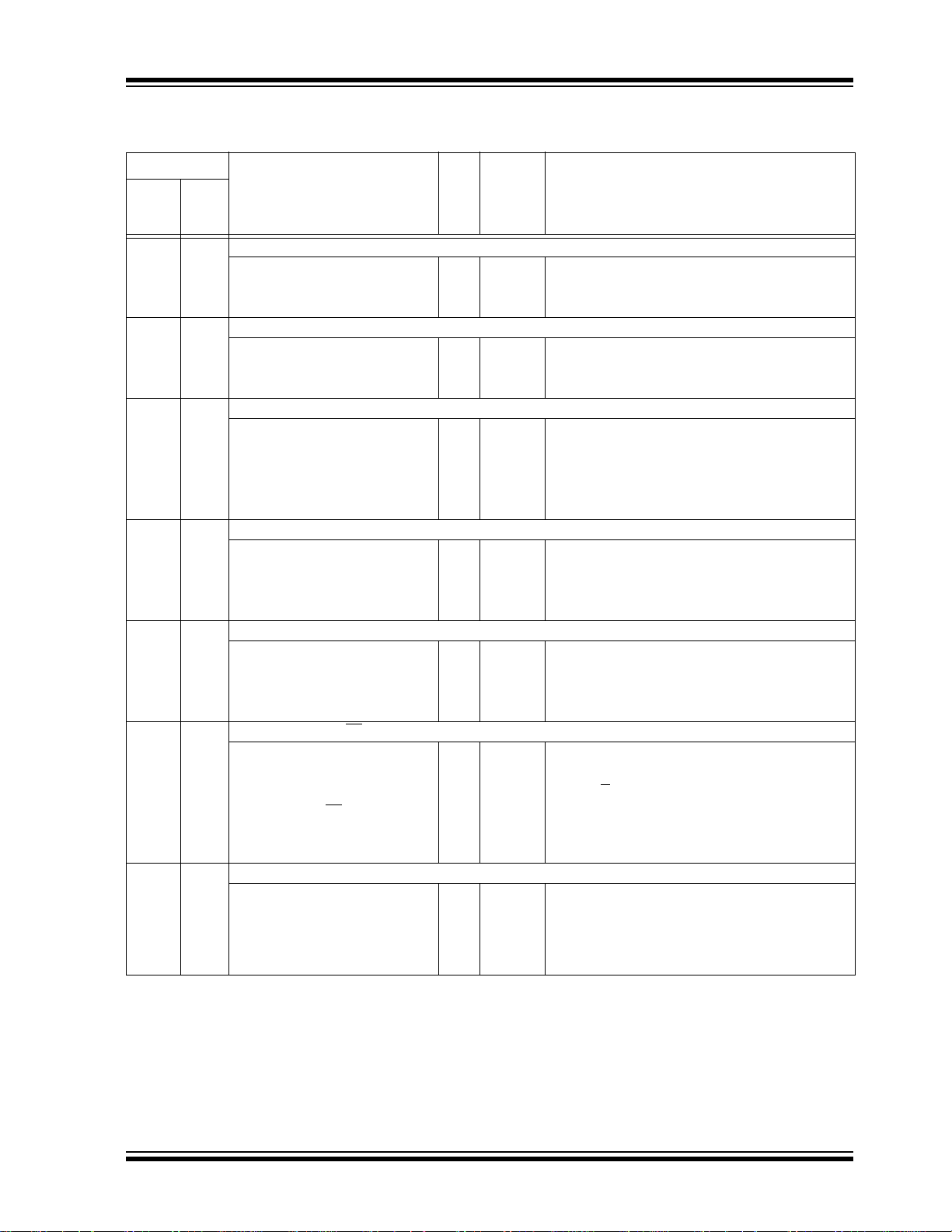

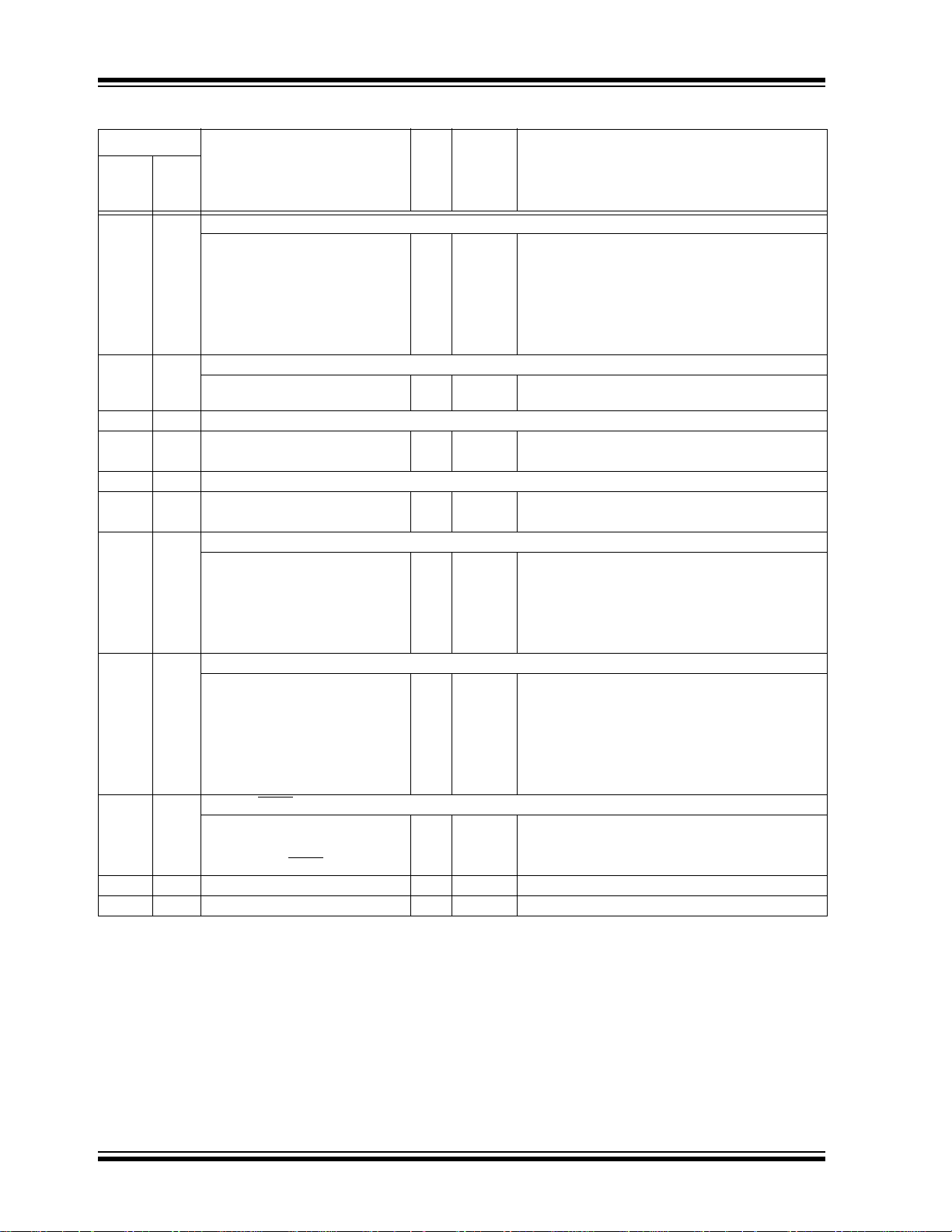

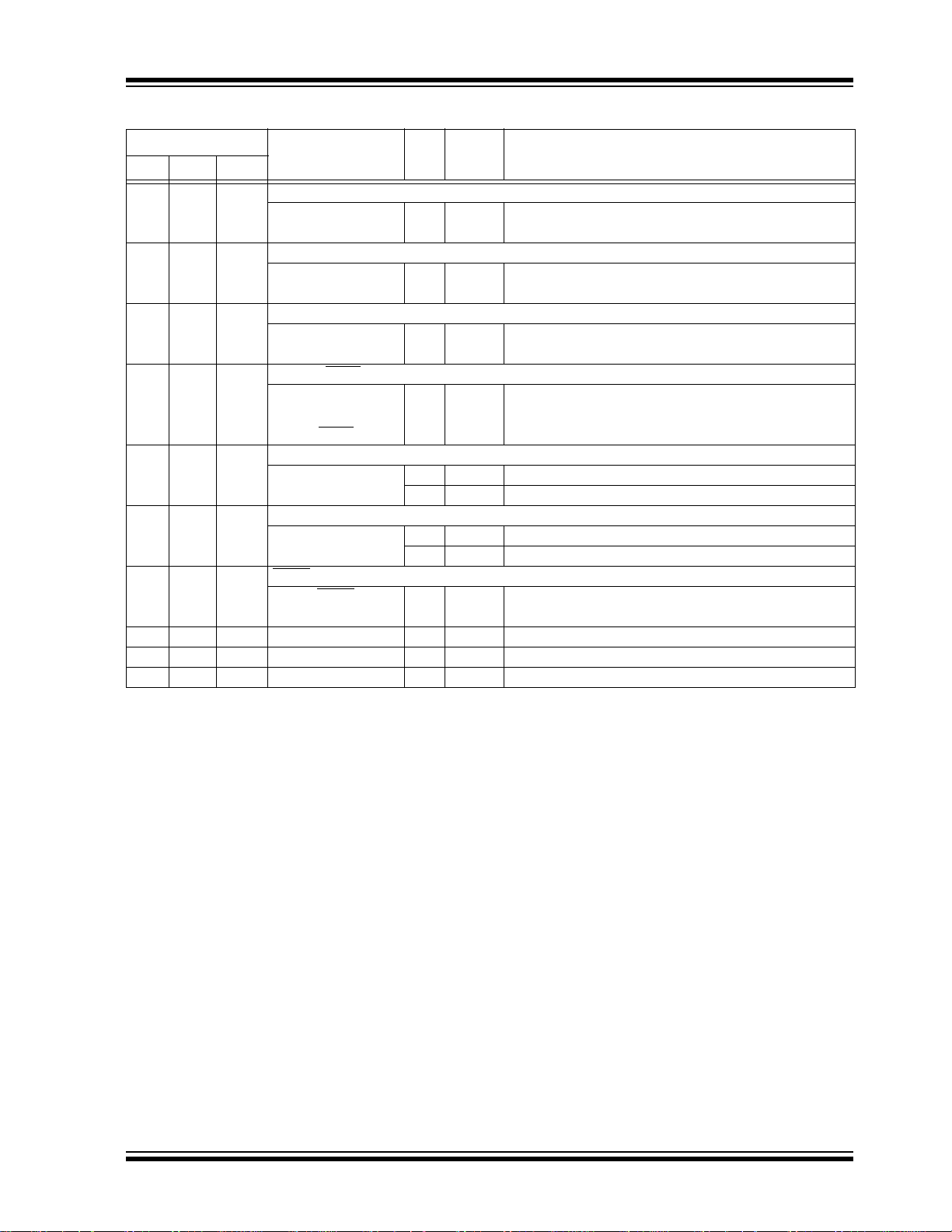

TABLE 1: PIC18(L)F2X/45K50 PIN SUMMARY

I/O

28-Pin QFN

40-Pin PDIP

28-PIn PDIP/SOIC/SSOP

RA0 2 27 2 17 19 AN0 C12IN0-

RA1 3 28 3 18 20 AN1 C12IN1- CTCMP

RA2 4 1 4 19 21 AN2 C2IN+ VREF-

RA3 5 2 5 20 22 AN3 C1IN+ VREF+

RA4 6 3 6 21 23 C1OUT SRQ T0CKI

RA5 7 4 7 22 24 AN4 C2OUT

RA6 10 7 14 29 31 OSC2

RA7 9 6 13 28 30 OSC1

RB0 21 18 33 8 8 AN12 SRI FLT0 SDI

RB1 22 19 34 9 9 AN10 C12IN3- P1C

RB2 23 20 35 10 10 AN8 CTED1 P1B

RB3 24 21 36 11 11 AN9 C12IN2- CTED2 CCP2

RB4 25 22 37 12 14 AN11 P1D

RB5 26 23 38 13 15 AN13 T1G

RB6 27 24 39 14 16 IOCB6 Y PGC

RB7 28 25 40 15 17 IOCB7 Y PGD

Note 1: Alternate CCP2 pin location based on Configuration bit.

2: Alternate T3CKI pin location based on Configuration bits.

3: Pins are enabled when ICPRT = 1, otherwise, they are disabled.

4: Location on 40/44-Pin parts (PIC18(L)F45K50). Function not on this pin on 28-Pin parts (PIC18(L)F2XK50).

5: Location on 28-Pin parts (PIC18(L)F2XK50). Function not on this pin on 40/44-Pin parts (PIC18(L)F45K50).

6: Alternate SDO pin location based on Configuration bits.

7: RE3 can be used for digital input only (no output functionality).

40-Pin UQFN

44-Pin TQFP

Analog

Comparator

CTMU

SR Latch

SRNQ

Reference

DACOUT

HLVDIN

USB

(E)CCP

(5)

(5)

(1)

(5)

EUSART

MSSP

SS

SDA

SCK

SCL

SDO Y

T3CKI

Timers

(2)

Interrupts

INT0 Y

INT1 Y

INT2 Y

IOCB4 Y

IOCB5 Y

Pull-up

CLKO

CLKI

Basic

ICD

PIC18(L)F2X/45K50

DS30684A-page 6 2012 Microchip Technology Inc.

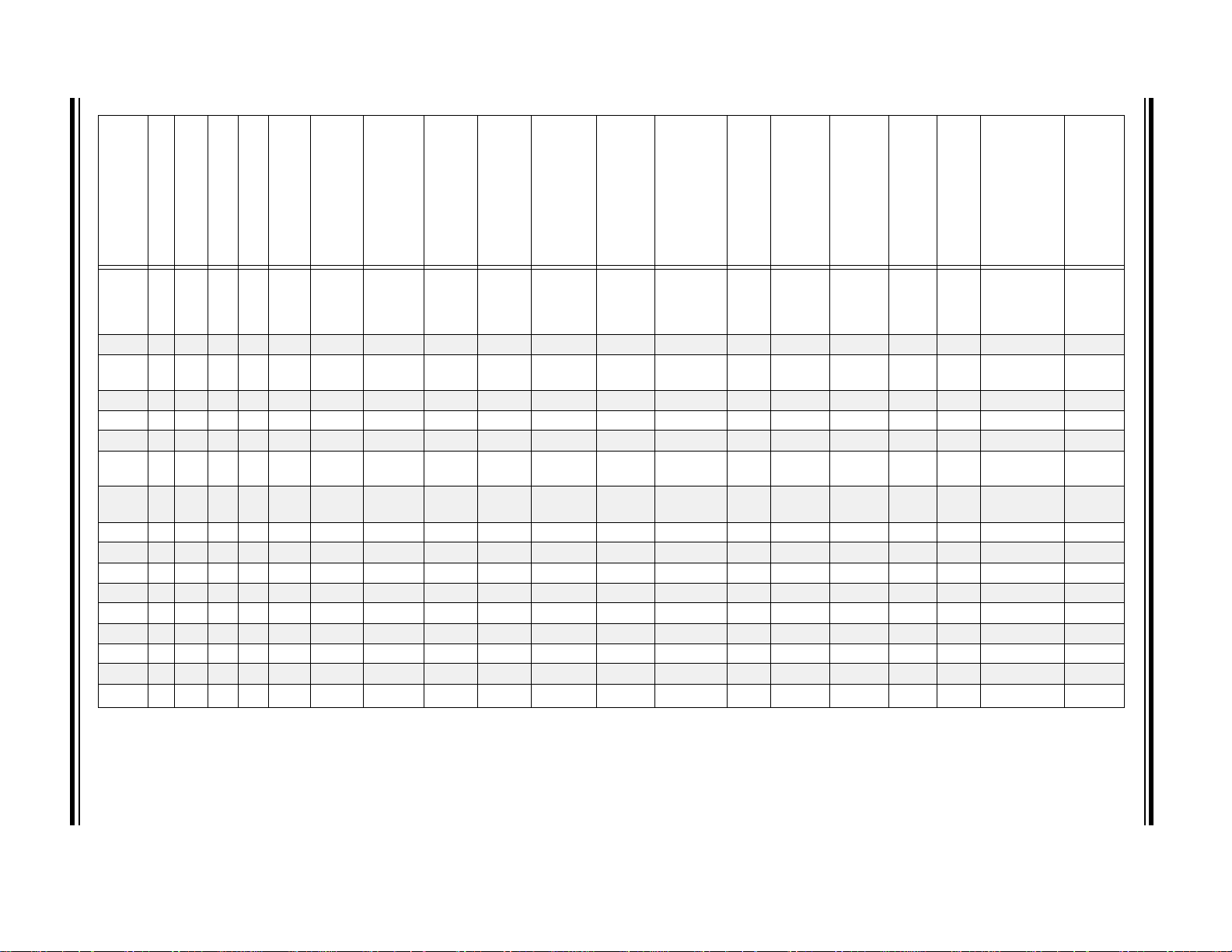

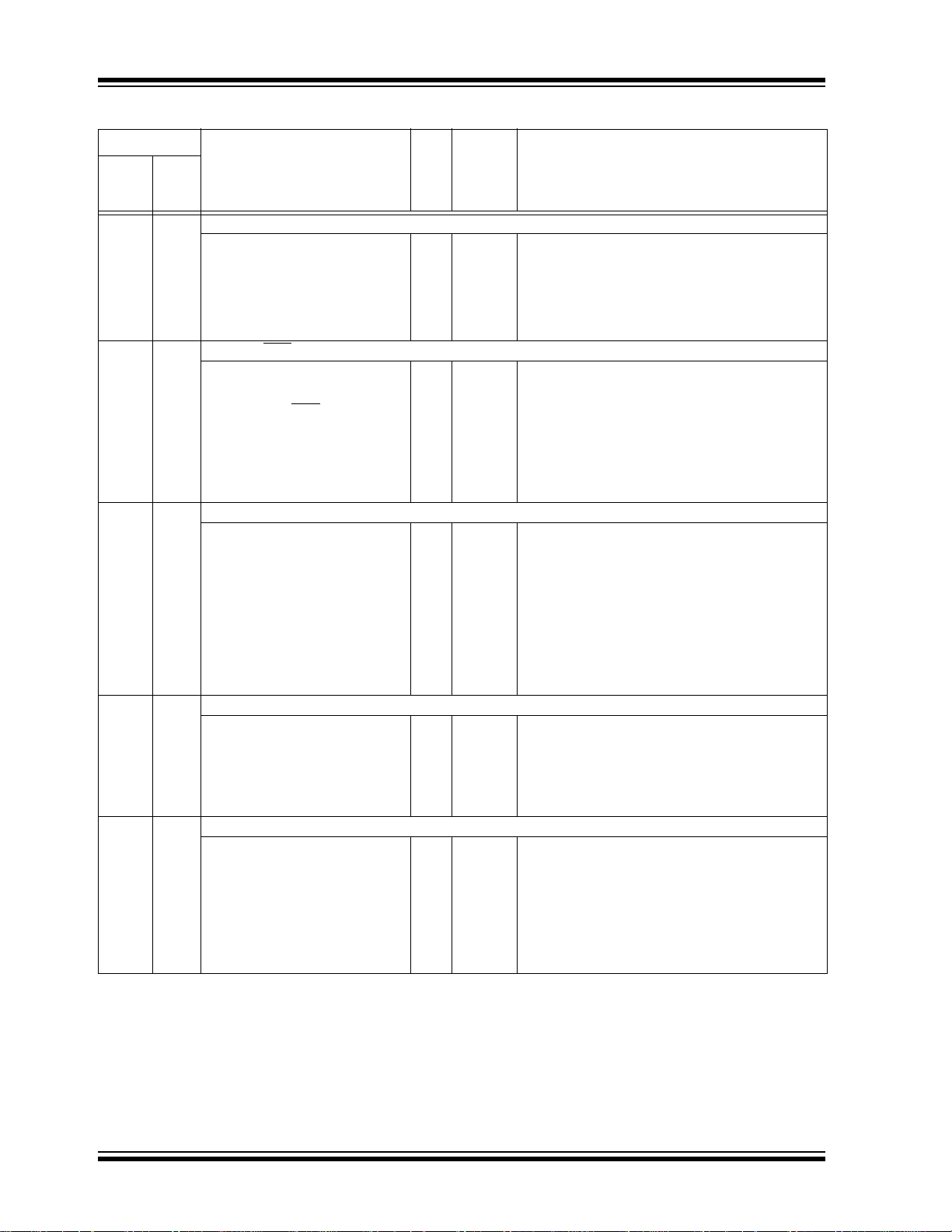

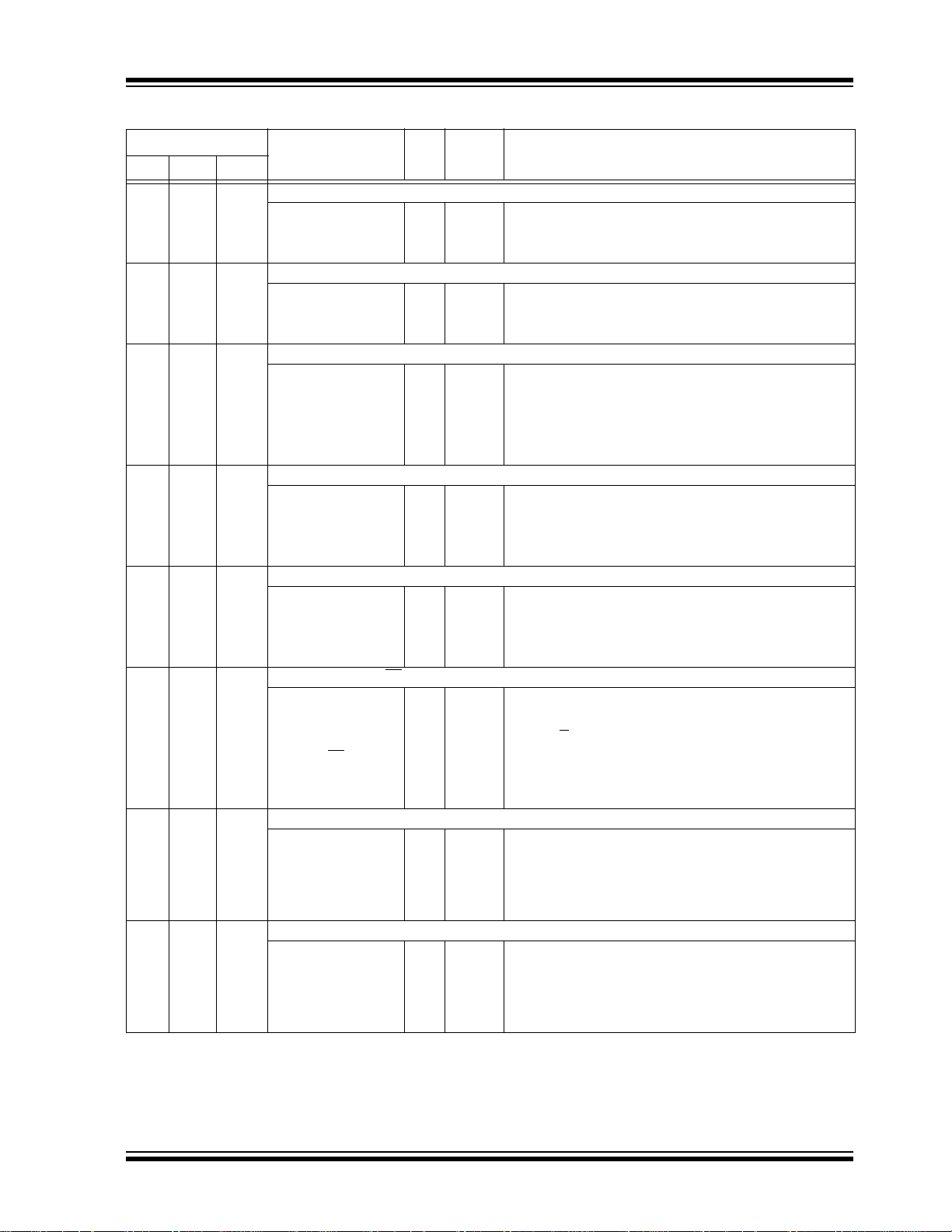

TABLE 1: PIC18(L)F2X/45K50 PIN SUMMARY

PIC18(L)F2X/45K50

I/O

28-Pin QFN

40-Pin PDIP

28-PIn PDIP/SOIC/SSOP

RC0 11 8 15 30 32 SOSCO

RC1 12 9 16 31 35 CCP2 SOSCI IOCC1

RC2 13 10 17 32 36 AN14 CTPLS CCP1

— 14 11 18 33 37 — VUSB3V3 VDDCORE

— 15 12 23 38 42 — D- IOCC4

— 16 13 24 39 43 — D+ IOCC5

RC6 17 14 25 40 44 AN18 TX

RC7 18 15 26 1 1 AN19 RXDTSDO

RD0 — — 19 34 38 AN20

RD1 — — 20 35 39 AN21

RD2 — — 21 36 40 AN22

RD3 — — 22 37 41 AN23

RD4 — — 27 2 2 AN24

RD5 — — 28 3 3 AN25 P1B

RD6 — — 29 4 4 AN26 P1C

RD7 — — 30 5 5 AN27 P1D

——

RE0

Note 1: Alternate CCP2 pin location based on Configuration bit.

2: Alternate T3CKI pin location based on Configuration bits.

3: Pins are enabled when ICPRT = 1, otherwise, they are disabled.

4: Location on 40/44-Pin parts (PIC18(L)F45K50). Function not on this pin on 28-Pin parts (PIC18(L)F2XK50).

5: Location on 28-Pin parts (PIC18(L)F2XK50). Function not on this pin on 40/44-Pin parts (PIC18(L)F45K50).

6: Alternate SDO pin location based on Configuration bits.

7: RE3 can be used for digital input only (no output functionality).

823 25 AN5

40-Pin UQFN

44-Pin TQFP

Analog

Comparator

CTMU

SR Latch

Reference

USB

P1A

(E)CCP

(4)

(4)

(4)

EUSART

CK

MSSP

(6)

Timers

T1CKI

T3CKI

T3G

Interrupts

IOCC0

IOCC2

IOCC6

IOCC7

Pull-up

Basic

ICD

2012 Microchip Technology Inc. DS30684A-page 7

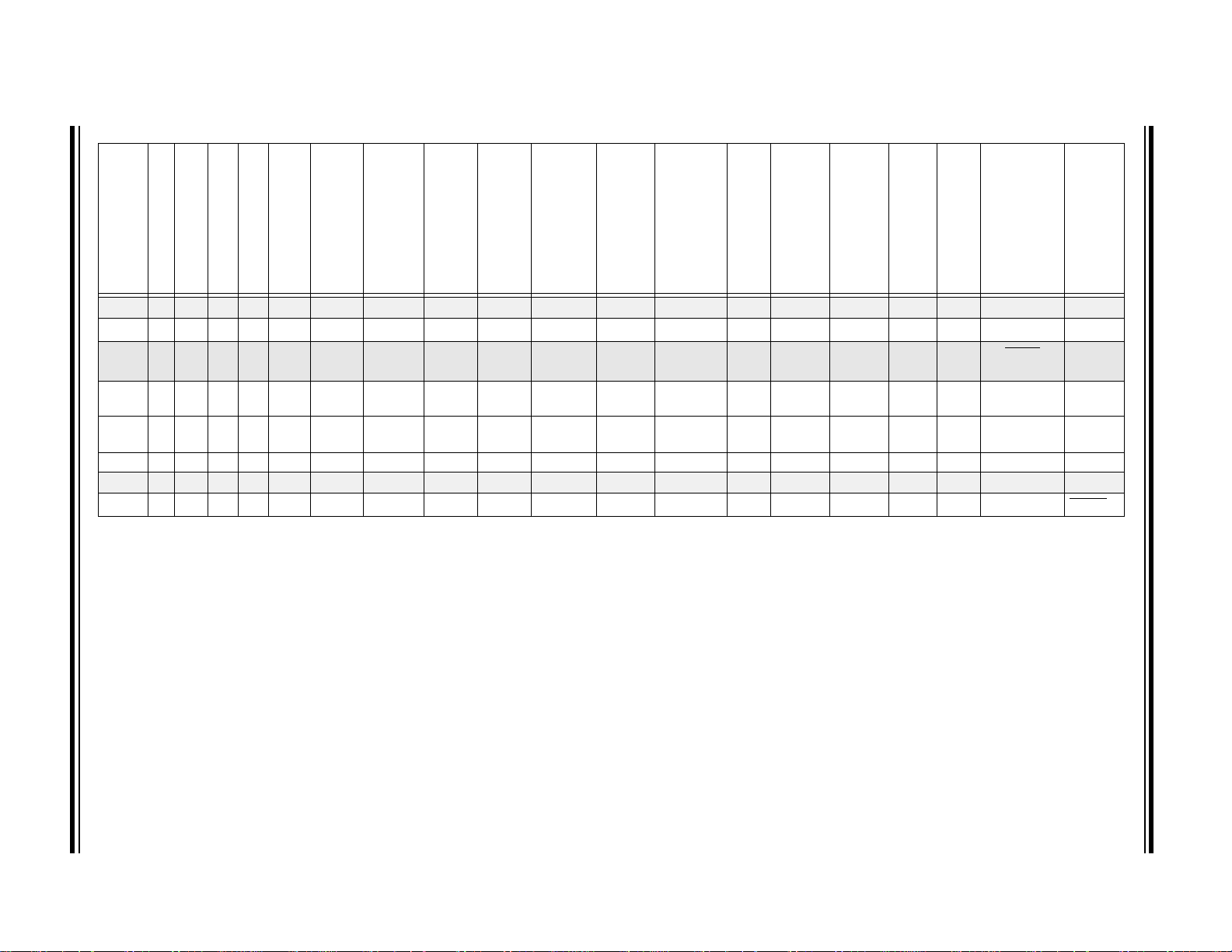

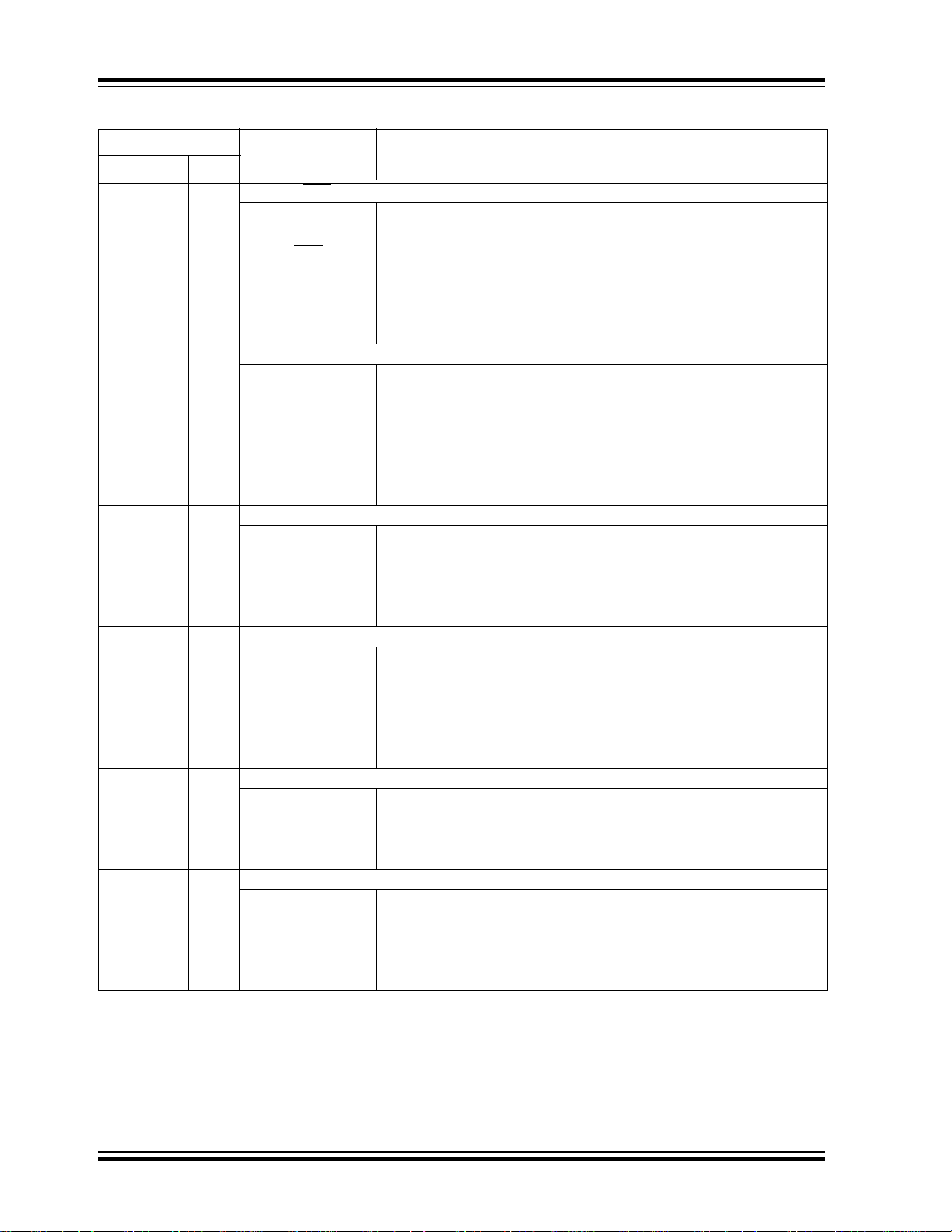

TABLE 1: PIC18(L)F2X/45K50 PIN SUMMARY

I/O

28-Pin QFN

40-Pin PDIP

28-PIn PDIP/SOIC/SSOP

— —

RE1

——

RE2

(7)

RE3

Note 1: Alternate CCP2 pin location based on Configuration bit.

1 26

20 17 11, 327, 267,

8,195,1612,316,276,

2: Alternate T3CKI pin location based on Configuration bits.

3: Pins are enabled when ICPRT = 1, otherwise, they are disabled.

4: Location on 40/44-Pin parts (PIC18(L)F45K50). Function not on this pin on 28-Pin parts (PIC18(L)F2XK50).

5: Location on 28-Pin parts (PIC18(L)F2XK50). Function not on this pin on 40/44-Pin parts (PIC18(L)F45K50).

6: Alternate SDO pin location based on Configuration bits.

7: RE3 can be used for digital input only (no output functionality).

9 24 26 AN6

10 25 27 AN7

1 16 18

––-12

– –- 13

–- –- 33

40-Pin UQFN

28

29

44-Pin TQFP

(3)

(3)

(3)

Analog

Comparator

—

CTMU

SR Latch

Reference

USB

(E)CCP

EUSART

MSSP

ICCK

ICDT

ICRST

ICD

(3)

(3)

(3)

MCLR

VPP

VDD

VSS

ICPGC

ICPGD

ICVPP

Basic

(3)

(3)

(3)

Timers

Pull-up

Interrupts

Y

PIC18(L)F2X/45K50

PIC18(L)F2X/45K50

Table of Contents

1.0 Device Overview ....................................................................................................................................................................... 13

2.0 Guidelines for Getting Started with PIC18(L)F2X/45K50 Microcontrollers ................................................................................ 27

3.0 Oscillator Module (With Fail-Safe Clock Monitor)...................................................................................................................... 33

4.0 Power-Managed Modes ............................................................................................................................................................ 57

5.0 Reset ......................................................................................................................................................................................... 69

6.0 Memory Organization ................................................................................................................................................................ 79

7.0 Flash Program Memory........................................................................................................................................................... 101

8.0 Data EEPROM Memory ........................................................................................................................................................... 111

9.0 8 x 8 Hardware Multiplier.......................................................................................................................................................... 117

10.0 Interrupts .................................................................................................................................................................................. 119

11.0 I/O Ports .................................................................................................................................................................................. 137

12.0 Timer0 Module......................................................................................................................................................................... 163

13.0 Timer1/3 Module with Gate Control......................................................................................................................................... 167

14.0 Timer2 Module......................................................................................................................................................................... 179

15.0 Capture/Compare/PWM Modules............................................................................................................................................ 183

16.0 Master Synchronous Serial Port (MSSP) Module ................................................................................................................... 215

17.0 Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) .............................................................. 271

18.0 Analog-to-Digital Converter (ADC) Module ............................................................................................................................. 301

19.0 Comparator Module................................................................................................................................................................. 315

20.0 Charge Time Measurement Unit (CTMU)................................................................................................................................ 325

21.0 SR L

22.0 Fixed Voltage Reference (FVR)............................................................................................................................................... 347

23.0 Digital-to-Analog Converter (DAC) Module ............................................................................................................................. 349

24.0 Universal Serial Bus (USB) ..................................................................................................................................................... 353

25.0 High/Low-Voltage Detect (HLVD) ............................................................................................................................................ 381

26.0 Special Features of the CPU ................................................................................................................................................... 387

27.0 Instruction Set Summary ......................................................................................................................................................... 407

28.0 Development Support.............................................................................................................................................................. 457

29.0 Electrical Characteristics ......................................................................................................................................................... 461

30.0 DC and AC Characteristics Graphs and Charts ...................................................................................................................... 501

31.0 Packaging Information............................................................................................................................................................. 503

Appendix A: Revision History............................................................................................................................................................ 521

Appendix B: Device Differences........................................................................................................................................................ 522

Index ................................................................................................................................................................................................. 523

The Microchip Web Site.................................................................................................................................................................... 533

Customer Change Notification Service ............................................................................................................................................. 533

Customer Support ............................................................................................................................................................................. 533

Reader Response ............................................................................................................................................................................. 534

Product Identification System............................................................................................................................................................ 535

ATCH................................................................................................................................................................................. 341

DS30684A-page 8 2012 Microchip Technology Inc.

PIC18(L)F2X/45K50

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at docerrors@microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150. We

welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

2012 Microchip Technology Inc. DS30684A-page 9

PIC18(L)F2X/45K50

NOTES:

DS30684A-page 10 2012 Microchip Technology Inc.

PIC18(L)F2X/45K50

1.0 DEVICE OVERVIEW

This document contains device-specific information for

the following devices:

•PIC18(L)F45K50

•PIC18(L)F25K50

•PIC18(L)F24K50

This family offers the advantages of all PIC18

microcontrollers – namely, high computational

performance at an economical price – with the addition

of high-endurance, Flash program memory. On top of

these features, the PIC18(L)F2X/45K50 family

introduces design enhancements that make these

microcontrollers a logical choice for many highperformance, power sensitive applications.

1.1 New Core Features

1.1.1 XLP TECHNOLOGY

All of the devices in the PIC18(L)F2X/45K50 family

incorporate a range of features that can significantly

reduce power consumption during operation. Key

items include:

• Alternate Run Modes: By clocking the controller

from the Timer1 source or the internal oscillator

block, power consumption during code execution

can be reduced by as much as 90%.

• Multiple Idle Modes: The controller can also run

with its CPU core disabled but the peripherals still

active. In these states, power consumption can be

reduced even further, to as little as 4% of normal

operation requirements.

• Peripheral Module Disable bits: User code can

power down individual peripheral modules during

Run and Idle modes for further lowering dynamic

power reduction.

• On-the-fly Mode Switching: The power-

managed modes are invoked by user code during

operation, allowing the user to incorporate powersaving ideas into their application’s software

design.

• Low Consumption in Key Modules: The

power requirements for both Timer1 and the

Watchdog Timer are minimized. See

Section 29.0 “Electrical Characteristics”

for values.

1.1.2 UNIVERSAL SERIAL BUS (USB)

Devices in the PIC18(L)F2X/45K50 family incorporate

a fully-featured USB communications module with a

built-in transceiver that is compliant with the USB

Specification Revision 2.0. The module supports both

low-speed and full-speed communication for all

supported data transfer types. The device

incorporates its own on-chip transceiver and 3.3V

regulator for USB.

1.1.3 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18(L)F2X/45K50 family

offer ten different oscillator options, allowing users a

wide range of choices in developing application

hardware. These include:

• Four Crystal modes, using crystals or ceramic

resonators

• Six External Clock modes, offering the option of

using two pins (oscillator input and a divide-by-4

clock output) or one pin (oscillator input, with the

second pin reassigned as general I/O)

• Two External RC Oscillator modes with the same

pin options as the External Clock modes

• An internal oscillator block which contains a

16 MHz HFINTOSC oscillator and a 31 kHz

INTRC oscillator, which together provide eight

user selectable clock frequencies, from 31 kHz to

16 MHz. This option frees the two oscillator pins

for use as additional general purpose I/O.

• 3x and 4x Phase Lock Loop (PLL) frequency

multipliers, available to both external and internal

oscillator modes, which allows clock speeds of up

to 48 MHz. Used with the internal oscillator, the

PLL gives users a complete selection of clock

speeds, from 31 kHz to 48 MHz – all without using

an external crystal or clock circuit.

Besides its availability as a clock source, the internal

oscillator block provides a stable reference source that

gives the family additional features for robust

operation:

• Active Clock Tuning: This option allows the

internal oscillator to automatically tune itself to

match USB host or external 32.768 kHz

secondary oscillator clock sources. Full-speed

USB operation can now meet specification

requirements without an external crystal, enabling

lower-cost designs.

• Fail-Safe Clock Monitor: This option constantly

monitors the main clock source against a

reference signal provided by the INTRC. If a clock

failure occurs, the controller is switched to the

internal oscillator block, allowing for continued

operation or a safe application shutdown.

• T wo-Speed Start-up: This option allows the

internal oscillator to serve as the clock source

from Power-on Reset, or wake-up from Sleep

mode, until the primary clock source is available.

2012 Microchip Technology Inc. DS30684A-page 11

PIC18(L)F2X/45K50

1.2 Other Special Features

• Memory Endurance: The Flash cells for both

program memory and data EEPROM are rated to

last for many thousands of erase/write cycles – up to

10K for program memory and 100K for EEPROM.

Data retention without refresh is conservatively

estimated to be greater than 40 years.

• Self-programmability: These devices can write

to their own program memory spaces under internal software control. By using a bootloader routine

located in the protected Boot Block at the top of

program memory, it becomes possible to create

an application that can update itself in the field.

• Extended Instruction Set: The PIC18(L)F2X/

45K50 family introduces an optional extension to

the PIC18 instruction set, which adds eight new

instructions and an Indexed Addressing mode.

This extension, enabled as a device configuration

option, has been specifically designed to optimize

re-entrant application code originally developed in

high-level languages, such as C.

• Enhanced CCP module: In PWM mode, this

module provides 1, 2 or 4 modulated outputs for

controlling half-bridge and full-bridge drivers.

Other features include:

- Auto-shutdown, for disabling PWM outputs

on interrupt or other select conditions

- Auto-restart, to reactivate outputs once the

condition has cleared

- Output steering to selectively enable one or

more of four outputs to provide the PWM

signal.

• Enhanced Addressable EUSART: This serial

communication module is capable of standard

RS-232 operation and provides support for the LIN

bus protocol. Other enhancements include

automatic baud rate detection and a 16-bit Baud

Rate Generator for improved resolution. When the

microcontroller is using the internal oscillator

block, the EUSART provides stable operation for

applications that talk to the outside world without

using an external crystal (or its accompanying

power requirement).

• 10-bit A/D Converter: This module incorporates

programmable acquisition time, allowing for a

channel to be selected and a conversion to be

initiated without waiting for a sampling period and

thus, reduce code overhead.

• Dedicated ICD/ICSP™ Port: These devices

introduce the use of debugger and programming

pins that are not multiplexed with other

microcontroller features. Offered as an option in

the TQFP packaged devices, this feature allows

users to develop I/O intensive applications while

retaining the ability to program and debug in the

circuit.

• Charge Time Measurement Unit (CTMU):

• SR Latch Output:

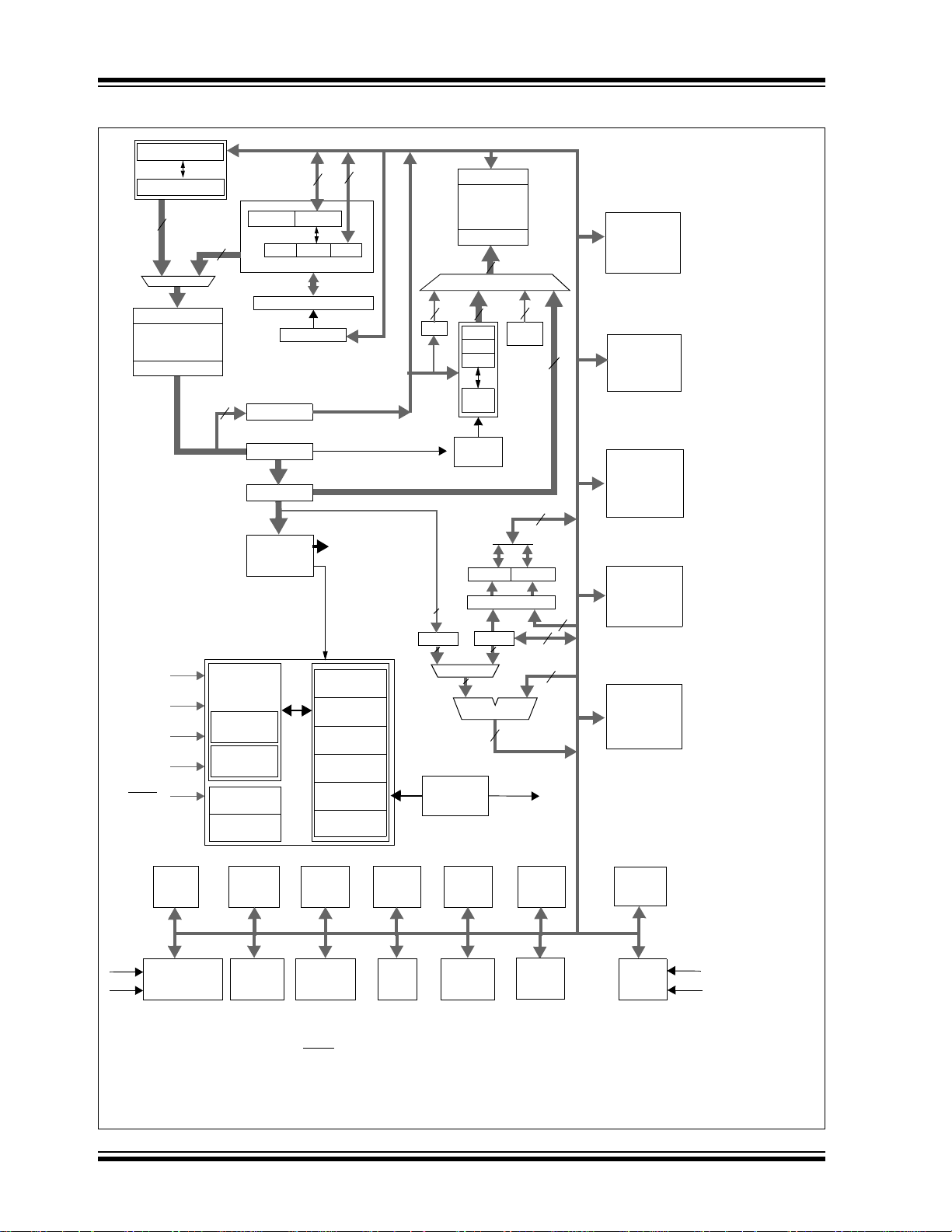

1.3 Details on Individual Family Members

Devices in the PIC18(L)F2X/45K50 family are available

in 28-pin and 40/44-pin packages. The block diagram

for the device family is shown in Figure 1-1.

The devices have the following differences:

1. Flash program memory

2. A/D channels

3. I/O ports

4. Input Voltage Range/Power Consumption

All other features for devices in this family are identical.

These are summarized in Ta bl e 1 -1 .

The pinouts for all devices are listed in the pin summary

table: Ta bl e 1 , and I/O description tables: Tab l e 1 -2 and

Table 1-3.

DS30684A-page 12 2012 Microchip Technology Inc.

PIC18(L)F2X/45K50

TABLE 1-1: DEVICE FEATURES

Features PIC18(L)F24K50 PIC18(L)F25K50 PIC18(L)F45K50

Program Memory (Bytes) 16384 32768 32768

Program Memory (Instructions) 8192 16384 16384

Data Memory (Bytes) 2048 2048 2048

Data EEPROM Memory (Bytes) 256 256 256

I/O Ports A, B, C, E

Capture/Compare/PWM Modules

(CCP)

Enhanced CCP Modules (ECCP) 1 1 1

10-bit Analog-to-Digital Module

(ADC)

Packages 28-pin PDIP

Interrupt Sources 25

Timers (16-bit) 2

Serial Communications MSSP,

SR Latch Yes

Charge Time Measurement Unit

Module (CTMU)

Programmable

High/Low-Voltage Detect (HLVD)

Programmable Brown-out Reset

(BOR)

Resets (and Delays) POR, BOR, LPBOR

Instruction Set 75 Instructions;

Operating Frequency DC – 48 MHz

Note 1: PORTE contains the single RE3 read-only bit.

3 internal

14 input

28-pin SOIC

28-pin SSOP

28-pin QFN

(1)

11 1

83 with Extended Instruction Set enabled

A, B, C, E

3 internal

28-pin PDIP

28-pin SOIC

28-pin SSOP

28-pin QFN

RESET Instruction,

(1)

14 input

EUSART

Yes

Yes

Yes

Stack Overflow,

Stack Underflow

(PWRT, OST),

, WDT

MCLR

A, B, C, D, E

3 internal

25 input

40-pin PDIP

40-pin UQFN

44-pin TQFP

2012 Microchip Technology Inc. DS30684A-page 13

PIC18(L)F2X/45K50

Instruction

Decode and

Control

Data Latch

Data Memory

Address Latch

Data Address<12>

12

Access

BSR

FSR0

FSR1

FSR2

inc/dec

logic

Address

4

12

4

PCH PCL

PCLATH

8

31-Level Stack

Program Counter

PRODLPRODH

8 x 8 Multiply

8

BITOP

8

8

ALU<8>

20

8

8

Table Pointer<21>

inc/dec logic

21

8

Data Bus<8>

Table Latch

8

IR

12

3

ROM Latch

PCLATU

PCU

Note 1: RE3 is only available when MCLR functionality is disabled.

2: OSC1/CLKIN and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O.

Refer to Section 6.0 “Memory Organization” for additional information.

EUSART

Comparators

MSSP

10-bit

ADC

Timer2

Timer1

CTMUTimer0

USB

HLVD

ECCP1

BOR

Data

EEPROM

W

Instruction Bus <16>

STKPTR

Bank

8

State machine

control signals

Decode

8

8

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

OSC1

(2)

OSC2

(2)

Brown-out

Reset

Internal

Oscillator

Fail-Safe

Clock Monitor

Precision

Reference

Band Gap

MCLR

(1)

Block

INTRC

Oscillator

16 MHz

Oscillator

Single-Supply

Programming

In-Circuit

Debugger

SOSCO

SOSCI

FVR

FVR

FVR

DAC

Address Latch

Program Memory

(16/32 Kbytes)

Data Latch

PORTA

RA0:RA7

PORTB

RB0:RB7

PORTC

RC0:RC3

PORTD

RD0:RD7

Timer3

SR Latch

C1/C2

CCP2

PORTE

RE0:RE2

RE3

(1)

DAC

RC6:RC7

DAC

FIGURE 1-1: PIC18(L)F2X/45K50 FAMILY BLOCK DIAGRAM

DS30684A-page 14 2012 Microchip Technology Inc.

PIC18(L)F2X/45K50

TABLE 1-2: PIC18(L)F2XK50 PINOUT I/O DESCRIPTIONS

Pin Number

Pin

PDIP,

SOIC,

SSOP

Legend: TTL = TTL compatible input; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;

Note 1: Default pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are set.

QFN

227

328

41

52

63

74

10 7

2: Alternate pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are clear.

RA0/C12IN0-/AN0

RA1/C12IN1-/AN1

RA2/C2IN+/AN2/DACOUT/VREF-

RA3/C1IN+/AN3/VREF+

RA4/C1OUT/SRQ/T0CKI

RA5/C2OUT/SRNQ/SS/HLVDIN/AN4

RA6/CLKO/OSC2

I = Input; O = Output; P = Power.

Pin Name

RA0 I/O TTL/DIG Digital I/O.

C12IN0- I Analog Comparators C1 and C2 inverting input.

AN0 I Analog Analog input 0.

RA1 I/O TTL/DIG Digital I/O.

C12IN1- I Analog Comparators C1 and C2 inverting input.

AN1 I Analog Analog input 1.

RA2 I/O TTL/DIG Digital I/O.

C2IN+ I Analog Comparator C2 non-inverting input.

AN2 I Analog Analog input 2.

DACOUT O Analog DAC Reference output.

REF- I Analog A/D reference voltage (low) input.

V

RA3 I/O TTL/DIG Digital I/O.

C1IN+ I Analog Comparator C1 non-inverting input.

AN3 I Analog Analog input 3.

REF+ I Analog A/D reference voltage (high) input.

V

RA4 I/O ST/DIG Digital I/O.

C1OUT O DIG Comparator C1 output.

SRQ O DIG SR latch Q output.

T0CKI I ST Timer0 external clock input.

RA5 I/O TTL/DIG Digital I/O.

C2OUT O DIG Comparator C2 output.

SRNQ O DIG SR latch Q

S

S I TTL SPI slave select input (MSSP).

HLVDIN I Analog High/Low-Voltage Detect input.

AN4 I Analog Analog input 4.

RA6 I/O TTL/DIG Digital I/O.

CLKO O DIG Outputs 1/4 the frequency of OSC1 and denotes the

OSC2 O — Oscillator crystal output. Connects to crystal or

Type

Buffer

Type

Description

output.

instruction cycle rate.

resonator in Crystal Oscillator modes.

2012 Microchip Technology Inc. DS30684A-page 15

PIC18(L)F2X/45K50

TABLE 1-2: PIC18(L)F2XK50 PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

Pin

PDIP,

SOIC,

SSOP

Legend: TTL = TTL compatible input; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;

Note 1: Default pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are set.

QFN

9 6 RA7/CLKI/OSC1

21 18

22 19

23 20

24 21

2: Alternate pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are clear.

RB0/INT0/FLT0 /SRI/SDI/SDA/AN12

RB1/INT1/P1C/SCK/SCL/C12IN3-/AN10

RB2/INT2/CTED1/P1B/AN8

RB3/CTED2/CCP2/SDO/C12IN2-/AN9

I = Input; O = Output; P = Power.

Pin Name

RA7 I/O TTL/DIG Digital I/O.

CLKI I CMOS External clock source input. Always associated with

OSC1 I ST Oscillator crystal input or external clock source input

RB0 I/O TTL/DIG Digital Output or Input with internal pull-up option.

INT0 I ST External interrupt 0.

FLT0

SRI I ST SR latch input.

SDI I ST SPI data in (MSSP).

SDA I/O I

AN12 I Analog Analog input 12.

RB1 I/O TTL/DIG Digital Output or Input with internal pull-up option.

INT1 I ST External interrupt 1.

P1C O DIG Enhanced CCP1 PWM output.

SCK I/O ST/DIG Synchronous serial clock input/output for SPI mode

SCL I/O I

C12IN3- I Analog Comparators C1 and C2 inverting input.

AN10 I Analog Analog input 10.

RB2 I/O TTL/DIG Digital Output or Input with internal pull-up option.

INT2 I ST External interrupt 2.

CTED1 I ST CTMU Edge 1 input.

P1B O DIG Enhanced CCP1 PWM output.

AN8 I Analog Analog input 8.

RB3 I/O TTL/DIG Digital Output or Input with internal pull-up option.

CTED2 I ST CTMU Edge 2 input.

(2)

CCP2

(1)

SDO

C12IN2- I Analog Comparators C1 and C2 inverting input.

AN9 I Analog Analog input 9.

Type

Buffer

Type

pin function OSC1.

ST buffer when configured in RC mode; CMOS

otherwise.

I ST PWM Fault input for ECCP auto-shutdown.

2

C™ I2C™ data I/O (MSSP).

2

I/O ST/DIG Alternate Capture 2 input/Compare 2 output/PWM 2

O DIG SPI data out (MSSP).

(MSSP).

C™ Synchronous serial clock input/output for I2C™ mode

(MSSP).

output.

Description

DS30684A-page 16 2012 Microchip Technology Inc.

PIC18(L)F2X/45K50

TABLE 1-2: PIC18(L)F2XK50 PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

Pin

PDIP,

SOIC,

SSOP

Legend: TTL = TTL compatible input; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;

Note 1: Default pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are set.

QFN

25 22 RB4/IOCB4/P1D/AN11

26 23

27 24

28 25

11 8

12 9

2: Alternate pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are clear.

RB5/IOCB5/T3CKI/T1G/AN13

RB6/IOCB6/PGC

RB7/IOCB7/PGD

RC0/IOCC0/T3CKI/T3G/T1CKI/SOSCO

RC1/IOCC1/CCP2/SOSCI

I = Input; O = Output; P = Power.

Pin Name

RB4 I/O TTL/DIG Digital Output or Input with internal pull-up option.

IOCB4 I TTL Interrupt-on-change pin.

P1D O DIG Enhanced CCP1 PWM output.

AN11 I Analog Analog input 11.

RB5 I/O TTL/DIG Digital Output or Input with internal pull-up option.

IOCB5 I TTL Interrupt-on-change pin.

(2)

T3CKI

T1G I ST Timer1 external clock gate input.

AN13 I Analog Analog input 13.

RB6 I/O TTL/DIG Digital Output or Input with internal pull-up option.

IOCB6 I TTL Interrupt-on-change pin.

PGC I/O ST In-Circuit Debugger and ICSP™ programming clock

RB7 I/O TTL/DIG Digital Output or Input with internal pull-up option.

IOCB7 I TTL Interrupt-on-change pin.

PGD I/O ST/DIG In-Circuit Debugger and ICSP™ programming data

RC0 I/O ST/DIG Digital I/O.

IOCC0 I TTL Interrupt-on-change pin.

(1)

T3CKI

T3G I ST Timer3 external clock gate input.

T1CKI I ST Timer1 clock input.

SOSCO O — Secondary oscillator output.

RC1 I/O ST/DIG Digital I/O.

IOCC1 I TTL Interrupt-on-change pin.

(1)

CCP2

SOSCI I Analog Secondary oscillator input.

Type

Buffer

Type

I ST Alternate Timer3 clock input.

pin.

pin.

I ST Timer3 clock input.

I/O ST/DIG Capture 2 input/Compare 2 output/PWM 2 output.

Description

2012 Microchip Technology Inc. DS30684A-page 17

PIC18(L)F2X/45K50

TABLE 1-2: PIC18(L)F2XK50 PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

Pin

PDIP,

SOIC,

SSOP

8, 19 5, 16 V

Legend: TTL = TTL compatible input; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;

Note 1: Default pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are set.

QFN

13 10 RC2/CTPLS/P1A/CCP1/IOCC2/AN14

14 11

15 12

16 13

17 14

18 15

1 26 RE3/VPP /MCLR

20 17 V

2: Alternate pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are clear.

VUSB3V3

D-/IOCC4

D+/IOCC5

RC6/IOCC6/TX/CK/AN18

RC7/SDO/IOCC7/RX/DT/AN19

I = Input; O = Output; P = Power.

Pin Name

RC2 I/O ST/DIG Digital I/O.

CTPLS O DIG CTMU pulse generator output.

P1A O DIG Enhanced CCP1 PWM output.

CCP1 I/O ST/DIG Capture 1 input/Compare 1 output/PWM 1 output.

IOCC2 I TTL Interrupt-on-change pin.

AN14 I Analog Analog input 14.

VUSB3V3 P — Internal 3.3V voltage regulator output, positive supply

D- I/O — USB differential minus line input/output.

IOCC4 I ST Interrupt-on-change pin.

D+ I/O — USB differential plus line input/output.

IOCC5 I ST Interrupt-on-change pin.

RC6 I/O ST/DIG Digital I/O.

IOCC6 I TTL Interrupt-on-change pin.

TX O DIG EUSART asynchronous transmit.

CK I/O ST EUSART synchronous clock (see related RX/DT).

AN18 I Analog Analog input 18.

RC7 I/O ST/DIG Digital I/O.

(2)

SDO

IOCC7 I TTL Interrupt-on-change pin.

RX I ST EUSART asynchronous receive.

DT I/O ST/DIG EUSART synchronous data (see related TX/CK).

AN19 I Analog Analog input 19.

RE3 I ST Digital input.

V

PP P Programming voltage input.

MCLR I ST Active-Low Master Clear (device Reset) input.

DD P — Positive supply for logic and I/O pins.

SS P — Ground reference for logic and I/O pins.

Type

Buffer

Type

for USB transceiver.

O DIG Alternate SPI data out pin assignment (MSSP).

Description

DS30684A-page 18 2012 Microchip Technology Inc.

PIC18(L)F2X/45K50

T ABLE 1-3: PIC18(L)F45K50 PINOUT I/O DESCRIPTIONS

Pin Number

PDIP TQFP UQFN

21917

32018

42119

52220

62321

72422

14 31 29

13 30 28

Legend: TTL = TTL compatible input; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;

I = Input; O = Output; P = Power.

Note 1: Default pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are set.

2: Alternate pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are clear.

3: Pin is “No Connect”, except on PIC18(L)F45K50 TQFP devices with ICPRT Configuration bit set.

Pin Name

RA0/C12IN0-/AN0

RA0 I/O TTL/DIG Digital I/O.

C12IN0- I Analog Comparators C1 and C2 inverting input.

AN0 I Analog Analog input 0.

RA1/C12IN1-/AN1

RA1 I/O TTL/DIG Digital I/O.

C12IN1- I Analog Comparators C1 and C2 inverting input.

AN1 I Analog Analog input 1.

RA2/C2IN+/AN2/DACOUT/VREF-

RA2 I/O TTL/DIG Digital I/O.

C2IN+ I Analog Comparator C2 non-inverting input.

AN2 I Analog Analog input 2.

DACOUT O Analog DAC Reference output.

REF- I Analog A/D reference voltage (low) input.

V

RA3/C1IN+/AN3/VREF+

RA3 I/O TTL/DIG Digital I/O.

C1IN+ I Analog Comparator C1 non-inverting input.

AN3 I Analog Analog input 3.

REF+ I Analog A/D reference voltage (high) input.

V

RA4/C1OUT/SRQ/T0CKI

RA4 I/O ST/DIG Digital I/O.

C1OUT O DIG Comparator C1 output.

SRQ O TTL SR latch Q output.

T0CKI I ST Timer0 external clock input.

RA5/C2OUT/SRNQ/SS/HLVDIN/AN4

RA5 I/O TTL/DIG Digital I/O.

C2OUT O DIG Comparator C2 output.

SRNQ O DIG SR latch Q output.

SS I TTL SPI slave select input (MSSP).

HLVDIN I Analog High/Low-Voltage Detect input.

AN4 I Analog Analog input 4.

RA6/CLKO/OSC2

RA6 I/O TTL/DIG Digital I/O.

CLKO O DIG Outputs 1/4 the frequency of OSC1 and denotes the

OSC2 O — Oscillator crystal output. Connects to crystal or resonator in

RA7/CLKI/OSC1

RA7 I/O TTL/DIG Digital I/O.

CLKI I CMOS External clock source input. Always associated with pin

OSC1 I ST Oscillator crystal input or external clock source input ST buffer

Pin

Type

Buffer

Type

Description

instruction cycle rate.

Crystal Oscillator mode.

function OSC1.

when configured in RC mode; CMOS otherwise.

2012 Microchip Technology Inc. DS30684A-page 19

PIC18(L)F2X/45K50

TABLE 1-3: PIC18(L)F45K50 PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

PDIP TQFP UQFN

33 8 8 RB0/INT0/FLT0

34 9 9

35 10 10

36 11 11 RB3/CTED2/SDO/CCP2/C12IN2-/AN9

37 14 12 RB4/IOCB4/P1D/AN11

38 15 13

Legend: TTL = TTL compatible input; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;

I = Input; O = Output; P = Power.

Note 1: Default pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are set.

2: Alternate pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are clear.

3: Pin is “No Connect”, except on PIC18(L)F45K50 TQFP devices with ICPRT Configuration bit set.

Pin Name

/SDI/SDA/SRI/AN12

RB0 I/O TTL/DIG Digital Output or Input with internal pull-up option.

INT0 I ST External interrupt 0.

FLT0

SDI I ST SPI Data in (MSSP).

SDA I/O I

SRI I ST SR latch input.

AN12 I Analog Analog input 12.

RB1/INT1/P1C/SCK/SCL/C12IN3-/AN10

RB1 I/O TTL/DIG Digital Output or Input with internal pull-up option.

INT1 I ST External interrupt 1.

P1C O DIG Enhanced CCP1 PWM output.

SCK I/O ST/DIG Synchronous serial clock input/output for SPI mode (MSSP).

SCL I/O I

C12IN3- I Analog Comparators C1 and C2 inverting input.

AN10 I Analog Analog input 10.

RB2/P1B/INT2/CTED1/AN8

RB2 I/O TTL/DIG Digital Output or Input with internal pull-up option.

P1B O DIG Enhanced CCP1 PWM output.

INT2 I ST External interrupt 2.

CTED1 I ST CTMU Edge 1 input.

AN8 I Analog Analog input 8.

RB3 I/O TTL/DIG Digital Output or Input with internal pull-up option.

CTED2 I ST CTMU Edge 2 input.

(1)

SDO

(2)

CCP2

C12IN2- I Analog Comparators C1 and C2 inverting input.

AN9 I Analog Analog input 9.

RB4 I/O TTL/DIG Digital Output or Input with internal pull-up option.

IOCB4 I TTL Interrupt-on-change pin.

P1D O DIG Enhanced CCP1 PWM output.

AN11 I Analog Analog input 11.

RB5/IOCB5/T3CKI/T1G/AN13

RB5 I/O TTL/DIG Digital Output or Input with internal pull-up option.

IOCB5 I TTL Interrupt-on-change pin.

(2)

T3CKI

T1G I ST Timer1 external clock gate input.

AN13 I Analog Analog input 13.

Pin

Buffer

Type

Type

I ST PWM Fault input for ECCP auto-shutdown.

2

C™ I2C™ Data I/O (MSSP).

2

C™ Synchronous serial clock input/output for I2C™ mode (MSSP).

O DIG SPI Data out (MSSP).

I/O ST Alternate Capture 2 input/Compare 2 output/PWM 2 output.

I ST Alternate Timer3 clock input.

Description

DS30684A-page 20 2012 Microchip Technology Inc.

PIC18(L)F2X/45K50

TABLE 1-3: PIC18(L)F45K50 PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

PDIP TQFP UQFN

39 16 14 RB6/IOCB6/PGC

40 17 15

15 32 30

16 35 31

17 36 32

18 37 33 V

23 42 38

24 43 39

Legend: TTL = TTL compatible input; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;

I = Input; O = Output; P = Power.

Note 1: Default pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are set.

2: Alternate pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are clear.

3: Pin is “No Connect”, except on PIC18(L)F45K50 TQFP devices with ICPRT Configuration bit set.

Pin Name

RB6 I/O TTL/DIG Digital Output or Input with internal pull-up option.

IOCB6 I TTL Interrupt-on-change pin.

PGC I/O ST In-Circuit Debugger and ICSP™ programming clock pin.

RB7/IOCB7/PGD

RB7 I/O TTL/DIG Digital Output or Input with internal pull-up option.

IOCB7 I TTL Interrupt-on-change pin.

PGD I/O ST In-Circuit Debugger and ICSP™ programming data pin.

RC0/IOCC0/T3CKI/T3G/T1CKI/SOSCO

RC0 I/O ST/DIG Digital I/O.

IOCC0 I TTL Interrupt-on-change pin.

(1)

T3CKI

T3G I ST Timer3 external clock gate input.

T1CKI I ST Timer1 clock input.

SOSCO O — Secondary oscillator output.

RC1/IOCC1/CCP2/SOSCI

RC1 I/O ST/DIG Digital I/O.

IOCC1 I TTL Interrupt-on-change pin.

(1)

CCP2

SOSCI I Analog Secondary oscillator input.

RC2/CTPLS/P1A/CCP1/IOCC2/AN14

RC2 I/O ST/DIG Digital I/O.

CTPLS O DIG CTMU pulse generator output.

P1A O DIG Enhanced CCP1 PWM output.

CCP1 I/O ST/DIG Capture 1 input/Compare 1 output/PWM 1 output.

IOCC2 I TTL Interrupt-on-change pin.

AN14 I Analog Analog input 14.

USB3V3

VUSB3V3 P — Internal 3.3V voltage regulator output, positive supply for USB

D-/IOCC4

D- I/O — USB differential minus line input/output.

IOCC4 I ST Interrupt-on-change pin.

D+/IOCC5

D+ I/O — USB differential plus line input/output.

IOCC5 I ST Interrupt-on-change pin.

Pin

Buffer

Type

Type

I ST Timer3 clock input.

I/O ST/DIG Capture 2 input/Compare 2 output/PWM 2 output.

transceiver.

Description

2012 Microchip Technology Inc. DS30684A-page 21

PIC18(L)F2X/45K50

TABLE 1-3: PIC18(L)F45K50 PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

PDIP TQFP UQFN

25 44 40 RC6/IOCC6/TX/CK/AN18

26 1 1

19 38 34 RD0/AN20

20 39 35

21 40 36 RD2/AN22

22 41 37

27 2 2

28 3 3

29 4 4

30 5 5

Legend: TTL = TTL compatible input; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;

I = Input; O = Output; P = Power.

Note 1: Default pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are set.

2: Alternate pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are clear.

3: Pin is “No Connect”, except on PIC18(L)F45K50 TQFP devices with ICPRT Configuration bit set.

Pin Name

RC6 I/O ST/DIG Digital I/O.

IOCC6 I TTL Interrupt-on-change pin.

TX O — EUSART asynchronous transmit.

CK I/O ST EUSART synchronous clock (see related RX/DT).

AN18 I Analog Analog input 18.

RC7/RX/DT/SDO/IOCC7/AN19

RC7 I/O ST/DIG Digital I/O.

RX I ST EUSART asynchronous receive.

DT I/O ST EUSART synchronous data (see related TX/CK).

(2)

SDO

IOCC7 I TTL Interrupt-on-change pin.

AN19 I Analog Analog input 19.

RD0 I/O ST/DIG Digital I/O.

AN20 I Analog Analog input 20.

RD1/AN21

RD1 I/O ST/DIG Digital I/O.

AN21 I Analog Analog input 21.

RD2 I/O ST/DIG Digital I/O

AN22 I Analog Analog input 22.

RD3/AN23

RD3 I/O ST/DIG Digital I/O.

AN23 I Analog Analog input 23.

RD4/AN24

RD4 I/O ST/DIG Digital I/O.

AN24 I Analog Analog input 24.

RD5/P1B/AN25

RD5 I/O ST/DIG Digital I/O.

P1B O DIG Enhanced CCP1 PWM output.

AN25 I Analog Analog input 25.

RD6/P1C/AN26

RD6 I/O ST/DIG Digital I/O.

P1C O DIG Enhanced CCP1 PWM output.

AN26 I Analog Analog input 26.

RD7/P1D/AN27

RD7 I/O ST/DIG Digital I/O.

P1D O DIG Enhanced CCP1 PWM output.

AN27 I Analog Analog input 27.

Pin

Buffer

Type

Type

O DIG Alternate SPI data out (MSSP).

Description

DS30684A-page 22 2012 Microchip Technology Inc.

PIC18(L)F2X/45K50

TABLE 1-3: PIC18(L)F45K50 PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

PDIP TQFP UQFN

82523RE0/AN5

92624

10 27 25 RE2/AN7

11816

— 12 — ICCK/ICPGC

— 13 — ICDT/ICPGD

— 33 — ICRST

11,32 7, 28 7, 26 V

12,31 6, 29 6, 27 V

34 NC

Legend: TTL = TTL compatible input; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;

I = Input; O = Output; P = Power.

Note 1: Default pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are set.

2: Alternate pin assignment for SDO, T3CKI and CCP2 when Configuration bits SDOMX, T3CMX and CCP2MX are clear.

3: Pin is “No Connect”, except on PIC18(L)F45K50 TQFP devices with ICPRT Configuration bit set.

Pin Name

RE0 I/O ST/DIG Digital I/O.

AN5 I Analog Analog input 5.

RE1/AN6

RE1 I/O ST/DIG Digital I/O.

AN6 I Analog Analog input 6.

RE2 I/O ST Digital I/O.

AN7 I Analog Analog input 7.

RE3/VPP/MCLR

RE3 I ST Digital input.

PP P Programming voltage input.

V

MCLR

ICCK I/O ST Dedicated In-Circuit Debugger clock.

(3)

ICPGC

ICDT I/O ST Dedicated In-Circuit Debugger data.

(3)

ICPGD

/ICVPP

ICRST I ST Dedicated Master Clear Reset input.

(3)

ICV

PP

DD P — Positive supply for logic and I/O pins.

SS P — Ground reference for logic and I/O pins.

Pin

Buffer

Type

Type

I ST Active-low Master Clear (device Reset) input.

I/O ST Dedicated ICSP™ programming clock.

I/O ST Dedicated ICSP™ programming data.

I P Dedicated programming voltage input.

Description

2012 Microchip Technology Inc. DS30684A-page 23

PIC18(L)F2X/45K50

NOTES:

DS30684A-page 24 2012 Microchip Technology Inc.

PIC18(L)F2X/45K50

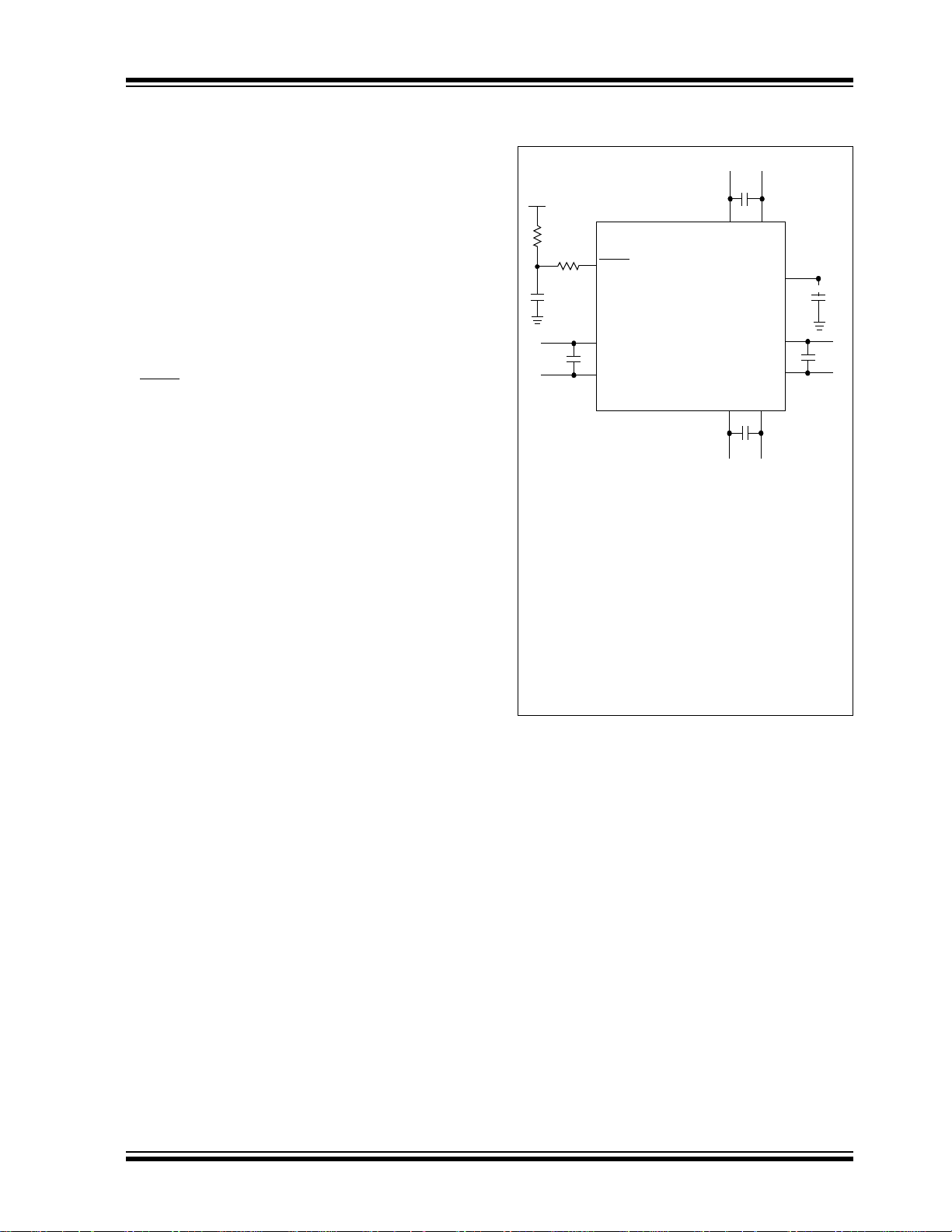

PIC18F2X/45K50

VDD

VSS

VDD

VSS

VSS

VDD

VDD

VSS

C1

R1

V

DD

MCLR

VUSB3V3

R2

C7

(2)

C2

(2)

C3

(2)

C4

(2)

C6

(2)

Key (all values are recommendations):

C1 through C6: 0.1 F, 20V ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

Note 1: See Section 2.4 “Voltage Regulator Pins

(V

USB3V3)” for explanation of VUSB3V3 pin

connections.

2: The example shown is for a PIC18F device

with five V

DD/VSS pairs. Other devices may

have more or less pairs; adjust the number

of decoupling capacitors appropriately.

(1)

2.0 GUIDELINES FOR GETTING

STARTED WITH

FIGURE 2-1: RECOMMENDED

MINIMUM CONNECTIONS

PIC18(L)F2X/45K50

MICROCONTROLLERS

2.1 Basic Connection Requirements

Getting started with the PIC18(L)F2X/45K50 family of

8-bit microcontrollers requires attention to a minimal

set of device pin connections before proceeding with

development.

The following pins must always be connected:

DD and VSS pins

•All V

(see Section 2.2 “Power Supply Pins”)

•MCLR

•V

These pins must also be connected if they are being

used in the end application:

• PGC/PGD pins used for In-Circuit Serial

• OSC1 and OSC2 pins when an external oscillator

Additionally, the following pins may be required:

•V

The minimum mandatory connections are shown in

Figure 2-1.

pin

(see Section 2.3 “Master Clear (MCLR) Pin”)

USB3V3 pins

(see Section 2.4 “Voltage Regulator Pins

(VUSB3V3)”)

Programming™ (ICSP™) and debugging purposes

(see Section 2.5 “ICSP Pins”)

source is used

(see Section 2.6 “External Oscillator Pins”)

REF+/VREF- pins are used when external voltage

reference for analog modules is implemented

2012 Microchip Technology Inc. DS30684A-page 25

PIC18(L)F2X/45K50

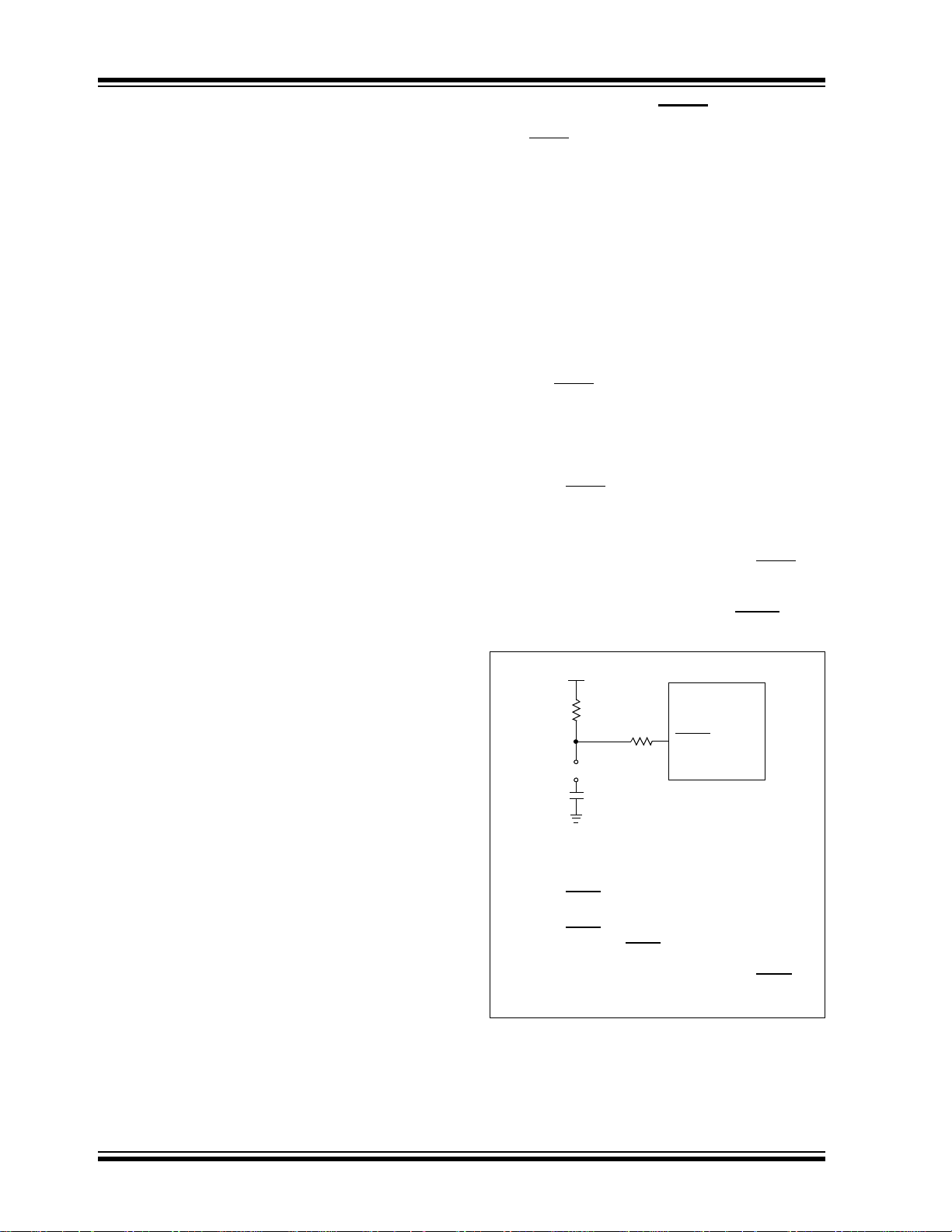

Note 1: R1 10 k is recommended. A suggested

starting value is 10 k. Ensure that the

MCLR

pin VIH and VIL specifications are met.

2: R2 470 will limit any current flowing into

MCLR

from the external capacitor, C, in the

event of MCLR

pin breakdown, due to

Electrostatic Discharge (ESD) or Electrical

Overstress (EOS). Ensure that the MCLR

pin

V

IH and VIL specifications are met.

C1

R2

R1

V

DD

MCLR

PIC18F2X/45K50

JP

2.2 Power Supply Pins

2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of

power supply pins, such as V

Consider the following criteria when using decoupling

capacitors:

• Value and type of capacitor: A 0.1 F (100 nF),

10-20V capacitor is recommended. The capacitor

should be a low-ESR device, with a resonance

frequency in the range of 200 MHz and higher.

Ceramic capacitors are recommended.

• Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended to

place the capacitors on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is no greater

than 0.25 inch (6 mm).

• Handling high-frequency noise: If the board is

experiencing high-frequency noise (upward of

tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling

capacitor. The value of the second capacitor can

be in the range of 0.01 F to 0.001 F. Place this

second capacitor next to each primary decoupling

capacitor. In high-speed circuit designs, consider

implementing a decade pair of capacitances as

close to the power and ground pins as possible

(e.g., 0.1 F in parallel with 0.001 F).

• Maximizing performance: On the board layout

from the power supply circuit, run the power and

return traces to the decoupling capacitors first,

and then to the device pins. This ensures that the

decoupling capacitors are first in the power chain.

Equally important is to keep the trace length

between the capacitor and the power pins to a

minimum, thereby reducing PCB trace

inductance.

DD and VSS is required.

2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device

functions: Device Reset, and Device Programming

and Debugging. If programming and debugging are

not required in the end application, a direct

connection to V

addition of other components, to help increase the

application’s resistance to spurious Resets from

voltage sags, may be beneficial. A typical

configuration is shown in Figure 2-1. Other circuit

designs may be implemented, depending on the

application’s requirements.

During programming and debugging, the resistance

and capacitance that can be added to the pin must

be considered. Device programmers and debuggers

drive the MCLR

levels (V

IH and VIL) and fast signal transitions must

not be adversely affected. Therefore, specific values

of R1 and C1 will need to be adjusted based on the

application and PCB requirements. For example, it is

recommended that the capacitor, C1, be isolated

from the MCLR

debugging operations by using a jumper (Figure 2-2).

The jumper is replaced for normal run-time

operations.

Any components associated with the MCLR

should be placed within 0.25 inch (6 mm) of the pin.

FIGURE 2-2: EXAMPLE OF MCLR PIN

DD may be all that is required. The

pin. Consequently, specific voltage

pin during programming and

pin

CONNECTIONS

2.2.2 TANK CAPACITORS

On boards with power traces running longer than

six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to

supply a local power source. The value of the tank

capacitor should be determined based on the trace

resistance that connects the power supply source to

the device, and the maximum current drawn by the

device in the application. In other words, select the tank

capacitor so that it meets the acceptable voltage sag at

the device. Typical values range from 4.7 F to 47 F.

DS30684A-page 26 2012 Microchip Technology Inc.

PIC18(L)F2X/45K50

-80

-70

-60

-50

-40

-30

-20

-10

0

10

5 1011121314151617

DC Bias Voltage (VDC)

Capacitance Change (%)

01234 6789

16V Capacitor

10V Capacitor

6.3V Capacitor

2.4 Volt age Regulator Pins (VUSB3V3)

The on-chip voltage regulator must always be

connected directly to either a supply voltage or to an

external capacitor.

When the regulator is enabled (F devices), a low-ESR

(< 5Ω) capacitor is required on the V

stabilize the voltage regulator output voltage. The

USB3V3 pin must not be connected to VDD and is

V

recommended to use a ceramic capacitor of between

0.22 to 0.47 µF connected to ground.

It is recommended that the trace length not exceed

0.25 inch (6 mm). Refer to Section 29.0 “Electrical

Characteristics” for additional information.

When the regulator is disabled (LF devices), the

USB3V3 pin should be externally tied to a voltage

V

source maintained at the V

Section 29.0 “Electrical Characteristics” for

information on VDD and VUSB3V3.

• LF devices (with the name, PIC18LF2X/45K50)

permanently disable the voltage regulator.

DD level of these devices must comply with

The V

the “voltage regulator disabled” specification for

Parameter D001, in Section 29.0 “Electrical

Characteristics”.

• F devices permanently enable the voltage

regulator.

These devices require an external capacitor on

USB3V3 pin. It is recommended that the

the V

capacitor be a ceramic cap between 0.22 to

0.47 µF.

USB3V3 pin to

DD level. Refer to

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex: ±15% over a wide

temperature range, but consult the manufacturer’s data

sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance

specifications of +22%/-82%. Due to the extreme

temperature tolerance, a 10 F nominal rated Y5V type

capacitor may not deliver enough total capacitance to

meet minimum internal voltage regulator stability and

transient response requirements. Therefore, Y5V

capacitors are not recommended for use with the

internal regulator if the application must operate over a

wide temperature range.

In addition to temperature tolerance, the effective

capacitance of large value ceramic capacitors can vary

substantially, based on the amount of DC voltage

applied to the capacitor. This effect can be very significant, but is often overlooked or is not always

documented.

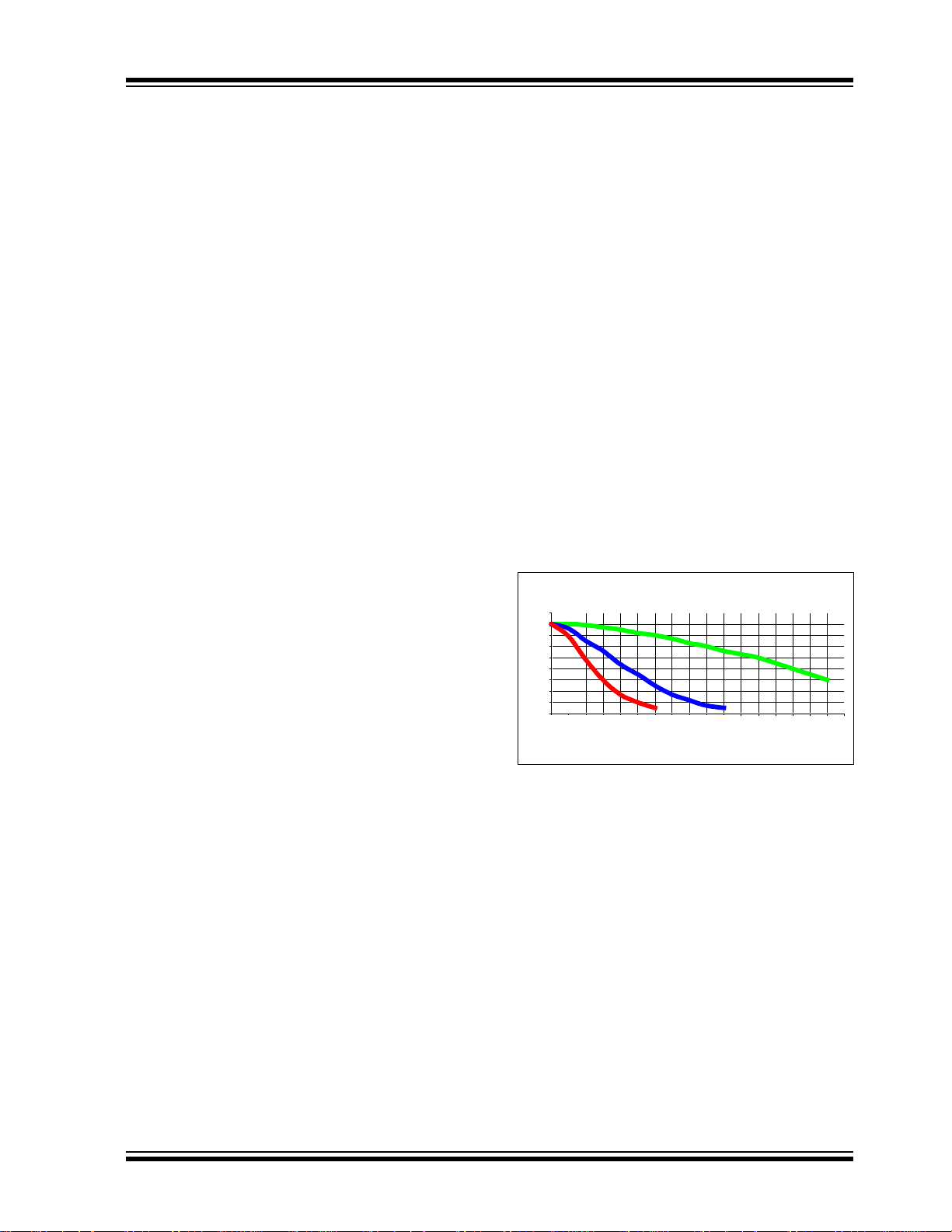

A typical DC bias voltage vs. capacitance graph for

X7R type and Y5V type capacitors is shown in

Figure 2-3.

FIGURE 2-3: DC BIAS VOLTAGE vs.

CAPACITANCE

CHARACTERISTICS

2.4.1 CONSIDERATIONS FOR CERAMIC

In recent years, large value, low-voltage, surface-mount

ceramic capacitors have become very cost effective in

sizes up to a few tens of microfarad. The low-ESR, small

physical size and other properties make ceramic

capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However,

some care is needed in selecting the capacitor to

ensure that it maintains sufficient capacitance over the

intended operating range of the application.

Typical low-cost, ceramic capacitors are available in

X5R, X7R and Y5V dielectric ratings (other types are

also available, but are less common). The initial tolerance specifications for these types of capacitors are

often specified as ±10% to ±20% (X5R and X7R), or

-20%/+80% (Y5V). However, the effective capacitance

that these capacitors provide in an application circuit will

also vary based on additional factors, such as the

applied DC bias voltage and the temperature. The total

in-circuit tolerance is, therefore, much wider than the

initial tolerance specification.

2012 Microchip Technology Inc. DS30684A-page 27

CAPACITORS

When selecting a ceramic capacitor to be used with the

internal voltage regulator, it is suggested to select a

high-voltage rating, so that the operating voltage is a

small percentage of the maximum rated capacitor

voltage. For example, choose a ceramic capacitor

rated at 16V for the 3.3V V

USB3V3 voltage.

PIC18(L)F2X/45K50

2.5 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial

Programming™ (ICSP™) and debugging purposes. It

is recommended to keep the trace length between the

ICSP connector and the ICSP pins on the device as

short as possible. If the ICSP connector is expected to

experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of

ohms, not to exceed 100Ω.

Pull-up resistors, series diodes and capacitors on the

PGC and PGD pins are not recommended as they will

interfere with the programmer/debugger communications to the device. If such discrete components are an

application requirement, they should be removed from

the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing

requirements information in the respective device

Flash programming specification for information on

capacitive loading limits, and pin input voltage high

IH) and input low (VIL) requirements.

(V

For device emulation, ensure that the “Communication

Channel Select” (i.e., PGCx/PGDx pins), programmed

into the device, matches the physical connections for

the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip

development tools connection requirements, refer to

Section 28.0 “Development Support”.

2.6 External Oscillator Pins

Many microcontrollers have options for at least two

oscillators: a high-frequency primary oscillator and a

low-frequency secondary oscillator (refer to

Section 3.0 “Oscillator Module (With Fail-Safe

Clock Monitor)” for details).

The oscillator circuit should be placed on the same

side of the board as the device. Place the oscillator

circuit close to the respective oscillator pins with no

more than 0.5 inch (12 mm) between the circuit

components and the pins. The load capacitors should

be placed next to the oscillator itself, on the same side

of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The

grounded copper pour should be routed directly to the

MCU ground. Do not run any signal traces or power

traces inside the ground pour. Also, if using a two-sided

board, avoid any traces on the other side of the board

where the crystal is placed.

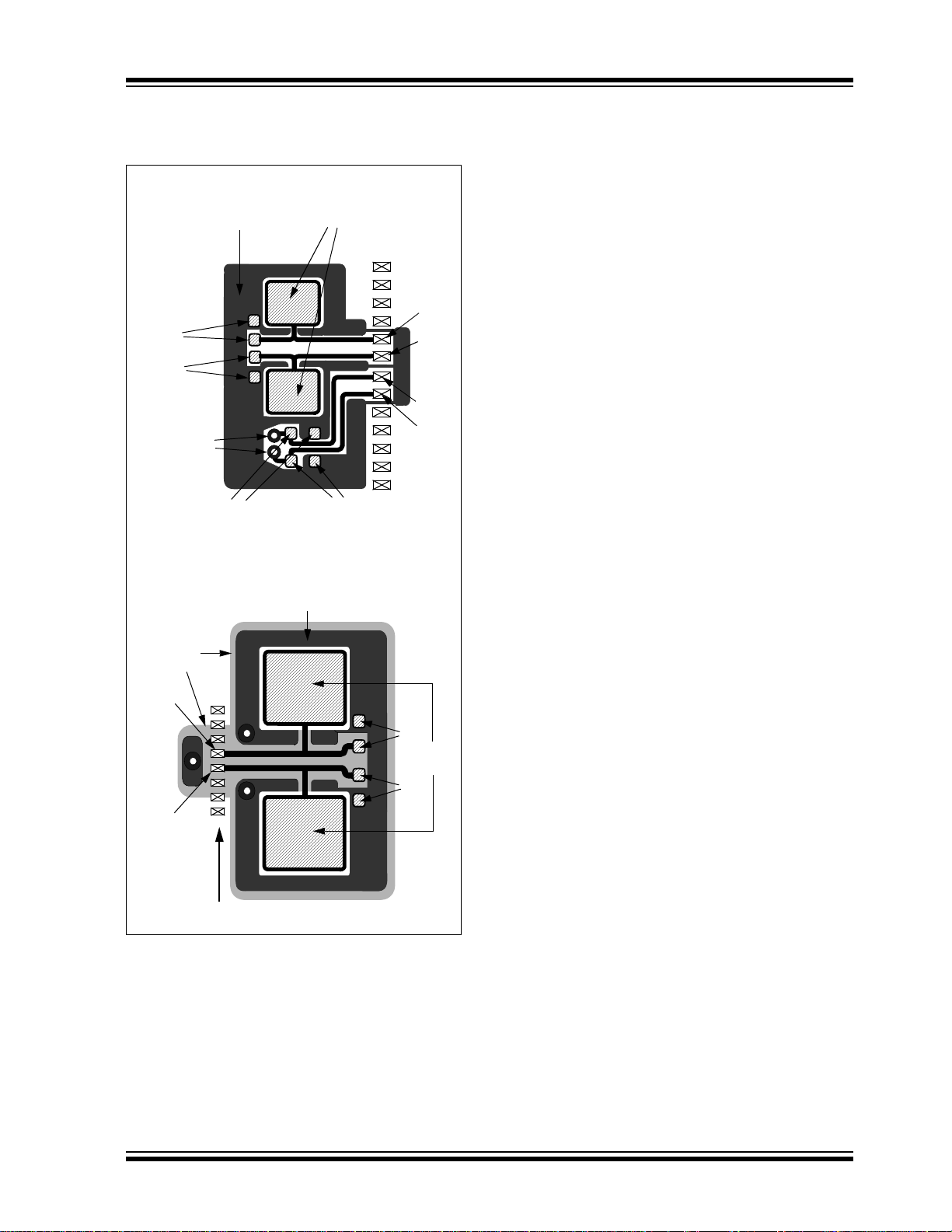

Layout suggestions are shown in Figure 2-4. In-line

packages may be handled with a single-sided layout

that completely encompasses the oscillator pins. With

fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable

solution is to tie the broken guard sections to a mirrored

ground layer. In all cases, the guard trace(s) must be

returned to ground.

In planning the application’s routing and I/O assignments, ensure that adjacent port pins, and other

signals in close proximity to the oscillator, are benign

(i.e., free of high frequencies, short rise and fall times,

and other similar noise).

For additional information and design guidance on

oscillator circuits, please refer to these Microchip

Application Notes, available at the corporate web site

(www.microchip.com):

• AN826, “Crystal Oscillator Basics and Crystal

Selection for rfPIC™ and PICmicro

• AN849, “Basic PICmicro® Oscillator Design”

• AN943, “Practical PICmicro

and Design”

• AN949, “Making Your Oscillator Work”

®

Devices”

®

Oscillator Analysis

2.7 Unused I/Os

Unused I/O pins should be configured as outputs and

driven to a logic low state. Alternatively, connect a 1 kΩ

to 10 kΩ resistor to V

output to logic low.

DS30684A-page 28 2012 Microchip Technology Inc.

SS on unused pins and drive the

FIGURE 2-4: SUGGESTE D

GND

`

`

`

OSC1

OSC2

SOSCO

SOSCI

Copper Pour

Primary Oscillator

Crystal

Timer1 Oscillator

Crystal

DEVICE PINS

Primary

Oscillator

C1

C2

T1 Oscillator: C1

T1 Oscillator: C2

(tied to ground)

Single-Sided and In-Line Layouts:

Fine-Pitch (Dual-Sided) Layouts:

GND

OSCO

OSCI

Bottom Layer

Copper Pour

Oscillator

Crystal

Top Layer Copper Pour

C2

C1

DEVICE PINS

(tied to ground)

(tied to ground)

PIC18(L)F2X/45K50

PLACEMENT OF THE

OSCILLATOR CIRCUIT

2012 Microchip Technology Inc. DS30684A-page 29

PIC18(L)F2X/45K50

NOTES:

DS30684A-page 30 2012 Microchip Technology Inc.

Loading...

Loading...