PIC16(L)F1454/5/9

Data Sheet

14/20-Pin Flash, 8-Bit USB Microcontrollers

with XLP Technology

2012 Microchip Technology Inc. Preliminary DS41639A

Note the following details of the code protection feature on Microchip devices:

YSTEM

CERTIFIED BY DNV

== ISO/TS 16949 ==

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device

applications and the like is provided only for your convenience

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION,

INCLUDING BUT NOT LIMITED TO ITS CONDITION,

QUALITY, PERFORMANCE, MERCHANTABILITY OR

FITNESS FOR PURPOSE. Microchip disclaims all liability

arising from this information and its use. Use of Microchip

devices in life support and/or safety applications is entirely at

the buyer’s risk, and the buyer agrees to defend, indemnify and

hold harmless Microchip from any and all damages, claims,

suits, or expenses resulting from such use. No licenses are

conveyed, implicitly or otherwise, under any Microchip

intellectual property rights.

Trademarks

The Microchip name and logo, the Microchip logo, dsPIC,

K

EELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART,

32

PIC

logo, rfPIC and UNI/O are registered trademarks of

Microchip Technology Incorporated in the U.S.A. and other

countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor,

MXDEV, MXLAB, SEEVAL and The Embedded Control

Solutions Company are registered trademarks of Microchip

Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, chipKIT,

chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net,

dsPICworks, dsSPEAK, ECAN, ECONOMONITOR,

FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP,

Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB,

MPLINK, mTouch, Omniscient Code Generation, PICC,

PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE,

rfLAB, Select Mode, Total Endurance, TSHARC,

UniWinDriver, WiperLock and ZENA are trademarks of

Microchip Technology Incorporated in the U.S.A. and other

countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2012, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT S

DS41639A-page 2 Preliminary 2012 Microchip Technology Inc.

ISBN: 9781620763476

Microchip received ISO/TS-16949:2009 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Company’s quality system processes and procedures

are for its PIC

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

®

MCUs and dsPIC® DSCs, KEELOQ

®

code hopping

PIC16(L)F1454/5/9

14/20-Pin, 8-Bit Flash USB Microcontroller with

XLP Technology

High-Performance RISC CPU:

• C Compiler Optimized Architecture

• Only 49 Instructions

• 14 Kbytes Linear Program Memory Addressing

• 1024 Bytes Linear Data Memory Addressing

• Operating Speed:

- DC – 48 MHz clock input

- DC – 83 ns instruction cycle

- Selectable 3x or 4x PLL for specific frequencies

• Interrupt Capability with Automatic Context

Saving

• 16-Level Deep Hardware Stack with Optional

Overflow/Underflow Reset

• Direct, Indirect and Relative Addressing modes:

- Two full 16-bit File Select Registers (FSRs)

capable of accessing both data or program

memory

- FSRs can read program and data memory

Special Microcontroller Features:

• Operating Voltage Range:

- 1.8V to 3.6V (PIC16LF145X)

- 2.3V to 5.5V (PIC16F145X)

• Self-Programmable under Software Control

• Power-on Reset (POR)

• Power-up Timer (PWRT)

• Programmable Brown-Out Reset (BOR)

• Low-Power BOR (LPBOR)

• Extended Watchdog Timer (WDT):

- Programmable period from 1 ms to 256s

• Programmable Code Protection

• In-Circuit Serial Programming™ (ICSP™) via Two

Pins

• Enhanced Low-Voltage Programming (LVP)

• Power-Saving Sleep mode:

Universal Serial Bus (USB) Features:

• Self-Tuning from USB Host

(eliminates need for external crystal)

• USB V2.0 Compliant SIE

• Low Speed (1.5 Mb/s) and Full Speed (12 Mb/s)

• Supports Control, Interrupt, Isochronous and Bulk

Transfers

• Supports up to Eight Bidirectional Endpoints

• 512-Byte Dual Access RAM for USB

• Interrupt-on-Change (IOC) on D+/D- for USB Host

Detection

• Configurable Internal Pull-up Resistors for use

with USB

Extreme Low-Power Management PIC16LF145X with XLP:

• Sleep mode: 25 nA @ 1.8V, typical

• Watchdog Timer Current: 290 nA @ 1.8V, typical

• Timer1 Oscillator: 600 nA @ 32 kHz, typical

• Operating Current: 25 A/MHz @ 1.8V, typical

Flexible Oscillator Structure:

• 16 MHz Internal Oscillator Block:

- Factory calibrated to ±0.25%, typical

- Software selectable frequency range from

16 MHz to 31 kHz

- Tunable to 0.25% across temperature range

- 48 MHz with 3x PLL

• 31 kHz Low-Power Internal Oscillator

• Clock Switching with run from:

- Primary Oscillator

- Secondary Oscillator (SOSC)

- Internal Oscillator

• Clock Reference Output:

- Clock Prescaler

-CLKOUT

Analog Features

• Analog-to-Digital Converter (ADC):

- 10-bit resolution

- Up to nine external channels

- Two internal channels:

- Fixed Voltage Reference channel

- DAC output channel

- Auto acquisition capability

- Conversion available during Sleep

• Two Comparators:

- Rail-to-rail inputs

- Power mode control

- Software controllable hysteresis

• Voltage Reference module:

- Fixed Voltage Reference (FVR) with 1.024V,

2.048V and 4.096V output levels

• Up to One Rail-to-Rail Resistive 5-Bit DAC with

Positive Reference Selection

Note 1: Analog features are not available on

PIC16(L)F1454 devices.

(1)

:

2012 Microchip Technology Inc. Preliminary DS41639A-page 3

PIC16(L)F145X

Peripheral Features:

• Up to 14 I/O Pins and Three Input-only Pins:

- High current sink/source 25 mA/25 mA

- Individually programmable weak pull-ups

- Individually programmable

Interrupt-On-Change (IOC) pins

• Timer0: 8-Bit Timer/Counter with 8-Bit

Programmable Prescaler

• Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

• Timer2: 8-Bit Timer/Counter with 8-Bit Period

Register, Prescaler and Postscaler

• Two 10-bit PWM modules

• Complementary Waveform Generator (CWG)

- Up to four selectable signal sources

- Selectable falling and rising edge dead-band

control

- Polarity control

- Up to four auto-shutdown sources

- Multiple input sources: PWM, Comparators

• Master Synchronous Serial Port (MSSP) with SPI

2

C™ with:

and I

- 7-bit address masking

- SMBus/PMBus™ compatibility

• Enhanced Universal Synchronous

Asynchronous Receiver Transmitter (EUSART):

- RS-232, RS-485 and LIN compatible

- Auto-baud detect

- Auto-wake-up on Start

(1)

:

Note 1: Not available on PIC16(L)F1454 devices.

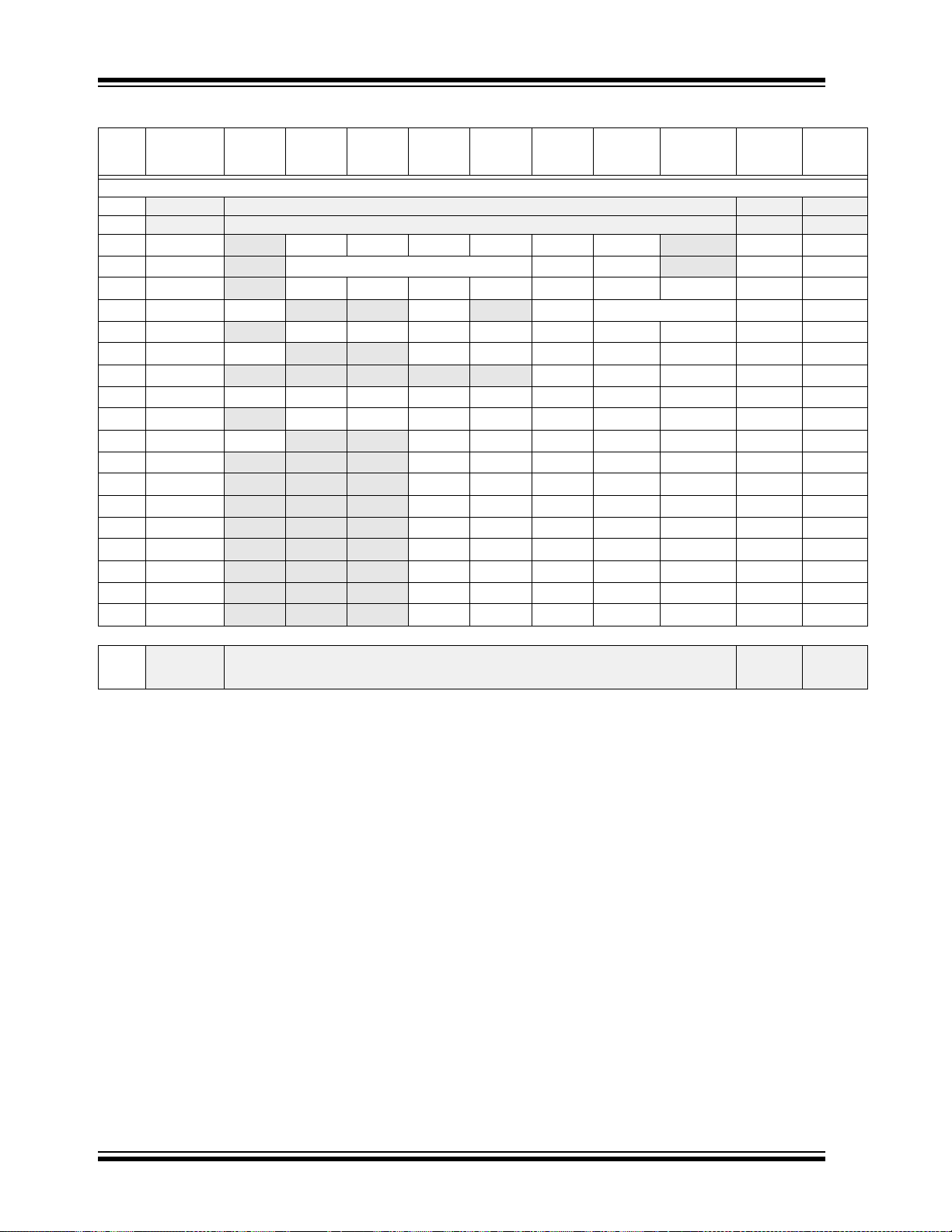

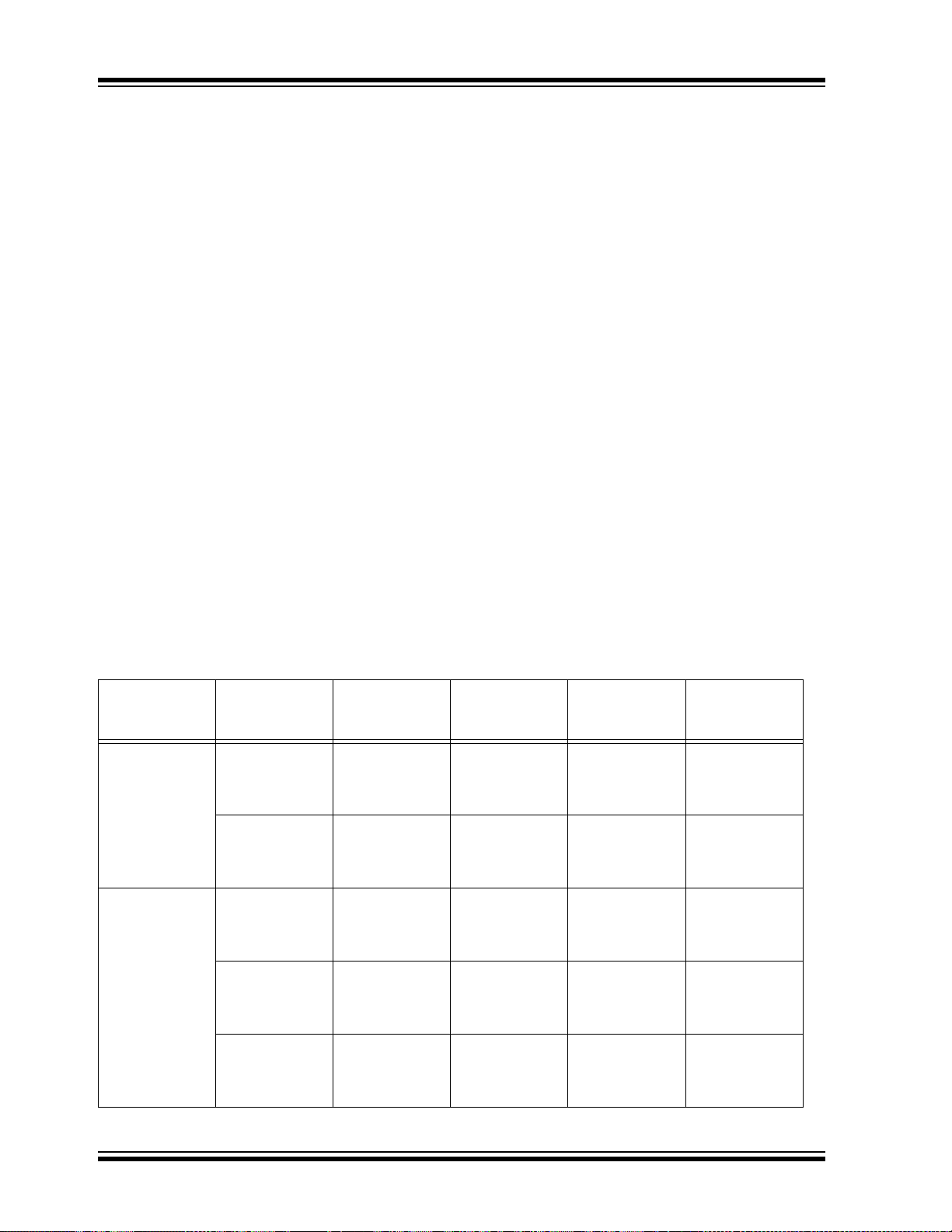

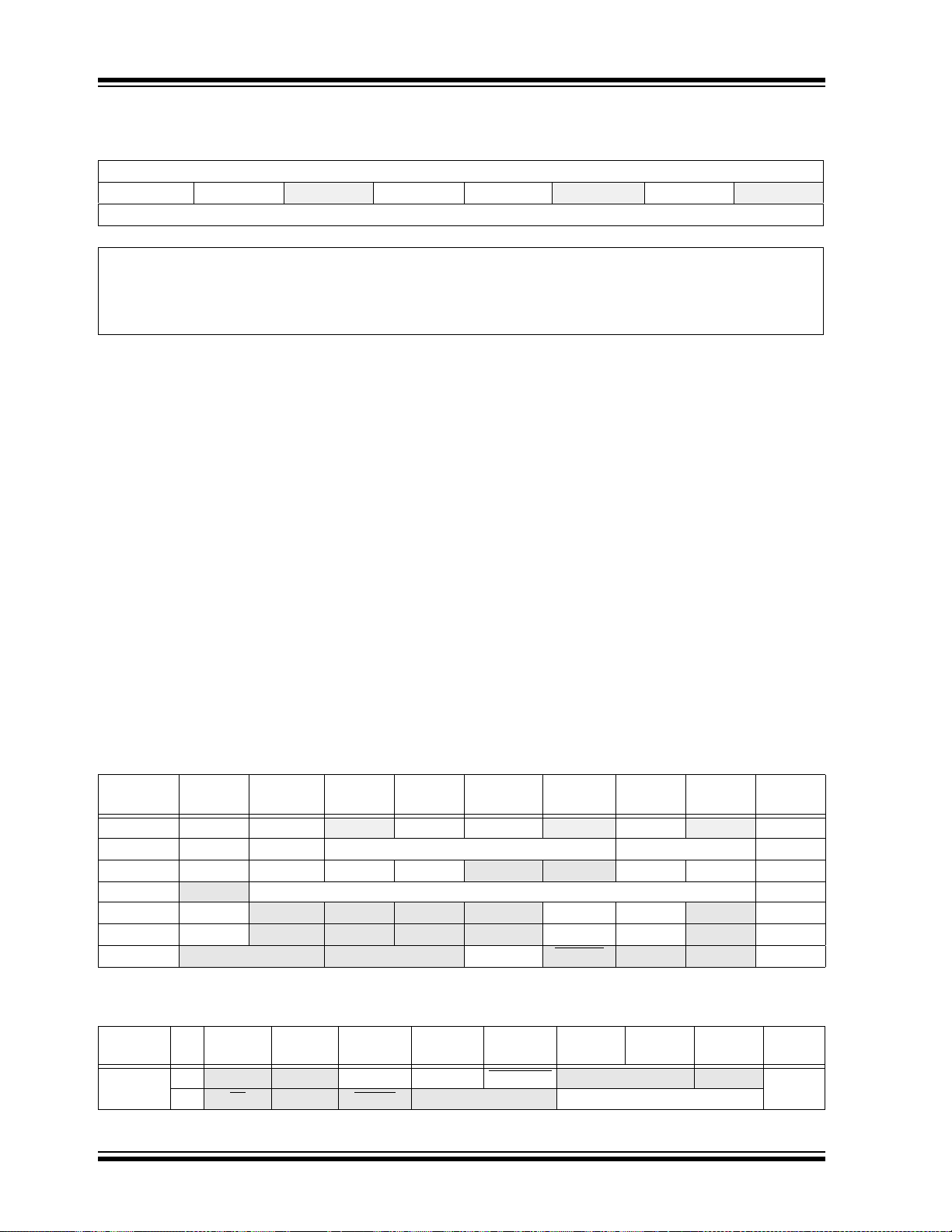

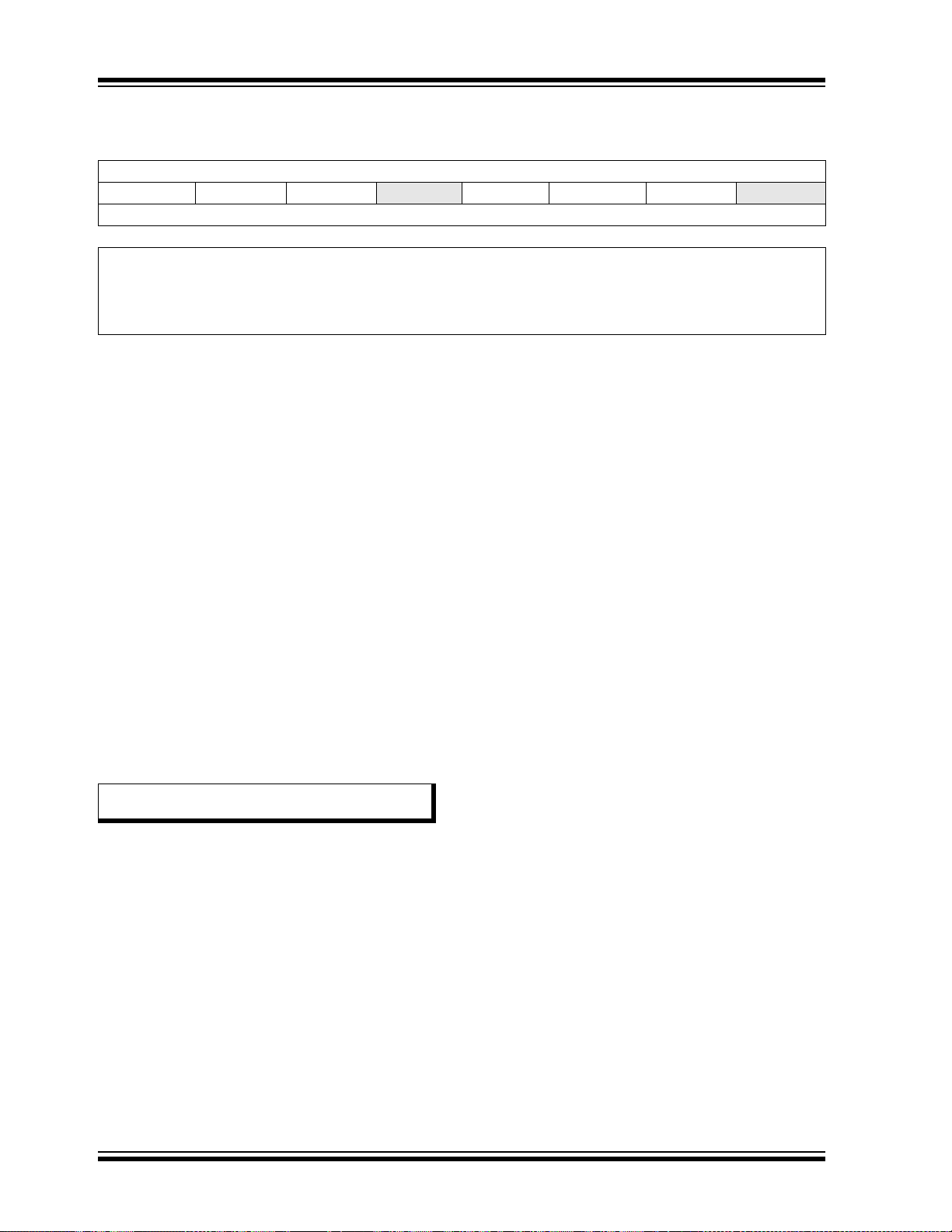

PIC16(L)F145X Family Types

(1)

Debug

Clock Reference

(bytes)

Data SRAM

(2)

Comparators

DAC

Timers

I/Os

10-bit ADC (ch)

PWM

(8/16-bit)

Device

Program Memory

Flash (words)

Data Sheet Index

PIC16(L)F1454 (1) 8192 1024 11 — — — 2/1 2 1 1 — 1 1 I/H Y

PIC16(L)F1455 (1) 8192 1024 11 5 2 1 2/1 2 1 1 1 1 1 I/H Y

PIC16(L)F1459 (1) 8192 1024 17 9 2 1 2/1 2 1 1 1 1 1 I/H Y

Note 1: I - Debugging, Integrated on Chip; H - Debugging, Available using Debug Header;

E - Emulation, Available using Emulation Header.

2: Three pins are input-only.

Data Sheet Index:

1: DS41639 PIC16(L)F1454/1455/1459 Data Sheet, 14/20-Pin Flash, 8-Bit USB Microcontrollers.

Note: For other small form-factor package availability and marking information, please visit

www.microchip.com/packaging or contact your local sales office.

C™/SPI)

2

EUSART

MSSP (I

USB

CWG

XLP

DS41639A-page 4 Preliminary 2012 Microchip Technology Inc.

PIC16(L)F145X

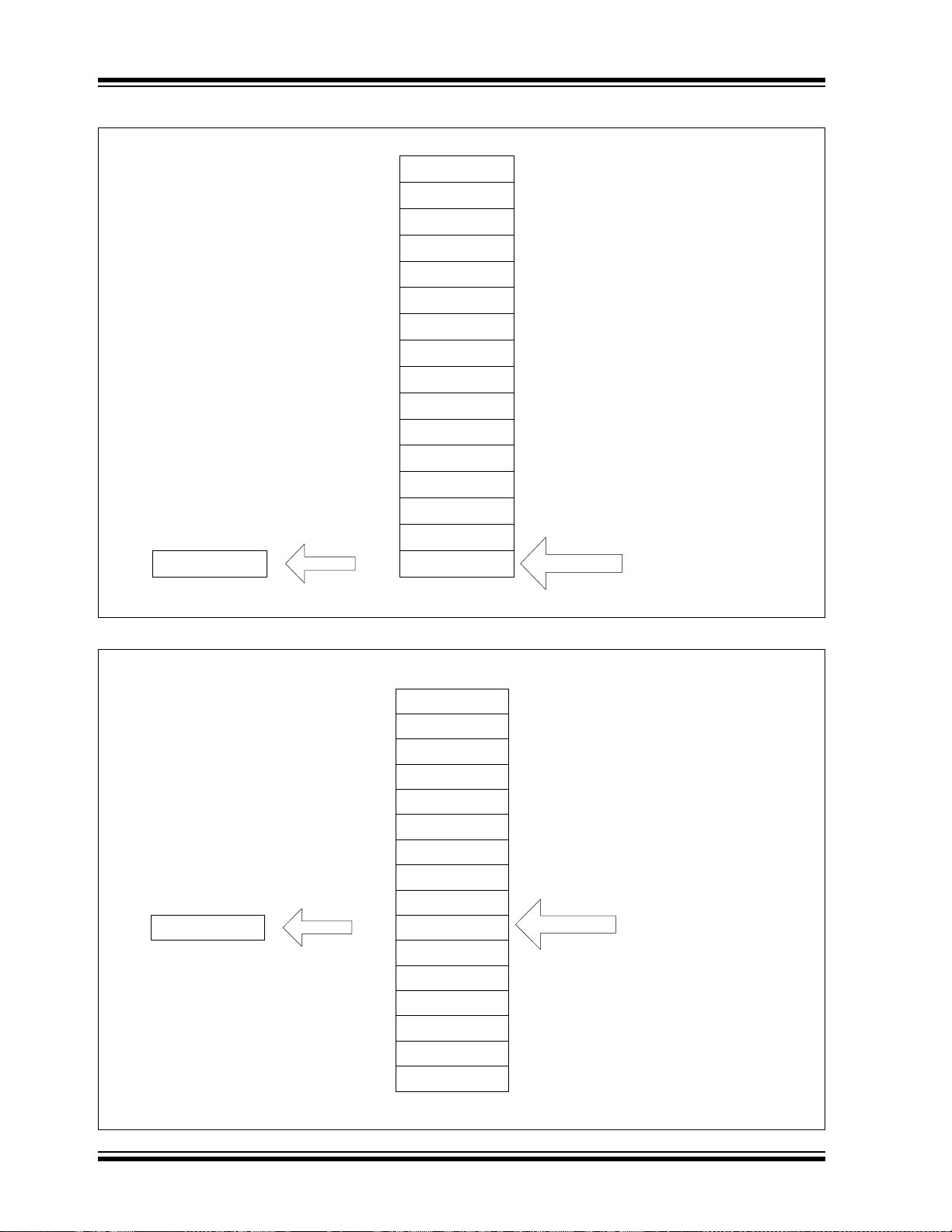

PDIP, SOIC, TSSOP

PIC16(L)F1454

PIC16(L)F1455

1

2

3

4

14

13

12

11

5

6

7

10

9

8

VDD

RA5

RA4

MCLR

/VPP/RA3

RC5

RC4

RC3

V

SS

RA0/D+/ICSPDAT

(1)

RA1/D-/ICSPCLK

(1)

VUSB3V3

RC0/ICSPDAT

RC1/ICSPCLK

RC2

Note 1: LVP support for PIC18(L)F1XK50 legacy designs.

2: See Ta bl e 1 and Tab l e 2 for location of all peripheral functions.

78

2

3

1

11

12

5

9

10

13141516

6

4

RA5

RA4

MCLR/VPP/RA3

RC4

RC3

ICSPCLK/RC1

RC2

RC0/ICSPDAT

RA0/D+/ICSPDAT

(1)

VUSB3V3

RA1/D-/ICSPCLK

(1)

Vss

VDD

NC

RC5

NC

QFN (4x4)

Note 1: LVP support for PIC18(L)F1XK50 legacy designs.

2: See Tab le 1 and Ta bl e 2 for location of all peripheral functions.

PIC16(L)F1454

PIC16(L)F1455

FIGURE 1: 14-PIN PDIP, SOIC, TSSOP DIAGRAM FOR PIC16(L)F1454/1455

FIGURE 2: 16-PIN QFN DIAGRAM FOR PIC16(L)F1454/1455

2012 Microchip Technology Inc. Preliminary DS41639A-page 5

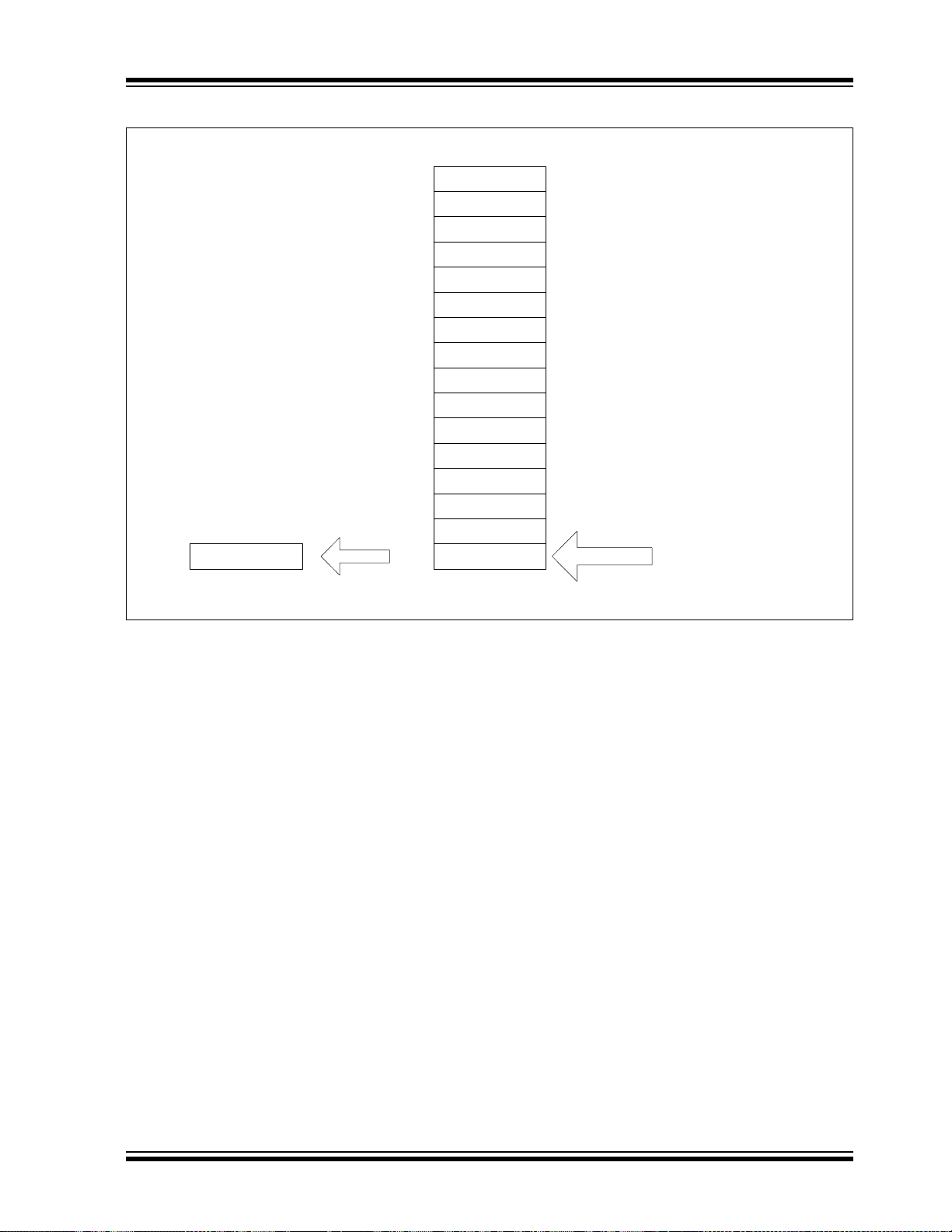

PIC16(L)F145X

PIC16(L)F1459

1

2

3

4

14

13

12

11

5

6

7

10

9

8

VDD

RA5

RA4

MCLR

/VPP/RA3

RC5

RC4

V

SS

RA0/D+/ICSPDAT

(1)

RA1/D-/ICSPCLK

(1)

VUSB3V3

RC0/ICSPDAT

RC1/ICSPCLK

RC2

RC3

PDIP, SOIC, SSOP

Note 1: LVP support for PIC18(L)F1XK50 legacy designs.

2: See Ta bl e 3 for location of all peripheral functions.

18

17

16

15

20

19

RC6

RC7

RB7

RB4

RB5

RB6

89

2

3

1

14

15

16

10

11

6

12

13

17181920

7

5

4

MCLR/VPP/RA3

RC5

RC4

RC3

RC6

RC7

RB7

RB4

RB5

RB6

RC1/ICSPCLK

RC0/ICSPDAT

V

USB3V3

RA1/D-/ICSPCLK

(1)

RA0/D+/ICSPDAT

(1)

Vss

V

DD

RA4

RA5

RC2

QFN (4x4)

Note 1: LVP support for PIC18(L)F1XK50 legacy designs.

2: See Table 3 for location of all peripheral functions.

PIC16(L)F1459

FIGURE 3: 20-PIN PDIP, SOIC, SSOP DIAGRAM FOR PIC16(L)F1459

FIGURE 4: 20-PIN QFN DIAGRAM FOR PIC16(L)F1459

DS41639A-page 6 Preliminary 2012 Microchip Technology Inc.

TABLE 1: 14-PIN ALLOCATION TABLE (PIC16(L)F1454)

PIC16(L)F145X

I/O

14-Pin PDIP/SOIC/TSSOP

RA0 13 12 — — — — — D+ — — — IOC ICSPDAT

RA1 12 11 — — — — — D- — — — IOC ICSPCLK

RA2 — — — — — — — — — — — — —

RA3 4 3 — — — T1G

RA4 3 2 — — — SOSCO

RA5 2 1 — — — SOSCI

RC0 10 9 — — — — — — — — SCL

RC1 9 8 — — — — — — — — SDA

RC2 8 7 — — — — — — — — SDO

RC3 7 6 — — — — — — — PWM2

RC4 6 5 — — — — — — TK

RC5 5 4 — — — T0CKI — — RXDTPWM1 — — —

VDD 1 16 — — — — — — — — — — VDD

VSS 14 13 — — — — — — — — — — VSS

VUSB3V3 11 10 — — — — — VUSB3V3 — — — — —

Note 1: Default location for peripheral pin function. Alternate location can be selected using the APFCON register.

2: Alternate location for peripheral pin function selected by the APFCON register.

3: LVP support for PIC18(L)F1XK50 legacy designs.

ADC

16-Pin QFN

Reference

Comparator

T1G

T1CKI

Timer

(2)

(1)

CWG

— — — — SS

— — — — SDO

— — — PWM2

USB

CK

EUSART

PWM

(2)

(1)

— — — —

MSSP

(2)

(2)

— IOC CLKIN

SCK

SDI

(1)

(1)

SS

Interrupt

IOC MCLR

IOC CLKOUT

— ICSPDAT

INT ICSPCLK

— —

— CLKR

VPP

OSC2

CLKR

OSC1

Basic

(3)

(3)

(1)

(2)

2012 Microchip Technology Inc. Preliminary DS41639A-page 7

PIC16(L)F145X

TABLE 2: 14-PIN ALLOCATION TABLE (PIC16(L)F1455)

I/O

14-Pin PDIP/SOIC/TSSOP

RA0 13 12 — — — — — D+ — — — IOC ICSPDAT

RA1 12 11 — — — — — D- — — — IOC ICSPCLK

RA2 — — — — — — — — — — — — —

RA3 4 3 — — — T1G

RA4 3 2 AN3 — — SOSCO

RA5 2 1 — — — SOSCI

RC0 10 9 AN4 VREF+ C1IN+

RC1 9 8 AN5 — C1IN1-

RC2 8 7 AN6 DACOUT1 C1IN2-

RC3 7 6 AN7 DACOUT2 C1IN3-

RC4 6 5 — — C1OUT

RC5 5 4 — — — T0CKI CWG1A — RXDTPWM1 — — —

VDD 1 16 — — — — — — — — — — VDD

VSS 14 13 — — — — — — — — — — VSS

VUSB3V3 11 10 — — — — — VUSB3V3 — — — — —

Note 1: Default location for peripheral pin function. Alternate location can be selected using the APFCON register.

2: Alternate location for peripheral pin function selected by the APFCON register.

3: LVP support for PIC18(L)F1XK50 legacy designs.

ADC

16-Pin QFN

Reference

Comparator

C2IN+

C2IN1-

C2IN2-

C2IN3-

C2OUT

Timer

(2)

(1)

T1G

T1CKI

— — — — — SCL

— CWGFLT — — — SDA

— — — — — SDO

— — — — PWM2

— CWG1B — TK

CWG

— — — — SS

— — — — SDO

— — — PWM2

USB

CK

EUSART

PWM

(2)

(1)

— — — —

MSSP

(2)

(2)

— IOC CLKIN

SCK

SDI

(1)

(1)

SS

Interrupt

IOC MCLR

IOC CLKOUT

— ICSPDAT

INT ICSPCLK

— —

— CLKR

VPP

OSC2

CLKR

OSC1

Basic

(3)

(3)

(1)

(2)

DS41639A-page 8 Preliminary 2012 Microchip Technology Inc.

TABLE 3: 20-PIN ALLOCATION TABLE (PIC16(L)F1459)

PIC16(L)F145X

I/O

20-Pin PDIP/SOIC/SSOP

RA0 19 16 — — — — — D+ — — — IOC ICSPDAT

RA1 18 15 — — — — — D- — — — IOC ICSPCLK

RA2 — — — — — — — — — — — — —

RA3 4 1 — — — T1G

RA4 3 20 AN3 — — SOSCO

RA5 2 19 — — — SOSCI

RB4 13 10 AN10 — — — — — — — SDA

RB5 12 9 AN11 — — — — — RX

RB6 11 8 — — — — — — — — SCL

RB7 10 7 — — — — — — TX

RC0 16 13 AN4 VREF+ C1IN+

RC1 15 12 AN5 — C1IN1-

RC2 14 11 AN6 DACOUT1 C1IN2-

RC3 7 4 AN7 DACOUT2 C1IN3-

RC4 6 3 — — C1OUT

RC5 5 2 — — — T0CKI CWG1A

RC6 8 5 AN8 — — — — — — PWM2 SS

RC7 9 6 AN9 — — — — — — — SDO — —

VDD 1 18 — — — — — — — — — — VDD

VSS 20 17 — — — — — — — — — — VSS

VUSB3V3 17 14 — — — — — VUSB3V3 — — — — —

Note 1: Default location for peripheral pin function. Alternate location can be selected using the APFCON register.

2: Alternate location for peripheral pin function selected by the APFCON register.

3: LVP support for PIC18(L)F1XK50 legacy designs.

ADC

20-Pin QFN

Reference

Comparator

C2IN+

C2IN1-

C2IN2-

C2IN3-

C2OUT

Timer

(2)

(1)

T1G

T1CKI

— — — — — — — ICSPDAT

— CWGFLT — — — — INT ICSPCLK

— — — — — — — —

— ——— — — — CLKR

— CWG1B — — — — — —

CWG

— — — — SS

— — — — — IOC OSC2

— — — — — IOC OSC1

USB

EUSART

DX

CK

— PWM1 — — —

—

PWM

— — IOC —

— — IOC —

MSSP

(2)

SDI

SCK

(1)

Interrupt

IOC MCLR

VPP

CLKOUT

CLKR

CLKIN

IOC —

IOC —

— —

Basic

(3)

(3)

(1)

(2)

2012 Microchip Technology Inc. Preliminary DS41639A-page 9

PIC16(L)F145X

Table of Contents

1.0 Device Overview ........................................................................................................................................................................ 13

2.0 Enhanced Mid-Range CPU ........................................................................................................................................................ 21

3.0 Memory Organization ................................................................................................................................................................. 23

4.0 Device Configuration.................................................................................................................................................................. 51

5.0 Oscillator Module (With Fail-Safe Clock Monitor)....................................................................................................................... 57

6.0 Resets ........................................................................................................................................................................................ 79

7.0 Reference Clock Module ............................................................................................................................................................ 87

8.0 Interrupts .................................................................................................................................................................................... 91

9.0 Power-Down Mode (Sleep) ...................................................................................................................................................... 103

10.0 Watchdog Timer (WDT) ........................................................................................................................................................... 107

11.0 Flash Program Memory Control ............................................................................................................................................... 112

12.0 I/O Ports ................................................................................................................................................................................... 129

13.0 Interrupt-On-Change ................................................................................................................................................................ 143

14.0 Fixed Voltage Reference (FVR) (PIC16(L)F1455/9 only)......................................................................................................... 149

15.0 Temperature Indicator Module (PIC16(L)F1455/9 only)........................................................................................................... 151

16.0 Analog-to-Digital Converter (ADC) Module

(PIC16(L)F1455/9 only) ............................................................................................................................................................. 153

17.0 Digital-to-Analog Converter (DAC) Module

(PIC16(L)F1455/9 only) ............................................................................................................................................................. 169

18.0 Comparator Module

(PIC16(L)F1455/9 only) ............................................................................................................................................................. 173

19.0 Timer0 Module ......................................................................................................................................................................... 183

20.0 Timer1 Module with Gate Control............................................................................................................................................. 187

21.0 Timer2 Module ......................................................................................................................................................................... 199

22.0 Master Synchronous Serial Port (MSSP) Module .................................................................................................................... 203

23.0 Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) ............................................................... 257

24.0 Pulse Width Modulation (PWM) Module................................................................................................................................... 287

25.0 Complementary Waveform Generator (CWG) Module

(PIC16(L)F1455/9 only)293

26.0 Universal Serial Bus (USB) ...................................................................................................................................................... 309

27.0 In-Circuit Serial Programming™ (ICSP™) ............................................................................................................................... 337

28.0 Instruction Set Summary .......................................................................................................................................................... 339

29.0 Electrical Specifications............................................................................................................................................................ 353

30.0 DC and AC Characteristics Graphs and Charts ....................................................................................................................... 383

31.0 Development Support............................................................................................................................................................... 385

32.0 Packaging Information.............................................................................................................................................................. 389

Appendix A: Data Sheet Revision History .......................................................................................................................................... 407

Index .................................................................................................................................................................................................. 409

The Microchip Web Site..................................................................................................................................................................... 415

Customer Change Notification Service .............................................................................................................................................. 415

Customer Support .............................................................................................................................................................................. 415

Reader Response .............................................................................................................................................................................. 416

Product Identification System............................................................................................................................................................. 417

DS41639A-page 10 Preliminary 2012 Microchip Technology Inc.

PIC16(L)F145X

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at docerrors@microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150. We

welcome your feedback.

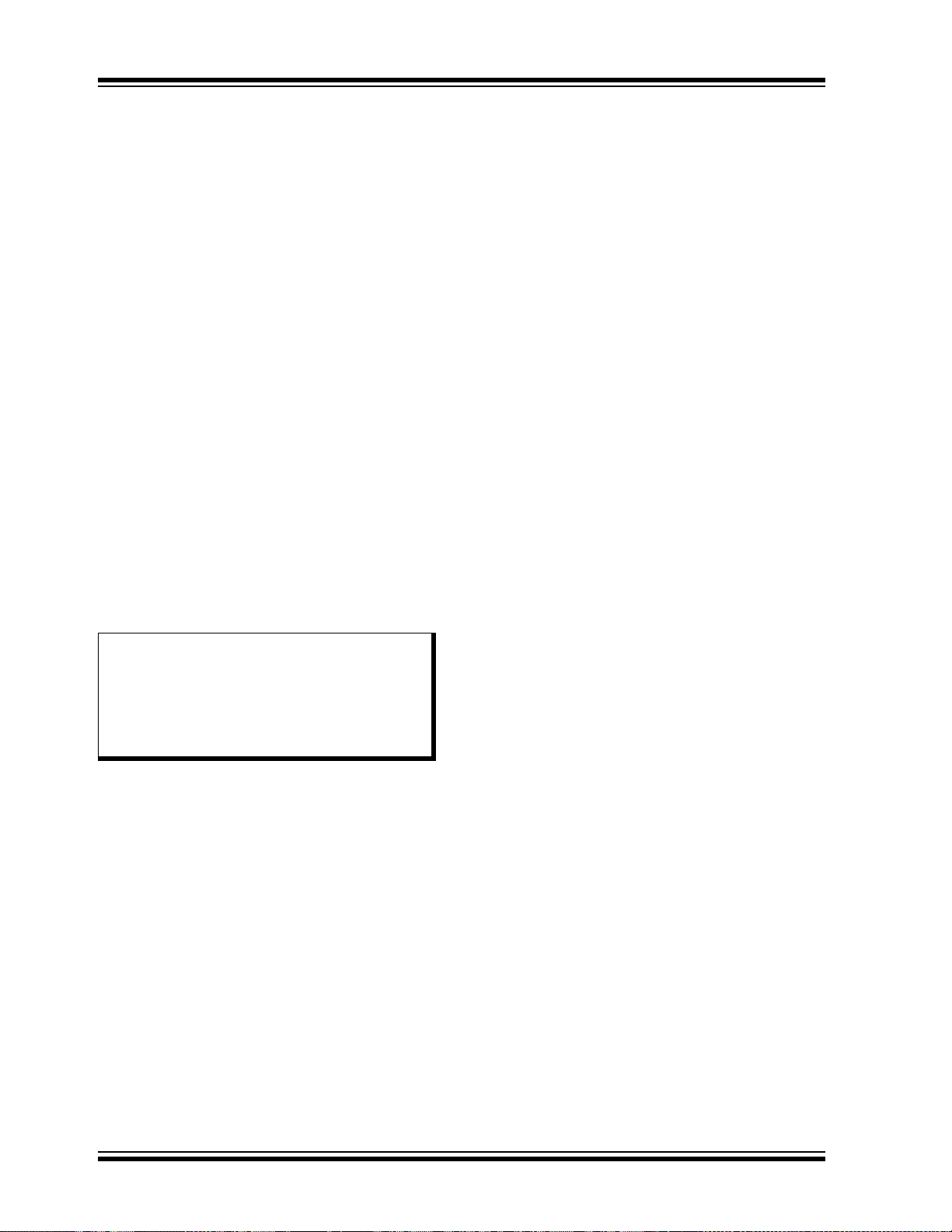

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

2012 Microchip Technology Inc. Preliminary DS41639A-page 11

PIC16(L)F145X

NOTES:

DS41639A-page 12 Preliminary 2012 Microchip Technology Inc.

1.0 DEVICE OVERVIEW

The PIC16(L)F1454/5/9 are described within this data

sheet. They are available in 14/20-pin packages.

Figure 1-1 shows a block diagram of the

PIC16(L)F1454/5/9 devices. Tables 1-2, 1-3 and 1-4

show the pinout descriptions.

Reference Ta bl e 1 -1 for peripherals available per

device.

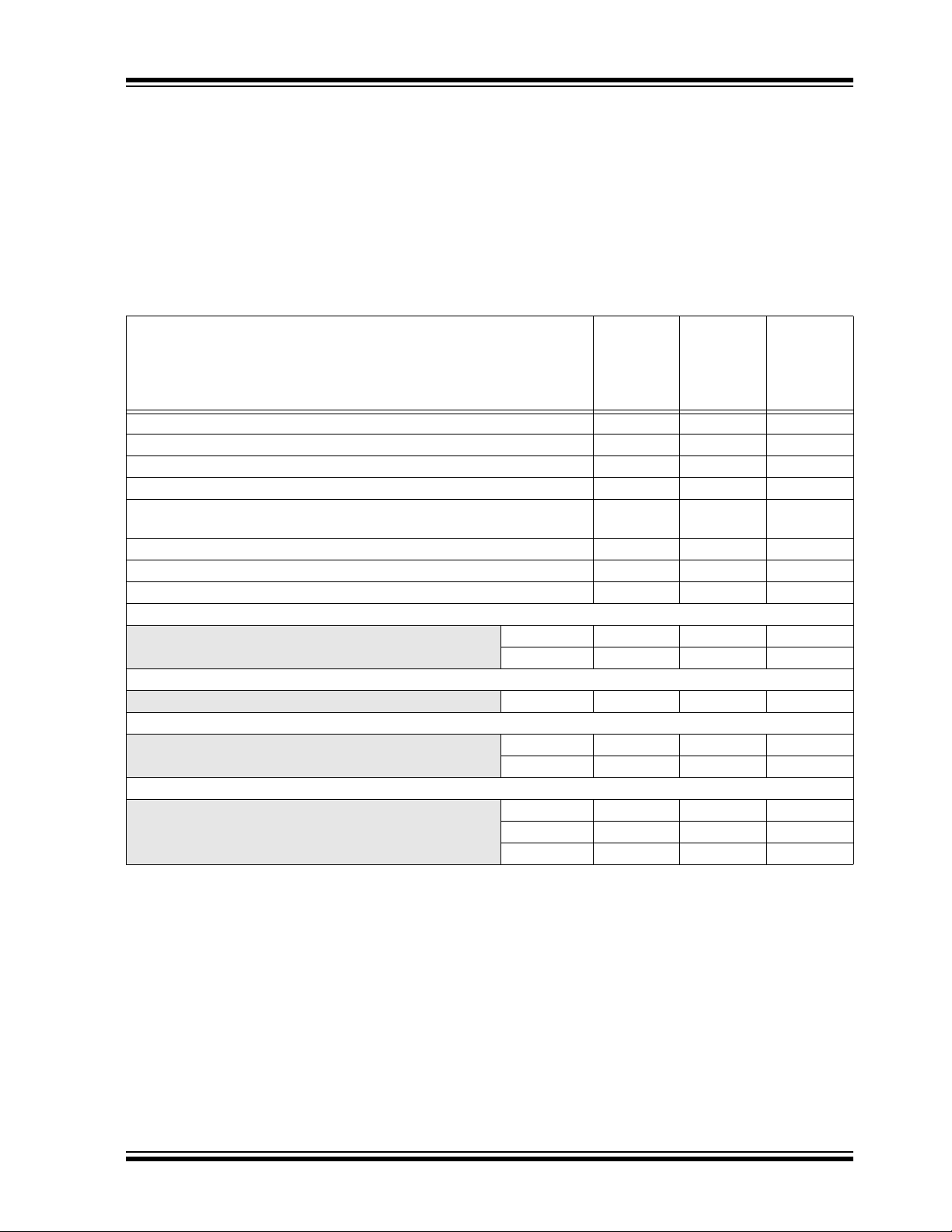

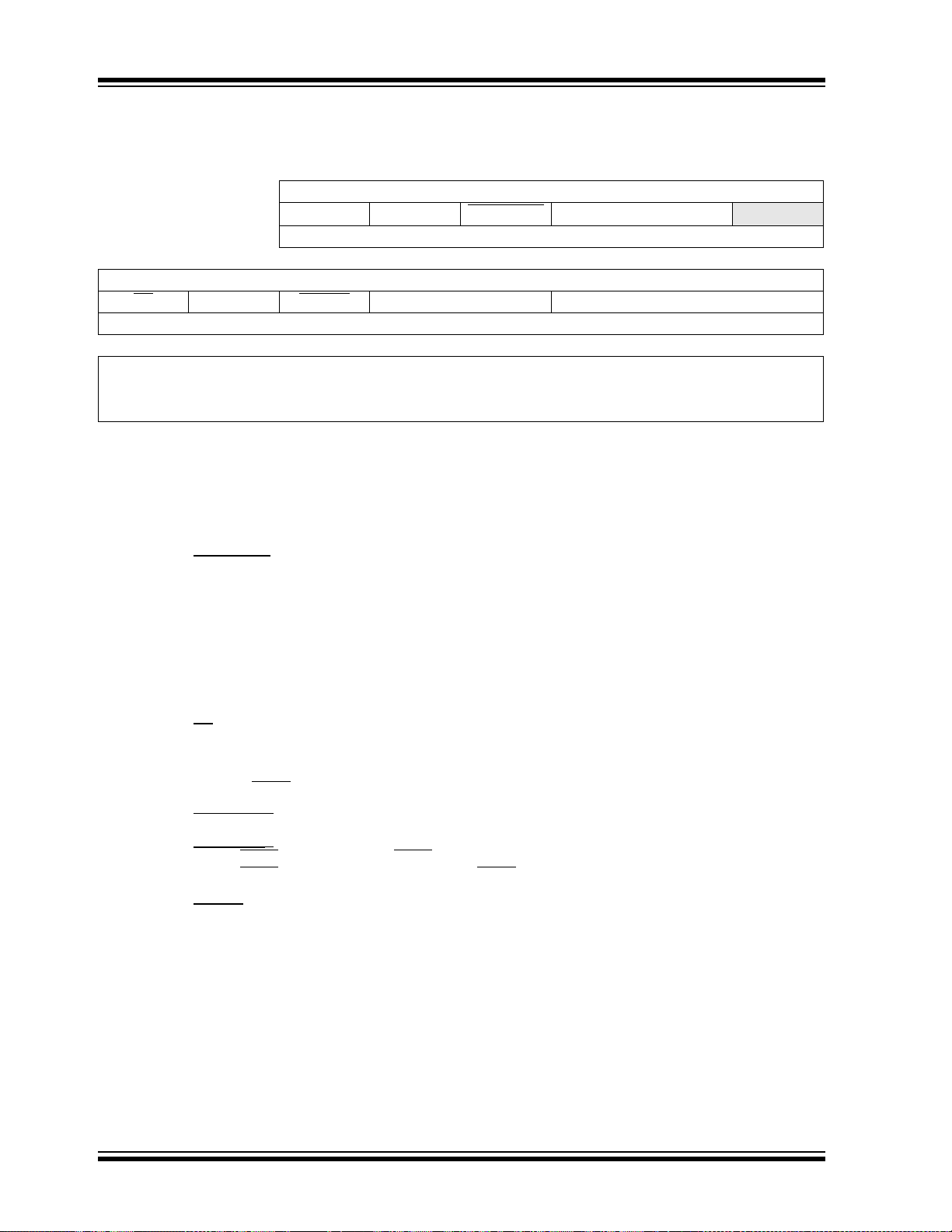

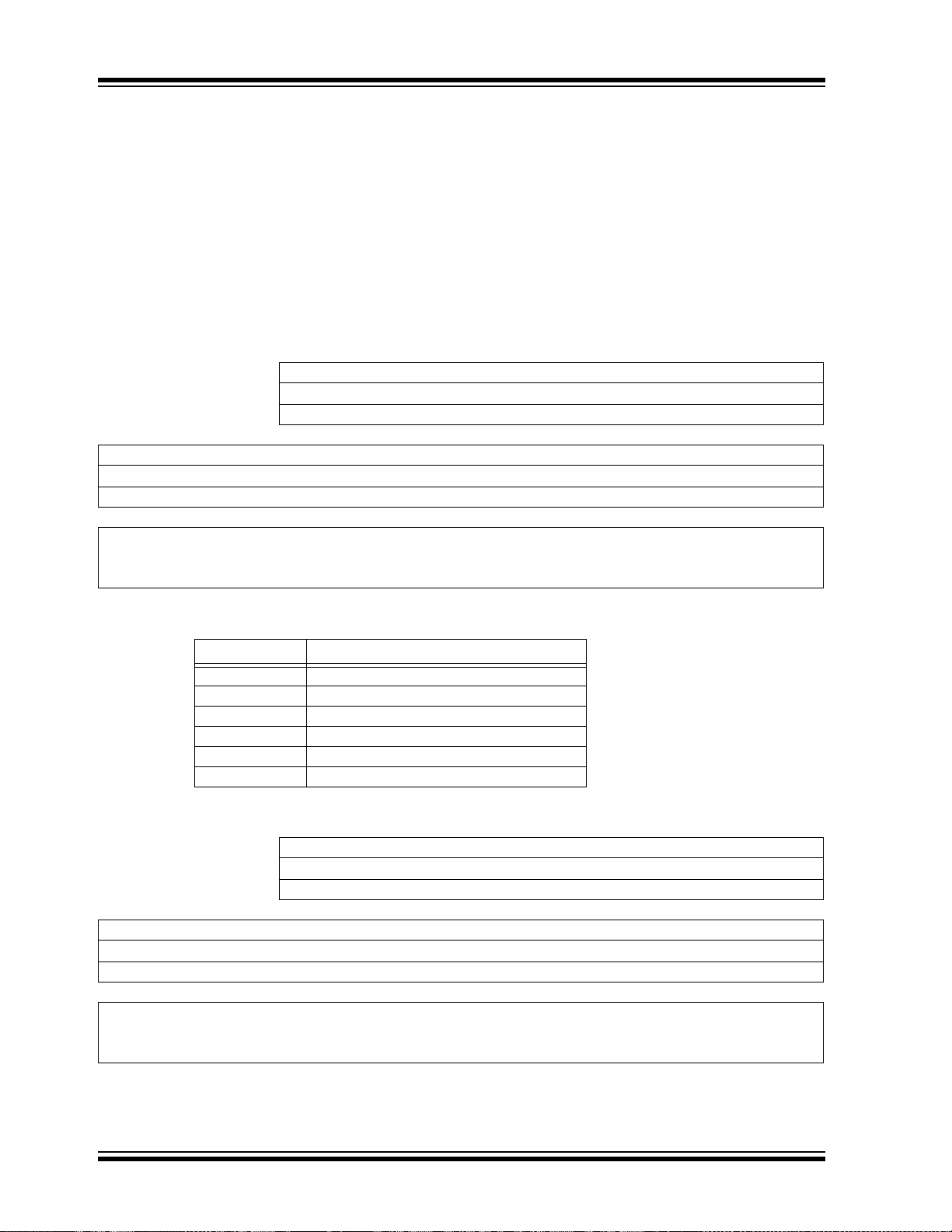

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

Peripheral

PIC16(L)F1454/5/9

PIC16F1454

PIC16LF1454

Analog-to-Digital Converter (ADC) ●●

Clock Reference ●●●

Complementary Wave Generator (CWG) ●●

Digital-to-Analog Converter (DAC) ●●

Enhanced Universal Synchronous/Asynchronous Receiver/Transmitter

(EUSART)

Fixed Voltage Reference (FVR) ●●

Temperature Indicator ●●

Universal Serial Bus (USB) ●●●

Comparators

C1 ●●

C2 ●●

Master Synchronous Serial Ports

MSSP1 ●●●

PWM Modules

PWM1 ●●●

PWM2 ●●●

Timers

Timer0 ●●●

Timer1 ●●●

Timer2 ●●●

●●●

PIC16F1455

PIC16LF1455

PIC16F1459

PIC16LF1459

2012 Microchip Technology Inc. Preliminary DS41639A-page 13

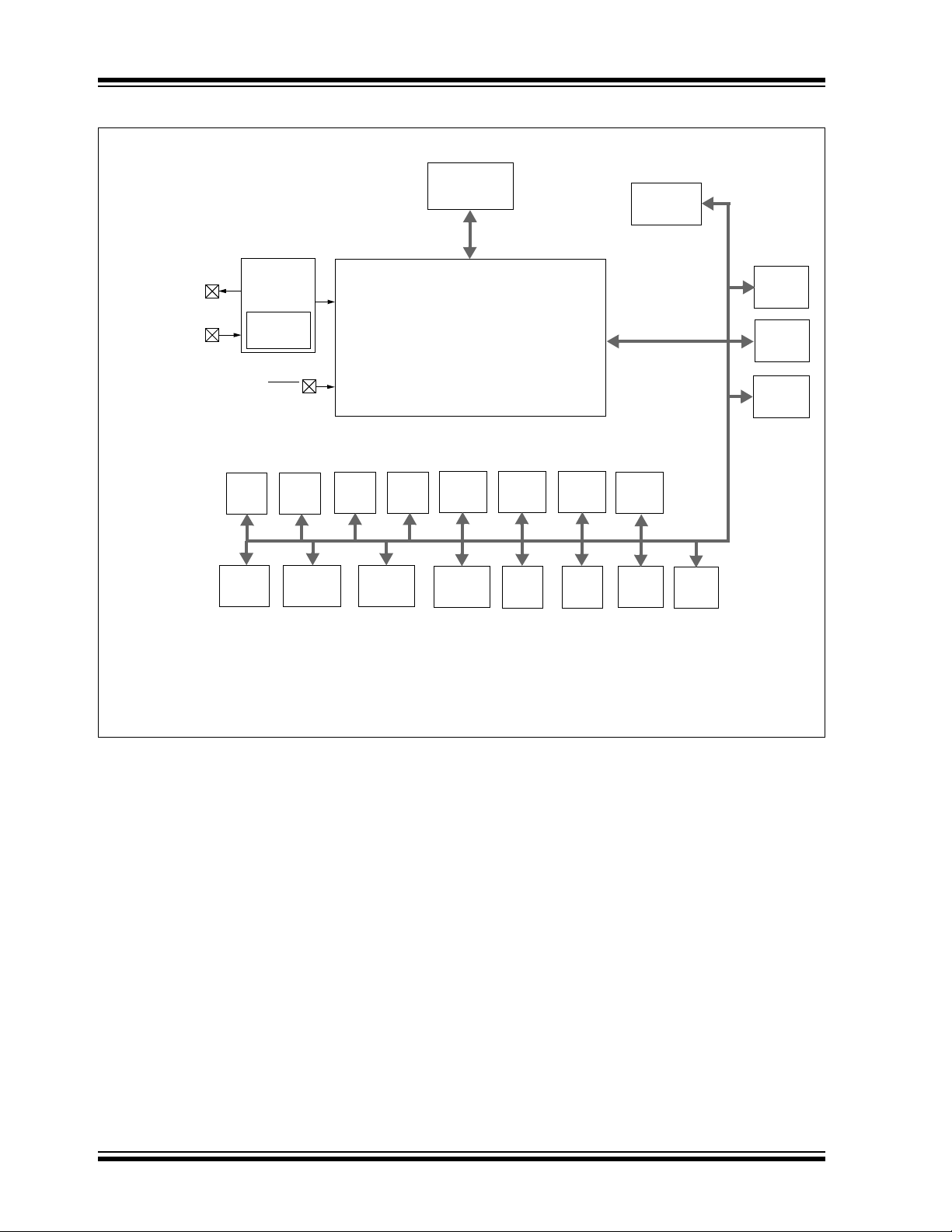

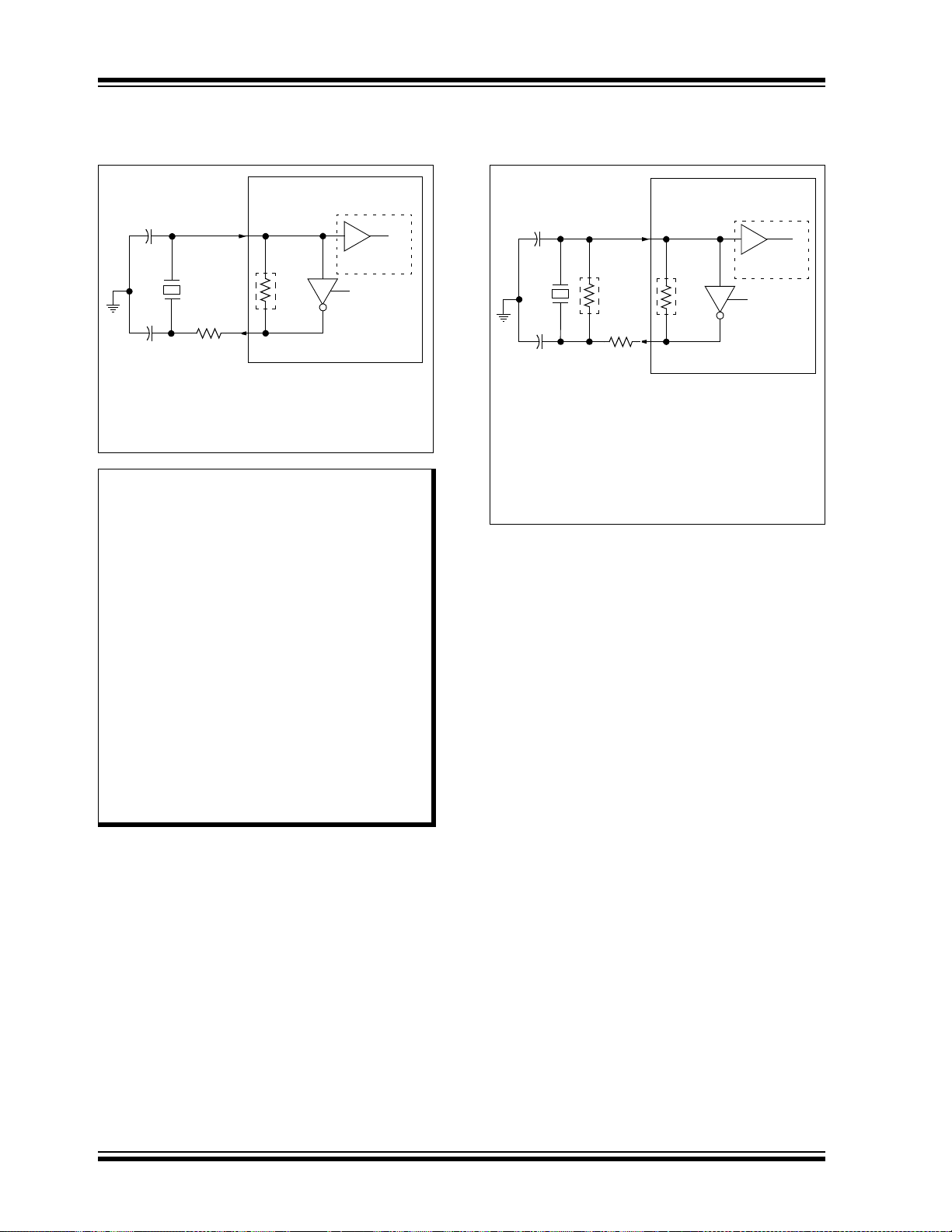

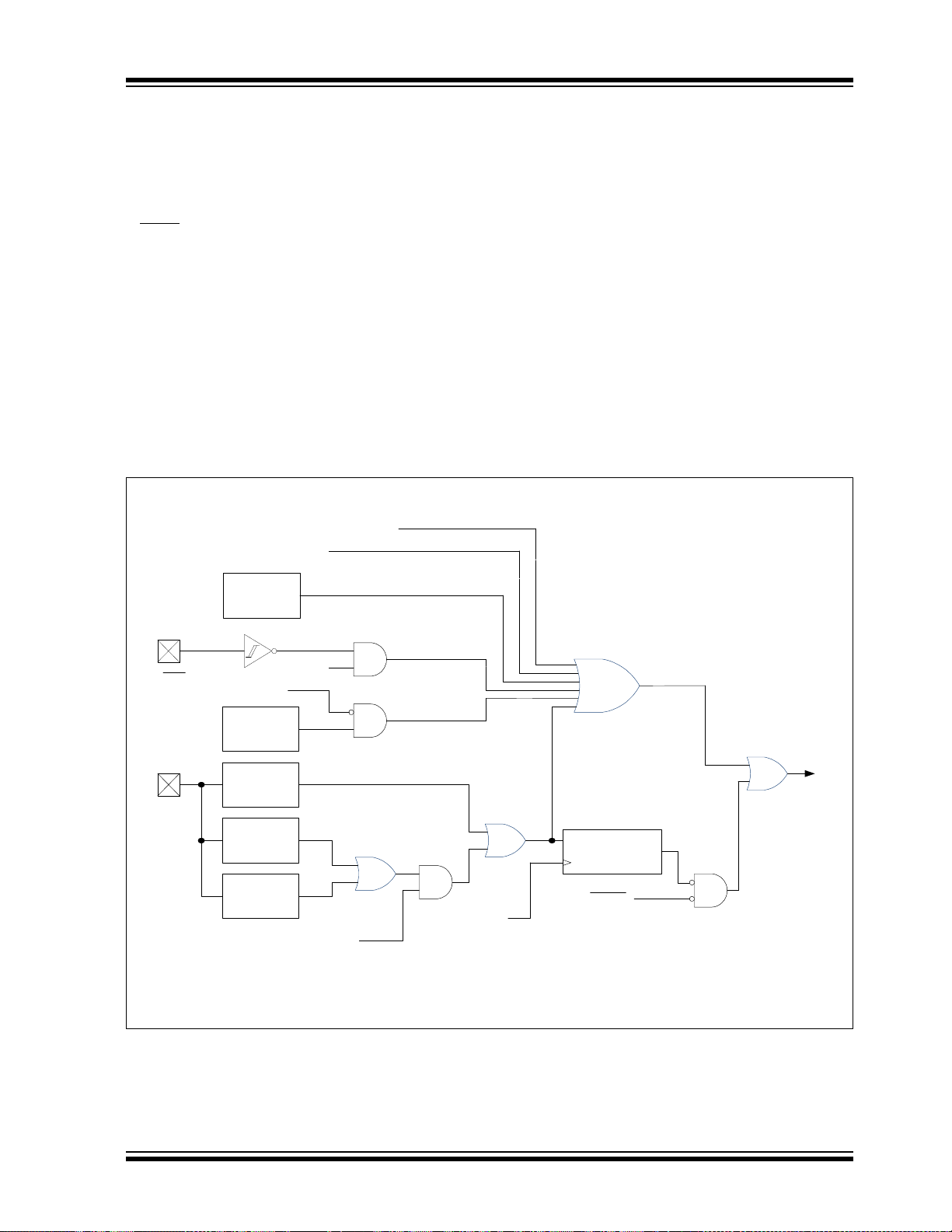

PIC16(L)F1454/5/9

PORTC

Note 1: PIC16(L)F1455/9 only.

2: PIC16(L)F1459 only.

CPU

Program

Flash Memory

RAM

Timi ng

Generation

INTRC

Oscillator

MCLR

(Figure 2-1)

Timer2Timer1Timer0

PWM1 PWM2

PORTA

CWG1

(1)

ADC

10-Bit

(1)

FVR

(1)

Te mp .

Indicator

(1)

OSC1/CLKIN

OSC2/CLKOUT

MSSP1

C2

(1)

C1

(1)

DAC

(1)

PORTB

(2)

EUSART

CLKRUSB

FIGURE 1-1: PIC16(L)F1454/5/9 BLOCK DIAGRAM

DS41639A-page 14 Preliminary 2012 Microchip Technology Inc.

PIC16(L)F1454/5/9

TABLE 1-2: PIC16(L)F1454 PINOUT DESCRIPTION

Input

Name Function

RA0/D+/ICSPDAT

(3)

RA0 TTL CMOS General purpose I/O.

D+ XTAL XTAL USB differential plus line.

ICSPDAT ST CMOS ICSP™ Data I/O.

RA1/D-/ICSPCLK

(3)

RA1 TTL CMOS General purpose I/O.

D- XTAL XTAL USB differential minus line.

ICSPCLK ST — ICSP Programming Clock.

(2)

RA3/V

PP/T1G

(2)

/SS

/MCLR RA3 TTL — General purpose input with IOC and WPU.

PP HV — Programming voltage.

V

T1G ST — Timer1 Gate input.

SS

MCLR

RA4/SOSCO/CLKOUT/

(1)

T1G

/SDO

(2)

/CLKR

(1)

/OSC2

RA4 TTL CMOS General purpose I/O.

SOSCO XTAL XTAL Secondary Oscillator Connection.

CLKOUT — CMOS F

T1G ST — Timer1 Gate input.

SDO — CMOS SPI data output.

CLKR — CMOS Clock reference output.

OSC2 XTAL XTAL Primary Oscillator connection.

RA5/CLKIN/SOSCI/T1CKI/

(2)

PWM2

/OSC1

RA5 TTL CMOS General purpose I/O.

CLKIN CMOS — External clock input (EC mode).

SOSCI XTAL XTAL Secondary Oscillator Connection.

T1CKI ST — Timer1 clock input.

PWM2 — CMOS PWM output.

OSC1 XTAL XTAL Primary Oscillator Connection.

RC0/SCL/SCK/ICSPDAT RC0 TTL CMOS General purpose I/O.

SCL I

SCK ST CMOS SPI clock.

ICSPDAT ST CMOS ICSP™ Data I/O.

RC1/SDA/SDI/INT/ICSPCLK RC1 TTL CMOS General purpose I/O.

SDA I

SDI CMOS — SPI data input.

INT ST — External input.

ICSPCLK ST — ICSP Programming Clock.

RC2/SDO

(1)

RC2 TTL CMOS General purpose I/O.

SDO — CMOS SPI data output.

RC3/PWM2

/SS

(1)

/CLKR

(2)

RC3 TTL CMOS General purpose I/O.

(1)

PWM2 — CMOS PWM output.

SS

CLKR — CMOS Clock reference output.

Legend: AN = Analog input or output CMOS= CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I

HV = High Voltage XTAL = Crystal levels

Note 1: Default location for peripheral pin function. Alternate location can be selected using the APFCON register.

2: Alternate location for peripheral pin function selected by the APFCON register.

3: LVP support for PIC18(L)F1XK50 legacy designs.

Typ e

Output

Typ e

Description

ST — Slave Select input.

ST — Master Clear with internal pull-up.

OSC/4 output.

2

CODI2C™ clock.

2

CODI2C data input/output.

ST — Slave Select input.

2

C™ = Schmitt Trigger input with I2C

2012 Microchip Technology Inc. Preliminary DS41639A-page 15

PIC16(L)F1454/5/9

TABLE 1-2: PIC16(L)F1454 PINOUT DESCRIPTION (CONTINUED)

Input

Name Function

RC4/TX/CK RC4 TTL CMOS General purpose I/O.

TX — CMOS USART asynchronous transmit.

CK ST CMOS USART synchronous clock.

RC5/T0CKI/RX/DT/PWM1 RC5 TTL CMOS General purpose I/O.

T0CKI ST — Timer0 clock input.

RX ST — USART asynchronous input.

DT ST CMOS USART synchronous data.

PWM1 — CMOS PWM output.

DD VDD Power — Positive supply.

V

SS VSS Power — Ground reference.

V

V

USB3V3 VUSB3V3 Power — Positive supply for USB transceiver.

Legend: AN = Analog input or output CMOS= CMOS compatible input or output OD = Open Drain

Note 1: Default location for peripheral pin function. Alternate location can be selected using the APFCON register.

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I

HV = High Voltage XTAL = Crystal levels

2: Alternate location for peripheral pin function selected by the APFCON register.

3: LVP support for PIC18(L)F1XK50 legacy designs.

Typ e

Output

Typ e

Description

2

C™ = Schmitt Trigger input with I2C

DS41639A-page 16 Preliminary 2012 Microchip Technology Inc.

PIC16(L)F1454/5/9

TABLE 1-3: PIC16(L)F1455 PINOUT DESCRIPTION

Input

Name Function

RA0/D+/ICSPDAT

(3)

RA0 TTL CMOS General purpose I/O.

D+ XTAL XTAL USB differential plus line.

ICSPDAT ST CMOS ICSP™ Data I/O.

RA1/D-/ICSPCLK

(3)

RA1 TTL CMOS General purpose I/O.

D- XTAL XTAL USB differential minus line.

ICSPCLK ST — ICSP Programming Clock.

(2)

RA3/V

PP/T1G

(2)

/SS

/MCLR RA3 TTL — General purpose input with IOC and WPU.

PP HV — Programming voltage.

V

T1G ST — Timer1 Gate input.

SS

MCLR

RA4/AN3/SOSCO/CLKOUT/

(1)

T1G

/SDO

(2)

/CLKR

(1)

/OSC2

RA4 TTL CMOS General purpose I/O.

AN3 AN — A/D Channel input.

SOSCO XTAL XTAL Secondary Oscillator Connection.

CLKOUT — CMOS F

T1G ST — Timer1 Gate input.

SDO — CMOS SPI data output.

CLKR — CMOS Clock reference output.

OSC2 XTAL XTAL Primary Oscillator connection.

RA5/CLKIN/SOSCI/T1CKI/

(2)

PWM2

/OSC1

RA5 TTL CMOS General purpose I/O.

CLKIN CMOS — External clock input (EC mode).

SOSCI XTAL XTAL Secondary Oscillator Connection.

T1CKI ST — Timer1 clock input.

PWM2 — CMOS PWM output.

OSC1 XTAL XTAL Primary Oscillator Connection.

RC0/AN4/V

REF+/C1IN+/C2IN+/

SCL/SCK/ICSPDAT

RC0 TTL CMOS General purpose I/O.

AN4 AN — A/D Channel input.

REF+ AN — Positive Voltage Reference input.

V

C1IN+ AN — Comparator positive input.

C2IN+ AN — Comparator positive input.

SCL I

SCK ST CMOS SPI clock.

ICSPDAT ST CMOS ICSP™ Data I/O.

Legend: AN = Analog input or output CMOS= CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I

HV = High Voltage XTAL = Crystal levels

Note 1: Default location for peripheral pin function. Alternate location can be selected using the APFCON register.

2: Alternate location for peripheral pin function selected by the APFCON register.

3: LVP support for PIC18(L)F1XK50 legacy designs.

Typ e

Output

Typ e

Description

ST — Slave Select input.

ST — Master Clear with internal pull-up.

OSC/4 output.

2

CODI2C™ clock.

2

C™ = Schmitt Trigger input with I2C

2012 Microchip Technology Inc. Preliminary DS41639A-page 17

PIC16(L)F1454/5/9

TABLE 1-3: PIC16(L)F1455 PINOUT DESCRIPTION (CONTINUED)

Input

Name Function

RC1/AN5/C1IN1-/

C2IN1-/CWGFLT

SDI/INT/ICSPCLK

RC2/AN6/DACOUT1/

C1IN2-/C2IN2-/SDO

RC3/AN7/DACOUT2/

C1IN3-/C2IN3-/PWM2

(1)

/CLKR

SS

RC4/C1OUT/C2OUT/

CWG1B/TX/CK

RC5/T0CKI/CWG1A/RX/DT/

PWM1

DD VDD Power — Positive supply.

V

SS VSS Power — Ground reference.

V

V

USB3V3 VUSB3V3 Power — Positive supply for USB transceiver.

Legend: AN = Analog input or output CMOS= CMOS compatible input or output OD = Open Drain

Note 1: Default location for peripheral pin function. Alternate location can be selected using the APFCON register.

2: Alternate location for peripheral pin function selected by the APFCON register.

3: LVP support for PIC18(L)F1XK50 legacy designs.

/SDA/

(1)

(1)

(2)

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I

HV = High Voltage XTAL = Crystal levels

/

RC1 TTL CMOS General purpose I/O.

AN5 AN — A/D Channel input.

C1IN1- AN — Comparator negative input.

C2IN1- AN — Comparator negative input.

CWGFLT

SDA I

SDI CMOS — SPI data input.

INT ST — External input.

ICSPCLK ST — ICSP™ Programming Clock.

RC2 TTL CMOS General purpose I/O.

AN6 AN — A/D Channel input.

DACOUT1 — AN Digital-to-Analog Converter output.

C1IN2- AN — Comparator negative input.

C2IN2- AN — Comparator negative input.

SDO — CMOS SPI data output.

RC3 TTL CMOS General purpose I/O.

AN7 AN — A/D Channel input.

DACOUT2 — AN Digital-to-Analog Converter output.

C1IN3- AN — Comparator negative input.

C2IN3- AN — Comparator negative input.

PWM2 — CMOS PWM output.

CLC2IN0 ST — Configurable Logic Cell source input.

CLKR — CMOS Clock reference output.

RC4 TTL CMOS General purpose I/O.

C1OUT — CMOS Comparator output.

C2OUT — CMOS Comparator output.

CWG1B — CMOS CWG complementary output.

TX — CMOS USART asynchronous transmit.

CK ST CMOS USART synchronous clock.

RC5 TTL CMOS General purpose I/O.

T0CKI ST — Timer0 clock input.

CWG1A — CMOS CWG complementary output.

RX ST — USART asynchronous input.

DT ST CMOS USART synchronous data.

PWM1 — CMOS PWM output.

Output

Typ e

Typ e

ST — Complementary Waveform Generator Fault input.

2

CODI2C™ data input/output.

Description

2

C™ = Schmitt Trigger input with I2C

DS41639A-page 18 Preliminary 2012 Microchip Technology Inc.

PIC16(L)F1454/5/9

TABLE 1-4: PIC16(L)F1459 PINOUT DESCRIPTION

Input

Name Function

RA0/D+/ICSPDAT

(3)

RA0 TTL CMOS General purpose I/O.

D+ XTAL XTAL USB differential plus line.

ICSPDAT ST CMOS ICSP™ Data I/O.

RA1/D-/ICSPCLK

(3)

RA1 TTL CMOS General purpose I/O.

D- XTAL XTAL USB differential minus line.

ICSPCLK ST — ICSP Programming Clock.

(2)

RA3/V

PP/T1G

(2)

/SS

/MCLR RA3 TTL — General purpose input with IOC and WPU.

PP HV — Programming voltage.

V

T1G ST — Timer1 Gate input.

SS

MCLR

RA4/AN3/SOSCO/CLKOUT/

T1G

(1)

/CLKR

(1)

/OSC2

RA4 TTL CMOS General purpose I/O.

AN3 AN — A/D Channel input.

SOSCO XTAL XTAL Secondary Oscillator Connection.

CLKOUT — CMOS F

T1G ST — Timer1 Gate input.

CLKR — CMOS Clock reference output.

OSC2 XTAL XTAL Primary Oscillator connection.

RA5/CLKIN/SOSCI/T1CKI/

OSC1

RA5 TTL CMOS General purpose I/O.

CLKIN CMOS — External clock input (EC mode).

SOSCI XTAL XTAL Secondary Oscillator Connection.

T1CKI ST — Timer1 clock input.

OSC1 XTAL XTAL Primary Oscillator Connection.

RB4/AN10/SDA/SDI RB4 TTL CMOS General purpose I/O.

AN10 AN — A/D Channel input.

SDA I

SDI CMOS — SPI data input.

RB5/AN11/RX/DT RB5 TTL CMOS General purpose I/O.

AN11 AN — A/D Channel input.

RX ST — USART asynchronous input.

DT ST CMOS USART synchronous data.

RB6/SCL/SCK RB6 TTL CMOS General purpose I/O.

SCL I

SCK ST CMOS SPI clock.

RB7/TX/CK RB7 TTL CMOS General purpose I/O.

TX — CMOS USART asynchronous transmit.

CK ST CMOS USART synchronous clock.

Legend: AN = Analog input or output CMOS= CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I

HV = High Voltage XTAL = Crystal levels

Note 1: Default location for peripheral pin function. Alternate location can be selected using the APFCON register.

2: Alternate location for peripheral pin function selected by the APFCON register.

3: LVP support for PIC18(L)F1XK50 legacy designs.

Typ e

Output

Typ e

Description

ST — Slave Select input.

ST — Master Clear with internal pull-up.

OSC/4 output.

2

CODI2C data input/output.

2

CODI2C™ clock.

2

C™ = Schmitt Trigger input with I2C

2012 Microchip Technology Inc. Preliminary DS41639A-page 19

PIC16(L)F1454/5/9

TABLE 1-4: PIC16(L)F1459 PINOUT DESCRIPTION (CONTINUED)

Input

Name Function

RC0/AN4/V

ICSPDAT

RC1/AN5/C1IN1-/C2IN1-/

CWGFLT

RC2/AN6/DACOUT1/

C1IN2-/C2IN2-

RC3/AN7/DACOUT2/

C1IN3-/C2IN3-/CLKR

RC4/C1OUT/C2OUT/

CWG1B

RC5/T0CKI/CWG1A/PWM1 RC5 TTL CMOS General purpose I/O.

RC6/AN8/SS

RC7/AN9/SDO RC7 TTL CMOS General purpose I/O.

DD VDD Power — Positive supply.

V

SS VSS Power — Ground reference.

V

USB3V3 VUSB3V3 Power — Positive supply for USB transceiver.

V

Legend: AN = Analog input or output CMOS= CMOS compatible input or output OD = Open Drain

Note 1: Default location for peripheral pin function. Alternate location can be selected using the APFCON register.

REF+/C1IN+/C2IN+/

/INT/ICSPCLK

(2)

(1)

/PWM2 RC6 TTL CMOS General purpose I/O.

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I

HV = High Voltage XTAL = Crystal levels

2: Alternate location for peripheral pin function selected by the APFCON register.

3: LVP support for PIC18(L)F1XK50 legacy designs.

RC0 TTL CMOS General purpose I/O.

AN4 AN — A/D Channel input.

REF+ AN — Positive Voltage Reference input.

V

C1IN+ AN — Comparator positive input.

C2IN+ AN — Comparator positive input.

ICSPDAT ST CMOS ICSP™ Data I/O.

RC1 TTL CMOS General purpose I/O.

AN5 AN — A/D Channel input.

C1IN1- AN — Comparator negative input.

C2IN1- AN — Comparator negative input.

CWGFLT

INT ST — External input.

ICSPCLK ST — ICSP Programming Clock.

RC2 TTL CMOS General purpose I/O.

AN6 AN — A/D Channel input.

DACOUT1 — AN Digital-to-Analog Converter output.

C1IN2- AN — Comparator negative input.

C2IN2- AN — Comparator negative input.

RC3 TTL CMOS General purpose I/O.

AN7 AN — A/D Channel input.

DACOUT2 — AN Digital-to-Analog Converter output.

C1IN3- AN — Comparator negative input.

C2IN3- AN — Comparator negative input.

CLKR — CMOS Clock reference output.

RC4 TTL CMOS General purpose I/O.

C1OUT — CMOS Comparator output.

C2OUT — CMOS Comparator output.

CWG1B — CMOS CWG complementary output.

T0CKI ST — Timer0 clock input.

CWG1A — CMOS CWG complementary output.

PWM1 — CMOS PWM output.

AN8 AN — A/D Channel input.

SS

PWM2 — CMOS PWM output.

AN9 AN — A/D Channel input.

SDO — CMOS SPI data output.

Output

Typ e

Typ e

ST — Complementary Waveform Generator Fault input.

ST — Slave Select input.

Description

2

C™ = Schmitt Trigger input with I2C

DS41639A-page 20 Preliminary 2012 Microchip Technology Inc.

PIC16(L)F1454/5/9

Data Bus

8

14

Program

Bus

Instruction reg

Program Counter

8 Level Stack

(13-bit)

Direct Addr

7

12

Addr MUX

FSR reg

STATUS reg

MUX

ALU

Instruction

Decode &

Control

Timing

Generation

OSC1/CLKIN

OSC2/CLKOUT

8

8

12

3

Internal

Oscillator

Block

Configuration

Data Bus

8

14

Program

Bus

Instruction reg

Program Counter

8 Level Stack

(13-bit)

Direct Addr

7

Addr MUX

FSR reg

STATUS reg

MUX

ALU

W Reg

Instruction

Decode &

Control

Timing

Generation

8

8

3

Internal

Oscillator

Block

Configuration

15

Data Bus

8

14

Program

Bus

Instruction Reg

Program Counter

16-Level Stack

(15-bit)

Direct Addr

7

RAM Addr

Addr MUX

Indirect

Addr

FSR0 Reg

STATUS Reg

MUX

ALU

Instruction

Decode and

Control

Timing

Generation

8

8

3

Internal

Oscillator

Block

Configuration

Flash

Program

Memory

RAM

FSR regFSR reg

FSR1 Reg

15

15

MUX

15

Program Memory

Read (PMR)

12

FSR regFSR reg

BSR Reg

5

Power-up

Timer

Power-on

Reset

Watchdog

Timer

V

DD

Brown-out

Reset

VSSVDD VSSVDD VSS

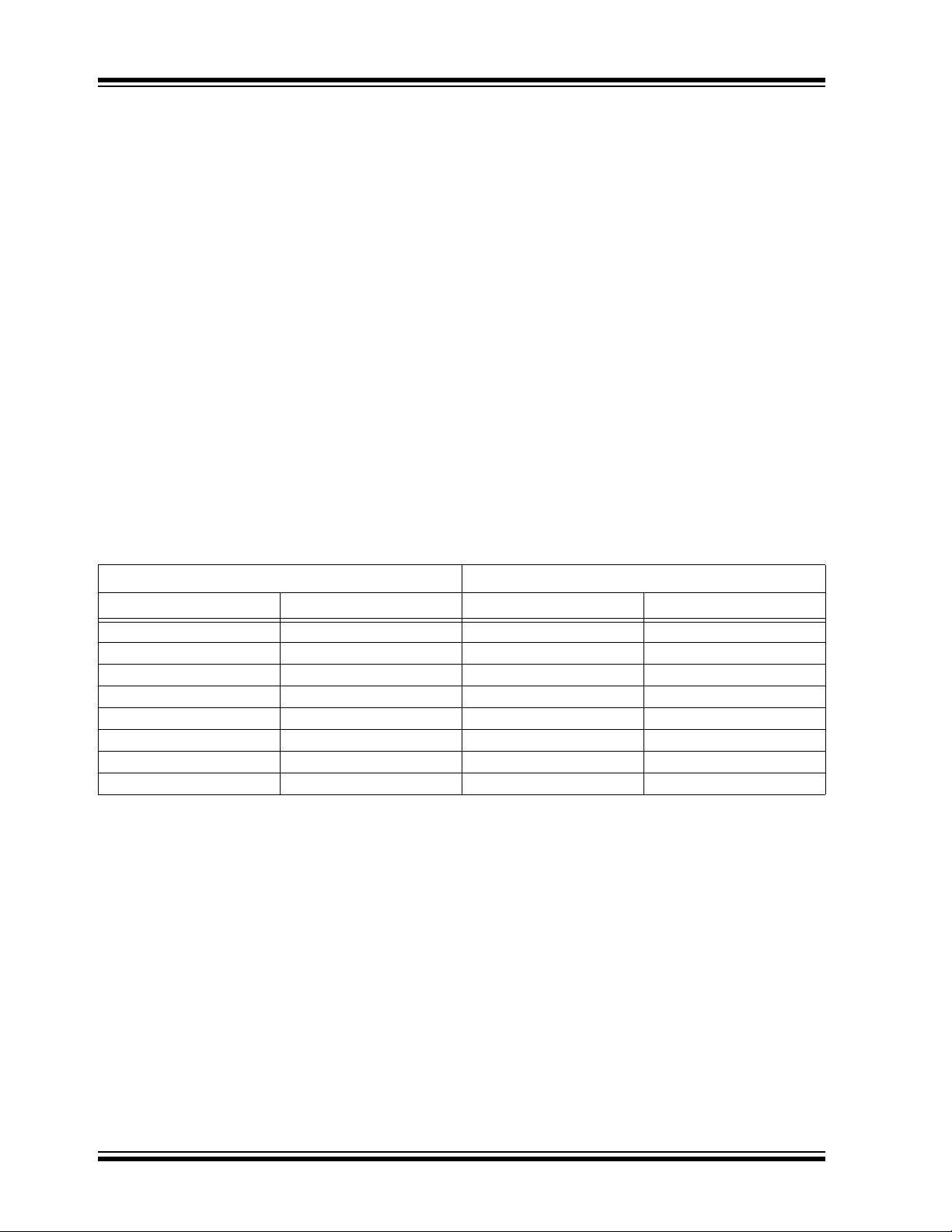

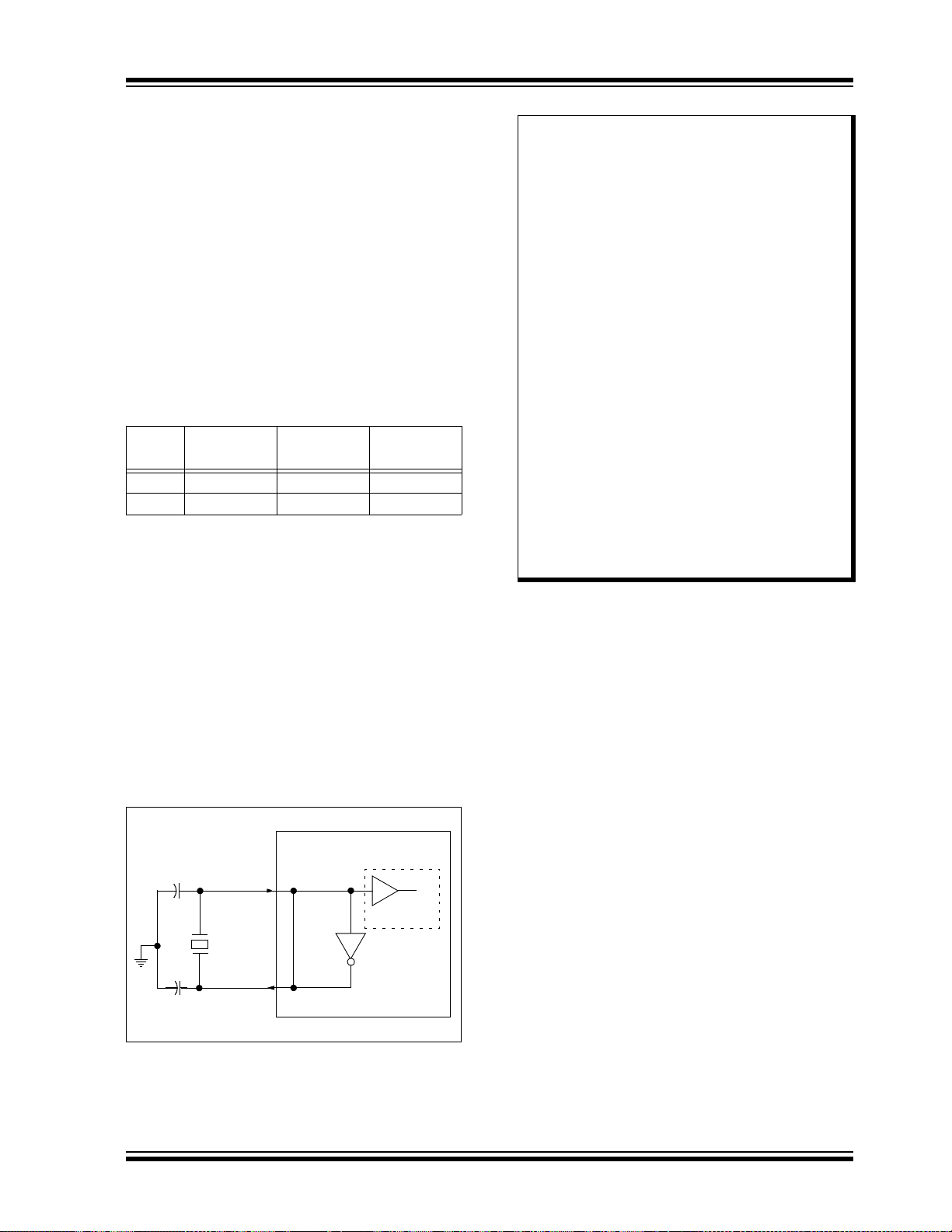

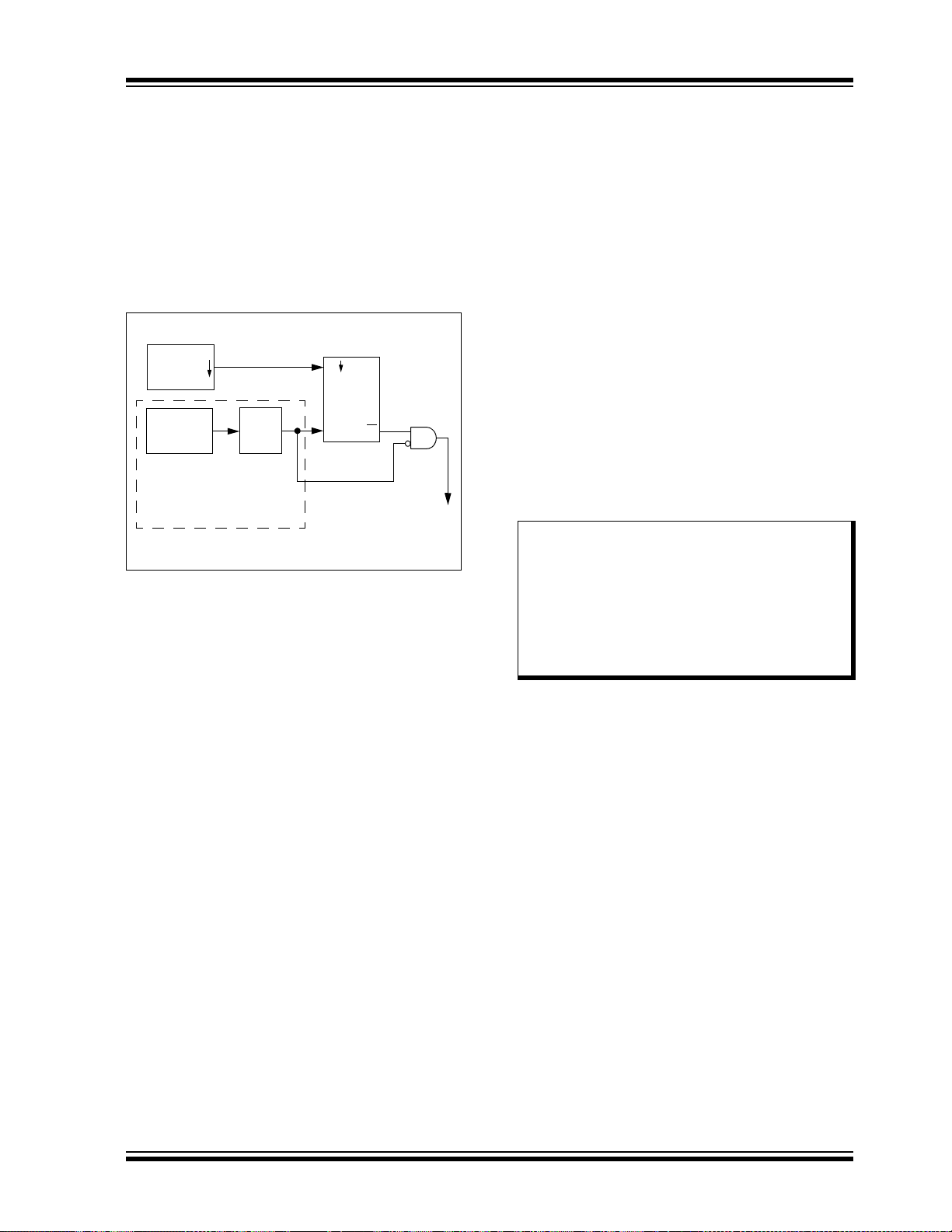

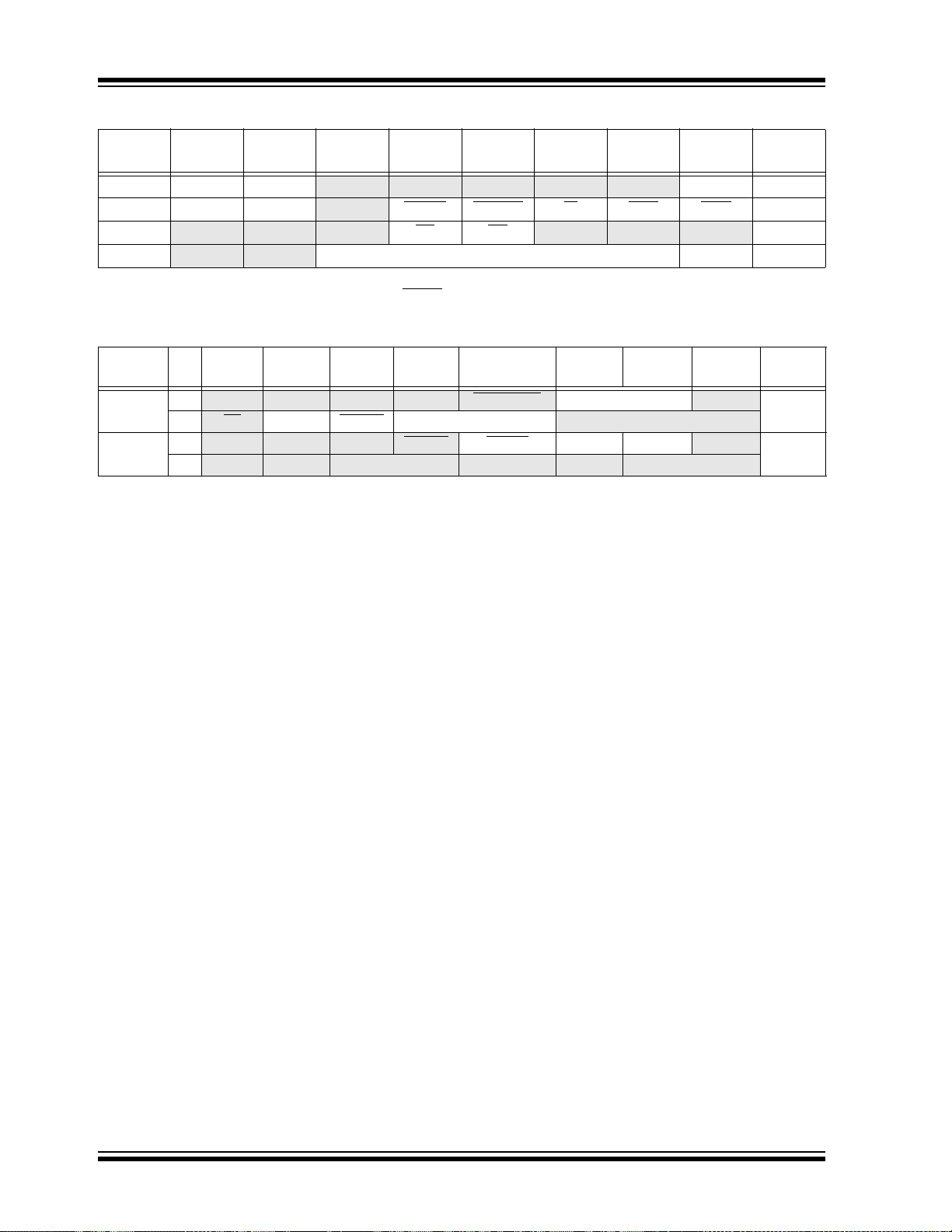

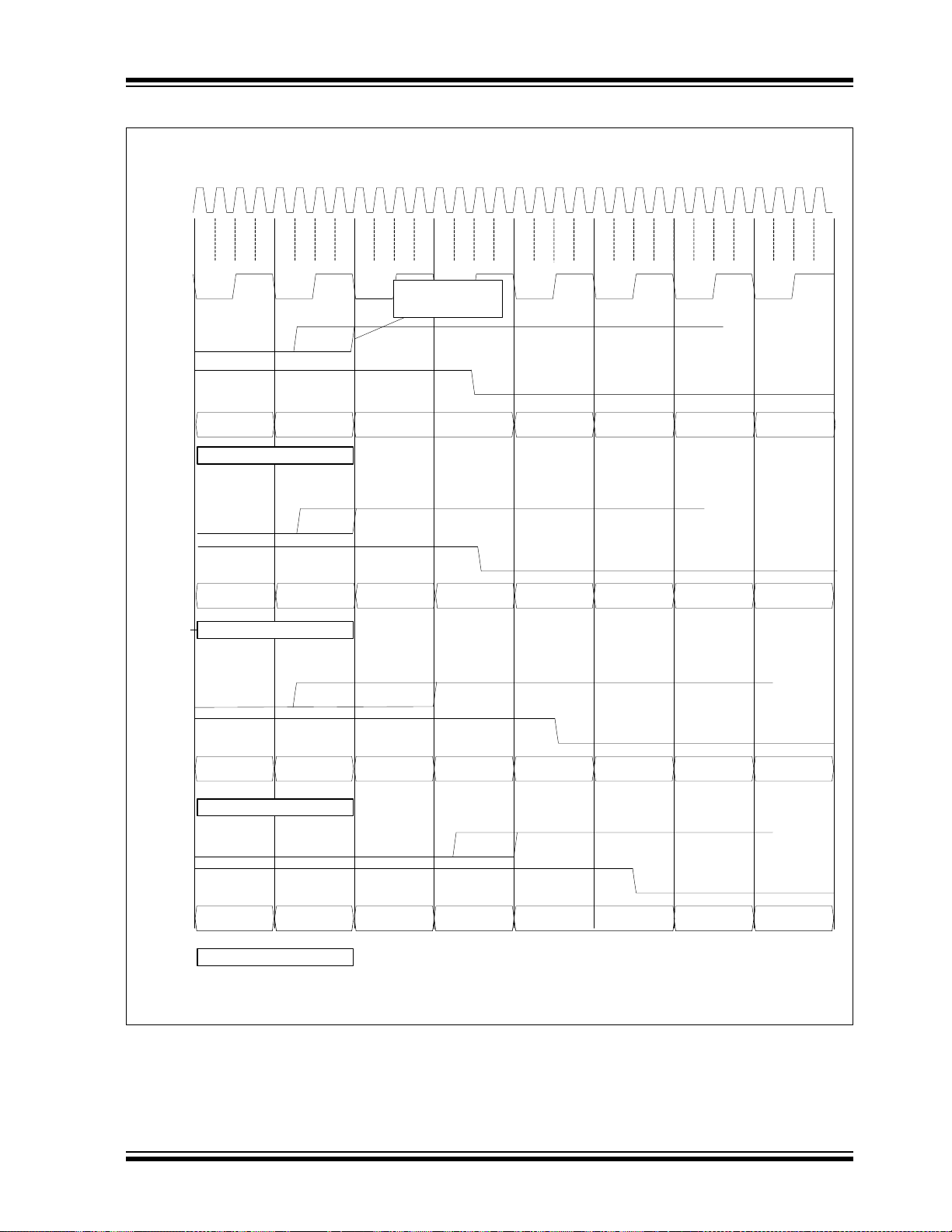

2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range

8-bit CPU core. The CPU has 49 instructions. Interrupt

capability includes automatic context saving. The

hardware stack is 16 levels deep and has Overflow and

Underflow Reset capability. Direct, Indirect, and

FIGURE 2-1: CORE BLOCK DIAGRAM

Relative Addressing modes are available. Two File

Select Registers (FSRs) provide the ability to read

program and data memory.

• Automatic Interrupt Context Saving

• 16-level Stack with Overflow and Underflow

• File Select Registers

• Instruction Set

2012 Microchip Technology Inc. Preliminary DS41639A-page 21

PIC16(L)F1454/5/9

2.1 Automatic Interrupt Context

Saving

During interrupts, certain registers are automatically

saved in shadow registers and restored when returning

from the interrupt. This saves stack space and user

code. See Section 8.5 “Automatic Context Saving”,

for more information.

2.2 16-Level Stack with Overflow and

Underflow

These devices have an external stack memory 15 bits

wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF)

in the PCON register, and if enabled will cause a software Reset. See section Section 3.5 “Stack” for more

details.

2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs

can access all file registers and program memory,

which allows one Data Pointer for all memory. When an

FSR points to program memory, there is one additional

instruction cycle in instructions using INDF to allow the

data to be fetched. General purpose memory can now

also be addressed linearly, providing the ability to

access contiguous data larger than 80 bytes. There are

also new instructions to support the FSRs. See

Section 3.6 “Indirect Addressing” for more details.

2.4 Instruction Set

There are 49 instructions for the enhanced mid-range

CPU to support the features of the CPU. See

Section 28.0 “Instruction Set Summary” for more

details.

DS41639A-page 22 Preliminary 2012 Microchip Technology Inc.

PIC16(L)F1454/5/9

3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

• Program Memory

- Configuration Words

- Device ID

-User ID

- Flash Program Memory

• Data Memory

- Core Registers

- Special Function Registers

- Dual-Port General Purpose RAM

- General Purpose RAM

- Common RAM

The following features are associated with access and

control of program memory and data memory:

• PCL and PCLATH

•Stack

• Indirect Addressing

3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program

counter capable of addressing a 32K x 14 program

memory space. Table 3-1 shows the memory sizes

implemented. Accessing a location above these

boundaries will cause a wrap-around within the

implemented memory space. The Reset vector is at

0000h and the interrupt vector is at 0004h (See

Figure 3-1).

TABLE 3-1: DEVICE SIZES AND ADDRESSES

Device

PIC16F1454

PIC16LF1454

PIC16F1455

PIC16LF1455

PIC16F1459

PIC16LF1459

Note 1: High-endurance Flash applies to low byte of each address in the range.

Program Memory

Space (Words)

8,192 1FFFh 1F80h-1FFFh

8,192 1FFFh 1F80h-1FFFh

8,192 1FFFh 1F80h-1FFFh

Last Program Memory

Address

High-Endurance Flash

Memory Address Range

(1)

2012 Microchip Technology Inc. Preliminary DS41639A-page 23

PIC16(L)F1454/5/9

PC<14:0>

15

0000h

0004h

Stack Level 0

Stack Level 15

Reset Vector

Interrupt Vector

Stack Level 1

0005h

On-chip

Program

Memory

Page 0

07FFh

Rollover to Page 0

0800h

0FFFh

1000h

7FFFh

Page 1

Rollover to Page 3

Page 2

Page 3

17FFh

1800h

1FFFh

2000h

CALL, CALLW

RETURN, RETLW

Interrupt, RETFIE

constants

BRW ;Add Index in W to

;program counter to

;select data

RETLW DATA0 ;Index0 data

RETLW DATA1 ;Index1 data

RETLW DATA2

RETLW DATA3

my_function

;… LOTS OF CODE…

MOVLW DATA_INDEX

call constants

;… THE CONSTANT IS IN W

FIGURE 3-1: PROGRAM MEMORY MAP

AND STACK FOR

PIC16(L)F1454/5/9

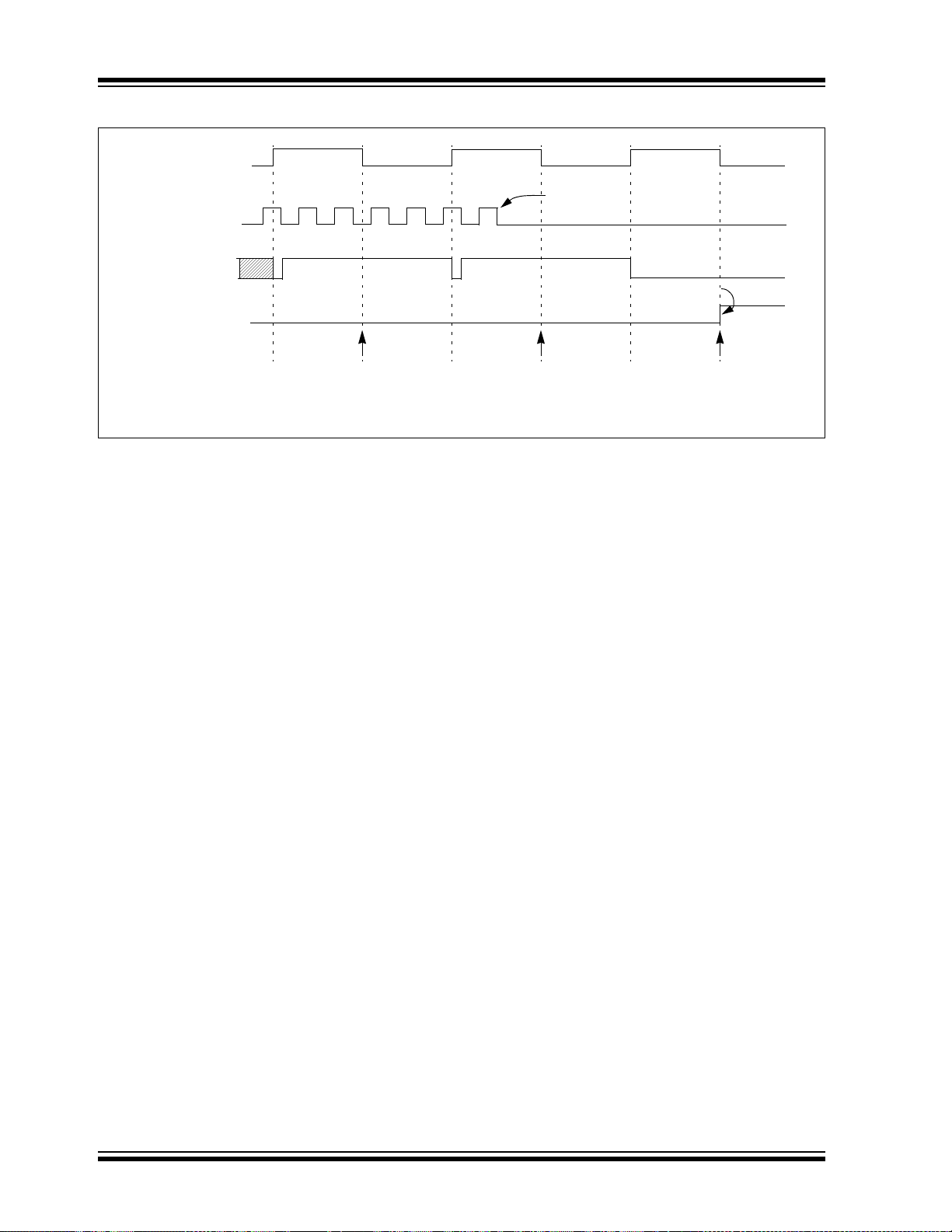

3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of

RETLW instructions. The second method is to set an

FSR to point to the program memory.

3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access

to tables of constants. The recommended way to create

such a table is shown in Example 3-1.

EXAMPLE 3-1: RETLW INSTRUCTION

The BRW instruction makes this type of table very simple to implement. If your code must remain portable

with previous generations of microcontrollers, then the

BRW instruction is not available so the older table read

method must be used.

DS41639A-page 24 Preliminary 2012 Microchip Technology Inc.

3.1.1.2 Indirect Read with FSR

constants

RETLW DATA0 ;Index0 data

RETLW DATA1 ;Index1 data

RETLW DATA2

RETLW DATA3

my_function

;… LOTS OF CODE…

MOVLW LOW constants

MOVWF FSR1L

MOVLW HIGH constants

MOVWF FSR1H

MOVIW 0[FSR1]

;THE PROGRAM MEMORY IS IN W

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the

lower eight bits of the addressed word in the W register.

Writes to the program memory cannot be performed via

the INDF registers. Instructions that access the program memory via the FSR require one extra instruction

cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The High directive will set bit<7> if a label points to a

location in program memory.

EXAMPLE 3-2: ACCESSING PROGRAM

MEMORY VIA FSR

PIC16(L)F1454/5/9

2012 Microchip Technology Inc. Preliminary DS41639A-page 25

PIC16(L)F1454/5/9

Addresses BANKx

x00h or x80h INDF0

x01h or x81h INDF1

x02h or x82h PCL

x03h or x83h STATUS

x04h or x84h FSR0L

x05h or x85h FSR0H

x06h or x86h FSR1L

x07h or x87h FSR1H

x08h or x88h BSR

x09h or x89h WREG

x0Ah or x8Ah PCLATH

x0Bh or x8Bh INTCON

3.2 Data Memory Organization

The data memory is partitioned in 32 memory banks

with 128 bytes in a bank. Each bank consists of

(Figure 3-2):

• 12 core registers

• 20 Special Function Registers (SFR)

• Up to 80 bytes of General Purpose RAM (GPR)

• Up to 80 bytes of Dual-Port General Purpose

RAM (DPR)

• 16 bytes of common RAM

The active bank is selected by writing the bank number

into the Bank Select Register (BSR). Unimplemented

memory will read as ‘0’. All data memory can be

accessed either directly (via instructions that use the

file registers) or indirectly via the two File Select

Registers (FSR). See Section 3.6 “Indirect

Addressing” for more information.

Data memory uses a 12-bit address. The upper 7-bits

of the address define the Bank address and the lower

5-bits select the registers/RAM in that bank.

3.2.1 CORE REGISTERS

The core registers contain the registers that directly

affect the basic operation. The core registers occupy

the first 12 addresses of every data memory bank

(addresses x00h/x08h through x0Bh/x8Bh). These

registers are listed below in Ta b l e 3 -2 . For detailed

information, see Tab le 3 -11 .

TABLE 3-2: CORE REGISTERS

DS41639A-page 26 Preliminary 2012 Microchip Technology Inc.

PIC16(L)F1454/5/9

3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

• the arithmetic status of the ALU

• the Reset status

The STATUS register can be the destination for any

instruction, like any other register. If the STATUS

register is the destination for an instruction that affects

the Z, DC or C bits, then the write to these three bits is

disabled. These bits are set or cleared according to the

device logic. Furthermore, the TO

writable. Therefore, the result of an instruction with the

STATUS register as destination may be different than

intended.

and PD bits are not

For example, CLRF STATUS will clear the upper three

bits and set the Z bit. This leaves the STATUS register

as ‘000u u1uu’ (where u = unchanged).

It is recommended, therefore, that only BCF, BSF,

SWAPF and MOVWF instructions are used to alter the

STATUS register, because these instructions do not

affect any Status bits. For other instructions not

affecting any Status bits (Refer to Section 28.0

“Instruction Set Summary”).

Note 1: The C and DC bits operate as Borrow

and Digit Borrow out bits, respectively, in

subtraction.

3.3 Register Definitions: Status

REGISTER 3-1: STATUS: STATUS REGISTER

U-0 U-0 U-0 R-1/q R-1/q R/W-0/u R/W-0/u R/W-0/u

— — —

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

‘1’ = Bit is set ‘0’ = Bit is cleared q = Value depends on condition

TO

PD ZDC

(1)

(1)

C

bit 7-5 Unimplemented: Read as ‘0’

bit 4 TO

bit 3 PD

bit 2 Z: Zero bit

bit 1 DC: Digit Carry/Digit Borrow

bit 0 C: Carry/Borrow

Note 1: For Borrow

second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order

bit of the source register.

: Time-Out bit

1 = After power-up, CLRWDT instruction or SLEEP instruction

0 = A WDT time-out occurred

: Power-Down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

1 = A carry-out from the 4th low-order bit of the result occurred

0 = No carry-out from the 4th low-order bit of the result

(1)

bit

(ADDWF, ADDLW, SUBLW, SUBWF instructions)

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

, the polarity is reversed. A subtraction is executed by adding the two’s complement of the

bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

(1)

(1)

2012 Microchip Technology Inc. Preliminary DS41639A-page 27

PIC16(L)F1454/5/9

3.3.1 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by

the application to control the desired operation of

peripheral functions in the device. The Special Function

Registers occupy the 20 bytes after the core registers of

every data memory bank (addresses x0Ch/x8Ch

through x1Fh/x9Fh). The registers associated with the

operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

3.3.2 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory

bank. The Special Function Registers occupy the 20

bytes after the core registers of every data memory

bank (addresses x0Ch/x8Ch through x1Fh/x9Fh).

3.3.2.1 Linear Access to GPR

The general purpose RAM can be accessed in a

non-banked method via the FSRs. This can simplify

access to large memory structures. See Section 3.6.2

“Linear Data Memory” for more information.

Refer to Table 3-3 for Dual Port and USB addressing

information.

TABLE 3-3: DUAL PORT RAM ADDRESSING

Port 0 Port 1

3.3.3 DUAL-PORT RAM

Part of the data memory is mapped to a special dual

access RAM. When the USB module is disabled, the

GPRs in these banks are used like any other GPR in

the data memory space.

When the USB module is enabled, the memory in these

banks is allocated as buffer RAM for USB operation.

This area is shared between the microcontroller core

and the USB Serial Interface Engine (SIE) and is used

to transfer data directly between the two.

It is theoretically possible to use the areas of USB RAM

that are not allocated as USB buffers for normal

scratchpad memory or other variable storage. In practice,

the dynamic nature of buffer allocation makes this risky at

best. Additional information on USB RAM and buffer

operation is provided in Section 26.0 “Universal Serial

Bus (USB)”.

3.3.4 COMMON RAM

There are 16 bytes of common RAM accessible from all

banks.

CPU Banked Address CPU Linear Address USB Banked Address USB Linear Address

020 - 06F 2000 - 204F 020 - 06F 2000 - 204F

0A0 - 0EF 2050 - 209F 0A0 - 0EF 2050 - 209F

120 - 16F 20A0 - 20EF 120 - 16F 20A0 - 20EF

1A0 - 1EF 20F0 - 213F 1A0 - 1EF 20F0 - 213F

220 - 26F 2140 - 218F 220 - 26F 2140 - 218F

2A0 - 2EF 2190 - 21DF 2A0 - 2EF 2190 - 21DF

320 - 32F 21E0 - 21EF 320 - 32F 21E0 - 21EF

370 - 37F (1) 370 - 37F (1)

Note 1: Accessible from banked memory only.

DS41639A-page 28 Preliminary 2012 Microchip Technology Inc.

PIC16(L)F1454/5/9

0Bh

0Ch

1Fh

20h

6Fh

70h

7Fh

00h

Common RAM

(16 bytes)

Dual Port RAM

(80 bytes maximum)

Core Registers

(12 bytes)

Special Function Registers

(20 bytes maximum)

Memory Region

7-bit Bank Offset

(1)

General Purpose RAM

(80 bytes maximum)

OR

Note 1: If the USB module is disabled, data

memory is GPR. If enabled, data

memory can be DPR. Refer to Memory Map for RAM type details.

FIGURE 3-2: BANKED MEMORY

PARTITIONING

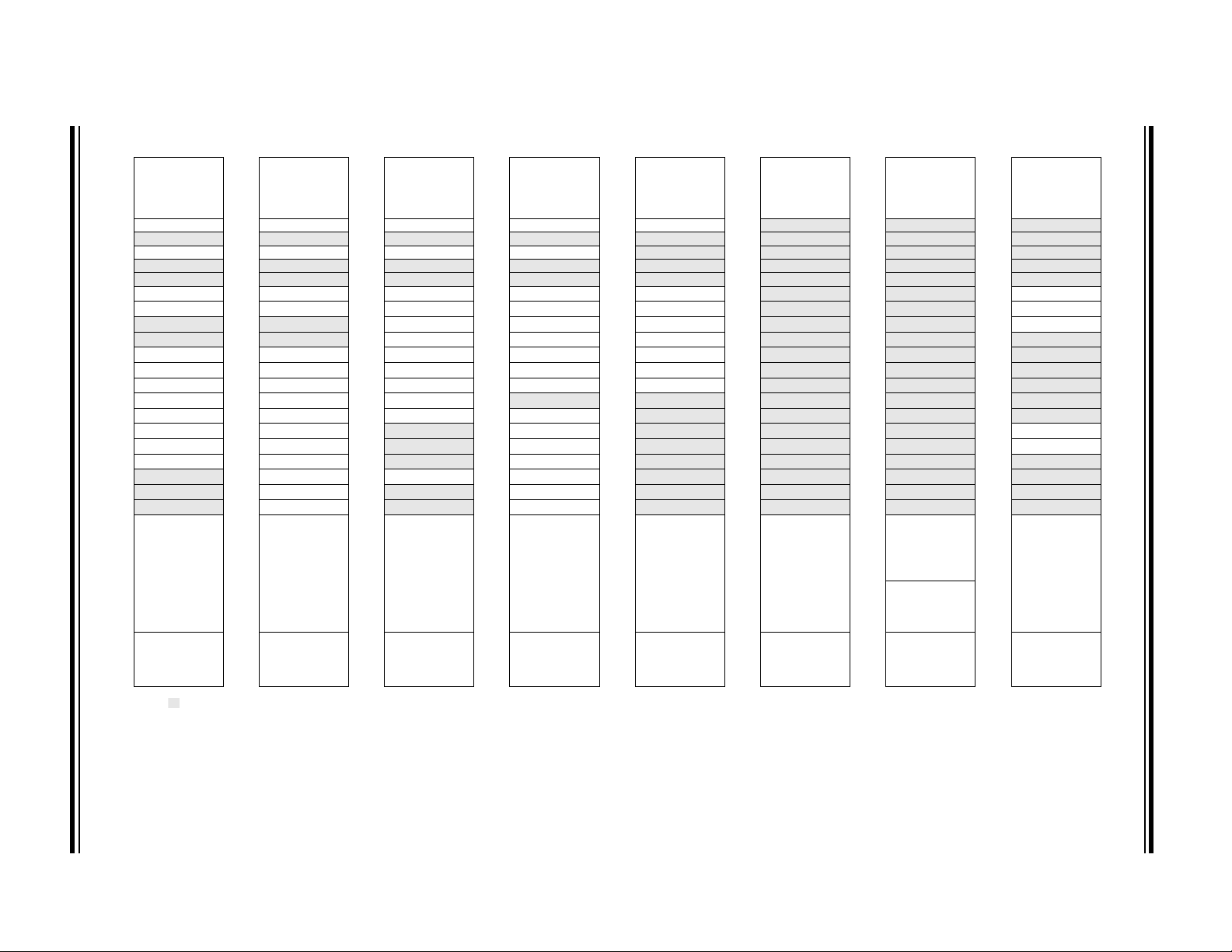

3.3.5 DEVICE MEMORY MAPS

The memory maps for PIC16(L)F1454/5/9 are as

shown in Tab le 3 -8 and Table 3-9.

2012 Microchip Technology Inc. Preliminary DS41639A-page 29

DS41639A-page 30 Preliminary 2012 Microchip Technology Inc.

TABLE 3-4: PIC16(L)F1454 MEMORY MAP, BANK 0-7

PIC16(L)F1454/5/9

BANK 0 BANK 1 BANK 2 BANK 3 BANK 4 BANK 5 BANK 6 BANK 7

000h

Core Registers

(Ta bl e 3- 2 )

00Bh 08Bh 10Bh 18Bh 20Bh 28Bh 30Bh 38Bh

00Ch PORTA 08Ch TRISA 10Ch LATA 18Ch

00Dh

00Eh PORTC 08Eh TRISC 10Eh LATC 18Eh

00Fh

010h

011h PIR1 091h PIE1 111h

012h PIR2 092h PIE2 112h

013h

014h

015h TMR0 095h OPTION_REG 115h

016h

017h

018h

019h

01Ah

01Bh

01Ch

01Dh

01Eh

01Fh

020h

06Fh

070h

07Fh 0FFh 17Fh 1FFh 27Fh 2FFh 37Fh 3FFh

Legend: = Unimplemented data memory locations, read as ‘0’.

— 08Dh — 10Dh — 18Dh — 20Dh — 28Dh — 30Dh — 38Dh —

—08Fh—10Fh—18Fh—20Fh—28Fh—30Fh—38Fh—

—090h—110h—190h—210h—290h

—093h—113h

—094h—114h

TMR1L 096h PCON 116h BORCON 196h PMCON2 216h

TMR1H 097h WDTCON 117h

T1CON 098h OSCTUNE 118h

T1GCON 099h OSCCON 119h

TMR2 09Ah OSCSTAT 11Ah

PR2 09Bh

T2CON 09Ch

— 09Dh

—

—

Dual-Port

General

Purpose

Register

80 Bytes

Dual-Port

Common RAM

080h

09Eh

09Fh

0A0h

0EFh

0F0h

Core Registers

(Ta bl e 3- 2 )

—11Bh—19Bh

— 11Ch — 19Ch

—

—

—

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

100h

Core Registers

(Table 3-2)

—

—

—

—

—

— 197h VREGCON 217h

—198h—218h

—199h

—19Ah

11Dh APFCON 19Dh

11Eh

11Fh

120h

16Fh 1EFh 26Fh 2EFh 36Fh 3EFh

170h

—

—19Fh

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

180h

Core Registers

(Table 3-2)

— 20Ch WPUA 28Ch — 30Ch — 38Ch —

—20Eh—28Eh—30Eh—38Eh—

191h PMADRL 211h

192h PMADRH 212h

193h PMDATL 213h

194h PMDATH 214h

195h PMCON1 215h

RCREG

TXREG

SPBRG

SPBRGH

RCSTA

19Eh

1A0h

1F0h

TXSTA

BAUDCON

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

200h

219h —299h— 319h — 399h —

21Ah —29Ah—31Ah—39Ah

21Bh —29Bh—31Bh

21Ch — 29Ch — 31Ch

21Dh

21Eh

21Fh

220h

270h

Core Registers

(Table 3-2)

SSP1BUF

SSP1ADD

SSP1MSK

SSP1STAT

SSP1CON1

SSP1CON2

SSP1CON3

—

—

—

—

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

280h

Core Registers

(Table 3-2)

—

291h

292h

293h

294h

295h

296h

297h — 317h — 397h —

298h

29Dh

29Eh

29Fh

2A0h

2F0h

—

—

—

—

—

— 316h — 396h

— 318h — 398h —

—

—

—

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

300h

310h

311h

312h

313h

314h

315h

31Dh

31Eh

31Fh

320h

32Fh

330h

370h

Core Registers

(Table 3-2)

— 390h —

—

—

—

—

—

—

—

—

—

—

Dual-Port

General

Purpose

Register

16Bytes

General

Purpose

Register

64 Bytes

Common RAM

(Accesses

70h – 7Fh)

380h

391h IOCAP

392h IOCAN

393h

394h

395h

39Bh CRCON

39Ch

39Dh

39Eh

39Fh

3A0h

3F0h

Core Registers

(Table 3-2)

IOCAF

CLKRCON

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

—

—

—

—

—

—

—

2012 Microchip Technology Inc. Preliminary DS41639A-page 31

TABLE 3-5: PIC16(L)F1455 MEMORY MAP, BANK 0-7

BANK 0 BANK 1 BANK 2 BANK 3 BANK 4 BANK 5 BANK 6 BANK 7

000h

Core Registers

(Ta bl e 3- 2 )

00Bh 08Bh 10Bh 18Bh 20Bh 28Bh 30Bh 38Bh

00Ch PORTA 08Ch TRISA 10Ch LATA 18Ch ANSELA 20Ch WPUA 28Ch

00Dh

00Eh PORTC 08Eh TRISC 10Eh LATC 18Eh ANSELC 20Eh

00Fh

010h

011h PIR1 091h PIE1 111h CM1CON0 191h PMADRL 211h

012h PIR2 092h PIE2 112h CM1CON1 192h PMADRH 212h

013h

014h

015h TMR0 095h OPTION_REG 115h CMOUT 195h PMCON1 215h

016h

017h

018h

019h

01Ah

01Bh

01Ch

01Dh

01Eh

01Fh

020h

06Fh

070h

07Fh 0FFh 17Fh 1FFh 27Fh 2FFh 37Fh 3FFh

Legend: = Unimplemented data memory locations, read as ‘0’.

— 08Dh — 10Dh — 18Dh — 20Dh — 28Dh — 30Dh — 38Dh —

—08Fh—10Fh—18Fh—20Fh—28Fh—30Fh—38Fh—

—090h—110h—190h—210h—290h

—093h— 113h CM2CON0 193h PMDATL 213h

—094h— 114h CM2CON1 194h PMDATH 214h

TMR1L 096h PCON 116h BORCON 196h PMCON2 216h

TMR1H 097h WDTCON 117h FVRCON 197h VREGCON 217h

T1CON 098h OSCTUNE 118h

T1GCON 099h OSCCON 119h

TMR2 09Ah OSCSTAT 11Ah

PR2 09BhADRESL11Bh

T2CON 09Ch ADRESH 11Ch

— 09Dh ADCON0 11Dh APFCON 19Dh

—

—

Dual-Port

General

Purpose

Register

80 Bytes

Dual-Port

Common RAM

080h

Core Registers

(Ta bl e 3- 2 )

09Eh ADCON1 11Eh

09Fh ADCON2 11Fh

0A0h

Dual-Port

General

Purpose

Register

80 Bytes

0EFh

0F0h

Common RAM

(Accesses

70h – 7Fh)

100h

120h

16Fh 1EFh 26Fh 2EFh 36Fh 3EFh

170h

Core Registers

(Table 3-2)

DACCON0

DACCON1

—19Ah

—19Bh

— 19Ch

—

—19Fh

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

180h

198h

199h

19Eh

1A0h

1F0h

Core Registers

(Table 3-2)

—218h

RCREG

TXREG

SPBRG

SPBRGH

RCSTA

TXSTA

BAUDCON

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

200h

Core Registers

(Table 3-2)

—28Eh—30Eh—38Eh—

SSP1BUF

SSP1ADD

SSP1MSK

SSP1STAT

SSP1CON1

SSP1CON2

SSP1CON3

—

219h

21Ah —29Ah—31Ah—39Ah

21Bh —29Bh—31Bh

21Ch — 29Ch — 31Ch

21Dh

21Eh

21Fh

220h

270h

—299h— 319h — 399h —

—

—

—

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

280h

291h

292h

293h

294h

295h

296h

297h

298h

29Dh

29Eh

29Fh

2A0h

2F0h

Core Registers

(Table 3-2)

— 30Ch — 38Ch —

—

—

—

—

—

—

— 316h — 396h

— 317h — 397h —

— 318h — 398h —

—

—

—

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

300h

310h

311h

312h

313h

314h

315h

31Dh

31Eh

31Fh

320h

32Fh

330h

370h

Core Registers

(Table 3-2)

— 390h —

—

—

—

—

—

—

—

—

—

—

Dual-Port

General

Purpose

Register

16Bytes

General

Purpose

Register

64 Bytes

Common RAM

(Accesses

70h – 7Fh)

380h

Core Registers

(Table 3-2)

391h IOCAP

392h IOCAN

393h

394h

395h

39Bh CRCON

39Ch

39Dh

39Eh

39Fh

3A0h

3F0h

IOCAF

—

—

—

CLKRCON

—

—

—

—

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

PIC16(L)F1454/5/9

DS41639A-page 32 Preliminary 2012 Microchip Technology Inc.

TABLE 3-6: PIC16(L)F1459 MEMORY MAP, BANK 0-7

PIC16(L)F1454/5/9

BANK 0 BANK 1 BANK 2 BANK 3 BANK 4 BANK 5 BANK 6 BANK 7

000h

Core Registers

(Ta bl e 3- 2 )

00Bh 08Bh 10Bh 18Bh 20Bh 28Bh 30Bh 38Bh

00Ch PORTA 08Ch TRISA 10Ch LATA 18Ch ANSELA 20Ch WPUA 28Ch

00Dh PORTB 08Dh TRISB 10Dh LATB 18Dh ANSELB 20Dh WPUB 28Dh

00Eh PORTC 08Eh TRISC 10Eh LATC 18Eh ANSELC 20Eh

00Fh

010h

011h PIR1 091h PIE1 111h CM1CON0 191h PMADRL 211h

012h PIR2 092h PIE2 112h CM1CON1 192h PMADRH 212h

013h

014h

015h TMR0 095h OPTION_REG 115h CMOUT 195h PMCON1 215h

016h

017h

018h

019h

01Ah

01Bh

01Ch

01Dh

01Eh

01Fh

020h

06Fh 0EFh

070h

07Fh 0FFh 17Fh 1FFh 27Fh 2FFh 37Fh 3FFh

Legend: = Unimplemented data memory locations, read as ‘0’.

—08Fh—10Fh—18Fh—20Fh—28Fh—30Fh—38Fh—

—090h—110h—190h—210h—290h

—093h— 113h CM2CON0 193h PMDATL 213h

—094h— 114h CM2CON1 194h PMDATH 214h

TMR1L 096h PCON 116h BORCON 196h PMCON2 216h

TMR1H 097h WDTCON 117h FVRCON 197h VREGCON 217h

T1CON 098h OSCTUNE 118h

T1GCON 099h OSCCON 119h

TMR2 09Ah OSCSTAT 11Ah

PR2 09BhADRESL11Bh

T2CON 09Ch ADRESH 11Ch

— 09Dh ADCON0 11Dh APFCON 19Dh

—

—

Dual-Port

General

Purpose

Register

80 Bytes

Dual-Port

Common RAM

080h

Core Registers

(Ta bl e 3- 2 )

09Eh ADCON1 11Eh

09Fh ADCON2 11Fh

0A0h

Dual-Port

General

Purpose

Register

80 Bytes

0F0h

Common RAM

(Accesses

70h – 7Fh)

100h

120h

16Fh 1EFh 26Fh 2EFh 36Fh

170h

Core Registers

(Table 3-2)

DACCON0

DACCON1

—19Ah

—19Bh

— 19Ch

—

—19Fh

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

180h

198h

199h

19Eh

1A0h

1F0h

Core Registers

(Table 3-2)

—218h

RCREG

TXREG

SPBRG

SPBRGH

RCSTA

TXSTA

BAUDCON

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

200h

Core Registers

(Table 3-2)

—28Eh—30Eh—38Eh—

SSP1BUF

SSP1ADD

SSP1MSK

SSP1STAT

SSP1CON1

SSP1CON2

SSP1CON3

—

219h

21Ah —29Ah—31Ah—39Ah

21Bh —29Bh—31Bh

21Ch — 29Ch — 31Ch

21Dh

21Eh

21Fh

220h

270h

—299h— 319h — 399h —

—

—

—

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

280h

291h

292h

293h

294h

295h

296h

297h

298h

29Dh

29Eh

29Fh

2A0h

2F0h

Core Registers

(Table 3-2)

— 30Ch — 38Ch —

— 30Dh — 38Dh —

—

—

—

—

—

—

— 316h — 396h IOCBF

— 317h — 397h —

— 318h — 398h —

—

—

—

Dual-Port

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

300h

310h

311h

312h

313h

314h

315h

31Dh

31Eh

31Fh

320h

32Fh

330h

370h

Core Registers

(Table 3-2)

— 390h —

—

—

—

—

—

—

—

—

—

—

Dual-Port

General

Purpose

Register

16Bytes

General

Purpose

Register

64 Bytes

Common RAM

(Accesses

70h – 7Fh)

380h

391h IOCAP

392h IOCAN

393h

394h IOCBP

395h IOCBN

39Bh CRCON

39Ch

39Dh

39Eh

39Fh

3A0h

3EFh

3F0h

Core Registers

(Table 3-2)

CLKRCON

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

IOCAF

—

—

—

—

2012 Microchip Technology Inc. Preliminary DS41639A-page 33

TABLE 3-7: PIC16(L)F1454 MEMORY MAP, BANK 8-23

BANK 8 BANK 9 BANK 10 BANK 11 BANK 12 BANK 13 BANK 14 BANK 15

400h

Core Registers

(Ta bl e 3- 2 )

40Bh

40Ch

40Dh

40Eh

40Fh

410h

411h

412h

413h

414h

415h

416h

417h

418h

419h

41Ah

41Bh

41Ch

41Dh

41Eh

41Fh

420h

46Fh 4EFh 56Fh 5EFh 66Fh 6EFh 76Fh 7EFh

470h

47Fh 4FFh 57Fh 5FFh 67Fh 6FFh 77Fh 7FFh

— 48Ch — 50Ch — 58Ch — 60Ch — 68Ch — 70Ch — 78Ch —

— 48Dh — 50Dh — 58Dh — 60Dh — 68Dh — 70Dh — 78Dh —

—48Eh—50Eh—58Eh—60Eh—68Eh—70Eh—78Eh—

—48Fh—50Fh—58Fh—60Fh—68Fh—70Fh—78Fh—

—490h—510h—590h—610h—690h— 710h — 790h —

—491h—511h—591h— 611h PWM1DCL 691h —711h— 791h —

—492h—512h—592h— 612h PWM1DCH 692h — 712h — 792h —

—493h—513h—593h— 613h PWM1CON 693h — 713h — 793h —

—494h—514h—594h— 614h PWM2DCL 694h — 714h — 794h —

—495h—515h—595h— 615h PWM2DCH 695h — 715h — 795h —

—496h—516h—596h— 616h PWM2CON 696h — 716h — 796h —

—497h—517h—597h—617h—697h— 717h — 797h —

—498h—518h—598h—618h—698h— 718h — 798h —

—499h—519h—599h—619h—699h— 719h — 799h —

—49Ah—51Ah—59Ah—61Ah—69Ah—71Ah—79Ah—

—49Bh—51Bh—59Bh—61Bh—69Bh—71Bh—79Bh—

— 49Ch — 51Ch — 59Ch — 61Ch — 69Ch — 71Ch — 79Ch —

— 49Dh — 51Dh — 59Dh — 61Dh — 69Dh — 71Dh — 79Dh —

—49Eh—51Eh—59Eh—61Eh—69Eh—71Eh—79Eh—

—49Fh—51Fh—59Fh—61Fh—69Fh—71Fh—79Fh—

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

480h

48Bh

4A0h

4F0h

Core Registers

(Ta bl e 3- 2 )

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

500h

50Bh

520h

570h

Core Registers

(Table 3-2)

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

580h

58Bh

5A0h

5F0h

Core Registers

(Table 3-2)

General

Purpose

Register

80 Bytes

Common RAM

(Accesses

70h – 7Fh)

600h

60Bh

620h

64Fh

650h

670h

Core Registers

(Table 3-2)

General

Purpose

Register

48 Bytes

Unimplemented

Read as ‘0’

Common RAM

(Accesses

70h – 7Fh)

680h

68Bh

6A0h

6F0h

Core Registers

(Table 3-2)

Unimplemented

Read as ‘0’

Common RAM

(Accesses

70h – 7Fh)

700h

70Bh

720h

770h

Core Registers

(Table 3-2)

Unimplemented

Read as ‘0’

Common RAM

(Accesses

70h – 7Fh)

780h

78Bh

7A0h

7F0h

Core Registers

(Table 3-2)

Unimplemented

Read as ‘0’

Common RAM

(Accesses

70h – 7Fh)

PIC16(L)F1454/5/9

BANK 16 BANK 17 BANK 18 BANK 19 BANK 20 BANK 21 BANK 22 BANK 23

800h

Core Registers

(Ta bl e 3- 2 )

80Bh

80Ch

Unimplemented

Read as ‘0’

86Fh 8EFh 96Fh

870h

Common RAM

(Accesses

87Fh 8FFh 97Fh 9FFh A7Fh AFFh B7Fh BFFh

Legend: = Unimplemented data memory locations, read as ‘0’.

70h – 7Fh)

880h

88Bh

88Ch

8F0h

Core Registers

(Ta bl e 3- 2 )

Unimplemented

Read as ‘0’

Common RAM

(Accesses

70h – 7Fh)

900h

90Bh

90Ch

970h

Core Registers

(Table 3-2)

Unimplemented

Read as ‘0’

Common RAM

(Accesses

70h – 7Fh)

980h

98Bh

98Ch

9EFh

9F0h