Page 1

INTEGRATED CIRCUITS

PCK2021

CK00 (100/133 MHz) spread spectrum

differential system clock generator

Product data

File under Integrated Circuits, ICL03

2001 Oct 11

Page 2

Philips Semiconductors Product data

CK00 (100/133 MHz) spread spectrum

differential system clock generator

FEA TURES

•3.3 V operation

•Six differential CPU clock pairs

•Two PCI clocks at 33 MHz and one 3V66 clock

•Two 48 MHz clocks at 3.3 V

•One 14.318 MHz reference clock

•Power management control pins

•Host clock jitter less than 200 ps cycle-to-cycle

•Host clock skew less than 150 ps pin-to-pin

•Spread Spectrum capability

•Optimized frequency and spread spectrum performance

DESCRIPTION

The PCK2021 is a clock synthesizer/driver for a Pentium III and

other similar processors.

The PCK2021 has six differential pair CPU current source outputs,

two 33 MHz outputs, one 3V66 output, and two 48 MHz clocks

which can be disabled on power-up, and one 3.3 V reference clock

at 14.318 MHz which can also be disabled on power-up.

The part possesses a dedicated power-down input pin for power

management control. This input is synchronized on chip, and

ensures glitch-free output transitions. In addition, the part can be

configured to disable the 48 MHz outputs for lower power operation

and an increase in the performance of the functioning outputs. The

REF and PCI outputs can also be disabled for the highest

performance of the Host outputs.

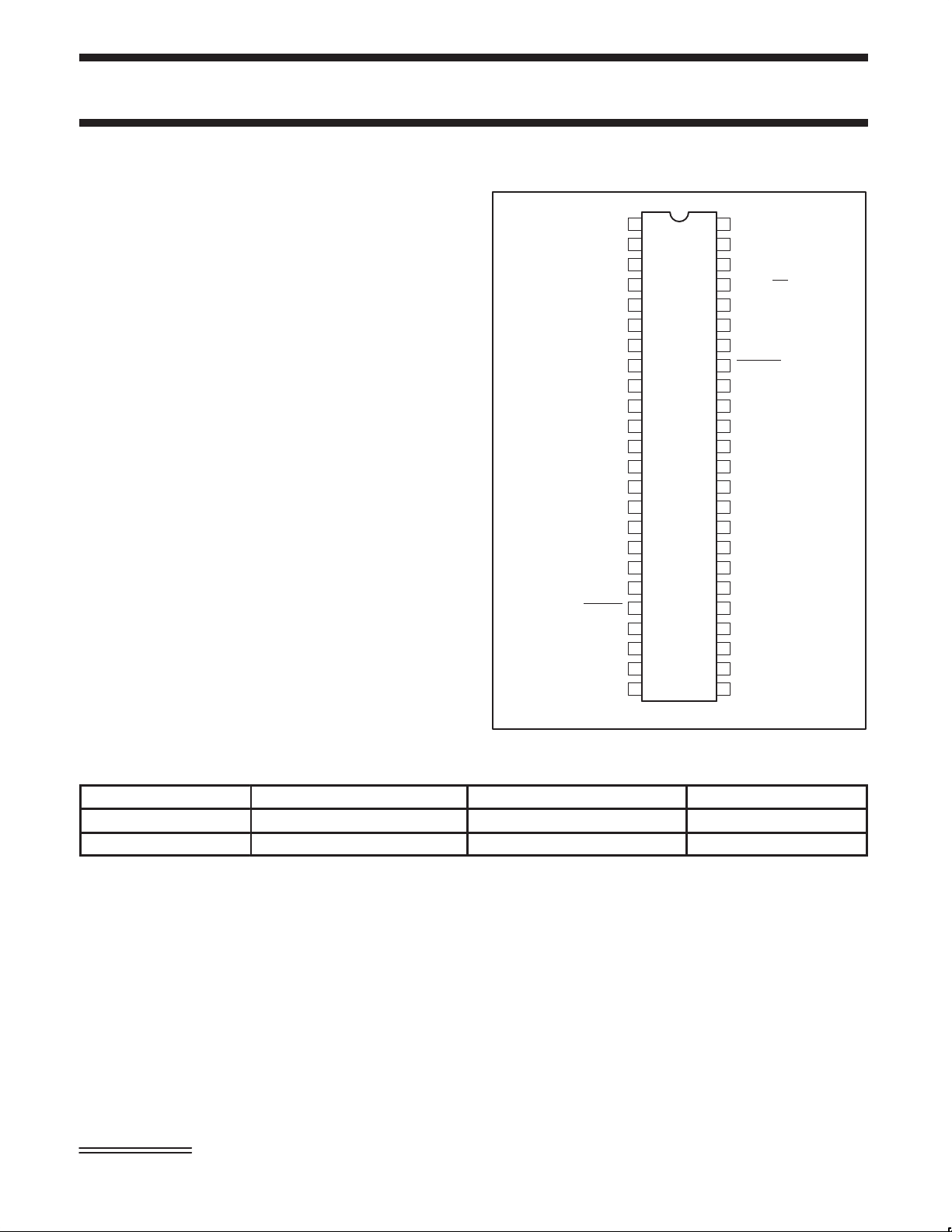

PIN CONFIGURATION

1

DDPCI

2

V

DD48

V

3V66

V

SS3V66

V

DD3V66

V

DDCPU

HCLK0

V

DDCPU

V

SSCPU

HCLK2

V

DDCPU

V

SSREF

XOUT

V

DDREF

SS48

REF

XIN

3

4

5

6

7

8

9

10

11

12 37

13

14

15

16

17

18 31

19 30

20

21

22

23

24 25

48M_0/SELA

48M_1/SELB

HCLKB0

HCLKB1

HCLKB2

PCK2021

48V

PCI0

47

PCI1

46

V

SSPCI

45

SEL133/100

44

NC

43

V

DDA

42

V

SSA

PWRDWN

41

40

V

DDCPU

39

HCLK3

38

HCLKB3

V

DDCPU

36HCLK1

HCLK4

HCLKB4

35

34

V

SSCPU

HCLK5

33

32

HCLKB5

V

DD

MULTSEL0

29SPREAD

MULTSEL1

V

28

SS

27

V

SSIREF

26

I

REF

V

DDIREF

SW00960

ORDERING INFORMA TION

PACKAGES TEMPERATURE RANGE ORDER CODE DRAWING NUMBER

48-Pin Plastic TSSOP 0 to +70 °C PCK2021DGG SOT362-1

48-Pin Plastic SSOP 0 to +70 °C PCK2021DL SOT370-1

Intel and Pentium III are trademarks of Intel Corporation.

2001 Oct 1 1 853-2301 27233

2

Page 3

Philips Semiconductors Product data

CK00 (100/133 MHz) spread spectrum differential

PCK2021

system clock generator

PIN DESCRIPTION

PIN(S) SYMBOL FUNCTION

1, 2, 8, 9,

12, 18, 24,

25, 31, 37,

40

3, 4 48M_0/SELA

6 3V66 66 MHz clock: 66 MHZ reference clock

10, 11 HCLK0

13, 14 HCLK1

16, 17 HCLK2

47, 48 PCI0

39, 38 HCLK3

36, 35 HCLK4

33, 32 HCLK5

19 REF 3.3 V fixed 14.318 MHz output

20 SPREAD Enables spread spectrum mode when held LOW on differential host outputs, 3V66 and PCI clocks.

22 XIN Crystal input

23 XOUT Crystal output

26 I

29, 30 MULTSEL0

41 PWRDWN Device enters power-down mode when held LOW. Asserts LOW .

45 SEL133/100 Select input pin for enabling 133 MHz or 100 MHz CPU outputs

5, 7, 15,

21, 27, 28,

34, 46

43 V

42 V

V

DD

48M_1/SELB

HCLKB0

HCLKB1

HCLKB2

PCI1

HCLKB3

HCLKB4

HCLKB5

REF

MULTSEL1

V

SS

DDA

SSA

3.3 V power supply

Pins 9, 12, and 18 supply host output pairs 0, 1, and 2.

Pins 37 and 40 supply host output pairs 3, 4, and 5.

3.3 V fixed 48 MHz clock outputs. During power-up pins function as latched inputs that enable SELA and

SELB prior to the pins being used for output of 3 V at 48 MHz. Part must be clocked to latch data in.

Host output pair 0

Host output pair 1

Host output pair 2

33 MHz clocks: 33 MHz reference clocks

Host output pair 3

Host output pair 4

Host output pair 5

Asserts LOW.

This pin controls the reference current for the host pairs. This pin requires a fixed precision resistor tied to

ground in order to establish the correct current.

Select input pin used to control the scaling of the HCLK and HCLKB output current.

Ground

3.3 V power supply for analog circuits

Ground for analog circuits

2001 Oct 1 1

3

Page 4

Philips Semiconductors Product data

CK00 (100/133 MHz) spread spectrum differential

system clock generator

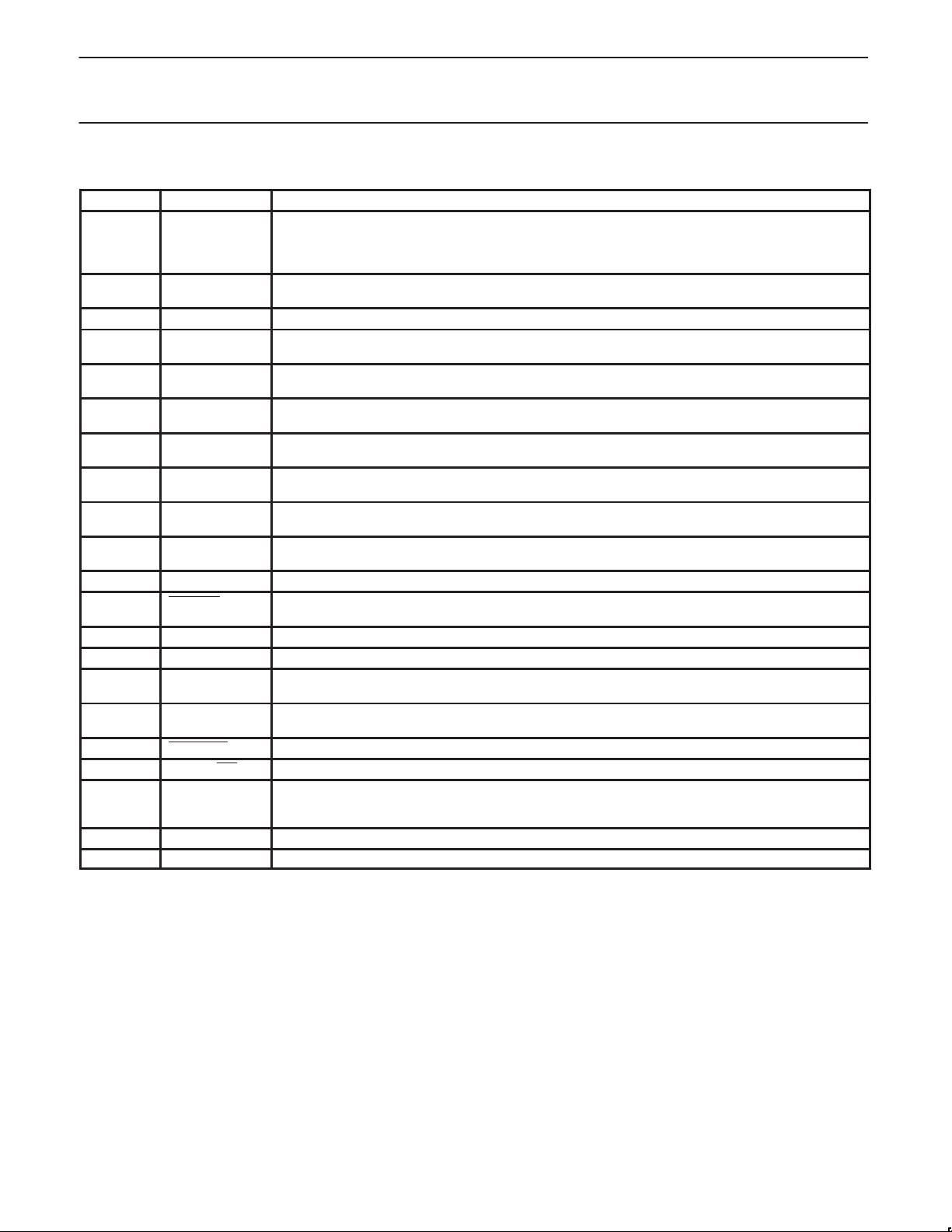

BLOCK DIAGRAM

XIN

XOUT

I

REF

14.318 MHz

OSC

USB PLL

SYS PLL

PWRDWN

PWRDWN

SELA/B

PWRDWN

PWRDWN

PWRDWN

PCK2021

REF[0] (14.318 MHz)

SELC

48MHz[0..1] (3 V)

HOST[0..5] (100/133 MHz)

IBIAS

HOST_BAR[0..5] (100/133 MHz)

PCI[0..1] (33 MHz)

PWRDWN

SEL133/100

SPREAD

MULTSEL0

MULTSEL1

PWRDWN

LOGIC

3V66[0] (66 MHz)

SW00961

FUNCTION TABLE

SEL100/133 SELA SELB HOST 48MHz PCI33MHz 66MHz REFCLK

0 0 0 100 MHz 48 MHz 33.3 MHz 66.7 MHz 14.3 MHz

0 0 1 100 MHz Disable/Low 33.3 MHz 66.7 MHz 14.3 MHz

0 1 0 100 MHz Disable/Low Disable/Low 66.7 MHz Disable/Low

0 1 1 Hi-Z Hi-Z Hi-Z Hi-Z Hi-Z

1 0 0 133 MHz 48 MHz 33.3 MHz 66.7 MHz 14.3 MHz

1 0 1 133 MHz Disable/Low 33.3 MHz 66.7 MHz 14.3 MHz

1 1 0 200 MHz 48 MHz 33.3 MHz 66.7 MHz 14.3 MHz

2001 Oct 1 1

4

Page 5

Philips Semiconductors Product data

CK00 (100/133 MHz) spread spectrum differential

system clock generator

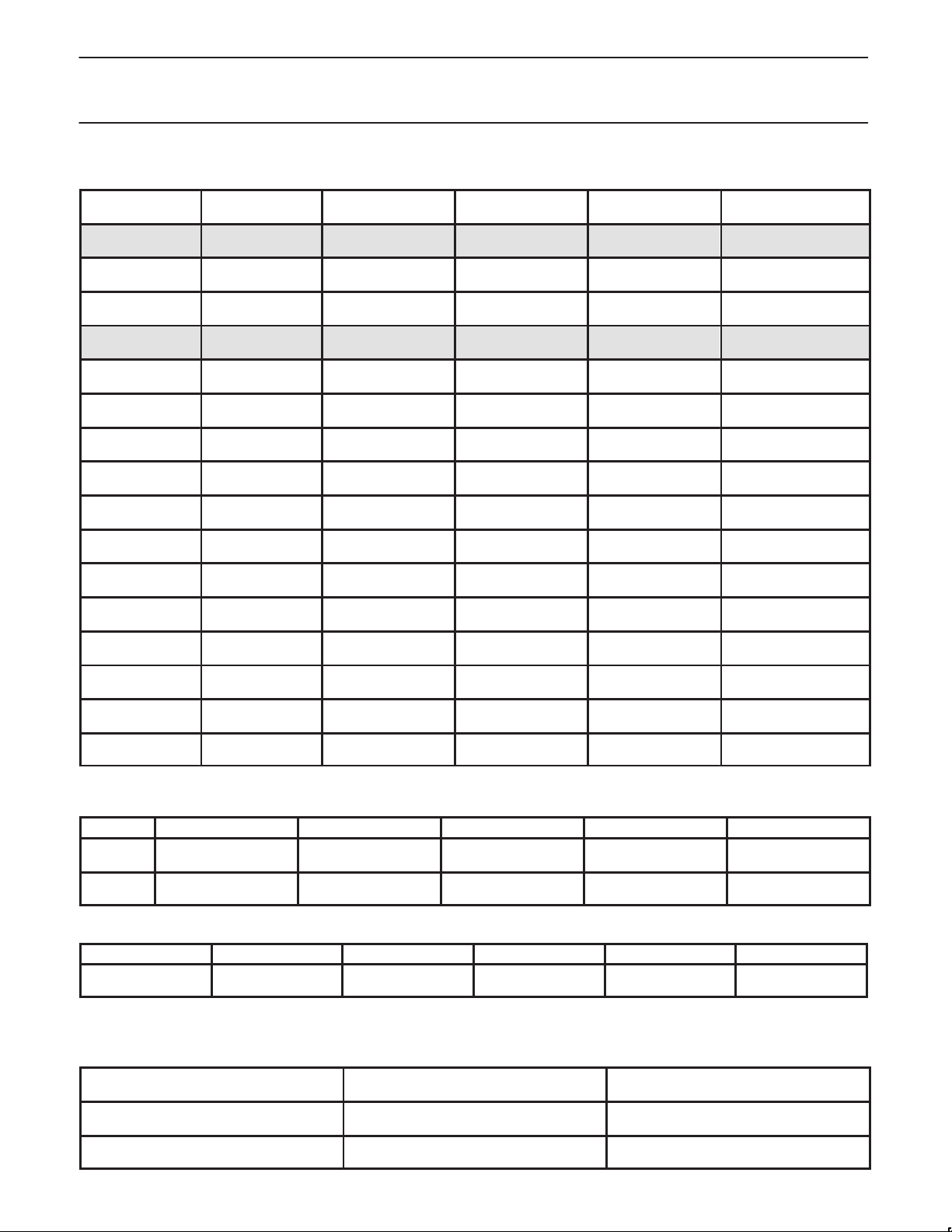

Table 1. Host swing select functions

MULTSEL0 MULTSEL1

0 0 60 Ω

0 0 50 Ω

0 1 60 Ω

0 1 50 Ω

1 0 60 Ω

1 0 50 Ω

1 1 60 Ω

1 1 50 Ω

0 0 30 Ω

0 0 25 Ω

0 1 30 Ω

0 1 25 Ω

1 0 30 Ω

1 0 25 Ω

1 1 30 Ω

1 1 25 Ω

NOTE:

The outputs are optimized for the configurations shown shaded.

BOARD

IMPEDANCE

R

I

R

I

R

I

R

I

R

I

R

I

R

I

R

I

R

R

R

R

R

R

R

R

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

I

REF

I

REF

I

REF

I

REF

I

REF

I

REF

I

REF

I

REF

REF

REF

REF

REF

REF

REF

REF

I

REF

= 475 1%

= 2.32 mA

= 475 1%

= 2.32 mA

= 475 1%

= 2.32 mA

= 475 1%

= 2.32 mA

= 475 1%

= 2.32 mA

= 475 1%

= 2.32 mA

= 475 1%

= 2.32 mA

= 475 1%

= 2.32 mA

= 221 1%

= 5 mA

= 221 1%

= 5 mA

= 221 1%

= 5 mA

= 221 1%

= 5 mA

= 221 1%

= 5 mA

= 221 1%

= 5 mA

= 221 1%

= 5 mA

= 221 1%

= 5 mA

I

OH

IOH = 5*I

IOH = 5*I

IOH = 6*I

IOH = 6*I

IOH = 4*I

IOH = 4*I

IOH = 7*I

IOH = 7*I

IOH = 5*I

IOH = 5*I

IOH = 6*I

IOH = 6*I

IOH = 4*I

IOH = 4*I

IOH = 7*I

IOH = 7*I

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

REF

PCK2021

VOH @ IREF = 2.32 mA

0.71 V

0.59 V

0.85 V

0.71 V

0.56 V

0.47 V

0.99 V

0.82 V

0.75 V

0.62 V

0.90 V

0.75 V

0.60 V

0.50 V

1.05 V

0.84 V

CONDITIONS CONFIGURATION LOAD MIN. MAX.

I

OUT

I

OUT

VDD = 3.3 V

VDD = 3.3 V ±5%

All combinations;

see Table 1 above

All combinations;

see Table 1 above

Nominal test load for

given configuration

Nominal test load for

given configuration

–7% of I

OH

see Table 1 above

–12% of I

see Table 1 above

OH

+7% of I

see Table 1 above

+12% of I

see Table 1 above

POWER-DOWN MODE

PWRDWN HCLK/HCLKB 3V66 PCI 48MHz REFCLK

Asserts LOW

0 = Active

Host = 2*I

Host_bar = undriven

REF

LOW LOW LOW LOW

NOTE:

The differential outputs should have a voltage forced across them when power-down is asserted.

SPREAD SPECTRUM FUNCTION

48 MHz PLL

REFCLK

No Spread

No Spread

2001 Oct 1 1

SPREAD # FUNCTION

1

0

Host, PCI, and 3V66

No Spread

Host, PCI, and 3V66

spread t0.5%

5

OH

OH

Page 6

Philips Semiconductors Product data

SYMBOL

PARAMETER

CONDITIONS

UNIT

SYMBOL

PARAMETER

CONDITIONS

UNIT

CK00 (100/133 MHz) spread spectrum differential

PCK2021

system clock generator

ABSOLUTE MAXIMUM RATINGS

LIMITS

MIN MAX

V

DD3

I

IK

V

I

OK

V

O

I

O

T

stg

P

tot

NOTES:

1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the

device at these or any other condition beyond those indicated under “recommended operating condition” is not implied. Exposure to

absolute-maximum-rated conditions for extended periods may affect device reliability .

2. The input and output voltage rating may be exceeded if the input and output current ratings are observed.

RECOMMENDED OPERATING CONDITIONS

V

DD3

AV

DD

C

f

ref

T

amb

DC 3.3 V supply –0.5 4.6 V

DC input diode current VI < 0 — –50 mA

DC input voltage Note 2 –0.5 V

I

DC output diode current VO > VDD or VO < 0 — ±50 mA

DC output voltage Note 2 –0.5 VDD+0.5 V

DC output source or sink current VO = 0 to V

DD

— ±50 mA

Storage temperature range –65 +150 °C

Power dissipation per package

plastic medium-shrink (TSSOP)

For temperature range 0 °C to +70 °C;

above +55 °C derate linearly with 11.3 mW/K

— 850 mW

LIMITS

MIN MAX

DC 3.3 V supply voltage 3.135 3.465 V

DC 3.3 V analog supply voltage 3.135 3.465 V

Capacitive load on:

3V666 1 device load, possible 2 10 30 pF

L

PCI Must meet JEDEC

PCI 2.1 Spec. Requirements

10 30 pF

48 MHz clock 1 device load 10 20 pF

REF 1 device load 10 20 pF

Reference frequency , oscillator normal value 14.31818 14.31818 MHz

Operating ambient temperature range in free air 0 +70 °C

DD

V

POWER MANAGEMENT

CONDITION

Power-down mode (PWRDWN = 0) 60 mA

Full active 100/133 MHz 250 mA

2001 Oct 1 1

MAXIMUM 3.3 V SUPPLY CONSUMPTION

MAXIMUM DISCRETE CAPACITANCE LOADS

V

= 3.465 V

DDL

ALL STATIC INPUTS = V

DD3

OR V

SS

6

Page 7

Philips Semiconductors Product data

SYMBOL

PARAMETER

UNIT

I

y

I

y

I

3.135 to 3.465

Type X1

I

y

I

y

VOLHOST/HOST_BAR

V

V

S

Type X1

0.05

V

CK00 (100/133 MHz) spread spectrum differential

system clock generator

DC ELECTRICAL CHARACTERISTICS

T

= 0 to +70 °C

amb

CONDITIONS LIMITS

VDD (V) OTHER MIN TYP MAX

V

V

V

OH3

V

OL3

V

OHP

V

OLP

OH

OH

OH

OL

OL

±I

±I

C

C

C

xtal

NOTE:

1. REF output limit is 100 mA.

HIGH level input voltage 3.135 to 3.465 2.0 — VDD+0.3 V

IH

LOW level input voltage 3.135 to 3.465 VSS–0.3 — 0.8 V

IL

3.3 V output HIGH voltage

REF, 48M

3.3 V output LOW voltage

REF, 48M

3.3 V output HIGH voltage

3V66/PCI

3.3 V output LOW voltage

3V66/PCI

Output HIGH current

3V66/PCI

Output HIGH current

48 MHz, REF

Output HIGH current

HOST/HOST_BAR

Output LOW current

3V66/PCI

Output LOW current

48 MHz, REF

Input leakage current 3.465 0 < VIN < V

I

3-State output

OZ

OFF-State current

Input pin capacitance — — 5 pF

in

Output pin capacitance — — 6 pF

out

3.135 to 3.465 IOH = –1 mA 2.0 — — V

3.135 to 3.465 IOH = 1 mA — — 0.4 V

3.135 to 3.465 IOH = –1 mA 2.4 — — V

3.135 to 3.465 IOH = 1 mA — — 0.55 V

3.135 V

3.465 V

3.135 V

3.465 V

OUT

= 3.135 V

OUT

OUT

= 3.135 V

OUT

= 1.0 V

= 1.0 V

0.66 V

0.76 V

3.135 V

3.465 V

3.135 V

3.465 V

= 0

SS

3.465

= 1.95 V

OUT

= 0.4 V

OUT

= 1.95 V

OUT

= 0.4 V

OUT

RS = 33.2 Ω

RP = 49.9 Ω

DD3

V

=

OUT

VDD or GND

Crystal input capacitance 13.5 — 22.5 pF

Type 5

12 – 55 Ω

Type 3

20 – 60 Ω

p

Type 5

12 – 55 Ω

Type 3

20 – 60 Ω

p

–33 — — mA

— — –33 mA

–29 — — mA

— — –23 mA

11 — — mA

— — 12.7 mA

30 — — mA

— — 38 mA

29 — — mA

— — 27 mA

— —

–50 — 50 µA

IO = 0 — — 10

PCK2021

1

µA

2001 Oct 1 1

7

Page 8

Philips Semiconductors Product data

SYMBOL

PARAMETER

UNITS

NOTES

CK00 (100/133 MHz) spread spectrum differential

PCK2021

system clock generator

AC ELECTRICAL CHARACTERISTICS

V

= 3.3 V ±5%; f

DD3

Host clock outputs

T

= 0 to +70 °C; see Figure 1 for waveforms and Figure 6 for test setup.

amb

SYMBOL PARAMETER

t

PERIOD

Abs Min Period Absolute minimum host clock period 7.35 N/A 9.85 N/A ns 11, 14, 19

t

RISE

t

FALL

t

JITTER

DUTY CYCLE Output duty cycle 45 55 45 55 % 11, 14, 19

t

SKEW

V

crossover

REFER TO NOTES ON PAGE 10.

USB clock output, 48MHz

T

= 0 to +70 °C; lump capacitance test load = 20 pF

amb

SYMBOL PARAMETER

f Frequency, actual 48.000 MHz 4

f

D

t

RISE

t

FALL

t

JITTER

DUTY CYCLE Output duty cycle 45 55 % 17, 19

REFER TO NOTES ON PAGE 10.

= 14.31818 MHz

crystal

LIMITS

133 MHz MODE 100 MHz MODE

UNITS NOTES

MIN MAX MIN MAX

HOST CLK average period 7.5 7.65 10.0 10.2 ns 11, 14, 19

HOST CLK rise time 175 700 175 700 ns 11, 15, 19

HOST CLK fall time 175 700 175 700 ps 11, 15, 19

HOST_CLK cycle-to-cycle jitter — 150 — 150 ps 11, 12, 14, 19

HOST CLK pin-to-pin skew — 150 — 110 ps 11, 14, 19

45% V

OH

55% V

OH

45% V

OH

55% V

OH

V 11, 14, 19

LIMITS

48 MHz MODE

UNITS NOTES

MIN MAX

Deviation from 48 MHz –0 +167 ppm 4

3V48MHZCLK rise time 1.0 4.0 ns 8, 19

3V48MHZCLK fall time 1.0 4.0 ns 8, 19

Cycle-to-cycle jitter — 450 ps 17, 19

PCI Outputs

T

= 0 to +70 °C

amb

LIMITS

MIN MAX

t

PERIOD

t

HIGH

t

LOW

t

RISE

t

FALL

DUTY CYCLE Duty cycle 45 55 % 17, 19

t

JITTER

t

SKEW

REFER TO NOTES ON PAGE 10.

2001 Oct 1 1

Period 30.0 N/A ns 2, 3, 9, 19

High time 12.0 N/A ns 5, 10, 19

Low time 12.0 N/A ns 6, 10, 19

Rise time 0.5 2.0 ns 8, 19

Fall time 0.5 2.0 ns 17, 19

Cycle-to-cycle jitter — 200 ps 17, 19

Pin-to-pin skew — 150 ps 2

8

Page 9

Philips Semiconductors Product data

SYMBOL

PARAMETER

UNITS

NOTES

CK00 (100/133 MHz) spread spectrum differential

PCK2021

system clock generator

3V66 Outputs

T

= 0 to +70 °C

amb

LIMITS

MIN MAX

t

PERIOD

t

HIGH

t

LOW

t

RISE

t

FALL

DUTY CYCLE Duty cycle 45 55 % 17, 19

t

JITTER

REFER TO NOTES ON PAGE 10.

REF clock output

T

= 0 to +70 °C; lump capacitance test load = 20 pF

amb

SYMBOL PARAMETER

f Frequency, actual 14.318 MHz 16, 19

t

JITTER

DUTY CYCLE Output duty cycle 45 55 % 17, 19

REFER TO NOTES ON PAGE 10.

Period 15.0 16.0 ns 2, 3, 9, 19

High time 5.25 N/A ns 5, 10, 19

Low time 5.05 N/A ns 6, 10, 19

Rise time 0.5 2.0 ns 8, 19

Fall time 0.5 2.0 ns 17, 19

Cycle-to-cycle jitter — 400 ps 17, 19

LIMITS

48 MHz MODE

MIN MAX

Cycle-to-cycle jitter — 300 ps 17, 19

UNITS NOTES

All outputs

T

= 0 to +70 °C

amb

SYMBOL PARAMETER

t

, t

PZL

PZH

t

, t

PZL

PZH

t

STABLE

REFER TO NOTES ON PAGE 10.

Output enable delay (all outputs) 1.0 10.0 1.0 10.0 ns 19

Output disable delay (all outputs) 1.0 10.0 1.0 10.0 ns 19

All clock stabilization from power-up — 3 — 3 ms 7, 19

LIMITS

133 MHz MODE 100 MHz MODE

MIN MAX MIN MAX

UNITS NOTES

2001 Oct 1 1

9

Page 10

Philips Semiconductors Product data

CK00 (100/133 MHz) spread spectrum differential

PCK2021

system clock generator

Group offset limits

GROUP OFFSET

3V66 to PCI 0–500 ps, 3V66 leads 30 pF 1.5 V 18, 19

NOTES TO THE AC TABLES:

1. Output drivers must have monotonic rise/fall times through the specified V

2. Period, jitter, offset, and skew measured on rising edge at 1.5 V for 3.3 V clocks.

3. PCI is a fixed 33 MHz and 3V66 is a fixed 66 MHz.

4. Frequency accuracy of 48 MHz must be +167 ppm to match USB default.

5. t

6. t

7. the time is specified from when V

8. t

9. The average period over any 1 µs period of time must be greater than the minimum specified period.

10.Calculated at minimum edge rate (1 V/ns) to guarantee 45–55% duty cycle. Pulse width is required to be wider at faster edge rate to ensure

11.Test load is R

12.Must be guaranteed in a realistic system environment.

13.Configured for V

14.Measured at crossing points.

15.Measured at 20% to 80%.

16.Frequency generated by crystal oscillator

17.Voltage measure point (V

18.All offsets are to be measured at rising edges.

19.Parameters are guaranteed by design.

is measured at 2.4 V for 3.3 V outputs, as shown in Figure 7.

HIGH

is measured at 0.4 V for all outputs as shown in Figure 7.

LOW

and operating within specification.

and t

RISE

duty specification is met.

are measured as a transition through the threshold region VOL = 0.4 V and VOH = 2.4 V (1 mA) JEDEC specification.

FALL

= 33.2 Ω, RP = 49.9 Ω.

S

= 0.71 V in a 50 Ω environment.

OH

= 1.5 V).

M

achieves its normal operating level (typical condition V

DDQ

MEASUREMENT LOADS

(LUMPED)

levels.

OL/VOH

MEASUREMENT POINTS NOTES

= 3.3 V) until the frequency output is stable

DDQ

2001 Oct 1 1

10

Page 11

Philips Semiconductors Product data

CK00 (100/133 MHz) spread spectrum differential

system clock generator

AC WAVEFORMS

VM = 1.25 V @ V

VX = VOL + 0.3 V

= VOH – 0.3 V

V

Y

V

and VOH are the typical output voltage drop that occur with the output load.

OL

HOST CLK

COMPONENT

MEASUREMENT

POINTS

and 1.5 V @ V

DDL

50%

t

PERIOD

DD3

Figure 1. HOST CLOCK

V

1.5 V

V

IL

DDL

= 2.0 V

V

IH

= 0.7 V

V

OL

= 0.4 V

VOH = 2.4 V

V

SS

Figure 2. 3.3 V clock waveforms

50%

SYSTEM

MEASUREMENT

POINTS

V

OH

V

SS

SW00962

SW00668

V

SEL1,

SEL0

GND

V

DD

OUTPUT

LOW-to-OFF

OFF-to-LOW

V

OL

V

OH

OUTPUT

HIGH-to-OFF

OFF-to-HIGH

V

SS

I

V

M

t

PLZ

V

X

t

PHZ

V

Y

outputs

enabled

outputs

disabled

Figure 3. State enable and disable times

PCK2021

t

PZL

V

M

t

PZH

V

M

outputs

enabled

SW00662

PULSE

GENERATOR

V

DD

V

I

DUT

R

T

TEST S

t

PLH/tPHL

t

PLZ/tPZL

t

PHZ/tPZH

VDD = V

Open

2 V

DD3

V

O

C

L

1

DD

V

SS

Figure 4. Load circuitry for switching times

S

1

500 Ω

500 Ω

2 V

Open

V

SS

SW00963

DD

2001 Oct 1 1

11

Page 12

Philips Semiconductors Product data

CK00 (100/133 MHz) spread spectrum differential

system clock generator

PWRDWN

HOST CLK

(INTERNAL)

PCICLK

(INTERNAL)

PWRDWN

HOST CLK

(EXTERNAL)

PCICLK

(EXTERNAL)

OSC & VCO

USB (48 MHz)

Figure 5. Power management

PCK2021

SW00669

3.3V CLOCKING

INTERFACE

CRYSTAL

14.318 MHz

t

PERIOD

DUTY CYCLE

t

HIGH

2.4 V

1.5 V

0.4 V

t

t

RISE

t

LOW

FALL

Figure 7. 3.3 V clock waveforms

V

DD

C

L

C

L

HOST

DUT

HOST_BAR

R

S

RS = 33.2 Ω

R

S

Figure 6. HOST CLOCK measurements

SW00943

RP = 50 Ω

= 50 Ω

R

P

SW00671

2001 Oct 1 1

12

Page 13

Philips Semiconductors Product data

CK00 (100/133 MHz) spread spectrum differential

PCK2021

system clock generator

TSSOP48: plastic thin shrink small outline package; 48 leads; body width 6.1 mm SOT362-1

2001 Oct 1 1

13

Page 14

Philips Semiconductors Product data

CK00 (100/133 MHz) spread spectrum differential

PCK2021

system clock generator

SSOP48: plastic shrink small outline package; 48 leads; body width 7.5 mm SOT370-1

2001 Oct 1 1

14

Page 15

Philips Semiconductors Product data

CK00 (100/133 MHz) spread spectrum differential

PCK2021

system clock generator

Data sheet status

Product

Data sheet status

Objective data

Preliminary data

Product data

[1] Please consult the most recently issued data sheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL

http://www.semiconductors.philips.com.

[1]

status

Development

Qualification

Production

[2]

Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For

detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or

at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended

periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips

Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or

modification.

Disclaimers

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can

reasonably be expected to result in personal injury . Philips Semiconductors customers using or selling these products for use in such applications

do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard

cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no

responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these

products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless

otherwise specified.

Contact information

For additional information please visit

http://www.semiconductors.philips.com . Fax: +31 40 27 24825

For sales offices addresses send e-mail to:

sales.addresses@www.semiconductors.philips.com.

Definitions

This data sheet contains data from the objective specification for product development.

Philips Semiconductors reserves the right to change the specification in any manner without notice.

This data sheet contains data from the preliminary specification. Supplementary data will be

published at a later date. Philips Semiconductors reserves the right to change the specification

without notice, in order to improve the design and supply the best possible product.

This data sheet contains data from the product specification. Philips Semiconductors reserves the

right to make changes at any time in order to improve the design, manufacturing and supply.

Changes will be communicated according to the Customer Product/Process Change Notification

(CPCN) procedure SNW-SQ-650A.

Koninklijke Philips Electronics N.V. 2001

All rights reserved. Printed in U.S.A.

Date of release: 10-01

Document order number: 9397 750 08953

2001 Oct 1 1

15

Loading...

Loading...