Page 1

1

- January 1998

Highlights

www.national.com

©

1998 National Semiconductor Corporation

PRELIMINARY

April 1998

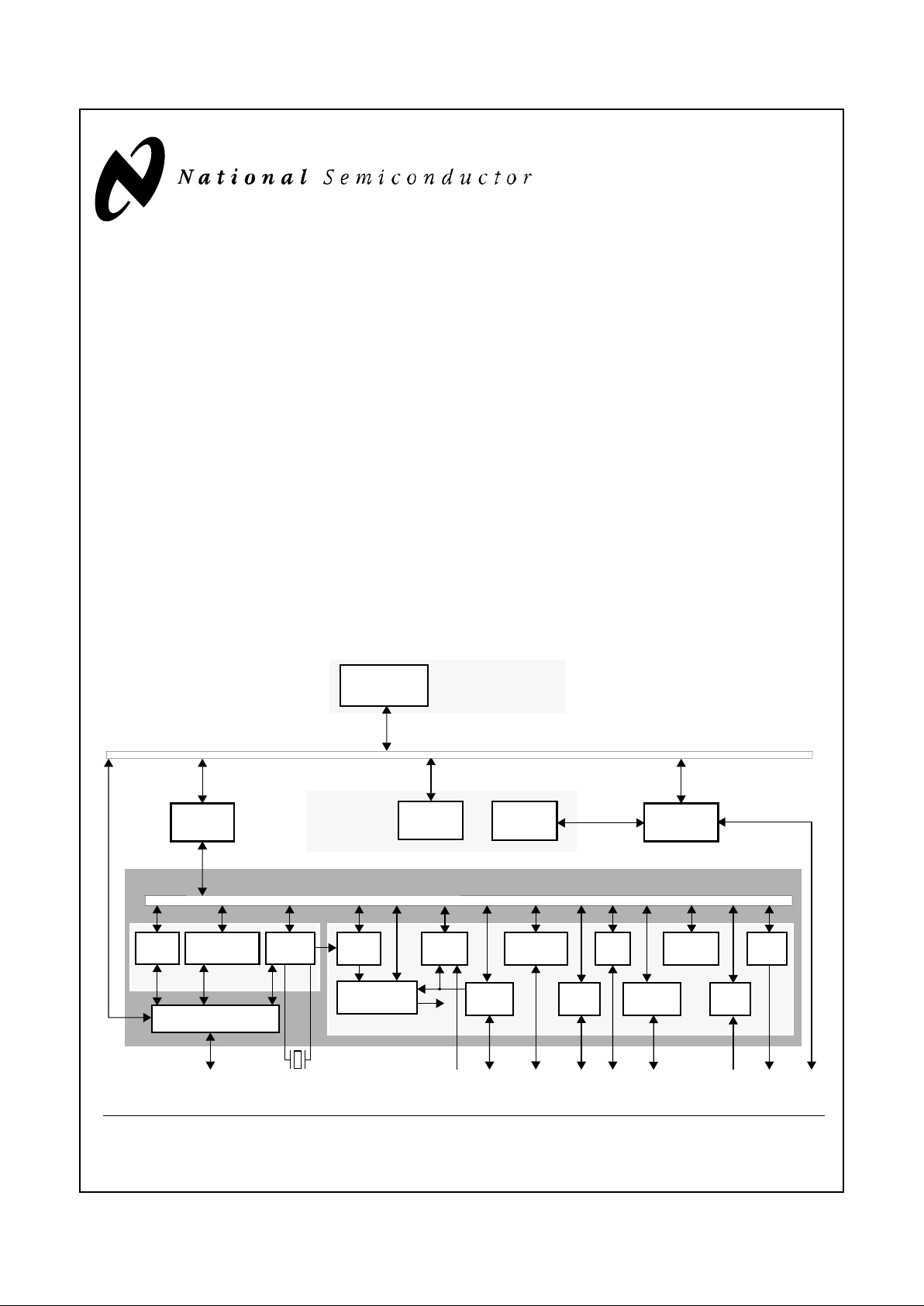

PC87570 Keyboard and Power Management Controller

Highlights

General Description

The PC87570 is a highly integrated embedded RISC-based

controller optimized for power management (PM), keyboard

and mouse (KBC) and system control in portable Personal

Computer (PC) applications.

The PC87570 incorporates National’s CompactRISC

CR16A core, a high performance 16-bit RISC processor

core, a Bus Interface Unit (BIU) that directly interfaces with

memory and I/O devices, on-chip memory and system support functions. Among these are legacy functions, handled

by the Host Bus Interface (HBI), that include the Real-Time

Clock and Advanced Power Control (RTC and APC), and

peripherals, including: frequency-multiplier-based High Frequency Clock Generator (HFCG), Power Mode Control

(PMC), Interrupt Control Unit (ICU), Multi-Input Wake-Up

(MIWU), General Purpose I/O Ports (GPIO) with internal

keyboard matrix scanning, PS/2

®

Interface, ACCESS.bus

®

(ACB) Interface, two Multi-Function 16-Bit Timers (MFT16),

periodic interrupt timer and WATCHDOG (TWD), ADC

and DAC.

The PC87570 highly efficient architecture and its on-chip

peripherals, supporting functions and low power consumption, provide a highly integrated solution for portable notebook PCs, sub-notebook PCs and other portable devices.

Outstanding Features

●

Shared BIOS memory

●

Fully ACPI-compliant embedded controller

●

Proprietary PS/2 shift mechanism

●

Extremely low current consumption in Idle mode

●

Support for a variety of off-chip wake-up sources

●

Scalable design for growth without controller upgrade

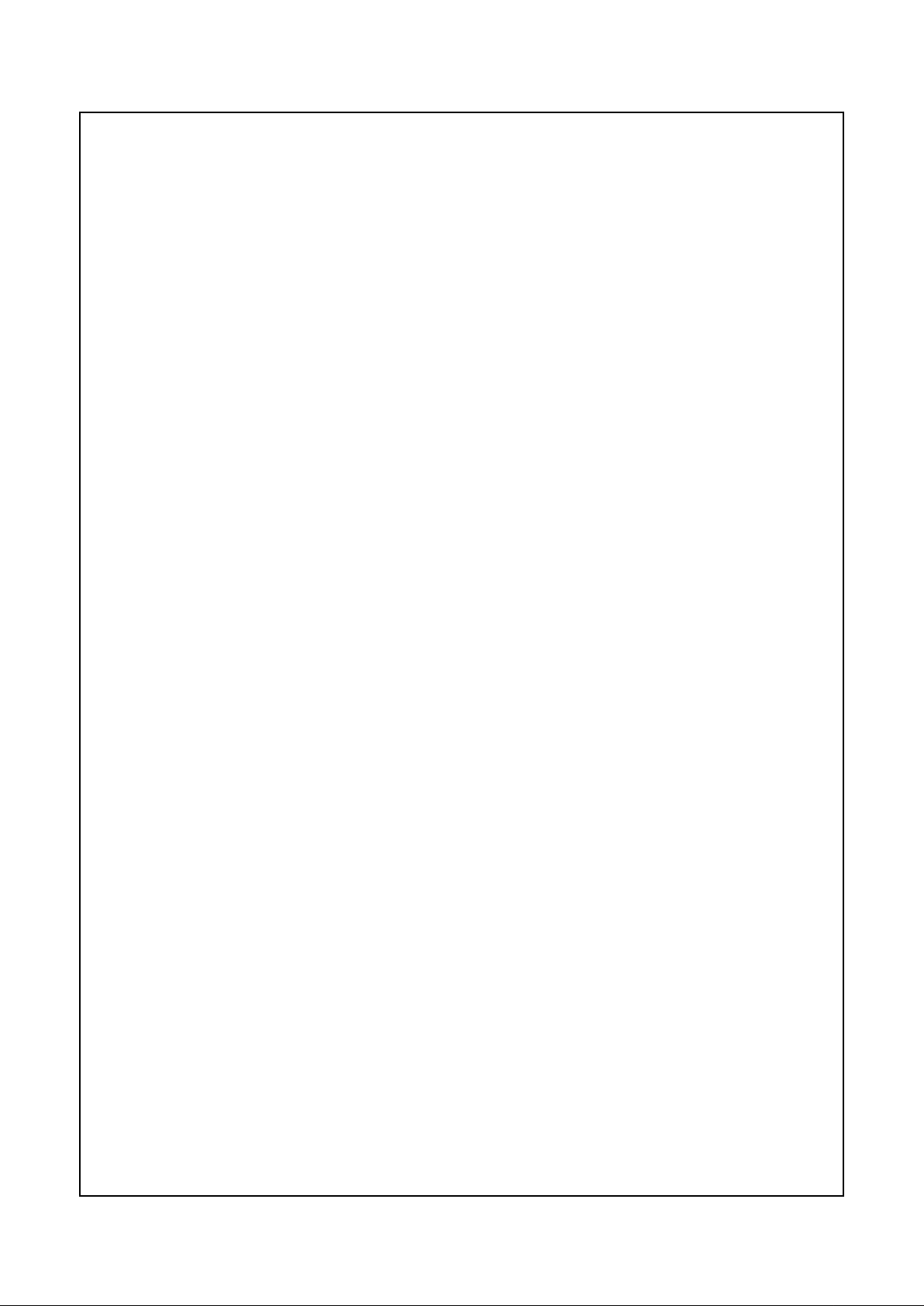

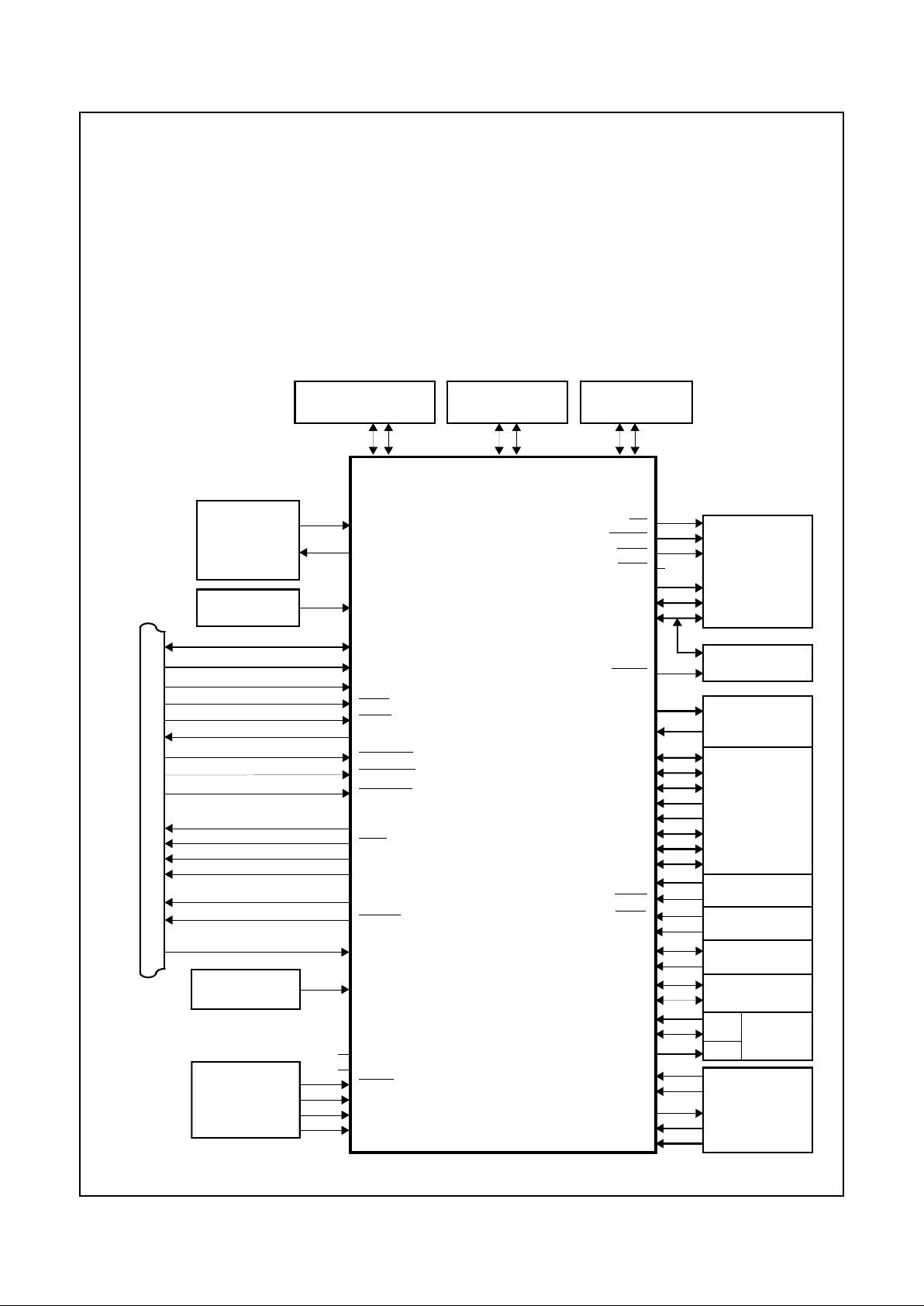

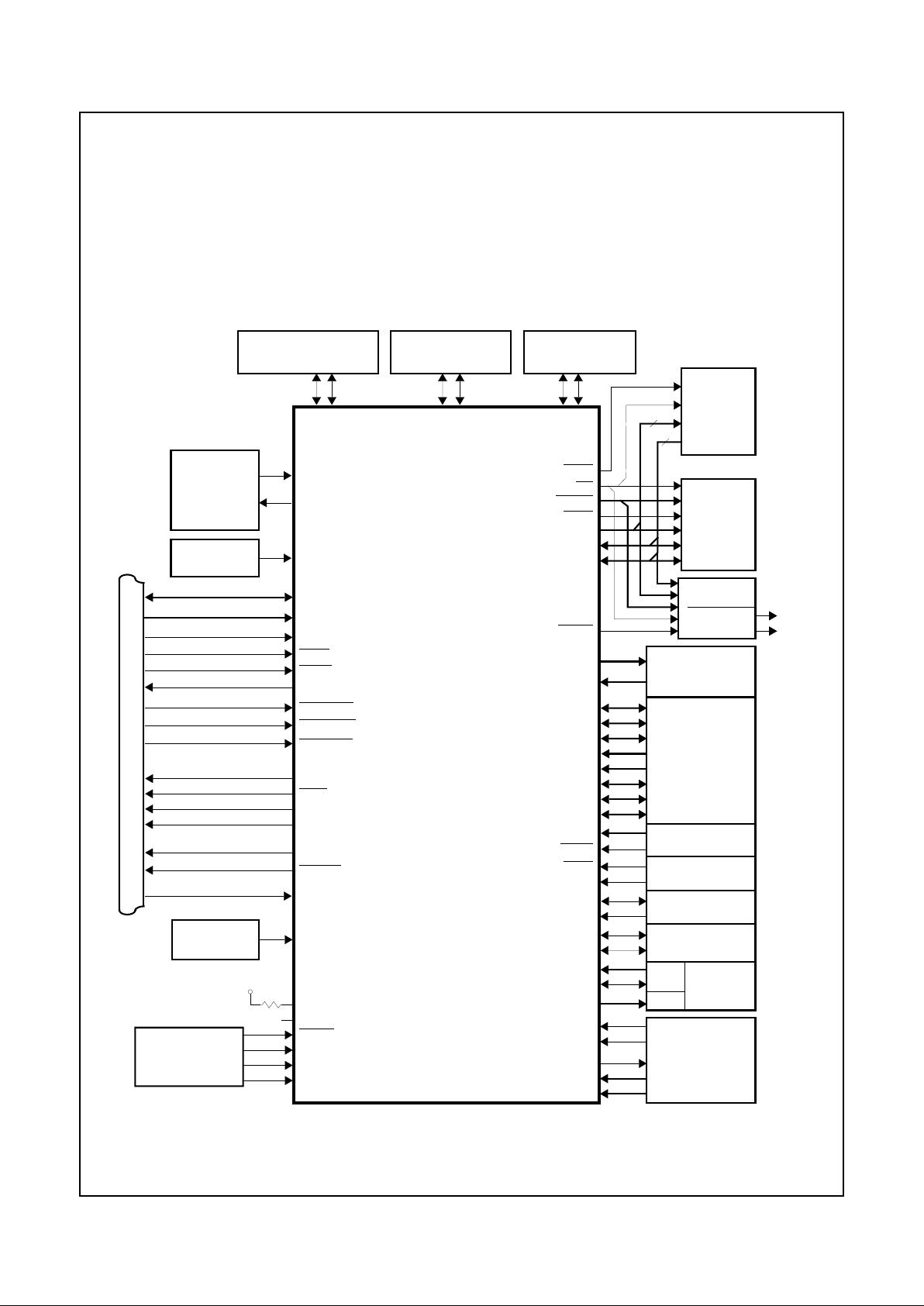

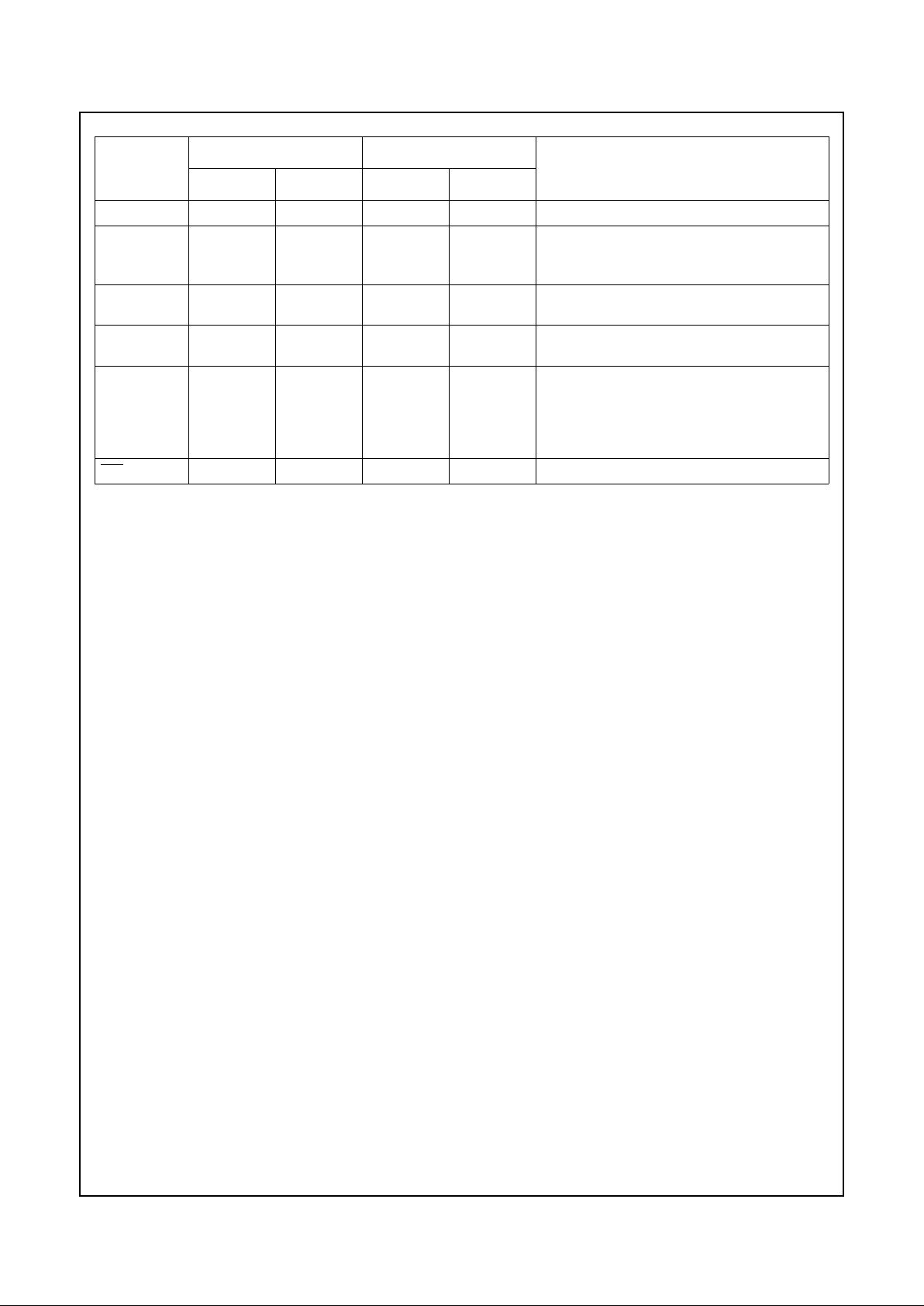

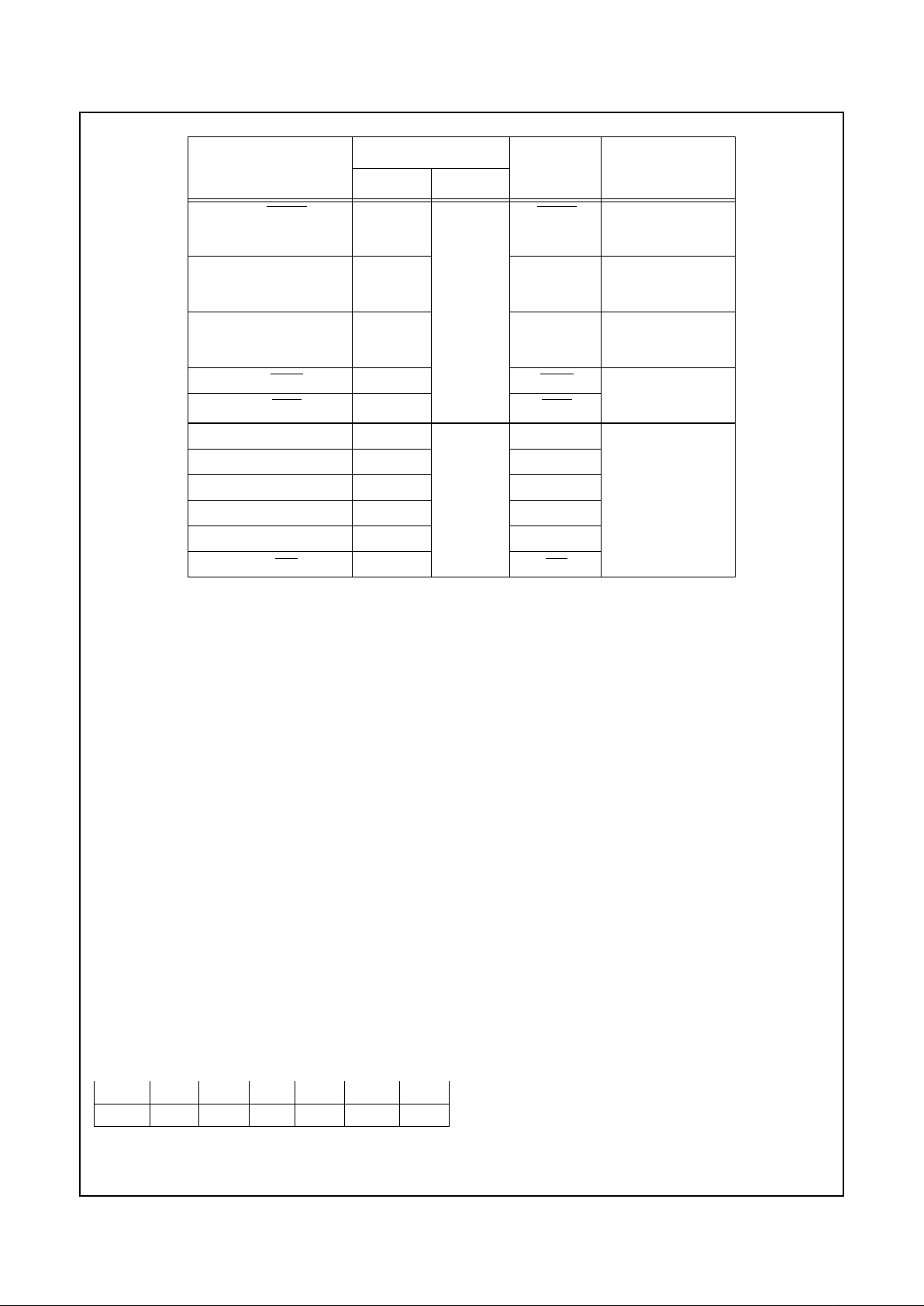

Block Diagram

Core Bus

Peripheral Bus

Bus

KBC + PM

Host I/F

RTC +

Processing

Unit

HBI

Host Bus

APC

Host

Config

RAM

Memory

External

BIU

CR16A Core

32.768

ICU

HFCG

PMC

ADC

KBSCAN

ACB

GPIO

WDG

Peripherals

Legacy

ROM

MIWU

IBM®, PC-AT® and PS/2® are registered trademarks of International Business Machines Corporation.

CompactRISC

TM

, WATCHDOGTM and TRI-STATE® are trademarks of National Semiconductor Corporation.

ACCESS.bus® is a registered trademark of Digital Equipment Corporation.

I

2C®

is a registered trademark of Philips.

Memory

(ISA Compatible)

MFT16

Timer +

KHz

Adapter

PS/2

I/F

I/F

CLK

DAC

+ I/O

(X2)

Page 2

2

Highlights

www.national.com

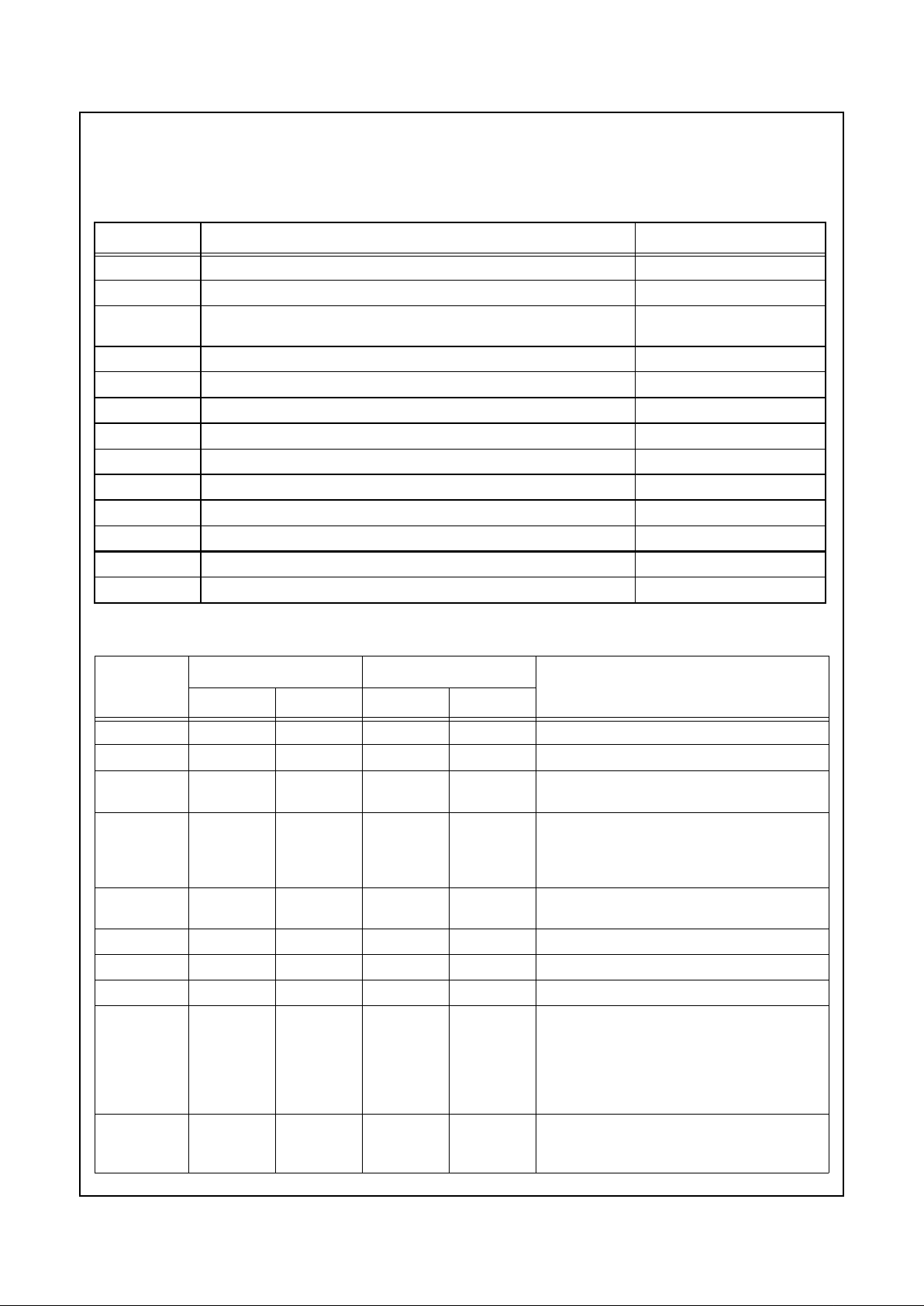

Features

• CR16A Core

— 16-bit embedded RISC processor core

• Bus Interface Unit (BIU)

— Three address zones for static devices (SRAM,

ROM FLASH, I/O)

— Configurable wait states and fast read bus cycles

• Internal Memory

— 2048 bytes of on-chip ROM

— 1024 bytes of on-chip RAM

— All memories can hold both code and data

• External Memory

— Supports BIOS memory (Flash) sharing with PC host

— Up to 56 Kbyte for code and data

— Field upgradable with Flash or SRAM devices

— Supports host controlled code download and update

• Host Bus Interface (HBI)

— Three host interface channels, typically used for the

KBC, PM and RTC devices

— Motherboard Plug and Play (PnP) configuration

o With Enable and Lock bits for each device

o Relocatable address for each device

— Host power supply indicator input pin

— 8042 KBC standard Interface (60h, 64h)

— Intel 80C51SL compatible

— IRQ1 and IRQ12 support

— Fast Gate A20 and Fast host Reset, via firmware

— PM interface port (62h, 66h)

— PM port IRQ11

• Real-Time Clock (RTC) and Advanced Power Control

(APC)

— RTC

o DS1287, MC146818 and PC87911 compatible

o 242 bytes battery backed-up CMOS RAM

o Calendar including century and automatic leap-

year adjustment

o Optional daylight saving adjustment

o BCD or binary format for timekeeping

o Three individually maskable interrupt event

flags: periodic rates from 122 µs to 500 ms; timeof-day alarm, once per second to once per day

o Separate backup battery pin

o Double buffer time registers

o The CMOS RAM and the RTC registers can be

accessed by the CR16A firmware

— APC

o Alarm wake-up

o Hardware wake-up events

o Software off events

• HFCG

— On-chip frequency multiplier

— Single 32.786KHz crystal

— Software controlled frequency generation

• PMC

— 3.3 and 5V operation with mixed voltage system

support

— Reduced power consumption capability

— Back-drive protection

— Three power modes, switched by software or hard-

ware:

o Active mode operating frequency 4-10MHz

o Idle (20 µA)

o Power Off - RTC only (0.9 µA typical) from back-

up battery

— Automatic wake-up on system events

• ICU

— 16 maskable interrupt sources

— Four general purpose external interrupt inputs

— Programmable trigger mode (level: high or low,

edge: falling or rising)

— Enable and pending indication for each interrupt

— Non-maskable interrupt input

• MIWU

— Supports up to 24 wake-up or interrupt inputs

— Generates wake-up to PMC

— Generates interrupts to ICU

— Provides user-selectable trigger conditions

• GPIO

— 76 ports

— I/O pins individually configured as input or output

— Configurable internal pull-up resistors

— Special ports for internal keyboard matrix scanning

o 16 open-collector outputs

o 8 Schmidt inputs with internal pull-up

— Special input for system On/Off switch

— Supports very low-cost implementation of additional

off-chip I/O ports

• PS/2 Interface

— Supports three independent devices (external KBC,

mouse and additional pointing device)

— Supports byte lev el handling via hardware accelerator

• ACB Interface

— Intel SMBus and Philips I

2C®

compatible

— ACCESS.bus master and slave

— Supports polling and interrupt controlled operation

— Generates a wake-up signal on detection of a Start

Condition, while in power-down mode

— Optional internal pull-up on SDA and SCL pins

Page 3

3

Highlights

www.national.com

• MFT16

— Two 16-bit timers

— Each timer supports Pulse Width Modulator (PWM),

Capture and Counter capabilities

• TWD

— 16-bit periodic interrupt timer with 30-µs resolution

and 5-bit prescaler, for system tick and periodic

wake-up tasks

— 8-bit WATCHDOG timer

• ADC

— Eight channels, 8-bit resolution

— 10 µs conversion/channel

— Internal or external voltage reference

• DAC

— Four channels, 8-bit resolution

— 1 µs conversion time for 50 pF load

— Full output range from AGND to AVCC

• Supports Microsoft Advanced Power Management

(APM) specifications revision 1.2, February 1996

— Generates the System Management Interrupt (SMI)

• 160-pin PQFP and 176-pin TQFP packages

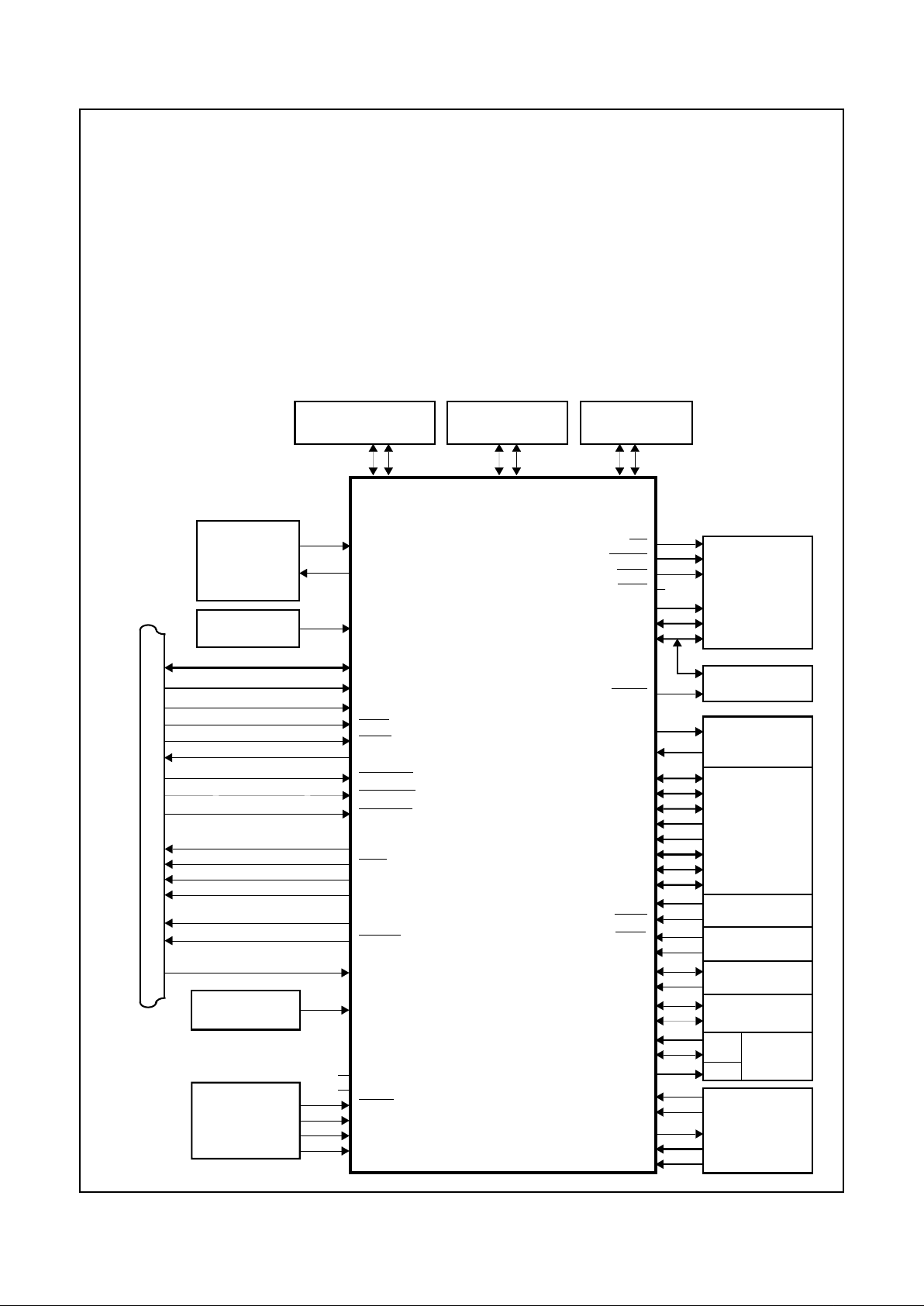

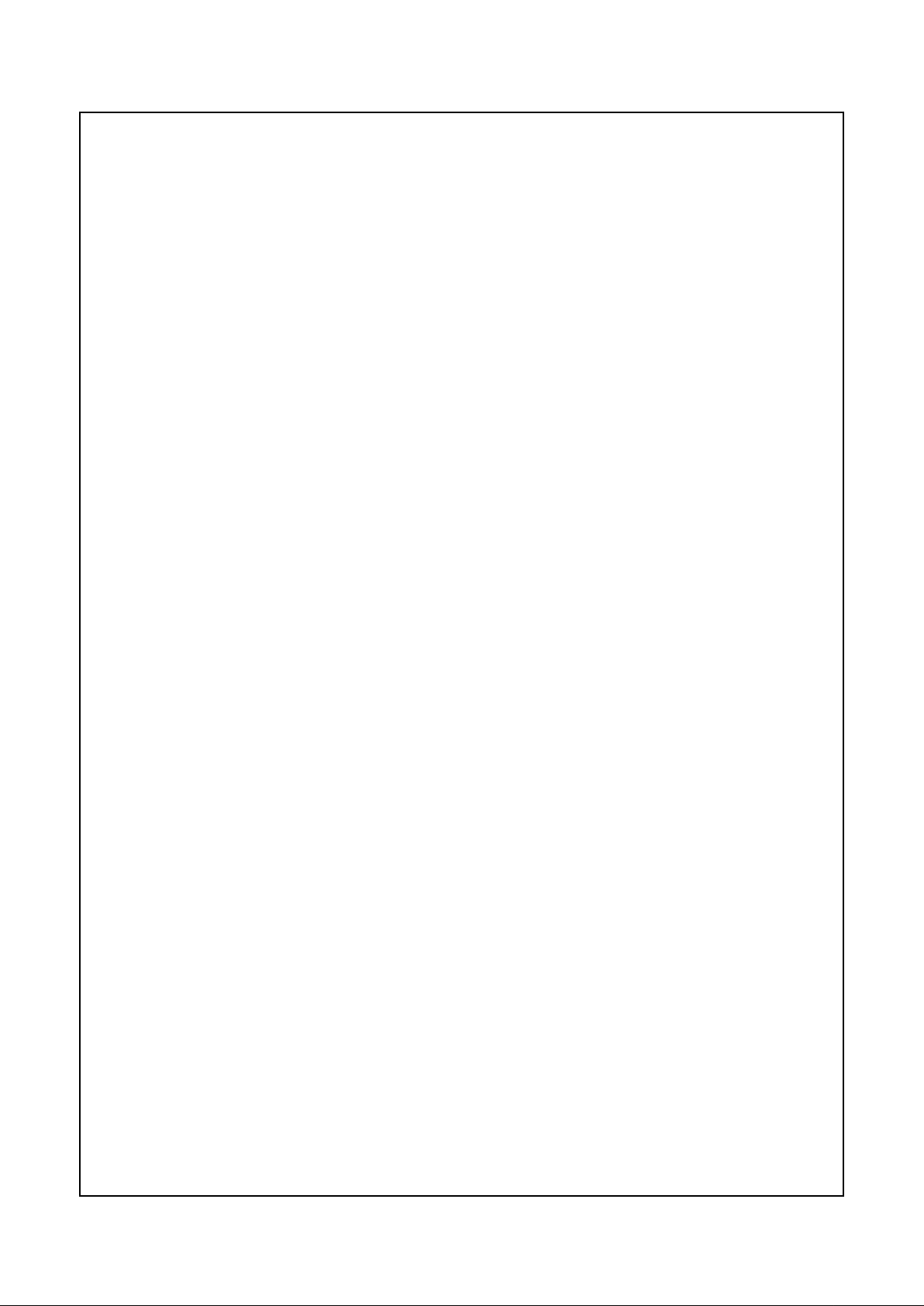

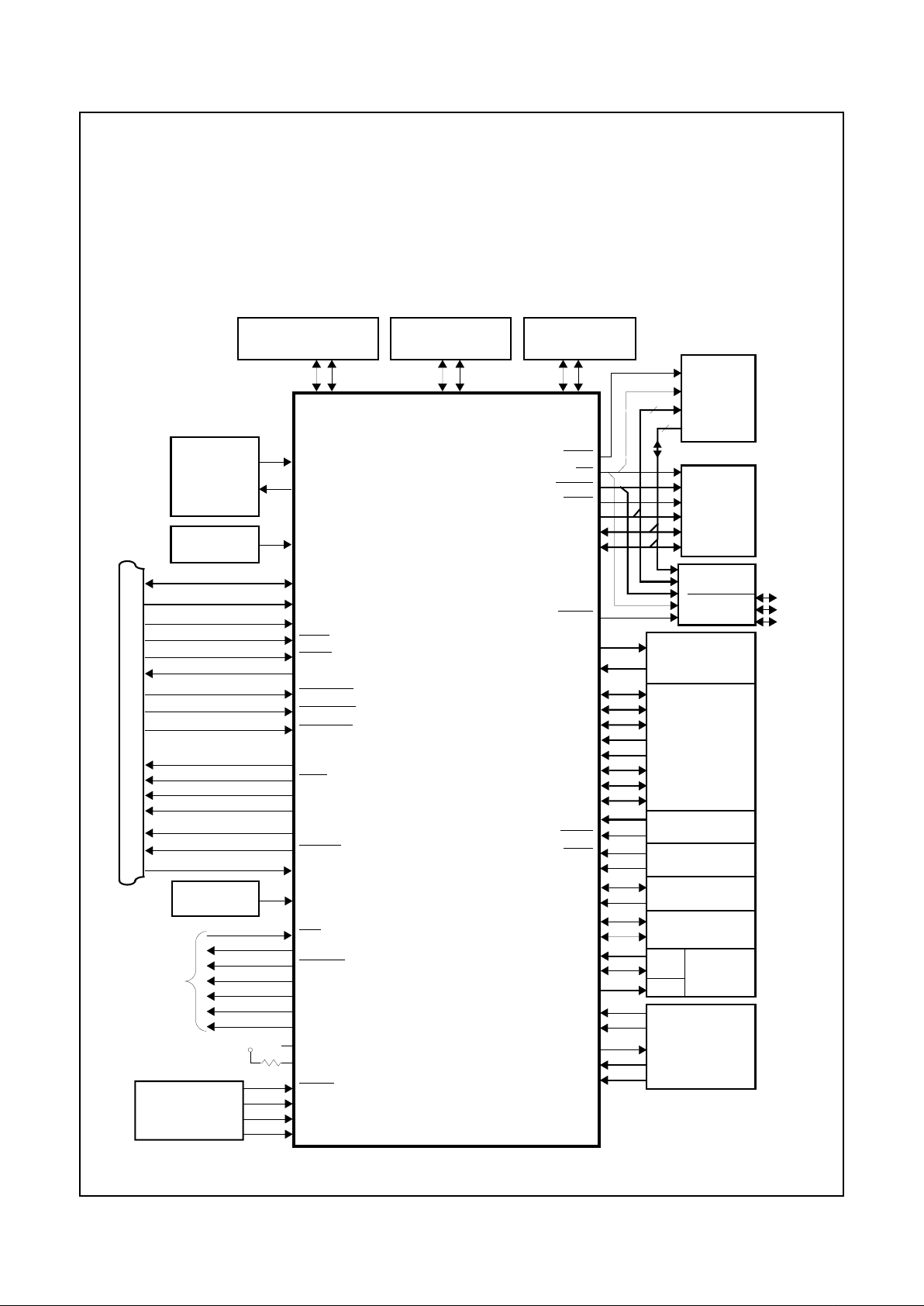

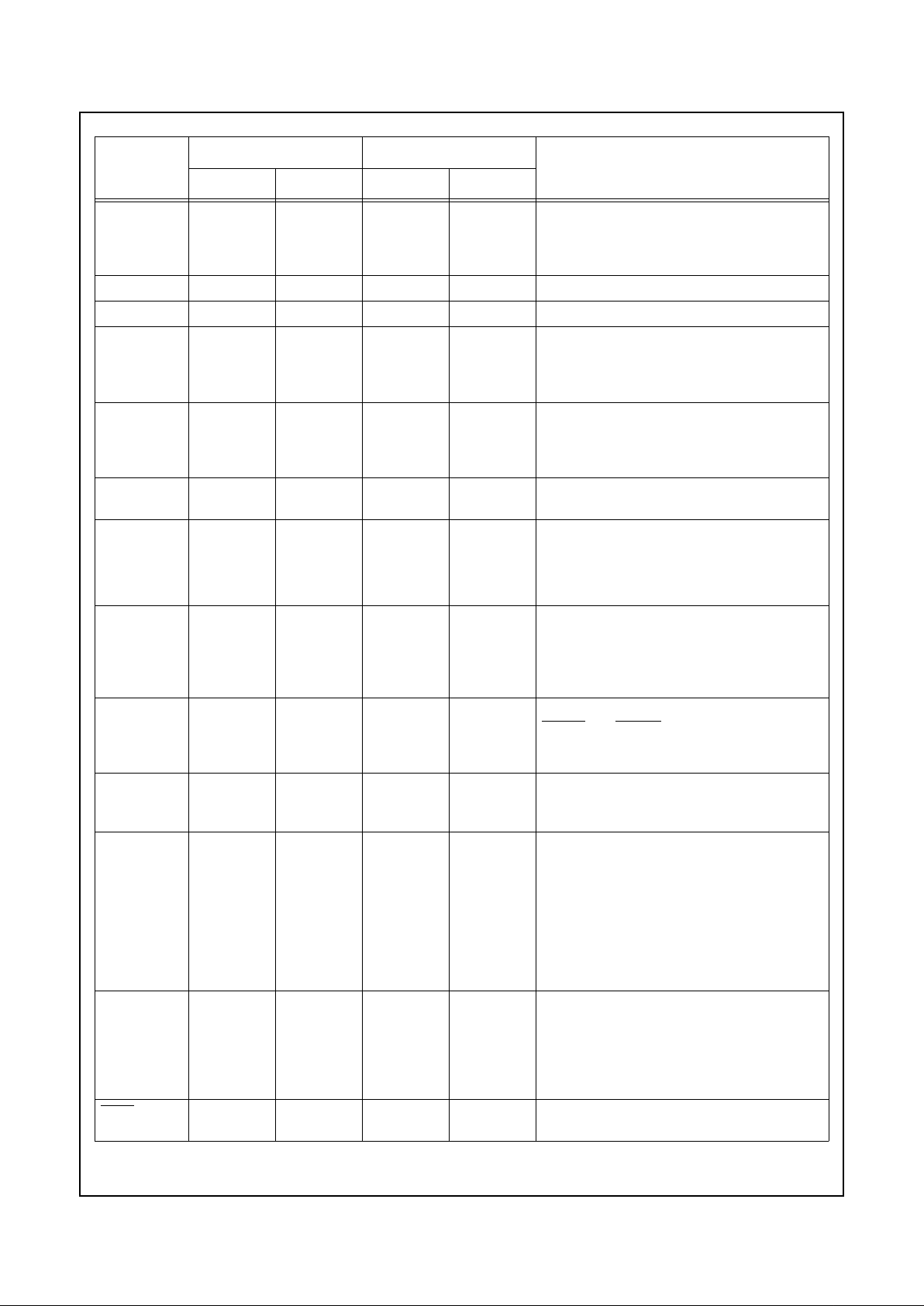

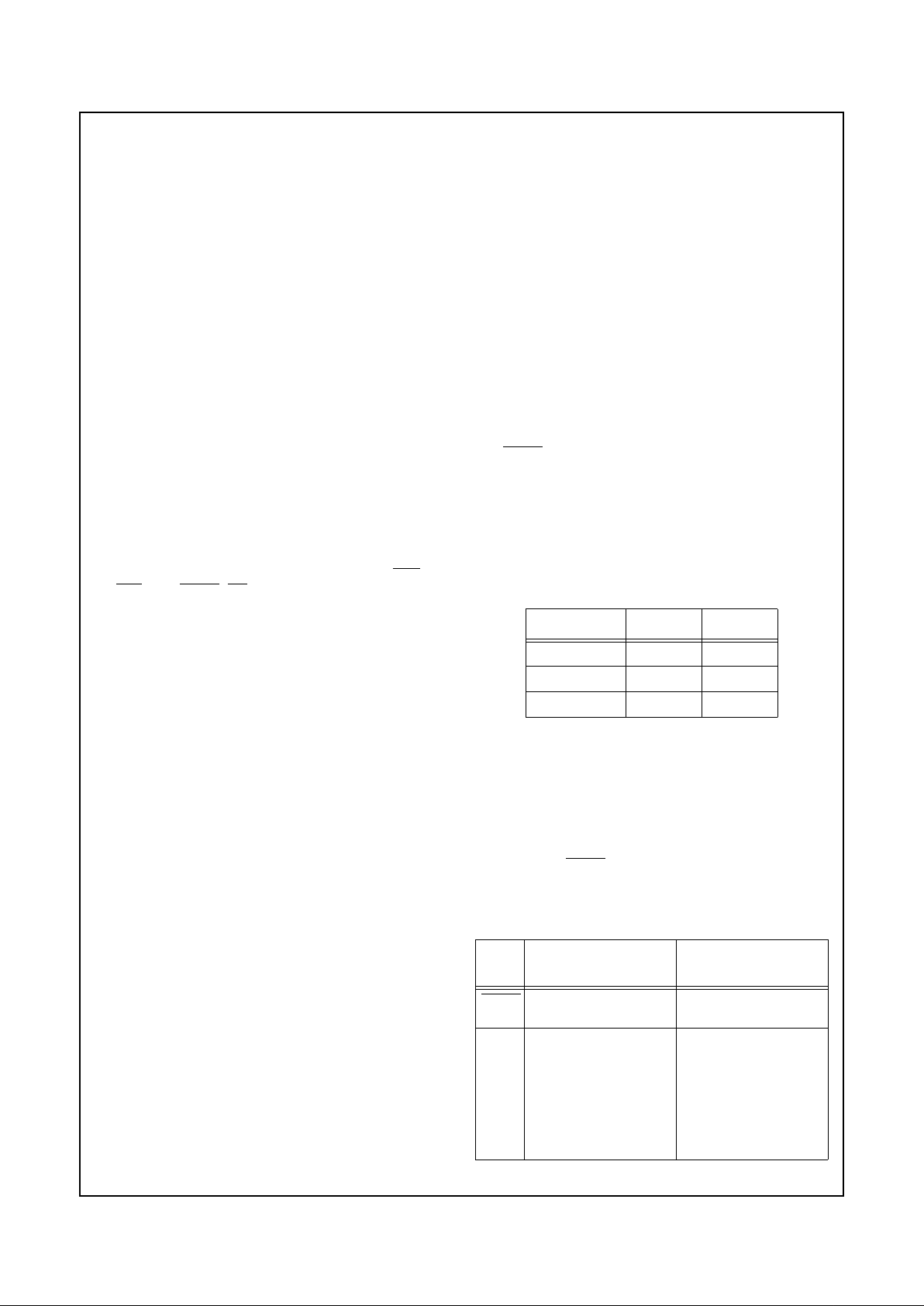

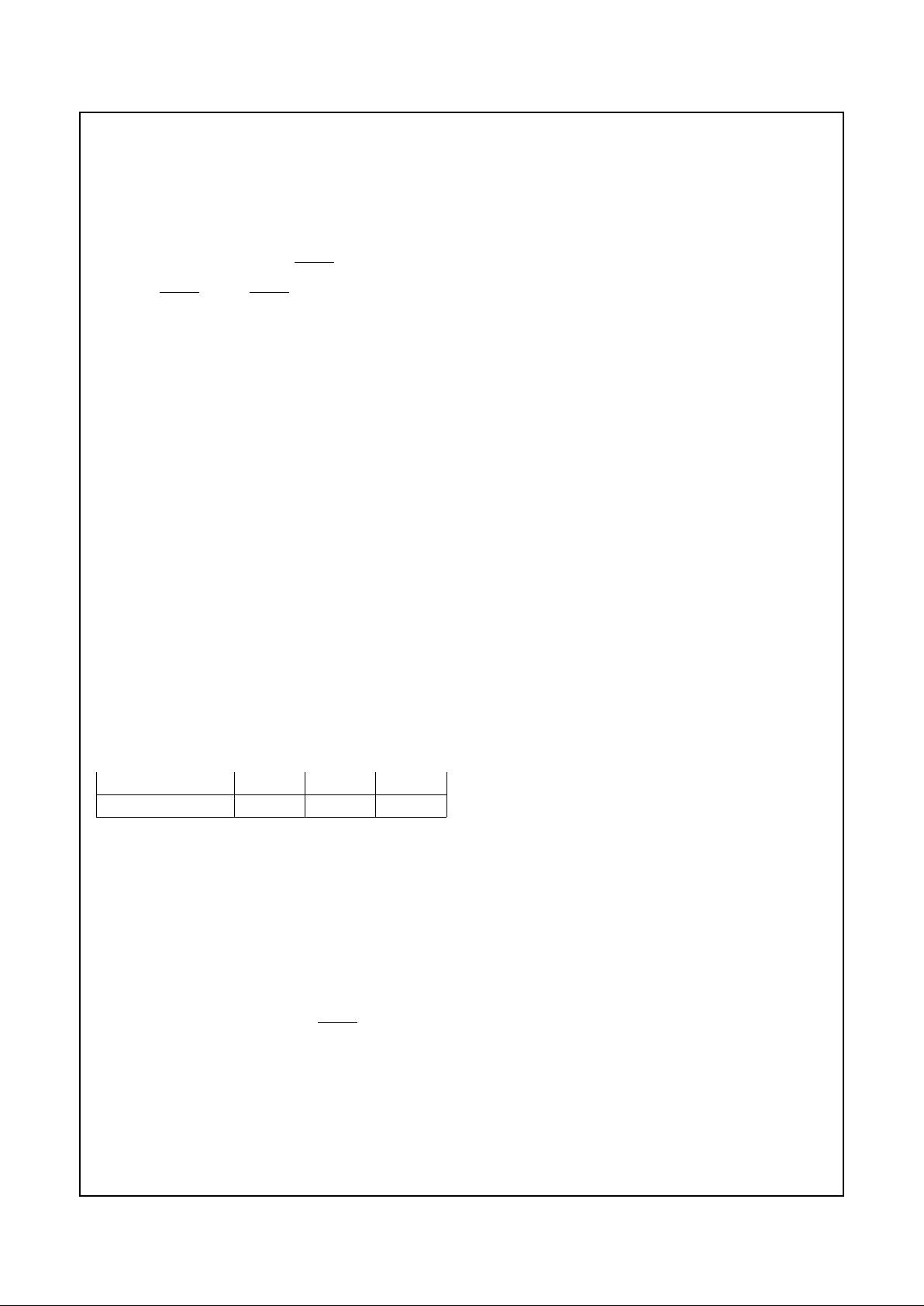

Basic Configuration

or

Clock

External

Memory

PC87570

Host System Bus (ISA Compatible)

32KX1/32KCLKIN

32KX2

HMR

HA18-0

HD7-0

HIOR

HIOW

IRQ1

IRQ11

IRQ12

RD

WR1-0

SEL0

A18-16, A15-0

D15-8

AD7-0

DA3-0

PA6-0

PB7-0

PC7-0

PD7-0

HIOCHRDY

RTC

Battery

V

BAT

IRQ8

PSCLK1

PSDAT1

Crystal

32.768 KHz

External Keyboard

Internal

Keyboard

KBSOUT15-0

KBSIN7-0

SRAM or

Flash

ENV0

GA20

AVCC

AGND

VCC

GND

Power

Supply

SCL

D7-0

HMEMRD

HMEMWR

PSCLK2

PSDAT2

PSCLK3

PSDAT3

PG4-0

PE1-0

PF7-0

PH5-0

HMEMCS

HAEN

EXINT0,10,11,15

PFAIL

RING

SHBM

HRMS

Configuration

Inputs

I/O

Expansion

TA

HDEN

TRIS

HPWRON

PC0

External Mouse

Auxiliary PS/2

Interface

Interface

Interface

HRSTO

SELIO

(Matrix)

SDA

TB

SWIN

Analog

Reset

Control

(power-up reset)

GPIO

Interrupt

ACCESS.bus

System

Timers

ENV1

NC

NC

SEL1

NC

(Application)

V

REF

ADC

DAC

Page 4

4

Table of Contents

www.national.com

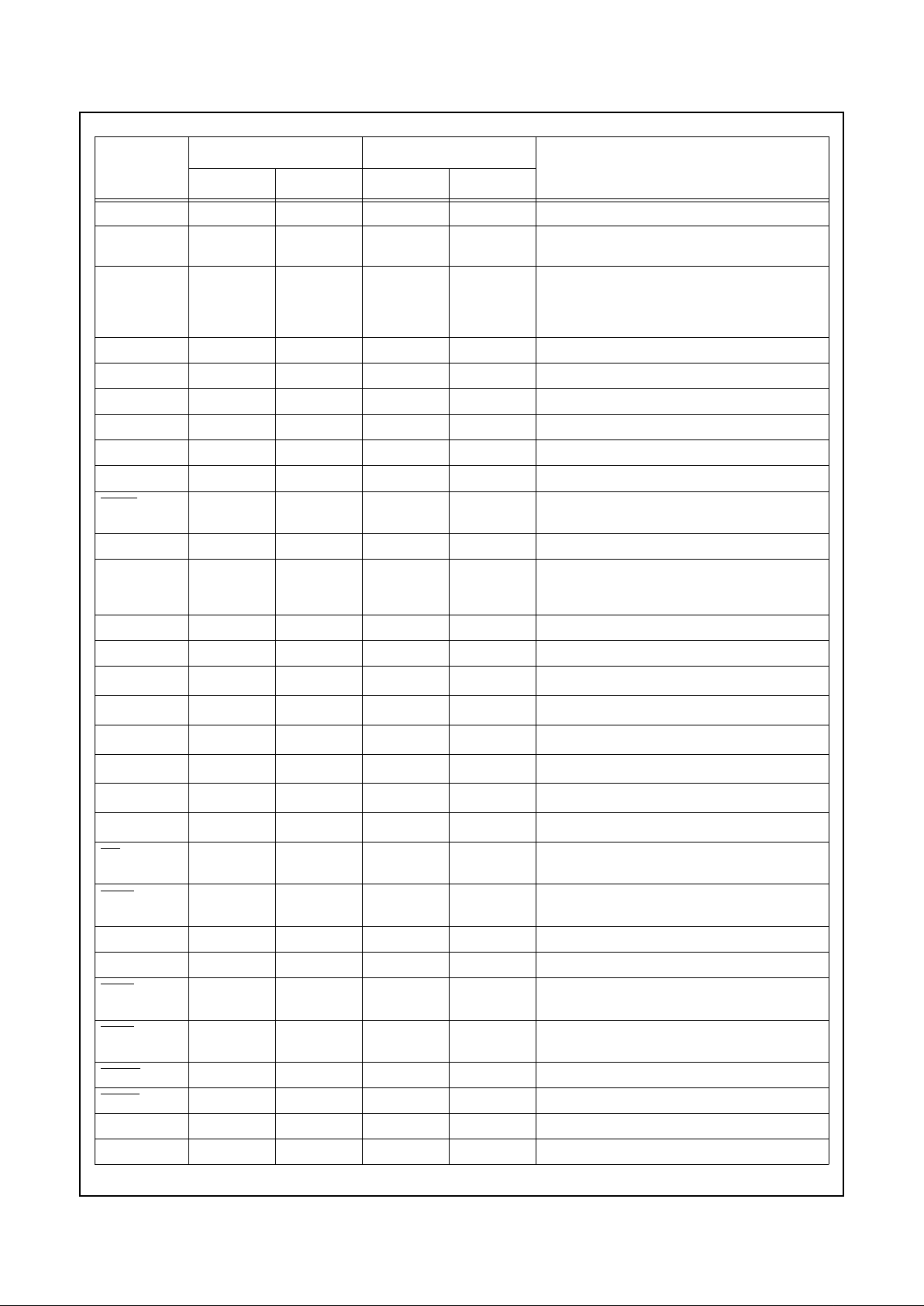

Table of Contents

Highlights.......................................................................................................................................................1

1.0 Introduction

1.1 INTERNAL ARCHITECTURE ....................................................................................................14

1.1.1 Processing Unit ...........................................................................................................14

1.1.2 BIU ...............................................................................................................................14

1.1.3 Memory ........................................................................................................................14

1.1.4 HBI ...............................................................................................................................14

1.1.5 Peripherals ..................................................................................................................14

1.2 EXPANSION OPTIONS .............................................................................................................15

1.3 OPERATING ENVIRONMENTS ................................................................................................15

1.3.1 IRE Environment .........................................................................................................16

1.3.2 IRD Environment .........................................................................................................17

1.3.3 DEV Environment ........................................................................................................18

2.0 Signal/Pin Connection and Description

2.1 CONNECTION DIAGRAMS ......................................................................................................19

2.2 SIGNAL/PIN DESCRIPTIONS ...................................................................................................21

2.3 RESET SOURCES AND TYPES ...............................................................................................26

2.3.1 Power-Up Reset ..........................................................................................................26

2.3.2 Warm Reset .................................................................................................................26

2.3.3 WATCHDOG Reset .....................................................................................................26

2.3.4 Triggering Reset ..........................................................................................................26

2.4 STRAP PINS ............................................................................................................................26

2.4.1 Setting the Environment ..............................................................................................26

2.4.2 Other Strap Pin Settings ..............................................................................................26

2.4.3 System Load on Strap Pins .........................................................................................27

2.4.4 Strap Inputs During Idle Mode .....................................................................................27

2.4.5 Strap Pin Status Register (STRPST) ...........................................................................27

2.5 ALTERNATE FUNCTIONS ........................................................................................................27

2.6 SYSTEM CONFIGURATION REGISTERS ...............................................................................29

2.6.1 Module Configuration Register (MCFG) ......................................................................29

2.6.2 PAGE Register ............................................................................................................30

2.7 SHARED MEMORY CONFIGURATION ...................................................................................30

2.8 MEMORY MAP ..........................................................................................................................30

2.8.1 Accessing Base Memory .............................................................................................31

2.8.2 Accessing External Memory ........................................................................................32

2.8.3 Accessing I/O Expansion Space .................................................................................33

3.0 Bus Interface Unit (BIU)

3.1 FEATURES ................................................................................................................................34

3.2 FUNCTIONAL DESCRIPTION ..................................................................................................34

3.2.1 Interfacing ....................................................................................................................34

3.2.2 Static Memory and I/O Support ...................................................................................34

Page 5

5

Table of Contents

www.national.com

3.2.3 Byte Accessing ............................................................................................................34

3.3 CLOCK AND BUS CYCLES ......................................................................................................34

3.3.1 Clock Cycles ................................................................................................................34

3.3.2 Control Signals ............................................................................................................35

3.3.3 Early Write Bus Cycle ..................................................................................................36

3.3.4 Late Write Bus Cycle ...................................................................................................38

3.3.5 Normal Read Bus Cycle ..............................................................................................40

3.3.6 Fast Read Bus Cycle ...................................................................................................42

3.3.7 I/O Expansion Bus Cycles ...........................................................................................43

3.3.8 I/O Expansion Example ...............................................................................................44

3.4 DEVELOPMENT SUPPORT .....................................................................................................44

3.4.1 Bus Status Signals ......................................................................................................44

3.4.2 Core Bus Monitoring ....................................................................................................44

3.5 BIU REGISTERS .......................................................................................................................45

3.5.1 BIU Configuration Register (BCFG) ............................................................................45

3.5.2 I/O Zone Configuration Register (IOCFG) ...................................................................45

3.5.3 Static Zone Configuration Register (SZCFGn) ............................................................45

3.6 USAGE HINTS ..........................................................................................................................46

4.0 On-Chip Memory

4.1 INTERNAL RAM ........................................................................................................................47

4.2 INTERNAL ROM ........................................................................................................................47

4.2.1 Access Times ..............................................................................................................47

4.2.2 ROM Shadow ..............................................................................................................47

5.0 Host Bus Interface (HBI)

5.1 FEATURES ................................................................................................................................48

5.2 HOST ACCESS TO SHARED MEMORY DEVICE ...................................................................49

5.2.1 Enabling Shared Memory Mode ..................................................................................49

5.2.2 Memory Device Interface .............................................................................................49

5.2.3 Host Access to Shared Memory ..................................................................................49

5.3 CORE ACCESS TO RTC/APC ..................................................................................................49

5.3.1 Host and CR16A Arbitration over RTC/APC ...............................................................49

5.4 USAGE HINTS ..........................................................................................................................49

5.4.1 Shared Memory ...........................................................................................................49

5.4.2 Wake-Up from Host .....................................................................................................50

5.4.3 Host Power-on Indication ............................................................................................50

5.5 HOST ACCESS TO PC87570 RESIDENT I/O DEVICES .........................................................50

5.5.1 Host Access to Configuration Registers ......................................................................50

5.5.2 Host Access to Resident I/O Devices ..........................................................................50

5.5.3 Host Bus I/O Cycles ....................................................................................................50

5.6 KBC CHANNEL .........................................................................................................................50

5.6.1 Status Register ............................................................................................................50

5.6.2 DBBOUT Register .......................................................................................................51

5.6.3 DBBIN Register ...........................................................................................................51

Page 6

6

Table of Contents

www.national.com

5.7 PM CHANNEL ...........................................................................................................................52

5.8 RTC/APC CHANNEL .................................................................................................................52

5.9 CR16A INTERRUPTS ...............................................................................................................52

5.10 HOST INTERRUPTS .................................................................................................................52

5.10.1 IRQ1, IRQ12 and IRQ11 and IRQ8 Buffers .................................................................53

5.11 SYSTEM CONSIDERATIONS ...................................................................................................53

5.11.1 Reset Configuration .....................................................................................................53

5.11.2 Host Power-On (HPWRON) Indication Input ...............................................................53

5.11.3 Host Master Reset (HMR) Input ..................................................................................53

5.11.4 Host Reset Output (HRSTO) from PC87570 ...............................................................53

5.11.5 HDEN Strap .................................................................................................................54

5.11.6 GA20 Pin Functionality ................................................................................................54

5.11.7 Host Driven Wake-Up ..................................................................................................54

5.11.8 APC-ON and APC-OFF Events ...................................................................................54

5.12 HBI REGISTERS ACCESSED BY CR16A ................................................................................54

5.12.1 Control and Status Register 1 (CST1) .........................................................................55

5.12.2 Control and Status Register 2 (CST2) .........................................................................55

5.12.3 RTC Core Address Register (RTCCA) ........................................................................55

5.12.4 RTC Core Data Register (RTCCD) .............................................................................56

5.12.5 Host PnP Initial Configuration Base Address Low and High Registers (HCFGBAL/H) 56

5.12.6 Host Interface Control Register (HICTRL) ...................................................................56

5.12.7 Host Interface IRQ Control Register (HIIRQC) ............................................................56

5.12.8 Host Interface KBC Status Register (HIKMST) ...........................................................57

5.12.9 Host Interface Keyboard Data Out Buffer Register (HIKDO) .......................................57

5.12.10 Host Interface Mouse Data Out Buffer Register (HIMDO) ...........................................58

5.12.11 Host Interface KBC Data In Buffer Register (HIKMDI) ................................................58

5.12.12 Host Interface PM Port Status Register (HIPMST) ......................................................58

5.12.13 Host Interface PM Data Out Buffer Register (HIPMDO) ..............................................58

5.12.14 Host Interface PM Data In Buffer Register (HIPMDI) ..................................................58

5.13 HOST CHANNEL CONFIGURATION .......................................................................................58

5.13.1 Chip Base Address Initial Setting ................................................................................58

5.13.2 Operation Guidelines ...................................................................................................60

5.14 HBI REGISTERS ACCESSED BY HOST .................................................................................61

5.14.1 Identification Register (SID) .........................................................................................61

5.14.2 Identification Type Register (SIDT) .............................................................................61

5.14.3 Identification Revision Register (SIDR) .......................................................................61

5.14.4 Base Address High Register (SBAH) ..........................................................................61

5.14.5 Base Address Low Register (SBAL) ............................................................................61

5.14.6 RTC Chip Select Address High Register (RTCCSAH) ................................................61

5.14.7 RTC Chip Select Address Low Register (RTCCSAL) .................................................61

5.14.8 KBC Chip Select Address High Register (KBCCSAH) ................................................62

5.14.9 KBC Chip Select Address Low Register (KBCCSAL) .................................................62

5.14.10 PM Chip Select Address High Register (PMCSAH) ....................................................62

5.14.11 PM Chip Select Address Low Register (PMCSAL) .....................................................62

5.14.12 Function Enable Register (FER) ..................................................................................62

5.14.13 Function Lock Register (FLR) ......................................................................................63

Page 7

7

Table of Contents

www.national.com

5.14.14 IRQ Enable Register (IRQE) .......................................................................................63

6.0 Real-Time Clock (RTC) and Advanced Power Control (APC)

6.1 FEATURES ................................................................................................................................64

6.2 RTC FUNCTIONAL DESCRIPTION ..........................................................................................64

6.2.1 Host Bus Interface .......................................................................................................64

6.2.2 Core Bus Interface .......................................................................................................64

6.2.3 Bank Description .........................................................................................................64

6.2.4 Bank Accessing ...........................................................................................................64

6.2.5 RTC Clock Generation ................................................................................................64

6.2.6 Internal Oscillator .........................................................................................................65

6.2.7 External Oscillator .......................................................................................................65

6.2.8 Timing Generation .......................................................................................................65

6.2.9 Timekeeping ................................................................................................................66

6.2.10 Updating ......................................................................................................................66

6.2.11 Alarms .........................................................................................................................67

6.2.12 Power Supply ..............................................................................................................67

6.2.13 System Bus Lockout ....................................................................................................68

6.2.14 Power-Up Detection ....................................................................................................68

6.2.15 Oscillator Activity .........................................................................................................68

6.2.16 Interrupt Handling ........................................................................................................68

6.2.17 Battery-Backed Register Banks and RAM ...................................................................68

6.3 RTC REGISTERS ......................................................................................................................69

6.3.1 RTC Control Register A (CRA) ....................................................................................69

6.3.2 RTC Control Register B (CRB) ....................................................................................70

6.3.3 RTC Control Register C (CRC) ...................................................................................70

6.3.4 RTC Control Register D (CRD) ...................................................................................71

6.4 USAGE HINTS ..........................................................................................................................71

6.5 APC FUNCTIONAL DESCRIPTION ..........................................................................................71

6.5.1 Operation .....................................................................................................................71

6.5.2 User Selectable Parameters ........................................................................................71

6.5.3 System Power States ..................................................................................................71

6.5.4 System Power Switching Logic ...................................................................................72

6.5.5 APC-ON/APC-OFF Interrupt Signals ...........................................................................72

6.5.6 Entering Power States .................................................................................................72

6.5.7 Predetermined Wake-Up .............................................................................................72

6.5.8 Ring Signal Event ........................................................................................................72

6.6 APC REGISTERS ......................................................................................................................72

6.6.1 APC Control Register 1 (APCR1) ................................................................................73

6.6.2 APC Control Register 2 (APCR2) ................................................................................73

6.6.3 APC Status Register (APSR) ......................................................................................73

6.6.4 RAM Lock Register (RLR) ...........................................................................................73

6.7 REGISTER BANKS ...................................................................................................................74

7.0 High Frequency Clock Generator (HFCG)

7.1 FEATURES ................................................................................................................................76

Page 8

8

Table of Contents

www.national.com

7.2 FUNCTIONAL DESCRIPTION ..................................................................................................76

7.2.1 Setting Clock Frequency .............................................................................................76

7.2.2 Fast Clock Setting .......................................................................................................77

7.3 HFCG REGISTERS ...................................................................................................................77

7.3.1 HFCG Control Register (HFCGCTRL) ........................................................................77

7.3.2 HFCGM Low Value Register (HFCGML) .....................................................................77

7.3.3 HFCGM High Value Register (HFCGMH) ...................................................................77

7.3.4 HFCGN Value Register (HFCGN) ...............................................................................77

7.3.5 HFCGI Low Value Register (HFCGIL) .........................................................................78

7.3.6 HFCGI High Value Register (HFCGIH) .......................................................................78

8.0 Power Mode Control (PMC)

8.1 FEATURES ................................................................................................................................79

8.2 THE POWER MODES ...............................................................................................................79

8.3 SWITCHING BETWEEN POWER MODES ...............................................................................79

8.3.1 Decreasing Power Consumption .................................................................................79

8.3.2 Increasing Performance ..............................................................................................79

8.4 POWER MODE CONTROL REGISTER (PMCR) .....................................................................80

8.5 USAGE HINTS ..........................................................................................................................80

9.0 Interrupt Control Unit (ICU)

9.1 FEATURES ................................................................................................................................81

9.2 FUNCTIONAL DESCRIPTION ..................................................................................................81

9.2.1 NMI ..............................................................................................................................81

9.2.2 Maskable Interrupts .....................................................................................................81

9.2.3 Edge/Level and Polarity Selection ...............................................................................81

9.2.4 Pending Interrupts .......................................................................................................81

9.2.5 External Interrupt Inputs ..............................................................................................81

9.2.6 Interrupt Assignment ...................................................................................................81

9.3 ICU REGISTERS .......................................................................................................................82

9.3.1 NMI Status Register (NMISTAT) .................................................................................82

9.3.2 Power Fail Control Register (PFAIL) ...........................................................................82

9.3.3 Interrupt Vector Register (IVCT) ..................................................................................83

9.3.4 Interrupt Enable and Mask Register (IENAM) .............................................................83

9.3.5 Interrupt Pending Register (IPEND) ............................................................................83

9.3.6 Edge Interrupt Clear Register (IECLR) ........................................................................83

9.3.7 Edge/Level Trigger Configuration Register (IELTG) ....................................................83

9.3.8 Trigger Polarity Configuration Register (ITRPL) ..........................................................83

9.4 USAGE HINTS ..........................................................................................................................83

9.4.1 Initializing .....................................................................................................................83

9.4.2 Clearing .......................................................................................................................83

9.4.3 Nesting ........................................................................................................................83

10.0 Multi-Input Wake-Up (MIWU)

10.1 FEATURES ................................................................................................................................84

Page 9

9

Table of Contents

www.national.com

10.2 FUNCTIONAL DESCRIPTION ..................................................................................................84

10.2.1 Trigger Conditions .......................................................................................................86

10.2.2 Pending Flags ..............................................................................................................86

10.2.3 Input Enable ................................................................................................................86

10.2.4 Interrupts .....................................................................................................................86

10.2.5 Input Assignments .......................................................................................................86

10.3 MIWU REGISTERS ...................................................................................................................86

10.3.1 Edge Detection Register 1(WKEDG1) .........................................................................86

10.3.2 Edge Detection Register 2 (WKEDG2) ........................................................................86

10.3.3 Edge Detection Register 3 (WKEDG3) ........................................................................86

10.3.4 Pending Register 1 (WKPND1) ...................................................................................86

10.3.5 Pending Register 2 (WKPND2) ...................................................................................86

10.3.6 Pending Register 3 (WKPND3) ...................................................................................87

10.3.7 Wake-Up Enable Register 1 (WKEN1) ........................................................................87

10.3.8 Wake-Up Enable Register 2 (WKEN2) ........................................................................87

10.3.9 Wake-Up Enable Register 3 (WKEN3) ........................................................................87

10.3.10 Pending Clear Register 1 (WKPCL1) ..........................................................................87

10.3.11 Pending Clear Register 2 (WKPCL2) ..........................................................................87

10.3.12 Pending Clear Register 3 (WKPCL3) ..........................................................................87

10.4 USAGE HINTS ..........................................................................................................................87

11.0 General Purpose I/O (GPIO) Ports

11.1 FEATURES ................................................................................................................................88

11.2 FUNCTIONAL DESCRIPTION ..................................................................................................88

11.2.1 Output Buffer ...............................................................................................................88

11.2.2 Input Buffer ..................................................................................................................88

11.2.3 Open Drain ..................................................................................................................88

11.2.4 Weak Pull-Up ...............................................................................................................88

11.3 GPIO PORT REGISTERS .........................................................................................................89

11.3.1 Port Alternate Function Register (PxALT) ...................................................................89

11.3.2 Port Direction Register (PxDIR) ...................................................................................89

11.3.3 Port Data Out Register (PxDOUT) ..............................................................................89

11.3.4 Port Data In Register (PxDIN) .....................................................................................89

11.3.5 Port Weak Pull-up Register (PxWPU) .........................................................................89

12.0 PS/2 Interface

12.1 FEATURES ................................................................................................................................90

12.2 FUNCTIONAL DESCRIPTION ..................................................................................................90

12.2.1 Configuration ...............................................................................................................90

12.2.2 Shift Mechanism ..........................................................................................................90

12.2.3 Quasi-Bidirectional Drivers ..........................................................................................90

12.2.4 Interrupt Signals ..........................................................................................................91

12.2.5 Power Modes ...............................................................................................................91

12.3 SHIFT MECHANISM ENABLED ................................................................................................91

12.3.1 Reset ...........................................................................................................................91

12.3.2 Enable .........................................................................................................................91

Page 10

10

Table of Contents

www.national.com

12.3.3 General PS/2 Interface Operation ...............................................................................91

12.3.4 Transmit Mode .............................................................................................................93

12.4 SHIFT MECHANISM DISABLED ...............................................................................................94

12.4.1 Clock Signal Control ....................................................................................................94

12.4.2 Data Signal Control .....................................................................................................94

12.4.3 Interrupt Generation ....................................................................................................94

12.5 PS/2 INTERFACE REGISTERS ................................................................................................95

12.5.1 PS/2 Data Register (PSDAT) ......................................................................................95

12.5.2 PS/2 Status Register (PSTAT) ....................................................................................95

12.5.3 PS/2 Control Register (PSCON) ..................................................................................95

12.5.4 PS/2 Output Signal Register (PSOSIG) ......................................................................96

12.5.5 PS/2 Input Signal Register (PSISIG) ...........................................................................96

12.5.6 PS/2 Interrupt Enable Register (PSIEN) ......................................................................96

13.0 ACCESS.bus (ACB) Interface

13.1 FEATURES ................................................................................................................................98

13.2 ACB PROTOCOL OVERVIEW ..................................................................................................98

13.2.1 ACB Interface ..............................................................................................................98

13.2.2 Data Transactions .......................................................................................................98

13.2.3 Start and Stop ..............................................................................................................98

13.2.4 Acknowledge Cycle .....................................................................................................98

13.2.5 “Acknowledge after every byte” Rule ...........................................................................99

13.2.6 Addressing Transfer Formats ....................................................................................100

13.2.7 Arbitration on the Bus ................................................................................................100

13.3 FUNCTIONAL DESCRIPTION ................................................................................................100

13.3.1 Master Mode ..............................................................................................................100

13.3.2 Slave Mode ................................................................................................................101

13.3.3 Power-Down ..............................................................................................................102

13.3.4 SDA and SCL Pin Configuration ................................................................................102

13.3.5 ACB Clock Frequency Configuration .........................................................................102

13.4 ACB REGISTERS ....................................................................................................................102

13.4.1 ACB Serial Data Register (ACBSDA) ........................................................................102

13.4.2 ACB Status Register (ACBST) ..................................................................................102

13.4.3 ACB Control Status Register (ACBCST) ...................................................................103

13.4.4 ACB Control Register 1 (ACBCTL) ............................................................................104

13.4.5 ACB Own Address Register (ACBADDR) .................................................................104

13.4.6 ACB Control Register 2 (ACBCTL2) ..........................................................................104

13.5 USAGE HINTS ........................................................................................................................105

14.0 Multi-Function 16-Bit Timer (MFT16)

14.1 FEATURES ..............................................................................................................................106

14.2 FUNCTIONAL DESCRIPTION ................................................................................................106

14.3 CLOCK SOURCE UNIT ...........................................................................................................107

14.3.1 Prescaler ...................................................................................................................107

14.3.2 External Event Clock .................................................................................................107

14.3.3 Pulse Accumulate Mode ............................................................................................107

Page 11

11

Table of Contents

www.national.com

14.3.4 Slow Speed Clock .....................................................................................................107

14.3.5 Counter Clock Source Select ....................................................................................108

14.4 TIMER/COUNTER AND ACTION UNIT ..................................................................................108

14.4.1 Operation Modes .......................................................................................................108

14.4.2 Timer Interrupts .........................................................................................................113

14.4.3 Timer I/O Functions ...................................................................................................113

14.5 MFT16 REGISTERS ................................................................................................................114

14.5.1 Clock Prescaler Register (TPRSC) ...........................................................................114

14.5.2 Clock Unit Control Register (TCKC) ..........................................................................114

14.5.3 Timer/Counter Register 1 (TCNT1) ...........................................................................114

14.5.4 Timer/Counter Register 2 (TCNT2) ...........................................................................114

14.5.5 Reload/Capture Register A(TCRA) ...........................................................................114

14.5.6 Reload/Capture Register B (TCRB) ..........................................................................114

14.5.7 Timer Mode Control Register (TCTRL) .....................................................................114

14.5.8 Timer Interrupt Control Register (TICTL) ...................................................................115

14.5.9 Timer Interrupt Clear Register (TICLR) .....................................................................115

15.0 Timer and WATCHDOG (TWD)

15.1 FEATURES ..............................................................................................................................116

15.2 FUNCTIONAL DESCRIPTION ................................................................................................116

15.2.1 Input Clock .................................................................................................................116

15.2.2 Pre-Scale ...................................................................................................................116

15.2.3 TWD Timer 0 .............................................................................................................116

15.3 WATCHDOG OPERATION ....................................................................................................117

15.4 TWD CONTROL AND CONFIGURATION ..............................................................................117

15.5 OPERATION IN IDLE MODE ..................................................................................................117

15.6 TWD REGISTERS ...................................................................................................................117

15.6.1 Timer and WATCHDOG Configuration Registers (TWCFG) .....................................117

15.6.2 Timer and Watchdog Clock Pre-Scaler Register (TWCP) .........................................117

15.6.3 TWD Timer 0 Register (TWDT0) ...............................................................................118

15.6.4 TWDT0 Control and Status Register (T0CSR) ..........................................................118

15.6.5 WATCHDOG Count Register (WDCNT) ...................................................................118

15.6.6 WATCHDOG Service Data Match Register (WDSDM) .............................................118

15.7 USAGE HINTS ........................................................................................................................118

16.0 Analog to Digital Converter (ADC)

16.1 FEATURES ..............................................................................................................................119

16.2 FUNCTIONAL DESCRIPTION ................................................................................................119

16.2.1 Reset .........................................................................................................................120

16.2.2 Reference Voltage .....................................................................................................120

16.2.3 Input Signal Range ....................................................................................................120

16.2.4 ADC Clock .................................................................................................................120

16.2.5 Initializing and Enabling the ADC ..............................................................................120

16.2.6 ADC Operation ..........................................................................................................121

16.2.7 Disabling the ADC to Save Power .............................................................................121

Page 12

12

Table of Contents

www.national.com

16.2.8 Sampling Time ...........................................................................................................121

16.2.9 Polling Driven Operation ............................................................................................121

16.2.10 Interrupt Driven Operation .........................................................................................121

16.2.11 Overflow ....................................................................................................................121

16.3 OPERATION MODES .............................................................................................................122

16.4 ADC REGISTERS ...................................................................................................................123

16.4.1 ADC Status Register (ADCST) ..................................................................................123

16.4.2 ADC Control Register 1 (ADCCNT1) .........................................................................123

16.4.3 ADC Control Register 2 (ADCCNT2) .........................................................................123

16.4.4 ADC Control Register 3 (ADCCNT3) .........................................................................124

16.4.5 ADC Data Registers ..................................................................................................125

16.5 USAGE HINTS ........................................................................................................................125

16.5.1 Power Supply and Layout Guidelines ........................................................................125

16.5.2 Power Consumption ..................................................................................................125

16.5.3 Filtering the Noise on Input Signals ...........................................................................126

16.5.4 AD0-7 Multiplexing with PD0-7 Port ..........................................................................126

16.5.5 Calculating the Sampling Time ..................................................................................126

17.0 Digital to Analog Converter (DAC)

17.1 FEATURES ..............................................................................................................................127

17.2 FUNCTIONAL DESCRIPTION ................................................................................................127

17.2.1 DAC Reset .................................................................................................................127

17.2.2 Reference Voltage .....................................................................................................127

17.2.3 Output Signal Range .................................................................................................127

17.2.4 Initializing and Enabling the DAC ..............................................................................128

17.2.5 Disabling the DAC .....................................................................................................128

17.2.6 Conversion Start ........................................................................................................128

17.3 DAC REGISTERS ...................................................................................................................128

17.3.1 DAC Control Register (DACCTRL) ............................................................................128

17.3.2 DAC Data Registers ..................................................................................................128

17.4 USAGE HINTS ........................................................................................................................128

17.4.1 Power Supply and Layout Guidelines ........................................................................128

17.4.2 Output Settling Time ..................................................................................................129

17.4.3 Output Voltage Accuracy ...........................................................................................129

17.4.4 Filtering Noise on Output Signals ..............................................................................129

17.4.5 Current Consumption ................................................................................................129

17.4.6 Entering Idle Mode ....................................................................................................129

18.0 Development System Support

18.1 ISE INTERRUPT .....................................................................................................................130

18.2 TRIS STRAP INPUT PIN .........................................................................................................130

18.3 FREEZING EVENTS ...............................................................................................................130

18.3.1 Disabling Maskable Interrupts ...................................................................................130

18.3.2 Freezing the WATCHDOG Counter ..........................................................................130

18.3.3 Disabling Additional Modules ....................................................................................130

18.3.4 Disabling Destructive Reads .....................................................................................130

Page 13

13

Table of Contents

www.national.com

18.4 MONITORING ACTIVITY DURING DEVELOPMENT .............................................................130

18.4.1 The Bus Status Signals .............................................................................................130

18.4.2 Transaction Effects on the External Bus ...................................................................130

18.4.3 Pipe Status Signals ...................................................................................................131

18.5 DEVELOPMENT SYSTEM REGISTERS ................................................................................131

18.5.1 Debug Configuration Register (DBGCFG) ................................................................131

18.5.2 Debug Freeze Enable Register (DBGFRZEN) ..........................................................131

19.0 Device Specifications

19.1 POWER AND GROUNDING ...................................................................................................132

19.2 GENERAL DC ELECTRICAL CHARACTERISTICS ...............................................................132

19.2.1 Recommended Operating Conditions .......................................................................132

19.2.2 Absolute Maximum Ratings .......................................................................................133

19.2.3 Power Supply Current under Recommended Operating Conditions .........................133

19.3 DC ELECTRICAL CHARACTERISTICS .................................................................................134

19.3.1 Analog .......................................................................................................................134

19.3.2 Digital .........................................................................................................................135

19.4 AC ELECTRICAL CHARACTERISTICS ..................................................................................137

19.4.1 Definitions ..................................................................................................................137

19.4.2 Timing Tables ............................................................................................................138

19.5 TIMING DIAGRAMS ................................................................................................................144

19.5.1 General ......................................................................................................................144

19.5.2 BIU .............................................................................................................................146

19.5.3 GPIO Ports ................................................................................................................149

19.5.4 Host Interface ............................................................................................................150

19.5.5 MFT16 .......................................................................................................................151

19.5.6 ACCESS Bus Interface ..............................................................................................152

19.5.7 Dev Environment Support .........................................................................................153

19.5.8 Interrupts and Wake-up .............................................................................................153

19.5.9 Reset .........................................................................................................................154

19.5.10 Host Power-on ...........................................................................................................154

19.5.11 PS/2 Interface ............................................................................................................155

A. CR16A Register Map

B. Bootloader Description

B.1 OVERVIEW .............................................................................................................................164

B.2 CONFIGURATION BLOCKS ...................................................................................................164

B.2.1 System Configuration Block ......................................................................................164

B.2.2 KBC Header ..............................................................................................................164

B.3 SYSTEM RESOURCES USED BY BOOTLOADER ...............................................................164

B.3.1 GPIO Pins ..................................................................................................................164

B.3.2 On-Chip RAM ............................................................................................................165

B.4 BOOTLOADER PROGRAM OPERATION ..............................................................................165

Page 14

Introduction

14

1.0 Introduction

www.national.com

1.0 Introduction

1.1 INTERNAL ARCHITECTURE

The following descriptions are based on the block diagram

in Highlights on page 1.

1.1.1 Processing Unit

The CompactRISC CR16A core is an advanced, generalpurpose, 16-bit microprocessor core with a RISC architecture. The core is responsible for arithmetic and logic operations and program control. For more details about the core

structure and instruction set, see

CR16A Core Architecture

Specification, Revision 1.1, January 1996.

1.1.2 BIU

The BIU controls access to:

●

on-chip Base Memory (boot-code, ZONE1, maskROM)

●

off-chip devices:

— Base Memory (boot-code, ZONE1, Flash or ROM)

— External Memory (application code, ZONE0, Flash

or SRAM)

— I/O Expansion

Each of these memories is associated with a ZONE in the

BIU. The zone configuration registers control access to devices connected to it. See Section 3.2 on page 34 for more

details on BIU.

1.1.3 Memory

ROM The on-chip ROM holds the CR16A boot program which

is run by the PC87570 upon reset (internal power-up reset, or

pulse on HMR pin). The 2048 byte on-chip ROM is used for

boot and External Memory update programs.

The boot program verifies that the External Memory exists

and holds a valid code; then, it jumps to execute this code.

If the External Memory does not hold a valid code (for example, the Flash is wrongly programmed), the boot program enables the host to download the code via the host

interface channel, and re-program the Flash.

The External Memory holds most of the PC87570 application

programs and constant data. The external memory can be any

kind of memory device since the PC87570 can directly interface with Flash, ROM or SRAM devices. This allows upgrading of the PC87570 firmware (keyboard controller code) in the

field.

RAM The 1024 byte on-chip RAM is mostly used for the

storage of program variables and stack. It can store short

programs used upon returning from Idle mode to Active

mode, and is preserved as long as VCC power is applied to

the PC87570. The PC87570 hardware arbitrates Flash usage by the CR16A firmware and the host processor BIOS

program, when the "shared-memory" configuration is used.

To reduce resource contention when this shared BIOS

Flash scheme is used, the host processor should copy the

Flash contents to the host’s main memory (DRAM) upon

system boot. Flash sharing is based on “cycle stealing” so

both the host processor and the CR16A can execute in parallel code from the same memory device.

1.1.4 HBI

The Host Bus Interface (HBI) bridges and arbitrates between host and CR16A accesses to shared resources. The

HBI allows the host and CR16A to share Flash memory.

See Section 5.2 on page 49 for more details on the shared

memory system.

The HBI enables host access to the KBD/MOUSE and the PM

interface ports, and to the RTC/APC. It also enables the

CR16A to access the RTC/APC and its CMOS RAM.

The host interface uses an ISA compatible bus protocol.

The PC87570 decodes the 16 ISA address lines to identify

the on-chip I/O device address as defined in the host configuration. Shared BIOS memory accesses to the device

are indicated by a memory chip select input from the host

(

HMEMCS signal), and three additional address lines (A16,

A17 and A18).

The Host Interface Configuration allows the host pro-

cessor to configure the interface to the PC87570 I/O devices (KBD, PM and RTC/APC host interface channels). The

Host Interface Configuration includes a motherboard Plugand-Play protocol that allows settings, such as the address

of each device, to be enabled and disabled. It also includes

a locking scheme to allow the BIOS program to protect the

configuration from tampering.

The Host Interface has three channels as follows:

●

Keyboard and Mouse (host addresses 60h, 64h).

●

Power Management (host address 62h, 66h)

●

RTC/APC (host address 70h, 71h).

The Host Interface supports the four legacy (ISA) interrupts.The PC87570 can generate interrupt requests to the

host processor via IRQ1, IRQ12, IRQ11 and

IRQ8 for the

Keyboard, Mouse, PM and RTC/APC handlers, respectively. This allows the PC87570 to be used with polling or interrupt driven schemes.

The PC87570 communicates with a host processor over an

ISA compatible, host interface bus. The KBD, PM and the

RTC/APC are interfaced as I/O devices over the I/O address space of the host.

In addition, the PC87570 generates the gate A20 control

signal (GA20 pin) and a soft reset signal (

HRSTO pin) to the

host. Optionally, this

HRSTO reset signal can be used to

prevent the host from accessing the shared Flash when the

PC87570 cannot perform the shared memory access during the PC87570’s boot-up time.

1.1.5 Peripherals

The RTC/APC has a low-power clock that provides time-of-

day, a calendar with century counter and alarm features. It

can work from either V

CC

or a backup battery using an internal switch. Other features include three maskable interrupt sources and 242 bytes of general-purpose RAM. An

external battery source maintains valid RAM and time during V

CC

failure. The RTC is software compatible with the

DS1287 and MC146818.

The APC hardware, with APM 1.2 compatible power con-

trol, features such as alarm wake-up, ring detection and

host control off commands. The APC controls the PC power

supply via the CR16A firmware. This allows maximum flexibility in designing an ACPI system based on the PC87570.

Page 15

Introduction

EXPANSION OPTIONS

15

www.national.com

The HFCG (High Frequency Clock Generator) provides

clocks for the various on-chip modules. These clocks are

generated directly from a 32.768 KHz crystal or from the onchip HFCG. The HFCG generates the high-frequency clock

using the RTC’s 32.768 KHz clock signal as a reference.

The PC87570 operation frequency is set by programming

the HFCG registers. The PMC enables and disables high

frequency clock generation, according to the required power mode.

The PMC (Power Mode Control) reduces the PC87570's

power consumption to the required activity level. Power

consumption is adjusted by controlling the clock frequency

and selective enabling/disabling of three power modes: Active, Idle and Power Off. Activity can be resumed by a periodic wake-up or via external events.

The ICU (Interrupt Control Unit) is a sixteen-channel module that interfaces between the interrupt requests (from different on-chip modules and external sources), and the

CR16A core. Both maskable and non-maskable interrupts

are generated.

For maskable interrupts, the ICU controls the masking of

the various sources and prioritizes the different requests. It

generates an interrupt to the core and indicates which of the

sources requested service. For non-maskable interrupts, it

combines the various sources into one and indicates which

is the requested service.

MIWU The Multi-Input Wake-Up module allows the device

to return from Idle mode. The CR16A can enable or disable

the various wake-up conditions. The PC87570 has a total of

23 wake-up signals, some of which are grouped to generate

a single interrupt signal.

GPIO Ports consist of up to 76 GPIO signals that provide

interface and control for the PC system. Some of these I/O

port signals share their pins with an alternate function (see

Table 2-5 on page 27), and may be mutually exclusive.

Some of these signals, when configured as inputs, can interrupt the CR16A when an event is detected even if the device is in Idle Mode. An example is the SWIN input, which is

dedicated for the PC’s On/Off switch.

One of the I/O pin can be used as an SMI output to the host

processor. The SMI is generated based on various events

identified by the CR16A. This includes an OFFcommand indication from the APC.

Internal keyboard scanning is supported by 16 open-drain

output port signals, and 8 input port signals with Schmidt

trigger input buffer and internal pull-up resistors. For power

efficiency, the inputs include an interrupt and a wake-up capability, so that pressing/releasing keys may be identified

without scanning the keyboard matrix in either Active or Idle

modes. The keyboard interrupt is controlled by the MIWU.

The PS/2 Interface, is an industry-standard, with PS/2compatible keyboard support, is implemented through a

two-wire, bidirectional TTL interface. Several vendors also

supply PS/2 mouse products and other pointing devices

with the same type of interface.

The PC87570 supports three PS/2 channels. Each channel

has two quasi-bidirectional signals which may be interfaced directly to an external keyboard, mouse or any other PS/2 compatible pointing device. Since the three channels are identical,

the connector ports are interchangeable.

The PC87570 includes a hardware accelerator that allows

the PS/2 channels to be controlled with minimal software

overhead. It also eliminates the sensitivity to interrupt latency that characterized traditional solutions.

The ACB Interface is a two-wire serial interface compatible with the ACCESS.bus physical layer. It is also compatible with Intel’s SMBus and Philips’ I

2

C. This module can

serve as a bus master or slave, and performs both transmit

or receive operations.

The MFT16 contains two 16-bit timers with a range of operation modes. These timers can operate from several

clock sources in PWM, Capture or Counter mode to satisfy

a wide range of application requirements.

The TWD has a 16-bit periodic interrupt timer that can be

programmed to generate interrupts at pre-defined intervals.

An 8-bit WATCHDOG timer can reset the PC87570 whenever the software loses control of the processor.

The ADC contains eight analog input channels. Each ADC

channel has a 10 µsec minimum conversion period. Either

an internal or external voltage source may be used as a reference for the A/D conversion.

The DAC has four channels of voltage output. Each of the

four DAC channels has an 8-bit resolution with a full output

range from AGND to AV

CC

. Conversion time is about 1 µsec

on a 50 pF load.

1.2 EXPANSION OPTIONS

The PC87570 system can be expanded cost effectively, as

follows:

●

I/O Expansion permits adding I/O port pins, in addition

to those available on-chip, using low-cost standard

74HC devices.

●

The External Memory may be configured to 8-bit width

to interface with 8-bit Flash/SRAM devices, or it may

be configured to 16-bit width when additional performance is required.

●

The PC87570 may be configured to interface with 32

Kbyte or 56 Kbyte of External Memory (application).

1.3 OPERATING ENVIRONMENTS

Upon power-up reset, the ENV1-0 pins select one the following operating environments:

●

Internal ROM Enabled (IRE)

●

Internal ROM Disabled (IRD)

●

Development (DEV)

See Section 2.4 on page 26 for more information about

these pins and controlling the loads connected to them.

Code written for IRE environment is executable in all environments, since it is binary compatible. The execution time of

code in on-chip Base Memory (the IRE environment) is identical to that in off-chip Base Memory (IRD and DEV environments); i.e., the operation is cycle-by-cycle compatible.

PC87570 devices are tested to ensure that they operate in

either IRE or IRD environment. Only selected parts are tested for operation in DEV environment.

Page 16

Introduction

16

OPERATING ENVIRONMENTS

www.national.com

1.3.1 IRE Environment

In this environment, after reset, (internal power-on reset circuit or an external pulse on HMR pin), the PC87570 starts

running the code written in the internal mask-ROM. This

ROM contains the PC87570’s boot program which is readonly. The boot-code size can be up to 2 Kbytes. After completion of the boot program, the process is handed over to

the External Memory. In the External Memory resides the

user-defined application.

The boot program performs several basic task needed to

start the system in a safe and ordered way. It checks if the

External Memory holds valid code. In case the code is invalid, it allows the host processor to re-program the Flash

device. See also Section B.1 on page 164.

To maximize on-chip ROM performance, configure the BIU

as described in Section 3.6 on page 46.

The majority of applications use the PC87570 in IRE environment, which provides up to 10 on-chip I/O ports with a total of 76 GPIO signals. The ports are: PA6-0, PB7-0, PC70, PD7-0, PE1-0, PF7-0, PG4-0, PH5-0, KBSIN7-0 and

KBSOUT15-0.

In addition, the PC87570 provides an interface to External

Memory and a variety of system functions, including ADC

and DAC, Timers, Interrupts, PM, ACCESS.bus/SMBus, and

other features (some features are mutually exclusive).

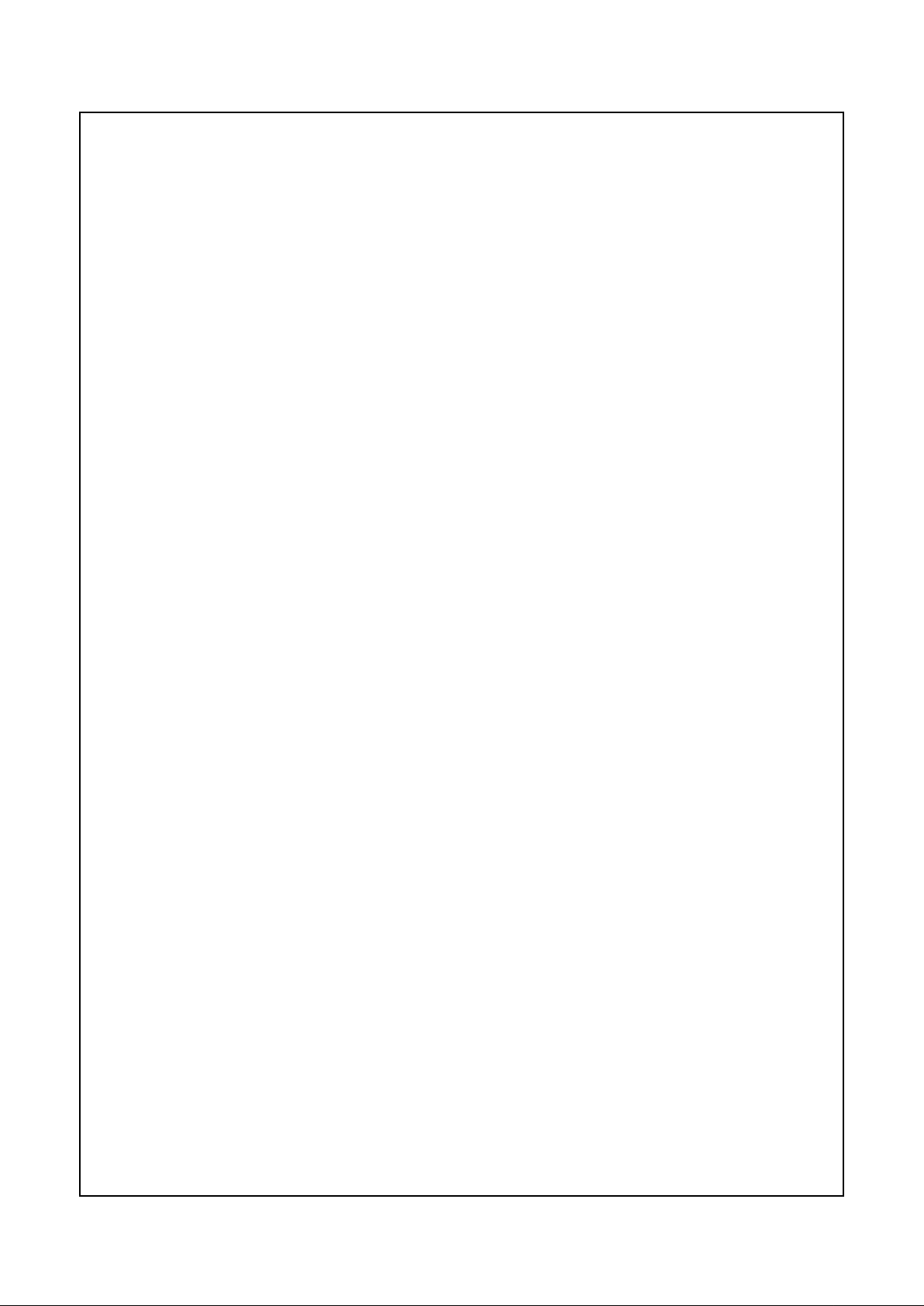

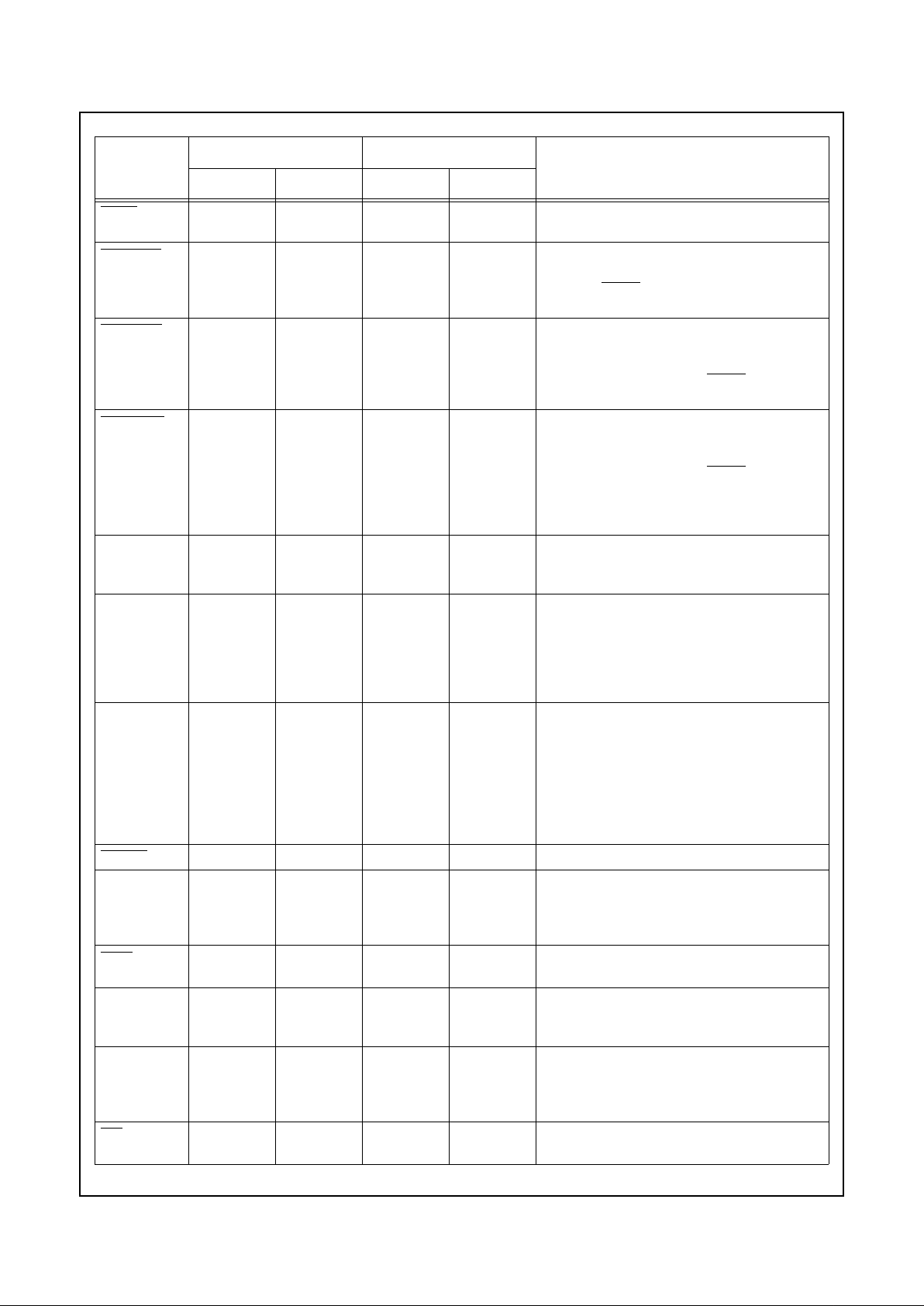

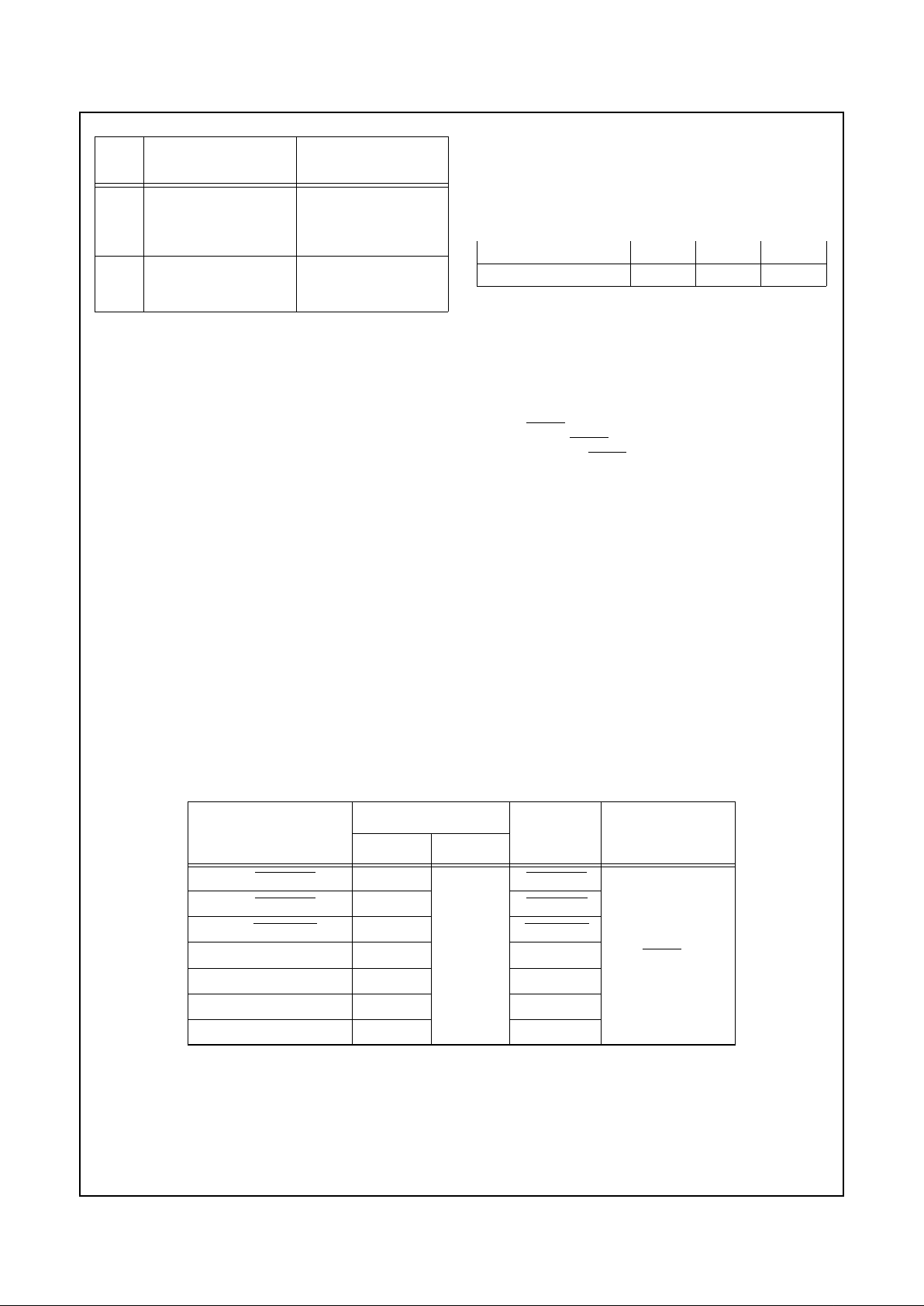

See Figure 1-1 for a system example in IRE environment.

In this environment, the ENV0 and ENV1 strap pins do not

need any external pull-up resistors.

or

Clock

External

Memory

PC87570

Host System Bus (ISA Compatible)

32KX1/32KCLKIN

32KX2

HMR

HA18-0

HD7-0

HIOR

HIOW

IRQ1

IRQ11

IRQ12

RD

WR1-0

SEL0

A18-16, A15-0

D15-8

AD7-0

DA3-0

PA6-0

PB7-0

PC7-0

PD7-0

HIOCHRDY

RTC

Battery

V

BAT

IRQ8

PSCLK1

PSDAT1

Crystal

32.768 KHz

External Keyboard

Internal

Keyboard

KBSOUT15-0

KBSIN7-0

SRAM or

Flash

ENV0

GA20

AVCC

AGND

VCC

GND

Power

Supply

SCL

D7-0

HMEMRD

HMEMWR

PSCLK2