Page 1

1

- February 1998

Highlights

www.national.com

©

1998 National Semiconductor Corporation

PRELIMINARY

February 1998

PC87317VUL/PC97317VUL SuperI/O Plug and Play

Compatible with ACPI Compliant Controller/Extender

Highlights

General Description

The PC87317VUL/PC97317VUL are functionally identical

parts that offer a single-chip solution to the most commonly

used ISA, EISA and MicroChannel

®

peripherals. This fully

Plug and Play (PnP) compatible chip conforms to the

Plug

and Play ISA Specification

Version 1.0a, May 5, 1994, and

meets specifications defined in the

PC97 Hardware Design

Guide

. It features a Controller/Extender that is fully compliant with Advanced Configuration and Power Interface (ACPI) Revision 1.0 requirements.

Note: All references to the PC87317VUL in this document

also refer to the PC97317VUL, unless otherwise specified.

References which are applicable to the PC97317VUL only

are italicized.

The PC87317VUL incorporates: an advanced Real-Time

Clock (RTC) device that provides both RTC timekeeping and

Advanced Power Control (APC) functionality, a Floppy Disk

Controller (FDC), a Keyboard and Mouse Controller (KBC),

two enhanced Serial Ports (UARTs) with Infrared (IR) support, a full IEEE 1284 Parallel Port, 24 General-Purpose Input/Output (GPIO) bit ports, three general-purpose chip

select signals that can be programmed for game port control

and a separate configuration register set for each module.

The PC87317VUL provides a LED drive output to comply

with PC97 specifications. The chip also provides support for

Power Management (PM), including a WATCHDOG timer,

and standard PC-AT address decoding for on-chip functions.

The PC87317VUL Infrared (IR) interface complies with the

HP-SIR and SHARP-IR standards, and supports all four basic protocols for Consumer Remote Control circuitry (RC-5,

RC-5 extended, RECS80 and NEC).

Outstanding Features

Among the most advanced members of National Semiconductor’s highly successful SuperI/O family, the PC87317VUL

offers:

●

Full compatibility with ACPI Revision 1.0 requirements

●

Compliancy with

PC97 Hardware Design Guide

speci-

fications, including PC97 LED support

●

Advanced RTC, including timekeeping and APC functionality

●

24 GPIO bit ports

●

FDC, KBC, two enhanced UARTs, IR support, IEEE

1284 parallel port

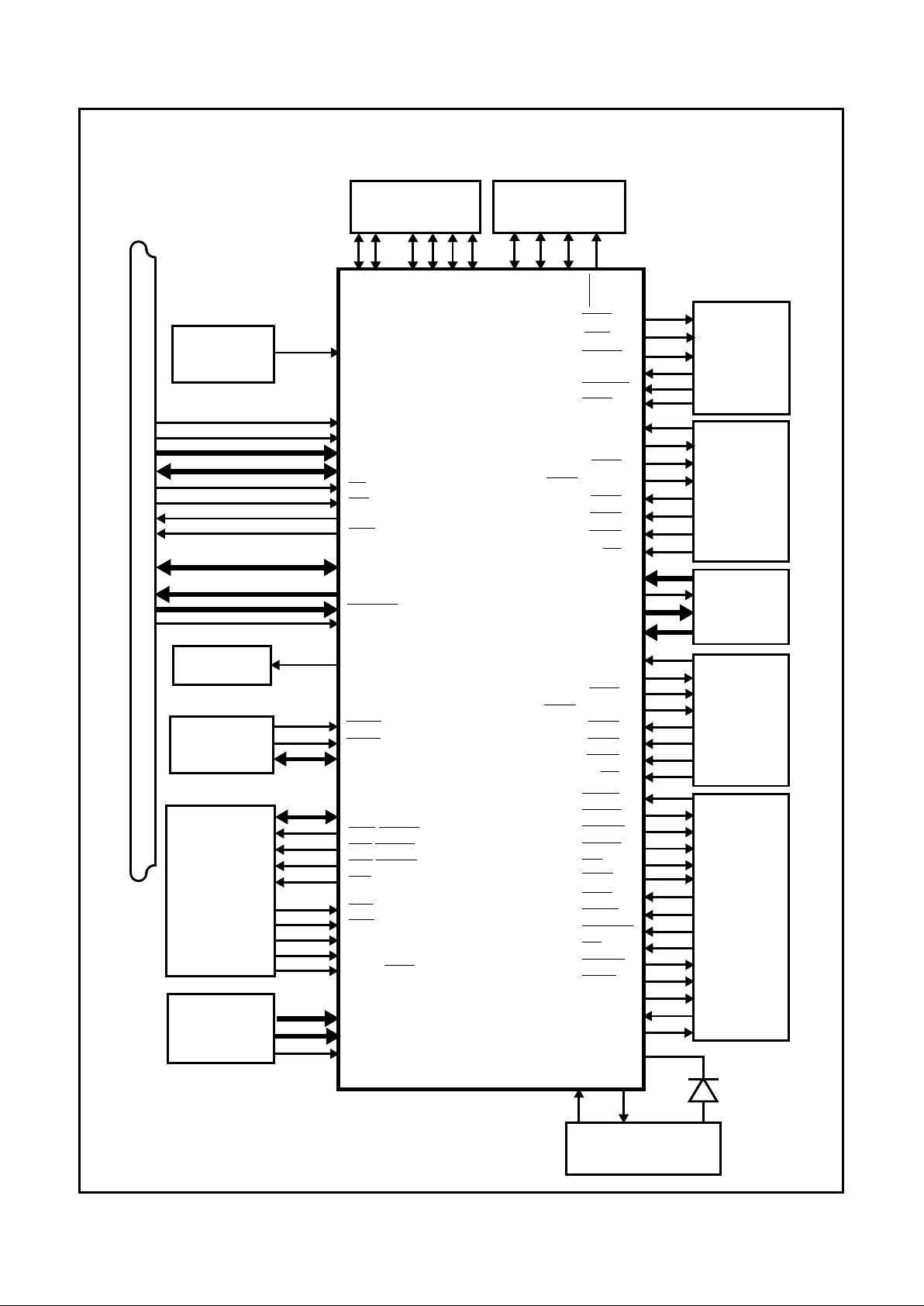

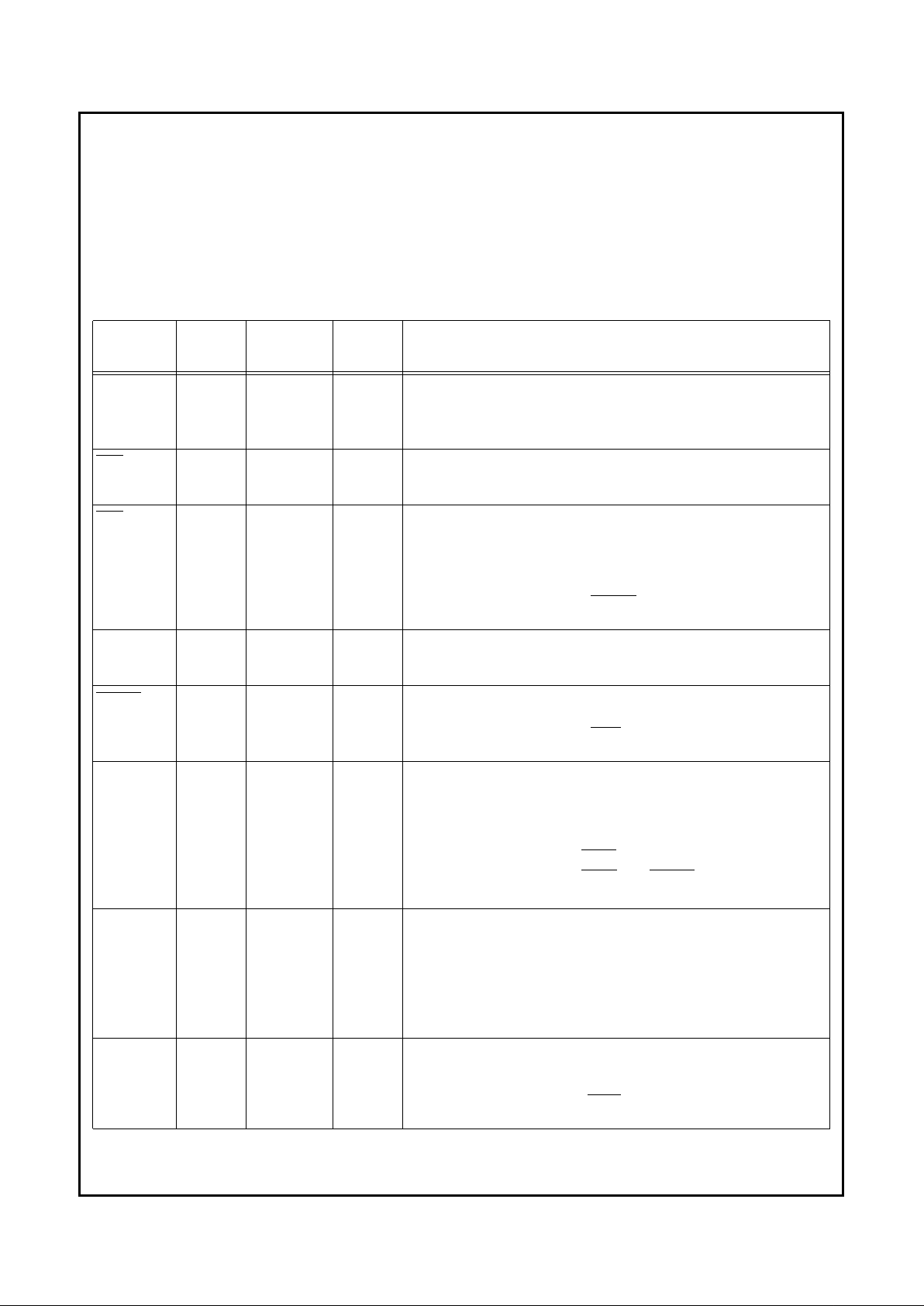

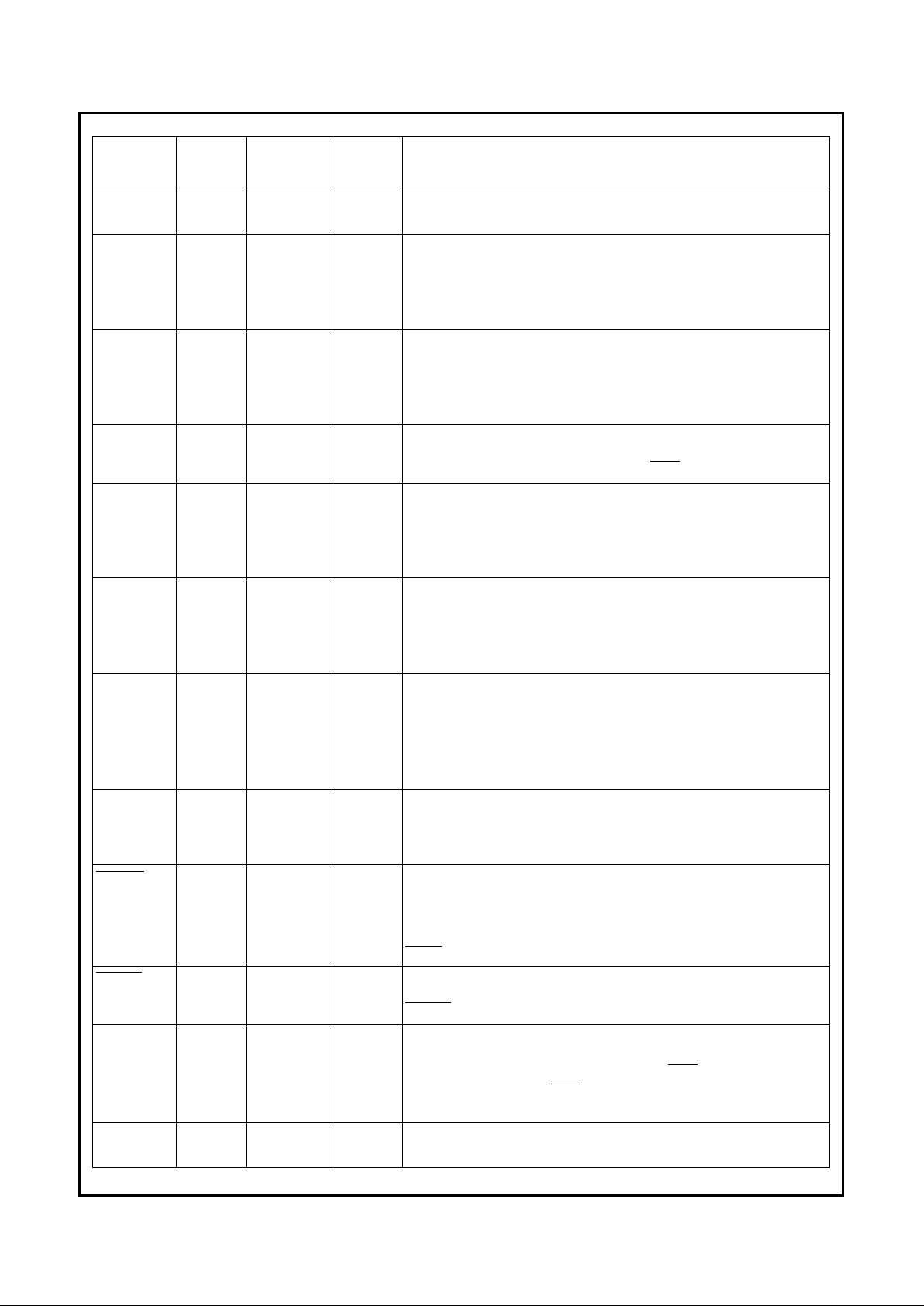

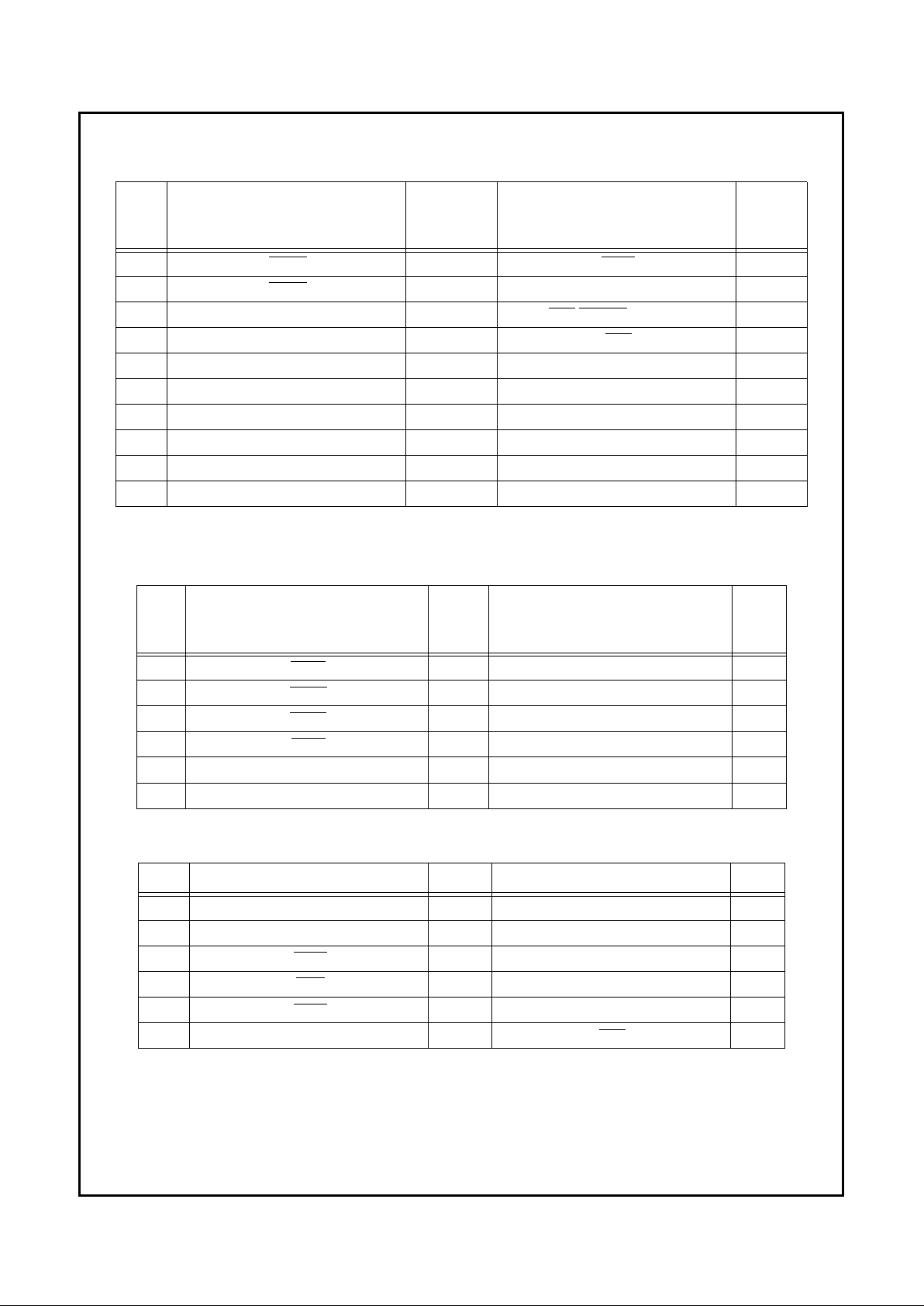

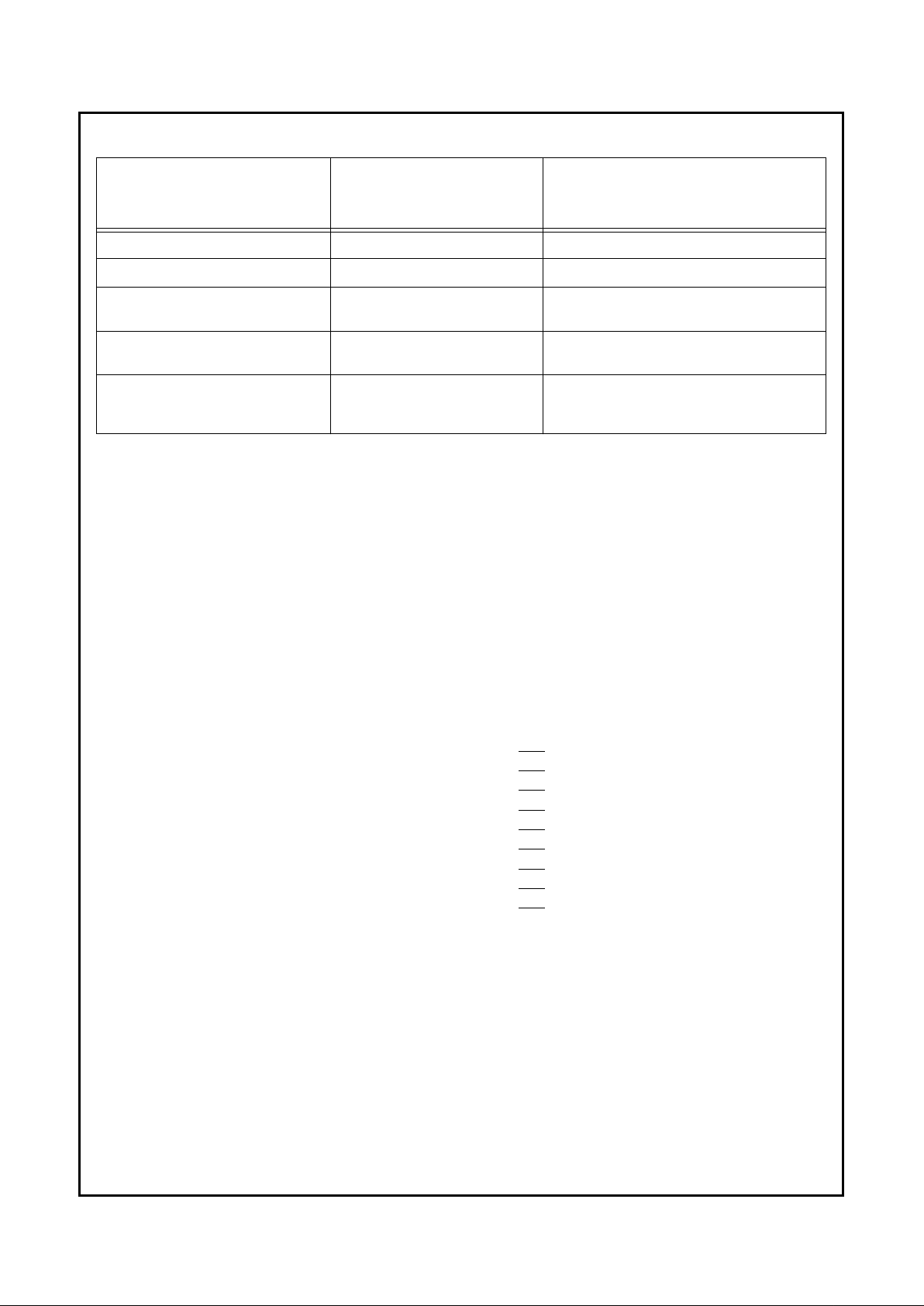

Block Diagram

Real-Time Clock

Floppy Disk

Controller (FDC)

Keyboard + Mouse

Controller (KBC)

Management (PM

)

µP Address

Floppy Drive

Interface

Data Handshake

Data

X-Bus

Control

Parallel Port

(PnP)

IRQ

Control

DMA

Channels

(RTC and APC)

Plug and Play

Data and

Control

General-Purpose I/O

(GPIO) Registers

I/O Ports

Control

Control

Data and

IEEE 1284

(Logical Device 2)

(Logical Devices 0 & 1)

(Logical Device 8)

(Logical Device 4)

(Logical Device 7)

(Logical Device 3)

Ports

Serial

with IR (UART2)

Interface

Infrared

Interface

(Logical Devices 5)

Power

Serial

(UART1)

Interface

(Logical Devices 6)

Serial Port Serial Port

TRI-STATE® and WATCHDOG are trademarks of National Semiconductor Corporation.

IBM

®

, MicroChannel®, PC-AT® and PS/2® are registered trademarks of International Business Machines Corporation.

Microsoft

®

and Windows® are registered trademarks of Microsoft Corporation.

Page 2

2

Highlights

www.national.com

Features

●

100% compatibility with PnP requirements specified in

the “

Plug and Play ISA Specification

”, ISA, EISA, and

MicroChannel architectures

●

A special PnP module that includes:

— Flexible IRQs, DMAs and base addresses that meet

the PnP requirements specified by Microsoft

®

in

their 1995 hardware design guide for Windows

®

and

PnP ISA Revision 1.0A

— PnP ISA mode (with isolation mechanism – Wait for

Key state)

— Motherboard PnP mode

●

An FDC that provides:

— A modifiable address that is referenced by a 16-bit

programmable register

— Software compatibility with the PC8477, which con-

tains a superset of the floppy disk controller functions in the µDP8473, the NEC µPD765A and the

N82077

— 13 IRQ channel options

— Four 8-bit DMA channel options

— 16-byte FIFO

— Burst and non-burst modes

— A new, high-performance, internal, digital data sep-

arator that does not require any external filter components

— Support for standard 5.25" and 3.5" floppy disk

drives

— Automatic media sense support

— Perpendicular recording drive support

— Three-mode Floppy Disk Drive (FDD) support

— Full suppor t for the IBM Tape Dr ive Register (TDR)

implementation of AT and PS/2 drive types

●

A KBC with:

— A modifiable address that is referenced by a 16-bit

programmable register, reported as a fixed address

in resource data

— 13 IRQ options for the Keyboard Controller

— 13 IRQ options for the Mouse Controller

— An 8-bit microcontroller

— Software compatibility with 8042AH and PC87911

microcontrollers

— 2 KB of custom-designed program ROM

— 256 bytes of RAM for data

— Five programmable dedicated open drain I/O lines

for keyboard controller applications

— Asynchronous access to two data registers and one

status register during normal operation

— Support for both interrupt and polling

— 93 instructions

— An 8-bit timer/counter

— Support for binary and BCD arithmetic

— Operation at 8 MHz,12 MHz or 16 MHz (programma-

ble option)

— Customizing by using the PC87323VUL, which in-

cludes a RAM-based KBC, as a development platform for keyboard controller code for the

PC87317VUL

●

An RTC that has:

— A modifiable address that is referenced by a 16-bit

programmable register

— 13 IRQ options, with programmable polarity

— DS1287, MC146818 and PC87911 compatibility

— 242 bytes of battery backed up CMOS RAM in two

banks

— Selective lock mechanisms for the RTC RAM

— Battery backed up century calendar in days, day of

the week, date of month, months, years and century ,

with automatic leap-year adjustment

— Battery backed-up time of day in seconds, minutes

and hours that allows a 12 or 24 hour format and adjustments for daylight savings time

— BCD or binary format for time keeping

— Three different maskable interrupt flags:

• Periodic interrupts - At intervals from 122 msec

to 500 msec

• Time-of-Month alarm - At intervals from once per

second to once per Month

• Updated Ended Interrupt - Once per second

upon completion of update

— Separate battery pin, 2.4 V operation that includes

an internal UL protection resistor

— 2 µA maximum power consumption during power

down

— Double-buffer time registers

●

ACPI Controller/Extender that supports the requirements of the ACPI spec (rev 1.0):

— Power Management Timer

— Power Button

— Real Time Clock Alarm

— Suspend modes via software emulation

— PnP SCI

— Global Lock mechanism

— General Purpose events

— Date of Month Alarm

— Century byte

●

An APC that controls the main power supply to the system, using open-drain output, as follows:

Power turned on when:

— The RTC reaches a pre-determined wake-up centu-

ry, date and time selection

— A high to low transition occurs on the RI input signals

of the UARTs

— A ring pulse or pulse train is detected on the RING

input signal

— A SWITCH input signal indicates a Switch On event

with a debounce-protection

— Any one of seven programmable Power Manage-

ment external trigger events occur

Powered turned off when:

— A SWITCH input signal indicates a Switch Off event

Page 3

3

Highlights

www.national.com

— A Fail-safe ev ent occurs (power-sav e mode detected

but the system is hung up)

— Software turns power off

— Any one of 10 programmable Power Management

trigger events occur

●

Two Serial Ports (UART1 and 2) that provide:

— Fully compatible with the 16550A and the 16450

— Extended UART mode

— 13 IRQ channel options

— Shadow register support for write-only bit monitoring

— UART data rates up to 1.5 Mbaud

●

An enhanced UART with IR interface on the UART2 that

supports:

— IrDA 1.0-SIR

— ASK-IR option of SHARP-IR

— DASK-IR option of SHARP-IR

— Consumer Remote Control circuitry

— DMA handshake signal routing for either 1 or 2 chan-

nels

— A PnP compatible external transceiver

●

A bidirectional parallel port that includes:

— A modifiable address that is referenced by a 16-bit

programmable register

— Software or hardware control

— 13 IRQ channel options

— Four 8-bit DMA channel options

— Demand mode DMA support

— An Enhanced Parallel Port (EPP) that is compatible

with the new version EPP 1.9, and is IEEE 1284

compliant

— An Enhanced Parallel Port (EPP) that also supports

version EPP 1.7 of the Xircom specification

— Support for an Enhanced Parallel Port (EPP) as

mode 4 of the Extended Capabilities Port (ECP)

— An Extended Capabilities Port (ECP) that is IEEE

1284 compliant, including level 2

— Selection of internal pull-up or pull-down resistor for

Paper End (PE) pin

— Reduction of PCI bus utilization by supporting a de-

mand DMA mode mechanism and a DMA fairness

mechanism

— A protection circuit that prevents damage to the par-

allel port when a printer connected to it powers up or

is operated at high voltages

— Output buffers that can sink and source14 mA

●

Three general-purpose pins for three separate programmable chip select signals, as follows:

— Can be programmed for game port control

— The Chip Select 0 (

CS0) signal produces open drain

output and is powered by the V

CCH

— The Chip Select 1 (CS1) and 2 (CS2) signals have

push-pull buffers and are pow ered b y the main V

DD

— Decoding of chip select signals depends on the ad-

dress and the Address Enable (AEN) signals, and

can be qualified using the Read (

RD) and Write

(

WR) signals.

●

24 single-bit GPIO ports:

— Modifiable addresses that are referenced by a 16-bit

programmable register

— Programmable direction for each signal (input or out-

put)

— Programmable drive type for each output pin (open-

drain or push-pull)

— Programmable option for internal pull-up resistor on

each input pin

— Configuration-Lock options

— Several signals may be selected as interrupt triggers

— A back-drive protection circuit

●

An X-bus data buffer that connects the 8-bit X data bus

to the ISA data bus

●

Clock source options:

— Source is a 32.768 KHz crystal - an internal frequen-

cy multiplier generates all the required internal fre-

quencies.

— Source may be either a 48 MHz or 24 MHz clock in-

put signal.

●

Enhanced Power Management (PM), including:

— Special configuration registers for power down

— WATCHDOG timer for power-saving strategies

— Reduced current leakage from pins

— Low-power CMOS technology

— Ability to shut off clocks to all modules

— LED control powered by V

CCH

●

General features include:

— All accesses to the SuperI/O chip activate a Zero

Wait State (

ZWS) signal, except for accesses to the

Enhanced Parallel Por t (EPP) and to configuration

registers

— Access to all configuration registers is through an In-

dex and a Data register, which can be relocated

within the ISA I/O address space

— 160-pin Plastic Quad Flatpack (PQFP) package

Page 4

4

Highlights

www.national.com

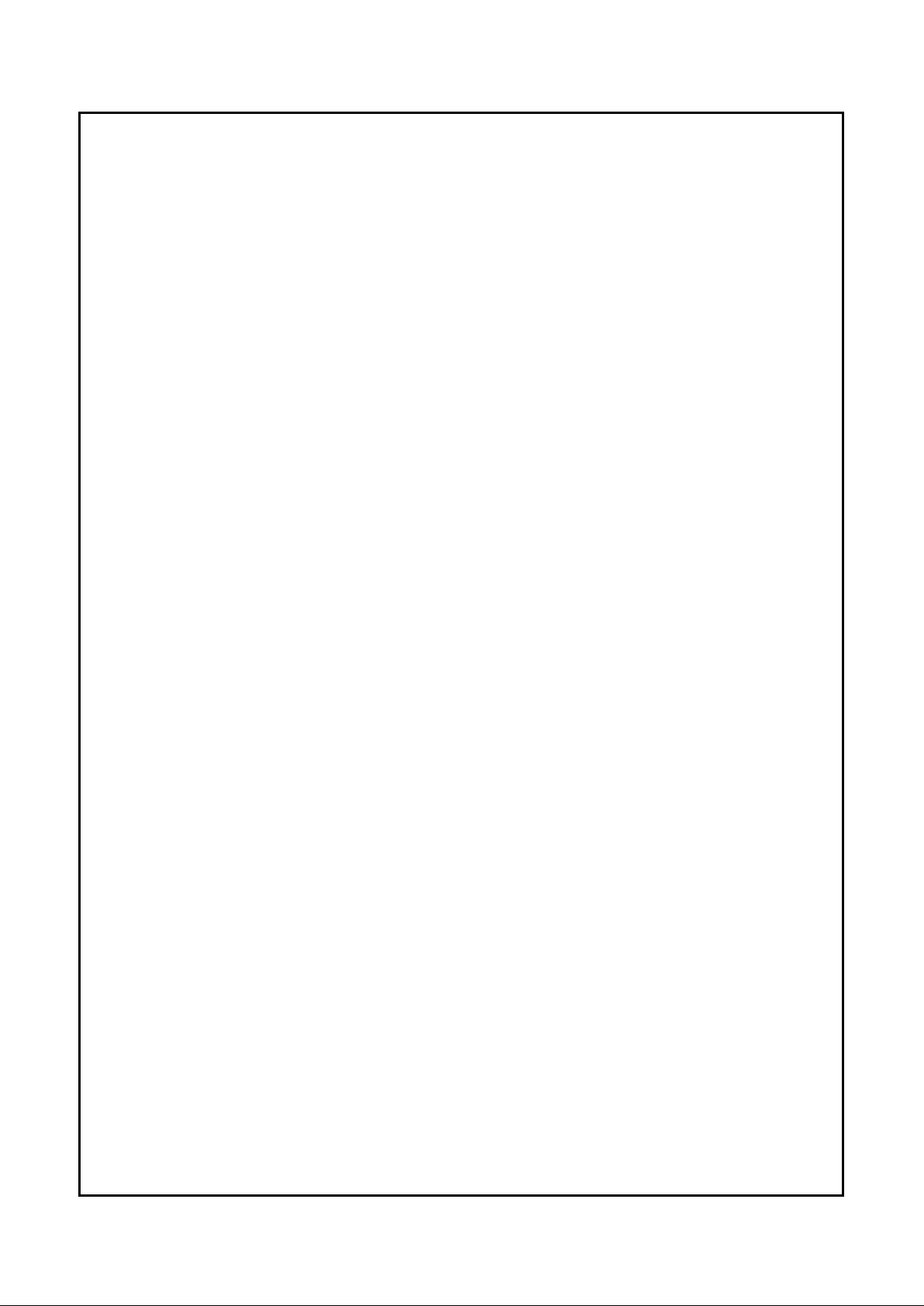

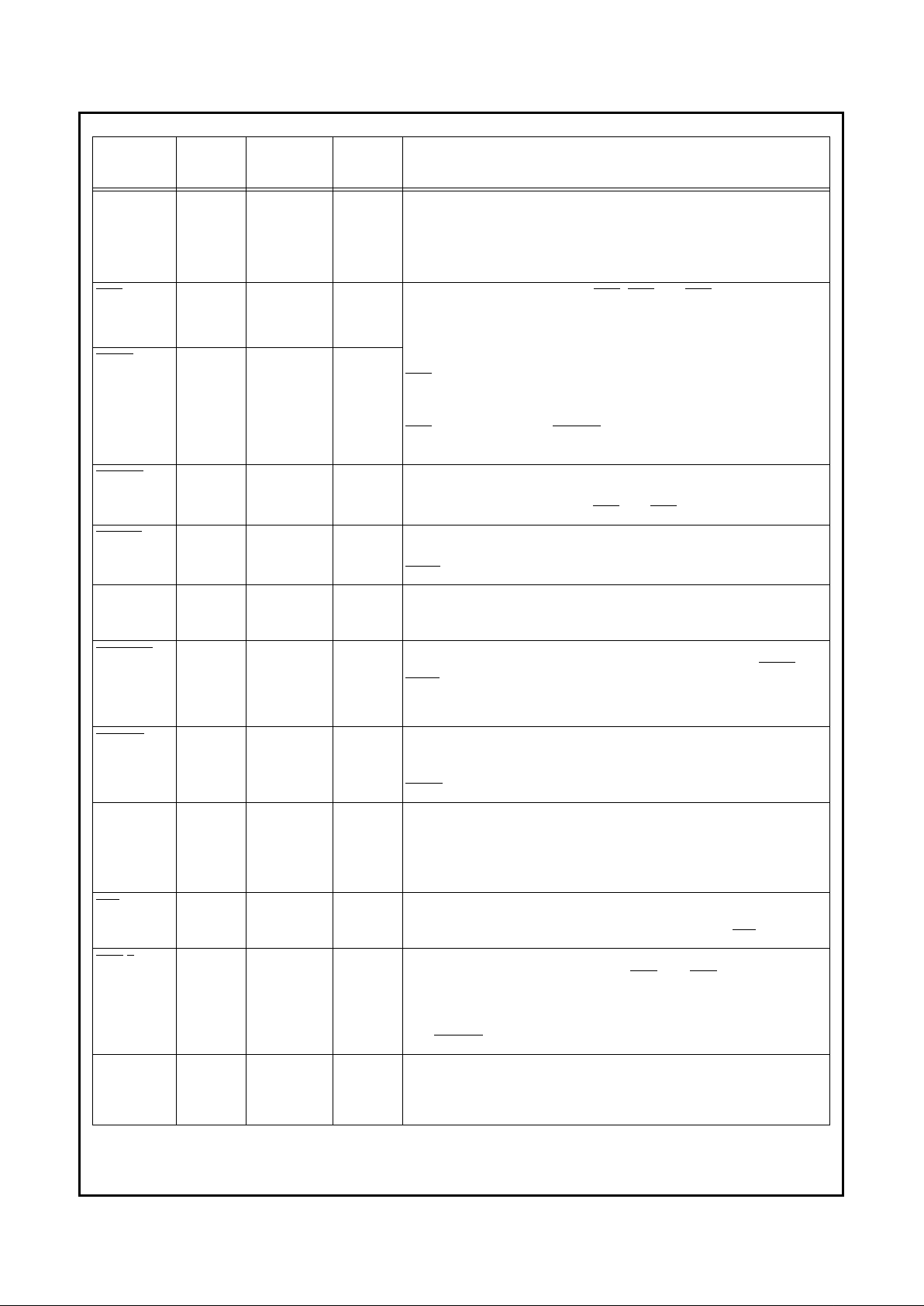

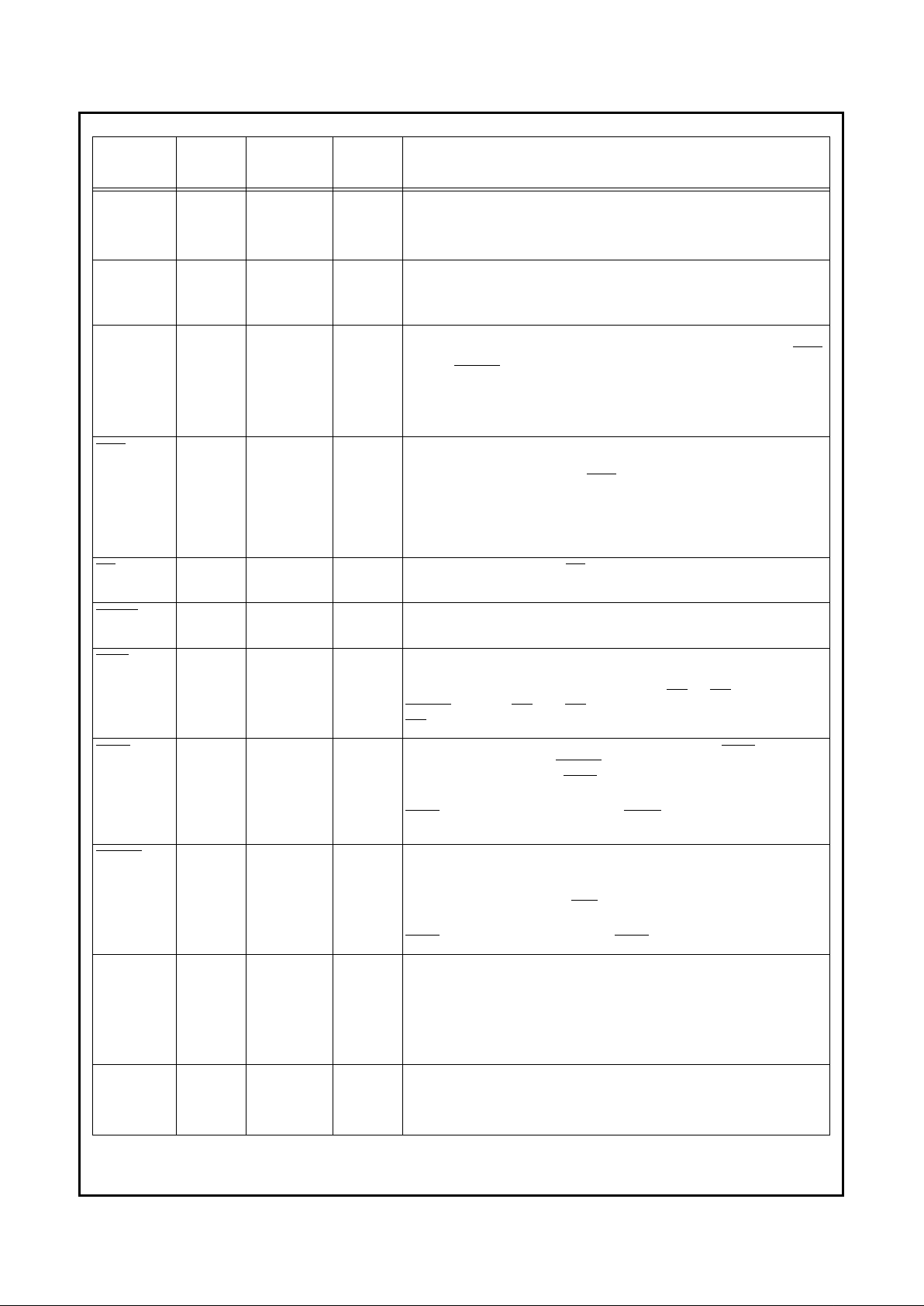

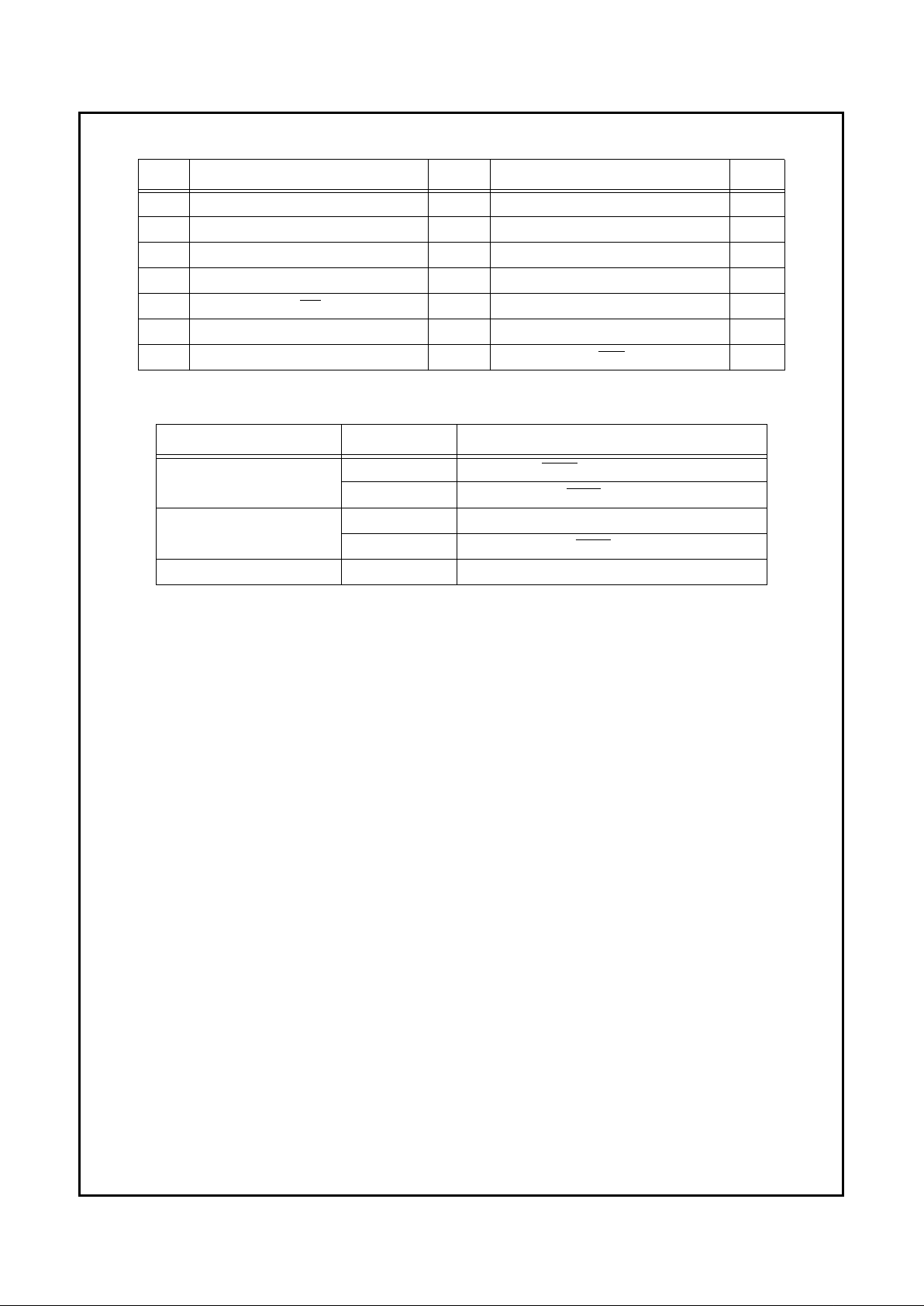

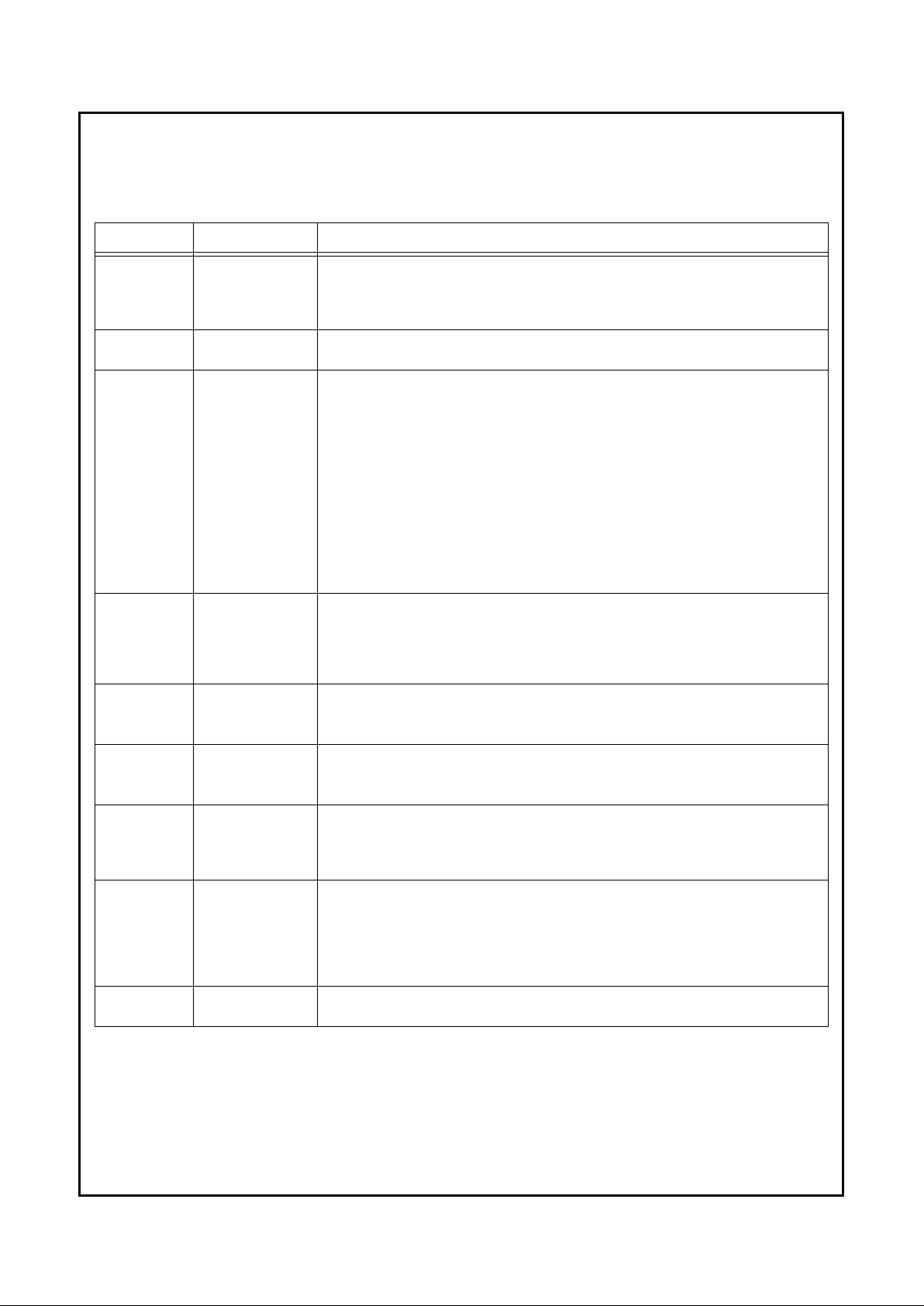

Basic Configuration

DRATE0

Parallel

Port

Connector

Configuration

Select Logic

Clock

EIA

Drivers

EIA

Drivers

FDC

ONCTL

ISA Bus

X1

MR

AEN

A15-0

D7-0

RD

WR

TC

PD7-0

SLIN/ASTRB

STB/WRITE

AFD/DSTRB

INIT

ACK

ERR

SLCT

PE

BUSY/

WAIT

BADDR1,0

CFG1,0

V

CCH

SWITCH

RING

SIN1

SOUT1

RTS1

DTR1/BOUT1

CTS1

DSR1

DCD1

RI1

SIN2

SOUT2

RTS2

DTR2/BOUT2

CTS2

DSR2

DCD2

RI2

RDATA

WDATA

WGATE

HDSEL

DIR

STEP

TRK0

INDEX

DSKCHG

WP

MTR1,0

DR1,0

DENSEL

IOCHRDY

ZWS

Real-Time Clock (RTC)

Crystal and Power

V

BAT

X1C X2C

DRQ3-0

DACK3-0

P17,16,12

P21,20

KBCLK

KBDAT

MDAT

MCLK

Keyboard I/O

Interface

(GPIO)

CS2,0

MSEN1,0

GPIO27-20

GPIO17-10

IRQ1

Infrared (IR)

Interface

IRRX2,1

IRTX

PC87317VUL

IRQ12-3

IRQ15-14

IRSL2-0

SELCS

X-Bus

XDCS

XD7-0

XDRD

WDO

POR

ID3-0

GPIO37-30

LED

LED

Power

Management

(PM)

Connector

General Purpose I/O

Page 5

5

Table of Contents

www.national.com

Table of Contents

Highlights.......................................................................................................................................................1

1.0 Signal/Pin Connection and Description

1.1 CONNECTION DIAGRAM .........................................................................................................16

1.2 SIGNAL/PIN DESCRIPTIONS ...................................................................................................17

2.0 Configuration

2.1 HARDWARE CONFIGURATION ...............................................................................................27

2.1.1 Wake Up Options ........................................................................................................27

2.1.2 The Index and Data Register Pair ...............................................................................27

2.1.3 The Strap Pins .............................................................................................................28

2.2 SOFTWARE CONFIGURATION ...............................................................................................28

2.2.1 Accessing the Configuration Registers ........................................................................28

2.2.2 Address Decoding .......................................................................................................28

2.3 THE CONFIGURATION REGISTERS .......................................................................................29

2.3.1 Standard Plug and Play (PnP) Register Definitions ....................................................30

2.3.2 Configuration Register Summary ................................................................................33

2.4 CARD CONTROL REGISTERS ................................................................................................37

2.4.1 PC87317 SID Register ................................................................................................37

2.4.2 PC97317 SID Register ................................................................................................37

2.4.3 SuperI/O Configuration 1 Register (SIOC1) ................................................................37

2.4.4 SuperI/O Configuration 2 Register (SIOC2) ................................................................38

2.4.5 Programmable Chip Select Configuration Index Register ...........................................38

2.4.6 Programmable Chip Select Configuration Data Register ............................................39

2.4.7 SuperI/O Configuration 3 Register (SIOC3) ................................................................39

2.4.8 PC97317 SRID Register ..............................................................................................39

2.4.9 SuperI/O Configuration F Register (SIOCF), Index 2Fh ..............................................40

2.5 KBC CONFIGURATION REGISTER (LOGICAL DEVICE 0) ....................................................40

2.5.1 SuperI/O KBC Configuration Register .........................................................................40

2.6 FDC CONFIGURATION REGISTERS (LOGICAL DEVICE 3) ..................................................40

2.6.1 SuperI/O FDC Configuration Register .........................................................................40

2.6.2 Drive ID Register .........................................................................................................41

2.7 PARALLEL PORT CONFIGURATION REGISTER (LOGICAL DEVICE 4) ...............................41

2.7.1 SuperI/O Parallel Port Configuration Register .............................................................41

2.8 UART2 AND INFRARED CONFIGURATION REGISTER (LOGICAL DEVICE 5) ....................42

2.8.1 SuperI/O UART2 Configuration Register .....................................................................42

2.9 UART1 CONFIGURATION REGISTER (LOGICAL DEVICE 6) ................................................42

2.9.1 SuperI/O UART1 Configuration Register .....................................................................42

2.10 PROGRAMMABLE CHIP SELECT CONFIGURATION REGISTERS ......................................42

2.10.1 CS0 Base Address MSB Register ...............................................................................43

2.10.2 CS0 Base Address LSB Register ................................................................................43

2.10.3 CS0 Configuration Register .........................................................................................43

2.10.4 Reserved .....................................................................................................................43

2.10.5 CS1 Base Address MSB Register ...............................................................................43

Page 6

6

Table of Contents

www.national.com

2.10.6 CS1 Base Address LSB Register ................................................................................43

2.10.7 CS1 Configuration Register .........................................................................................43

2.10.8 Reserved .....................................................................................................................44

2.10.9 CS2 Base Address MSB Register ...............................................................................44

2.10.10 CS2 Base Address LSB Register ................................................................................44

2.10.11 CS2 Configuration Register .........................................................................................44

2.10.12 Reserved, Second Level Indexes 0Bh-0Fh .................................................................44

2.10.13 Not Accessible, Second Level Indexes 10h-FFh .........................................................44

2.11 CONFIGURATION REGISTER BITMAPS ................................................................................44

3.0 Keyboard (and Mouse) Controller (KBC) (Logical Devices 0 and 1)

3.1 SYSTEM ARCHITECTURE .......................................................................................................47

3.2 FUNCTIONAL OVERVIEW .......................................................................................................48

3.3 DEVICE CONFIGURATION ......................................................................................................48

3.3.1 I/O Address Space ......................................................................................................48

3.3.2 Interrupt Request Signals ............................................................................................48

3.3.3 KBC Clock ...................................................................................................................49

3.3.4 Timer or Event Counter ...............................................................................................50

3.4 EXTERNAL I/O INTERFACES ..................................................................................................50

3.4.1 Keyboard and Mouse Interface ...................................................................................50

3.4.2 General Purpose I/O Signals .......................................................................................50

3.5 INTERNAL KBC - PC87317VUL INTERFACE ..........................................................................51

3.5.1 The KBC DBBOUT Register, Offset 60h, Read Only ..................................................52

3.5.2 The KBC DBBIN Register, Offset 60h (F1 Clear) or 64h (F1 Set), Write Only ............52

3.5.3 The KBC STATUS Register ........................................................................................52

3.6 INSTRUCTION TIMING .............................................................................................................52

4.0 Real-Time Clock (RTC) and Advanced Power Control (APC) (Logical Device 2)

4.1 RTC OVERVIEW .......................................................................................................................53

4.1.1 RTC Hardware and Functional Description .................................................................53

4.1.2 Timekeeping ................................................................................................................54

4.1.3 Power Management ....................................................................................................55

4.1.4 Interrupt Handling ........................................................................................................56

4.2 THE RTC REGISTERS .............................................................................................................56

4.2.1 RTC Control Register A (CRA) ....................................................................................56

4.2.2 RTC Control Register B (CRB) ....................................................................................57

4.2.3 RTC Control Register C (CRC) ...................................................................................58

4.2.4 RTC Control Register D (CRD) ...................................................................................58

4.2.5 Date-of-Month Alarm Register (DMAR ........................................................................59

4.2.6 Month Alarm Register (MAR) ......................................................................................59

4.2.7 Century Register (CR) .................................................................................................59

4.3 APC OVERVIEW .......................................................................................................................59

4.3.1 System Power States ..................................................................................................61

4.3.2 System Power Switching Logic ...................................................................................62

4.4 APC DETAILED DESCRIPTION ...............................................................................................62

Page 7

7

Table of Contents

www.national.com

4.4.1 The ONCTL Flip-Flop and Signal ................................................................................62

4.4.2 Entering Power States .................................................................................................65

4.4.3 System Power-Up and Power-Off Activation Event Description ..................................67

4.5 APC REGISTERS ......................................................................................................................69

4.5.1 APC Control Register 1 (APCR1) ................................................................................70

4.5.2 APC Control Register 2 (APCR2) ................................................................................70

4.5.3 APC Status Register (APSR) ......................................................................................71

4.5.4 Wake up Day of Week Register (WDWR) ...................................................................71

4.5.5 Wake up Date of Month Register (WDMR) .................................................................72

4.5.6 Wake up Month Register (WMR) .................................................................................72

4.5.7 Wake up Year Register (WYR) ....................................................................................72

4.5.8 RAM Lock Register (RLR) ...........................................................................................72

4.5.9 Wake up Century Register (WCR) ..............................................................................73

4.5.10 APC Control Register 3 (APCR3) ................................................................................73

4.5.11 APC Control Register 4 (APCR4), Bank 2, Index 4Ah ................................................74

4.5.12 APC Control Register 5 (APCR5) ................................................................................75

4.5.13 APC Control Register 6 (APCR6) ................................................................................75

4.5.14 APC Control Register 7 (APCR7) ................................................................................76

4.5.15 APC Status Register 1 (APSR1) .................................................................................77

4.5.16 Day-of-Month Alarm Address Register (DADDR) ........................................................77

4.5.17 Month Alarm Address Register (MADDR) ...................................................................77

4.5.18 Century Address Register (CADDR) ...........................................................................77

4.6 ACPI FIXED REGISTERS .........................................................................................................78

4.6.1 Power Management 1 Status Low Byte Register (PM1_STS_LOW) ..........................78

4.6.2 Power Management 1 Status High Byte Register (PM1_STS_HIGH) ........................78

4.6.3 Power Management 1 Enable Low Byte Register (PM1_EN_LOW) ...........................79

4.6.4 Power Management 1 Enable High Byte Register (PM1_EN_HIGH) .........................79

4.6.5 Power Management 1 Control Low Byte Register (PM1_CNT_LOW) ........................80

4.6.6 Power Management 1 Control High Byte Register (PM1_CNT_HIGH) .......................80

4.6.7 Power Management Timer Low Byte Register (PM1_TMR_LOW) .............................80

4.6.8 Power Management Timer Middle Byte Register (PM1_TMR_MID) ...........................81

4.6.9 Power Management Timer High Byte Register (PM1_TMR_HIGH) ............................81

4.6.10 Power Management Timer Extended Byte Register (PM1_TMR_EXT) ......................81

4.7 GENERAL PURPOSE EVENT REGISTERS ............................................................................81

4.7.1 General Purpose 1 Status Register (GP1_STS0) .......................................................81

4.7.2 General Purpose 1 Status 1 Register (GP1_STS1), Offset 01h ..................................82

4.7.3 General Purpose 1 Status 2 Register (GP1_STS2), Offset 02h ..................................82

4.7.4 General Purpose 1 Status 3 Register (GP1_STS3), Offset 03h ..................................82

4.7.5 General Purpose 1 Enable 0 Register (GP1_EN0) .....................................................82

4.7.6 General Purpose 1 Enable 1 Register (GP1_EN1), Offset 05h ...................................83

4.7.7 General Purpose 1 Enable 2 Register (GP1_EN2), Offset 06hr .................................83

4.7.8 General Purpose 1 Enable 3 Register (GP1_EN3), Offset 07h ...................................83

4.7.9 General Purpose 2 Enable 0 Register (GP2_EN0) .....................................................83

4.7.10 Bit 3 - IRRX2 Enable (IRRX2_E) .................................................................................83

4.7.11 SMI Command Register (SMI_CMD), Offset 0Ch .......................................................83

4.8 RTC AND APC REGISTER BITMAPS ......................................................................................84

4.8.1 RTC Register Bitmaps .................................................................................................84

Page 8

8

Table of Contents

www.national.com

4.8.2 APC Register Bitmaps .................................................................................................84

4.9 REGISTER BANK TABLES .......................................................................................................89

5.0 The Digital Floppy Disk Controller (FDC) (Logical Device 3)

5.1 FDC FUNCTIONS .....................................................................................................................92

5.1.1 Microprocessor Interface .............................................................................................92

5.1.2 System Operation Modes ............................................................................................92

5.2 DATA TRANSFER .....................................................................................................................93

5.2.1 Data Rates ...................................................................................................................93

5.2.2 The Data Separator .....................................................................................................93

5.2.3 Perpendicular Recording Mode Support .....................................................................94

5.2.4 Data Rate Selection .....................................................................................................94

5.2.5 Write Precompensation ...............................................................................................95

5.2.6 FDC Low-Power Mode Logic .......................................................................................95

5.2.7 Reset ...........................................................................................................................95

5.3 THE FDC REGISTERS .............................................................................................................96

5.3.1 Status Register A (SRA) ..............................................................................................96

5.3.2 Status Register B (SRB) ..............................................................................................97

5.3.3 Digital Output Register (DOR) .....................................................................................97

5.3.4 Tape Drive Register (TDR) ..........................................................................................99

5.3.5 Main Status Register (MSR) ......................................................................................100

5.3.6 Data Rate Select Register (DSR) ..............................................................................101

5.3.7 Data Register (FIFO) .................................................................................................102

5.3.8 Digital Input Register (DIR) ........................................................................................103

5.3.9 Configuration Control Register (CCR) .......................................................................104

5.4 THE PHASES OF FDC COMMANDS .....................................................................................104

5.4.1 Command Phase .......................................................................................................104

5.4.2 Execution Phase ........................................................................................................104

5.4.3 Result Phase .............................................................................................................106

5.4.4 Idle Phase ..................................................................................................................106

5.4.5 Drive Polling Phase ...................................................................................................106

5.5 THE RESULT PHASE STATUS REGISTERS ........................................................................107

5.5.1 Result Phase Status Register 0 (ST0) .......................................................................107

5.5.2 Result Phase Status Register 1 (ST1) .......................................................................107

5.5.3 Result Phase Status Register 2 (ST2) .......................................................................108

5.5.4 Result Phase Status Register 3 (ST3) .......................................................................109

5.6 FDC REGISTER BITMAPS .....................................................................................................109

5.6.1 Standard ....................................................................................................................109

5.6.2 Result Phase Status ..................................................................................................111

5.7 THE FDC COMMAND SET .....................................................................................................112

5.7.1 Abbreviations Used in FDC Commands ....................................................................113

5.7.2 The CONFIGURE Command ....................................................................................114

5.7.3 The DUMPREG Command .......................................................................................114

5.7.4 The FORMAT TRACK Command .............................................................................115

5.7.5 The INVALID Command ............................................................................................117

5.7.6 The LOCK Command ................................................................................................118

Page 9

9

Table of Contents

www.national.com

5.7.7 The MODE Command ...............................................................................................119

5.7.8 The NSC Command ..................................................................................................121

5.7.9 The PERPENDICULAR MODE Command ...............................................................121

5.7.10 The READ DATA Command .....................................................................................122

5.7.11 The READ DELETED DATA Command ....................................................................124

5.7.12 The READ ID Command ...........................................................................................125

5.7.13 The READ A TRACK Command ...............................................................................126

5.7.14 The RECALIBRATE Command .................................................................................127

5.7.15 The RELATIVE SEEK Command ..............................................................................127

5.7.16 The SCAN EQUAL, the SCAN LOW OR EQUAL and the SCAN HIGH OR EQUAL

Commands ................................................................................................................128

5.7.17 The SEEK Command ................................................................................................129

5.7.18 The SENSE DRIVE STATUS Command ..................................................................129

5.7.19 The SENSE INTERRUPT Command ........................................................................130

5.7.20 The SET TRACK Command ......................................................................................131

5.7.21 The SPECIFY Command ..........................................................................................131

5.7.22 The VERIFY Command .............................................................................................133

5.7.23 The VERSION Command ..........................................................................................134

5.7.24 The WRITE DATA Command ....................................................................................134

5.7.25 The WRITE DELETED DATA Command ..................................................................135

5.8 EXAMPLE OF A FOUR-DRIVE CIRCUIT ...............................................................................136

6.0 Parallel Port (Logical Device 4)

6.1 PARALLEL PORT CONFIGURATION ....................................................................................137

6.1.1 Parallel Port Operation Modes ..................................................................................137

6.1.2 Configuring Operation Modes ....................................................................................137

6.1.3 Output Pin Protection ................................................................................................137

6.2 STANDARD PARALLEL PORT (SPP) MODES ......................................................................137

6.2.1 SPP Modes Register Set ...........................................................................................138

6.2.2 SPP Data Register (DTR) ..........................................................................................138

6.2.3 Status Register (STR) ...............................................................................................139

6.2.4 SPP Control Register (CTR) ......................................................................................140

6.3 ENHANCED PARALLEL PORT (EPP) MODES ......................................................................141

6.3.1 EPP Register Set .......................................................................................................141

6.3.2 SPP or EPP Data Register (DTR) .............................................................................141

6.3.3 SPP or EPP Status Register (STR) ...........................................................................141

6.3.4 SPP or EPP Control Register (CTR) .........................................................................142

6.3.5 EPP Address Register (ADDR) .................................................................................142

6.3.6 EPP Data Register 0 (DATA0) ..................................................................................142

6.3.7 EPP Data Register 1 (DATA1) ..................................................................................142

6.3.8 EPP Data Register 2 (DATA2) ..................................................................................142

6.3.9 EPP Data Register 3 (DATA3) ..................................................................................143

6.3.10 EPP Mode Transfer Operations ................................................................................143

6.3.11 EPP 1.7 and 1.9 Zero Wait State Data Write and Read Operations .........................144

6.4 EXTENDED CAPABILITIES PARALLEL PORT (ECP) ...........................................................145

6.4.1 ECP Modes ...............................................................................................................145

6.4.2 Software Operation ....................................................................................................145

Page 10

10

Table of Contents

www.national.com

6.4.3 Hardware Operation ..................................................................................................145

6.5 ECP MODE REGISTERS ........................................................................................................145

6.5.1 Accessing the ECP Registers ....................................................................................146

6.5.2 Second Level Offsets ................................................................................................146

6.5.3 ECP Data Register (DATAR) .....................................................................................147

6.5.4 ECP Address FIFO (AFIFO) Register .......................................................................147

6.5.5 ECP Status Register (DSR) .......................................................................................147

6.5.6 ECP Control Register (DCR) .....................................................................................148

6.5.7 Parallel Port Data FIFO (CFIFO) Register .................................................................148

6.5.8 ECP Data FIFO (DFIFO) Register .............................................................................148

6.5.9 Test FIFO (TFIFO) Register ......................................................................................149

6.5.10 Configuration Register A (CNFGA) ...........................................................................149

6.5.11 Configuration Register B (CNFGB) ...........................................................................149

6.5.12 Extended Control Register (ECR) .............................................................................150

6.5.13 ECP Extended Index Register (EIR) .........................................................................151

6.5.14 ECP Extended Data Register (EDR) .........................................................................152

6.5.15 ECP Extended Auxiliary Status Register (EAR) ........................................................152

6.5.16 Control0 Register .......................................................................................................152

6.5.17 Control2 Register .......................................................................................................152

6.5.18 Control4 Register .......................................................................................................153

6.5.19 PP Confg0 Register ...................................................................................................153

6.6 DETAILED ECP MODE DESCRIPTIONS ...............................................................................154

6.6.1 Software Controlled Data Transfer

(Modes 000 and 001) ................................................................................................154

6.6.2 Automatic Data Transfer

(Modes 010 and 011) ................................................................................................154

6.6.3 Automatic Address and Data Transfers (Mode 100) .................................................156

6.6.4 FIFO Test Access (Mode 110) ..................................................................................156

6.6.5 Configuration Registers Access

(Mode 111) ................................................................................................................156

6.6.6 Interrupt Generation ..................................................................................................156

6.7 PARALLEL PORT REGISTER BITMAPS ...............................................................................157

6.7.1 EPP Modes ................................................................................................................157

6.7.2 ECP Modes ...............................................................................................................158

6.8 PARALLEL PORT PIN/SIGNAL LIST ......................................................................................160

7.0 Enhanced Serial Port with IR - UART2 (Logical Device 5)

7.1 FEATURES ..............................................................................................................................161

7.2 FUNCTIONAL MODES OVERVIEW .......................................................................................161

7.2.1 UART Modes: 16450 or 16550, and Extended ..........................................................161

7.2.2 Sharp-IR, IrDA SIR Infrared Modes ...........................................................................161

7.2.3 Consumer IR Mode ...................................................................................................161

7.3 REGISTER BANK OVERVIEW ...............................................................................................161

7.4 UART MODES – DETAILED DESCRIPTION ..........................................................................162

7.4.1 16450 or 16550 UART Mode .....................................................................................162

7.4.2 Extended UART Mode ...............................................................................................163

Page 11

11

Table of Contents

www.national.com

7.5 SHARP-IR MODE – DETAILED DESCRIPTION .....................................................................163

7.6 SIR MODE – DETAILED DESCRIPTION ................................................................................163

7.7 CONSUMER-IR MODE – DETAILED DESCRIPTION ............................................................164

7.7.1 Consumer-IR Transmission .......................................................................................164

7.7.2 Consumer-IR Reception ............................................................................................164

7.8 FIFO TIME-OUTS ....................................................................................................................165

7.8.1 UART, SIR or Sharp-IR Mode Time-Out Conditions .................................................165

7.8.2 Consumer-IR Mode Time-Out Conditions .................................................................165

7.8.3 Transmission Deferral ...............................................................................................165

7.9 AUTOMATIC FALLBACK TO A NON-EXTENDED UART MODE ..........................................165

7.11 BANK 0 – GLOBAL CONTROL AND STATUS REGISTERS .................................................166

7.11.1 Receiver Data Port (RXD) or the Transmitter Data Port (TXD) .................................166

7.11.2 Interrupt Enable Register (IER) .................................................................................167

7.11.3 Event Identification Register (EIR) ............................................................................168

7.11.4 FIFO Control Register (FCR) .....................................................................................170

7.11.5 Link Control Register (LCR) and Bank Selection Register (BSR) .............................171

7.11.6 Bank Selection Register (BSR) .................................................................................172

7.11.7 Modem/Mode Control Register (MCR) ......................................................................172

7.11.8 Link Status Register (LSR) ........................................................................................174

7.11.9 Modem Status Register (MSR) ..................................................................................175

7.11.10 Scratchpad Register (SPR) .......................................................................................175

7.11.11 Auxiliary Status and Control Register (ASCR) ..........................................................176

7.12 BANK 1 – THE LEGACY BAUD GENERATOR DIVISOR PORTS .........................................176

7.12.1 Legacy Baud Generator Divisor Ports (LBGD(L) and LBGD(H)), ..............................177

7.12.2 Link Control Register (LCR) and Bank Select Register (BSR) ..................................177

7.13 BANK 2 – EXTENDED CONTROL AND STATUS REGISTERS ............................................177

7.13.1 Baud Generator Divisor Ports, LSB (BGD(L)) and MSB (BGD(H)) ...........................178

7.13.2 Extended Control Register 1 (EXCR1) ......................................................................179

7.13.3 Link Control Register (LCR) and Bank Select Register (BSR) ..................................180

7.13.4 Extended Control and Status Register 2 (EXCR2) ....................................................180

7.13.5 Reserved Register .....................................................................................................180

7.13.6 TX_FIFO Current Level Register (TXFLV) ................................................................180

7.13.7 RX_FIFO Current Level Register (RXFLV) ...............................................................181

7.14 BANK 3 – MODULE REVISION ID AND SHADOW REGISTERS ..........................................181

7.14.1 Module Revision ID Register (MRID) ........................................................................181

7.14.2 Shadow of Link Control Register (SH_LCR) .............................................................181

7.14.3 Shadow of FIFO Control Register (SH_FCR) ............................................................182

7.14.4 Link Control Register (LCR) and Bank Select Register (BSR) ..................................182

7.15 BANK 4 – IR MODE SETUP REGISTER ................................................................................182

7.15.1 Reserved Registers ...................................................................................................182

7.15.2 Infrared Control Register 1 (IRCR1) ..........................................................................182

7.15.3 Link Control Register (LCR) and Bank Select Register (BSR) ..................................182

7.15.4 Reserved Registers ...................................................................................................182

7.16 BANK 5 – INFRARED CONTROL REGISTERS .....................................................................183

7.16.1 Reserved Registers ...................................................................................................183

Page 12

12

Table of Contents

www.national.com

7.16.2 (LCR/BSR) Register ..................................................................................................183

7.16.3 Infrared Control Register 2 (IRCR2) ..........................................................................183

7.16.4 Reserved Registers ...................................................................................................183

7.17 BANK 6 – INFRARED PHYSICAL LAYER CONFIGURATION REGISTERS .........................183

7.17.1 Infrared Control Register 3 (IRCR3) ..........................................................................183

7.17.2 Reserved Register .....................................................................................................184

7.17.3 SIR Pulse Width Register (SIR_PW) .........................................................................184

7.17.4 Link Control Register (LCR) and Bank Select Register (BSR) ..................................184

7.17.5 Reserved Registers ...................................................................................................184

7.18 BANK 7 – CONSUMER-IR AND OPTICAL TRANSCEIVER CONFIGURATION REGISTERS 184

7.18.1 Infrared Receiver Demodulator Control Register (IRRXDC) .....................................184

7.18.2 Infrared Transmitter Modulator Control Register (IRTXMC) ......................................185

7.18.3 Consumer-IR Configuration Register (RCCFG), .......................................................187

7.18.4 Link Control/Bank Select Registers (LCR/BSR) ........................................................188

7.18.5 Infrared Interface Configuration Register 1 (IRCFG1) ...............................................188

7.18.6 Reserved Register .....................................................................................................189

7.18.7 Infrared Interface Configuration 3 Register (IRCFG3) ...............................................189

7.18.8 Infrared Interface Configuration Register 4 (IRCFG4) ...............................................189

7.19 UART2 WITH IR REGISTER BITMAPS ..................................................................................190

8.0 Enhanced Serial Port - UART1 (Logical Device 6)

8.1 REGISTER BANK OVERVIEW ...............................................................................................195

8.2 DETAILED DESCRIPTION ......................................................................................................195

8.2.1 16450 or 16550 UART Mode .....................................................................................196

8.2.2 Extended UART Mode ...............................................................................................196

8.3 FIFO TIME-OUTS ....................................................................................................................196

8.4 AUTOMATIC FALLBACK TO A NON-EXTENDED UART MODE ..........................................197

8.4.1 Transmission Deferral ...............................................................................................197

8.5 BANK 0 – GLOBAL CONTROL AND STATUS REGISTERS .................................................197

8.5.1 Receiver Data Port (RXD) or the Transmitter Data Port (TXD) .................................197

8.5.2 Interrupt Enable Register (IER) .................................................................................198

8.5.3 Event Identification Register (EIR) ............................................................................199

8.5.4 FIFO Control Register (FCR) .....................................................................................200

8.5.5 Line Control Register (LCR) and Bank Selection Register (BSR) .............................201

8.5.6 Bank Selection Register (BSR) .................................................................................202

8.5.7 Modem/Mode Control Register (MCR) ......................................................................203

8.5.8 Line Status Register (LSR) ........................................................................................204

8.5.9 Modem Status Register (MSR) ..................................................................................205

8.5.10 Scratchpad Register (SPR) .......................................................................................205

8.5.11 Auxiliary Status and Control Register (ASCR) ..........................................................205

8.6 BANK 1 – THE LEGACY BAUD GENERATOR DIVISOR PORTS .........................................206

8.6.1 Legacy Baud Generator Divisor Ports (LBGD(L) and LBGD(H)), ..............................206

8.6.2 Line Control Register (LCR) and Bank Select Register (BSR) ..................................207

8.7 BANK 2 – EXTENDED CONTROL AND STATUS REGISTERS ............................................207

8.7.1 Baud Generator Divisor Ports, LSB (BGD(L)) and MSB (BGD(H)) ...........................207

Page 13

13

Table of Contents

www.national.com

8.7.2 Extended Control Register 1 (EXCR1) ......................................................................208

8.7.3 Line Control Register (LCR) and Bank Select Register (BSR) ..................................209

8.7.4 Extended Control and Status Register 2 (EXCR2) ....................................................209

8.7.5 Reserved Register .....................................................................................................209

8.7.6 TX_FIFO Current Level Register (TXFLV) ................................................................209

8.7.7 RX_FIFO Current Level Register (RXFLV) ...............................................................210

8.8 BANK 3 – MODULE REVISION ID AND SHADOW REGISTERS ..........................................210

8.8.1 Module Revision ID Register (MRID) ........................................................................210

8.8.2 Shadow of Line Control Register (SH_LCR) .............................................................210

8.8.3 Shadow of FIFO Control Register (SH_FCR) ............................................................211

8.8.4 Line Control Register (LCR) and Bank Select Register (BSR) ..................................211

8.9 UART1 REGISTER BITMAPS .................................................................................................211

9.0 General Purpose Input and Output (GPIO) Ports (Logical Device 7) and Chip

Select Output Signals

9.1 GPIO PORT ACTIVATION ......................................................................................................215

9.2 GPIO CONTROL REGISTERS ...............................................................................................215

9.2.1 Special GPIO Signal Features ...................................................................................215

9.2.2 Reading and Writing to GPIO Pins ............................................................................215

9.2.3 Multiplexed GPIO Signals ..........................................................................................215

9.2.4 Multiplexed GPIO Signal Selection ............................................................................215

9.3 PROGRAMMABLE CHIP SELECT OUTPUT SIGNALS .........................................................216

10.0 Power Management (Logical Device 8)

10.1 POWER MANAGEMENT OPTIONS .......................................................................................218

10.1.1 Configuration Options ................................................................................................218

10.1.2 WATCHDOG Feature ................................................................................................218

10.2 POWER MANAGEMENT REGISTERS ...................................................................................218

10.2.1 Power Management Index Register ..........................................................................218

10.2.2 Power Management Data Register ...........................................................................219

10.2.3 Function Enable Register 1 (FER1) ...........................................................................219

10.2.4 Function Enable Register 2 (FER2) ...........................................................................219

10.2.5 Power Management Control Register (PMC1) ..........................................................220

10.2.6 Power Management Control 2 Register (PMC2) .......................................................221

10.2.7 Power Management Control 3 Register (PMC3) .......................................................221

10.2.8 WATCHDOG Time-Out Register (WDTO) ................................................................222

10.2.9 WATCHDOG Configuration Register (WDCF) ..........................................................222

10.2.10 WATCHDOG Status Register (WDST) ......................................................................223

10.2.11 PM1 Event Base Address Register (Bits 7-0) ............................................................223

10.2.12 PM1 Event Base Address Register (Bits 15-8) ..........................................................223

10.2.13 PM Timer Base Address (Bits 7-0) ............................................................................223

10.2.14 PM Timer Base Address Register (Bits 15-8) ............................................................224

10.2.15 PM1 Control Base Address Register (Bits 7-0) .........................................................224

10.2.16 PM1 Control Base Address Register (Bits 15-8) .......................................................224

10.2.17 General Purpose Status Base Address Register (Bits 7-0) .......................................224

10.2.18 General Purpose Status Base Address Register (Bits 15-8) .....................................224

Page 14

14

Table of Contents

www.national.com

10.2.19 ACPI Support Register ..............................................................................................225

10.3 POWER MANAGEMENT REGISTER BITMAPS ....................................................................226

11.0 X-Bus Data Buffer

12.0 The Internal Clock

12.1 THE CLOCK SOURCE ............................................................................................................230

12.2 THE INTERNAL ON-CHIP CLOCK MULTIPLIER ...................................................................230

12.3 SPECIFICATIONS ...................................................................................................................230

12.4 POWER-ON PROCEDURE WHEN CFG0 = 0 ........................................................................230

13.0 Interrupt and DMA Mapping

13.1 IRQ MAPPING .........................................................................................................................231

13.2 DMA MAPPING .......................................................................................................................231

14.0 Device Specifications

14.1 GENERAL DC ELECTRICAL CHARACTERISTICS ...............................................................232

14.1.1 Recommended Operating Conditions .......................................................................232

14.1.2 Absolute Maximum Ratings .......................................................................................232

14.1.3 Capacitance ...............................................................................................................232

14.1.4 Power Consumption Under Recommended Operating Conditions ...........................233

14.2 DC CHARACTERISTICS OF PINS, BY GROUP ....................................................................233

14.2.1 Group 1 ......................................................................................................................233

14.2.2 Group 2 ......................................................................................................................234

14.2.3 Group 3 ......................................................................................................................234

14.2.4 Group 4 ......................................................................................................................235

14.2.5 Group 5 ......................................................................................................................235

14.2.6 Group 6 ......................................................................................................................235

14.2.7 Group 7 ......................................................................................................................236

14.2.8 Group 8 ......................................................................................................................236

14.2.9 Group 9 ......................................................................................................................237

14.2.10 Group 10 ....................................................................................................................237

14.2.11 Group 11 ....................................................................................................................238

14.2.12 Group 12 ....................................................................................................................238

14.2.13 Group 13 ....................................................................................................................239

14.2.14 Group 14 ....................................................................................................................239

14.2.15 Group 15 ....................................................................................................................240

14.2.16 Group 16 ....................................................................................................................240

14.2.17 Group 17 ....................................................................................................................240

14.2.18 Group 18 ....................................................................................................................240

14.2.19 Group 19 ....................................................................................................................241

14.2.20 Group 20 ....................................................................................................................241

14.2.21 Group 21 ....................................................................................................................241

14.2.22 Group 22 ....................................................................................................................241

14.2.23 Group 23 ....................................................................................................................241

14.2.24 Group 24 ....................................................................................................................242

Page 15

15

Table of Contents

www.national.com

14.2.25 Group 25 ....................................................................................................................242

14.2.26 Group 26 ....................................................................................................................243

14.2.27 Group 27 ....................................................................................................................243

14.2.28 Group 28 ....................................................................................................................243

14.3 AC ELECTRICAL CHARACTERISTICS ..................................................................................244

14.3.1 AC Test Conditions TA = 0 °C to 70 °C, VDD = 5.0 V ±10% ......................................244

14.3.2 Clock Timing ..............................................................................................................244

14.3.3 Microprocessor Interface Timing ...............................................................................245

14.3.4 Baud Output Timing ...................................................................................................247

14.3.5 Transmitter Timing .....................................................................................................248

14.3.6 Receiver Timing .........................................................................................................249

14.3.7 UART, Sharp-IR, SIR and Consumer Remote Control Timing ..................................251

14.3.8 IRSLn Write Timing ...................................................................................................252

14.3.9 Modem Control Timing ..............................................................................................252

14.3.10 DMA Timing ...............................................................................................................253

14.3.11 Reset Timing .............................................................................................................256

14.3.12 Write Data Timing ......................................................................................................257

14.3.13 Drive Control Timing ..................................................................................................258

14.3.14 Read Data Timing ......................................................................................................258

14.3.15 Parallel Port Timing ...................................................................................................259

14.3.16 Enhanced Parallel Port 1.7 Timing ............................................................................260

14.3.17 Enhanced Parallel Port 1.9 Timing ............................................................................261

14.3.18 Extended Capabilities Port (ECP) Timing ..................................................................262

14.3.19 GPIO Write Timing ....................................................................................................263

14.3.20 RTC Timing ...............................................................................................................263

14.3.21 APC Timing ...............................................................................................................264

14.3.22 Chip Select Timing ....................................................................................................267

14.3.23 LED Timing ................................................................................................................267

Glossary .....................................................................................................................................................268

Page 16

Signal/Pin Connection and Description

16

1.0 Signal/Pin Connection and Description

www.national.com

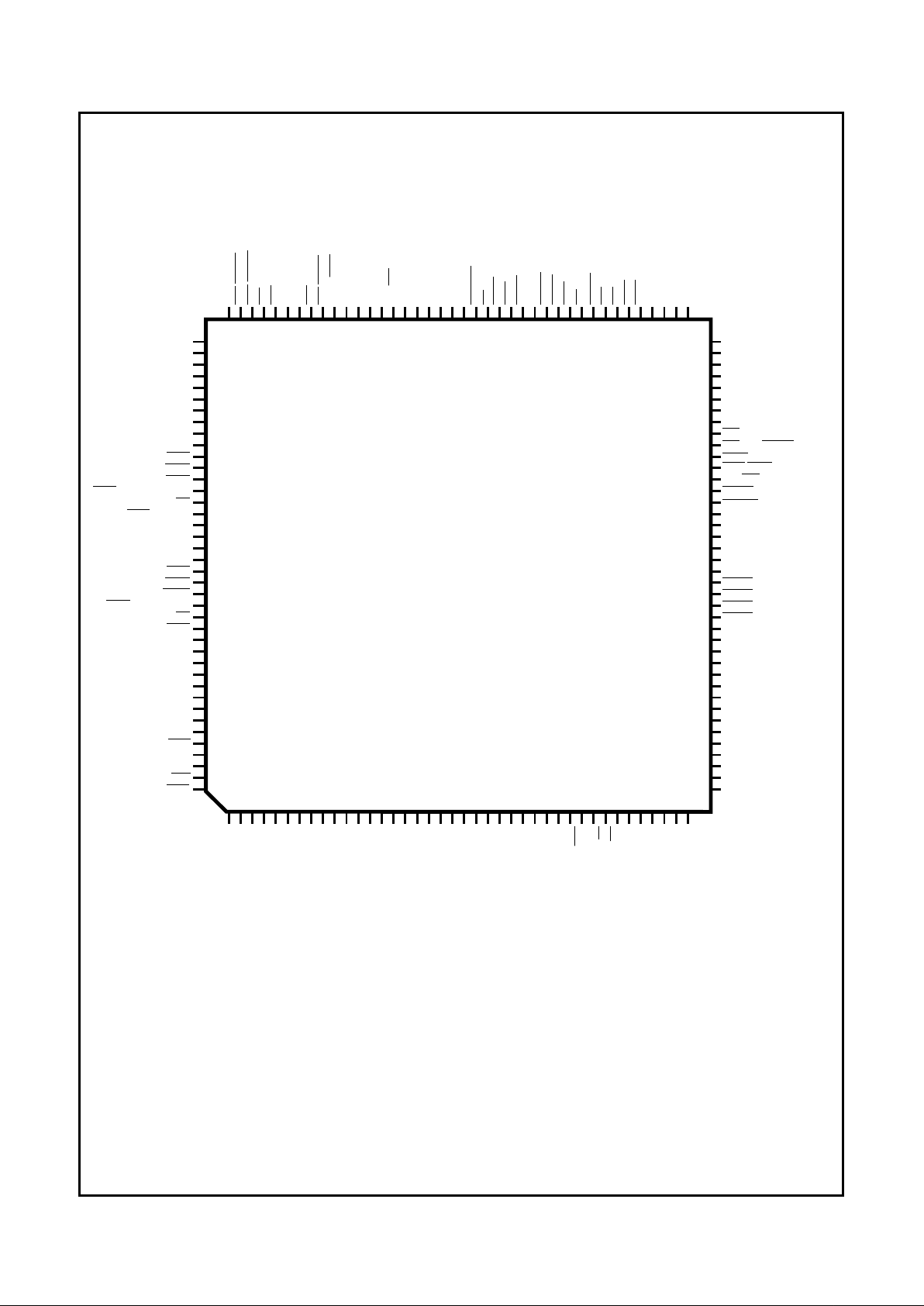

1.0 Signal/Pin Connection and Description

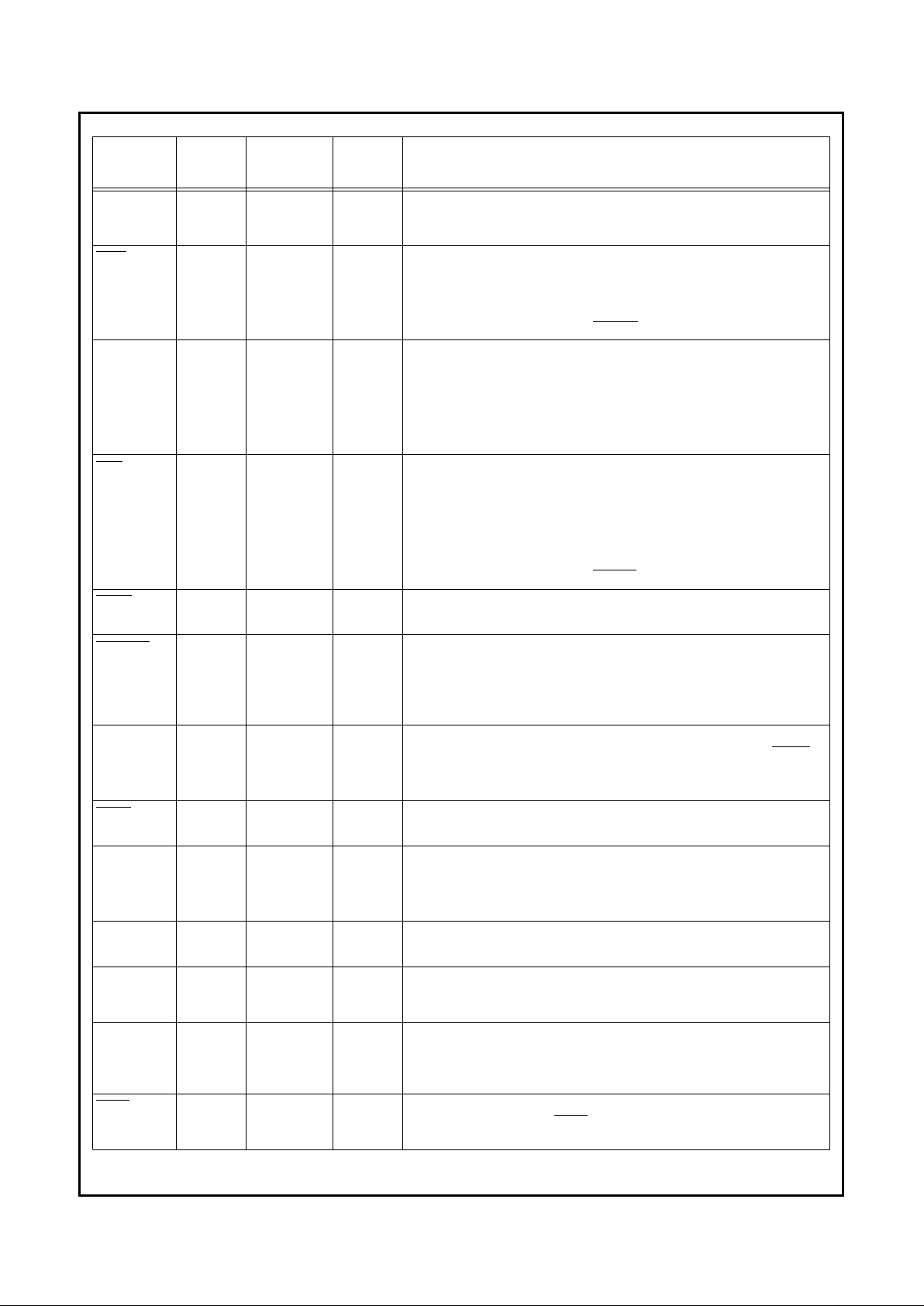

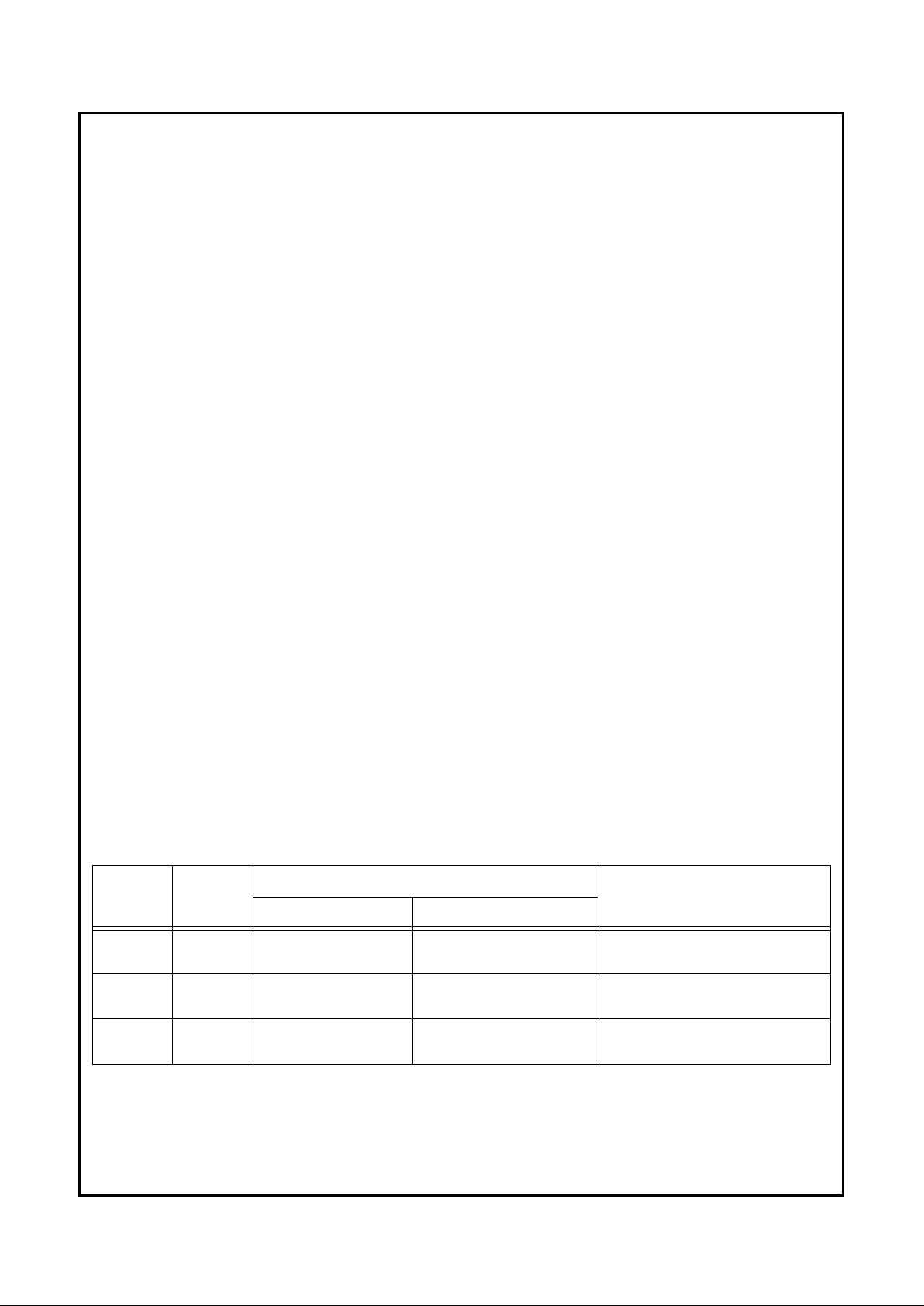

1.1 CONNECTION DIAGRAM

80

75

70

65

60

55

50

1 5 10 15 20 25 30

859095100

4035

PC87317VUL

105110115120

45

41

81

121

125

130

135

140

145

150

155

160

A1

A2

V

SS

V

DD

A3A4A5A6A7A8A9

A10

A11

A12

A13

IOCHRDY

RD

ZWS

WGATE

TRK0WPRDATA

HDSEL

A0

MTR1

DSKCHG

DIR

STEP

WDATA

MSEN1

DENSEL

INDEX

MTR0

DR1

DR0

XDRD/ID3

MSEN0

V

DD

P21

P20

P17

P16/GPIO25

P12/

CS0

GPIO10

GPIO11

GPIO12

GPIO13

CS2/XD1

STB/WRITE

V

SS

V

DD

SLIN/ASTRB

SLCT

PE

BUSY/

WAIT

ACK

V

DD

INIT

D7

CS1/XD0/CSOUT-NSC-Test

X1

V

SS

D0D1D2D3D4D5D6

MR

X2C

V

CCH

A15

A14

V

BAT

X1C

VSSVDDKBCLK

KBDAT

MDAT

MCLK

IRQ15

IRQ14

IRQ12

IRQ11

DACK3

DRATE0

DTR1/BADDR0/BOUT1

RI1

DCD1

DSR1

SIN1

RTS1/BADDR1

SOUT1/CFG0

CTS1

IRQ10

AEN

WR

TC

IRQ9

IRQ8

IRQ7

IRQ6

IRQ1

IRQ3

IRQ4

IRQ5

GPIO14

GPIO15/PME2

GPIO16/PME1

GPIO17/WDO

GPIO20/IRSL1/ID1

GPIO21/IRSL0/IRSL2/ID2

GPIO22/POR

V

SS

V

DD

DRQ1

DRQ0

DACK2

DACK1

DACK0

DRQ2

DRQ3

ERR

V

SS

V

SS

V

SS

DTR2/CFG1/BOUT2

GPIO33/RI2

GPIO31/DCD2

GPIO32/DSR2

GPIO35/SIN2

GPIO34/RTS2

GPIO36/SOUT2

GPIO30/CTS2

AFD/DSTRB

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

V

SS

IRTX

GPIO24/IRRX1

GPIO37/IRRX2/IRSL0/ID0

IRSL1/ID1/XD7

IRSL2/SELCS/GPIO21/XD6

GPIO27/XD5

GPIO26/XD4

GPIO25/XD3

GPIO24/XD2

LED/

CS0

ONCTL

SWITCH

RING/XDCS

GPIO23/

RING

PlasticQuad Flatpack (PQFP), EIAJ

Order Number PC87317VUL/PC97317VUL

NS Package Number VUL160A

Page 17

Signal/Pin Connection and Description

SIGNAL/PIN DESCRIPTIONS

17

www.national.com

1.2 SIGNAL/PIN DESCRIPTIONS

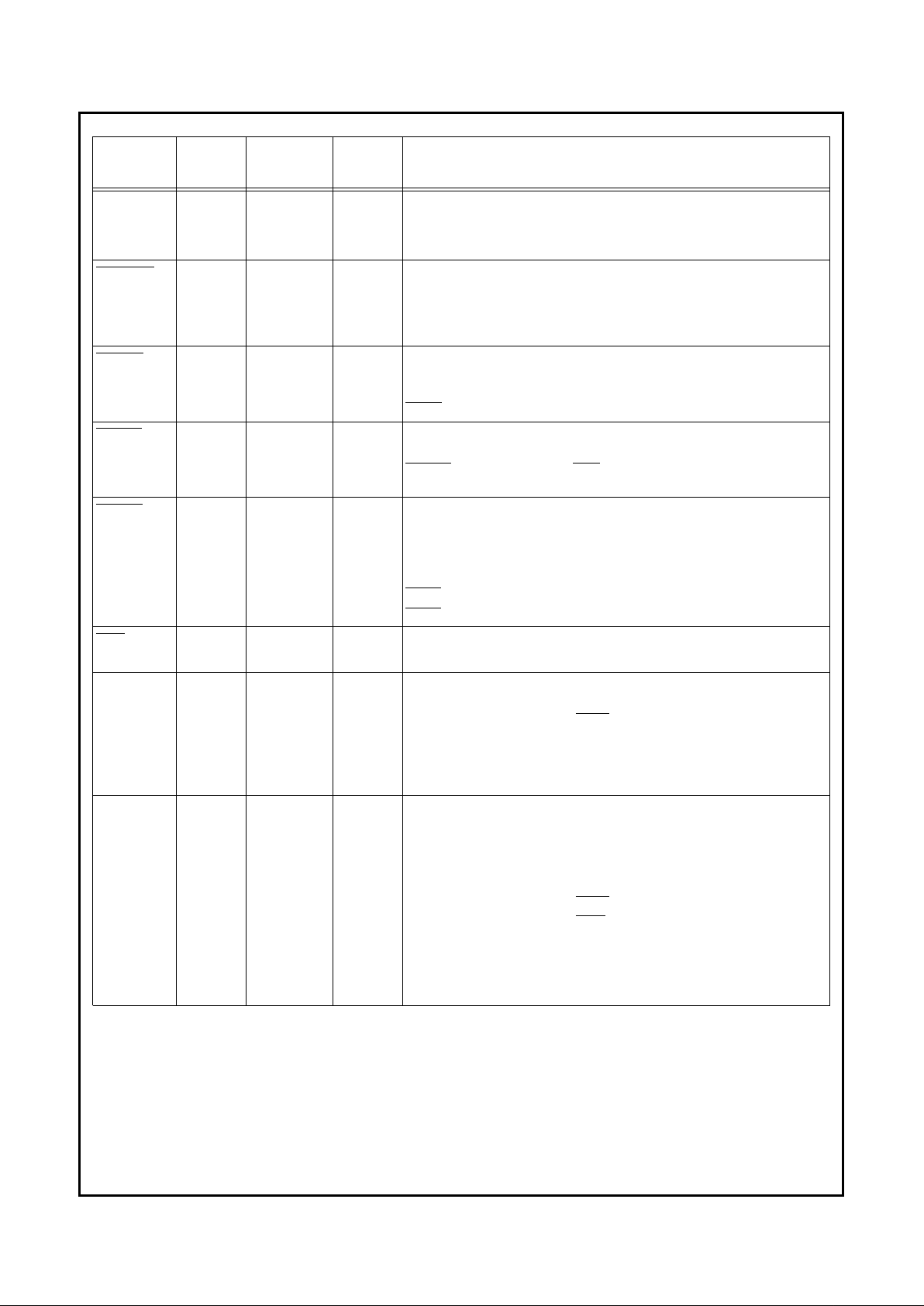

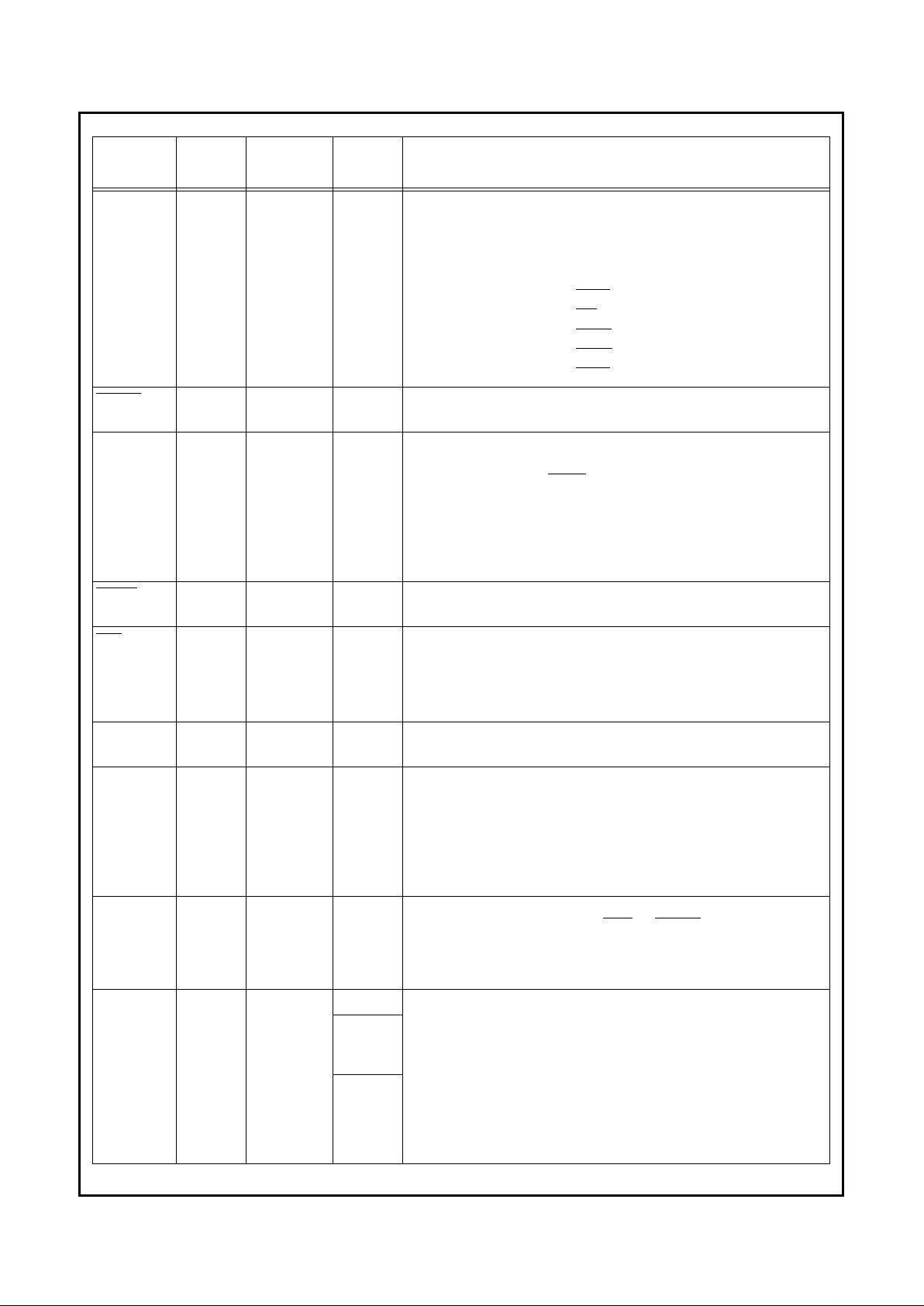

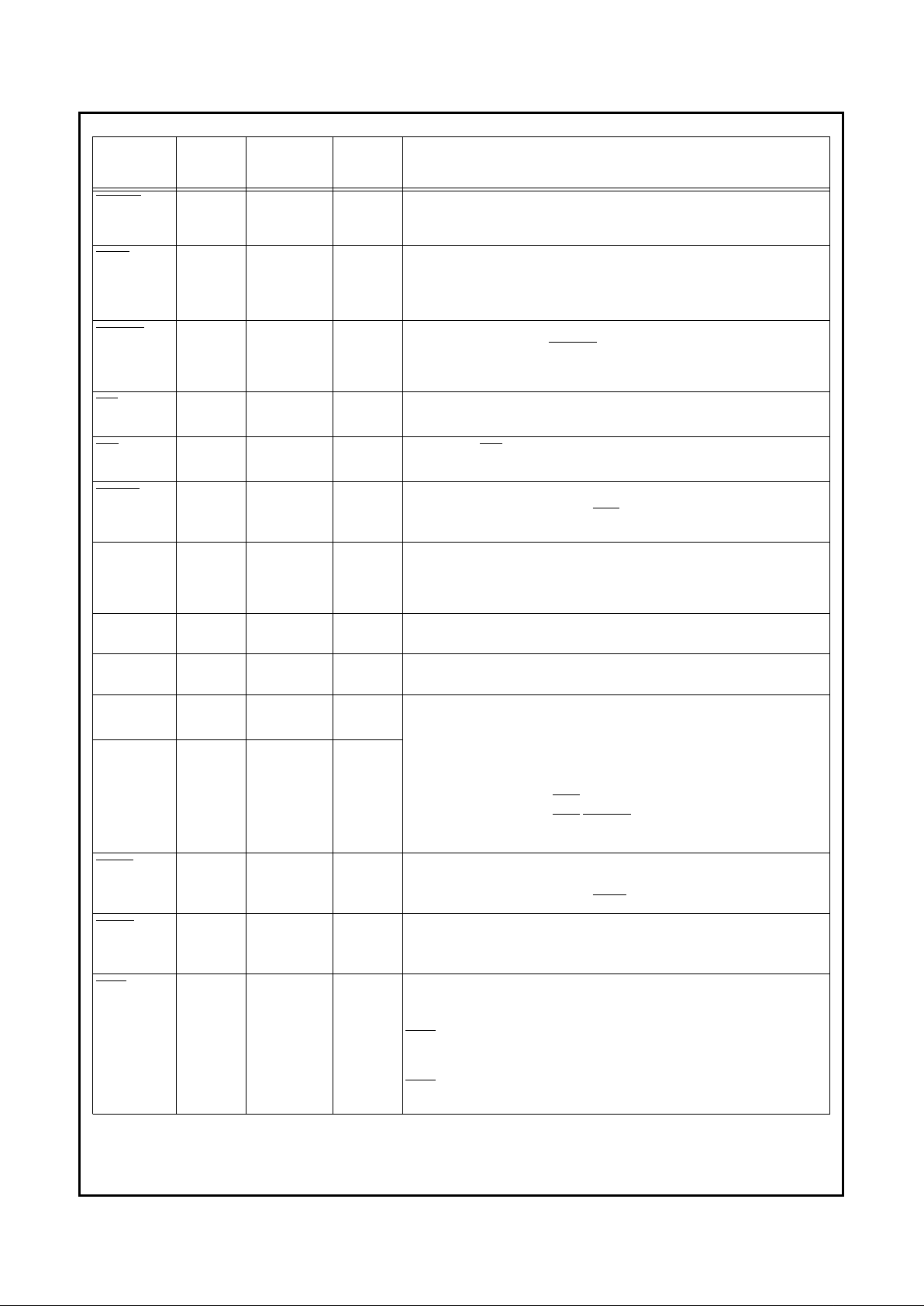

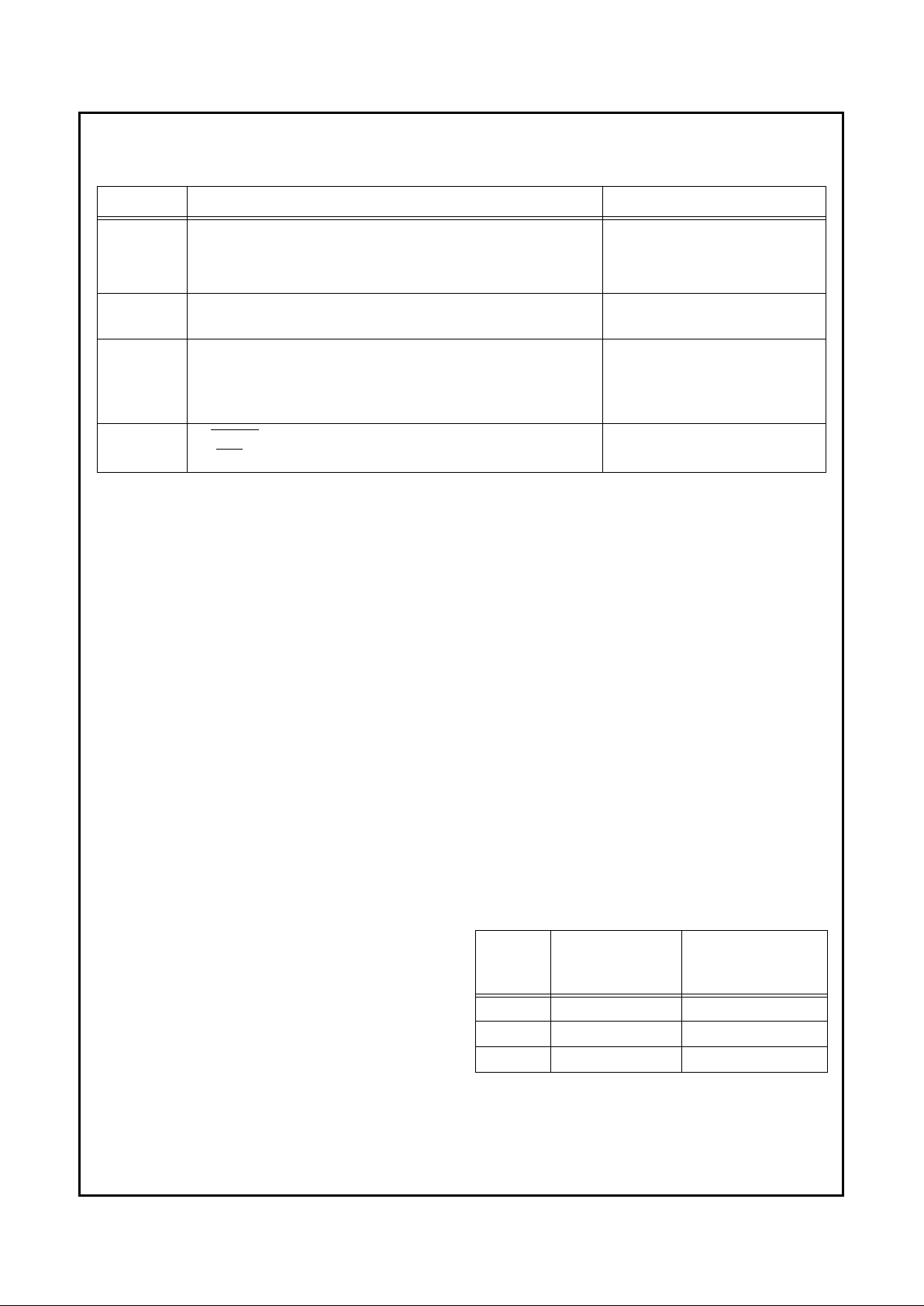

TABLE 1-1 "Signal/Pin Description Table" lists the signals

of the PC87317VUL in alphabetical order and shows the

pin(s) associated with each. TABLE 1-2 "Multiplexed X-Bus

Data Buffer (XDB) Pins" on page 25 lists the X-Bus Data

Buffer (XDB) signals that are multiplexed and TABLE 1-6

"Pins with a Strap Function During Reset" on page 26 lists

the pins that have strap functions during reset.

The Module column indicates the functional module that is

associated with these pins. In this column, the System label

indicates internal functions that are common to more than

one module. The I/O and Group # column describes whether the pin is an input, output, or bidirectional pin (marked as

Input, Output or I/O, respectively).

TABLE 1-1. Signal/Pin Description Table

Signal/Pin

Name

Pin

Number

Module

I/O and

Group #

Function

A15-0 29-26,

23-12

ISA-Bus Input

Group 1

ISA-Bus Address – A15-0 are used for address decoding on any

access except DMA accesses, on condition that the AEN signal is

low.

See Section 2.2.2 on page 28.

ACK 113 Parallel Port Input

Group 3

Acknowledge – This input signal is pulsed low by the printer to

indicate that it has received data from the parallel port. This pin is

internally connected to a weak pull-up.

AFD 119 Parallel Por t I/O

Group 13

Automatic Feed – When this signal is low the printer should

automatically feed a line after printing each line. This pin is in TRISTATE after a 0 is loaded into the corresponding control register bit.

An external 4.7 KΩ pull-up resistor should be attached to this pin.

For Input mode see bit 5 in Section 6.5.16 on page 152.

This signal is multiplexed with

DSTRB. See TABLE 6-12 on page 160

for more information.

AEN 30 ISA-Bus Input

Group 1

DMA Address Enable – This input signal disables function selection

via A15-0 when it is high. Access during DMA transfer is not affected

by this signal.

ASTRB 118 Parallel Port Output

Group 13

Address Strobe (EPP) – This signal is used in EPP mode as an

address strobe. It is active low.

This signal is multiplexed with

SLIN.See TABLE 6-12 on page 160 for

more information.

BADDR1,0 136, 134 Configuration Input

Group 5

Base Address Strap Pins 0 and 1 – These pins determine the base

addresses of the Index and Data registers, the value of the Plug and

Play ISA Serial Identifier and the configuration state immediately after

reset. These pins are pulled down by internal 30 KΩ resistors.

External 10 KΩ pull-up resistors to V

DD

should be employed.

BADDR1 is multiplexed with

RTS1.

BADDR0 is multiplexed with

DTR1 and BOUT1.

See TABLE 2-2 on page 28 and Section 2.1 on page 27.

BOUT2,1 148, 138 UART1,

UART 2

Output

Group 17

Baud Output – This multi-function pin provides the associated serial

channel Baud Rate generator output signal if test mode is selected,

i.e., bit 7 of the EXCR1 register is set. See “Bit 7 - Baud Generator

Test (BTEST)” on page 180.

After Master Reset this pin provides the SOUT function.

BOUT2 is multiplexed with DTR2 and CFG1.

BOUT1 is multiplexed with DTR1 and BADDR0.

BUSY 111 Parallel Port Input

Group 2

Busy – This pin is set to high by the printer when it cannot accept

another character. It is internally connected to a weak pull-down

resistor.

This signal is multiplexed with