Page 1

- March 1998

Highlights

www.national.com

©

1998 National Semiconductor Corporation

PRELIMINARY

April 1998

PC87309 SuperI/O Plug and Play Compatible Chip

in Compact 100-Pin VLJ Packaging

Highlights

General Description

The PC87309 is a single-chip solution to the most commonly used ISA, EISA and MicroChannel

®

peripherals in a compact, 100-pin VLJ packaging. This fully Plug and Play (PnP)

and PC97 compatible chip conforms to the

Plug and Play

ISA Specification

Version 1.0a, May 5, 1994, and meets

specifications defined in the

PC97 Hardware Design Guide

.

The PC87309 incorporates: a Floppy Disk Controller (FDC),

a Mouse and Keyboard Controller (KBC), two enhanced

UARTs, one of which is with Infrared (IR) support, a full

IEEE 1284parallel port and support for Power Management

(PM). The chip also provides a separate configuration register set for each module.

The Infrared (IR) interface complies with the HP-SIR and

SHARP-IR standards, and supports all four basic protocols

for Consumer Remote Control circuitry (RC-5, RC-6, NEC,

RCA and RECS 80).

For flexible UART and IR support, the PC87309 offers two

operation modes:

●

Mode 1: Full-IR Mode

UART1 works as UART; UART2 works as fully IRcompliant device

●

Mode 2: Two-UART Mode

Either both UARTs work as UARTs, or UART1 works

as UART and UART2 works as partially IR-compliant

device, providing only IRRX and IRTX support

Outstanding Features

●

Full SuperI/O functionality in compact, cost-effective

100-pin VLJ packaging

●

PC97 compliant

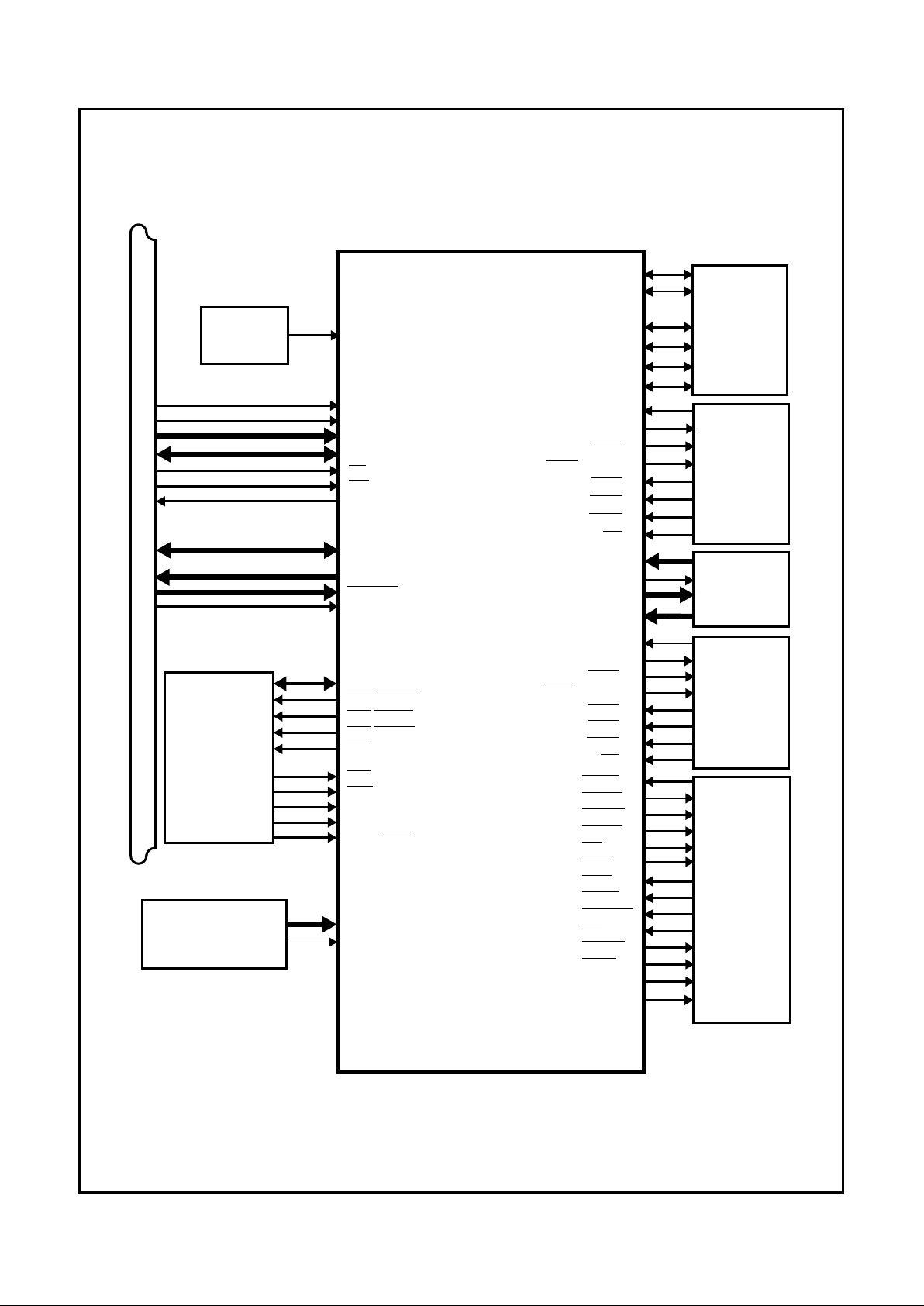

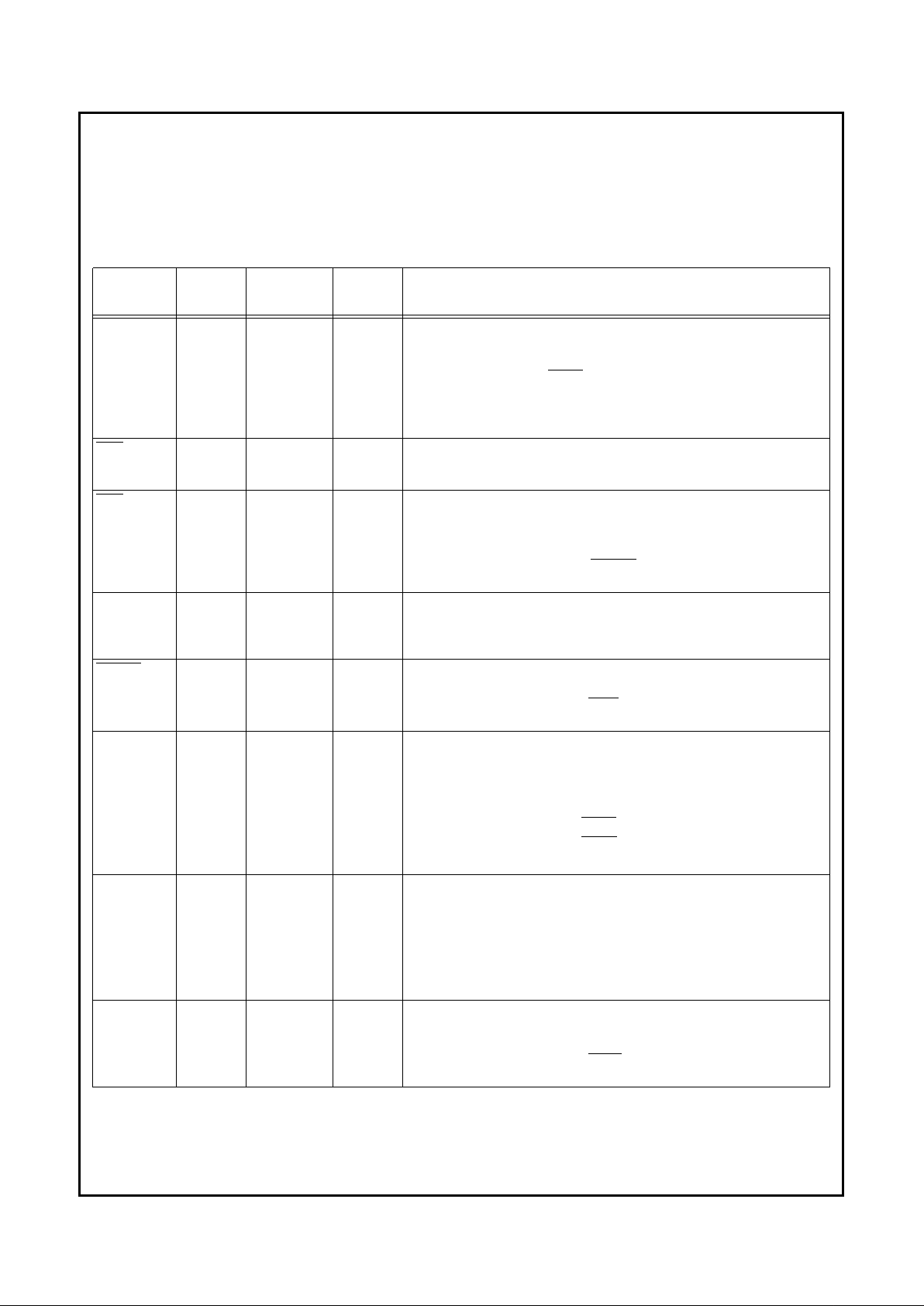

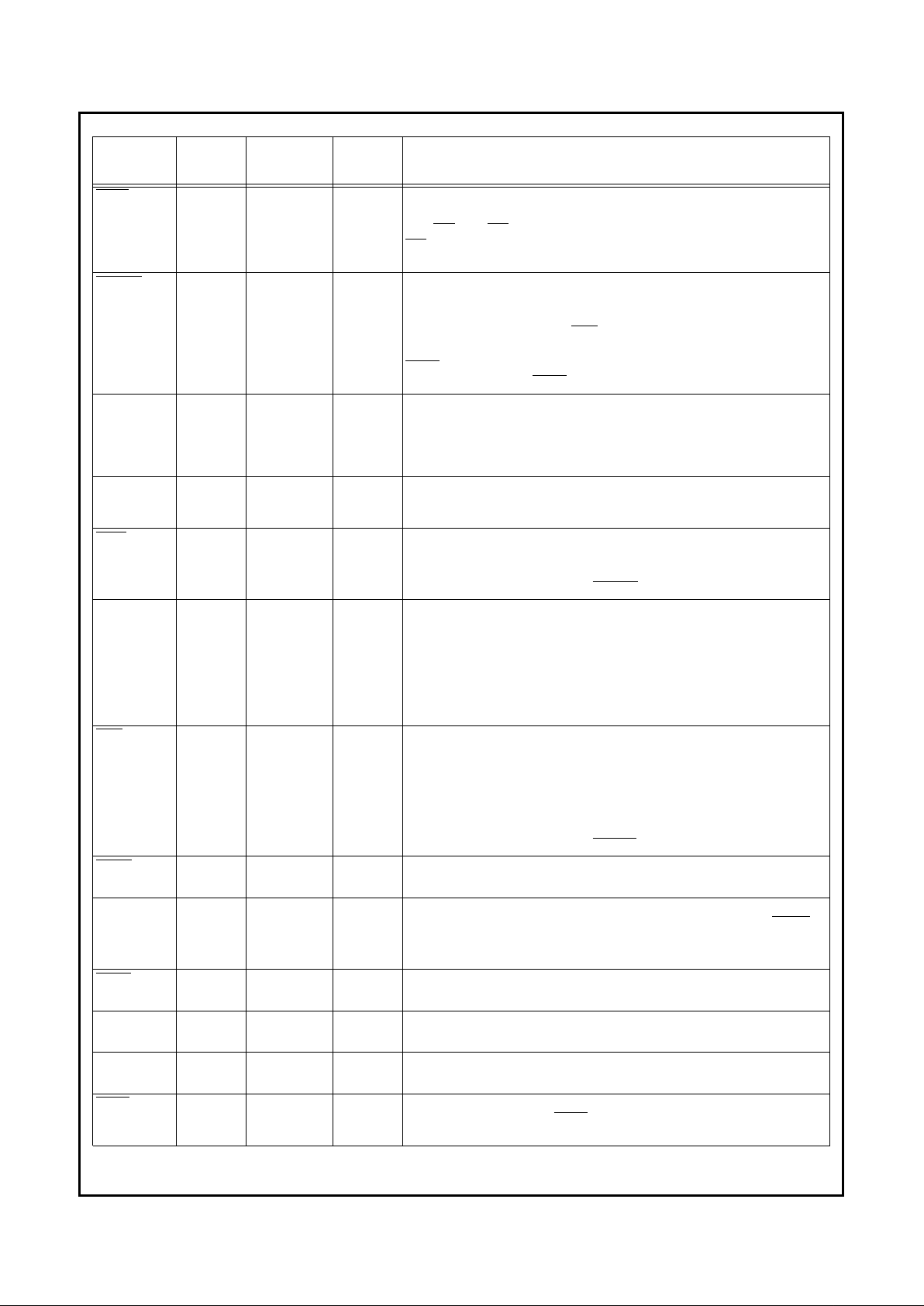

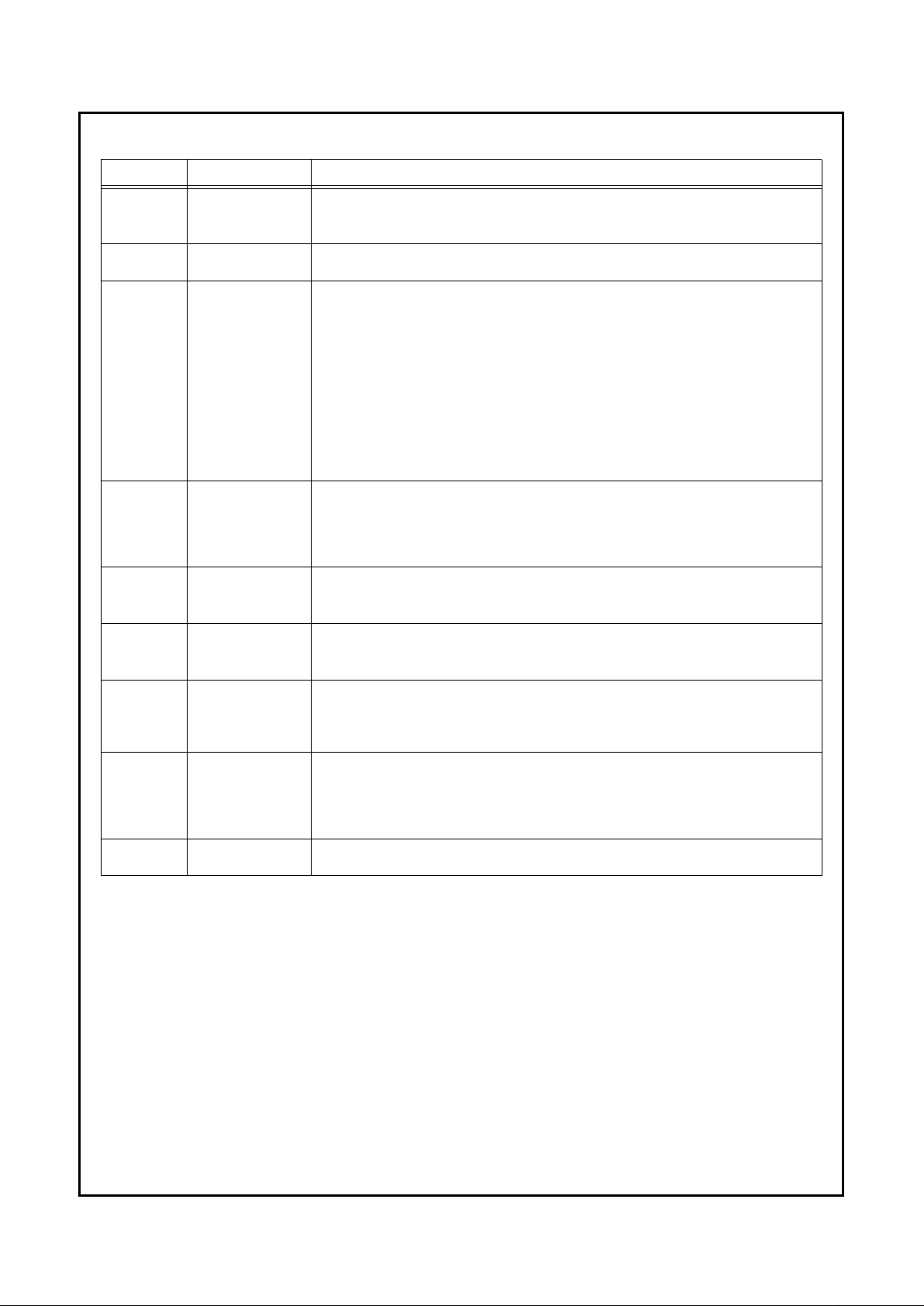

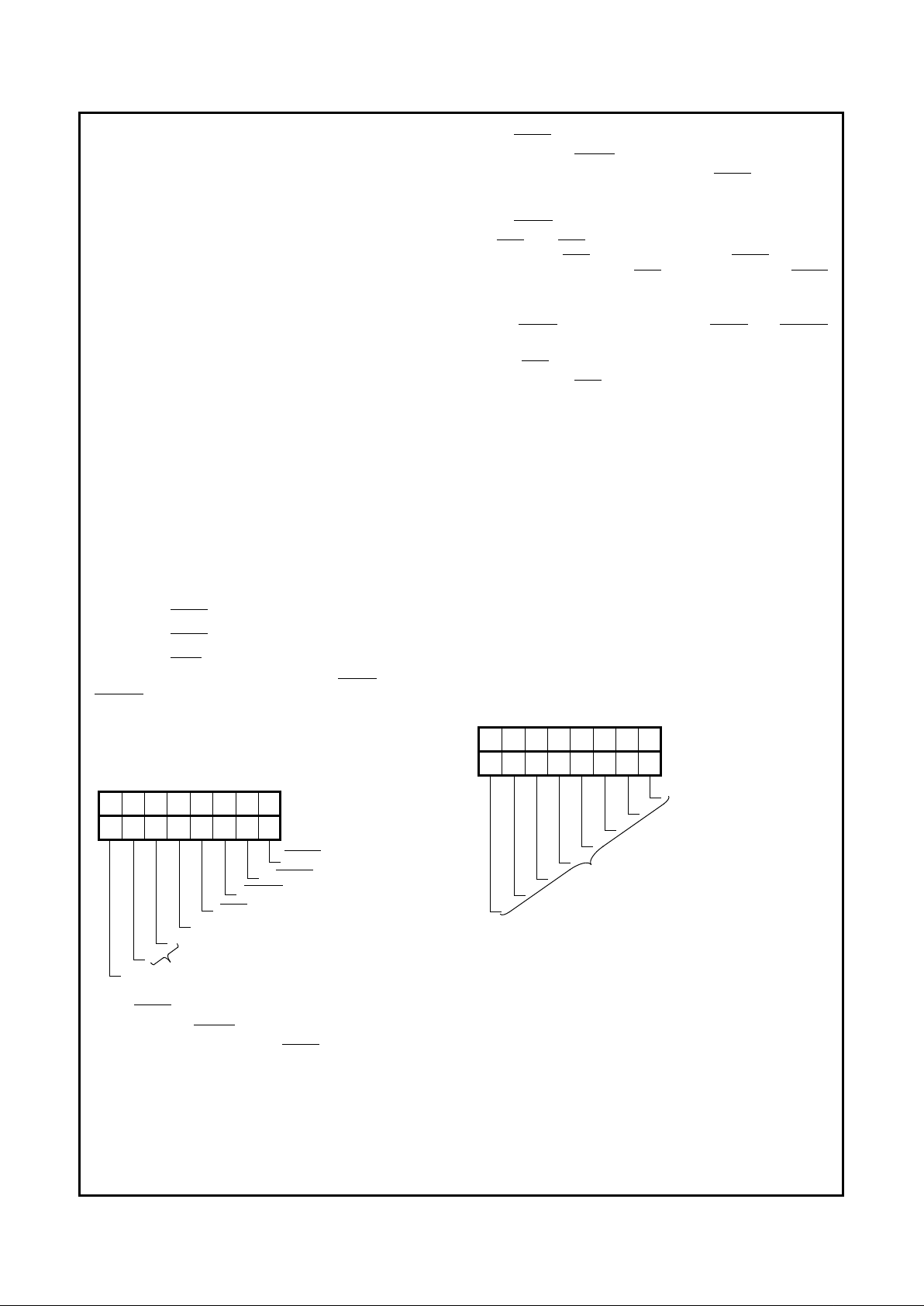

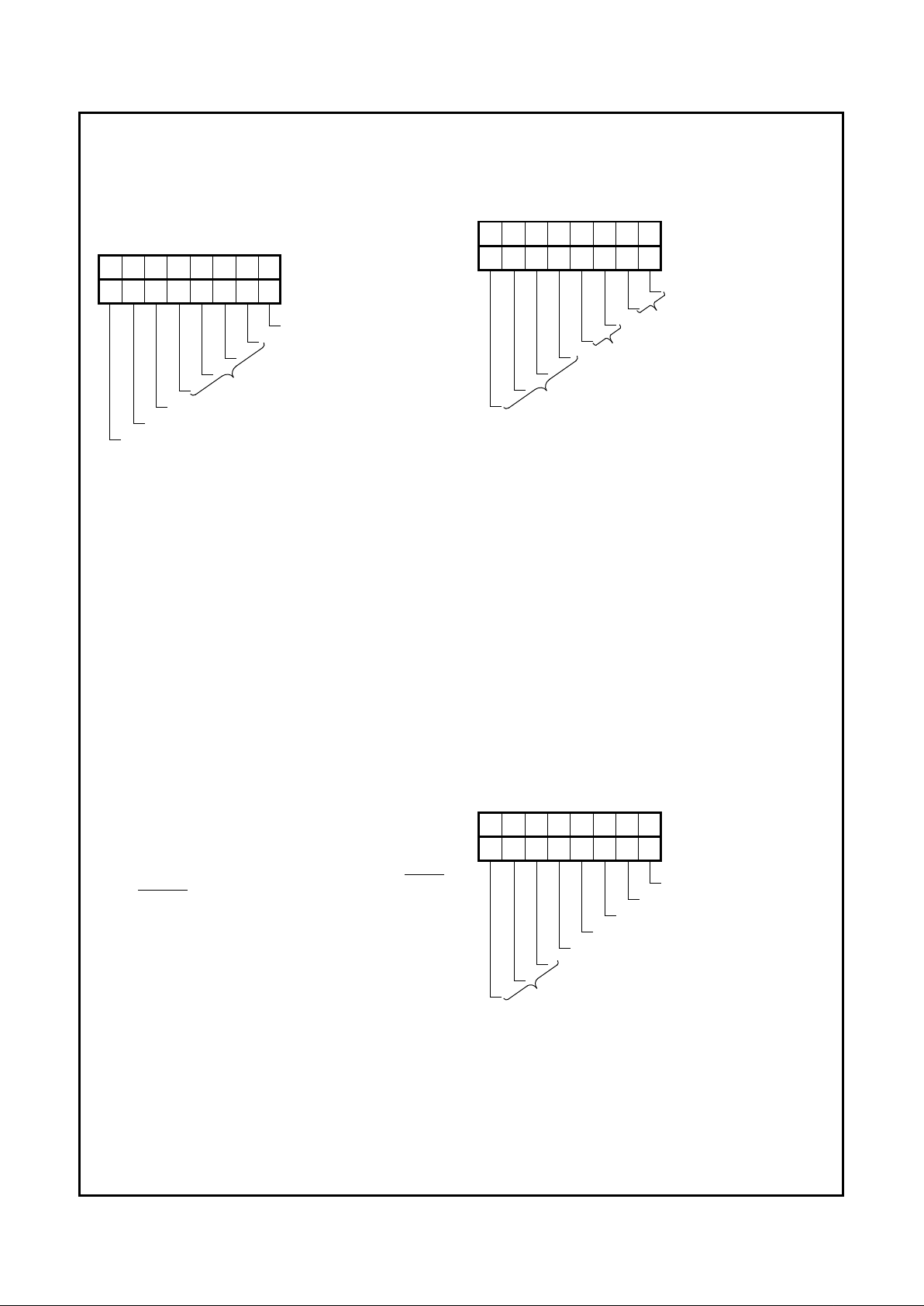

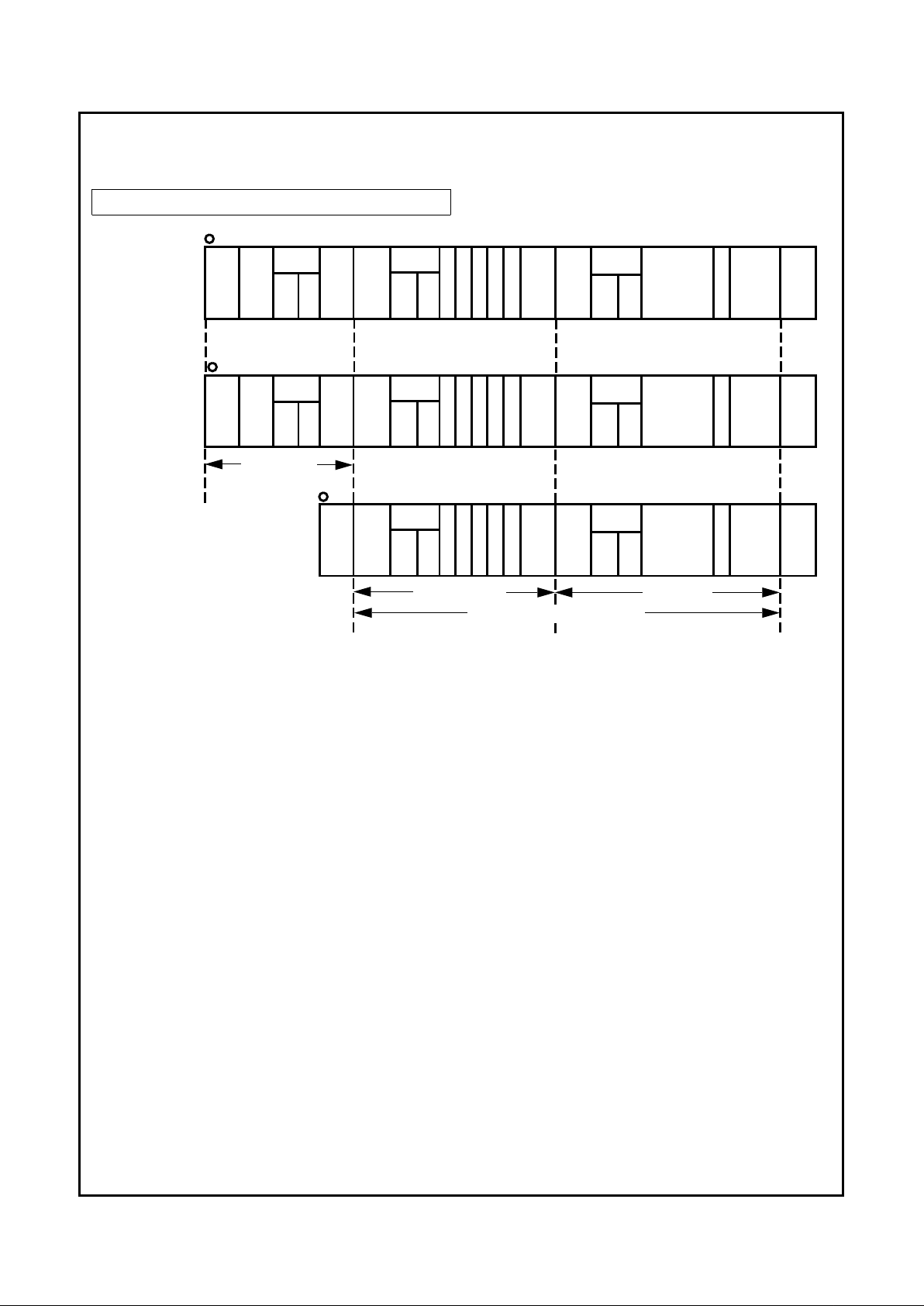

PC87309 Block Diagram

High Current Driver

Controller (KBC)

Power Management

(PM) Logic

µP Address

IEEE 1284

Control

Parallel Port

Ports

(Logical Device 4)

(Logical Devices 5 & 6)

Data and

Control

(Logical Device 0)

(Logical Device 1)

Control

Data and

(PnP)

IRQ

DMA

Channels

Plug and Play

Floppy Disk

Controller (FDC)

Floppy Drive

Interface

Mouse and Keyboard

Data Handshake

Serial

with IR (UART2)

Infrared

(Logical Devices 2)

Serial

(UART1)

Interface

(Logical Devices 3)

Serial Port

Serial Port

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

IBM

®

, MicroChannel®, PC-AT® and PS/2® are registered trademarks of International Business Machines Corporation.

Microsoft

®

and Windows® are registered trademarks of Microsoft Corporation.

Page 2

2

Highlights

www.national.com

Features

●

100% compatibility with PnP requirements specified in

the “

Plug and Play ISA Specification

”, PC97, ISA, EISA,

and MicroChannel architectures

●

A special PnP module that includes:

— Flexible IRQs, DMAs and base addresses that meet

the PnP requirements specified by Microsoft

®

in

their 1995 hardware design guide for Windows

®

and

PnP ISA Revision 1.0A

— PnP ISA mode (with isolation mechanism – Wait for

Key state Motherboard PnP mode

●

A Floppy Disk Controller (FDC) that provides:

— A relocatable address that is referenced by an 11-bit

programmable register

— Software compatibility with the PC8477, which con-

tains a superset of the floppy disk controller functions in the µDP8473, the NEC µPD765A and the

N82077

— 7 IRQ channel options

— Three 8-bit DMA channel options

— 16-byte FIFO

— Burst and non-burst modes

— A new high-performance, on-chip, digital data sepa-

rator that does not require any external filter components

— Support for standard 5.25" and 3.5" floppy disk

drives

— Perpendicular recording drive support

— Three-mode Floppy Disk Drive (FDD) support

— Full suppor t for the IBM Tape Drive Register (TDR)

implementation of AT and PS/2 drive types

●

A Keyboard and mouse Controller (KBC) with:

— A relocatable address that is referenced by an 11-bit

programmable register, reported as a fixed address

in resource data

— 7 IRQ options for the keyboard controller

— 7 IRQ options for the mouse controller

— An 8-bit microcontroller

— Software compatibility with the 8042AH and

PC87911 microcontrollers

— 2 KB of custom-designed program ROM

— 256 bytes of RAM for data

— Three programmable dedicated open drain I/O lines

for keyboard controller applications

— Asynchronous access to two data registers and one

status register during normal operation

— Support for both interrupt and polling

— 93 instructions

— An 8-bit timer/counter

— Support for binary and BCD arithmetic

— Operation at 8 MHz,12 MHz or 16 MHz (programma-

ble option)

— Customizing by using the PC87323VUL, which in-

cludes a RAM-based KBC, as a development platform for keyboard controller code for the PC87309

●

Two UARTs that provide:

— Software compatibility with the 16550A and the 16450

— A relocatable address that is referenced by an 11-bit

programmable register

— 7 IRQ channel options

— Shadow register support for write-only bit monitoring

— UART data rates up to 1.5 Mbaud

●

An enhanced UART and Infrared (IR) interface on the

UART2 that supports:

— HP-SIR

— ASK-IR option of SHARP-IR

— DASK-IR option of SHARP-IR

— Consumer Remote Control circuitry

— A PnP compatible external transceiver

— Three 8-bit DMA options for the UART with Slow In-

frared support (UART2)

●

A bidirectional parallel port that includes:

— A relocatable address that is referenced by an 11-bit

programmable register

— Software or hardware control

— 7 IRQ channel options

— Three 8-bit DMA channel options

— Demand mode DMA support

— An Enhanced Parallel Port (EPP) that is compatible

with the new version EPP 1.9, and is IEEE 1284

compliant

— An Enhanced Parallel Port (EPP) that also supports

version EPP 1.7 of the Xircom specification.

— Support for an Enhanced Parallel Port (EPP) as

mode 4 of the Extended Capabilities Port (ECP)

— An Extended Capabilities Port (ECP) that is IEEE

1284 compliant, including level 2

— Selection of internal pull-up or pull-down resistor for

Paper End (PE) pin

— Reduction of PCI bus utilization by supporting a de-

mand DMA mode mechanism and a DMA fairness

mechanism

— A protection circuit that prevents damage to the par-

allel port when a printer connected to it powers up or

is operated at high voltages

— Output buffers that can sink and source 14 mA

●

Enhanced Power Management (PM), including:

— Reduced current leakage from pins

— Low-power CMOS technology

— Ability to shut off clocks to all modules

●

Clock source:

— Source is a 48 MHz clock input signal.

●

General features include:

— Access to all configuration registers is through an In-

dex and a Data register, which can be relocated

within the ISA I/O address space

— 100-pin Plastic Quad Flatpack (PQFP) package

Page 3

3

Highlights

www.national.com

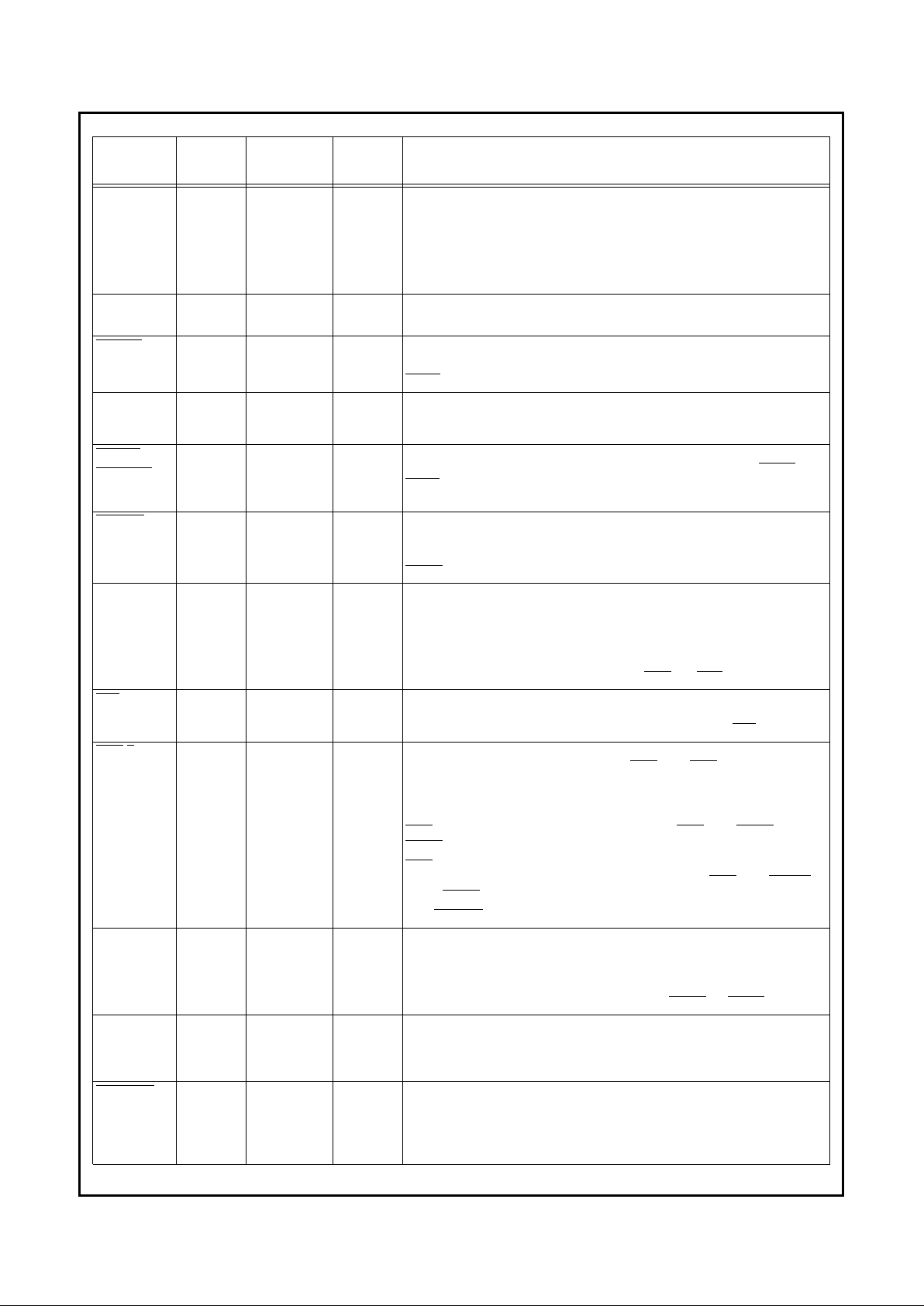

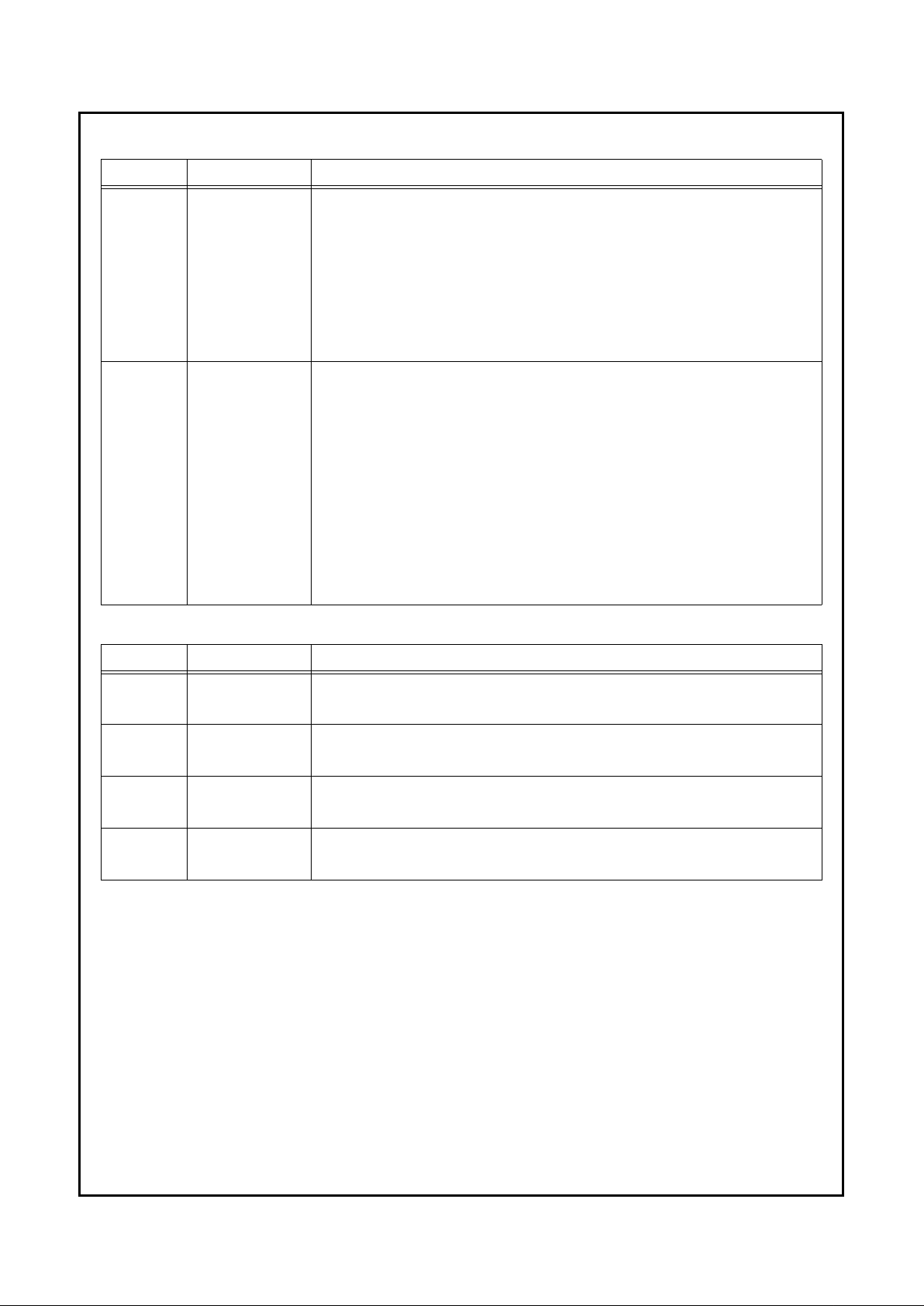

DRATE0

Parallel

Port

Connector

Configuration

Select Logic

48 MHz

EIA

Drivers

EIA

Drivers

ISA Bus

Basic Configuration

CLKIN

MR

AEN

A11-0

D7-0

RD

WR

TC

PD7-0

SLIN/ASTRB

STB/WRITE

AFD/DSTRB

INIT

ACK

ERR

SLCT

PE

BUSY/

WAIT

BADDR1,0

CFG0

SIN1

SOUT1

RTS1

DTR1/BOUT1

CTS1

DSR1

DCD1

RI1

SIN2

SOUT2

RTS2

DTR2/BOUT2

CTS2

DSR2

DCD2

RI2

RDATA

WDATA

WGATE

HDSEL

DIR

STEP

TRK0

INDEX

DSKCHG

WP

MTR1,0

DR1,0

DENSEL

IOCHRDY

DRQ3-1

DACK3-1

P12

P21,20

KBCLK

KBDAT

MDAT

MCLK

Keyboard I/O

Interface

IRQ1

Infrared (IR)

Interface

IRRX2,1

IRTX

PC87309

IRQ7-3

IRQ12

IRSL2-0

ID3-0

Clock

Floppy

Disk

(FDC)

Controller

Connector

Page 4

4

Table of Contents

www.national.com

Table of Contents

Highlights.......................................................................................................................................................1

1.0 Signal/Pin Connection and Description

1.1 CONNECTION DIAGRAM .........................................................................................................12

1.2 SIGNAL/PIN DESCRIPTIONS ...................................................................................................13

2.0 Configuration

2.1 HARDWARE CONFIGURATION ...............................................................................................19

2.1.1 Wake Up Options ........................................................................................................19

2.1.2 The Index and Data Register Pair ...............................................................................19

2.2 SOFTWARE CONFIGURATION ...............................................................................................20

2.2.1 Accessing the Configuration Registers ........................................................................20

2.2.2 Address Decoding .......................................................................................................20

2.3 THE CONFIGURATION REGISTERS .......................................................................................21

2.3.1 Standard Plug and Play (PnP) Register Definitions ....................................................21

2.3.2 Configuration Register Summary ................................................................................25

2.4 CARD CONTROL REGISTERS ................................................................................................28

2.4.1 SID Register ................................................................................................................28

2.4.2 SuperI/O Configuration 1 Register (SIOCF1) ..............................................................28

2.4.3 SuperI/O Configuration 2 Register (SIOCF2) ..............................................................29

2.4.4 SRID Register ..............................................................................................................29

2.5 FDC CONFIGURATION REGISTERS (LOGICAL DEVICE 0) ..................................................30

2.5.1 SuperI/O FDC Configuration Register .........................................................................30

2.5.2 Drive ID Register .........................................................................................................30

2.6 SUPERI/O PARALLEL PORT CONFIGURATION REGISTER (LOGICAL DEVICE 1) .............30

2.7 SUPERI/O UART2 AND INFRARED CONFIGURATION REGISTER (LOGICAL DEVICE 2) ..31

2.8 SUPERI/O UART1 CONFIGURATION REGISTER (LOGICAL DEVICE 3) ..............................32

2.9 SUPERI/O KBC CONFIGURATION REGISTER (LOGICAL DEVICE 6) ..................................32

2.10 CONFIGURATION REGISTER BITMAPS ................................................................................32

3.0 The Floppy Disk Controller (FDC) (Logical Device 0)

3.1 FDC FUNCTIONS .....................................................................................................................34

3.1.1 Microprocessor Interface .............................................................................................34

3.1.2 System Operation Modes ............................................................................................34

3.2 DATA TRANSFER .....................................................................................................................35

3.2.1 Data Rates ...................................................................................................................35

3.2.2 The Data Separator .....................................................................................................35

3.2.3 Perpendicular Recording Mode Support .....................................................................36

3.2.4 Data Rate Selection .....................................................................................................36

3.2.5 Write Precompensation ...............................................................................................37

3.2.6 FDC Low-Power Mode Logic .......................................................................................37

3.2.7 Reset ...........................................................................................................................37

3.3 THE REGISTERS OF THE FDC ...............................................................................................37

Page 5

5

Table of Contents

www.national.com

3.3.1 Status Register A (SRA) ..............................................................................................38

3.3.2 Status Register B (SRB) ..............................................................................................39

3.3.3 Digital Output Register (DOR) .....................................................................................39

3.3.4 Tape Drive Register (TDR) ..........................................................................................41

3.3.5 Main Status Register (MSR) ........................................................................................42

3.3.6 Data Rate Select Register (DSR) ................................................................................43

3.3.7 Data Register (FIFO) ...................................................................................................43

3.3.8 Digital Input Register (DIR) ..........................................................................................44

3.3.9 Configuration Control Register (CCR) .........................................................................45

3.4 THE PHASES OF FDC COMMANDS .......................................................................................45

3.4.1 Command Phase .........................................................................................................45

3.4.2 Execution Phase ..........................................................................................................45

3.4.3 Result Phase ...............................................................................................................47

3.4.4 Idle Phase ....................................................................................................................47

3.4.5 Drive Polling Phase .....................................................................................................48

3.5 THE RESULT PHASE STATUS REGISTERS ..........................................................................48

3.5.1 Result Phase Status Register 0 (ST0) .........................................................................48

3.5.2 Result Phase Status Register 1 (ST1) .........................................................................49

3.5.3 Result Phase Status Register 2 (ST2) .........................................................................49

3.5.4 Result Phase Status Register 3 (ST3) .........................................................................50

3.6 FDC REGISTER BITMAPS .......................................................................................................51

3.6.1 Standard ......................................................................................................................51

3.6.2 Result Phase Status ....................................................................................................52

3.7 COMMAND SET .......................................................................................................................53

3.7.1 Abbreviations Used in FDC Commands ......................................................................54

3.7.2 The CONFIGURE Command ......................................................................................55

3.7.3 The DUMPREG Command .........................................................................................55

3.7.4 The FORMAT TRACK Command ...............................................................................56

3.7.5 The INVALID Command ..............................................................................................58

3.7.6 The LOCK Command ..................................................................................................60

3.7.7 The MODE Command .................................................................................................60

3.7.8 The NSC Command ....................................................................................................62

3.7.9 The PERPENDICULAR MODE Command .................................................................62

3.7.10 The READ DATA Command .......................................................................................64

3.7.11 The READ DELETED DATA Command ......................................................................66

3.7.12 The READ ID Command .............................................................................................67

3.7.13 The READ A TRACK Command .................................................................................68

3.7.14 The RECALIBRATE Command ...................................................................................68

3.7.15 The RELATIVE SEEK Command ................................................................................69

3.7.16 The SCAN EQUAL, the SCAN LOW OR EQUAL and the SCAN HIGH OR EQUAL

Commands ..................................................................................................................69

3.7.17 The SEEK Command ..................................................................................................70

3.7.18 The SENSE DRIVE STATUS Command ....................................................................71

3.7.19 The SENSE INTERRUPT Command ..........................................................................71

3.7.20 The SET TRACK Command ........................................................................................72

3.7.21 The SPECIFY Command ............................................................................................73

3.7.22 The VERIFY Command ...............................................................................................74

Page 6

6

Table of Contents

www.national.com

3.7.23 The VERSION Command ............................................................................................76

3.7.24 The WRITE DATA Command ......................................................................................76

3.7.25 The WRITE DELETED DATA Command ....................................................................77

3.8 EXAMPLE OF A FOUR-DRIVE CIRCUIT USING THE PC87309 .............................................78

4.0 Parallel Port (Logical Device 1)

4.1 PARALLEL PORT CONFIGURATION ......................................................................................79

4.1.1 Parallel Port Operation Modes ....................................................................................79

4.1.2 Configuring Operation Modes ......................................................................................79

4.1.3 Output Pin Protection ..................................................................................................79

4.2 STANDARD PARALLEL PORT (SPP) MODES ........................................................................79

4.2.1 SPP Modes Register Set .............................................................................................80

4.2.2 SPP Data Register (DTR) ............................................................................................80

4.2.3 Status Register (STR) .................................................................................................81

4.2.4 SPP Control Register (CTR) ........................................................................................81

4.3 ENHANCED PARALLEL PORT (EPP) MODES ........................................................................82

4.3.1 EPP Register Set .........................................................................................................82

4.3.2 SPP or EPP Data Register (DTR) ...............................................................................83

4.3.3 SPP or EPP Status Register (STR) .............................................................................83

4.3.4 SPP or EPP Control Register (CTR) ...........................................................................83

4.3.5 EPP Address Register (ADDR) ...................................................................................83

4.3.6 EPP Data Register 0 (DATA0) ....................................................................................84

4.3.7 EPP Data Register 1 (DATA1) ....................................................................................84

4.3.8 EPP Data Register 2 (DATA2) ....................................................................................84

4.3.9 EPP Data Register 3 (DATA3) ....................................................................................84

4.3.10 EPP Mode Transfer Operations ..................................................................................85

4.3.11 EPP 1.7 and 1.9 Data Write and Read Operations .....................................................85

4.4 EXTENDED CAPABILITIES PARALLEL PORT (ECP) .............................................................86

4.4.1 ECP Modes .................................................................................................................86

4.4.2 Software Operation ......................................................................................................86

4.4.3 Hardware Operation ....................................................................................................87

4.5 ECP MODE REGISTERS ..........................................................................................................87

4.5.1 Accessing the ECP Registers ......................................................................................87

4.5.2 Second Level Offsets ..................................................................................................88

4.5.3 ECP Data Register (DATAR) .......................................................................................88

4.5.4 ECP Address FIFO (AFIFO) Register .........................................................................88

4.5.5 ECP Status Register (DSR) .........................................................................................88

4.5.6 ECP Control Register (DCR) .......................................................................................89

4.5.7 Parallel Port Data FIFO (CFIFO) Register ...................................................................90

4.5.8 ECP Data FIFO (DFIFO) Register ...............................................................................90

4.5.9 Test FIFO (TFIFO) Register ........................................................................................90

4.5.10 Configuration Register A (CNFGA) .............................................................................90

4.5.11 Configuration Register B (CNFGB) .............................................................................91

4.5.12 Extended Control Register (ECR) ...............................................................................91

4.5.13 ECP Extended Index Register (EIR) ...........................................................................92

4.5.14 ECP Extended Data Register (EDR) ...........................................................................93

Page 7

7

Table of Contents

www.national.com

4.5.15 ECP Extended Auxiliary Status Register (EAR) ..........................................................93

4.5.16 Control0 Register .........................................................................................................93

4.5.17 Control2 Register .........................................................................................................93

4.5.18 Control4 Register .........................................................................................................94

4.5.19 PP Confg0 Register .....................................................................................................94

4.6 DETAILED ECP MODE DESCRIPTIONS .................................................................................95

4.6.1 Software Controlled Data Transfer (Modes 000 and 001) ...........................................95

4.6.2 Automatic Data Transfer (Modes 010 and 011) ..........................................................95

4.6.3 Automatic Address and Data Transfers (Mode 100) ...................................................97

4.6.4 FIFO Test Access (Mode 110) ....................................................................................97

4.6.5 Configuration Registers Access (Mode 111) ...............................................................97

4.6.6 Interrupt Generation ....................................................................................................97

4.7 PARALLEL PORT REGISTER BITMAPS .................................................................................98

4.7.1 EPP Modes ..................................................................................................................98

4.7.2 ECP Modes .................................................................................................................99

4.8 PARALLEL PORT PIN/SIGNAL LIST ......................................................................................101

5.0 Enhanced Serial Port with IR -UART2 (Logical Device 2)

5.1 FEATURES ..............................................................................................................................102

5.2 FUNCTIONAL MODES OVERVIEW .......................................................................................102

5.2.1 UART Modes: 16450 or 16550, and Extended ..........................................................102

5.2.2 Sharp-IR, IrDA SIR Infrared Modes ...........................................................................102

5.2.3 Consumer IR Mode ...................................................................................................102

5.3 REGISTER BANK OVERVIEW ...............................................................................................102

5.4 UART MODES – DETAILED DESCRIPTION ..........................................................................104

5.4.1 16450 or 16550 UART Mode .....................................................................................104

5.4.2 Extended UART Mode ...............................................................................................104

5.5 SHARP-IR MODE – DETAILED DESCRIPTION .....................................................................105

5.6 SIR MODE – DETAILED DESCRIPTION ................................................................................105

5.7 CONSUMER-IR MODE – DETAILED DESCRIPTION ............................................................105

5.7.1 Consumer-IR Transmission .......................................................................................105

5.7.2 Consumer-IR Reception ............................................................................................106

5.8 FIFO TIME-OUTS ....................................................................................................................106

5.8.1 UART, SIR or Sharp-IR Mode Time-Out Conditions .................................................106

5.8.2 Consumer-IR Mode Time-Out Conditions .................................................................106

5.8.3 Transmission Deferral ...............................................................................................107

5.9 AUTOMATIC FALLBACK TO A NON-EXTENDED UART MODE ..........................................107

5.11 BANK 0 – GLOBAL CONTROL AND STATUS REGISTERS .................................................107

5.11.1 Receiver Data Port (RXD) or the Transmitter Data Port (TXD) .................................108

5.11.2 Interrupt Enable Register (IER) .................................................................................108

5.11.3 Event Identification Register (EIR) ............................................................................110

5.11.4 FIFO Control Register (FCR) .....................................................................................112

5.11.5 Link Control Register (LCR) and Bank Selection Register (BSR) .............................112

5.11.6 Bank Selection Register (BSR) .................................................................................113

5.11.7 Modem/Mode Control Register (MCR) ......................................................................114

Page 8

8

Table of Contents

www.national.com

5.11.8 Link Status Register (LSR) ........................................................................................115

5.11.9 Modem Status Register (MSR) ..................................................................................116

5.11.10 Scratchpad Register (SPR) .......................................................................................117

5.11.11 Auxiliary Status and Control Register (ASCR) ..........................................................117

5.12 BANK 1 – THE LEGACY BAUD GENERATOR DIVISOR PORTS .........................................117

5.12.1 Legacy Baud Generator Divisor Ports (LBGD(L) and LBGD(H)), ..............................118

5.12.2 Link Control Register (LCR) and Bank Select Register (BSR) ..................................118

5.13 BANK 2 – EXTENDED CONTROL AND STATUS REGISTERS ............................................118

5.13.1 Baud Generator Divisor Ports, LSB (BGD(L)) and MSB (BGD(H)) ...........................119

5.13.2 Extended Control Register 1 (EXCR1) ......................................................................120

5.13.3 Link Control Register (LCR) and Bank Select Register (BSR) ..................................121

5.13.4 Extended Control and Status Register 2 (EXCR2) ....................................................121

5.13.5 Reserved Register .....................................................................................................121

5.13.6 TX_FIFO Current Level Register (TXFLV) ................................................................121

5.13.7 RX_FIFO Current Level Register (RXFLV) ...............................................................122

5.14 BANK 3 – MODULE REVISION ID AND SHADOW REGISTERS ..........................................122

5.14.1 Module Revision ID Register (MRID) ........................................................................122

5.14.2 Shadow of Link Control Register (SH_LCR) .............................................................122

5.14.3 Shadow of FIFO Control Register (SH_FCR) ............................................................123

5.14.4 Link Control Register (LCR) and Bank Select Register (BSR) ..................................123

5.15 BANK 4 – IR MODE SETUP REGISTER ................................................................................123

5.15.1 Reserved Registers ...................................................................................................123

5.15.2 Infrared Control Register 1 (IRCR1) ..........................................................................123

5.15.3 Link Control Register (LCR) and Bank Select Register (BSR) ..................................123

5.15.4 Reserved Registers ...................................................................................................123

5.16 BANK 5 – INFRARED CONTROL REGISTERS .....................................................................123

5.16.1 Reserved Registers ...................................................................................................124

5.16.2 (LCR/BSR) Register ..................................................................................................124

5.16.3 Infrared Control Register 2 (IRCR2) ..........................................................................124

5.16.4 Reserved Registers ...................................................................................................124

5.17 BANK 6 – INFRARED PHYSICAL LAYER CONFIGURATION REGISTERS .........................124

5.17.1 Infrared Control Register 3 (IRCR3) ..........................................................................124

5.17.2 Reserved Register .....................................................................................................124

5.17.3 SIR Pulse Width Register (SIR_PW) .........................................................................124

5.17.4 Link Control Register (LCR) and Bank Select Register (BSR) ..................................125

5.17.5 Reserved Registers ...................................................................................................125

5.18 BANK 7 – CONSUMER-IR AND OPTICAL TRANSCEIVER CONFIGURATION REGISTERS 125

5.18.1 Infrared Receiver Demodulator Control Register (IRRXDC) .....................................125

5.18.2 Infrared Transmitter Modulator Control Register (IRTXMC) ......................................126

5.18.3 Consumer-IR Configuration Register (RCCFG) ........................................................128

5.18.4 Link Control/Bank Select Registers (LCR/BSR) ........................................................129

5.18.5 Infrared Interface Configuration Register 1 (IRCFG1) ...............................................129

5.18.6 Reserved Register .....................................................................................................129

5.18.7 Infrared Interface Configuration 3 Register (IRCFG3) ...............................................129

5.18.8 Infrared Interface Configuration Register 4 (IRCFG4) ...............................................130

5.19 UART2 WITH IR REGISTER BITMAPS ..................................................................................131

Page 9

9

Table of Contents

www.national.com

6.0 Enhanced Serial Port - UART1 (Logical Device 3)

6.1 REGISTER BANK OVERVIEW ...............................................................................................136

6.2 DETAILED DESCRIPTION ......................................................................................................136

6.2.1 16450 or 16550 UART Mode .....................................................................................137

6.2.2 Extended UART Mode ...............................................................................................137

6.3 FIFO TIME-OUTS ....................................................................................................................137

6.4 AUTOMATIC FALLBACK TO A NON-EXTENDED UART MODE ..........................................138

6.4.1 Transmission Deferral ...............................................................................................138

6.5 BANK 0 – GLOBAL CONTROL AND STATUS REGISTERS .................................................138

6.5.1 Receiver Data Port (RXD) or the Transmitter Data Port (TXD) .................................138

6.5.2 Interrupt Enable Register (IER) .................................................................................139

6.5.3 Event Identification Register (EIR) ............................................................................140

6.5.4 FIFO Control Register (FCR) .....................................................................................142

6.5.5 Line Control Register (LCR) and Bank Selection Register (BSR) .............................142

6.5.6 Bank Selection Register (BSR) .................................................................................143

6.5.7 Modem/Mode Control Register (MCR) ......................................................................143

6.5.8 Line Status Register (LSR) ........................................................................................144

6.5.9 Modem Status Register (MSR) ..................................................................................145

6.5.10 Scratchpad Register (SPR) .......................................................................................146

6.5.11 Auxiliary Status and Control Register (ASCR) ..........................................................146

6.6 BANK 1 – THE LEGACY BAUD GENERATOR DIVISOR PORTS .........................................146

6.6.1 Legacy Baud Generator Divisor Ports (LBGD(L) and LBGD(H)), ..............................147

6.6.2 Line Control Register (LCR) and Bank Select Register (BSR) ..................................147

6.7 BANK 2 – EXTENDED CONTROL AND STATUS REGISTERS ............................................148

6.7.1 Baud Generator Divisor Ports, LSB (BGD(L)) and MSB (BGD(H)) ...........................148

6.7.2 Extended Control Register 1 (EXCR1) ......................................................................149

6.7.3 Line Control Register (LCR) and Bank Select Register (BSR) ..................................149

6.7.4 Extended Control and Status Register 2 (EXCR2) ....................................................149

6.7.5 Reserved Register .....................................................................................................150

6.7.6 TX_FIFO Current Level Register (TXFLV) ................................................................150

6.7.7 RX_FIFO Current Level Register (RXFLV) ...............................................................150

6.8 BANK 3 – MODULE REVISION ID AND SHADOW REGISTERS ..........................................150

6.8.1 Module Revision ID Register (MRID) ........................................................................151

6.8.2 Shadow of Line Control Register (SH_LCR) .............................................................151

6.8.3 Shadow of FIFO Control Register (SH_FCR) ............................................................151

6.8.4 Line Control Register (LCR) and Bank Select Register (BSR) ..................................151

6.9 UART1 REGISTER BITMAPS .................................................................................................151

7.0 Power Management (Logical Device 4)

7.1 POWER MANAGEMENT OPTIONS .......................................................................................155

7.2 THE POWER MANAGEMENT REGISTERS ..........................................................................155

7.2.1 Power Management Index Register ..........................................................................155

7.2.2 Power Management Data Register ...........................................................................155

7.2.3 Function Enable Register 1 (FER1) ...........................................................................155

7.2.4 Power Management Control Register (PMC1) ..........................................................156

Page 10

10

Table of Contents

www.national.com

7.2.5 Power Management Control 3 Register (PMC3) .......................................................156

7.3 POWER MANAGEMENT REGISTER BITMAPS ....................................................................157

8.0 Mouse and Keyboard Controller (KBC) (Logical Devices 5 and 6)

8.1 SYSTEM ARCHITECTURE .....................................................................................................158

8.2 FUNCTIONAL OVERVIEW .....................................................................................................159

8.3 DEVICE CONFIGURATION ....................................................................................................159

8.3.1 I/O Address Space ....................................................................................................159

8.3.2 Interrupt Request Signals ..........................................................................................159

8.3.3 KBC Clock .................................................................................................................161

8.3.4 Timer or Event Counter .............................................................................................161

8.4 EXTERNAL I/O INTERFACES ................................................................................................161

8.4.1 Keyboard and Mouse Interface .................................................................................161

8.4.2 General Purpose I/O Signals .....................................................................................162

8.5 INTERNAL KBC - PC87309 INTERFACE ...............................................................................163

8.5.1 The KBC DBBOUT Register, Offset 60h, Read Only ................................................163

8.5.2 The KBC DBBIN Register, Offset 60h (F1 Clear) or 64h (F1 Set), Write Only ..........163

8.5.3 The KBC STATUS Register ......................................................................................163

8.6 INSTRUCTION TIMING ...........................................................................................................163

9.0 Interrupt and DMA Mapping

9.1 IRQ MAPPING .........................................................................................................................164

9.2 DMA MAPPING .......................................................................................................................164

10.0 Device Specifications

10.1 GENERAL DC ELECTRICAL CHARACTERISTICS ...............................................................165

10.1.1 Recommended Operating Conditions .......................................................................165

10.1.2 Absolute Maximum Ratings .......................................................................................165

10.1.3 Capacitance ...............................................................................................................165

10.1.4 Power Consumption under Recommended Operating Conditions ............................165

10.2 DC CHARACTERISTICS OF PINS, BY GROUP ....................................................................166

10.2.1 Group 1 ......................................................................................................................166

10.2.2 Group 2 ......................................................................................................................166

10.2.3 Group 3 ......................................................................................................................166

10.2.4 Group 4 ......................................................................................................................167

10.2.5 Group 5 ......................................................................................................................167

10.2.6 Group 6 ......................................................................................................................167

10.2.7 Group 7 ......................................................................................................................168

10.2.8 Group 8 ......................................................................................................................168

10.2.9 Group 9 ......................................................................................................................169

10.2.10 Group 10 ....................................................................................................................169

10.2.11 Group 11 ....................................................................................................................169

10.2.12 Group 12 ....................................................................................................................169

10.2.13 Group 13 ....................................................................................................................170

10.2.14 Group 14 ....................................................................................................................170

Page 11

11

Table of Contents

www.national.com

10.2.15 Group 15 ....................................................................................................................170

10.2.16 Group 18 ....................................................................................................................170

10.3 AC ELECTRICAL CHARACTERISTICS ..................................................................................171

10.3.1 AC Test Conditions ....................................................................................................171

10.3.2 Clock Timing ..............................................................................................................171

10.3.3 Microprocessor Interface Timing ...............................................................................172

10.3.4 Baud Output Timing ...................................................................................................174

10.3.5 Transmitter Timing .....................................................................................................175

10.3.6 Receiver Timing .........................................................................................................176

10.3.7 UART, Sharp-IR, SIR and Consumer Remote Control Timing ..................................178

10.3.8 IRSLn Write Timing ...................................................................................................179

10.3.9 Modem Control Timing ..............................................................................................179

10.3.10 FDC DMA Timing ......................................................................................................180

10.3.11 ECP DMA Timing ......................................................................................................181

10.3.12 UART2 DMA Timing ..................................................................................................182

10.3.13 Reset Timing .............................................................................................................183

10.3.14 FDC - Write Data Timing ...........................................................................................183

10.3.15 FDC - Drive Control Timing .......................................................................................184

10.3.16 FDC - Read Data Timing ...........................................................................................184

10.3.17 Standard Parallel Port Timing ....................................................................................185

10.3.18 Enhanced Parallel Port 1.7 Timing ............................................................................186

10.3.19 Enhanced Parallel Port 1.9 Timing ............................................................................187

10.3.20 Extended Capabilities Port (ECP) Timing ..................................................................188

Glossary .....................................................................................................................................................189

Page 12

Signal/Pin Connection and Description

12

1.0 Signal/Pin Connection and Description

www.national.com

1.0 Signal/Pin Connection and Description

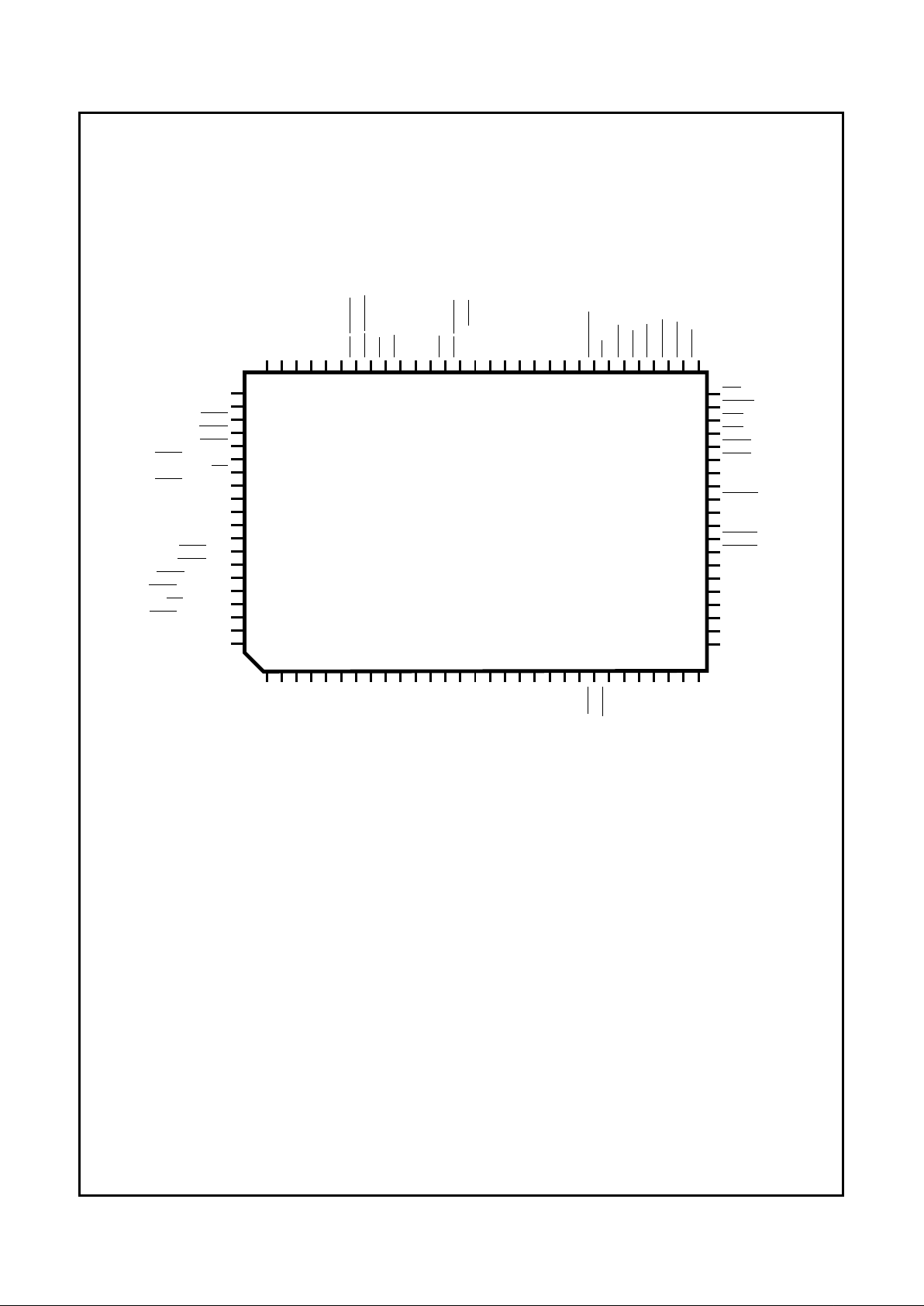

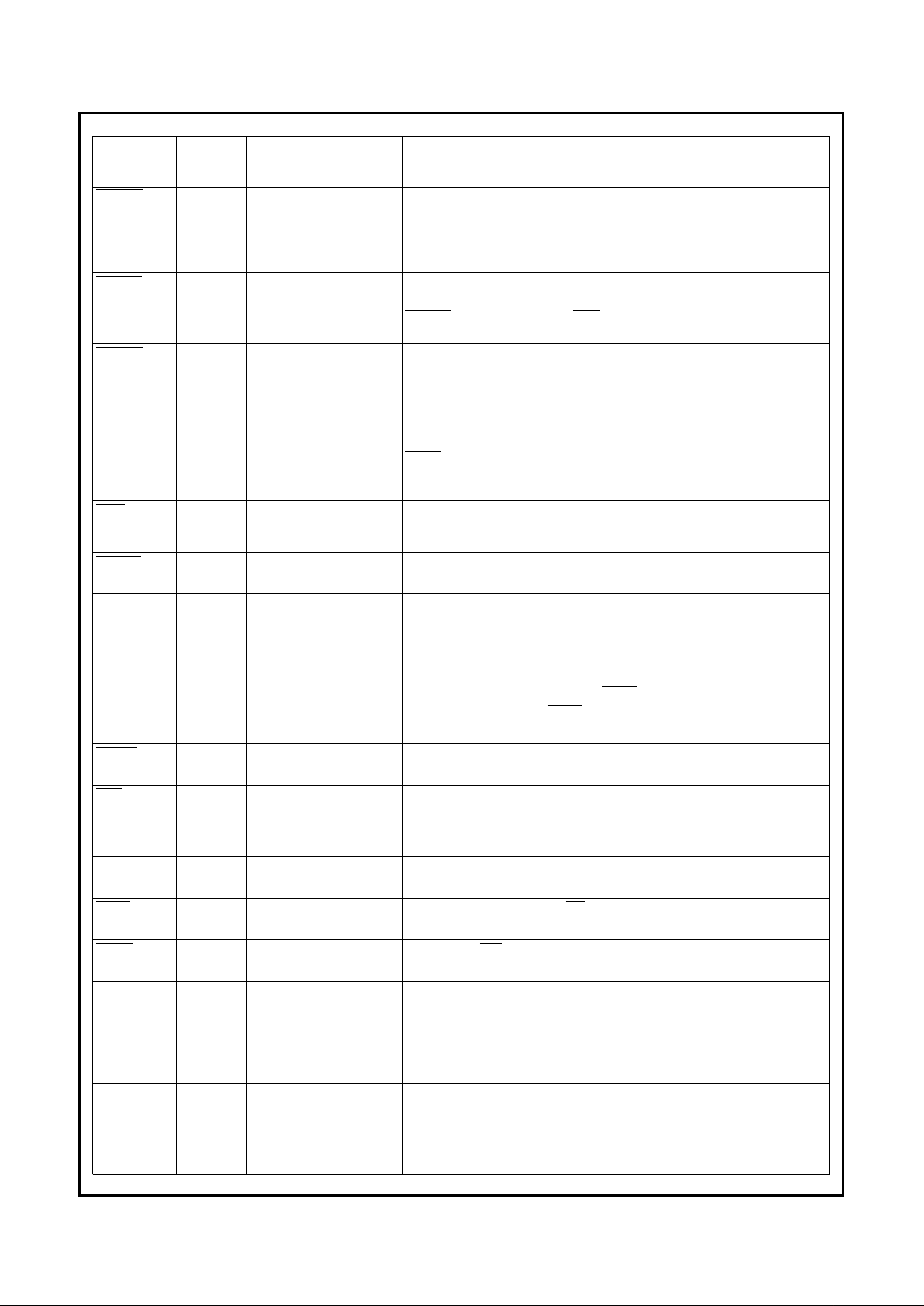

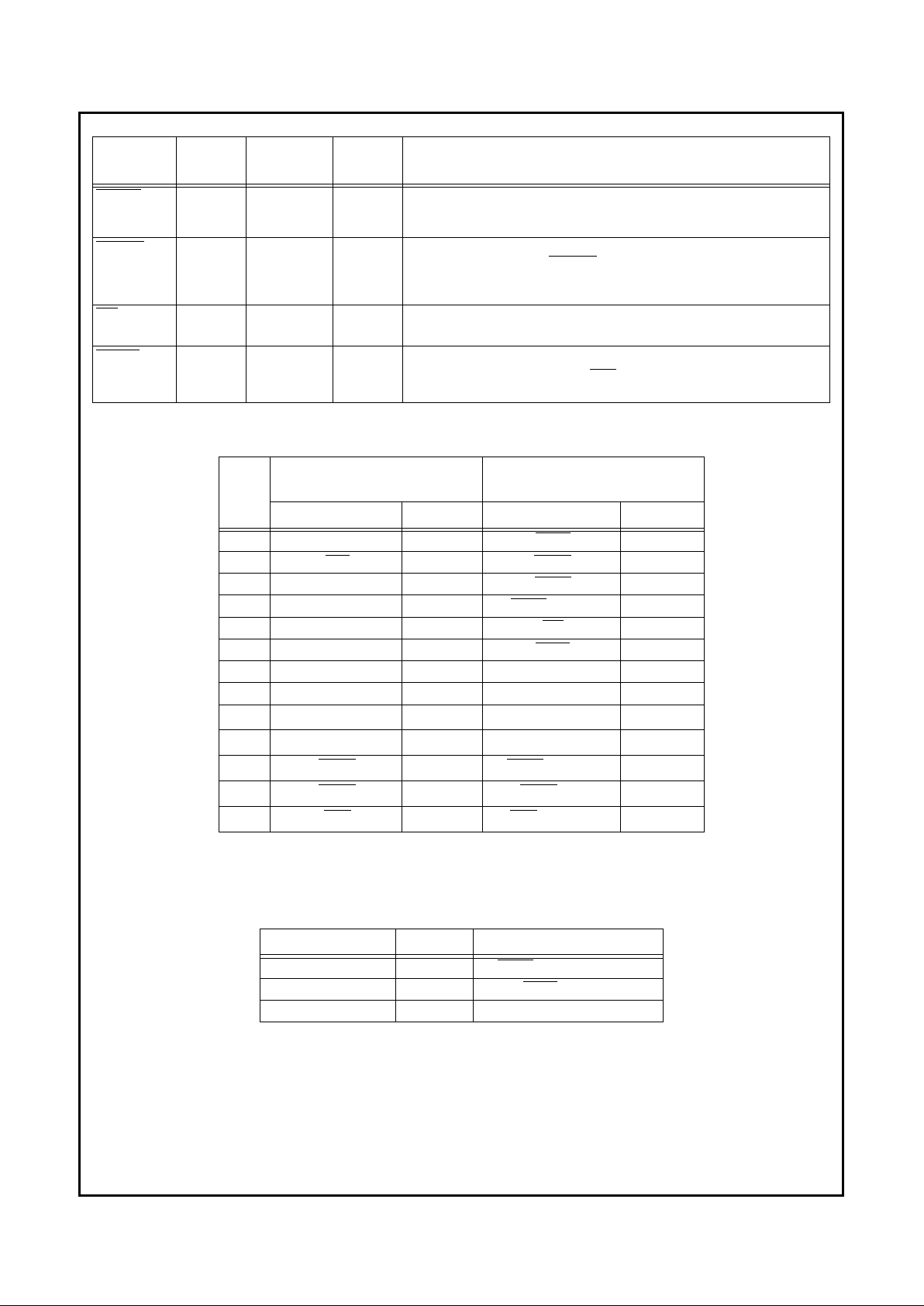

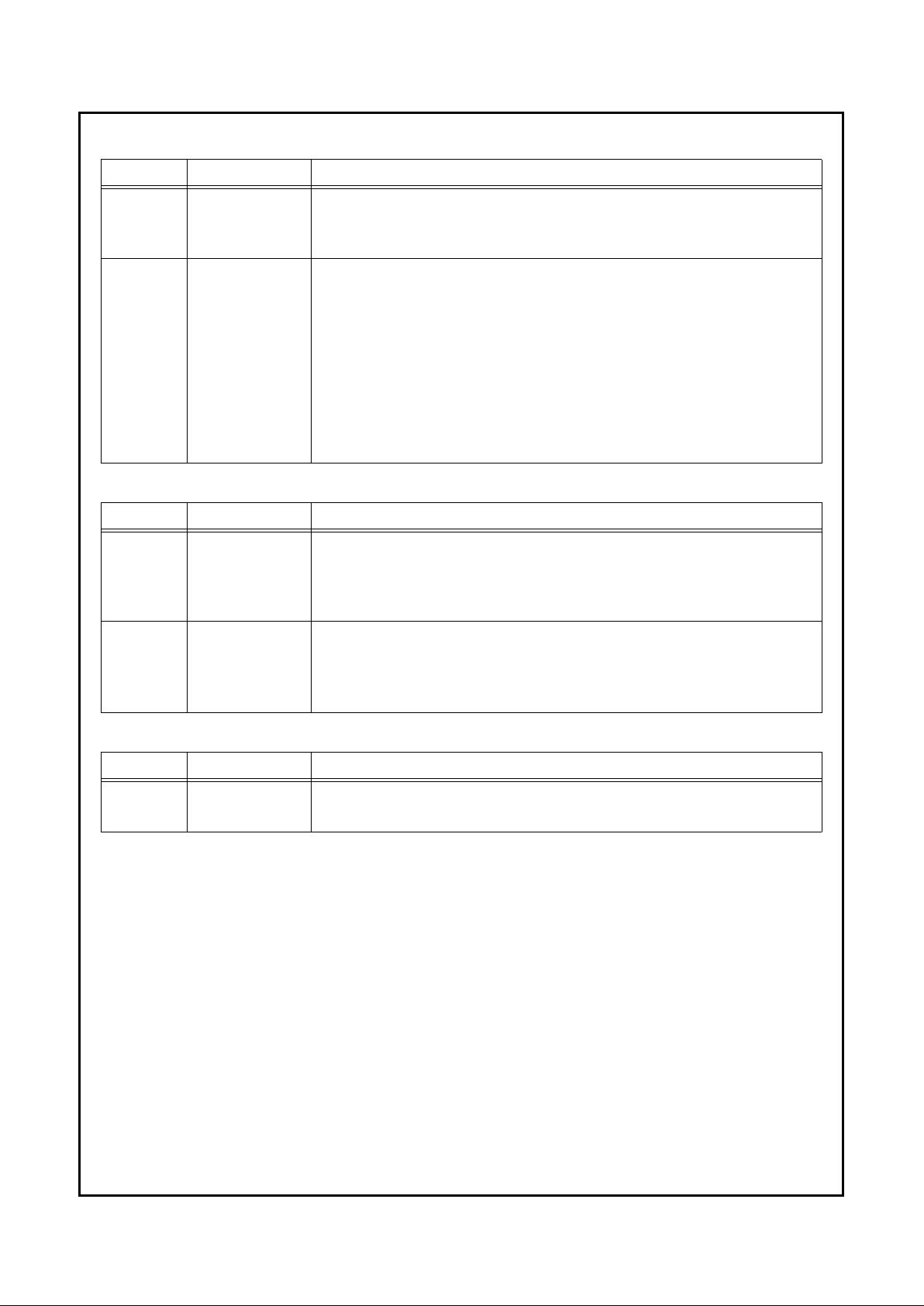

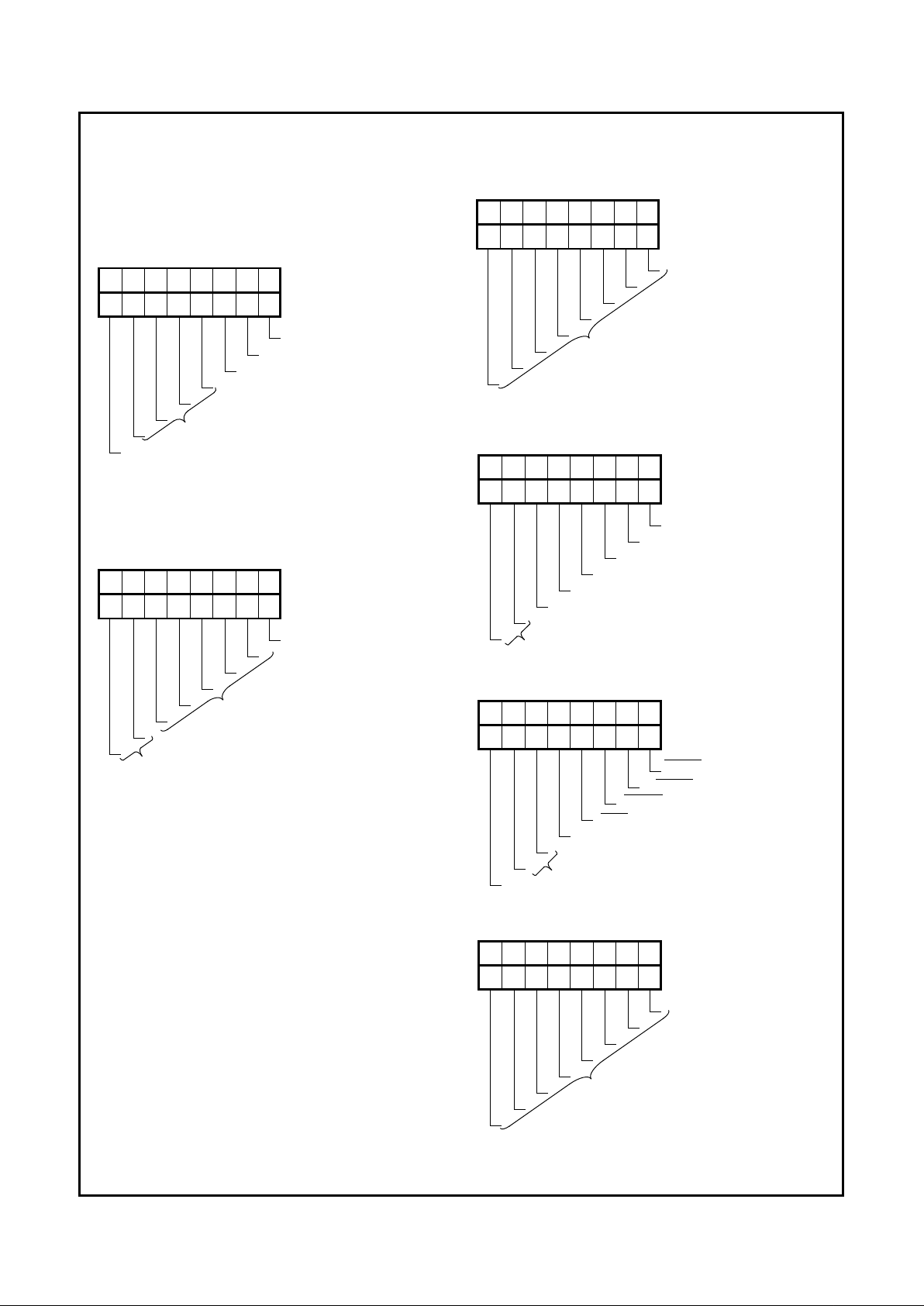

1.1 CONNECTION DIAGRAM

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51

1 2 3 4 5 6 7 8 9 101112131415161718192021222324252627282930

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

DIR

WDATA

DR1/DENSEL

DR0

MTR1/P12

MTR0/DRATE0

IRTX/DENSEL

IRRX1/P12/DRATE0

DACK3

VDD

VSS

DACK2

DACK1

DRQ3

DRQ2

DRQ1

MR

IRQ12

IRQ7

PD6

PD7

CTS1

DCD1

DSR1

BOUT1/

DTR1/BADDR0

RI1

RTS1/BADDR1

SIN1

VDD

VSS

SOUT1/CGF0

CTS2/A11

DCD2/P12

DSR2/DRATE0

BOUT2/

DTR2/IRSL2/ID2

RI2/DENSEL

RTS2/IRSL1/ID1

SIN2/ID3

SOUT2/IRSL0/IRRX2/ID0

PD5

PD4

PD3

PD2

PD0

AFD/DSTRB

SLIN/ASTRB

INIT

ERRPESLCT

ACK

STB/WRITE

BUSY/WAIT

VSS

P21

P20

MDAT

MCLK

KBCLK

INDEX

TRK0

WGATE

HDSEL

STEP

PD1

D0D1D2

D5D6D7

A0A1A2A3A4

A5

VSS

A6A7A8

A9

A10

AEN

IOCHRDY

IORD

IOWR

TC

IRQ1

IRQ3

IRQ4

IRQ5

IRQ6

PC87309VLJ

RDATA

D4

D3

CLKIN

KBDAT

DSKCHG

WP

Page 13

Signal/Pin Connection and Description

SIGNAL/PIN DESCRIPTIONS

13

www.national.com

1.2 SIGNAL/PIN DESCRIPTIONS

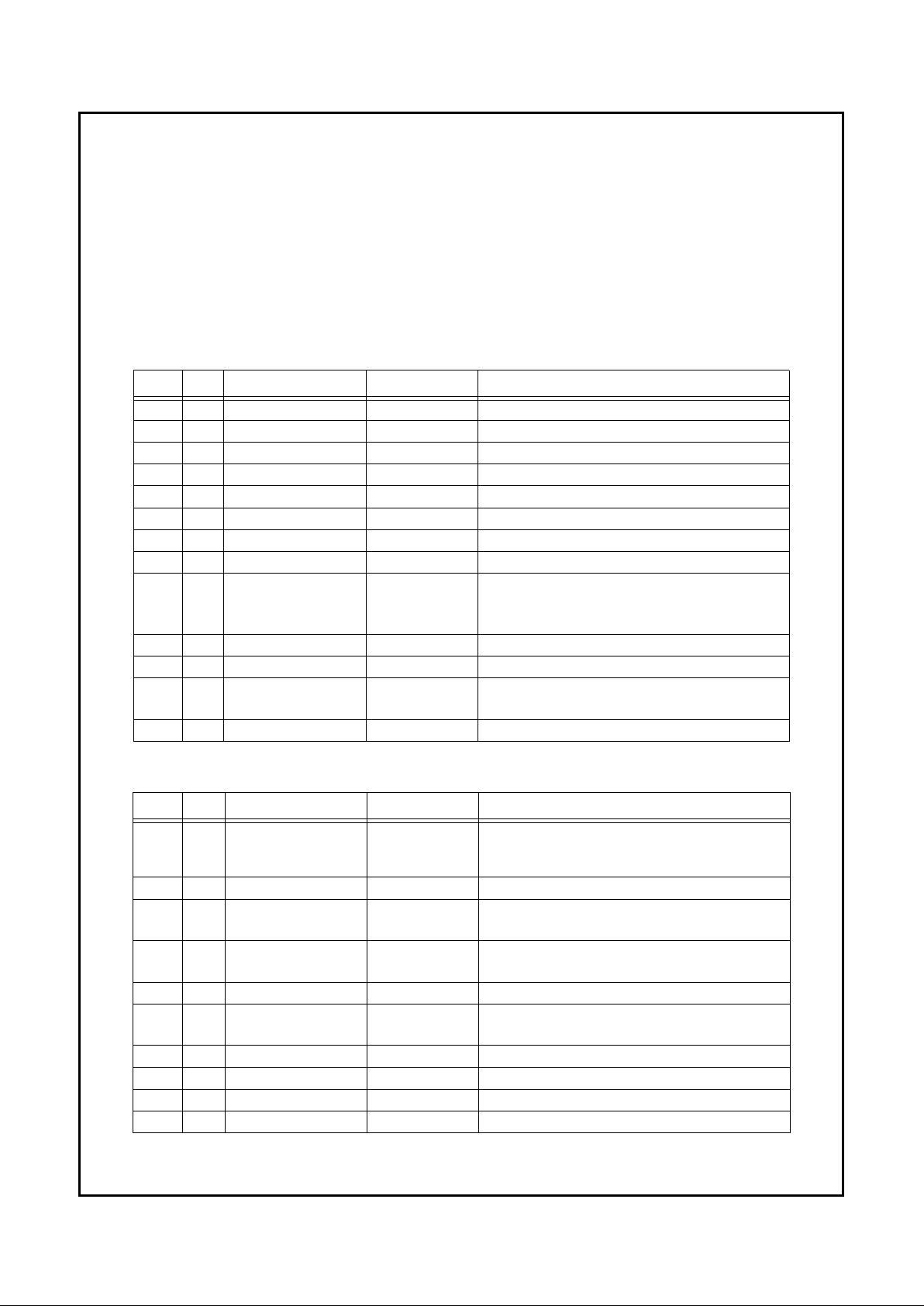

TABLE 1-1 lists the signals of the PC87309 in alphabetical

order and shows the pin(s) associated with each. TABLE

1-2 on page 18 lists the signals that are multiplexed in FullIR and Two-UART modes. TABLE 1-3 on page 18 lists the

pins that have strap functions during reset.

The Module column indicates the functional module that is

associated with these pins. In this column, the System label

indicates internal functions that are common to more than

one module. The I/O and Group # column describes whether the pin is an input, output, or bidirectional pin (marked as

Input, Output or I/O, respectively).

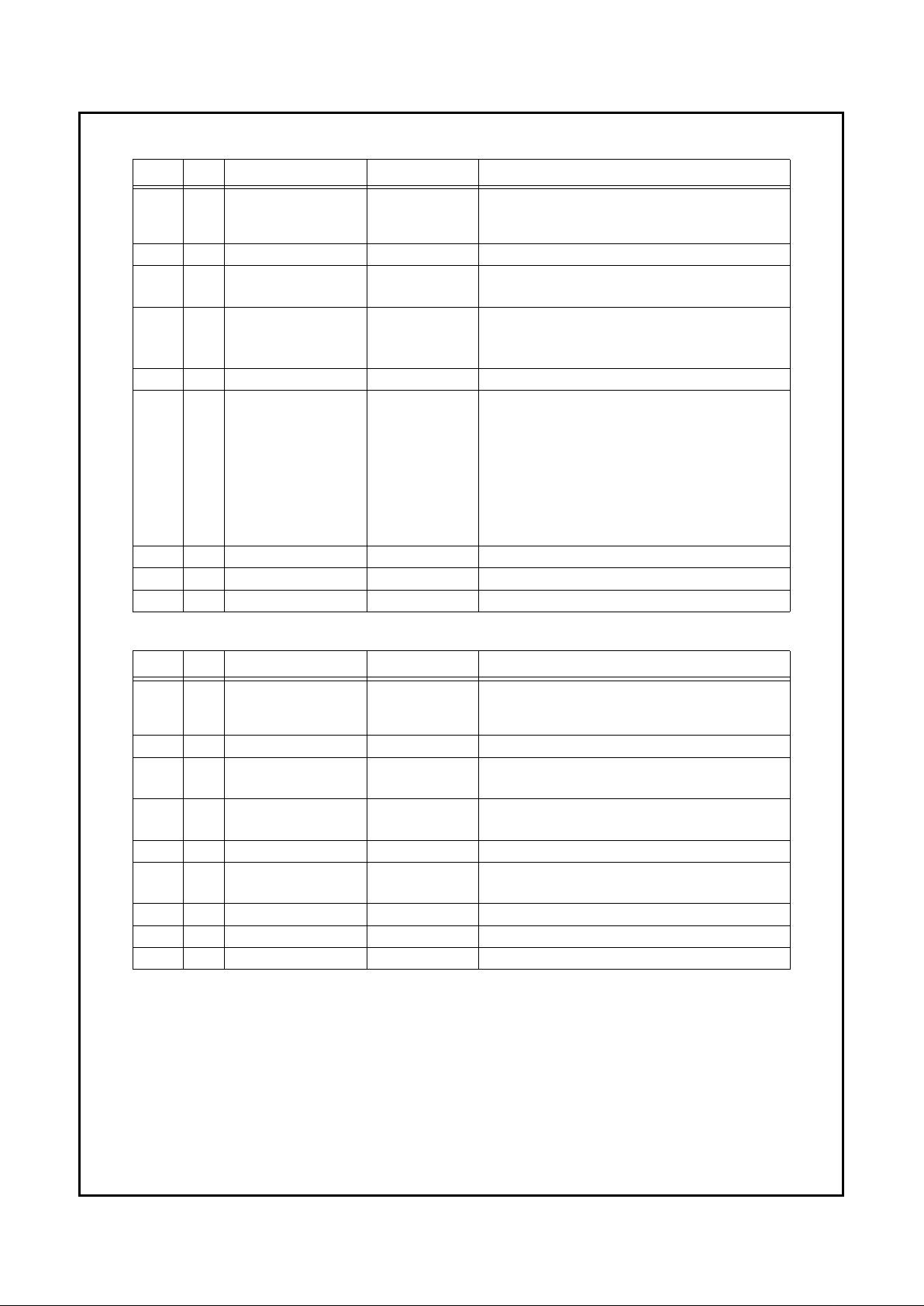

TABLE 1-1. Signal/Pin Description Table

Signal/Pin

Name

Pin

Number

Module

I/O and

Group #

Function

A11-0 93, 20-16,

14-9

ISA-Bus Input

Group 1

ISA-Bus Address – A11-0 are used for address decoding on any

access except DMA accesses, on the condition that the AEN signal is

low.

A11 is multiplexed with

CTS2 on pin 93 and available in Full-IR mode

only. Since A11 is required to suppor t full ISA PnP mode (for

decoding A79h), this mode is not available in Two-UART mode.

See Section 2.2.2.

ACK 68 Parallel Por t Input

Group 3

Acknowledge – This input signal is pulsed low by the printer to

indicate that it has received data from the parallel port. This pin is

internally connected to an internal weak pull-up.

AFD 74 Parallel Port I/O

Group 8

Automatic Feed – When this signal is low the printer should

automatically feed a line after printing each line. This pin is in TRISTATE after a 0 is loaded into the corresponding control register bit.

An external 4.7 KΩ pull-up resistor should be attached to this pin.

This signal is multiplexed with

DSTRB. See TABLE 4-12 on page 101

for more information.

AEN 21 ISA-Bus Input

Group 1

DMA Address Enable – This input signal disables function selection

via A11-0 when it is high. Access during DMA transfer is not affected

by this signal. This pin is used for external decoding of A11-15 in

Two-UART mode or A15-12 in Full-IR mode.

ASTRB 73 Parallel Port Output

Group 8

Address Strobe (EPP) – This signal is used in EPP mode as an

address strobe. It is active low.

This signal is multiplexed with

SLIN. See TABLE 4-12 on page 101 for

more information.

BADDR1,0 88,86 Configuration Input

Group 4

Base Address Strap Pins 0 and 1 – These pins determine the base

addresses of the Index and Data registers, the value of the Plug and

Play ISA Serial Identifier and the configuration state immediately after

reset. These pins are pulled down by internal 30 KΩ resistors.

External 10 KΩ pull-up resistors to V

DD

should be employed.

BADDR1 is multiplexed with

RTS1.

BADDR0 is multiplexed with

DTR1 and BOUT1.

See TABLE 2-1 and Section 2.1.

BOUT2,1 96,86 UART1,

UART 2

Output

Group 12

Baud Output – This multi-function pin provides the associated serial

channel Baud Rate generator output signal if test mode is selected,

i.e., bit 7 of the EXCR1 register is set. See “Bit 7 - Baud Generator

Test (BTEST)” on page 121.

After Master Reset this pin provides the DTR function.

BOUT2 is multiplexed with DTR2, IRSL2 and ID2.

BOUT1 is multiplexed with DRT1 and BADDR0.

BUSY 66 Parallel Port Input

Group 2

Busy – This pin is set high by the printer when it cannot accept

another character. It is internally connected to a weak pull-down

resistor.

This signal is multiplexed with

WAIT. See TABLE 4-12 on page 101 for

more information.

Page 14

Signal/Pin Connection and Description

14

SIGNAL/PIN DESCRIPTIONS

www.national.com

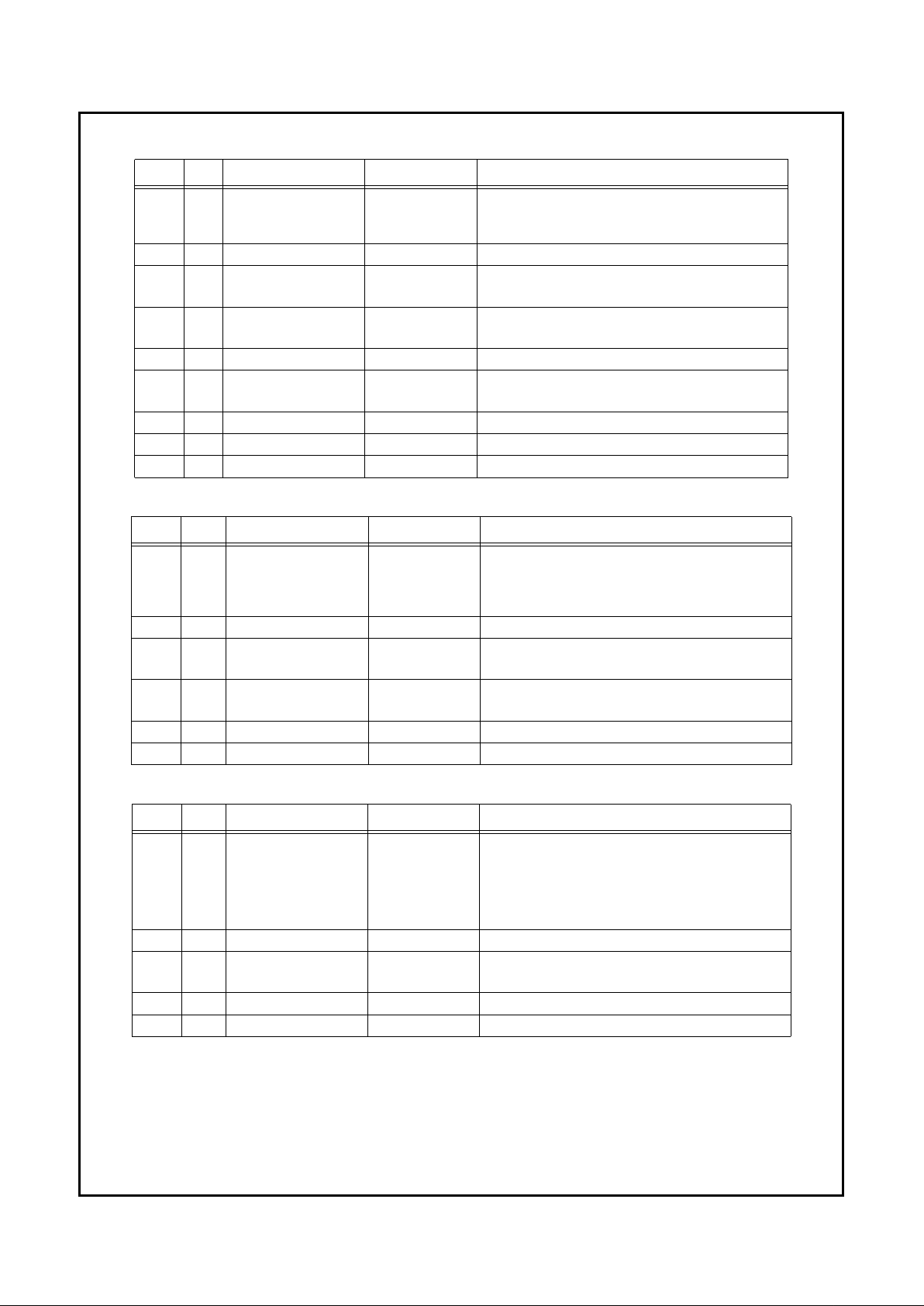

CFG0 92 Configuration Input

Group 4

This pin selects between Full-IR and Two-UART mode as the default

configuration upon power up. It is pulled down by internal 30 KΩ

resistors. External 10 KΩ pull-up resistors to V

DD

should be

employed.

This signal is multiplexed with SOUT1.

See TABLE 2-1 and Section 2.1.

CLKIN 33 Clock Input

Group 1

Clock In – A TTL or CMOS compatible 48 MHz clock.

CTS2,1 93,83 UART1,

UART 2

Input

Group 1

UART1 and UART2 Clear to Send – When low, these signals indicate

that the modem or other data transfer device is ready to exchange data.

CTS2 is multiplexed with A11, and available only in Two-UART mode.

D7-0 8-1 ISA-Bus I/O

Group 5

ISA-Bus Data – Bidirectional data lines to the microprocessor. D0 is

the LSB and D7 is the MSB. These signals have 24 mA (sink)

buffered outputs.

DACK3

DACK2,14239,38

ISA-Bus Input

Group 1

DMA Acknowledge 1,2 and 3 – These active low input signals

acknowledge a request for DMA services and enable the

IOWR and

IORD input signals during a DMA transfer. These DMA signals can be

mapped to the following logical devices: FDC, UART or Parallel Por t.

DCD2,1 94,84 UART1,

UART 2

Input

Group 1

UART1 and UART2 Data Carrier Detected – When low, this signal

indicates that the modem or other data transfer device has detected

the data carrier.

DCD2 is multiplexed with P12 and available only in Two-UART mode.

DENSEL 97, 48 or

44

FDC Output

Group 11

Density Select – Indicates that a high FDC density data rate (500

Kbps or 1 Mbps) or a low density data rate (250 or 300 Kbps) is

selected.

DENSEL polarity is controlled by bit 5 of the SuperI/O FDC

Configuration register as described in Section 2.5.1.

This signal is multiplexed with: IRTX, ,

DR1, or R12.

DIR 50 FDC Output

Group 11

Direction – This output signal determines the direction of the Floppy

Disk Drive (FDD) head movement (active = step in, inactive = step

out) during a seek operation. During reads or writes,

DIR is inactive.

DR1,0 48, 47 FDC Output

Group 11

Drive Select 0 and 1 – These active low output signals are the

decoded drive select output signals.

DR0 and DR1 are controlled by

Digital Output Register (DOR) bits 0 and 1. They are encoded with

information to control four FDDs when bit 7 of the SuperI/O FDC

Configuration register is 1, as described in Section 2.5.1.

DR0 can optionally become a logical OR of DR0 and MTR0 when

MTR0/DRATE0 is used as DRATE0.

DR1 is multiplexed with DENSEL and is available only in Two-UART

mode. Optionally, it can become a logical OR of

DR1 and MTR1

when

MTR1/P12 is used as P12.

See

MTR0,1 for more information.

DRATE0 95, 45 or

43

FDC Output

Group 14

Data Rate 0 – This output signal reflects the value of bit 0 of the

Configuration Control Register (CCR) or the Data Rate Select Register

(DSR), whichever was written to last. Output from the pin is totem-pole

buffered (6 mA sink, 6 mA source).

This signal is multiplexed with IRRX1/P12,

MTR0 or DSR2

DRQ3-1 37-35 ISA-Bus Output

Group 13

DMA Request 1, 2 and 3 – These active high output signals inform

the DMA controller that a data transfer is needed. These DMA signals

can be mapped to the following logical devices: Floppy Disk Controller

(FDC), UART or parallel port.

DSKCHG 58 FDC Input

Group 1

Disk Change – This input signal indicates whether or not the drive

door has been opened. The state of this pin is available from the

Digital Input Register (DIR). This pin can also be configured as the

RGATE data separator diagnostic input signal via the MODE

command. See the MODE command in Section 3.7.7.

Signal/Pin

Name

Pin

Number

Module

I/O and

Group #

Function

Page 15

Signal/Pin Connection and Description

SIGNAL/PIN DESCRIPTIONS

15

www.national.com

DSR2,1 95,85 UART1,

UART2

Input

Group 1

Data Set Ready – When low, this signal indicates that the data

transfer device, e.g., modem, is ready to establish a communications

link.

DSR2 is multiplexed with DRATE0 and available only in Two-UART

mode.

DSTRB 74 Parallel Por t Output

Group 8

Data Strobe – This signal is used in EPP mode as a data strobe. It

is active low.

DSTRB is multiplexed with AFD. See TABLE 4-12 on page 101 fo r

more information.

DTR2,1 96,86 UART1,

UART 2

Output

Group 12

Data Terminal Ready – When low, this output signal indicates to the

modem or other data transfer device that the UART1 or UART2 is

ready to establish a communications link.

A Master Reset (MR) deactivates this signal high, and loopback

operation holds this signal inactive.

DTR1 is multiplexed with BADDR0 and with BOUT1.

DTR2 is multiplexed with IRSL2/ID2/BOUT2 and is available only in

Two-UART mode. (BOUT2 is multiplexed implicitly and controlled by

UART2.)

ERR 71 Parallel Port Input

Group 3

Error – This input signal is set active low by the printer when it has

detected an error. This pin is internally connected to an internal weak

pull-up.

HDSEL 52 FDC Output

Group 11

Head Select – This output signal determines which side of the FDD

is accessed. Active low selects side 1, inactive selects side 0.

ID3

ID2

ID1

ID0

99

96

98

100

UART2 Input

Group 1

Identification – These ID signals identify the infrared transceiver for

Plug and Play support. These pins are read after reset.

ID0,1,2 are multiplexed implicitly with IRSL0,1,2 respectively by the

UART2 cell.

ID3 is multiplexed with SIN2.

ID2 is multiplexed with BOUT2,

DTR2, IRSL2.

ID1 is multiplexed with

RTS2, IRSL1

ID0 is multiplexed with SOUT2,IRSL0, IRRX2

INDEX 56 FDC Input

Group 1

Index – This input signal indicates the beginning of an FDD track.

INIT 72 Parallel Port I/O

Group 8

Initialize – When this signal is active low, it causes the printer to be

initialized. This signal is in TRI-STATE after a 1 is loaded into the

corresponding control register bit.

An external 4.7 KΩ pull-up resistor should be employed.

IOCHRDY 22 ISA-Bus Output

Group 15

I/O Channel Ready – This is the I/O channel ready open drain output

signal. When IOCHRDY is dr iven low, the EPP extends the host cycle.

IORD 23 ISA-Bus Input

Group 1

I/O Read – An active low RD input signal indicates that the

microprocessor has read data.

IOWR 24 ISA-Bus Input

Group 1

I/O Write – WR is an active low input signal that indicates a write

operation from the microprocessor to the controller.

IRQ1

IRQ7-3

IRQ12

26

31-27

32

ISA-Bus I/O

Group 10

Interrupt Requests 1, 3, 4, 5, 6, 7 and 12 – IRQ polarity and pushpull or open-drain output selection is software configurable by the

logical device mapped to the IRQ line.

Keyboard Controller (KBC) or Mouse interrupts can be configured by

the Interrupt Request Type Select 0 register (index 71h) as either

edge or level.

IRRX2,1 100,43 UART2 Input

Group 18

Infrared Reception 1 and 2 – Infrared serial input data.

IRRX1 is multiplexed with P12/DRATE0 and is available only in Two-

UART mode.

IRRX2 is multiplexed with SOUT2/IRSL0/ID0 and is available only in

Full-IR mode.

Signal/Pin

Name

Pin

Number

Module

I/O and

Group #

Function

Page 16

Signal/Pin Connection and Description

16

SIGNAL/PIN DESCRIPTIONS

www.national.com

IRSL0

IRSL1

IRSL2

100

98

96

UART2 Output

Group 12

Infrared Control Signals 0, 1 and 2 – These signals control the

Infrared analog front end. The pins on which these signals are driven

is determined by the SuperI/O Configuration 2 register (index 22h).

SeeTABLE 1-2 for more information.

IRSL0 is multiplexed on pin 100 with SOUT2, IRRX2 and ID0, and is

available only in Full-IR mode.

IRSL1 is multiplexed on pin 98 with

RTS2 and ID1, and is available

only in Full-IR mode.

IRSL2 is multiplexed on pin 96 with

DTR2, BOUT2 and ID2, and is

available only in Full-IR mode.

IRTX 44 UART2 Output

Group 12

Infrared Transmit – Infrared serial output data.

This signal is multiplexed with DENSEL only in Two-UART mode.

KBCLK 59 KBC I/O

Group 6

Keyboard Clock – This I/O pin transfers the keyboard clock between

the SuperI/O chip and the external keyboard using the PS/2 protocol.

This pin is connected internally to the internal TO signal of the KBC.

KBDAT 60 KBC I/O

Group 6

Keyboard Data – This I/O pin transfers the keyboard data between

the SuperI/O chip and the external keyboard using the PS/2 protocol.

This pin is connected internally to KBC’s P10.

MCLK 61 KBC I/O

Group 6

Mouse Clock – This I/O pin transfers the mouse clock between the

SuperI/O chip and the external keyboard using the PS/2 protocol.

This pin is connected internally to KBC’s T1.

MDAT 62 KBC I/O

Group 6

Mouse Data – This I/O pin transfers the mouse data between the

SuperI/O chip and the external keyboard using the PS/2 protocol.

This pin is connected internally to KBC’s P11.

MR 34 ISA-Bus Input

Group 1

Master Reset – An active high MR input signal resets the controller

to the idle state, and resets all disk interface output signals to their

inactive states. MR also clears the DOR, DSR and CCR registers,

and resets the MODE command, CONFIGURE command, and LOCK

command parameters to their default values. MR does not affect the

SPECIFY command parameters. MR sets the configuration registers

to their selected default values.

MTR1,0 46,45 FDC Output

Group 11

Motor Select 1,0 – These motor enable lines for drives 0 and 1 are

controlled by bits D7-4 of the Digital Output Register (DOR). They are

output signals that are active when they are low. They are encoded with

information to control four FDDs when bit 7 of the SuperI/O FDC

Configuration register is set See TABLE 1-2 for more information. See

DR1,0.

MTR0 is multiplexed with DRATE0 only in Two-UART mode.

MTR1 is multiplexed with P12 only in Two-UART mode.

P12 94, 46 or

43

KBC I/O

Group 7

I/O Port – KBC quasi-bidirectional port for general purpose input and

output.

P12 is multiplexed on pin 43 with IRRX1 and DRATE0, on pin 46 with

MTR1, and on pin 94 with DCD2.

P21,P20 64,63 KBC I/O

Group 7

I/O Port – KBC open-drain signals for general purpose input and

output. These signals are controlled by KBC firmware.

PD7-0 82-75 Parallel Por t I/O

Group 9

Parallel Port Data – These bidirectional signals transfer data to and

from the peripheral data bus and the appropriate parallel port data

register. These signals have a high current dr ive capability. See

Section 10.1.

PE 70 Parallel Port Input

Group 2

Group 3

Paper End – This input signal is set high by the printer when it is out

of paper. This pin has an internal weak pull-up or pull-down resistor.

RDATA 54 FDC Input

Group 1

Read Data – This input signal holds raw serial data read from the

Floppy Disk Drive (FDD).

Signal/Pin

Name

Pin

Number

Module

I/O and

Group #

Function

Page 17

Signal/Pin Connection and Description

SIGNAL/PIN DESCRIPTIONS

17

www.national.com

RI2,1 97,87 UART1 Input

Group 1

Ring Indicators (Modem) – When low, this signal indicates that a

telephone ring signal has been received by the modem.

The

RI1 and RI2 pins have schmitt-trigger input buffers.

RI2 is multiplexed with DENSEL and available only in Two-UART

mode.

RTS2,1 98,88 UART1,

UART 2

Output

Group 12

Request to Send – When low, these output signals indicate to the

modem or other data transfer device that the corresponding UART1

or UART2 is ready to exchange data.

A Master Reset (MR) sets

RTS to inactive high. Loopback operation

holds it inactive.

RTS2 is multiplexed on pin 98 with IRSL1 and ID1, and available only

in Two-UART mode.

RTS1 is multiplexed on pin 88 with BADDR1.

SIN2,1 99,89 UART1,

UART 2

Input

Group 1

Serial Input – This input signal receives composite serial data from

the communications link (peripheral device, modem or other data

transfer device).

SIN2 is multiplexed on pin 99 with ID3 and available only in TwoUART mode.

SLCT 69 Parallel Port Input

Group 2

Select – This input signal is set active high by the printer when the

printer is selected. This pin is internally connected to a nominal 25KΩ

pull-down resistor.

SLIN 73 Parallel Port I/O

Group 8

Select Input – When this signal is active low it selects the printer.

This signal is in TRI-STATE after a 0 is loaded into the corresponding

control register bit. Use an external 4.7 KΩ pull-up resistor.

This signal is multiplexed with

ASTRB.

SOUT2,1 100,92 UART1,

UART 2

Output

Group 12

Serial Output – This output signal sends composite serial data to the

communications link (peripheral device, modem or other data transfer

device).

The SOUT2,1 signals are set active high after a Master Reset (MR).

SOUT2 is multiplexed on pin 100 with IRRX2, IRSL0 and ID0, and is

available only in Two-UART mode.

SOUT1 is multiplexed on pin 92 with CFG0.

STB 67 Parallel Por t I/O

Group 8

Data Strobe – This output signal indicates to the printer that valid

data is available at the printer port.

This signal is in TRI-STATE after a 0 is loaded into the corresponding

control register bit.

An external 4.7 KΩ pull-up resistor should be employed.

For Input mode see bit 5, described in Section 4.5.16.

This signal is multiplexed with

WRITE.

STEP 51 FDC Output

Group 11

Step – This output signal issues pulses to the disk drive at a software

programmable rate to move the head during a seek operation.

TC 25 ISA-Bus Input

Group 1

DMA Terminal Count – The DMA controller issues TC to indicate the

termination of a DMA transfer. TC is accepted only when a

DACK

signal is active.

TC is active high in PC-AT mode, and active low in PS/2 mode.

TRK0 55 FDC Input

Group 1

Track 0 – This input signal indicates to the controller that the head of

the selected floppy disk drive is at track 0.

V

DD

90,41 Power

Supply

Input Main 5 V Power Supply – This signal is the 5 V supply voltage for

the digital circuitry.

V

SS

91,65,40,

15

Power

Supply

Output Ground – This signal provides the ground for the digital circuitry.

WAIT 66 Parallel Por t Input

Group 2

Wait – In EPP mode, the parallel port device uses this signal to

extend its access cycle.

WAIT is active low. This signal is multiplexed

with BUSY. See TABLE 4-12 on page 101 for more information.

Signal/Pin

Name

Pin

Number

Module

I/O and

Group #

Function

Page 18

Signal/Pin Connection and Description

18

SIGNAL/PIN DESCRIPTIONS

www.national.com

TABLE 1-3. Pins with a Strap Function During Reset

1. These pins have additional multiplexing options in Two-UART mode,

controlled by a configuration register. They do not automatically

change functions.

WDATA 49 FDC Output

Group 11

Write Data (FDC) – This output signal holds the write

precompensated serial data that is written to the selected floppy disk

drive. Precompensation is software selectable.

WGATE 53 FDC Output

Group 11

Write Gate (FDC) – This output signal enables the write circuitry of

the selected disk drive.

WGATE is designed to prevent glitches during

power up and power down. This prevents writing to the disk when

power is cycled.

WP 57 FDC Input

Group 1

Write Protected – This input signal indicates that the disk in the

selected drive is write protected.

WRITE 67 Parallel Port Output

Group 8

Write Strobe – In EPP mode, this active low signal is a write strobe.

This signal is multiplexed with

STB. See TABLE 4-12 on page 101 for

more information.

Signal/Pin

Name

Pin

Number

Module

I/O and

Group #

Function

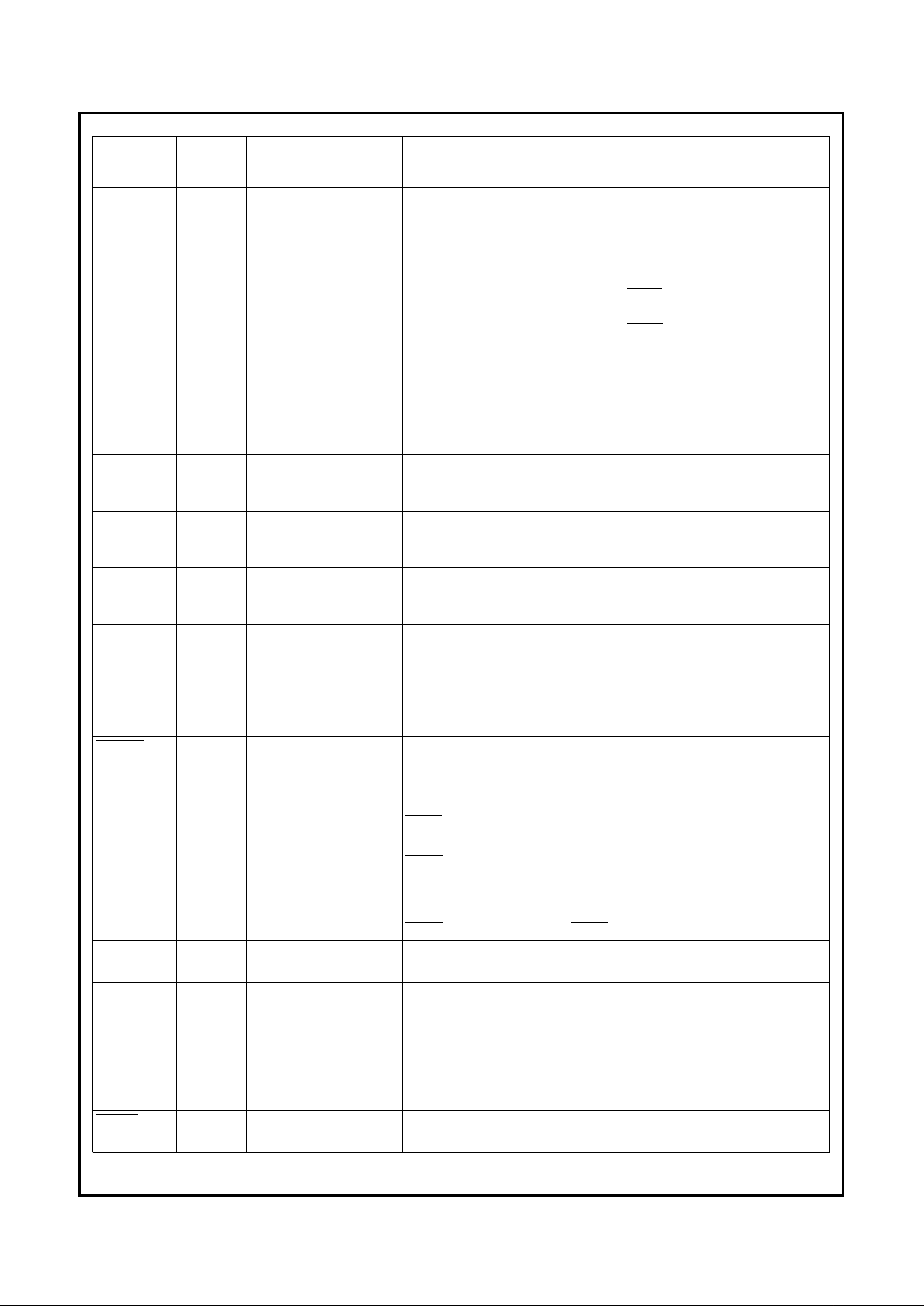

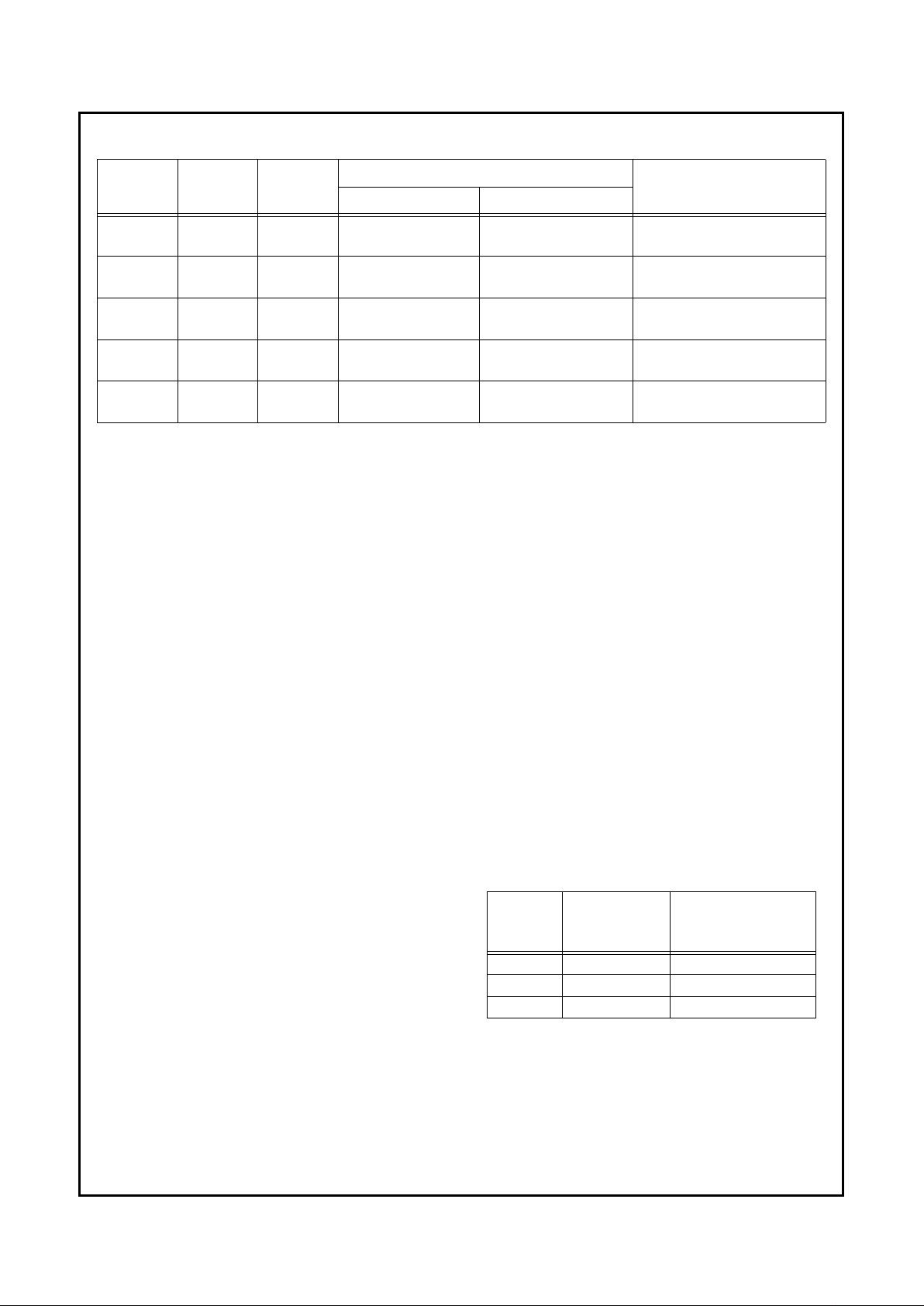

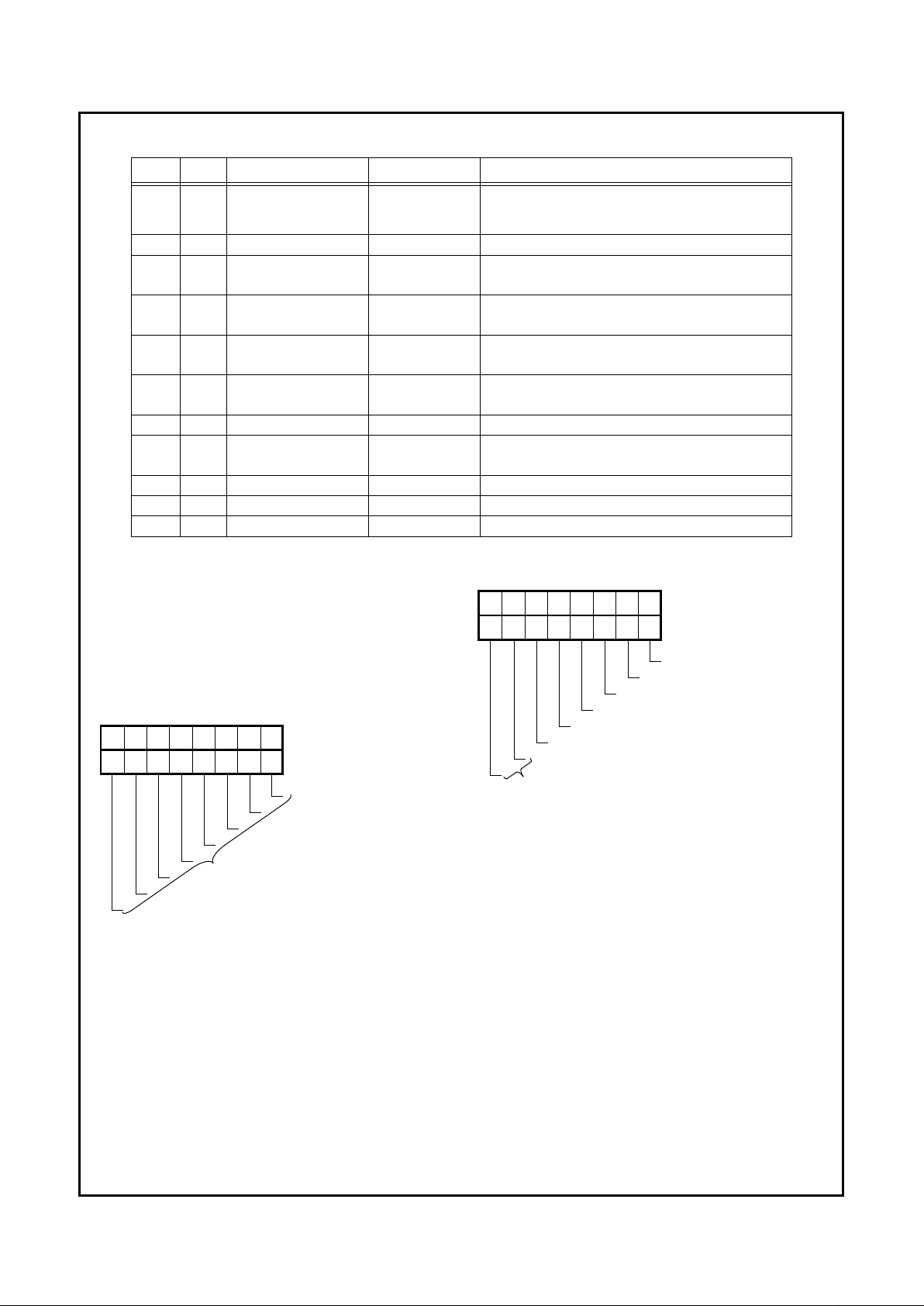

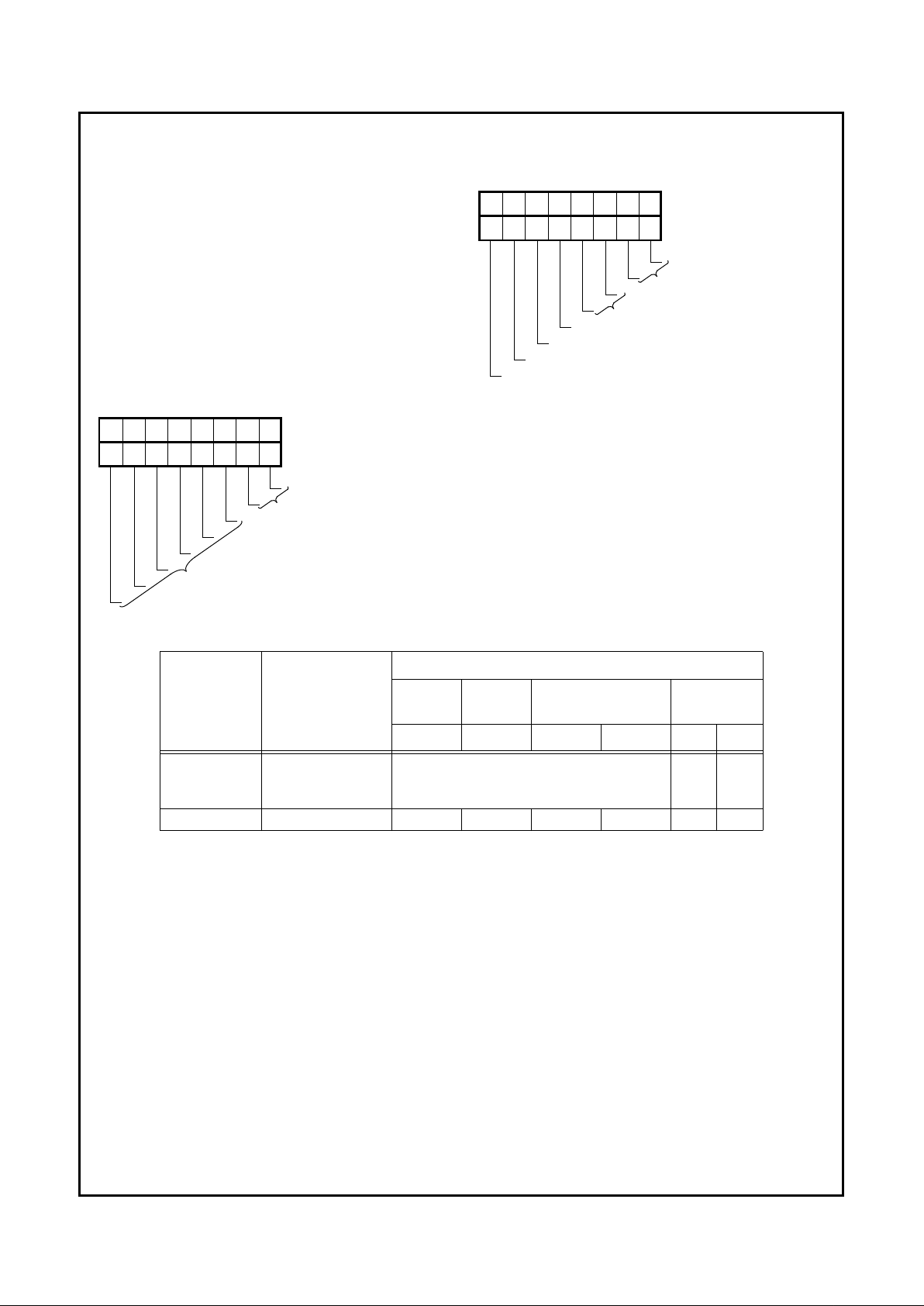

TABLE 1-2. Multiplexed Pins in Full-IR and Two-UART Modes

Pin

Full-IR Mode

CFG0 = 0

Two-UART Mode

CFG0 = 1

Signal/Pin Name Direction Signal/Pin Name Direction

93 A11 I

CTS2 I

94

P12 I/O DCD2 I

95 DRATE0 O

DSR2 I

96 IRSL2/ID2 I/O

DTR2/BOUT2 O

97 DENSEL I/O

RI2 I

98 IRSL1/ID1 I/O

RTS2 O

99 ID3 I SIN2 I

100 IRRX2/IRSL0/ID0 I/O SOUT2 O

43

1

IRRX1 I IRRX1/P12/DRATE0 I/O

44

1

IRTX O IRTX/DENSEL O

45

1

MTR0 O MTR0/DRATE0 O

46

1

MTR1 O MTR1/P12 I/O

48

1

DR1 O DR1/DENSEL O

Function Pin Symbols

BADDR0 86

DTR1/BOUT1/BADDR0

BADDR1 88

RTS1/BADDR1

CFG0 92 SOUT1/CFG0

Page 19

Configuration

19

2.0 Configuration

www.national.com

2.0 Configuration

The PC87309VLJ is partially configured by hardware, during reset. The configuration can also be changed by software, by changing the values of the configuration registers.

The configuration registers are accessed using an Index

register and a Data register. During reset, hardware strapping options define the addresses of the configuration registers. See Section 2.1.2 "The Index and Data Register

Pair".

After the Index and Data register pair have determined the

addresses of the configuration registers, the addresses of

the Index and Data registers can be changed within the ISA

I/O address space, and a 11-bit programmable register controls references to their addresses and to the addresses of

the other registers.

This chapter describes the hardware and software configuration processes. For each, it describes configuration of the

Index and Data register pair first. See Sections 2.1 "HARDWARE CONFIGURATION" and 2.2 "SOFTWARE CONFIGURATION" on page 20.

Section 2.3 "THE CONFIGURATION REGISTERS" on

page 21 presents an overview of the configuration registers

of the PC87309VLJ and describes each in detail.

2.1 HARDWARE CONFIGURATION

The PC87309VLJ Hardware Cofiguration is based on three

strap-pins: BADDR0, BADDR1 and CFG0.

The PC87309VLJ wakes up with the KBC active (enabled)

and all the other logical devices wake up inactive (disabled).

This is always true and is not affected by strapping.

Clock source is 48MHz, fed via CLKIN.

2.1.1 Wake Up Options

The PC87309VLJ supports three available Wake Up Options:

●

Full PnP ISA with Full-IR mode.

●

PnP Motherboard with Full-IR mode.

●

PnP Motherboard with Two-UART mode.

TABLE 2-1 "Strap Pins and Base Addresses" on page 20

shows the strap pins and their applicable wake up options.

The three available wake up options are a combination of

the four basic modes which are determined by three strappins during reset:

BADDR0 and BADDR1 strap-pins select one of two basic

modes.

●

Full PnP ISA mode – System wakes up in Wait for Key

state. (Not available when in Two-UART mode - see

CFG0 in TABLE 2-1).

Index and Data register addresses are as defined in the

“Plug and Play ISA Specification, Version 1.0a, May 5,

1994.”

●

PnP Motherboard mode – system wakes up in Config

state.

The BIOS configures the PC87309VLJ. Index and Data

register addresses are different from the addresses of

the PnP Index and Data registers. Configuration registers can be accessed as if the serial isolation procedure

had already been done, and the PC87309VLJ is selected.

The BIOS may switch the addresses of the Index and

Data registers to the PnP ISA addresses of the Index

and Data registers, by using software to modify the base

address bits, as shown in Section 2.4.3 on page 29.

CFG0 strap-pin selects between the following two modes:

●

Mode 1: Full-IR Mode

UART1 works as UART; UART2 works as fully IRcompliant device

●

Mode 2: Two-UART Mode

Either both UART1 and UART2 work as UARTs, or

UART 1 works as UART and UART2 works as par tially

IR-compliant device, providing only IRRX and IRTX

support

2.1.2 The Index and Data Register Pair

During reset, a hardware strapping option on the BADDR0

and BADDR1 pins defines an address for the Index and

Data Register pair.

TABLE 2-1 "Strap Pins and Base Addresses" shows the

base addresses for the Index and Data registers that hardware sets for each combination of values of the Base Address strap pins (BADDR0 and BADDR1). You can access

and change the content of the configuration registers at any

time, as long as the base addresses of the Index and Data

registers are defined.

When BADDR1 is low (0), the PnP protocol defines the addresses of the Index and Data register, and the system

wakes up from reset in the Wait for Key state.