Page 1

CALIFORNIA MICRO DEVICES

PACRG

P/Active

High Performance GTL/ECL Local Termination Network

Features

• Designed especially for Pentium Pro and RISCbased computers/servers

• Provides high speed bus termination

• Reduces ground bounce with center ground

pin placement

• Terminates 22 lines in a QSOP package

• Saves board space and reduces assembly cost

Product Description

CAMD’s P/Active RG GTL+ Local Bus Terminator is ideal

for Pentium Pro and related high speed bus termination

applications where a resistor approach is deemed suitable.

This device also meets the high-speed bus termination

demands of microprocessors like Motorola’s PowerPC,

DEC’s Alpha, Sun’s SPARC, and SGI’s MIPs processor, as

well as other high performance RISC processors for

embedded control applications.

The PACRG offers 22 terminations per package and meets

all related Intel specifications for Pentium Pro termination

requirements. Four popular values are available for a

variety of bus termination applications and line impedance

requirements: 47, 50, 56 and 68 ohms.

Applications

• Pentium Pro servers

• Pentium Pro desk top systems

• GTL, ECL terminator for embedded

processor busses

Refer to AP-201 Termination Application Note and AP-203 GTL+

Termination Application Note for further information.

The P/Active RG Termination Networks provide high

performance, high reliability, and low cost through manufacturing efficiency. The termination resistor elements are

fabricated using proprietary state-of-the-art thin film

technology. CAMD’s highly integrated solution is siliconbased and has the same enhanced reliability characteristics as today’s microprocessor products. The thin film

resistors have very high stability over a wide temperature

range, over applied voltage, and over life. In addition, the

QSOP industry standard packaging is manufacturingfriendly and yields the high reliability of other semiconductor components. The P/Active RG Pentium Pro Termination

Network provides a complete 300 point termination

solution in only 14 QSOP packages.

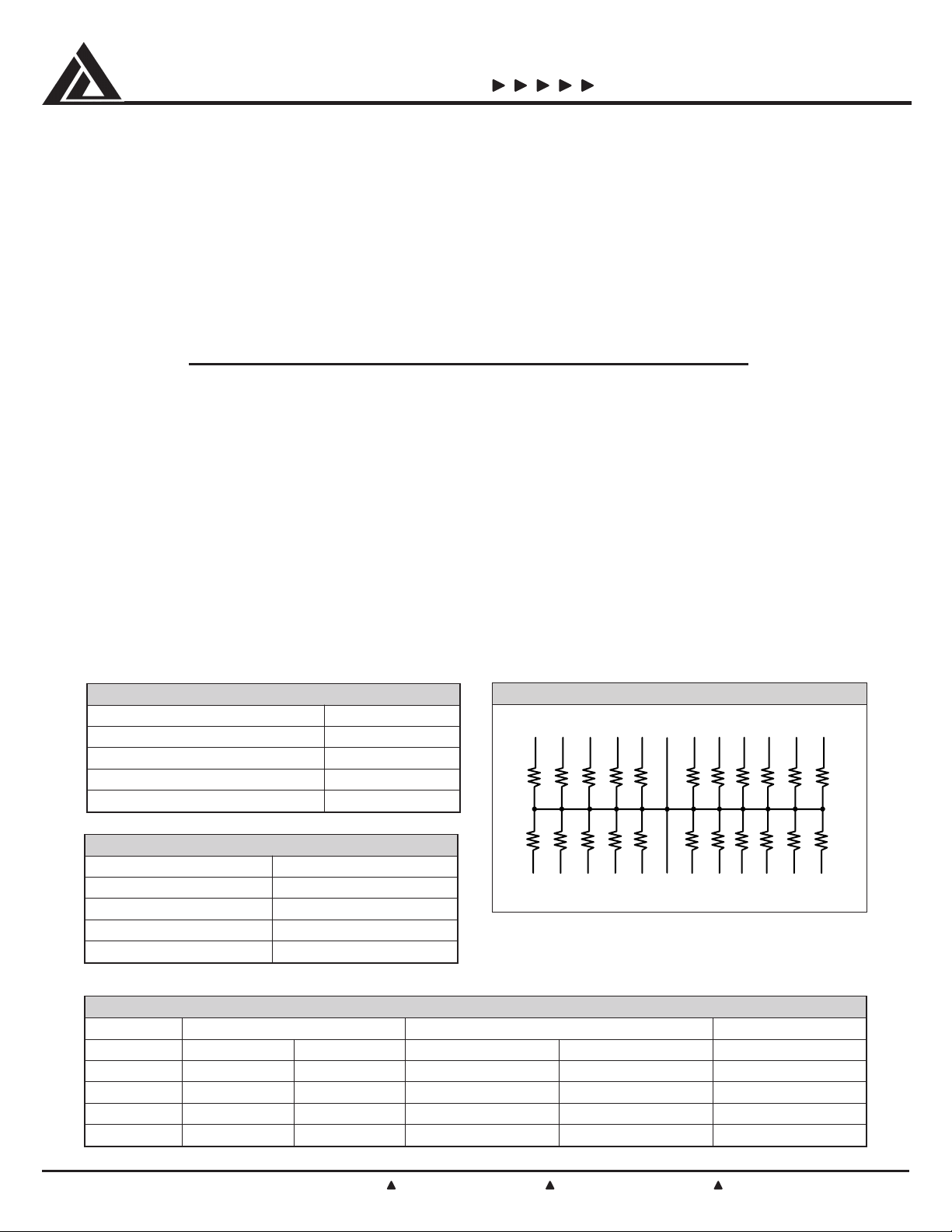

PIN DIAGRAM

)R(ecnareloTetulosbA%5±

egnaRerutarepmeTgnitarepOC°07otC°0

rotsiseR/gnitaRrewoPWm001

erutarepmeTegarotSC°051otC°56–

gnitaRrewoPegakcaPxaM,w00.1

SNOITACIFICEPSDRADNATS

24

R

T

R

T

SEULAVDRADNATS

(R ΩΩΩΩΩ)edoC

74074

05005

65065

86086

1232223214205196187178169151014111312

NOITAMROFNIGNIREDROTRAPDRADNATS

egakcaPrebmuNtraPgniredrO

edoCRsniPelytSsebuTleeR&epaTgnikraMtraP

)%1(07442POSQT/QGR074CAPR/QGR074CAPQGR074CAP

)%1(00542POSQT/QGR005CAPR/QGR005CAPQGR005CAP

)%1(06542POSQT/QGR065CAPR/QGR065CAPQGR065CAP

)%1(08642POSQT/QGR086CAPR/QGR086CAPQGR086CAP

© 2000 California Micro Devices Corp. All rights reserved.

8/10/2000

215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com

+'"

1

Page 2

CALIFORNIA MICRO DEVICES

Cha

500mV/De

Cha

e

PACRG

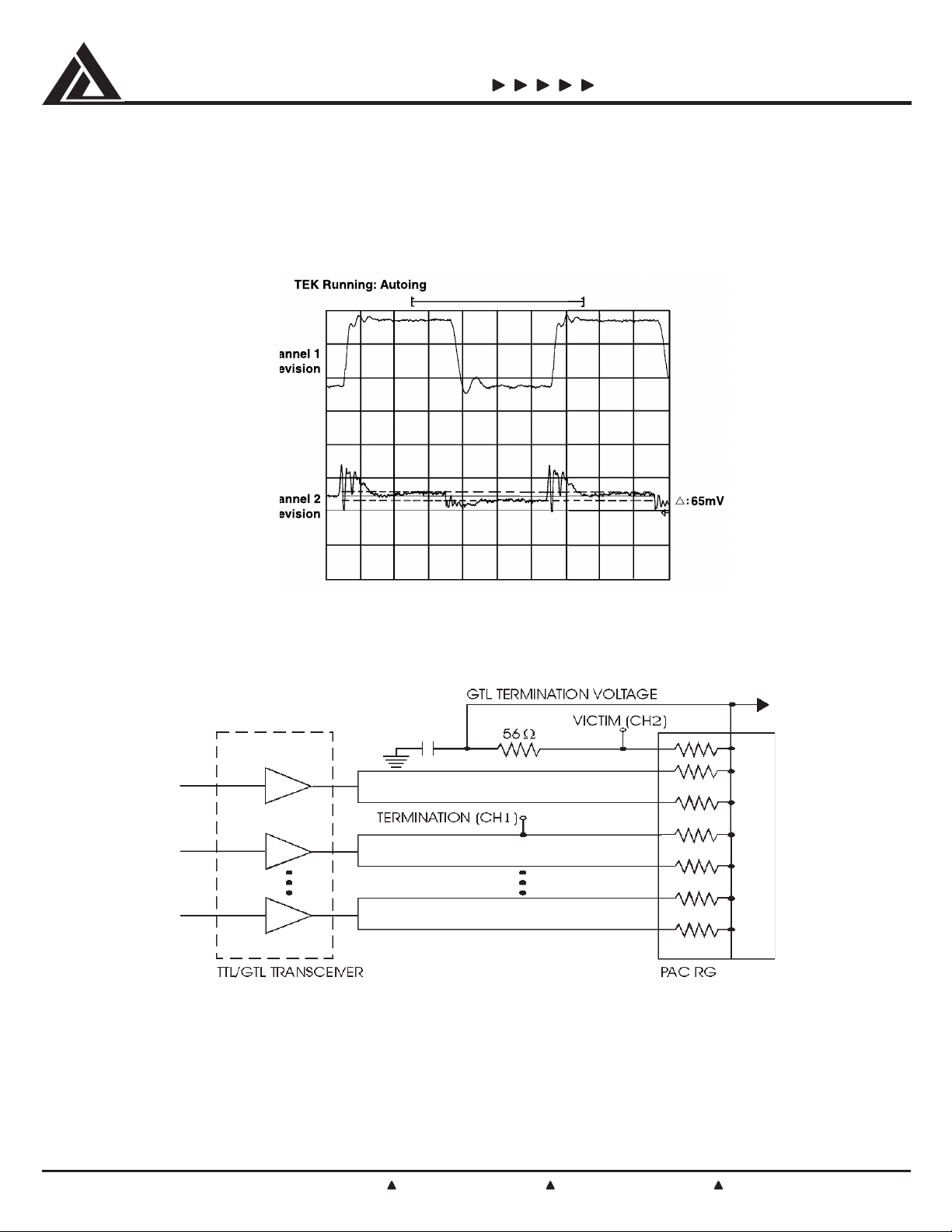

Signal at Termination and Victim Line (TA=25OC) (See Test Circuit)

Channel 1 (500mV/division) Termination Signal, Channel 2 (250mV/division) Victim Voltage. The victim voltage

crosstalk measures 65mV in the critical areas around the system clock. The system clock occurs approximately 4ns

before each data transition. The horizontal dashed lines are 65mV apart. The time scale is 5.0ns/division. The signal

voltage rise and fall times have been adjusted at the driver to conform to Intel specifications.) Measurements made

using Tektronix TDS820 6 GHz Digitizing Oscilloscope with P6207 FET Probes.

250mV/D

Test Circuit Block Diagram

©2000 California Micro Devices Corp. All rights reserved.

2

215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com

8/10/2000

Page 3

CALIFORNIA MICRO DEVICES

Test Circuit

JP1

GND

1

VCC_5

2

GND

3

VCC_3

4

GND

5

VCC_1.5

6

GND

7

GND

8

POWER

VREF

1000pF

GND

C25

0.1uF

PACRG

TP1

TP1

PB1

GND

GND

VCC_3

W1

SMA

GND

C11

0.1uF

GND

GND

GND

GATE1

GATE2

GATE3

GATE4

GND

GND

BUFFER1

GND

GND

1

2

3

5

6

7

8

9

10

12

13

14

15

16

17

19

20

21

22

23

24

26

27

28

GND

RIN1

RIN2

100

VCC_3

GND

C9

0.1uF

GND

100

GND

GND

C8

0.1uF

C10

0.1uF

VCC_5

GND

2

4

6

8

11

13

15

17

1

19

U1

/OEAB

LEAB

A1

A2

A3

VCC_3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

VCC_3

A16

A17

CLKIN

/OEBA

LEBA

74GTL16616

U2

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

1G

2G

74FCT244

/CEAB

CLKAB

CLKOUT

CLKBA

/CEBA

VREF

18

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

BUFFER1

16

14

12

GATE1

9

7

GATE2

5

GATE3

GATE4

3

TP4

PB4

TP4

GND

VCC_5

C17

GTL1

GTL2

GTL3

GTL4

GTL5

GTL6

GTL7

GTL8

GTL9

GTL10

GTL11

GTL_TEST

VREF

VICTIM

C12

0.1uF

0.1uF

GND

GND

R1

VCC_1.5

56

C15

1000pF

C16

0.1uF

GND

C13

C14

1000pF

0.1uF

GNDVCC_5

GND

56

55

54

52

51

49

48

47

45

44

43

42

41

40

38

37

36

35

34

33

31

30

29

VCC_5

VCC_3

VCC_1.5

GND

VCC_1.5

R3

1K

R4

2KC24

GND

PULSE_GEN

VCC_5

VCC_3

© 2000 California Micro Devices Corp. All rights reserved.

8/10/2000

215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com

VCC_1.5

C18

1000pF

GND

TP5

PB5

VICTIM

GND

R2

C20

1000pF

56

VTT

GND

C19

0.1uF

GND

GTL1

GTL2

GTL2

GTL3

GTL3

GTL4

GTL4

C21

GTL5 GTL7

0.1uF

GTL5

GTL6 GTL6

TP3

PB3

GND

U3

R

R

R

R

R

G

R

R

R

R

R

R

PRN331A

24

GTL11

R

23

GTL11

R

22

GTL10

R

21

GTL10

R

20

GTL9

R

19

G

18

R

17

R

16

R

15

R

14

R

13

R

GTL9

GTL8

GTL8

GTL7

VTT

C22

1000pF

VCC_1.5

C23

0.1uF

GND

1

2

3

4

5

6

7

8

9

10

11

12

TP3

3

Loading...

Loading...