Page 1

INTEGRATED CIRCUITS

83C749/87C749

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM,

low pin count

Preliminary specification

Supersedes data of 1998 Jan 06

IC20 Data Handbook

1998 Apr 23

Page 2

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

DESCRIPTION

The Philips 83C749/87C749 offers many of the advantages of the

80C51 architecture in a small package and at low cost.

The 8XC749 Microcontroller is fabricated with Philips high-density

CMOS technology. Philips epitaxial substrate minimizes CMOS

latch-up sensitivity.

The 8XC749 contains a 2k × 8 ROM (83C749) EPROM (87C749), a

64 × 8 RAM, 21 I/O lines, a 16-bit auto-reload counter/timer, a

fixed-priority level interrupt structure, an on-chip oscillator, a five

channel multiplexed 8-bit A/D converter, and an 8-bit PWM output.

The EPROM version of this device, the 87C749, is available in

plastic one-time programmable (OTP) packages. Once the array

has been programmed, it is functionally equivalent to the masked

ROM 83C749. Thus, unless explicitly stated otherwise, all

references made to the 83C749 apply equally to the 87C749.

The 83C749 supports two power reduction modes of operation

referred to as the idle mode and the power-down mode.

FEA TURES

•Available in erasable quartz lid or One-Time Programmable plastic

packages

•80C51 based architecture

•Small package sizes

– 28-pin DIP

– 28-pin Shrink Small Outline Package (SSOP)

– 28-pin PLCC

•Wide oscillator frequency range: 3.5MHz to 16MHz

•Low power consumption:

– Normal operation: less than 11mA @ 5V, 12MHz

– Idle mode

– Power-down mode

•2k × 8 ROM (83C749)

EPROM (87C749)

•64 × 8 RAM

•16-bit auto reloadable counter/timer

•5-channel 8-bit A/D converter

•8-bit PWM output/timer

•10-bit fixed-rate timer

•Boolean processor

•CMOS and TTL compatible

•Well suited for logic replacement, consumer and industrial

applications

83C749/87C749

P ART NUMBER SELECTION

ROM EPROM

P83C749EBP N P87C749EBP N OTP 0 to +70, 28-pin Plastic Dual In-line Package 3.5 to 16MHz SOT117-2

P83C749EBA A P87C749EBA A OTP 0 to +70, 28-pin Plastic Leaded Chip Carrier 3.5 to 16MHz SOT261-3

P83C749EBD DB P87C749EBD DB OTP 0 to +70, 28-pin Shrink Small Outline Package 3.5 to 16MHz SOT341-1

NOTE:

1. OTP = One Time Programmable EPROM.

1

TEMPERATURE RANGE °C

AND PACKAGE

FREQUENCY

DRAWING

NUMBER

1998 Apr 23

2

Page 3

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

BLOCK DIAGRAM

P0.0–P0.4

PORT 0

DRIVERS

V

CC

V

SS

RAM ADDR

REGISTER

B

REGISTER

RAM

ACC

TMP2

PSW

PORT 0

LATCH

ALU

PWM

PORT 2

LATCH

TMP1

PCON TCON

TH0 TL0

RTH RTL

INTERRUPT AND

TIMER BLOCKS

STACK

POINTER

IE

ROM/

EPROM

83C749/87C749

PROGRAM

ADDRESS

REGISTER

BUFFER

PC

INCRE-

MENTER

RST

TIMING

AND

CONTROL

OSCILLATOR

X1

INSTRUCTION

PD

REGISTER

X2

AV

ADC

SSAVCC

PORT 1

LATCH

PORT 1

DRIVERS

P1.0–P1.7

PORT 3

LATCH

PORT 3

DRIVERS

P3.0–P3.7

PROGRAM

COUNTER

DPTR

SU00305

1998 Apr 23

3

Page 4

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

PIN CONFIGURATION

P3.4/A4

P3.3/A3

P3.2/A2/A10

P3.1/A1/A9

P3.0/A0/A8

P0.2/V

P0.1/OE–PGM

P0.0/ASEL

RST

V

P1.0/ADC0/D0

P1.1/ADC1/D1

1

2

3

4

5

PLASTIC

DUAL

6

PP

X2

X1

SS

7

8

9

10

11

12

13

14

IN-LINE

PACKAGE

AND

SHRINK

SMALL

OUTLINE

PACKAGE

V

28

CC

P3.5/A5

27

P3.6/A6

26

P3.7/A7

25

24

P0.4/PWM OUT

23

P0.3

22

P1.7/T0/D7

21

P1.6/INT1/D6

20

P1.5/INT0/D5

19

AV

CC

18

AV

SS

17

P1.4/ADC4/D4

16

P1.3/ADC3/D3

15

P1.2/ADC2/D2

83C749/87C749

4126

5

11

12 18

Pin Function

1 P3.4/A4

2 P3.3/A3

3 P3.2/A2/A10

4 P3.1/A1/A9

5 P3.0/A0/A8

6 P0.2/V

7 P0.1/OE-PGM

8 P0.0/ASEL

9 RST

10 X2

11 X1

12 V

13 P1.0/ADC0/D0

14 P1.1/ADC1/D1

PP

SS

PLASTIC

LEADED

CHIP

CARRIER

Pin Function

15 P1.2/ADC2/D2

16 P1.3/ADC3/D3

17 P1.4/ADC4/D4

18 AV

19 AV

20 P1.5/INT0/D5

21 P1.6/INT1

22 P1.7/T0/D7

23 P0.3

24 P0.4/PWM OUT

25 P3.7/A7

26 P3.6/A6

27 P3.5/A5

28 V

25

19

SS

CC

/D6

CC

SU00304

1998 Apr 23

4

Page 5

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

83C749/87C749

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

PIN DESCRIPTION

MNEMONIC PIN NO. TYPE NAME AND FUNCTION

V

SS

V

CC

P0.0–P0.4 8–6

P1.0–P1.7 13–17,

P3.0–P3.7 5–1,

RST 9 I Reset: A high on this pin for two machine cycles while the oscillator is running resets the device. An

X1 11 I Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits. X1

X2 10 O Crystal 2: Output from the inverting oscillator amplifier.

1

AV

CC

1

AV

SS

NOTE:

1. AV

(reference ground) must be connected to 0V (ground). AVCC (reference input) cannot differ from VCC by more than ±0.2V, and must be

SS

in the range 4.5V to 5.5V .

2. When P0.2 is at or close to 0 volt, it may affect the internal ROM operation. We recommend that P0.2 be tied to V

(e.g., 2kΩ).

12 I Circuit Ground Potential.

28 I Supply voltage during normal, idle, and power-down operation.

I/O Port 0: Port 0 is a 5-bit bidirectional port. Port 0.0–P0.2 are open drain. Port 0.0–P0.2 pins that have

23, 24

1s written to them float, and in that state can be used as high-impedance inputs. P0.3–P0.4 are

bidirectional I/O port pins with internal pull-ups. These pins are driven low if the port register bit is

written with a 0. The state of the pin can always be read from the port register by the program. Port 0.3

and 0.4 have internal pull-ups that function identically to port 3. Pins that have 1s written to them are

pulled high by the internal pull-ups and can be used as inputs.

While P0.0 anbd P0.1 differ from “standard TTL” characteristics, they are close enough for the pins to

still be used as general-purpose I/O.

6 I VPP (P0.2) – Programming voltage input. (See Note 2.)

7 I OE/PGM (P0.1) – Input which specifies verify mode (output enable) or the program mode.

OE/PGM = 1 output enabled (verify mode).

OE/PGM = 0 program mode.

8 I ASEL (P0.0) – Input which indicates which bits of the EPROM address are applied to port 3.

ASEL = 0 low address byte available on port 3.

ASEL = 1 high address byte available on port 3 (only the three least significant bits are used).

I/O Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to

20–22

them are pulled high by the internal pull-ups and can be used as inputs. P0.3–P0.4 pins are

bidirectional I/O port pins with internal pull-ups. As inputs, port 1 pins that are externally pulled low will

source current because of the internal pull-ups. (See DC Electrical Characteristics: I

serves the special function features of the SC80C51 family as listed below:

). Port 1 also

IL

20 I INT0 (P1.5): External interrupt.

21 I INT1 (P1.6): External interrupt.

22 I T0 (P1.7): T imer 0 external input.

13–17 I ADC0 (P1.0)–ADC4 (P1.4): Port 1 also functions as the inputs to the five channel multiplexed A/D

converter. These pins can be used as outputs only if the A/D function has been disabled. These pins

can be used as digital inputs while the A/D converter is enabled.

Port 1 serves to output the addressed EPROM contents in the verify mode and accepts as inputs the

value to program into the selected address during the program mode.

I/O Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to

27–25

them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are

externally being pulled low will source current because of the pull-ups. (See DC Electrical

Characteristics: I

programmed (or verified). The 11-bit address is multiplexed into this port as specified by P0.0/ASEL.

). Port 3 also functions as the address input for the EPROM memory location to be

IL

internal diffused resistor to VSS permits a power-on RESET using only an external capacitor to VCC.

After the device is reset, a 10-bit serial sequence, sent LSB first, applied to RESET, places the device

in the programming state allowing programming address, data and V

or verification purposes. The RESET serial sequence must be synchronized with the X1 input.

to be applied for programming

PP

also serves as the clock to strobe in a serial bit stream into RESET to place the device in the

programming state.

19 I Analog supply voltage and reference input.

18 I Analog supply and reference ground.

via a small pullup

CC

1998 Apr 23

5

Page 6

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

OSCILLA T OR CHARACTERISTICS

X1 and X2 are the input and output, respectively, of an inverting

amplifier which can be configured for use as an on-chip oscillator.

To drive the device from an external clock source, X1 should be

driven while X2 is left unconnected. There are no requirements on

the duty cycle of the external clock signal, because the input to the

internal clock circuitry is through a divide-by-two flip-flop. However,

minimum and maximum high and low times specified in the data

sheet must be observed.

IDLE MODE

The 8XC749 includes the 80C51 power-down and idle mode

features. In idle mode, the CPU puts itself to sleep while all of the

on-chip peripherals except the A/D and PWM stay active. The

functions that continue to run while in the idle mode are Timer 0,

Timer I, and the interrupts. The instruction to invoke the idle mode is

the last instruction executed in the normal operating mode before

the idle mode is activated. The CPU contents, the on-chip RAM, and

all of the special function registers remain intact during this mode.

The idle mode can be terminated either by any enabled interrupt (at

which time the process is picked up at the interrupt service routine

and continued), or by a hardware reset which starts the processor in

the same manner as a power-on reset. Upon powering-up the

circuit, or exiting from idle mode, sufficient time must be allowed for

stabilization of the internal analog reference voltages before an A/D

conversion is started.

Special Function Registers

The special function registers (directly addressable only) contain all

of the 8XC751 registers except the program counter and the four

register banks. Most of the 21 special function registers are used to

control the on-chip peripheral hardware. Other registers include

arithmetic registers (ACC, B, PSW), stack pointer (SP) and data

pointer registers (DPH, DPL). Nine of the SFRs are bit addressable.

Data Pointer

The data pointer (DPTR) consists of a high byte (DPH) and a low

byte (DPL). In the 80C51 this register allows the access of external

data memory using the MOVX instruction. Since the 83C749 does

not support MOVX or external memory accesses, this register is

generally used as a 16-bit offset pointer of the accumulator in a

MOVC instruction. DPTR may also be manipulated as two

independent 8-bit registers.

POWER-DOWN MODE

In the power-down mode, the oscillator is stopped and the

instruction to invoke power-down is the last instruction executed.

Only the contents of the on-chip RAM are preserved. A hardware

reset is the only way to terminate the power-down mode. The control

bits for the reduced power modes are in the special function register

PCON.

Table 1. External Pin Status During Idle and

Power-Down Modes

MODE Port 0* Port 1 Port 2

Idle Data Data Data

Power-down Data Data Data

* Except for PWM output (P0.4).

DIFFERENCES BETWEEN THE 8XC749 AND THE

80C51

Program Memory

On the 8XC749, program memory is 2048 bytes long and is not

externally expandable, so the 80C51 instructions MOVX, LJMP, and

LCALL are not implemented. If these instructions are executed, the

appropriate number of instruction cycles will take place along with

external fetches; however, no operation will take place. The LJMP

may not respond to all program address bits. The only fixed

locations in program memory are the addresses at which execution

is taken up in response to reset and interrupts, which are as follows:

Event Address

Reset 000

External INT0

Counter/timer 0 00B

External INT1 013

Timer I 01B

ADC 02B

PWM 033

Memory Organization

The 8XC749 manipulates operands in three memory address

spaces. The first is the program memory space which contains

program instructions as well as constants such as look-up tables.

The program memory space contains 2k bytes in the 8XC749.

The second memory space is the data memory array which has a

logical address space of 128 bytes. However, only the first 64 (0 to

3FH) are implemented in the 8XC749.

The third memory space is the special function register array having

a 128-byte address space (80H to FFH). Only selected locations in

this memory space are used (see Table 2). Note that the

architecture of these memory spaces (internal program memory,

internal data memory , and special function registers) is identical to

the 80C51, and the 8XC749 varies only in the amount of memory

physically implemented.

The 8XC749 does not directly address any external data or program

memory spaces. For this reason, the MOVX instructions in the

80C51 instruction set are not implemented in the 83C749, nor are

the alternate I/O pin functions RD

I/O Ports

The I/O pins provided by the 83C749 consist of port 0, port 1, and

port 3.

Port 0

Port 0 is a 5-bit bidirectional I/O port and includes alternate functions

on some pins of this port. Pins P0.3 and P0.4 are provided with

internal pullups while the remaining pins (P0.0, P0.1, and P0.2) have

open drain output structures. The alternate function for port P0.4 is

PWM output.

If the alternate function PWM is not being used, then this pin may be

used as an I/O port.

83C749/87C749

Program Memory

003

and WR.

1998 Apr 23

6

Page 7

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

Port 1

Port 1 is an 8-bit bidirectional I/O port whose structure is identical to

the 80C51, but also includes alternate input functions on all pins.

The alternate pin functions for port 1 are:

P1.0-P1.4 - ADC0-ADC4 - A/D converter analog inputs

P1.5 INT0

P1.6 INT1

- external interrupt 0 input

- external interrupt 1 input

P1.7 - T0 - timer 0 external input

If the alternate functions INT0

, INT1, or T0 are not being used, these

pins may be used as standard I/O ports. It is necessary to connect

and AVSS to VCC and VSS, respectively, in order to use P1.5,

AV

CC

P1.6, and P1.7 pins as standard I/O pins. When the A/D converter is

enabled, the analog channel connected to the A/D may not be used

as a digital input; however, the remaining analog inputs may be used

as digital inputs. They may not be used as digital outputs. While the

A/D is enabled, the analog inputs are floating.

Port 3

Port 3 is an 8-bit bidirectional I/O port whose structure is identical to

the 80C51. Note that the alternate functions associated with port 3

of the 80C51 have been moved to port 1 of the 83C749 (as

applicable). See Figure 1 for port bit configurations.

Counter/Timer Subsystem

The 8XC749 has one counter/timer called timer/counter 0. Its

operation is similar to mode 2 operation on the 80C51, but is

extended to 16 bits with 16 bits of autoload. The controls for this

counter are centralized in a single register called TCON.

Timer I Implementation

Timer I is clocked once per machine cycle, which is the oscillator

frequency divided by 12. The timer operation is enabled by setting

the TIRUN bit (bit 4) in the I2CFG register. Writing a 0 into the

TIRUN bit will stop and clear the timer. The timer is 10 bits wide, and

when it reaches the terminal count of 1024, it carries out and sets

the Timer I interrupt flag. An interrupt will occur if the Timer I

interrupt is enabled by bit ETI (bit 4) of the Interrupt Enable (IE)

register, and global interrupts are enabled by bit EA (bit 7) of the

same IE register.

The vector address for the Timer I interrupt is 1Bhex, and the

interrupt service routine must start at this address. As with all 8051

family microcontrollers, only the Program Counter is pushed onto

the stack upon interrupt (other registers that are used both by the

interrupt service routine and elsewhere must be explicitly saved).

The Timer I interrupt flag is cleared by setting the CKRTI bit (bit 5 of

the I1CFG register. For more information, see application note

AN427.

Interrupt Subsystem—Fixed Priority

The IP register and the 2-level interrupt system of the 80C51 are

eliminated. The interrupt structure is a seven-source, one-level

interrupt system similar to the 8XC751. Simultaneous interrupt

conditions are resolved by a single-level, fixed priority as follows:

Highest priority: Pin INT0

Lowest priority: ADC

The vector addresses are as follows:

Source Vector Address

INT0 0003H

TF0 000BH

INT1 0013H

TIMER I 001BH

ADC 002BH

PWM 0033H

Interrupt Control Registers

The 80C51 interrupt enable register is modified to take into account

the different interrupt sources of the 8XC749.

Interrupt Enable Register

MSB LSB

EA

Position Symbol Function

IE.7 EA Global interrupt disable when EA = 0

IE.6 EAD A/D conversion complete

IE.5 ETI Timer I

IE.4 —

IE.3 EPWM PWM counter overflow

IE.2 EX1 External interrupt 1

IE.1 ET0 Timer 0 overflow

IE.0 EX0 External interrupt 0

83C749/87C749

Counter/timer flag 0

Pin INT1

PWM

Timer I

EAD ETI — EPWM EX1 ET0 EX0

READ

LATCH

INT. BUS

WRITE TO

LATCH

READ

1998 Apr 23

PIN

ALTERNATE

OUTPUT

FUNCTION

DQ

P1.X

LATCH

CL Q

ALTERNATE INPUT

FUNCTION

READ

V

DD

INTERNAL

PULL-UP

P1.X

PIN

LATCH

INT. BUS

WRITE TO

LATCH

READ

PIN

Figure 1. Port Bit Latches and I/O Buffers

7

ALTERNATE

OUTPUT

FUNCTION

DQ

P0.X

LATCH

CL Q

ALTERNATE INPUT

FUNCTION

P0.X

PIN

SU00306

Page 8

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

Pulse Width Modulation Output (P0.4)

The PWM outputs pulses of programmable length and interval. The

repetition frequency is defined by an 8-bit prescaler which generates

the clock for the counter. The prescaler register is PWMP. The

prescaler and counter are not associated with any other timer. The

8-bit counter counts modulo 255, that is from 0 to 254 inclusive. The

value of the 8-bit counter is compared to the contents of a compare

register, PWM. When the counter value matches the contents of this

register, the output of the PWM is set high. When the counter reaches

zero, the output of the PWM is set low. The pulse width ratio (duty

cycle) is defined by the contents of the compare register and is in the

range of 0 to 1 programmed in increments of 1/255. The PWM output

can be set to be continuously high by loading the compare register

with 0 and the output can be set to be continuously low by loading the

compare register with 255. The PWM output is enabled by a bit in a

special function register, PWENA. When enabled, the pin output is

driven with a fully active pull-up. That is, when the output is high, a

strong pull-up is continuously applied. When disabled, the pin

functions as a normal bidirectional I/O pin, however, the counter

remains active.

The PWM function is disabled during RESET and remains disabled

after reset is removed until re-enabled by software. The PWM output

is high during power down and idle. The counter is disabled during

idle. The repetition frequency of the PWM is given by:

f

= f

PWM

The low/high ratio of the PWM signal is PWM / (255 – PWM) for

PWM not equal to 255. For PWM = 255, the output is always low.

The repetition frequency range is 92Hz to 23.5kHz for an oscillator

frequency of 12MHz.

An interrupt will be asserted upon PWM counter overflow if the

interrupt is not masked off.

The PWM output is an alternative function of P0.4. In order to use

this port as a bidirectional I/O port, the PWM output must be

disabled by clearing the enable/disable bit in PWENA. In this case,

the PWM subsystem can be used as an interval timer by enabling

the PWM interrupt.

/ 2 (1 + PWMP) 255

OSC

Special Function Register Addresses

Special function registers for the 8XC749 are identical to those of

the 80C51, except for the changes listed below:

80C51 special function registers not present in the 8XC749 are

TMOD (89), P2 (A0) and IP (B8). Additional special function

registers are ADCON (A0), ADAT (84), PWM (8E), PWMP (8F), and

PWENA (FE).

A/D Converter

The analog input circuitry consists of a 5-input analog multiplexer and

an A to D converter with 8-bit resolution. The conversion takes 40

machine cycles, i.e., 40µs at 12MHz oscillator frequency. The A/D

converter is controlled using the ADCON control register. Input

channels are selected by the analog multiplexer through ADCON

register bits 0–2.

The 83C749 contains a five-channel multiplexed 8-bit A/D converter.

The conversion requires 40 machine cycles (40µs at 12MHz

oscillator frequency).

The A/D converter is controlled by the A/D control register, ADCON.

Input channels are selected by the analog multiplexer by bits

ADCON.0 through ADCON.2. The ADCON register is not bit

addressable.

ADCON Register

MSB LSB

X X ENADC ADCI ADCS AADR2 AADR1 AADR0

ADCI ADCS Operation

0 0 ADC not busy, a conversion can be started.

0 1 ADC busy, start of a new conversion is blocked.

1 0 Conversion completed, start of a new conversion is

1 1 Not possible.

ADDR2 ADDR1 ADDR0 INPUT PIN

0 0 0 P1.0

0 0 1 P1.1

0 1 0 P1.2

0 1 1 P1.3

1 0 0 P1.4

Position Symbol Function

ADCON.5 ENADC Enable A/D function when ENADC = 1. Reset

ADCON.4 ADCI ADC interrupt flag. This flag is set when an

ADCON.3 ADCS ADC start. Setting this bit starts an A/D

ADCON.2 AADR2 Analog input select.

ADCON.1 AADR1 Analog input select.

ADCON.0 AADR0 Analog input select. This binary coded

The completion of the 8-bit ADC conversion is flagged by ADCI in

the ADCON register, and the result is stored in the special function

register ADAT.

An ADC conversion in progress is unaffected by an ADC start. The

result of a completed conversion remains unaffected provided ADCI

remains at a logic 1. While ADCS is a logic 1 or ADCI is a logic 1, a

new ADC START will be blocked and consequently lost. An ADC

conversion in progress is aborted when the idle or power-down

mode is entered. The result of a completed conversion (ADCI = logic

1) remains unaffected when entering the idle mode. See Figure 2 for

an A/D input equivalent circuit.

The analog input pins ADC0-ADC4 may be used as digital inputs

and outputs when the A/D converter is disabled by a 0 in the

ENADC bit in ADCON. When the A/D is enabled, the analog input

channel that is selected by the ADDR2-ADDR0 bits in ADCON

cannot be used as a digital input. Reading the selected A/D channel

as a digital input will always return a 1. The unselected A/D inputs

83C749/87C749

blocked.

INPUT CHANNEL SELECTION

forces ENADC = 0.

ADC conversion is complete. If IE.6 = 1, an

interrupt is requested when ADCI = 1. The

ADCI flag is cleared when conversion data is

read. This flag is read only.

conversion. Once set, ADCS remains high

throughout the conversion cycle. On

completion of the conversion, it is reset just

before the ADCI interrupt flag is cleared.

ADCS cannot be reset by software. ADCS

should not be used to monitor the A/D

converter status. ADCI should be used for this

purpose.

address selects one of the five analog input

port pins of P1 to be input to the converter. It

can only be changed when ADCI and ADCS

are both low. AADR2 is the most significant

bit.

1998 Apr 23

8

Page 9

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

83C749/87C749

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

may always be used as digital inputs. Unselected analog inputs will

be floating and may not be used as digital outputs.

The A/D reference inputs on the 8XC749 are tied together with the

analog supply pins AVCC and AVSS. This means that the reference

voltage on the A/D cannot be varied separately from the analog

supply pins. AV

connected to a supply voltage between 4.5V and 5.5V . A/D

measurements may be made in the range of 4.5V to 5.5V .

Increasing the voltage on the A/D ground reference above 0V or

reducing the voltage on the positive A/D reference below 4.5V is not

permitted.

Table 2. 8XC749 Special Function Registers

SYMBOL DESCRIPTION

ACC* Accumulator E0H E7 E6 E5 E4 E3 E2 E1 E0 00H

ADAT# A/D result 84H 00H

ADCON# A/D control A0H – – ENADC ADCI ADCS AADR2 AADR1 AADR0 C0H

B* B register F0H F7 F6 F5 F4 F3 F2 F1 F0 00H

DPTR:

DPL

DPH

IE*# Interrupt enable ADH EA EAD ETI — EPWM EX1 ET0 EX0 00H

P0*# Port 0 80H – – – PWM0 – – – – xxx11111B

P1*# Port 1 90H T0 INT1 INT0 ADC4 ADC3 ADC2 ADC1 ADC0

P3* Port 3 B0H B7 B6 B5 B4 B3 B2 B1 B0 FFH

PCON# Power control 87H – – – – – – PD IDL xxxx0000B

PSW* Program status word D0H CY AC F0 RS1 RS0 OV – P 00H

PWCM# PWM compare 8EH xxxxxxxxB

PWENA# PWM enable FEH – – – – – – – PWE FEH

PWMP# PWM prescaler 8FH 00H

RTL# Timer low reload 8BH 00H

RTH# Timer high reload 8DH 00H

SP Stack pointer 81H 07H

TL# Timer low 8AH 00H

TH# Timer high 8CH 00H

TICON*# Timer I control D8H/RD – – 0 TIRUN – – – – 0000xx00B

TCON*# Timer control 88H GATE C/T TF TR IE0 IT0 IE1 IT1 00H

* SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

Data pointer

(2 bytes)

Data pointer low

Data pointer high

DIRECT

ADDRESS

82H

83H

WR – – CLRTI TIRUN – – – –

BIT ADDRESS, SYMBOL, OR ALTERNATIVE PORT FUNCTION

MSB LSB

AF AE AD AC AB AA A9 A8

– – – 84 83 82 81 80

97 96 95 94 93 92 91 90 FFH

D7 D6 D5 D4 D3 D2 D1 D0

DF DE DD DC DB DA D9 D8

8F 8E 8D 8C 8B 8A 89 88

must be connected to 0V and AVCC must be

SS

RESET

VALUE

00H

00H

1998 Apr 23

9

Page 10

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

83C749/87C749

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

I

N+1

I

N

+

R

S

V

ANALOG

INPUT

Rm = 0.5 - 3 kΩ

CS + CC = 15pF maximum

RS = Recommended < 9.6 kΩ for 1 LSB @ 12MHz

NOTE:

Because the analog to digital converter has a sampled-data comparator, the input looks capacitive to a source. When a conversion

is initiated, switch Sm closes for 8tcy (8µs @ 12MHz crystal frequency) during which time capacitance Cs + Cc is charged. It should

be noted that the sampling causes the analog input to present a varying load to an analog source.

Figure 2. A/D Input: Equivalent Circuit

Sm

Sm

C

S

N+1

N

Multiplexer

Rm

Rm

N+1

N

To Comparator

C

C

SU00199

A/D CONVERTER P ARAMETER DEFINITIONS

The following definitions are included to clarify some specifications

given and do not represent a complete set of A/D parameter

definitions.

Absolute Accuracy Error

Absolute accuracy error of a given output is the difference between

the theoretical analog input voltage to produce a given output and

the actual analog input voltage required to produce the same code.

Since the same output code is produced by a band of input voltages,

the “required input voltage” is defined as the midpoint of the band of

input voltage that will produce that code. Absolute accuracy error

not specified with a code is the maximum over all codes.

Nonlinearity

If a straight line is drawn between the end points of the actual

converter characteristics such that zero offset and full scale errors

are removed, then non-linearity is the maximum deviation of the

code transitions of the actual characteristics from that of the straight

line so constructed. This is also referred to as relative accuracy and

also integral non-linearity.

Differential Non-Linearity

Differential non-linearity is the maximum difference between the

actual and ideal code widths of the converter. The code widths are

the differences expressed in LSB between the code transition

points, as the input voltage is varied through the range for the

complete set of codes.

Gain Error

Gain error is the deviation between the ideal and actual analog input

voltage required to cause the final code transition to a full-scale

output code after the offset error has been removed. This may

sometimes be referred to as full scale error.

Offset Error

Offset error is the difference between the actual input voltage that

causes the first code transition and the ideal value to cause the first

code transition. This ideal value is 1/2 LSB above V

ref–

.

Channel to Channel Matching

Channel to channel matching is the maximum difference between

the corresponding code transitions of the actual characteristics

taken from different channels under the same temperature, voltage

and frequency conditions.

Crosstalk

Crosstalk is the measured level of a signal at the output of the

converter resulting from a signal applied to one deselected channel.

T otal Error

Maximum deviation of any step point from a line connecting the ideal

first transition point to the ideal last transition point.

Relative Accuracy

Relative accuracy error is the deviation of the ADC’s actual code

transition points from the ideal code transition points on a straight

line which connects the ideal first code transition point and the final

code transition point, after nullifying offset error and gain error. It is

generally expressed in LSBs or in percent of FSR.

1998 Apr 23

10

Page 11

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

COUNTER/TIMER

The 8XC749 counter/timer is designated Timer 0 and is separate

from Timer I and from the PWM. Its operation is similar to mode 2 of

the 80C51 counter/timer , extended to 16 bits. When Timer 0 is used

in the external counter mode, the T0 input (P1.7) is sampled every

S4P1. The counter/timer function is controlled using the timer control

register (TCON).

TCON Register

MSB LSB

GATE C/T TF TR IE0 IT0 IE1 IT1

Position Symbol Function

TCON.7 GATE 1 – Timer 0 is enabled only when INT0 pin is

high and TR is 1.

0 – Timer 0 is enabled only when TR is 1.

TCON.6 C/T 1 – Counter operation from T0 pin.

0 – Timer operation from internal clock.

TCON.5 TF 1 – Set on overflow of T0.

0 – Cleared when processor vectors to interrupt

routine and by reset.

TCON.4 TR 1 – Enable timer 0

0 – Disable timer 0

TCON.3 IE0 1 – Edge detected on INT0

TCON.2 IT0 1 – INT0 is edge triggered.

0 – INT0 is level sensitive.

TCON.1 IE1 1 – Edge detected on INT1

TCON.0 IT1 1 – INT1 is edge triggered.

0 – INT1 is level sensitive.

These flags are functionally identical to the corresponding 80C51

flags except that there is only one of the 80C51 style timers, and the

flags are combined into one register.

Note that the positions of the IE0/IT0 and IE1/IT1 bits are

transposed from the positions used in the standard 80C51 TCON

register.

Timer I may be used as a fixed time base timer or watchdog timer.

Timer T0 is a 16-bit autoreloadable timer/counter , that operates

similar to mode 2 operation on the 80C51, but is extended to 16 bits.

The timer/counter is clocked by either 1/12 the oscillator frequency

or by transitions on the T0 pin. The C/T bit in special function

register TCON selects between these two modes. When the TCON

TR bit is set, the timer/counter is enabled. Register pair TH and TL

are incremented by the clock source. When the register pair

overflows, the register pair is reloaded with the values in registers

RTH and RTL. The value in the reload registers is left unchanged.

The TF bit in special function register TCON is set on counter

overflow and, if the interrupt is enabled, will generate an interrupt

(see Figure 3).

83C749/87C749

INT0

OSC

T0 Pin

TR

Gate

Pin

÷ 12

C/T = 0

C/T = 1

TL TH TF

Reload

RTL RTH

Int.

SU00300

Figure 3. 83C749 Counter/Timer Block Diagram

ABSOLUTE MAXIMUM RATINGS

1, 3, 4

PARAMETER RATING UNIT

Storage temperature range –65 to +150 °C

Voltage from V

CC

to V

SS

–0.5 to +6.5 V

Voltage from any pin to VSS (except VPP) –0.5 to VCC + 0.5 V

Power dissipation 1.0 W

Voltage from VPP pin to V

SS

–0.5 to + 13.0 V

NOTES ON PAGE 13.

1998 Apr 23

11

Page 12

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

DC ELECTRICAL CHARACTERISTICS

T

= 0°C to +70°C, AVCC = 5V ±5, AVSS = 0V

amb

VCC = 5V ± 10%, VSS = 0V

SYMBOL PARAMETER CONDITIONS MIN TYP

I

CC

Inputs

V

IL

V

IH

V

IH1

V

IL1

V

IH2

Outputs

V

OL

V

OL1

V

OH

V

OH2

V

OL2

C

I

IL

I

TL

I

LI

R

RST

C

IO

I

PD

V

PP

I

PP

Analog Inputs (A/D guaranteed only with quartz window covered.)

AV

CC

AI

CC

AV

IN

C

IA

t

ADS

t

ADC

NOTES ON FOLLOWING PAGE.

Supply current (see Figure 6)

Input low voltage (0 to 70°C) –0.5 0.2VCC–0.1 V

Input high voltage, except X1, RST (0 to 70°C) 0.2VCC+0.9 VCC+0.5 V

Input high voltage, X1, RST (0 to 70°C) 0.7V

P0.2

Input low voltage (0 to 70°C) –0.5 0.3V

Input high voltage (0 to 70°C) 0.7V

Output low voltage, ports 1, 3, 0.3, and 0.4

(PWM disabled)

Output low voltage, port 0.2 IOL = 3.2mA

Output high voltage, ports 1, 3, 0.3, and 0.4

(PWM disabled)

Output high voltage, P0.4 (PWM enabled) IOH = –40µA 0.9V

Port 0.0 and 0.1 – Drivers

Output low voltage

Driver, receiver combined:

Capacitance

Logical 0 input current,

ports 1, 3, 0.3, and 0.4 (PWM disabled)

Logical 1 to 0 transition current,

ports 1, 3, 0.3 and 0.4

11

Input leakage current, port 0.0, 0.1 and 0.2 0.45 < VIN < V

Reset pull-down resistor 25 175 kΩ

Pin capacitance Test freq = 1MHz,

Power-down current

5

VPP program voltage (87C749 only) VSS = 0V

Program current (87C749 only) VPP = 13.0V 50 mA

Analog supply voltage

10

Analog operating supply current AVCC = 5.12V 3

Analog input voltage AVSS–0.2 AVCC+0.2 V

Analog input capacitance 15 pF

Sampling time 8t

Conversion time 40t

4

TEST LIMITS

CC

CC

IOL = 1.6mA

2

2

IOH = –60µA, 2.4 V

IOH = –25µA 0.75V

IOH = –10µA 0.9V

CC

CC

IOH = –400µA 2.4 V

CC

IOL = 3mA

(over VCC range)

VIN = 0.45V (0 to 70°C) –50 µA

11

VIN = 2V (0 to 70°C) –650 µA

CC

T

= 25°C

amb

VCC = 2 to 5.5V

VCC = 2 to 6.0V

(83C749)

12.5 13.0 V

VCC = 5V±10%

T

= 21°C to 27°C

amb

AVCC = VCC±0.2V 4.5 5.5 V

83C749/87C749

4

1

MAX UNIT

VCC+0.5 V

CC

VCC+0.5 V

0.45 V

0.45 V

0.4 V

10 pF

±10 µA

10 pF

50 µA

9

CY

CY

mA

V

V

V

V

s

s

1998 Apr 23

12

Page 13

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

83C749/87C749

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

DC ELECTRICAL CHARACTERISTICS (Continued)

T

= 0°C to +70°C, AVCC = 5V ±5, AVSS = 0V

amb

VCC = 5V ± 10%, VSS = 0V

SYMBOL PARAMETER CONDITIONS MIN TYP

Analog Inputs (A/D guaranteed only with quartz window covered.) (Continued)

R Resolution 8 bits

E

RA

OS

e

G

e

M

CTC

C

t

NOTES:

1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and

functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section

of this specification is not implied.

2. Under steady state (non-transient) conditions, I

If I

test conditions.

3. This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static

charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maxima.

4. Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V

noted.

5. Power-down I

6. I

CC

RST = port 0 = V

7. Idle I

port 0 = V

8. Load capacitance for ports = 80pF.

9. The resistor ladder network is not disconnected in the power down or idle modes. Thus, to conserve power, the user may remove AVCC.

10.If the A/D function is not required, or if the A/D function is only needed periodically, AV

the digital circuitry. Contents of ADCON and ADAT are not guaranteed to be valid. If AV

less than 0.5V . Digital inputs on P1.0–P1.4 will not function normally.

11.These parameters do not apply to P1.0–P1.4 if the A/D function is enabled.

Relative accuracy ±1 LSB

Zero scale offset ±1 LSB

Full scale gain error 0.4 %

Channel to channel matching ±1 LSB

Crosstalk 0–100kHz –60 dB

Maximum I

Maximum I

Maximum total I

exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed

OL

is measured with all output pins disconnected; port 0 = VCC; X2, X1 n.c.; RST = VSS.

is measured with all output pins disconnected; X1 driven with t

CC

CC

is measured with all output pins disconnected; X1 driven with t

RST = VSS.

CC;

per port pin: 10mA (NOTE: This is 85°C spec.)

OL

per 8-bit port: 26mA

OL

for all outputs: 67mA

OL

. ICC will be slightly higher if a crystal oscillator is used.

CC

4

TEST LIMITS

must be externally limited as follows:

OL

, t

CLCH

CHCL

CLCH

4

1

MAX UNIT

unless otherwise

SS

= 5ns, VIL = VSS + 0.5V, VIH = VCC – 0.5V; X2 n.c.;

, t

= 5ns, VIL = VSS + 0.5V, VIH = VCC – 0.5V; X2 n.c.;

CHCL

may be removed without affecting the operation of

CC

is removed, the A/D inputs must be lowered to

CC

AC ELECTRICAL CHARACTERISTICS

T

= 0°C to +70°C or –40°C to +85°C, VCC = 5V ±10%, VSS = 0V

amb

SYMBOL PARAMETER MIN MAX MIN MAX UNIT

1/t

CLCL

Oscillator frequency: 3.5 16 MHz

External Clock (Figure 4)

t

CHCX

t

CLCX

t

CLCH

t

CHCL

High time 20 20 ns

Low time 20 20 ns

Rise time 20 20 ns

Fall time 20 20 ns

1998 Apr 23

4, 8

16MHz CLOCK VARIABLE CLOCK

13

Page 14

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

EXPLANATION OF THE AC SYMBOLS

Each timing symbol has five characters. The first character is always

‘t’ (= time). The other characters, depending on their positions,

indicate the name of a signal or the logical status of that signal.

The designations are:

C – Clock

D – Input data

H – Logic level high

VCC –0.5

0.45V

0.2 V

0.2 V

+ 0.9

CC

– 0.1

CC

Figure 4. External Clock Drive

L – Logic level low

Q – Output data

T – Time

V – Valid

X – No longer a valid logic level

Z – Float

t

CLCX

t

CHCL

t

CLCL

t

CLCH

t

CHCX

83C749/87C749

SU00297

–0.5

V

CC

0.45V

0.2 VCC + 0.9

0.2 VCC – 0.1

SU00307

Figure 5. AC Testing Input/Output

CC

CC

CC

7

6

6

MAX ACTIVE I

22

20

18

16

14

12

I

mA

CC

10

8

6

4

TYP ACTIVE I

MAX IDLE I

1998 Apr 23

Maximum I

2

4MHz 8MHz 12MHz 16MHz

FREQ

TYP IDLE I

SU00308

Figure 6. ICC vs. FREQ

values taken at VCC = 5.5V and worst case temperature.

CC

Typical I

Notes 6 and 7 refer to AC Electrical Characteristics.

values taken at VCC = 5.0V and 25°C.

CC

14

CC

7

Page 15

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

PROGRAMMING CONSIDERATIONS

EPROM Characteristics

The 87C749 is programmed by using a modified Quick-Pulse

Programming algorithm similar to that used for devices such as the

87C451 and 87C51. It differs from these devices in that a serial data

stream is used to place the 87C749 in the programming mode.

Figure 7 shows a block diagram of the programming configuration

for the 87C749. Port pin P0.2 is used as the programming voltage

supply input (V

(PGM/) signal. This pin is used for the 25 programming pulses.

Port 3 is used as the address input for the byte to be programmed

and accepts both the high and low components of the eleven bit

address. Multiplexing of these address components is performed

using the ASEL input. The user should drive the ASEL input high

and then drive port 3 with the high order bits of the address. ASEL

should remain high for at least 13 clock cycles. ASEL may then be

driven low which latches the high order bits of the address internally.

The high address should remain on port 3 for at least two clock

cycles after ASEL is driven low. Port 3 may then be driven with the

low byte of the address. The low address will be internally stable 13

clock cycles later. The address will remain stable provided that the

low byte placed on port 3 is held stable and ASEL is kept low. Note:

ASEL needs to be pulsed high only to change the high byte of the

address.

Port 1 is used as a bidirectional data bus during programming and

verify operations. During programming mode, it accepts the byte to

be programmed. During verify mode, it provides the contents of the

EPROM location specified by the address which has been supplied

to Port 3.

The XTAL1 pin is the oscillator input and receives the master system

clock. This clock should be between 1.2 and 6MHz.

The RESET pin is used to accept the serial data stream that places

the 87C749 into various programming modes. This pattern consists

of a 10-bit code with the LSB sent first. Each bit is synchronized to

the clock input, X1.

signal). Port pin P0.1 is used as the program

PP

Programming Operation

Figures 8 and 9 show the timing diagrams for the program/verify

cycle. RESET should initially be held high for at least two machine

cycles. P0.1 (PGM/) and P0.2 (VPP) will be at VOH as a result of the

RESET operation. At this point, these pins function as normal

quasi-bidirectional I/O ports and the programming equipment may

pull these lines low. However, prior to sending the 10-bit code on the

RESET pin, the programming equipment should drive these pins

high (V

for the data stream which places the 87C749 in the programming

mode. Data bits are sampled during the clock high time and thus

should only change during the time that the clock is low. Following

transmission of the last data bit, the RESET pin should be held low.

Next the address information for the location to be programmed is

placed on port 3 and ASEL is used to perform the address

multiplexing, as previously described. At this time, port 1 functions

as an output.

A high voltage V

(This sets Port 1 as an input port). The data to be programmed into

the EPROM array is then placed on Port 1. This is followed by a

series of programming pulses applied to the PGM/ pin (P0.1). These

pulses are created by driving P0.1 low and then high. This pulse is

). The RESET pin may now be used as the serial data input

IH

level is then applied to the VPP input (P0.2).

PP

repeated until a total of 25 programming pulses have occurred. At

the conclusion of the last pulse, the PGM/ signal should remain high.

The V

PP

87C749 in the verify mode. (Port 1 is now used as an output port).

After four machine cycles (48 clock periods), the contents of the

addressed location in the EPROM array will appear on Port 1.

The next programming cycle may now be initiated by placing the

address information at the inputs of the multiplexed buffers, driving

the V

pin to the VPP voltage level, providing the byte to be

PP

programmed to Port1 and issuing the 26 programming pulses on the

PGM/ pin, bringing V

byte.

Programming Modes

The 87C749 has four programming features incorporated within its

EPROM array. These include the USER EPROM for storage of the

application’s code, a 16-byte encryption key array and two security

bits. Programming and verification of these four elements are

selected by a combination of the serial data stream applied to the

RESET pin and the voltage levels applied to port pins P0.1 and

P0.2. The various combinations are shown in Table 3.

Encryption Key Table

The 87C749 includes a 16-byte EPROM array that is programmable

by the end user. The contents of this array can then be used to

encrypt the program memory contents during a program memory

verify operation. When a program memory verify operation is

performed, the contents of the program memory location is

XNOR’ed with one of the bytes in the 16-byte encryption table. The

resulting data pattern is then provided to port 1 as the verify data.

The encryption mechanism can be disable, in essence, by leaving

the bytes in the encryption table in their erased state (FFH) since

the XNOR product of a bit with a logical one will result in the original

bit. The encryption bytes are mapped with the code memory in

16-byte groups. the first byte in code memory will be encrypted with

the first byte in the encryption table; the second byte in code

memory will be encrypted with the second byte in the encryption

table and so forth up to and including the 16the byte. The encryption

repeats in 16-byte groups; the 17th byte in the code memory will be

encrypted with the first byte in the encryption table, and so forth.

Security Bits

Two security bits, security bit 1 and security bit 2, are provided to

limit access to the USER EPROM and encryption key arrays.

Security bit 1 is the program inhibit bit, and once programmed

performs the following functions:

1. Additional programming of the USER EPROM is inhibited.

2. Additional programming of the encryption key is inhibited.

3. Verification of the encryption key is inhibited.

4. Verification of the USER EPROM and the security bit levels may

still be performed.

(If the encryption key array is being used, this security bit should be

programmed by the user to prevent unauthorized parties from

reprogramming the encryption key to all logical zero bits. Such

programming would provide data during a verify cycle that is the

logical complement of the USER EPROM contents).

Security bit 2, the verify inhibit bit, prevents verification of both the

USER EPROM array and the encryption key arrays. The security bit

levels may still be verified.

83C749/87C749

signal may now be driven to the VOH level, placing the

back down to the VC level and verifying the

PP

1998 Apr 23

15

Page 16

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

83C749/87C749

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

Programming and Verifying Security Bits

Security bits are programmed employing the same techniques used

to program the USER EPROM and KEY arrays using serial data

streams and logic levels on port pins indicated in Table 3. When

programming either security bit, it is not necessary to provide

address or data information to the 87C749 on ports 1 and 3.

Table 3. Implementing Program/Verify Modes

OPERATION SERIAL CODE P0.1 (PGM/) P0.2 (VPP)

Program user EPROM 296H –* V

Verify user EPROM 296H V

Program key EPROM 292H –* V

Verify key EPROM 292H V

Program security bit 1 29AH –* V

Program security bit 2 298H –* V

Verify security bits 29AH V

NOTE:

* Pulsed from V

to VIL and returned to VIH.

IH

Verification occurs in a similar manner using the RESET serial

stream shown in Table 3. Port 3 is not required to be driven and the

results of the verify operation will appear on ports 1.6 and 1.7.

Ports 1.7 contains the security bit 1 data and is a logical one if

programmed and a logical zero if not programmed. Likewise, P1.6

contains the security bit 2 data and is a logical one if programmed

and a logical zero if not programmed.

IH

IH

IH

PP

V

IH

PP

V

IH

PP

PP

V

IH

EPROM PROGRAMMING AND VERIFICATION

T

= 21°C to +27°C, VCC = 5V ±10%, VSS = 0V

amb

SYMBOL

1/t

CLCL

t

AVGL

t

GHAX

t

DVGL

t

DVGL

t

GHDX

t

SHGL

t

GHSL

t

GLGH

t

AVQV

t

GHGL

t

SYNL

t

SYNH

t

MASEL

t

MAHLD

t

HASET

t

ADSTA

1

2

Oscillator/clock frequency 1.2 6 MHz

Address setup to P0.1 (PROG–) low 10µs + 24t

Address hold after P0.1 (PROG–) high 48t

Data setup to P0.1 (PROG–) low 38t

Data setup to P0.1 (PROG–) low 38t

Data hold after P0.1 (PROG–) high 36t

VPP setup to P0.1 (PROG–) low 10 µs

VPP hold after P0.1 (PROG–) 10 µs

P0.1 (PROG–) width 90 110 µs

VPP low (VCC) to data valid 48t

P0.1 (PROG–) high to P0.1 (PROG–) low 10 µs

P0.0 (sync pulse) low 4t

P0.0 (sync pulse) high 8t

ASEL high time 13t

Address hold time 2t

Address setup to ASEL 13t

Low address to address stable 13t

NOTES:

1. Address should be valid at least 24t

2. For a pure verify mode, i.e., no program mode in between, t

PARAMETER MIN MAX UNIT

before the rising edge of P0.2 (VPP).

CLCL

AVQV

is 14t

CLCL

CLCL

CLCL

CLCL

CLCL

CLCL

CLCL

CLCL

CLCL

CLCL

CLCL

CLCL

CLCL

maximum.

1998 Apr 23

16

Page 17

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8-bit A/D, PWM, low pin count

87C749

P3.0–P3.7

P0.0/ASEL

P0.1

P0.2

XTAL1

RESET

TEN BIT SERIAL CODE

PROGRAMMING

VOLTAGE

V

PP/VIH

CLK SOURCE

XTAL1

RESET

PULSES

SOURCE

A0–A10

ADDRESS STROBE

MIN 2 MACHINE

CYCLES

RESET

CONTROL

LOGIC

Figure 7. Programming Configuration

BIT 0 BIT 1 BIT 2 BIT 3 BIT 4 BIT 5 BIT 6 BIT 7 BIT 8 BIT 9

V

CC

V

SS

P1.0–P1.7

83C749/87C749

+5V

DATA BUS

SU00309

UNDEFINED

P0.2

UNDEFINED

P0.1

SU00302

Figure 8. Entry into Program/Verify Modes

12.75V

)

P0.2 (V

P0.1 (PGM

P0.0 (ASEL)

PORT 3

PORT 1 INVALID DATA VALID DATA DATA TO BE PROGRAMMED INVALID DATA VALID DATA

PP

5V

t

SHGL

25 PULSES

)

t

t

MASEL

t

HASET

HIGH ADDRESS LOW ADDRESS

t

HAHLD

t

ADSTA

GLGH

98µs MIN 10µs MIN

t

DVGLtGHDX

t

GHGL

5V

t

GHSL

t

AVQV

1998 Apr 23

VERIFY MODE PROGRAM MODE VERIFY MODE

SU00310

Figure 9. Program/Verify Cycle

17

Page 18

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

83C749/87C749

2K/64 OTP/ROM, 5 channel 8 bit A/D, PWM, low pin count

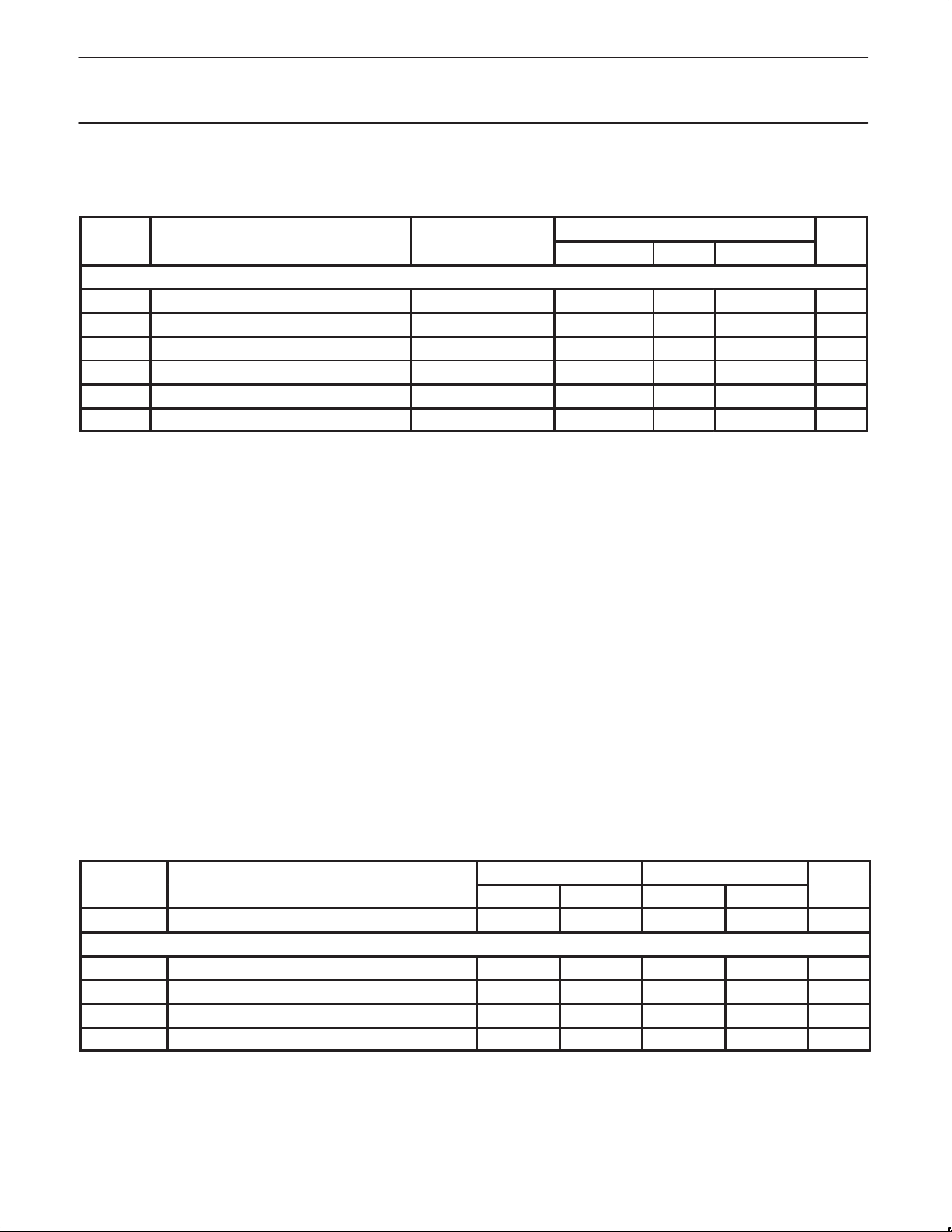

DIP28: plastic dual in-line package; 28 leads (600 mil); long body SOT117-2

1998 Apr 23

18

Page 19

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

83C749/87C749

2K/64 OTP/ROM, 5 channel 8 bit A/D, PWM, low pin count

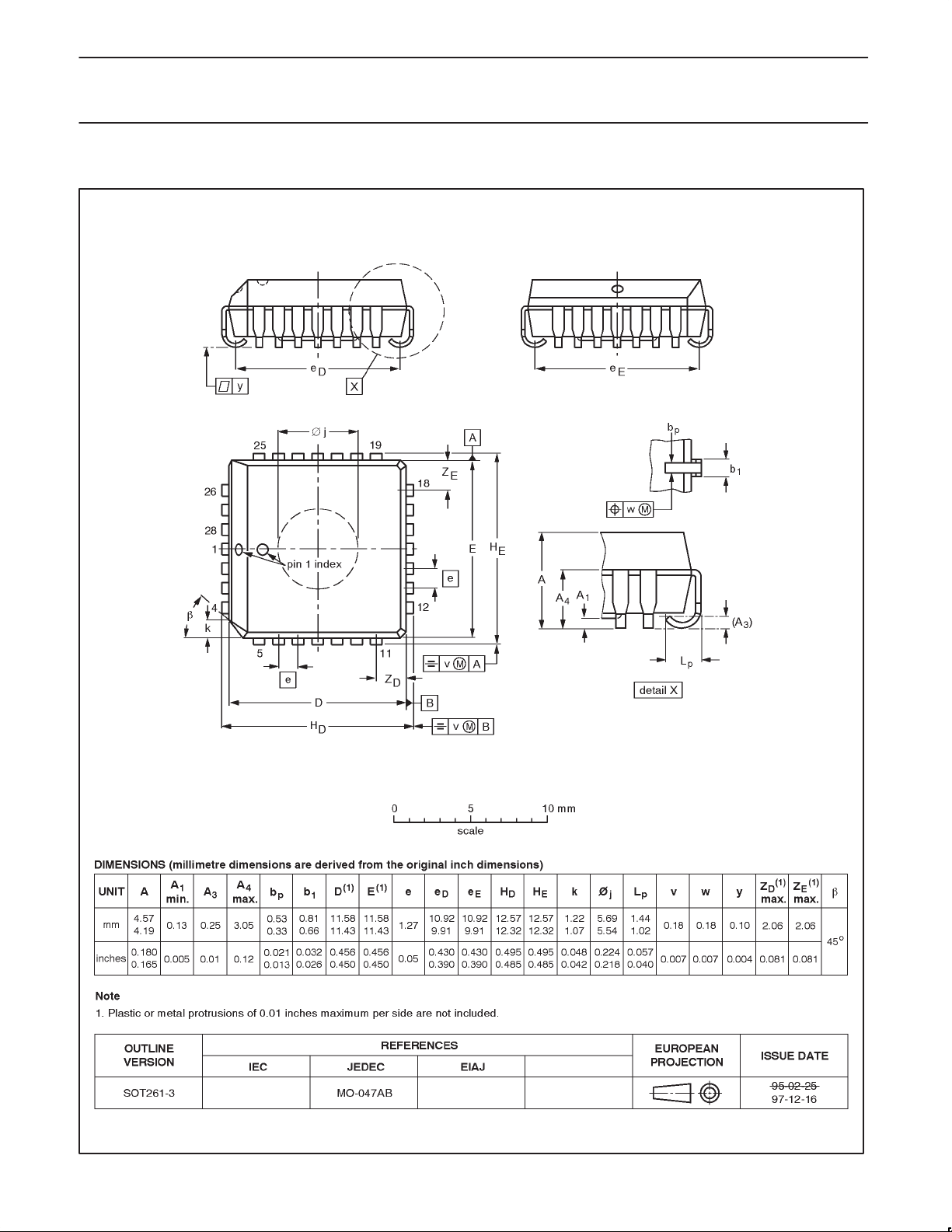

PLCC28: plastic leaded chip carrer; 28 leads; pedestal SOT261-3

1998 Apr 23

19

Page 20

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

83C749/87C749

2K/64 OTP/ROM, 5 channel 8 bit A/D, PWM, low pin count

SSOP28: plastic shrink small outline package; 28 leads; body width 5.3mm SOT341-1

1998 Apr 23

20

Page 21

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8 bit A/D, PWM, low pin count

NOTES

83C749/87C749

1998 Apr 23

21

Page 22

Philips Semiconductors Preliminary specification

80C51 8-bit microcontroller family

2K/64 OTP/ROM, 5 channel 8 bit A/D, PWM, low pin count

Data sheet status

Data sheet

status

Objective

specification

Preliminary

specification

Product

specification

Product

status

Development

Qualification

Production

Definition

This data sheet contains the design target or goal specifications for product development.

Specification may change in any manner without notice.

This data sheet contains preliminary data, and supplementary data will be published at a later date.

Philips Semiconductors reserves the right to make chages at any time without notice in order to

improve design and supply the best possible product.

This data sheet contains final specifications. Philips Semiconductors reserves the right to make

changes at any time without notice in order to improve design and supply the best possible product.

[1]

83C749/87C749

[1] Please consult the most recently issued datasheet before initiating or completing a design.

Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For

detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or

at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended

periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips

Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or

modification.

Disclaimers

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can

reasonably be expected to result in personal injury . Philips Semiconductors customers using or selling these products for use in such applications

do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard

cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no

responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these

products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless

otherwise specified.

Philips Semiconductors

811 East Arques Avenue

P.O. Box 3409

Sunnyvale, California 94088–3409

Telephone 800-234-7381

Copyright Philips Electronics North America Corporation 1998

All rights reserved. Printed in U.S.A.

Date of release: 05-98

Document order number: 9397 750 03856

1998 Apr 23

22

Loading...

Loading...