Datasheet OPA2130UA, OPA2130UA-2K5, OPA4130UA-2K5, OPA4130PA, OPA2130PA Datasheet (Burr Brown)

...Page 1

®

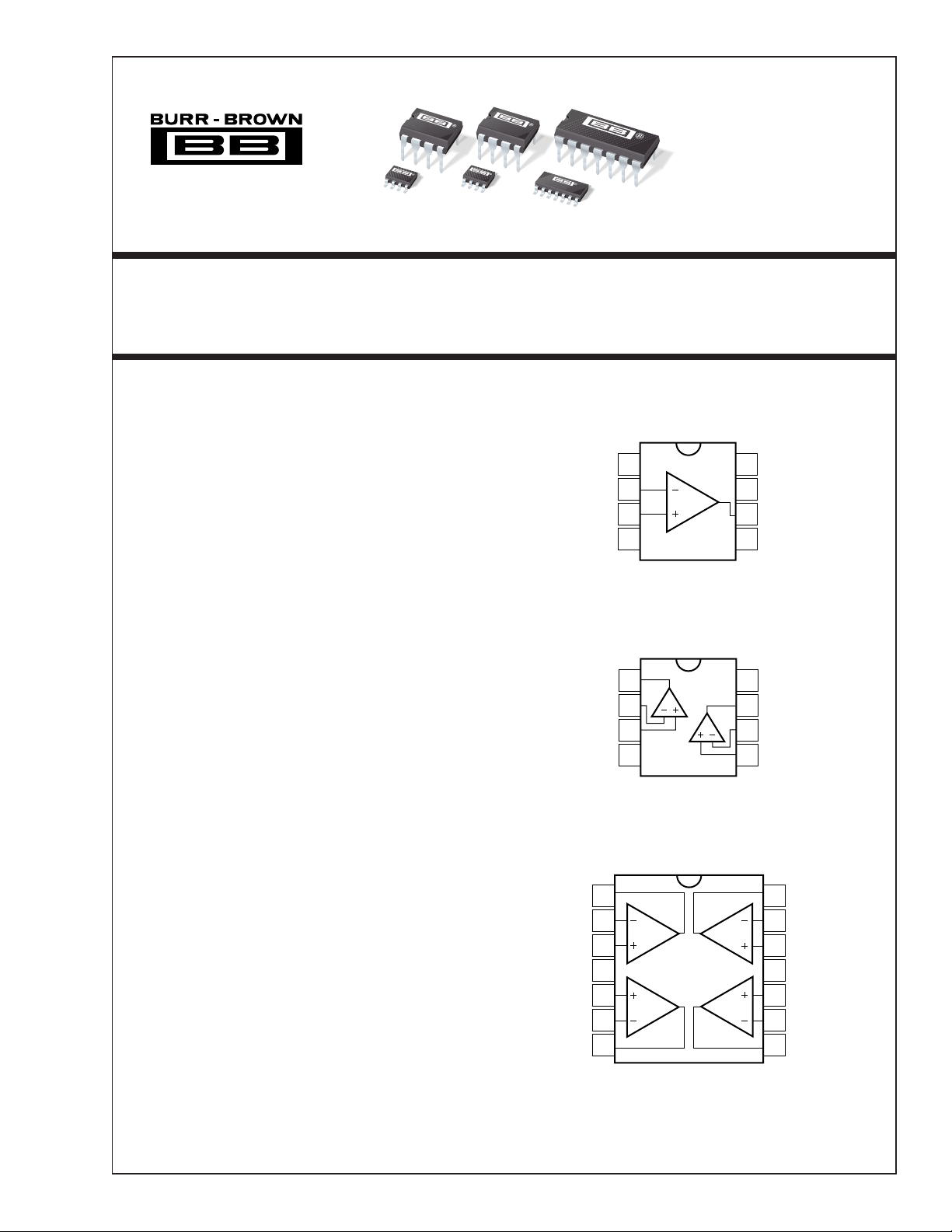

OPA130

OPA2130

OPA4130

OPA130

OPA130

Low Power, Precision

FET-INPUT OPERATIONAL AMPLIFIERS

FEATURES

● LOW QUIESCENT CURRENT: 530µA/amp

● LOW OFFSET VOLTAGE: 1mV max

● HIGH OPEN-LOOP GAIN: 120dB min

● HIGH CMRR: 90 dB min

● FET INPUT: I

● EXCELLENT BANDWIDTH: 1MHz

● WIDE SUPPLY RANGE: ±2.25 to ±18V

● SINGLE, DUAL, AND QUAD VERSIONS

= 20pA max

B

OPA2130

OPA4130

Offset Trim

–In

+In

V–

1

2

3

4

8-Pin DIP, SO-8

OPA130

OPA2130

OPA4130

NC

8

V+

7

Output

6

Offset Trim

5

DESCRIPTION

The OPA130 series of FET-input op amps combine

precision dc performance with low quiescent current.

Single, dual, and quad versions have identical specifications for maximum design flexibility. They are ideal

for general-purpose, portable, and battery operated

applications, especially with high source impedance.

OPA130 op amps are easy to use and free from phase

inversion and overload problems often found in

common FET-input op amps. Input cascode circuitry

provides excellent common-mode rejection and

maintains low input bias current over its wide input

voltage range. OPA130 series op amps are stable in

unity gain and provide excellent dynamic behavior

over a wide range of load conditions, including high

load capacitance. Dual and quad designs feature

completely independent circuitry for lowest crosstalk

and freedom from interaction, even when overdriven

or overloaded.

Single and dual versions are available in 8-pin DIP

and SO-8 surface-mount packages. Quad is

available in 14-pin DIP and SO-14 surface-mount

packages. All are specified for –40°C to +85°C

operation.

Out A

–In A

+In A

V+

+In B

–In B

Out B

Out A

–In A

+In A

V–

OPA2130

1

A

2

3

4

8-Pin DIP, SO-8

1

2

3

4

5

6

7

AD

BC

14-Pin DIP

B

OPA4130

SO-14

V+

8

Out B

7

–In B

6

+In B

5

Out D

14

–In D

13

+In D

12

V–

11

+In C

10

–In C

9

Out C

8

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111

Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

© 1995 Burr-Brown Corporation PDS-1298B Printed in U.S.A. May, 1998

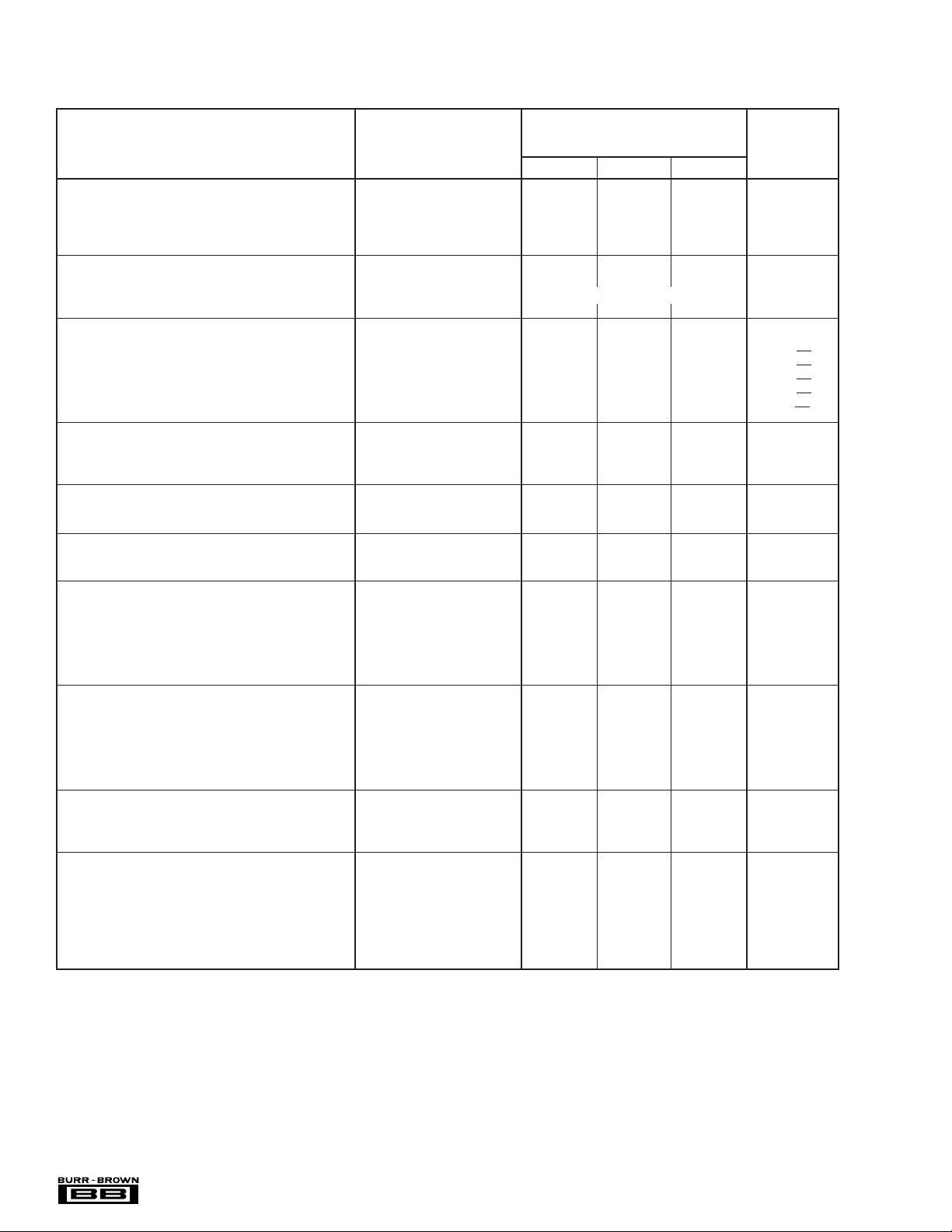

Page 2

SPECIFICATIONS

At TA = +25°C, VS = ±15V, and RL = 10kΩ, unless otherwise noted.

OPA130PA, UA

OPA2130PA, UA

OPA4130PA, UA

PARAMETER CONDITION MIN TYP MAX UNITS

OFFSET VOLTAGE

Input Offset Voltage ±0.2 ±1mV

vs Temperature

vs Power Supply V

Channel Separation (dual and quad) 0.3 µV/V

INPUT BIAS CURRENT

Input Bias Current VCM = 0V +5 ±10 pA

vs Temperature See Typical Curve

Input Offset Current V

NOISE

Input Voltage Noise

Noise Density, f = 10Hz 30 nV/√Hz

Current Noise Density, f = 1kHz 4 fA/√Hz

INPUT VOLTAGE RANGE

Common-Mode Voltage Range, Positive (V+)–2 (V+)–1.5 V

Common-Mode Rejection V

INPUT IMPEDANCE

Differential 1013 || 1 Ω || pF

Common-Mode V

OPEN-LOOP GAIN

Open-loop Voltage Gain V

FREQUENCY RESPONSE

Gain-Bandwidth Product 1 MHz

Slew Rate 2V/µs

Settling Time: 0.1% G = 1, 10V Step, C

Overload Recovery Time G = 1, V

Total Harmonic Distortion + Noise 1kHz, G = 1, V

OUTPUT

Voltage Output, Positive (V+)–2 (V+)–1.5 V

Short-Circuit Current ±18 mA

Capacitive Load Drive (Stable Operation) 10 nF

POWER SUPPLY

Specified Operating Voltage ±15 V

Operating Voltage Range ±2.25 ±18 V

Quiescent Current (per amplifier) I

TEMPERATURE RANGE

Operating Range –40 +85 °C

Storage –40 +125 °C

Thermal Resistance,

8-Pin DIP 100 °C/W

SO-8 Surface-Mount 150 °C/W

14-Pin DIP 80 °C/W

SO-14 Surface-Mount 110 °C/W

NOTES: (1) Guaranteed by wafer test. (2) High-speed test at T

(1)

(2)

Operating Temperature Range ±2 ±10 µV/° C

= ±2.25V to ±18V 2 20 µV/V

S

= 0V ±2 ±20 pA

CM

f = 100Hz 18 nV/√Hz

f = 1kHz 16 nV/√Hz

f = 10kHz 16 nV/√Hz

Negative (V–)+2 (V–)+1.2 V

= –13V to +13V 90 105 dB

CM

= –13V to +13V 1013 || 3 Ω || pF

CM

= –13.8V to +13V 120 135 dB

O

= 2kΩ, VO = –13V to +12V 120 135 dB

R

L

= 100pF 5.5 µs

L

0.01% G = 1, 10V Step, C

= 100pF 7 µs

L

= ±15V 2 µs

IN

= 3.5Vrms 0.0003 %

O

Negative (V–)+1.2 (V–)+1 V

Positive R

Negative R

θ

JA

= 25°C.

J

= 2kΩ (V+)–3 (V+)–2.5 V

L

= 2kΩ (V–)+2 (V–)+1.5 V

L

= 0 ±530 ±650 µA

O

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes

no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change

without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant

any BURR-BROWN product for use in life support devices and/or systems.

®

OPA130, 2130, 4130

2

Page 3

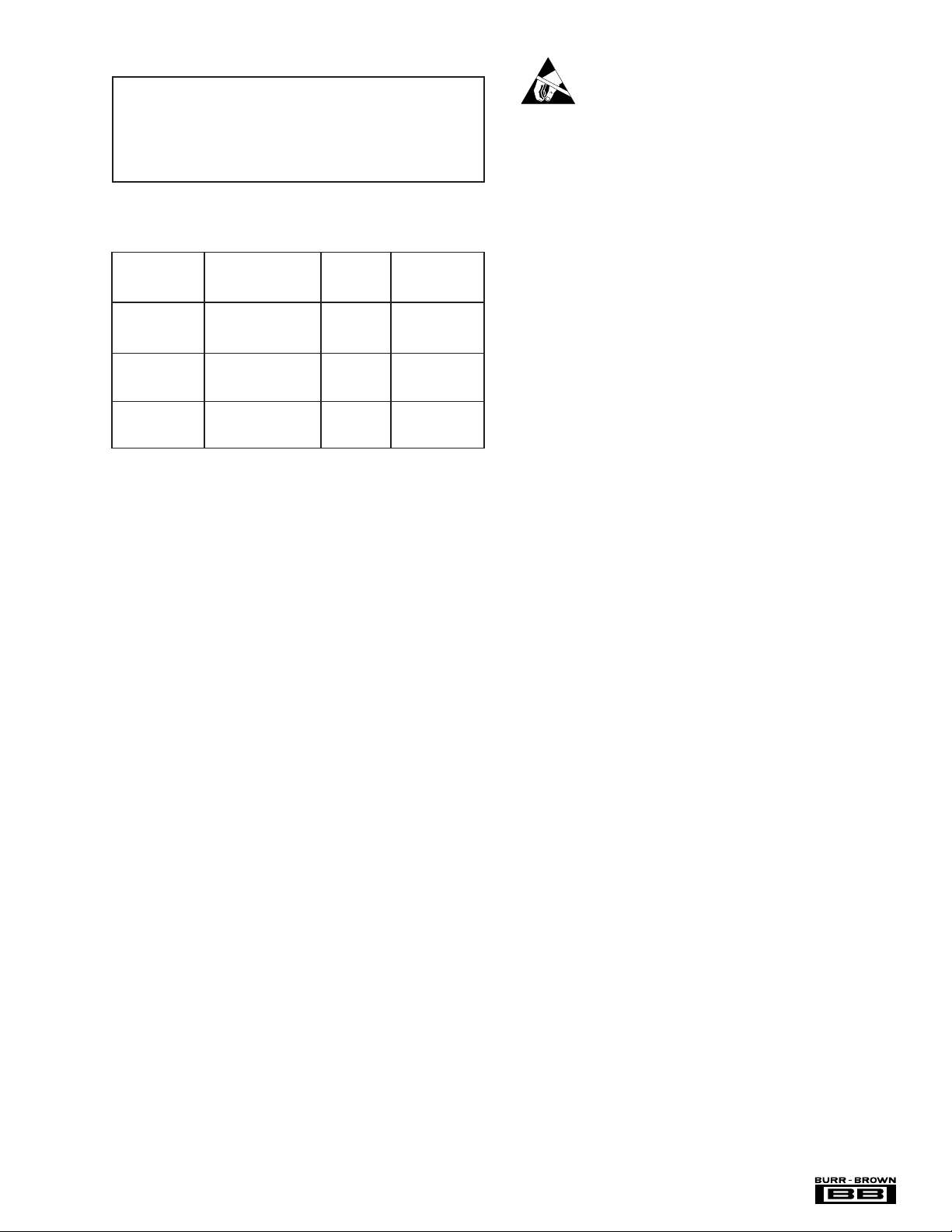

ABSOLUTE MAXIMUM RATINGS

Supply Voltage, V+ to V–....................................................................36V

Input Voltage .................................................... (V–) –0.7V to (V+) +0.7V

Output Short-Circuit

Operating Temperature ................................................. –40°C to +125°C

Storage Temperature ..................................................... –40°C to +125°C

Junction Temperature...................................................................... 150°C

Lead Temperature (soldering, 10s)................................................. 300°C

NOTE: (1) Short-circuit to ground, one amplifier per package.

(1)

.............................................................. Continuous

PACKAGE/ORDERING INFORMATION

PACKAGE

DRAWING TEMPERATURE

(1)

PRODUCT PACKAGE NUMBER

Single

OPA130PA 8-Pin Plastic DIP 006 –40°C to +85°C

OPA130UA SO-8 Surface-Mount 182 –40°C to +85°C

Dual

OPA2130PA 8-Pin Plastic DIP 006 –40°C to +85°C

OPA2130UA SO-8 Surface-Mount 182 –40°C to +85°C

Quad

OPA4130PA 14-Pin Plastic DIP 010 –40°C to +85°C

OPA4130UA SO-14 Surface-Mount 235 –40°C to +85°C

NOTE: (1) For detailed drawing and dimension table, please see end of data

sheet, or Appendix C of Burr-Brown IC Data Book.

RANGE

ELECTROSTATIC

DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown

recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling

and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits

may be more susceptible to damage because very small

parametric changes could cause the device not to meet its

published specifications.

®

3

OPA130, 2130, 4130

Page 4

TYPICAL PERFORMANCE CURVES

At TA = +25°C, VS = ±15V, and RL = 10kΩ, unless otherwise noted.

120

100

80

60

40

Voltage Gain (dB)

20

0

–20

1k

100

10

Voltage Noise (nV/√Hz)

1

OPEN-LOOP GAIN/PHASE vs FREQUENCY

1

10 100 1k 10k 100k 1M 10M

1

CL = 100pF

φ

G

Frequency (Hz)

INPUT VOLTAGE AND CURRENT NOISE

SPECTRAL DENSITY vs FREQUENCY

Voltage Noise

Current Noise

10 100 1k 10k 100k 1M

Frequency (Hz)

0

–45

–90

–135

–180

1k

100

10

1

120

110

100

90

80

70

60

50

Phase Shift (°)

Current Noise (fA/√Hz)

40

PSR, CMR (dB)

30

20

10

0

10 100 1k 10k 100k 1M

160

140

120

100

Channel Separation (dB)

80

10 100 1k 10k 100k

POWER SUPPLY AND COMMON-MODE REJECTION

CHANNEL SEPARATION vs FREQUENCY

Dual and quad devices.

G = 1, all channels.

Quad measured channel

A to D or B to C—other

combinations yield improved

rejection.

vs FREQUENCY

–PSR

CMR

+PSR

Frequency (Hz)

RL = 10kΩ

Frequency (Hz)

INPUT BIAS AND INPUT OFFSET CURRENT

10k

1k

100

10

1

0.1

Input Bias and Input Offset Current (pA)

0.01

–75 –50 –25 0 25 50 75 100 125

VCM = 0V

®

vs TEMPERATURE

I

B

Ambient Temperature (°C)

OPA130, 2130, 4130

INPUT BIAS CURRENT

10

I

OS

5

Input Bias Current (pA)

0

–15 –10 –5 0 5 10 15

vs INPUT COMMON-MODE VOLTAGE

Common-Mode Voltage (V)

4

Page 5

TYPICAL PERFORMANCE CURVES (CONT)

MAXIMUM OUTPUT VOLTAGE

vs FREQUENCY

1M

Frequency (Hz)

10k

100k

30

25

20

15

10

5

0

Output Voltage (Vp-p)

VS = ±2.25V

VS = ±5V

Maximum output voltage

without slew-rate induced

distortion

VS = ±15V

At TA = +25°C, VS = ±15V, and RL = 10kΩ, unless otherwise noted.

140

AOL, CMR, PSR vs TEMPERATURE

130

Open-Loop

Gain

120

, CMR, PSR (dB)

OL

A

110

PSR

CMR

100

–75 –50 –25 0 25 50 75 100 125

Ambient Temperature (°C)

OFFSET VOLTAGE

15

10

5

Percent of Amplifiers (%)

0

–700

PRODUCTION DISTRIBUTION

–600

–500

–400

–300

–200

–100

Offset Voltage (µV)

0

100

200

300

400

500

600

700

QUIESCENT CURRENT AND SHORT-CIRCUIT CURRENT

0.65

0.60

0.55

0.50

0.45

0.40

Quiescent Current Per Amp (mA)

0.35

–75 –50 –25 0 25 50 75 100 125

20

18

16

14

12

10

8

6

4

Percent of Amplifiers (%)

2

0

0.00

0.50

1.00

vs TEMPERATURE

I

Q

–

I

SC

+

I

SC

Temperature (°C)

OFFSET VOLTAGE DRIFT

PRODUCTION DISTRIBUTION

1.50

2.00

2.50

3.00

3.50

4.00

4.50

5.00

Offset Voltage Drift (µV/°C)

5.50

6.00

6.50

7.00

7.50

40

35

30

25

20

Short-Circuit Current (mA)

15

10

8.00

THD + Noise (%)

TOTAL HARMONIC DISTORTION + NOISE

vs FREQUENCY

0.1

0.01

0.001

G = +1

0.0001

100 1k 10k 100k

G = +10

Frequency (Hz)

RL = 10kΩ

R

L

= 2kΩ

®

5

OPA130, 2130, 4130

Page 6

TYPICAL PERFORMANCE CURVES (CONT)

SMALL-SIGNAL STEP RESPONSE

G = 1, C

L

= 1000pF

50mV/div

5µs/div

At TA = +25°C, VS = ±15V, and RL = 10kΩ, unless otherwise noted.

50mV/div

SMALL-SIGNAL STEP RESPONSE

LARGE-SIGNAL STEP RESPONSE

G =1, C

500ns/div

G = 1, C

= 100pF

L

= 100pF

L

100

SETTLING TIME vs GAIN

0.01%

5V/div

5µs/div

OUTPUT VOLTAGE SWING vs OUTPUT CURRENT

15

14

13

12

11

10

–10

–11

–12

Output Voltage Swing (V)

–13

–14

–15

0 ±5 ±10 ±15 ±20

+125°C

+125°C

Output Current (mA)

+25°C

+25°C

–55°C

+85°C

–55°C

10

Settling Time (µs)

1

±1 ±10 ±100

Gain (V/V)

SMALL-SIGNAL OVERSHOOT

80

70

60

50

40

30

Overshoot (%)

20

10

0

10pF 100pF 1nF 10nF 100nF

vs LOAD CAPACITANCE

Load Capacitance (F)

0.1%

G = +1

G = –1

G = ±5

®

OPA130, 2130, 4130

6

Page 7

APPLICATIONS INFORMATION

V+

V–

100kΩ

OPA130 single op amp only.

Use offset adjust pins only to null

offset voltage of op amp—see text.

Trim Range: ±5mV typ

OPA130

6

7

5

4

3

2

1

10nF

10nF

OPA130 series op amps are unity-gain stable and suitable

for a wide range of general-purpose applications. Power

supply pins should be bypassed with 10nF ceramic capacitors or larger.

OPA130 op amps are free from unexpected output phasereversal common with FET op amps. Many FET-input op

amps exhibit phase-reversal of the output when the input

common-mode voltage range is exceeded. This can occur in

voltage-follower circuits, causing serious problems in

control loop applications. OPA130 series op amps are free

from this undesirable behavior. All circuitry is completely

independent in dual and quad versions, assuring normal

behavior when one amplifier in a package is overdriven or

short-circuited.

FIGURE 1. OPA130 Offset Voltage Trim Circuit.

OPERATING VOLTAGE

OPA130 series op amps operate with power supplies from

±2.25V to ±18V with excellent performance. Although

specifications are production tested with ±15V supplies,

most behavior remains unchanged throughout the full

operating voltage range. Parameters which vary significantly with operating voltage are shown in the typical

performance curves.

OFFSET VOLTAGE TRIM

Offset voltage of OPA130 series amplifiers is laser trimmed

and usually requires no user adjustment. The OPA130

(single op amp version) provides offset voltage trim connections on pins 1 and 5. Offset voltage can be adjusted by

connecting a potentiometer as shown in Figure 1. This

adjustment should be used only to null the offset of the op

amp, not to adjust system offset or offset produced by the

signal source. Nulling offset that is not produced by the

amplifier will change the offset voltage drift behavior of

the op amp.

INPUT BIAS CURRENT

The input bias current is approximately 5pA at room temperature and increases with temperature as shown in the

typical performance curve “Input Bias Current vs Temperature.”

Input stage cascode circuitry assures that the input bias

current remains virtually unchanged throughout the full

input common-mode range of the OPA130. See the typical

performance curve “Input Bias Current vs Common-Mode

Voltage.”

®

7

OPA130, 2130, 4130

Loading...

Loading...