Datasheet OP193FS-REEL, OP193ES, OP293ES, OP493FS, OP493ES-REEL Datasheet (Analog Devices)

...Page 1

Precision, Micropower

NC = NO CONNECT

1

2

3

4

8

7

6

5

OUT A

V+

NULL

NC

NULL

–IN A

+IN A

V–

OP193

OP193

OUT A

V+

NULL

NCNULL

–IN A

+IN A

V–

14

13

12

11

10

9

8

1

2

3

4

5

6

7

OP493

OUT A

–IN A

+IN A

V+

+IN B

–IN B

OUT B

OUT D

–IN D

+IN D

V–

+IN C

–IN C

OUT C

OP493

OUT D

–IN D

+IN D

V–

+IN C

–IN C

OUT C

NC

OUT A

–IN A

+IN A

V+

+IN B

–IN B

OUT B

NC

NC = NO CONNECT

a

FEATURES

Operates from +1.7 V to ⴞ18 V

Low Supply Current: 15 A/Amplifier

Low Offset Voltage: 75 V

Outputs Sink and Source: ⴞ8 mA

No Phase Reversal

Single- or Dual-Supply Operation

High Open-Loop Gain: 600 V/mV

Unity-Gain Stable

APPLICATIONS

Digital Scales

Strain Gages

Portable Medical Equipment

Battery-Powered Instrumentation

Temperature Transducer Amplifier

GENERAL DESCRIPTION

The OP193 family of single-supply operational amplifiers features a combination of high precision, low supply current and

the ability to operate at low voltages. For high performance in

single-supply systems the input and output ranges include

ground, and the outputs swing from the negative rail to within

600 mV of the positive supply. For low voltage operation the

OP193 family can operate down to 1.7 volts or ±0.85 volts.

The combination of high accuracy and low power operation

make the OP193 family useful for battery-powered equipment.

Its low current drain and low voltage operation allow it to

continue performing long after other amplifiers have ceased

functioning either because of battery drain or headroom.

The OP193 family is specified for single +2 volt through dual

±15 volt operation over the HOT (–40°C to +125°C) temperature

range. They are available in plastic DIPs, plus SOIC surfacemount packages.

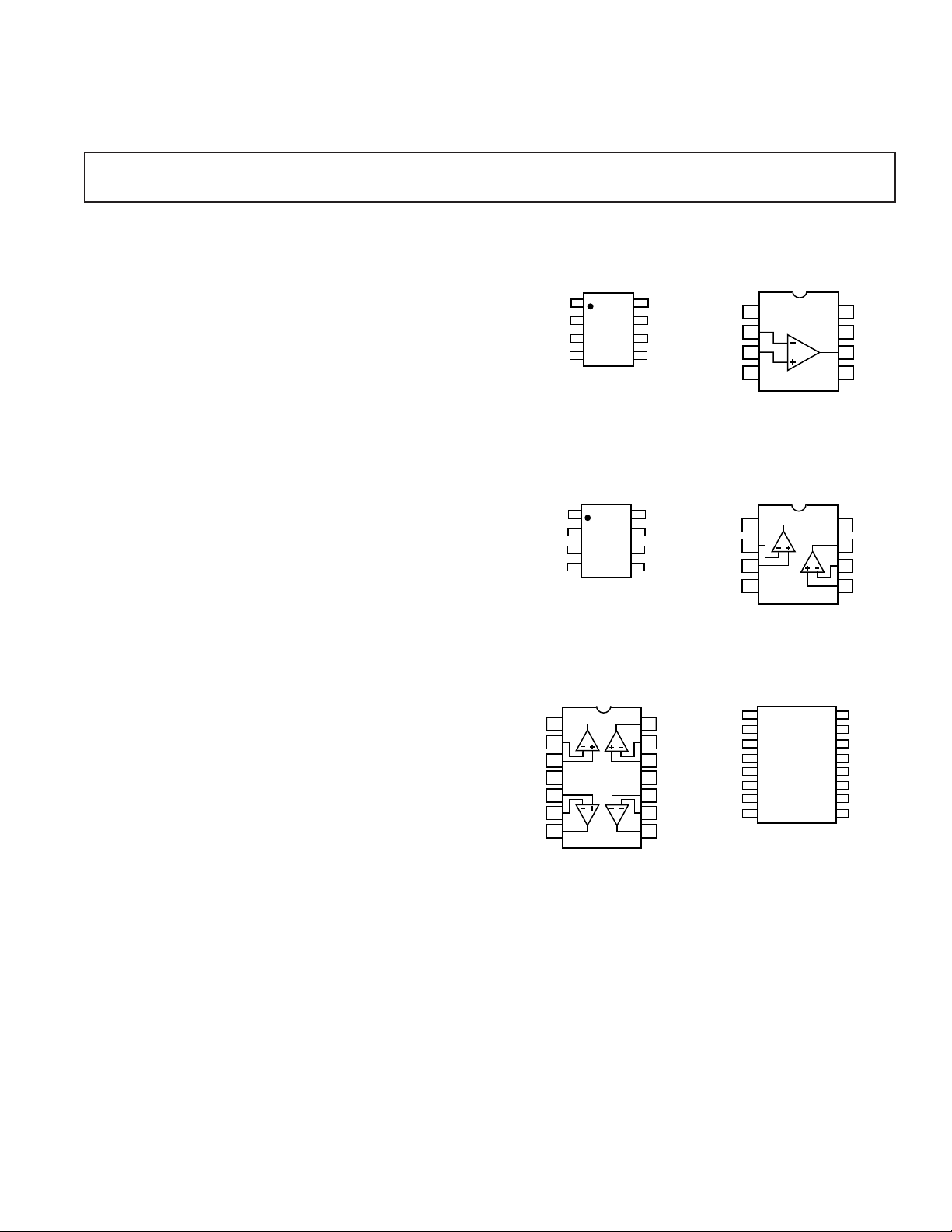

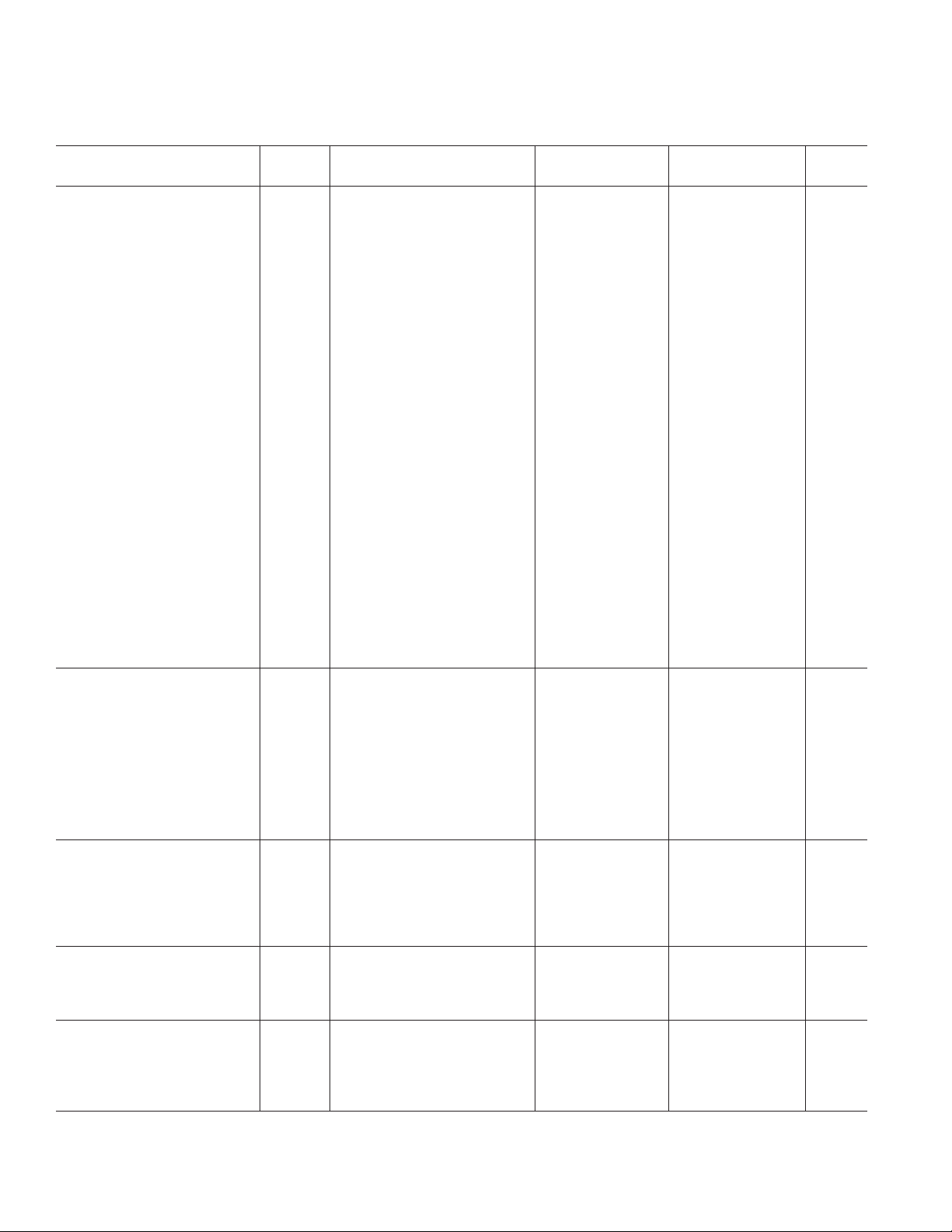

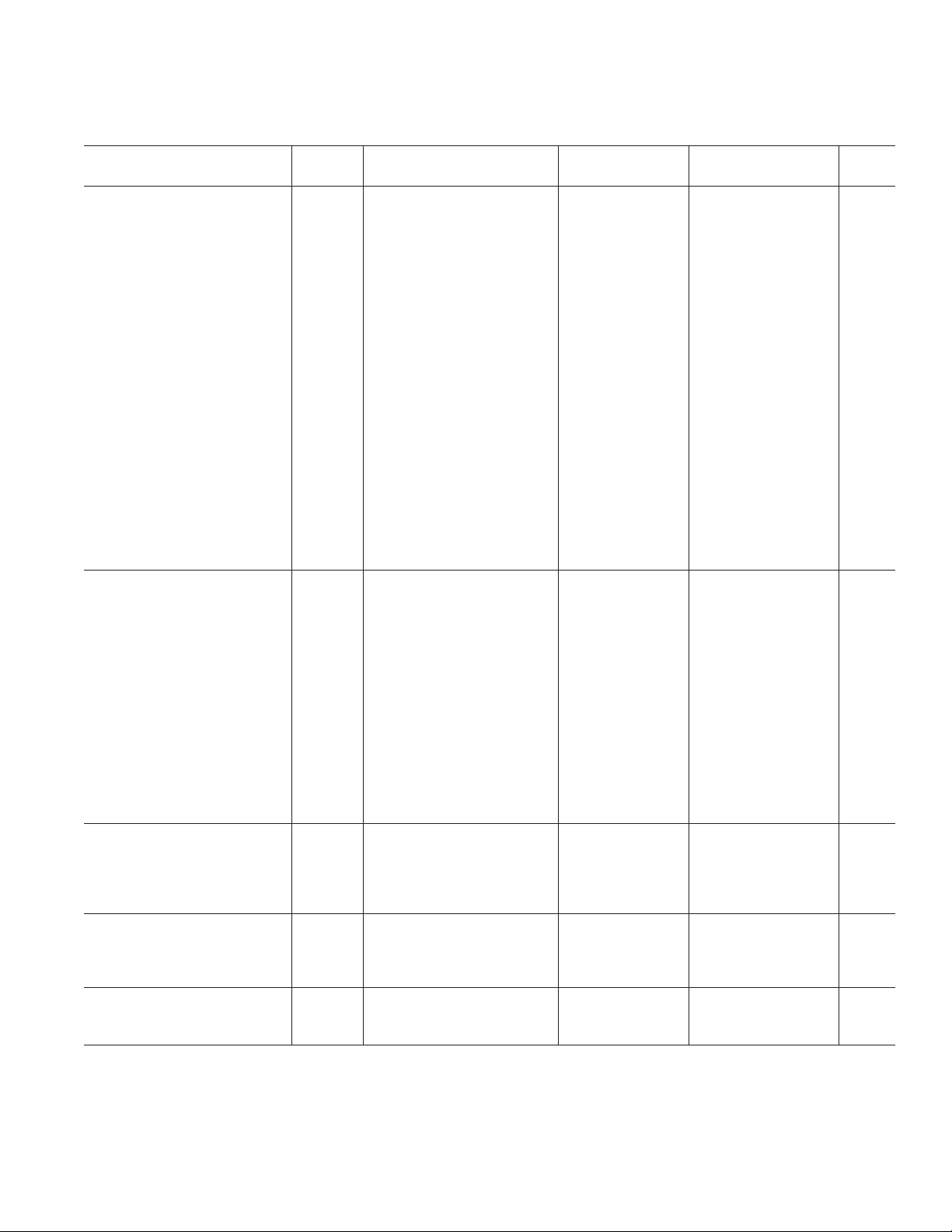

Operational Amplifiers

OP193/OP293/OP493

PIN CONFIGURATIONS

8-Lead SO

(S Suffix)

8-Lead SO

(S Suffix)

OUT A

–IN A

OP293

+IN A

V–

14-Lead Epoxy DIP

(P Suffix)

V+

OUT B

–IN B

+IN B

*

8-Lead Epoxy DIP

(P Suffix)

8-Lead Epoxy DIP

(P Suffix)

1

OUT A

–IN A

+IN A

V–

OP293

2

3

4

16-Lead Wide Body SOL

(S Suffix)

8

7

6

5

V+

OUT B

–IN B

+IN B

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

Page 2

OP193/OP293/OP493–SPECIFICATIONS

ELECTRICAL SPECIFICATIONS

(@ VS = ⴞ15.0 V, TA = 25ⴗC unless otherwise noted)

“E” Grade “F” Grade

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage V

OS

OP193 75 150 µV

OP193, –40°C ≤ T

≤ +125°C 175 250 µV

A

OP293 100 250 µV

OP293, –40°C ≤ T

≤ +125°C 200 350 µV

A

OP493 125 275 µV

OP493, –40°C ≤ T

Input Bias Current I

B

V

= 0 V,

CM

–40°C ≤ T

Input Offset Current I

OS

VCM = 0 V,

–40°C ≤ T

Input Voltage Range V

CM

Common-Mode Rejection CMRR –14.9 ≤ V

≤ +125°C1520nA

A

≤ +125°C24nA

A

CM

≤ +125°C 225 375 µV

A

–14.9 +13.5 –14.9 +13.5 V

≤ +14 V 100 116 97 116 dB

–14.9 ≤ VCM ≤ +14 V,

Large Signal Voltage Gain A

VO

–40°C ≤ T

RL = 100 kΩ,

–10 V ≤ V

≤ +125°C9794dB

A

≤ +10 V 500 500 V/mV

OUT

–40°C ≤ TA ≤ +85°C 300 300 V/mV

Large Signal Voltage Gain A

VO

–40°C ≤ T

RL = 10 kΩ,

–10 V ≤ V

≤ +125°C 300 300 V/mV

A

≤ +10 V 350 350 V/mV

OUT

–40°C ≤ TA ≤ +85°C 200 200 V/mV

Large Signal Voltage Gain A

VO

–40°C ≤ T

RL = 2 kΩ,

–10 V ≤ V

≤ +125°C 150 150 V/mV

A

≤ +10 V 200 200 V/mV

OUT

–40°C ≤ TA ≤ +85°C 125 125 V/mV

–40°C ≤ TA ≤ +125°C 100 100 V/mV

Long Term Offset Voltage V

OS

Note 1 150 300 µV

Offset Voltage Drift ∆VOS/∆T Note 2 0.2 1.75 µV/°C

OUTPUT CHARACTERISTICS

Output Voltage Swing High V

OH

IL = 1 mA 14.1 14.2 14.1 14.2 V

I

= 1 mA,

L

–40°C ≤ TA ≤ +125°C 14.0 14.0 V

I

= 5 mA 13.9 14.1 13.9 14.1 V

Output Voltage Swing Low V

OL

L

IL = –1 mA –14.7 –14.6 –14.7 –14.6 V

I

= –1 mA,

L

–40°C ≤ TA ≤ +125°C –14.4 –14.4 V

I

= –5 mA +14.2 –14.1 +14.2 –14.1 V

Short Circuit Current I

SC

L

±25 ±25 mA

POWER SUPPLY

Power Supply Rejection Ratio PSRR V

= ±1.5 V to ± 18 V 100 120 97 120 dB

S

V

= ±1.5 V to ± 18 V,

S

–40°C ≤ TA ≤ +125°C9794dB

Supply Current/Amplifier I

SY

–40°C ≤ TA ≤ +125°C, RL = ∞

V

= 0 V, VS = ±18 V 30 30 µA

OUT

NOISE PERFORMANCE

Voltage Noise Density e

Current Noise Density i

n

n

f = 1 kHz 65 65 nV/√Hz

f = 1 kHz 0.05 0.05 pA/√Hz

Voltage Noise en p-p 0.1 Hz to 10 Hz 3 3 µV p-p

DYNAMIC PERFORMANCE

Slew Rate SR R

= 2 kΩ 15 15 V/ms

L

Gain Bandwidth Product GBP 35 35 kHz

Channel Separation V

= 10 V p-p,

OUT

RL = 2 kΩ, f = 1 kHz 120 120 dB

NOTES

1

Long term offset voltage is guaranteed by a 1000 hour life test performed on three independent lots at 125 °C, with an LTPD of 1.3.

2

Offset voltage drift is the average of the –40°C to +25°C delta and the +25°C to +125°C delta.

Specifications subject to change without notice.

–2–

REV. B

Page 3

OP193/OP293/OP493

ELECTRICAL SPECIFICATIONS

(@ VS = 5.0 V, VCM = 0.1 V, TA = 25ⴗC unless otherwise noted)

“E” Grade “F” Grade

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage V

OS

OP193 75 150 µV

OP193, –40°C ≤ T

≤ +125°C 175 250 µV

A

OP293 100 250 µV

OP293, –40°C ≤ T

≤ +125°C 200 350 µV

A

OP493 125 275 µV

OP493, –40°C ≤ T

Input Bias Current I

Input Offset Current I

Input Voltage Range V

B

OS

CM

–40°C ≤ TA ≤ +125°C1520nA

–40°C ≤ TA ≤ +125°C24nA

Common-Mode Rejection CMRR 0.1 ≤ V

≤ 4 V 100 116 96 116 dB

CM

≤ +125°C 225 375 µV

A

0404V

0.1 ≤ VCM ≤ 4 V,

Large Signal Voltage Gain A

VO

–40°C ≤ T

RL = 100 kΩ,

0.03 ≤ V

≤ +125°C92 92 dB

A

≤ 4.0 V 200 200 V/mV

OUT

–40°C ≤ TA ≤ +85°C 125 125 V/mV

Large Signal Voltage Gain A

VO

–40°C ≤ T

RL = 10 kΩ,

0.03 ≤ V

≤ +125°C 130 130 V/mV

A

≤ 4.0 V 75 75 V/mV

OUT

–40°C ≤ TA ≤ +85°C 50 50 V/mV

Long Term Offset Voltage V

OS

–40°C ≤ T

Note 1 150 300 µV

≤ +125°C 70 70 V/mV

A

Offset Voltage Drift ∆VOS/∆T Note 2 0.2 1.25 µV/°C

OUTPUT CHARACTERISTICS

Output Voltage Swing High V

OH

IL = 100 µA 4.4 4.4 V

I

= 1 mA 4.1 4.4 4.1 4.4 V

L

IL = 1 mA,

–40°C ≤ T

≤ +125°C 4.0 4.0 V

A

IL = 5 mA 4.0 4.4 4.0 4.4 V

Output Voltage Swing Low V

OL

IL = –100 µA 140 160 140 160 mV

IL = –100 µA,

–40°C ≤ T

≤ +125°C 220 220 mV

A

No Load 5 5 mV

I

= –1 mA 280 400 280 400 mV

L

IL = –1 mA,

–40°C ≤ T

≤ +125°C 500 500 mV

A

IL = –5 mA 700 900 700 900 mV

Short Circuit Current I

SC

±8 ±8mA

POWER SUPPLY

Power Supply Rejection Ratio PSRR V

= ±1.7 V to ± 6.0 V 100 120 97 120 dB

S

VS = ±1.5 V to ± 18 V,

Supply Current/Amplifier I

–40°C ≤ T

SY

VCM = 2.5 V, RL = ∞ 14.5 14.5 µA

≤ +125°C94 90 dB

A

NOISE PERFORMANCE

Voltage Noise Density e

Current Noise Density i

n

n

f = 1 kHz 65 65 nV/√Hz

f = 1 kHz 0.05 0.05 pA/√Hz

Voltage Noise en p-p 0.1 Hz to 10 Hz 3 3 µV p-p

DYNAMIC PERFORMANCE

Slew Rate SR R

= 2 kΩ 12 12 V/ms

L

Gain Bandwidth Product GBP 35 35 kHz

NOTES

1

Long term offset voltage is guaranteed by a 1000 hour life test performed on three independent lots at 125 °C, with an LTPD of 1.3.

2

Offset voltage drift is the average of the –40°C to +25°C delta and the +25°C to +125°C delta.

Specifications subject to change without notice.

REV. B

–3–

Page 4

OP193/OP293/OP493

ELECTRICAL SPECIFICATIONS

(@ VS = 3.0 V, VCM = 0.1 V, TA = 25ⴗC unless otherwise noted)

“E” Grade “F” Grade

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage V

OS

OP193 75 150 µV

OP193, –40°C ≤ T

≤ +125°C 175 250 µV

A

OP293 100 250 µV

OP293, –40°C ≤ T

≤ +125°C 200 350 µV

A

OP493 125 275 µV

OP493, –40°C ≤ T

Input Bias Current I

Input Offset Current I

Input Voltage Range V

B

OS

CM

–40°C ≤ TA ≤ +125°C1520nA

–40°C ≤ TA ≤ +125°C24nA

Common-Mode Rejection CMRR 0.1 ≤ V

≤ 2 V 97 116 94 116 dB

CM

≤ +125°C 225 375 µV

A

0202V

0.1 ≤ VCM ≤ 2 V,

Large Signal Voltage Gain A

VO

–40°C ≤ T

RL = 100 kΩ, 0.03 ≤ V

–40°C ≤ T

≤ +125°C9087dB

A

≤ +85°C 75 75 V/mV

A

≤ 2 V 100 100 V/mV

OUT

–40°C ≤ TA ≤ +125°C 100 100 V/mV

Long Term Offset Voltage V

OS

Note 1 150 300 µV

Offset Voltage Drift ∆VOS/∆T Note 2 0.2 1.25 µV/°C

OUTPUT CHARACTERISTICS

Output Voltage Swing High V

OH

IL = 1 mA 2.1 2.14 2.1 2.14 V

IL = 1 mA,

–40°C ≤ T

≤ +125°C 1.9 1.9 V

A

IL = 5 mA 1.9 2.1 1.9 2.1 V

Output Voltage Swing Low V

OL

IL = –1 mA 280 400 280 400 mV

IL = –1 mA

–40°C ≤ T

≤ +125°C 500 500 mV

A

IL = –5 mA 700 900 700 900 mV

Short Circuit Current I

SC

±8 ±8mA

POWER SUPPLY

Power Supply Rejection Ratio PSRR V

= +1.7 V to +6 V, 100 97

S

–40°C ≤ TA ≤ +125°C9490dB

Supply Current/Amplifier I

SY

VCM = 1.5 V, RL = ∞ 14.5 22 14.5 22 µA

–40°C ≤ TA ≤ +125°C2222µA

Supply Voltage Range V

S

+2 ±18 +2 ± 18 V

NOISE PERFORMANCE

Voltage Noise Density e

Current Noise Density i

n

n

f = 1 kHz 65 65 nV/√Hz

f = 1 kHz 0.05 0.05 pA/√Hz

Voltage Noise en p-p 0.1 Hz to 10 Hz 3 3 µV p-p

DYNAMIC PERFORMANCE

Slew Rate SR R

= 2 kΩ 10 10 V/ms

L

Gain Bandwidth Product GBP 25 25 kHz

Channel Separation V

= 10 V p-p,

OUT

RL = 2 kΩ, f = 1 kHz 120 120 dB

NOTES

1

Long term offset voltage is guaranteed by a 1000 hour life test performed on three independent lots at 125 °C, with an LTPD of 1.3.

2

Offset voltage drift is the average of the –40°C to +25°C delta and the +25°C to +125°C delta.

Specifications subject to change without notice.

–4–

REV. B

Page 5

OP193/OP293/OP493

ELECTRICAL SPECIFICATIONS

(@ VS = 2.0 V, VCM = 0.1 V, TA = 25ⴗC unless otherwise noted)

“E” Grade “F” Grade

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage V

OS

OP193 75 150 µV

OP193, –40°C ≤ T

≤ +125°C 175 250 µV

A

OP293 100 250 µV

OP293, –40°C ≤ T

≤ +125°C 175 350 µV

A

OP493 125 275 µV

Input Bias Current I

Input Offset Current I

Input Voltage Range V

Large Signal Voltage Gain A

B

OS

CM

VO

OP493, –40°C ≤ T

–40°C ≤ TA ≤ +125°C1520nA

–40°C ≤ TA ≤ +125°C24nA

RL = 100 kΩ, 0.03 ≤ V

≤ +125°C 225 375 µV

A

0101V

≤ 1 V 60 60 V/mV

OUT

–40°C ≤ TA ≤ +125°C 70 70 V/mV

Long Term Offset Voltage V

OS

Note 1 150 300 µV

POWER SUPPLY

Power Supply Rejection Ratio PSRR V

Supply Current/Amplifier I

Supply Voltage Range V

SY

S

= 1.7 V to 6 V, 100 97

S

–40°C ≤ T

≤ +125°C9490dB

A

VCM = 1.0 V, RL = ∞ 13.2 20 13.2 20 µA

–40°C ≤ T

≤ +125°C2525µA

A

+2 ±18 +2 ± 18 V

NOISE PERFORMANCE

Voltage Noise Density e

Current Noise Density i

n

n

f = 1 kHz 65 65 nV/√Hz

f = 1 kHz 0.05 0.05 pA/√Hz

Voltage Noise en p-p 0.1 Hz to 10 Hz 3 3 µV p-p

DYNAMIC PERFORMANCE

Slew Rate SR R

= 2 kΩ 10 10 V/ms

L

Gain Bandwidth Product GBP 25 25 kHz

Specifications subject to change without notice.

REV. B

–5–

Page 6

OP193/OP293/OP493

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 18 V

Input Voltage

Differential Input Voltage

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 18 V

2

. . . . . . . . . . . . . . . . . . . . . . . ± 18 V

1

Output Short-Circuit Duration to Gnd . . . . . . . . . . Indefinite

Storage Temperature Range

P, S Package . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Operating Temperature Range

OP193/OP293/OP493E, F . . . . . . . . . . . . –40°C to +125°C

Junction Temperature Range

P, S Package . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering, 60 sec) . . . . . . . . 300°C

Package Type θ

3

JA

θ

JC

Unit

8-Pin Plastic DIP (P) 103 43 °C/W

8-Pin SOIC (S) 158 43 °C/W

14-Pin Plastic DIP (P) 83 39 °C/W

16-Pin SOL (S) 92 27 °C/W

NOTES

1

Absolute maximum ratings apply to both DICE and packaged parts, unless

otherwise noted.

2

For supply voltages less than ± 18 V, the input voltage is limited to the supply

voltage.

3

θJA is specified for the worst case conditions; i.e., θJA is specified for device in socket

for PDIP, and θ

is specified for device soldered in circuit board for SOIC package.

JA

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

OP193ES* –40°C to +125°C 8-Pin SOIC SO-8

OP193ES-REEL* –40°C to +125°C 8-Pin SOIC SO-8

OP193ES-REEL7* –40°C to +125°C 8-Pin SOIC SO-8

OP193FP* –40°C to +125°C 8-Pin Plastic DIP N-8

OP193FS –40°C to +125°C 8-Pin SOIC SO-8

OP193FS-REEL –40°C to +125°C 8-Pin SOIC SO-8

OP193FS-REEL7 –40°C to +125°C 8-Pin SOIC SO-8

OP293ES –40°C to +125°C 8-Pin SOIC SO-8

OP293ES-REEL –40°C to +125°C 8-Pin SOIC SO-8

OP293ES-REEL7 –40°C to +125°C 8-Pin SOIC SO-8

OP293FP* –40°C to +125°C 8-Pin Plastic DIP N-8

OP293FS –40°C to +125°C 8-Pin SOIC SO-8

OP293FS-REEL –40°C to +125°C 8-Pin SOIC SO-8

OP293FS-REEL7 –40°C to +125°C 8-Pin SOIC SO-8

OP493ES* –40°C to +125°C 16-Pin SOL SOL-16

OP493ES-REEL* –40°C to +125°C 16-Pin SOL SOL-16

OP493FP* –40°C to +125°C 14-Pin Plastic DIP N-14

OP493FS* –40°C to +125°C 16-Pin SOL SOL-16

OP493FS-REEL* –40°C to +125°C 16-Pin SOL SOL-16

*Not for new design, obsolete April 2002.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the OP193/OP293/OP493 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions

are recommended to avoid performance degradation or loss of functionality.

–6–

REV. B

Page 7

Typical Performance Characteristics–OP193/OP293/OP493

200

160

120

80

40

NUMBER OF AMPLIFIERS

0

OFFSET – V

VS ⴝ ±15V

ⴝ 25°C

T

A

450 ⴛ PDIPS

45

756030150–15–30–45–60–75

TPC 1. OP193 Offset Distribution,

= ±15 V

V

S

150

120

90

60

30

NUMBER OF AMPLIFIERS

VS ⴝ ⴞ15V

–40°C ⱕ T

450 ⴛ PDIPS

ⱕ +125°C

A

200

160

120

80

40

NUMBER OF AMPLIFIERS

0

–75

–45 6045–30 0 30

OFFSET – V

VS ⴝ 3V

V

ⴝ 0.1V

CM

T

ⴝ 25°C

A

450 ⴛ PDIPS

15–15–60

75

TPC 2. OP193 Offset Distribution,

= +3 V

V

S

1

VS ⫽ 5V

INPUT BIAS CURRENT – nA

0

–1

–2

–3

–40°C

+125°C

+25°C

150

120

90

60

30

NUMBER OF AMPLIFIERS

0

0.2 0.80.4

0

VS ⴝ 3V

V

–40°C ⱕ T

450 ⴛ PDIPS

TCV

OS

TPC 3. OP193 TCV

= +3 V

V

S

120

100

PSRR – dB

80

60

40

20

–PSRR

+PSRR

ⴝ 0.1V

CM

ⱕ +125°C

A

0.6

– VⲐ° C

Distribution,

OS

5V ⱕ VS ⱕ 30V

T

ⴝ 25°C

A

1.0

0

0

0.2 0.80.4

TCVOS – VⲐ° C

TPC 4. OP193 TCV

= ±15 V

V

S

120

100

80

60

CMRR – dB

40

20

0

10 100 1k 10k

VS ⴝ +5V

FREQUENCY – Hz

OS

VS ⴝ ±15V

0.6

Distribution,

TA ⴝ 25°C

1.0

–4

0

1 234

COMMON-MODE VOLTAGE – V

TPC 5. Input Bias Current vs.

Common-Mode Voltage

25

20

15

10

SLEW RATE – V/ms

+SR ⴝ –SR

ⴝ ±15V

V

S

+SR ⴝ –SR

ⴝ +5V

V

S

5

0

–50

0 25 50 100

–25 125

TEMPERATURE – °C

75

5

0

10 100 1k 10k

FREQUENCY – Hz

TPC 6. PSRR vs. Frequency

40

+ISC

ⴝ ±15V

V

S

| –I SC |

VS ⴝ +5V

–25 1250 25 50 100

TEMPERATURE – °C

+ISC

V

S

| –I SC |

VS ⴝ ±15V

ⴝ +5V

75

SHORT CIRCUIT CURRENT – mA

30

20

10

0

–50

TPC 7. CMRR vs. Frequency TPC 8. Slew Rate vs. Temperature TPC 9. Short Circuit Current vs.

Temperature

REV. B

–7–

Page 8

OP193/OP293/OP493

0

–0.5

–0.10

–0.15

–0.20

INPUT OFFSET CURRENT – nA

–0.25

–50

VS ⴝ +2V

V

ⴝ 0.1V

CM

VS ⴝ ±15V

–25 1250 25 50 100

TEMPERATURE – °C

75

TPC 10. Input Offset Current vs.

Temperature

1000

100

10

5V ⱕ VS ⱕ 30V

T

ⴝ 25°C

A

0

–1

VS ⴝ ±15V

ⴝ 0.1V

75

TEMPERATURE – °C

INPUT BIAS CURRENT – nA

–2

–3

VS ⴝ +2V

–4

V

CM

–5

–50

–25 1250 25 50 100

TPC 11. Input Bias Current vs.

Temperature

1000

Hz

100

10

5V ⱕ VS ⱕ 30V

T

ⴝ 25°C

A

25

20

15

10

SUPPLY CURRENT – µA

5

0

–50

–25 1250 25 50 100

VS ⴝ ±18V

VS ⴝ +2V

V

CM

75

TEMPERATURE – °C

ⴝ 1V

TPC 12. Supply Current vs.

Temperature

10000

1000

100

DELTA

FROM V

10

CC

DELTA

FROM V

5V ⱕ VS ⱕ 30V

T

ⴝ 25°C

A

EE

VOLTAGE NOISE DENSITY – nVⲐ Hz

1

0.1 1 10 100 1k

FREQUENCY – Hz

TPC 13. Voltage Noise Density vs.

Frequency

2500

VOLTAGE GAIN – VⲐmV

2000

1500

1000

500

VS ⴝ ±15V

–10V ⱕ V

VS ⴝ +5V

0.03V ⱕ V

0

–50

–25 1250 25 50 100

ⱕ +10V

OUT

ⱕ 4V

OUT

TEMPERATURE – °C

75

TPC 16. Voltage Gain

= 100 kΩ) vs. Temperature

(R

L

CURRENT NOISE DENSITY – pAⲐ

1

0.1 1 10 100 1k

FREQUENCY – Hz

TPC 14. Current Noise Density vs.

Frequency

1000

VOLTAGE GAIN – VⲐmV

800

600

400

200

0

–50

–25 1250 25 50 100

VS ⴝ ±15V

–10V ⱕ V

VS ⴝ +5V

0.03V ⱕ V

TEMPERATURE – °C

OUT

ⱕ 4V

OUT

ⱕ +10V

75

TPC 17. Voltage Gain

= 10 kΩ) vs. Temperature

(R

L

DELTA FROM SUPPLY RAIL – mV

1

0.1 1 10 100 1000 10000

LOAD CURRENT – A

TPC 15. Delta Output Swing from

Either Rail vs. Current Load

60

40

20

GAIN – dB

0

–20

10 100 1k 10k 100k

FREQUENCY – Hz

TA ⴝ 25°C

ⴝ 5V

V

S

TPC 18. Closed-Loop Gain vs.

Frequency, V

= 5 V

S

–8–

REV. B

Page 9

OP193/OP293/OP493

p

g

(

)

g

60

40

20

GAIN – dB

0

–20

10 100 1k 10k 100k

FREQUENCY – Hz

TA ⴝ 25°C

V

ⴝ ±15V

S

TPC 19. Closed-Loop Gain vs.

Frequency, V

60

40

20

0

GAIN – dB

–20

–40

100 1k 10k 100k 1M

= ±15 V

S

PHASE

GAIN

FREQUENCY – Hz

VS ⴝ ±15V

90

45

0

–45

–90

rees

PHASE – De

60

VS ⴝ 5V TA ⴝ 25°C

A

ⴝ 1

V

50

50mV ⱕ V

LOADS TO GND

40

30

20

OVERSHOOT – %

10

0

10 100 1000 10000

ⱕ 150mV

IN

+OS

ⴝ

R

ⴥ

L

–OS

R

ⴝ

L

CAPACITIVE LOAD –

TPC 20. Small Signal Overshoot

vs. Capacitive Load

TPC 22. Open-Loop, Gain and

Phase vs. Frequency

FUNCTIONAL DESCRIPTION

The OP193 family of operational amplifiers are single-supply,

micropower, precision amplifiers whose input and output ranges

both include ground. Input offset voltage (V

) is only 75 µV

OS

maximum, while the output will deliver ±5 mA to a load. Supply current is only 17 µA.

A simplified schematic of the input stage is shown in Figure 1.

Input transistors Q1 and Q2 are PNP devices, which permit the

inputs to operate down to ground potential. The input transistors have resistors in series with the base terminals to protect the

junctions from over voltage conditions. The second stage is an

NPN cascode which is buffered by an emitter follower before

driving the final PNP gain stage.

The OP193 includes connections to taps on the input load

resistors, which can be used to null the input offset voltage, V

OS

.

The OP293 and OP493 have two additional transistors, Q7 and

Q8. The behavior of these transistors is discussed in the Output

Phase Reversal section of this data sheet.

The output stage, shown in Figure 2, is a noninverting NPN

“totem-pole” configuration. Current is sourced to the load by

emitter follower Q1, while Q2 provides current sink capability.

When Q2 saturates, the output is pulled to within 5 mV of

ground without an external pull-down resistor. The totem-pole

output stage will supply a minimum of 5 mA to an external

load, even when operating from a single 3.0 V power supply.

+OS ⴝ | –OS

RL ⴝ 50k⍀

+OS ⴝ | –OS

RL ⴝ 10k⍀

ⴥ

60

|

40

20

0

GAIN – dB

|

F

–20

–40

100 1k 10k 100k 1M

PHASE

GAIN

FREQUENCY – Hz

VS ⴝ 5V

90

45

0

–45

–90

rees

PHASE – De

TPC 21. Open-Loop, Gain and

Phase vs. Frequency

V+

I

1

I

2

I3I

+INPUT

–INPUT

OP293,

OP493

ONLY

2k⍀

2k⍀

Q1 Q2

Q7

R1

A

R1

B

TERMINALS

OP193 ONLY

NULLING

Q4

Q8

R2

A

R2

B

Q3

4

Q5

Q6

TO

OUTPUT

I5I

STAGE

6

V–

D1

Figure 1. OP193/OP293/OP493 Equivalent Input Circuit

V+

Q4

FROM

INPUT

STAGE

I

3

Q1

Q3

I

2

I

1

Q5

OUTPUT

Q2

V–

Figure 2. OP193/OP293/OP493 Equivalent Output Circuit

By operating as an emitter follower, Q1 offers a high impedance

load to the final PNP collector of the input stage. Base drive to

Q2 is derived by monitoring Q1’s collector current. Transistor

Q5 tracks the collector current of Q1. When Q1 is on, Q5 keeps

Q4 off, and current source I1 keeps Q2 turned off. When Q1 is

driven to cutoff (i.e., the output must move toward V–), Q5

allows Q4 to turn on. Q4’s collector current then provides the

base drive for Q3 and Q2, and the output low voltage swing is

set by Q2’s V

which is about 5 mV.

CE,SAT

REV. B

–9–

Page 10

OP193/OP293/OP493

Driving Capacitive Loads

OP193 family amplifiers are unconditionally stable with capacitive

loads less than 200 pF. However, the small signal, unity-gain

overshoot will improve if a resistive load is added. For example,

transient overshoot is 20% when driving a 1000 pF/ 10 kΩ load.

When driving large capacitive loads in unity-gain configurations,

an in-the-loop compensation technique is recommended as

illustrated in Figure 6.

Input Overvoltage Protection

As previously mentioned, the OP193 family of op amps use a

PNP input stage with protection resistors in series with the

inverting and noninverting inputs. The high breakdown of the

PNP transistors, coupled with the protection resistors, provides

a large amount of input protection from over voltage conditions.

The inputs can therefore be taken 20 V beyond either supply

without damaging the amplifier.

Output Phase Reversal—OP193

The OP193’s input PNP collector-base junction can be forwardbiased if the inputs are brought more than one diode drop (0.7 V)

below ground. When this happens to the noninverting input, Q4

of the cascode stage turns on and the output goes high. If the

positive input signal can go below ground, phase reversal can be

prevented by clamping the input to the negative supply (i.e.,

GND) with a diode. The reverse leakage of the diode will, of

course, add to the input bias current of the amplifier. If input bias

current is not critical, a 1N914 will add less than 10 nA of leakage. However, its leakage current will double for every 10°C

increase in ambient temperature. For critical applications, the

collector-base junction of a 2N3906 transistor will add only about

10 pA of additional bias current. To limit the current through the

diode under fault conditions, a 1 kΩ resistor is recommended in

series with the input. (The OP193’s internal current limiting

resistors will not protect the external diode.)

Output Phase Reversal—OP293 and OP493

The OP293 and OP493 include lateral PNP transistors Q7 and

Q8 to protect against phase reversal. If an input is brought more

than one diode drop (≈0.7 V) below ground, Q7 and Q8 combine to level shift the entire cascode stage, including the bias to

Q3 and Q4, simultaneously. In this case Q4 will not saturate

and the output remains low.

The OP293 and OP493 do not exhibit output phase reversal for

inputs up to –5 V below V– at +25°C. The phase reversal limit

at +125°C is about –3 V. If the inputs can be driven below these

levels, an external clamp diode, as discussed in the previous

section, should be added.

Battery-Powered Applications

OP193 series op amps can be operated on a minimum supply

voltage of 1.7 V, and draw only 13 µA of supply current per

amplifier from a 2.0 V supply. In many battery-powered circuits,

OP193 devices can be continuously operated for thousands of

hours before requiring battery replacement, thus reducing

equipment downtime and operating cost.

High performance portable equipment and instruments frequently use lithium cells because of their long shelf life, light

weight, and high energy density relative to older primary cells.

Most lithium cells have a nominal output voltage of 3 V and are

noted for a flat discharge characteristic. The low supply voltage

requirement of the OP193, combined with the flat discharge

characteristic of the lithium cell, indicates that the OP193 can

be operated over the entire useful life of the cell. Figure 3 shows

the typical discharge characteristic of a 1 AH lithium cell powering the OP193, OP293, and OP493, with each amplifier, in

turn, driving 2.1 Volts into a 100 kΩ load.

4

3

2

OP493 OP293

CELL VOLTAGE – V

1

LITHIUM SULPHUR DIOXIDE

0

1000 70002000 3000 4000 6000

50000

HOURS

OP193

Figure 3. Lithium Sulfur Dioxide Cell Discharge Characteristic with OP193 Family and 100 k

Ω

Loads

Input Offset Voltage Nulling

The OP193 provides two offset nulling terminals that can be

used to adjust the OP193’s internal V

. In general, operational

OS

amplifier terminals should never be used to adjust system offset

voltages. The offset null circuit of Figure 4 provides about

±7 mV of offset adjustment range. A 100 kΩ resistor placed in

series with the wiper arm of the offset null potentiometer, as

shown in Figure 5, reduces the offset adjustment range to 400 µV

and is recommended for applications requiring high null resolution. Offset nulling does not adversely affect TCV

performance,

OS

providing that the trimming potentiometer temperature coefficient does not exceed ±100 ppm/°C.

V+

7

2

OP193

3

1

6

4

5

100k⍀

V–

Figure 4. Offset Nulling Circuit

–10–

REV. B

Page 11

OP193/OP293/OP493

6

7

2

3

OP193

4

R2

100k⍀

V

OUT =

100mV/mA(I

TEST

)

5

V+

1

R2

9.9k⍀

R3

100k⍀

R5

100⍀

R1

1⍀

TO CIRCUIT

UNDER TEST

I

TEST

V+

7

2

OP193

3

1

6

4

5

100k⍀

100k⍀

V–

Figure 5. High Resolution Offset Nulling Circuit

A Micropower False-Ground Generator

Some single-supply circuits work best when inputs are biased

above ground, typically at 1/2 of the supply voltage. In these

cases a false ground can be created by using a voltage divider

buffered by an amplifier. One such circuit is shown in Figure 6.

This circuit will generate a false-ground reference at 1/2 of the

supply voltage, while drawing only about 27 µA from a 5 V supply.

The circuit includes compensation to allow for a 1 µF bypass

capacitor at the false-ground output. The benefit of a large

capacitor is that not only does the false ground present a very low

dc resistance to the load, but its ac impedance is low as well. The

OP193 can both sink and source more than 5 mA, which improves

recovery time from transients in the load current.

5V OR 12V

10k⍀

0.022F

240k⍀

7

240k⍀

1F

2

3

OP193

4

100⍀

6

2.5V OR 6V

1F

Figure 6. A Micropower False-Ground Generator

A Battery-Powered Voltage Reference

The circuit of Figure 7 is a battery-powered voltage reference

that draws only 17 µA of supply current. At this level, two AA

alkaline cells can power this reference for more than 18 months.

At an output voltage of 1.23 V @ 25°C, drift of the reference is

only 5.5 µV/°C over the industrial temperature range. Load

regulation is 85 µV/mA with line regulation at 120 µV/V.

Design of the reference is based on the Brokaw bandgap core

technique. Scaling of resistors R1 and R2 produces unequal

currents in Q1 and Q2. The resulting ∆V

across R3 creates a

BE

temperature-proportional voltage (PTAT) which, in turn, produces a larger temperature-proportional voltage across R4 and

R5, V1. The temperature coefficient of V1 cancels (first order)

the complementary to absolute temperature (CTAT) coefficient

. When adjusted to 1.23 V @ 25°C, output voltage

of V

BE1

tempco is at a minimum. Bandgap references can have start-up

problems. With no current in R1 and R2, the OP193 is beyond

its positive input range limit and has an undefined output state.

Shorting Pin 5 (an offset adjust pin) to ground forces the output

high under these circumstances and ensures reliable startup

without significantly degrading the OP193’s offset drift.

–11–

REV. B

240k⍀

C1

1000pF

V1

130k⍀

R5 20k⍀

OUTPUT

ADJUST

R1

R4

Q2

1

2

V

3

BE2

1.5M⍀

MAT-01AH

R3 68k⍀

⌬V

BE

R2

7

2

OP193

3

Q1

7

6

5

V

BE1

5

4

(2.5V TO 36V)

6

V+

V

OUT

(1.23V @ 25°C)

Figure 7. A Battery-Powered Voltage Reference

A Single-Supply Current Monitor

Current monitoring essentially consists of amplifying the voltage

drop across a resistor placed in series with the current to be

measured. The difficulty is that only small voltage drops can be

tolerated, and with low precision op amps this greatly limits the

overall resolution. The single-supply current monitor of Figure

8 has a resolution of 10 µA and is capable of monitoring 30 mA

of current. This range can be adjusted by changing the current

sense resistor R1. When measuring total system current, it may

be necessary to include the supply current of the current monitor, which bypasses the current sense resistor, in the final result.

This current can be measured and calibrated (together with the

residual offset) by adjustment of the offset trim potentiometer,

R2. This produces a deliberate temperature dependent offset.

However, the supply current of the OP193 is also proportional

to temperature, and the two effects tend to track. Current in R4

and R5, which also bypasses R1, can be adjusted via a gain trim.

Figure 8. Single-Supply Current Monitor

Page 12

OP193/OP293/OP493

∆

∆

∆

∆

I

T

V

T

R6 R7

R2 R10

OUT

TEMP

=

+

×

()

A Single-Supply Instrumentation Amplifier

Designing a true single-supply instrumentation amplifier with

zero-input and zero-output operation requires special care.

The traditional configuration, shown in Figure 9, depends upon

amplifier A1’s output being at 0 V when the applied commonmode input voltage is at 0 V. Any error at the output is multiplied

by the gain of A2. In addition, current flows through resistor R3

as A2’s output voltage increases. A1’s output must remain at 0 V

while sinking the current through R3, or a gain error will result.

With a maximum output voltage of 4 V, the current through R3

is only 2 µA, but this will still produce an appreciable error.

–IN

+IN

R1

20k⍀

R2

1.98M⍀

5V

A1

1/2 OP293

R3

V+

20k⍀

V–

I

SINK

R4

1.98M⍀

A2

1/2 OP293

5V

V+

V–

V

OUT

Figure 9. A Conventional Instrumentation Amplifier

One solution to this problem is to use a pull-down resistor. For

example, if R3 = 20 kΩ, then the pull-down resistor must be

less than 400 Ω. However, the pull-down resistor appears as a

fixed load when a common-mode voltage is applied. With a 4 V

common-mode voltage, the additional load current will be 10 mA,

which is unacceptable in a low power application.

Figure 10 shows a better solution. A1’s sink current is provided

by a pair of N-channel FET transistors, configured as a current

mirror. With the values shown, sink current of Q2 is about

340 µA. Thus, with a common-mode voltage of 4 V, the addi-

tional load current is limited to 340 µA versus 10 mA with a

400 Ω resistor.

R1

20k⍀

–IN

+IN

Figure 10. An Improved Single-Supply, 0 VIN, 0 V

R2

1.98M⍀

5V

A1

1/2 OP293

VN2222

V+

V–

5V

10k⍀

Q1

R3

20k⍀

Q2

R4

1.98M⍀

5V

V+

A2

1/2 OP293

V

OUT

V–

OUT

Instrumentation Amplifier

A Low-Power, Temperature to 4–20 mA Transmitter

A simple temperature to 4–20 mA transmitter is shown in Figure 11. After calibration, this transmitter is accurate to ±0.5°C

over the –50°C to +150°C temperature range. The transmitter

operates from 8 V to 40 V with supply rejection better than

3 ppm/V. One half of the OP293 is used to buffer the V

TEMP

pin, while the other half regulates the output current to satisfy

the current summation at its noninverting input:

VR6R7

×+

+

TEMP

R2 R10

×

−

I

OUT

()

V

SET

R2 R6 R7

++

R2 R10

×

The change in output current with temperature is the derivative

of the transfer function:

REF-43BZ

V

IN

V

OUT

V

TEMP

GND

2

6

3

R1 10k⍀

4

ALL RESISTORS 1/4W, 5% UNLESS OTHERWISE NOTED

2

1/2 OP293

3

8

V

1

TEMP

4

R3

100k⍀

R2

1k⍀

R5

5k⍀

R4

20k⍀

ZERO

TRIM

1N4002

SPAN TRIM

R6

3k⍀

R7

5k⍀

6

7

SET

1/2 OP293

5

V

R9

100k⍀

1%, 1/2 W

R8

1k⍀

R10

100⍀

2N1711

I

OUT

R

LOAD

V+

8V TO 40V

Figure 11. Temperature to 4–20 mA Transmitter

–12–

REV. B

Page 13

OP193/OP293/OP493

From the formulas, it can be seen that if the span trim is

adjusted before the zero trim, the two trims are not interactive,

which greatly simplifies the calibration procedure.

Calibration of the transmitter is simple. First, the slope of the

output current versus temperature is calibrated by adjusting the

span trim, R7. A couple of iterations may be required to be sure

the slope is correct.

Once the span trim has been completed, the zero trim can be made.

Remember that adjusting the zero trim will not affect the gain.

The zero trim can be set at any known temperature by adjusting

R5 until the output current equals:

ITT

=−+

OUT

∆

T

∆

OPERATING

I

FS

()

AMBIENT MIN

4 mA

Table I shows the values of R6 required for various temperature

ranges.

Table I. R6 Values vs. Temperature

Temp Range R6

0°C to 70°C 10 kΩ

–40°C to +85°C 6.2 kΩ

–55°C to +150°C3 kΩ

A Micropower Voltage Controlled Oscillator

An OP293 in combination with an inexpensive quad CMOS

analog switch forms the precision VCO of Figure 12. This circuit provides triangle and square wave outputs and draws only

50 µA from a single 5 V supply. A1 acts as an integrator; S1

switches the charging current symmetrically to yield positive and

negative ramps. The integrator is bounded by A2 which acts as

a Schmitt trigger with a precise hysteresis of 1.67 volts, set by

resistors R5, R6, and R7, and associated CMOS switches. The

resulting output of A1 is a triangle wave with upper and lower

levels of 3.33 and 1.67 volts. The output of A2 is a square wave

with almost rail-to-rail swing. With the components shown,

frequency of operation is given by the equation:

fV V

=× V Hz10 /

OUT CONTROL

but this can easily be changed by varying C1. The circuit operates well up to 500 Hz.

V

CONTROL

R1

200k⍀

R2

200k⍀

R3

100k⍀

1 IN/OUT

2 OUT/IN

3 OUT/IN

4 IN/OUT

5 CONT

6 CONT

7

V

SS

C1

75nF

2

3

R4

200k⍀

CD4066

S1

S2

S3

S4

5V

A1

1/2 OP293

R8

200k⍀

8

1

4

TRIANGLE

V

DD

CONT 13

CONT 12

IN/OUT 11

OUT/IN 10

OUT/IN 9

IN/OUT 8

5V

OUT

200k⍀

14

5V

R5

200k⍀

6

A2

1/2 OP293

5

R6

5V

5V

R7

200k⍀

SQUARE

OUT

7

Figure 12. Micropower Voltage Controlled Oscillator

A Micropower, Single-Supply Quad Voltage Output 8-Bit DAC

The circuit of Figure 13 uses the DAC8408 CMOS quad 8-bit

DAC and the OP493 to form a single-supply quad voltage output DAC with a supply drain of only 140 µA. The DAC8408 is

used in the voltage switching mode and each DAC has an output resistance (≈10 kΩ) independent of the digital input code.

The output amplifiers act as buffers to avoid loading the DACs.

The 100 kΩ resistors ensure that the OP493 outputs will swing

to within 1/2 LSB of ground, i.e.:

1

1.23 V

×=

3 mV

2 256

REV. B

–13–

Page 14

OP193/OP293/OP493

5V

3.6k⍀

4

5

6

25

AD589

1.23V

I

OUT1A

I

OUT2A/2B

I

OUT1B

I

OUT1C

5V

1

V

DD

DAC A

1/4

DAC8408

DAC B

1/4

DAC8408

DAC C

1/4

DAC8408

5V

A Single-Supply Micropower Quad Programmable-Gain

Amplifier

4

The combination of the quad OP493 and the DAC8408 quad

8-bit CMOS DAC creates a quad programmable-gain amplifier

with a quiescent supply drain of only 140 µA (Figure 14). The

2

A

A

V

REF

2

B

V

REF

8

3

6

5

1/4 OP493

B

1/4 OP493

V

OUT

1

11

R1

100k⍀

V

OUT

7

R2

100k⍀

digital code present at the DAC, which is easily set by a microprocessor, determines the ratio between the fixed DAC feedback

A

resistor and the resistance that the DAC feedback ladder presents to the op amp feedback loop. The gain of each amplifier is:

V

Vn

B

where n equals the decimal equivalent of the 8-bit digital code

OUT

IN

256

=

present at the DAC.

If the digital code present at the DAC consists of all zeros, the

feedback loop will be open causing the op amp to saturate. The

10 MΩ resistors placed in parallel with the DAC feedback loop

eliminates this problem with a very small reduction in gain

13

C

C

V

REF

27

12

1/4 OP493

V

OUT

14

R3

100k⍀

accuracy. The 2.5 V reference biases the amplifiers to the center

C

of the linear region providing maximum output swing.

I

OUT2C/2D

24

DAC D

V

D

REF

I

23

OUT1D

1/4

DAC8408

9

D

10

1/4 OP493

21

8

R4

100k⍀

OP493

DAC DATA BUS

PINS 9(LSB)–16(MSB)

DAC8408ET

DGND

28

A/B

R/W

DS1

DS2

17

18

DIGITAL

CONTROL

19

SIGNALS

20

Figure 13. Micropower Single-Supply Quad VoltageOutput 8-Bit DAC

V

D

OUT

–14–

REV. B

Page 15

VINA

VINB

VINC

VIND

DIGITAL

CONTROL

SIGNALS

C1

0.1F

C2

0.1F

C3

0.1F

C4

0.1F

OP193/OP293/OP493

1

V

DD

RFBA

3

DAC A

1/4

DAC8408

RFBB

7

DAC B

1/4

DAC8408

RFBC

26

DAC C

1/4

DAC8408

RFBD

22

DAC D

1/4

DAC8408

DAC DATA BUS

PINS 9(LSB)–16(MSB)

V

REF

I

OUT1A

I

OUT2A/2B

V

REF

I

OUT1B

V

REF

I

OUT1C

I

OUT2C/2D

V

REF

I

OUT1D

A

2

R1

10M⍀

4

5

B

8

R2

10M⍀

6

C

27

R3

10M⍀

25

24

D

21

R4

10M⍀

23

2

3

6

5

9

10

13

12

A

1/4 OP493

B

1/4 OP493

C

1/4 OP493

D

1/4 OP493

4

OP493

17

A/B

18

R/W

19

DS1

20

DS2

DAC8408ET

DGND

28

1

11

7

8

14

5V

V

OUT

V

OUT

V

OUT

V

OUT

2.5V

REFERENCE

VOLTAGE

A

B

C

D

REV. B

Figure 14. Single-Supply Micropower Quad Programmable-Gain Amplifier

–15–

Page 16

OP193/OP293/OP493

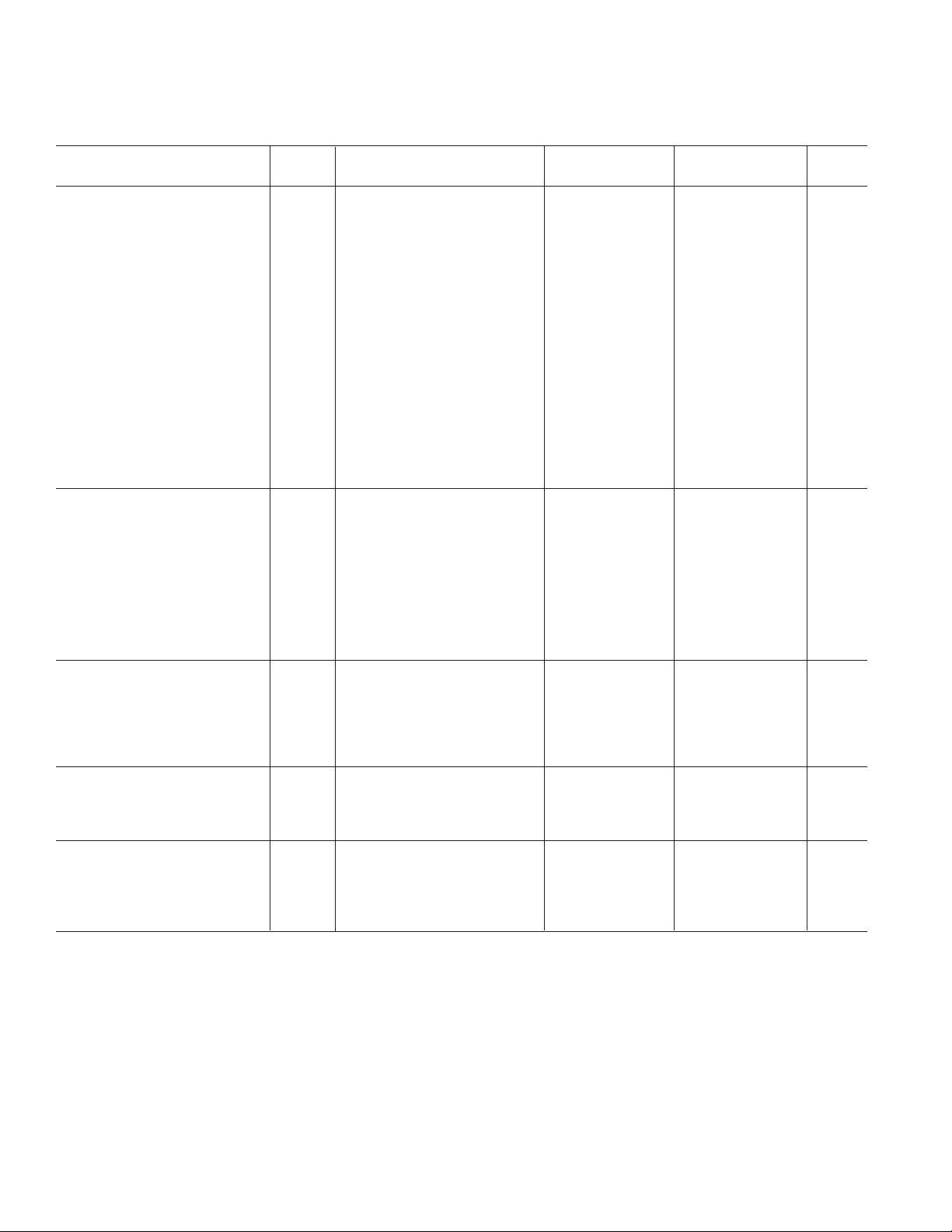

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

0.0098 (0.25)

0.0040 (0.10)

PIN 1

0.210

(5.33)

MAX

0.160 (4.06)

0.115 (2.93)

PIN 1

14

1

0.022 (0.558)

0.014 (0.356)

8-Lead SO

(S Suffix)

8

1

0.1968 (5.00)

0.1890 (4.80)

0.0500

(1.27)

BSC

5

4

0.0192 (0.49)

0.0138 (0.35)

0.1574 (4.00)

0.1497 (3.80)

0.2440 (6.20)

0.2284 (5.80)

0.0688 (1.75)

0.0532 (1.35)

0.0098 (0.25)

0.0075 (0.19)

14-Lead Epoxy DIP

(P Suffix)

8

7

0.795 (20.19)

0.725 (18.42)

0.070 (1.77)

0.100

(2.54)

0.045 (1.15)

BSC

0.280 (7.11)

0.240 (6.10)

0.060 (1.52)

0.015 (0.38)

0.130

(3.30)

MIN

SEATING

PLANE

0.0196 (0.50)

0.0099 (0.25)

8

°

0

°

0.325 (8.25)

0.300 (7.62)

0.015 (0.381)

0.008 (0.204)

x 45

0.0500 (1.27)

0.0160 (0.41)

0.195 (4.95)

0.115 (2.93)

8-Lead Epoxy DIP

(P Suffix)

8

PIN 1

1

0.430 (10.92)

0.348 (8.84)

°

0.210

(5.33)

MAX

0.160 (4.06)

0.115 (2.93)

0.022 (0.558)

0.014 (0.356)

0.100

(2.54)

BSC

5

4

0.070 (1.77)

0.045 (1.15)

0.280 (7.11)

0.240 (6.10)

0.060 (1.52)

0.015 (0.38)

0.130

(3.30)

MIN

SEATING

PLANE

0.325 (8.25)

0.300 (7.62)

0.015 (0.381)

0.008 (0.204)

0.195 (4.95)

0.115 (2.93)

C00295–0–1/02(B)

16-Lead Wide Body SOL

(S Suffix)

0.0192 (0.49)

0.0138 (0.35)

9

0.2992 (7.60)

0.2914 (7.40)

8

0.1043 (2.65)

0.0926 (2.35)

0.4193 (10.65)

0.3937 (10.00)

0.0125 (0.32)

0.0091 (0.23)

8

°

0

°

0.0291 (0.74)

0.0098 (0.25)

x 45

°

0.0500 (1.27)

0.0157 (0.40)

16

PIN 1

1

0.0118 (0.30)

0.0040 (0.10)

0.4133 (10.50)

0.3977 (10.00)

0.0500 (1.27)

BSC

Revision History

Location Page

Data Sheet changed from REV. A to REV. B.

Deletion of WAFER TEST LIMITS Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Deletion of DICE CHARACTERISTICS Images . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Edits to ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

–16–

REV. B

PRINTED IN U.S.A.

Loading...

Loading...