Page 1

NTE1853

Integrated Circuit

Digital Filter for Compact Disc Digital Audio System

Features:

D 16–Bit Serial Data Input (Two’s Complement)

D Interpolated Data Replaces Erroneous Data Samples

D –12dB Attenuation via the Active Low Attenuation Input Control (ATSB)

D Smoothed Trasitions Before and After Muting

D Two Identical Finite Impulse Response Transversal Filters each with a Sampling Rate of Four

Times that of the Normal Digital Audio Data

D Digital Audio Output of 32–Bit Words Transmitted in Biphasemark Code

Applications:

D Compact Disc Digital Audio System

D Digital Filter

Absolute Maximum Ratings:

Supply Voltage Range (Pin24), V

Maximum Input Voltage Range, V

Electrostatic Handling (Note 2), V

DD

I

ES

Operating Ambient Temperature Range, T

Storage Temperature Range, T

stg

A

–0.5V to +7.0V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–0.5V to VDD+0.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–1000V to +1000V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–20° to +70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–65° to +150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Note 1. All outputs are short–circuit protected except the crystal oscillator output.

Note 2. Equivalent to discharging a 100pF capacitor through a 1.5Ω series resistor with a rise time

of 15ns.

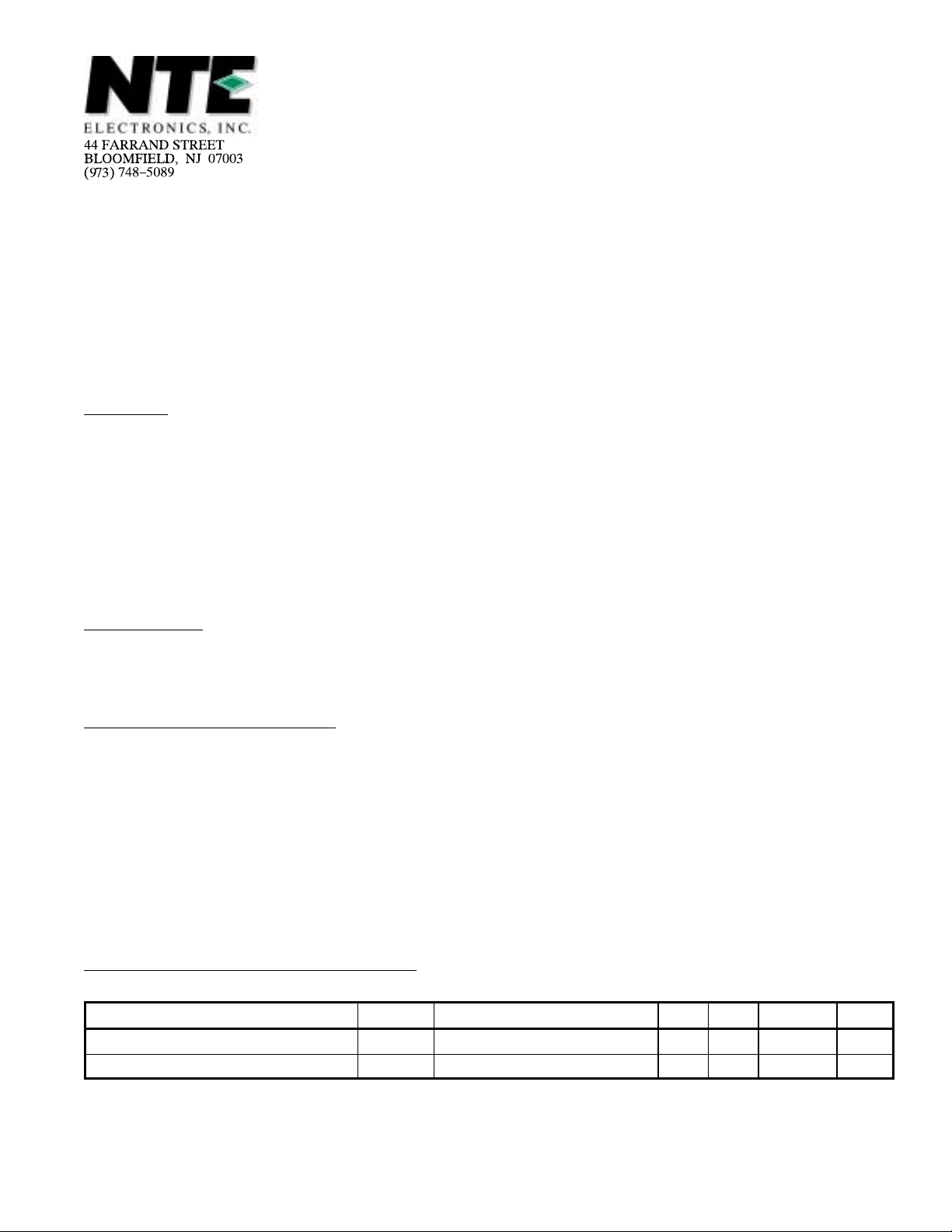

DC and AC Electrical Characteristics:

(VDD = 4.5 to 5.5V, VSS = 0, TA = –20° to +70°C unless

otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Unit

Supply Voltage (Pin24) V

Supply Current (Pin24) I

DD

DD

4.5 5.0 5.5 V

– 180 – mA

Page 2

DC and AC Electrical Characteristics (Cont’d): (VDD = 4.5 to 5.5V, VSS = 0, TA = –20° to +70°C

unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Unit

WSAB, DAAB

Input Voltage, Low V

Input Voltage, High V

Input Leakage Current I

Input Capacitance C

EFAB, SDAB (Note 1)

Input Voltage, Low V

Input Voltage, High V

Input Leakage Current I

Input Capacitance C

CLAB, SCAB, ATSB, MUSB (Note 2)

Input Voltage, Low V

Input Voltage, High V

Input Leakage Current I

Input Capacitance C

Output XOUT

Mutual Conductance at 100kHz G

Small–Signal Voltage Gain A

Input Capacitance C

Feedback Capacitance C

Output Capacitance C

Input Leakage Current I

Slave Clock Mode

Input Voltage (Peak to Peak) V

I(P–P)

Input Voltage, Low V

Input Voltage, High V

Input Rise Time t

Input Fall Time t

Input High Time at 2V (Relative to

t

HIGH

Clock Period)

IH

LI

IH

LI

IH

LI

FB

LI

IH

R

F

IL

I

IL

VI = 0V –10 – – µA

VI = V

DD

I

IL

VI = 0V –30 – – µA

VI = V

DD

I

M

AV = GM x R

V

I

O

O

Note 3 3.0 – VDD+0.5 V

Note 3 0 – 1 V

IL

Note 3 3.0 – VDD+0.5 V

Note 4 – – 20 ns

Note 4 – – 20 ns

–0.3 – +0.8 V

2.0 – VDD+0.5 V

–10 – +10 µA

– – 7 pF

–0.3 – +0.8 V

2.0 – VDD+0.5 V

– – +50 µA

– – 7 pF

–0.3 – +0.8 V

2.0 – VDD+0.5 V

– – +10 µA

– – 7 pF

1.5 – – mA/V

3.5 – – V/V

– – 10 pF

– – 5 pF

– – 10 pF

–10 0 +10 µA

35 – 65 %

Note 1. Inputs EFAB and SDAB both have internal pull–downs.

Note 2. Inputs CLAB, SCAB, ATSB

, and MUSB have internal pull–ups.

Note 3. The minimum peak–to–peak voltage can be reduced to 2V if the output XSYS is not being

used. Similarly V

can be reduced to 2.4V (Min). All other levels remain the same.

IH

Note 4. Reference levels = 10% and 90%.

Page 3

DC and AC Electrical Characteristics (Cont’d): (VDD = 4.5 to 5.5V, VSS = 0, TA = –20° to +70°C

unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Unit

DABD, CLBD, WSBD

Output Voltage, Low V

Output Voltage, High V

Load Capacitance C

OL

OH

IOL = 1.6mA 0 – 0.4 V

–IOH = 0.2mA 2.4 – V

L

– – 50 pF

DD

V

XSYS (Note 5)

Output Voltage, Low V

Output Voltage, High V

Load Capacitance C

OL

OH

L

0 – 0.4 V

2.4 – V

DD

– – 50 pF

V

DOBM

Voltage Across a 75Ω Load via

V

L(P–P)

0.4 – 0.6 V

Attenuator (Peak–to–Peak)

Note 5. The output current conditions are dependent on the drive conditions. When a crystal oscilla-

tor is being used, the output current capability is I

input is being used, the output currents are reduced to I

= +1.6mA; IOH = –0.2mA. But if a slave

OL

= +0.2mA; IOH = –0.2mA.

OL

Timing Characteristics:

Parameter Symbol Test Conditions Min Typ Max Unit

Operating Frequency (XTAL) f

Inputs

SCAB, CLAB (Note 6)

SCAB Clock Frequency (Burst Clock) f

CLAB Clock Frequency f

Clock Low Time t

Clock High Time t

Input Rise Time t

Input Fall Time t

DAAB, WSAB, EFAB (Note 8)

Data Setup Time tSU, t

Data Hold Time tHD, t

Input Rise Time t

Input Fall Time t

XTAL

SCAB

CLAB

CKL

CKH

R

F

DAT

DAT

R

F

10.16 11.2896 12.42 MHz

– 2.8224 – MHz

Note 7 – 2.8224 – MHz

– 1.4112 – MHz

110 – – ns

110 – – ns

– – 20 ns

– – 20 ns

40 – – ns

0 – – ns

– – 20 ns

– – 20 ns

Note 6. Reference levels = 0.8V and 2.0V

1

Note 7. The signal CLAB can run at either 2.8MHz (

/4 system clock) or 1.4MHz (1/8 system clock)

under typical conditions. It does not have a minimum or maximum frequency, but is limited

to being

1

/4 or 1/8 of the system clock frequency.

Note 8. Input setup and hold times measured with respect to clock input from A–chip (CLAB). Refer-

ence levels = 0.8V and 2.0V.

Page 4

Timing Characteristics (Cont’d):

Parameter Symbol Test Conditions Min Typ Max Unit

SDAB (Note 9)

Subcode Data Setup Time tSU, t

Subcode Data Hold Time tHD, t

Input Rise Time t

Input Fall Time t

Outputs

WSBD (Note 6 & Note 10)

Word Select Setup Time tSU, t

Word Select Hold Time tHD, t

WSBD (Note 6)

Output Rise Time t

Output Fall Time t

DABD (Note 6 & Note 10)

Data Setup Time tSU, t

Data Hold Time tHD, t

Outputs (Cont’d)

DABD (Note 6)

Output Rise Time t

Output Fall Time t

CLBD (Note 6 & Note 10)

Clock Period t

Clock Low Time t

Clock High Time t

Clock Setup Time tSU, t

Clock Hold Time tHD, t

CLBD (Note 6)

Output Rise Time t

Output Fall Time t

DABD (Note 6 & Note 11)

Data Setup Time tSU, t

Data Hold Time tHD, t

SDAT

SDAT

R

F

WS

WS

R

F

DATD

DATD

R

F

CK

CKL

CKH

CLD

CLD

R

F

DATBD

DATBD

40 – – ns

0 – – ns

– – 20 ns

– – 20 ns

40 – – ns

0 – – ns

– – 20 ns

– – 20 ns

40 – – ns

0 – – ns

– – 20 ns

– – 20 ns

161 177 197 ns

65 – – ns

65 – – ns

40 – – ns

0 – – ns

– – 20 ns

– – 20 ns

40 – – ns

60 – – ns

Note 6. Reference levels = 0.8V and 2.0V

1

Note 7. The signal CLAB can run at either 2.8MHz (

/4 system clock) or 1.4MHz (1/8 system clock)

under typical conditions. It does not have a minimum or maximum frequency, but is limited

to being

1

/4 or 1/8 of the system clock frequency.

Note 8. Input setup and hold times measured with respect to clock input from A–chip (CLAB). Refer-

ence levels = 0.8V and 2.0V.

Note 9. Input setup and hold times measured with respect to subcode burst clock input from A–chip

(SCAB). Reference levels = 0.8V and 2.0V.

Note10. Output setup and hold times measured with respect to system clock output (XSYS).

Note11. Output setup and hold times measured with respect to clock output (CLBD).

Page 5

Timing Characteristics (Cont’d):

Parameter Symbol Test Conditions Min Typ Max Unit

WSBD (Note 6 & Note 11)

Word Select Setup Time tSU,

t

DATWSD

Word Select Hold Time tSU,

t

DATWSD

DOBM (Note 12)

Output Rise Time t

Output Fall Time t

Data Bit 0 Pulse Width High t

Data Bit 0 Pulse Width Low t

Data Bit 1 Pulse Width High t

Data Bit 1 Pulse Width Low t

XSYS

Output Rise Time t

Output Fall Time t

Output High Time at 2V

(Relative to Clock Period)

HIGH(0)

LOW(0)

HIGH(1)

LOW(1)

t

R

F

R

F

HIGH

40 – – ns

60 – – ns

– – 20 ns

– – 20 ns

– 354 – ns

– 354 – ns

– 177 – ns

– 177 – ns

Note 6 – – 20 ns

Note 6 – – 20 ns

35 – 65 %

Note 6. Reference levels = 0.8V and 2.0V

Note11. Output setup and hold times measured with respect to clock output (CLBD).

Note 12. Output rise and fall times measured between the 10% and 90% levels; the data bit pulse

width measured at the 50% level.

Page 6

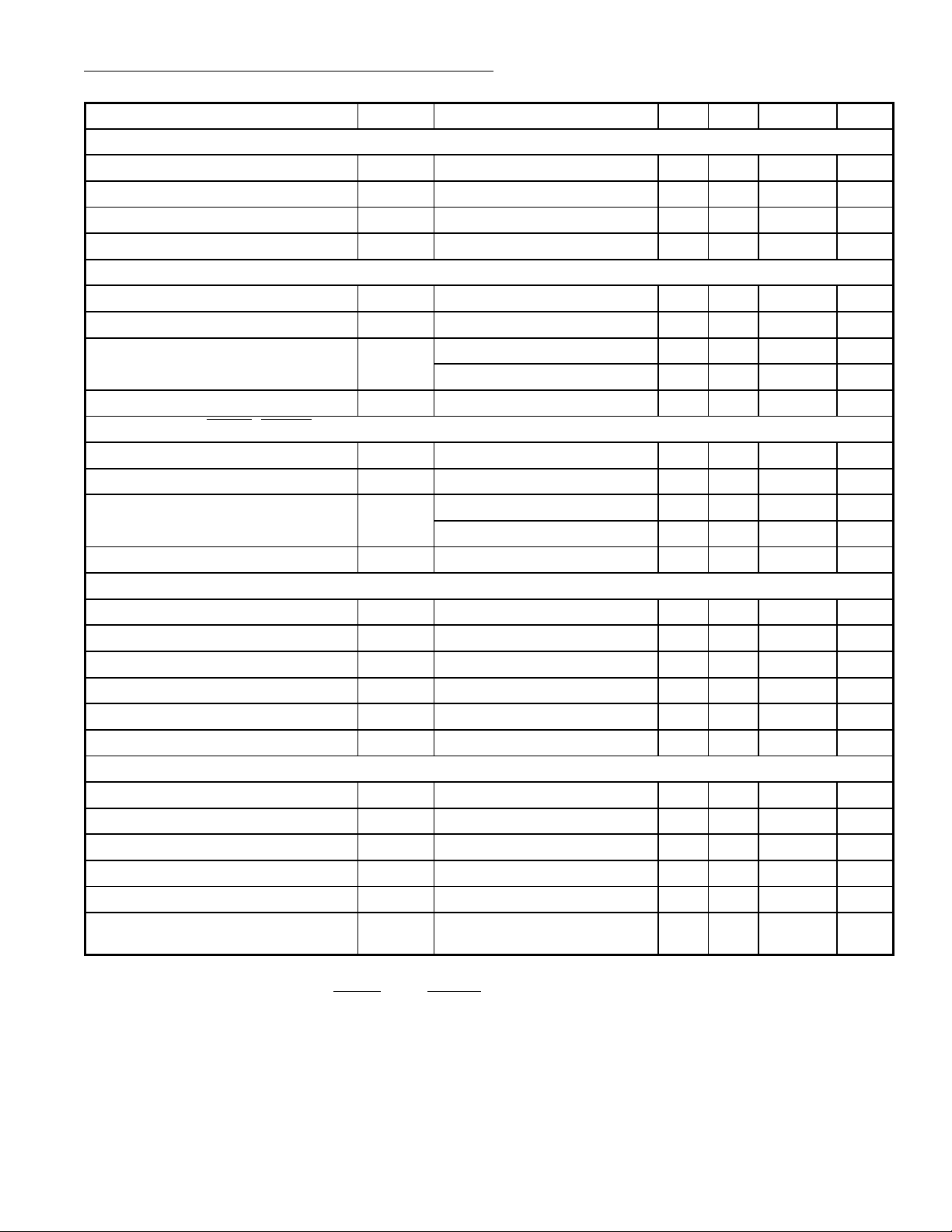

Pin Connection Diagram

WSAB

CLAB

DAAB

EFAB

N.C.

SCAB

SDAB

N.C.

X

SYS

X

OUT

X

V

SS

IN

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

V

DD

MUSB

ATSB

N.C.

N.C.

N.C.

WSDB

N.C.

CLBD

DABD

DOBM

TEST

24 13

112

1.300 (33.02)

Max

.520

(13.2)

.225

(5.73)

Max

.100 (2.54)

1.100 (27.94)

.600

(15.24)

.126

Loading...

Loading...