Page 1

NT7502

65 X 132 RAM-Map LCD Controller / Driver

Features

! Direct RAM data display using the display RAM. When

RAM data bit is 0, it is not displayed. When RAM data bit

is 1, it is displayed. (At normal display)

! RAM capacity: 65 X 132 = 8580 bits

! Many command functions: Read/Write Display Data.

Display ON/OFF. Normal/Reverse Display. Page

Address Set. Set Display Start Line. Set LCD Bias,

Electronic contrast Controls, V0 voltage regulation

internal resistor ratio set, Read Modify Write, Select

Segment Driver Direction, Power Save

! High-speed 8-bit microprocessor interface allowing direct

connection to both the 8080 and 6800

! Serial interface

! Power supply voltage: 2.4 - 3.5V

! Maximum 12V LCD driving output voltage

! 2X / 3X / 4X on chip DC-DC converter

! Voltage regulator

! Voltage follower

! On-chip oscillator

General Description

The NT7502 is a single-chip LCD driver for dot-matrix liquid

crystal displays which is directly connectable to a

microcomputer bus. It accepts 8-bit serial or parallel display

data directly sent from a microcomputer and stores it in an

on-chip display RAM. It generates a LCD drive signal

independent of the microprocessor clock.

The set of the on-chip display RAM of 65 X 132 bits and a

one-to-one correspondence between LCD panel pixel dots

and on-chip RAM bits permit implementation of displays with

a high degree of freedom.

The NT7502 contains 65 common output circuits and 132

segment output circuits, so that a single chip of NT7502 can

make 65 X 132, 55 X 132, 49 X 132 and 33 X 132 dot

displays with pad option (DUTY1, DUTY0).

No external operation clock is required for RAM read/write

operations. Accordingly, this driver can be operated with a

minimum current consumption and its onboard

low-current-consumption liquid crystal power supply can

implement a high-performance handy display system with

minimum current consumption and the smallest LSI

configuration.

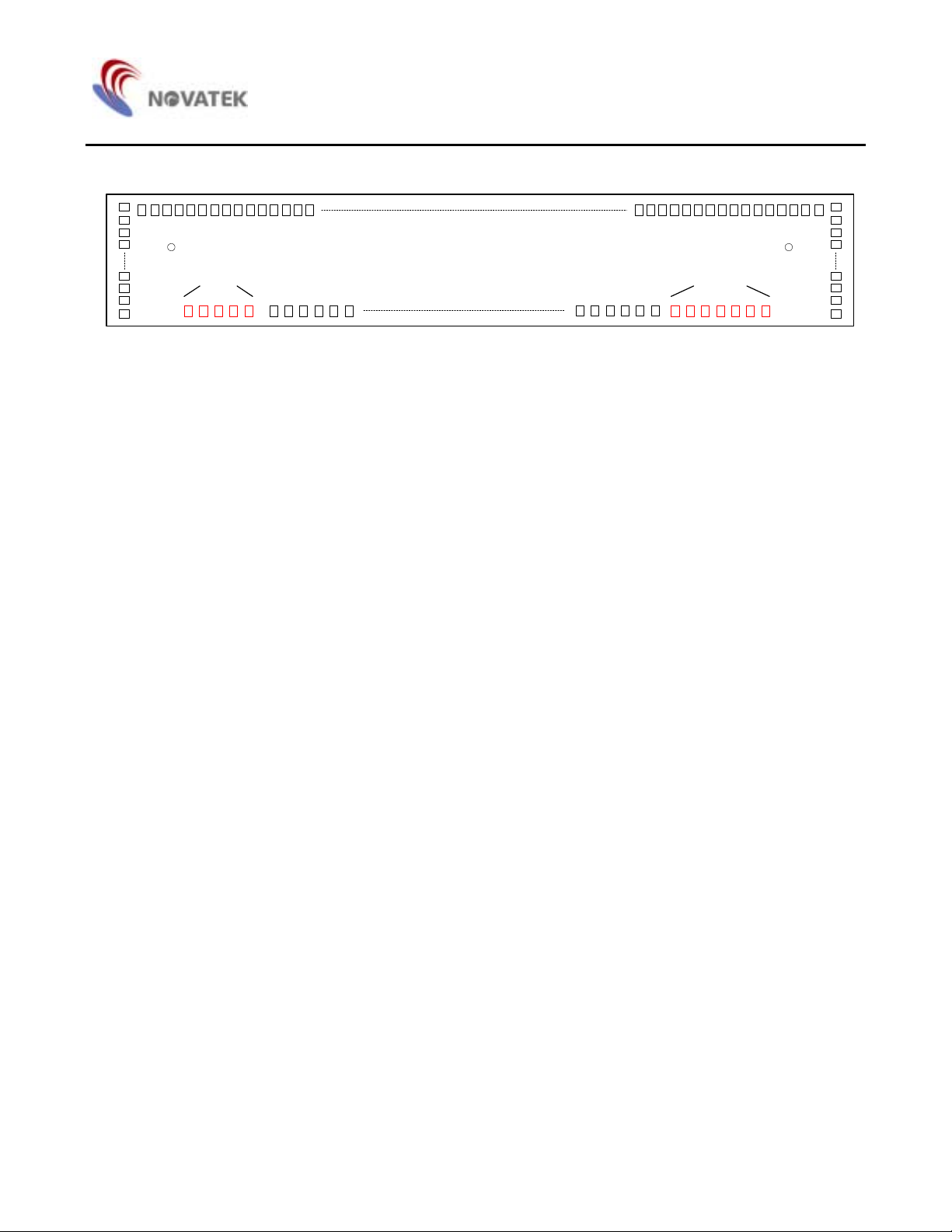

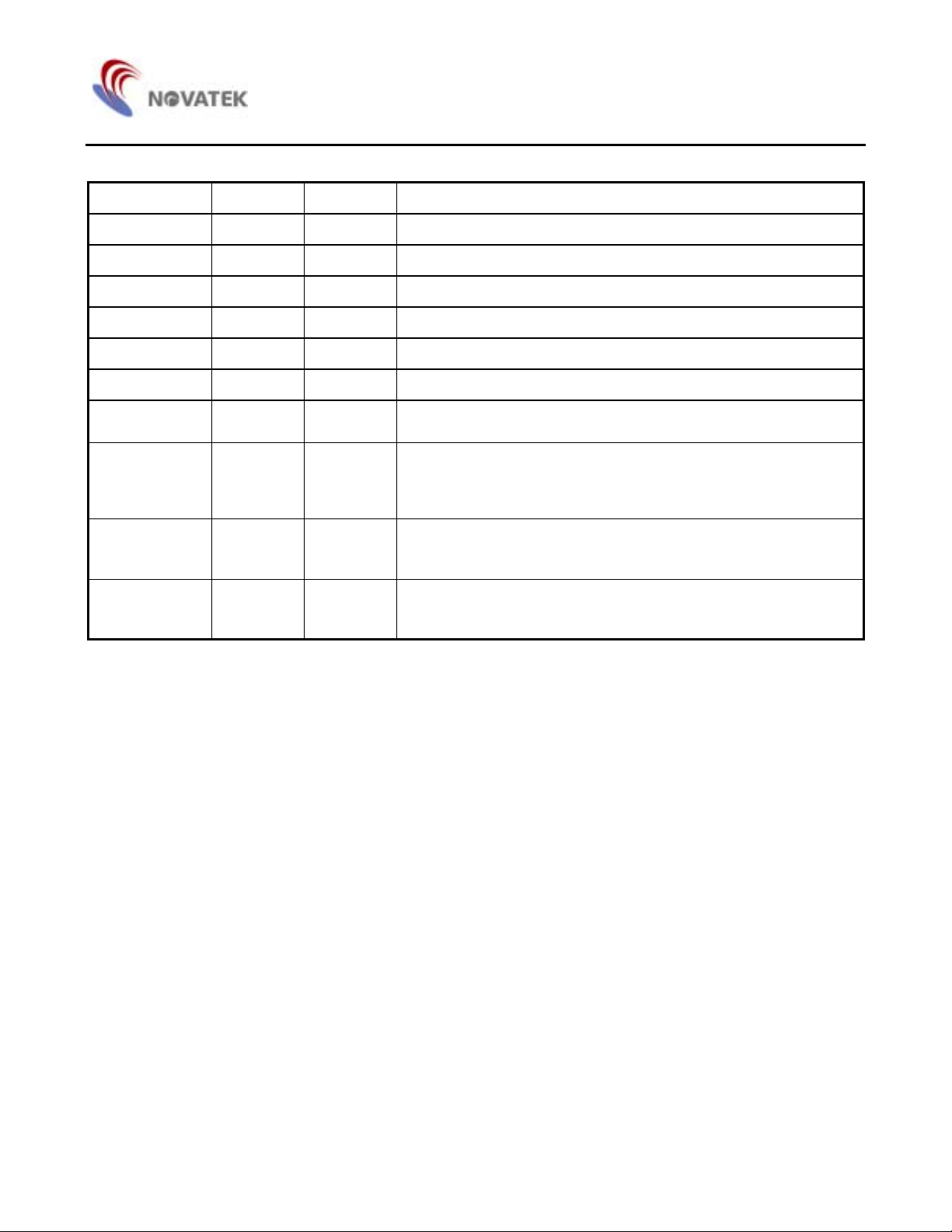

Pin Configuration

SEG130

48COM31

COM30

COM29

495051

COM28

COMS

COM1

COM0

SEG0

7879808182

SEG1

SEG2

83

SEG131

COM32

COM33

211

212

213

214

COM62

COM34

215

COM63

COMS

FRS

FR

243

244

245

246

247

NT7502H-TABF1

(Copper Side View)

40414243444546

47

P/S

HPM

IRS

39

V4

V3NCV0VRM/S

CLS

C86

+CAP2-VEXT

VRSV1V2

CAP1

+

VDD2

VSS

VOUTNCCAP3+CAP1-CAP2

1 V1.0

1011121314151617181920212223242526272829303132333435363738

CS1

CS2

RESA0WRRDD0D1D2D3D4D5D6D7DUTY0DUTY1VDD

NC

123456789

NCNCNCNCFRCLDOF

Page 2

NT7502

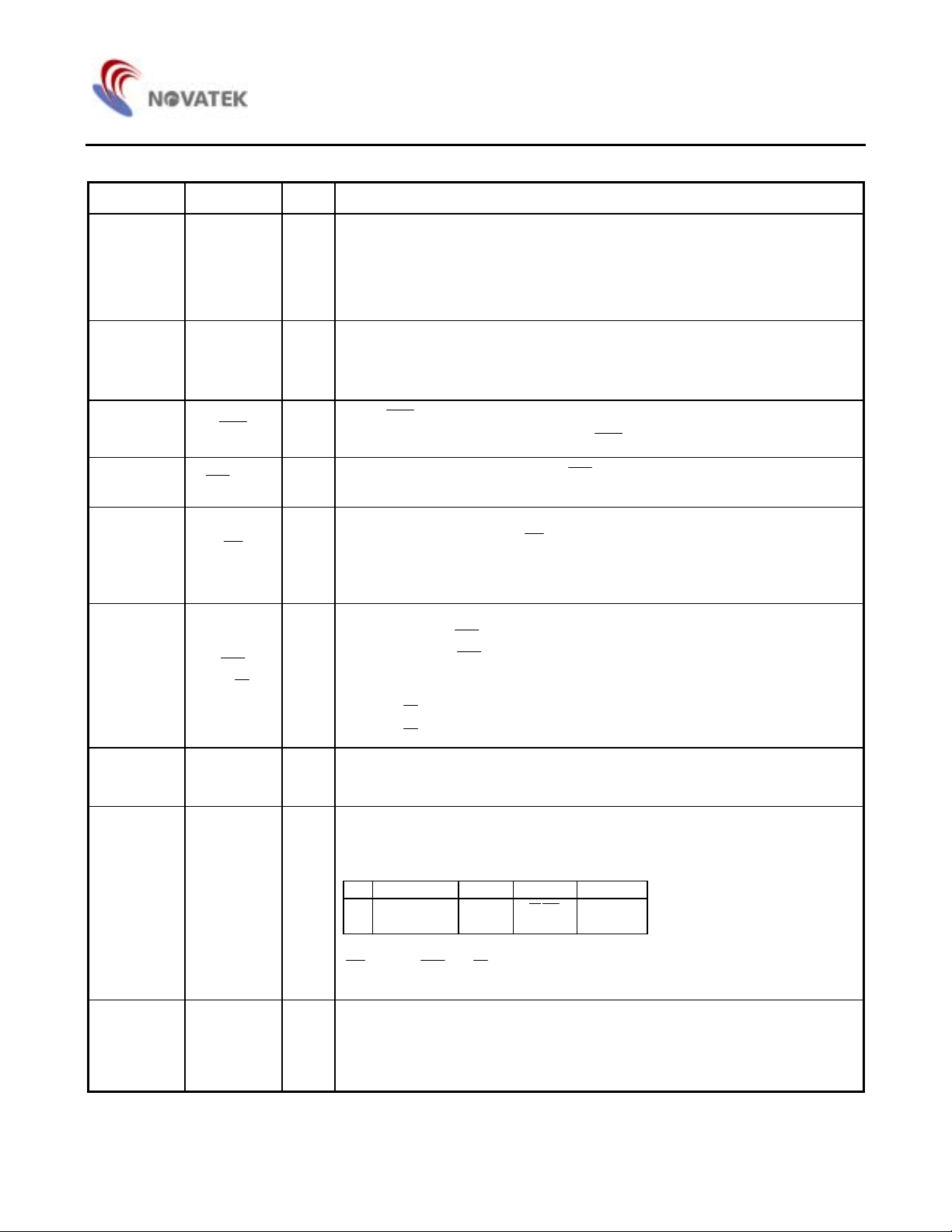

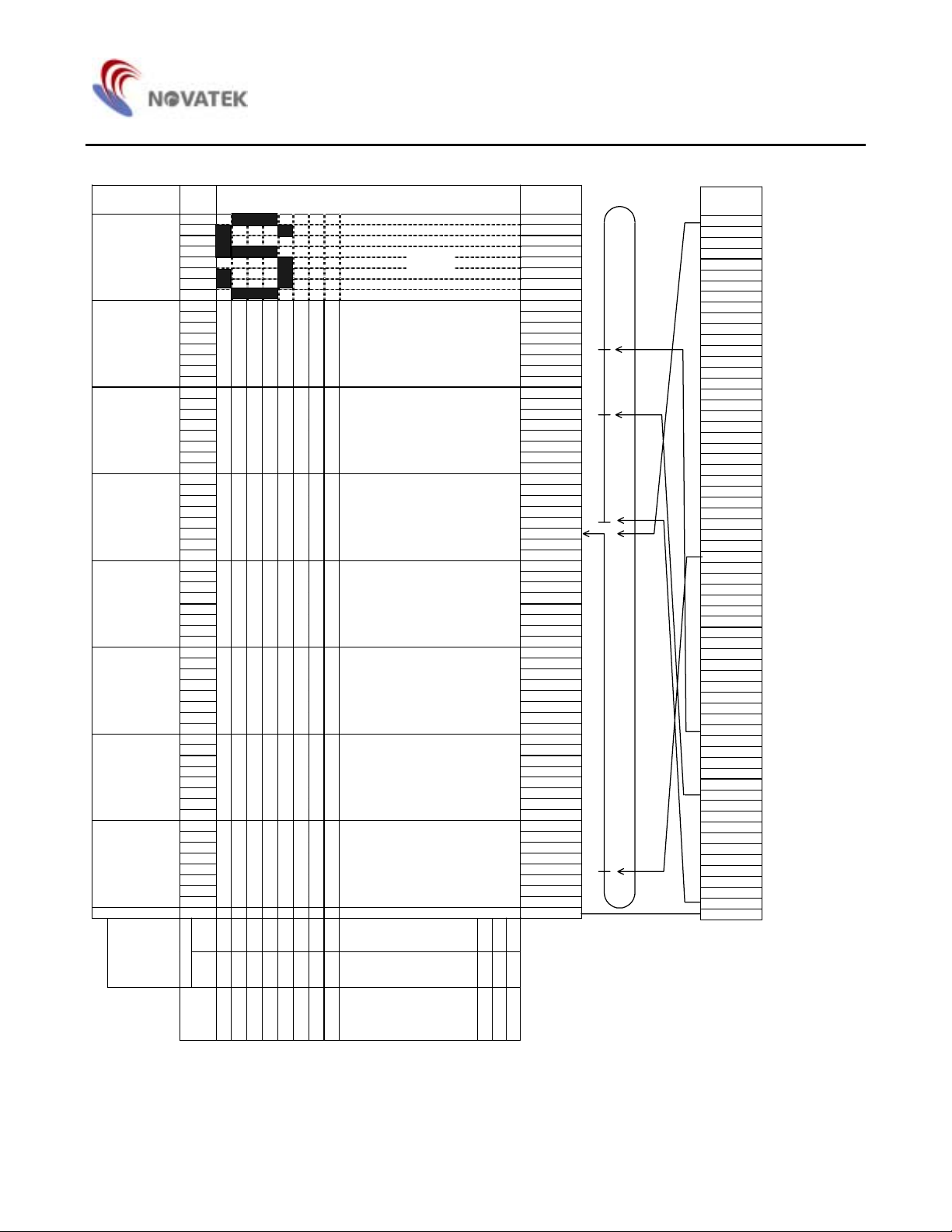

Pad Configuration

281

282

ALK_L ALK_R

118

NT7502

DUMMY DUMMY

298

DUMMY0 DUMMY4 DUMMY5 DUMMY11

1001

117

101

2

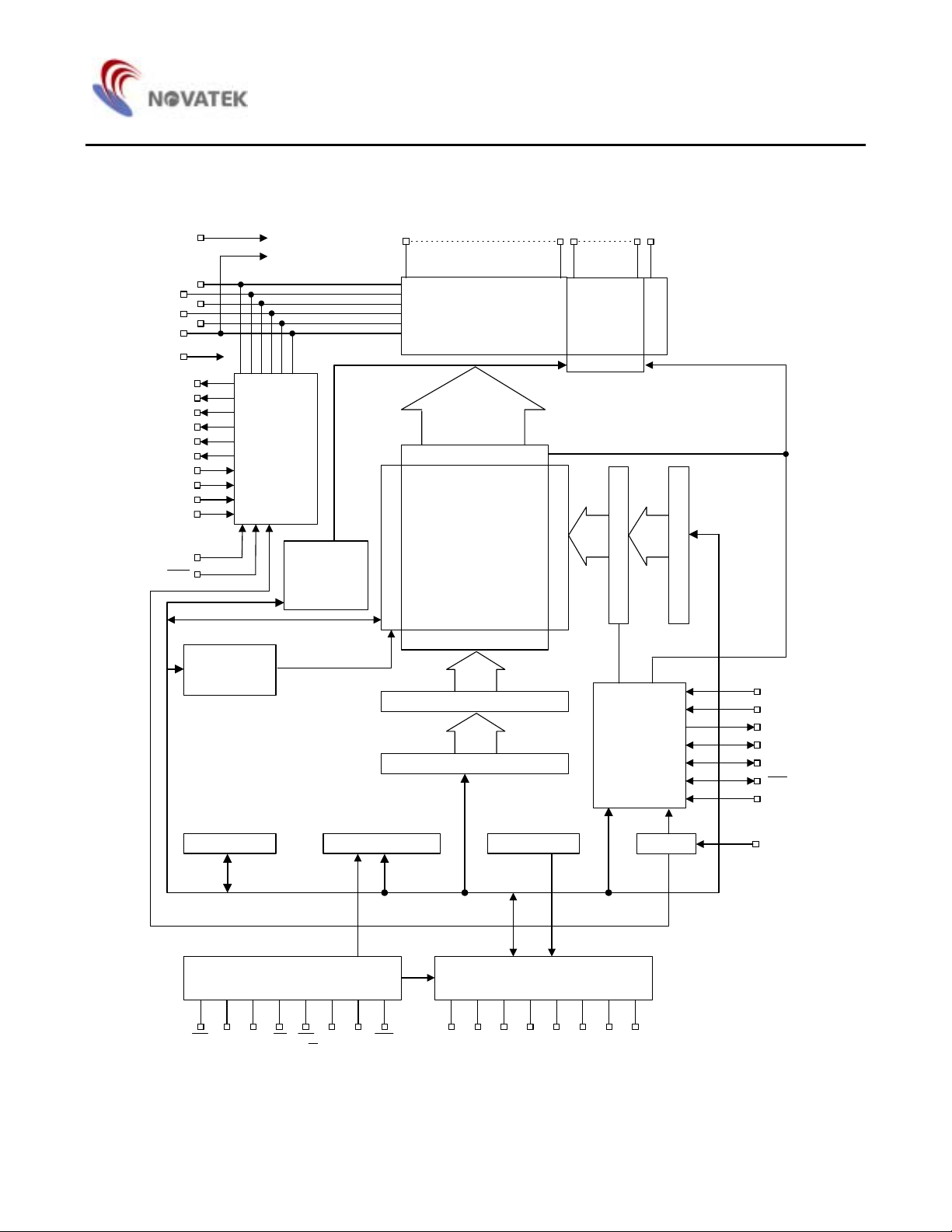

Page 3

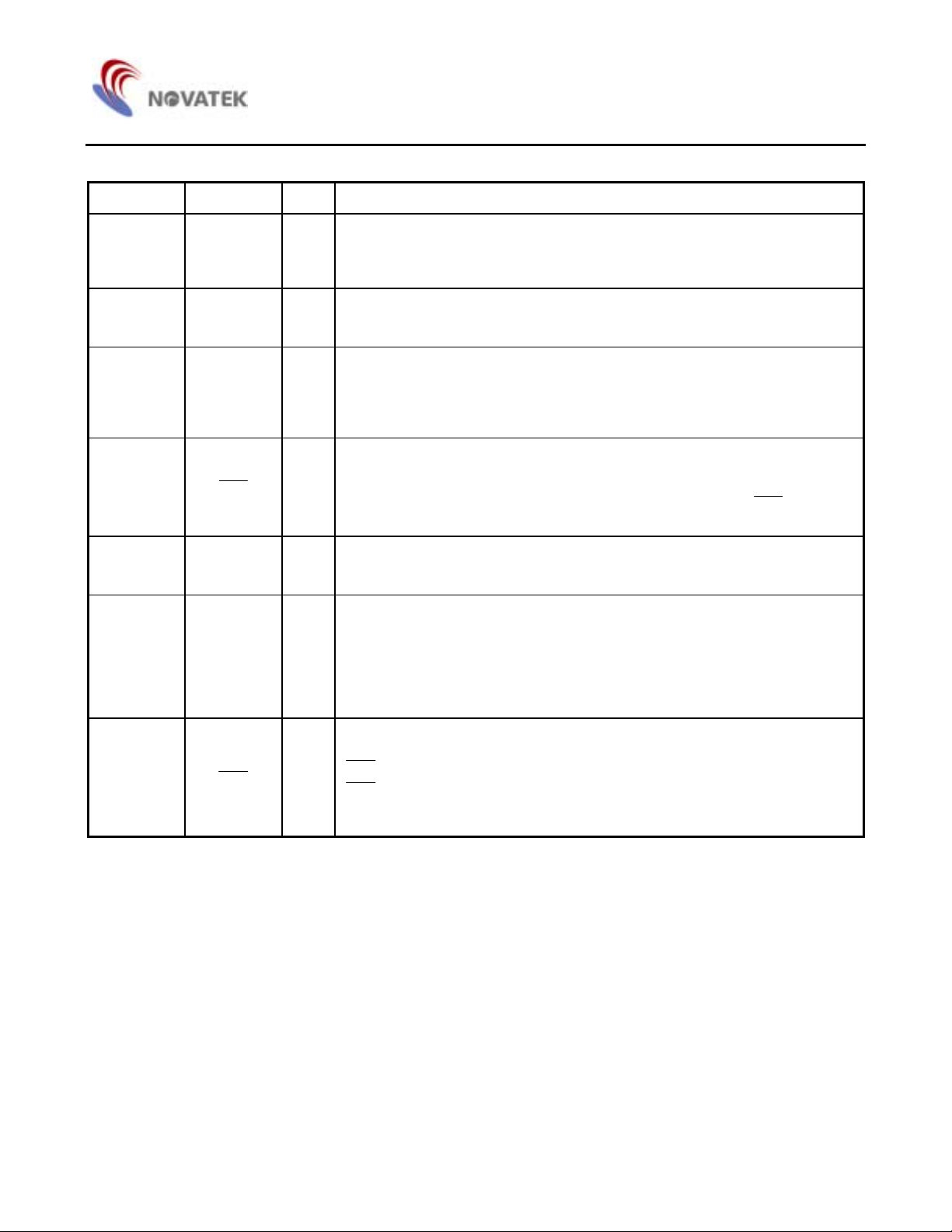

NT7502

Block Diagram

V1

V3

Vss

TMPS

CAP1+

CAP1-

CAP2+

CAP2-

CAP3+

V

DD

V

0

V2

V4

V

EXT

OUT

V

V

DD2

V

R

V

RS

IRS

HPM

Page address

Power Supply

register

Circuit

Output

status

selector

circuit

SEG0

SEG131

Segment driver

Display data latch

132*65-dot

display data RAM

I/O buffer circuit

Column address decoder

8-bit column address counter

8-bit column address counter

COM0 COM63 COMS

Common

driver

Shift register

Line counter

line address decoder

Display timing

generator

circuit

COM S

Initial display line register

DUTY0

DUTY1

FRS

FR

CL

DOF

M/S

Bus holder Command decoder Bus holder

Oscillator

CLS

Microprocessor interface I/O buffer

CS2 A0

RD

(E)

WR

C86 P/S

)W/R(

RES1CS

D7

(SI)

D5 D4 D3 D2 D1 D0

D6

(SCL)

3

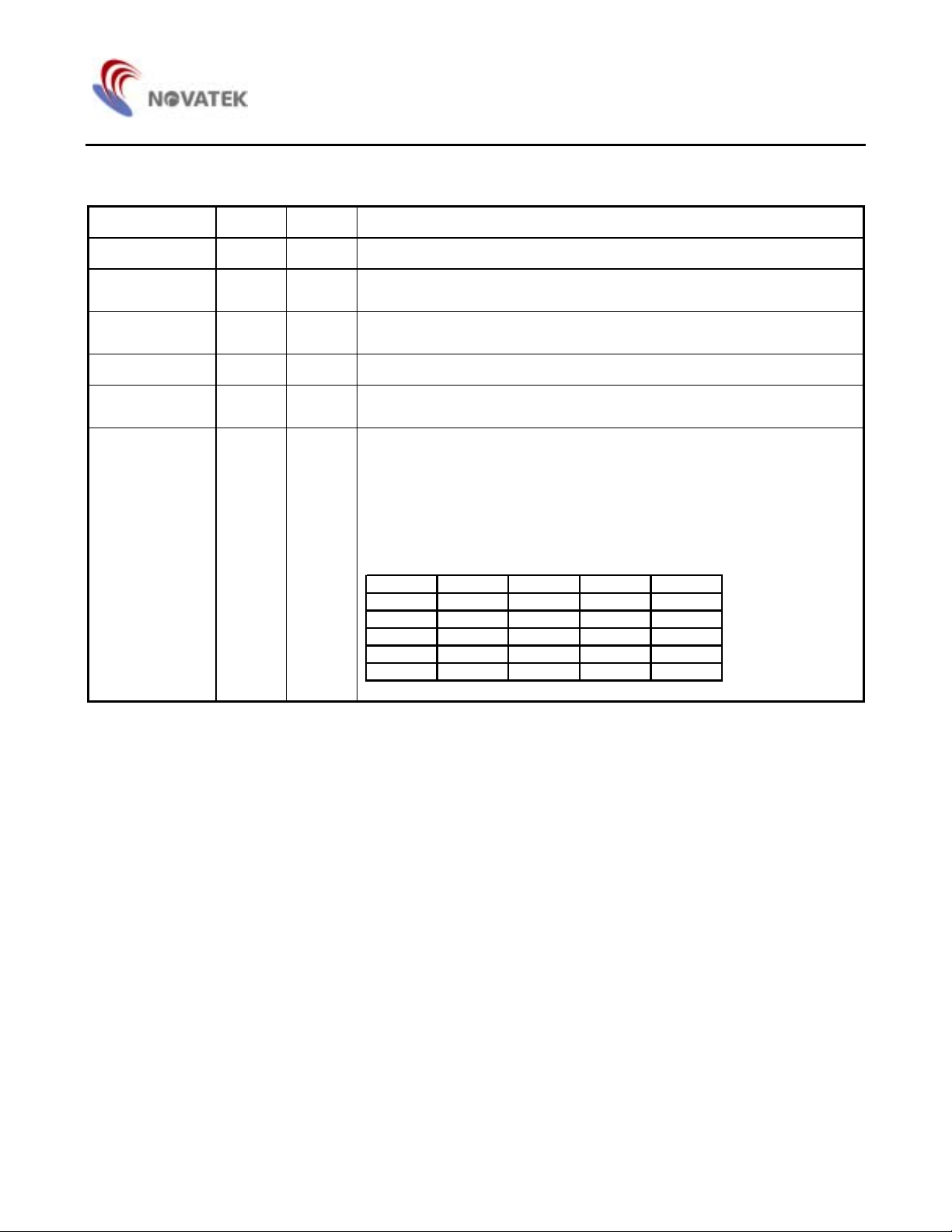

Page 4

NT7502

V1V2V3V

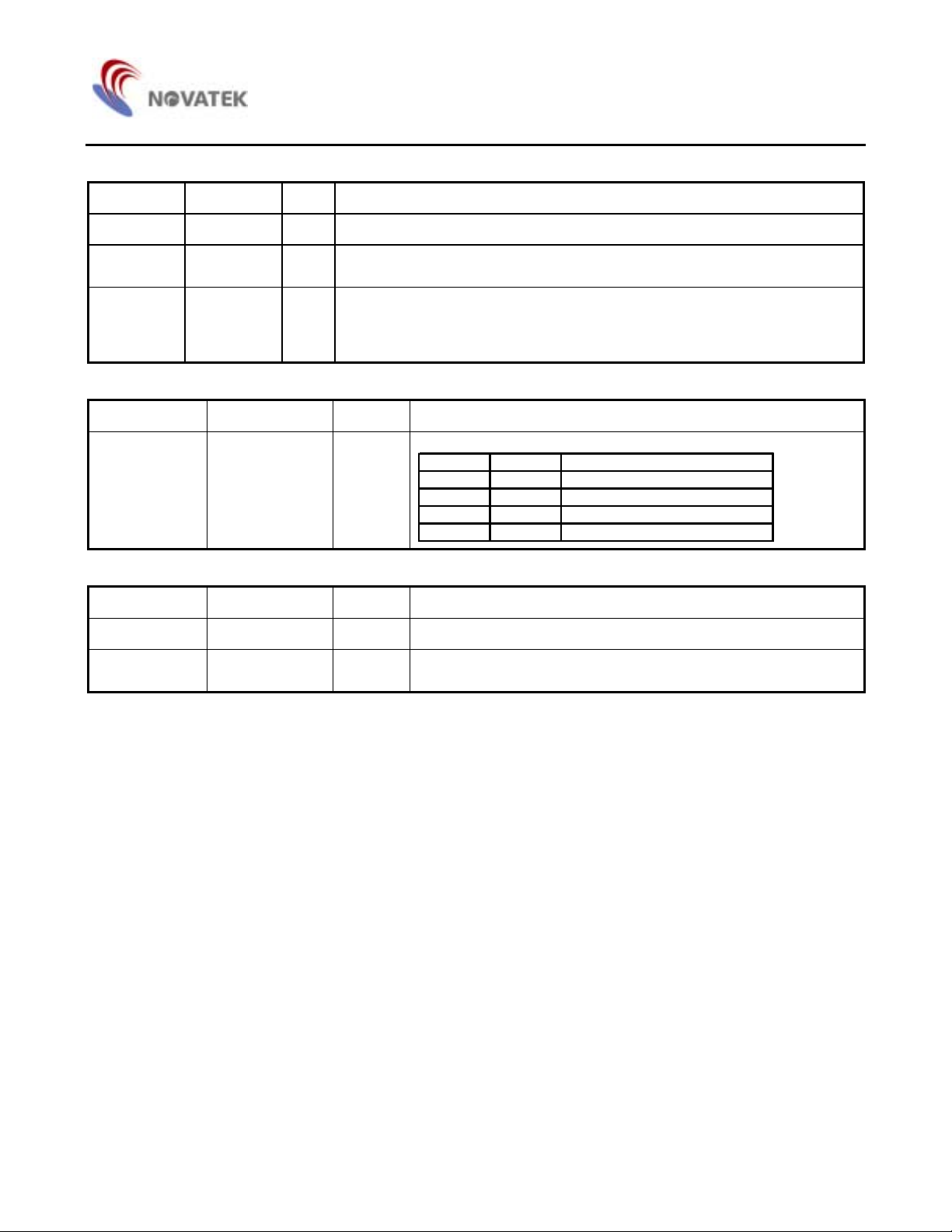

Pad Description

Power Supply

Pad No. Symbol I/O Descriptions

30 - 33 VDD Supply 2.4 - 3.5V power supply input. These pads must be connected each other

10, 16, 26, 53, 71,

77, 81, 91

34 - 36 VDD2 Supply

DD Supply 2.4 - 3.5V power supply output for pad option

V

This is the reference power supply for the step-up voltage circuit for the LCD.

These pads must be connected each other

37 - 40 VSS Supply Ground. These pads must be connected each other

7, 13, 25, 29 , 56,

69 - 70, 74, 79, 83

V

SS Supply Ground output for pad option

LCD driver supply voltages. The voltage determined by LCD cell is

impedance-converted by a resistive driver or an operation amplifier for

application. Voltages should be according to the following relationship:

0 ≥ V1 ≥ V2 ≥ V3 ≥ V4 ≥ VSS

65 - 66

57 - 58

59 - 60

61 - 62

63 - 64

V

V

V2

V3

V4

0

1

Supply

V

When the on-chip operating power circuit is on, the following voltages

are supplied to V

1 to V4 by the on-chip power circuit. Voltage selection is

performed by the Set LCD Bias command.

LCD bias

1/5 bias 4/5V0 3/5V0 2/5V0 1/5V0

1/6 bias 5/6V0 4/6V0 2/6V0 1/6V0

1/7 bias 6/7V0 5/7V0 2/7V0 1/7V0

1/8 bias 7/8V0 6/8V0 2/8V0 1/8V0

1/9 bias 8/9V0 7/9V0 2/9V0 1/9V0

4

4

Page 5

NT7502

LCD Driver Supplies

Pad No. Symbol I/O Descriptions

45 - 46 CAP1- O Capacitor 1- pad for internal DC/DC voltage converter

47 - 48 CAP1+ O Capacitor 1+ pad for internal DC/DC voltage converter

51 - 52 CAP2- O Capacitor 2- pad for internal DC/DC voltage converter

49 - 50 CAP2+ O Capacitor 2+ pad for internal DC/DC voltage converter

43 - 44 CAP3+ O Capacitor 3+ pad for internal DC/DC voltage converter

41 - 42 VOUT O DC/DC voltage converter output

67 - 68 VR I

54 VEXT I

82 TMPS I

55 VRS I

Voltage adjustment pad. Applies voltage between V

0 and VSS using a

resistive divider

This is the external input reference voltage (VREF) for the internal

voltage regulator. It is valid only when external V

EXT must be ≥ 2.4V and ≤ VDD2

V

When using internal V

REF, this pad must be NC

REF is used.

Selects temperature coefficient of the reference voltage

TMPS = 0: -0.05% / °C

TMPS = 1: -0.2 % / °C

Select the internal voltage regulator or external voltage regulator,

VRS = 0: using the external VREF

VRS = 1: using the internal VREF

5

Page 6

NT7502

System Bus Connection Pads

Pad No. Symbol I/O Descriptions

This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit

standard MPU data bus.

When the serial interface is selected (P/S = “L”), then D7 serves as the serial

I/O

data input terminal (SI) and D6 serves as the serial clock input terminal (SCL)

At this time, D0 to D5 are set to high impedance.

17 - 24

D0 - D7

(SI)

(SCL)

When the chip select is inactive, D0 to D7 are set to high impedance.

This is connected to the least significant bit of the normal MPU address bus,

12 A0 I

and it determines whether the data bits are data or a command

A0 = “H” indicating that D0 to D7 are display data, and

A0 = “L” indicating that D0 to D7 are control data.

When

11

RES

I

RES is set to “L”, the settings are initialized.

The reset operation is performed by the

RES signal level.

This is the chip select signal. When

8, 9

1CS CS2

I

select becomes active, and data/command I/O is enabled.

When connected to an 8080 MPU, it is active LOW.

15

RD

(E)

This pad is connected to the

I

data bus is in an output status when this signal is “L”.

When connected to a 6800 Series MPU, this is active HIGH.

This is used as an enable clock input of the 6800 series MPU.

When connected to an 8080 MPU, this is active LOW. This terminal connects

to the 8080 MPU

14

(

WR

W/R )

rising edge of the

I

When connected to a 6800 Series MPU, this is the read/write control signal

input terminal.

When

When

This is the MPU interface switch terminal

75 C86 I

C86 = “H”: 6800 Series MPU interface

C86 = “L”: 8080 MPU interface

This is the parallel data input/serial data input switch terminal

P/S = “H”: Parallel data input

P/S = “L”: Serial data input

The following applies depending on the P/S status:

76 P/S I

P/S Data/Command Data Read/Write Serial Clock

"H" A0 D0 to D7

"L" A0 SI (D7) Write only SCL (D6)

When P/S = “L”, D0 to D5 are HZ. D0 to D5 may be “H”, “L” or Open.

RD(E) and WR ( WR/ ) are fixed to either “H” or “L”. With serial data input,

RAM display data reading is not supported.

1CS = “L” and CS2 = “H”, then the chip

RD signal of the 8080MPU, and the NT7502

WR signal. The signals on the data bus are latched at the

WR signal.

WR/ = “H”: Read

WR/ = “L”: Write

RDWR

Terminal is used to select whether enable or disable the display clock internal

oscillator circuit.

73 CLS I

CLS = “H”: Internal oscillator circuit is enabled

CLS = “L”: Internal oscillator circuit is disabled (requires external input).

When CLS = “L”, input the display clock through the CL pad.

6

Page 7

DOF

This terminal selects the master/slave operation for the NT7502 chips.

Master operation outputs the timing signals that are required for the LCD display,

while slave operation inputs the timing signals required for the liquid crystal display,

synchronizing the liquid crystal display system.

This is the display clock input terminal.

When the NT7502 chips are used in master/slave mode, the various CL

terminals must be connected.

This is the liquid crystal alternating current signal I/O terminal

M/S = “H”: Output.

M/S = “L”: Input.

When the NT7502 chip is used in master/slave mode, the various FR terminals

must be connected.

This is the liquid crystal display blanking control terminal.

M/S = “H”: Output.

M/S = “L”: Input.

I/O

When the NT7502 chip is used in master/slave mode, the various

must be connected.

This is the output terminal for the static drive.

This terminal is only enabled when the static indicator display is ON in

master operation mode, and is used in conjunction with the FR terminal.

DOF terminals

NT7502

System Bus Connection Pads (continue)

Pad No. Symbol I/O Description

72 M/S I

4 CL I/O

3 FR I/O

5

2 FRS O

80 IRS I

78

HPM

This terminal selects the resistors for the V0 voltage level adjustment

IRS = “H”, Use the internal resistors.

IRS = “L”, Do not use the internal resistors.

The V0 voltage level is regulated by an external resistive voltage divider

attached to the VR terminal.

This pad is enabled only when the master operation mode is selected.

It is fixed to either “H” or “L” when the slave operation mode is selected.

This is the power control terminal for the power supply circuit for liquid

crystal drive.

HPM = “H”, Normal mode

I

HPM = “L”, High power mode

This pad is enabled only when the master operation mode is selected.

It is fixed to either “H” or “L” when the slave operation mode is selected.

7

Page 8

NT7502

y

Liquid Crystal Drive Pads

Pad No. Symbol I/O Description

134 - 265 SEG0 - 131 O Segment signal output for LCD display

101 - 132

266 - 297

133, 298 COMS O

Configuration Pads

Pad No. Symbol I/O Description

27, 28 DUTY0, DUTY1 I

Test Pads

Pad No. Symbol I/O Description

90 TEST3 I Test pads, and must be connected to VDD

1, 6, 84 - 89

92 - 100

COM31 - 0

COM32 - 63

NC NC pads, no connection for user

Common signal output for LCD display

O

When in master/slave mode, the same signal is output by both master and slave

These are the COM output terminals for the indicator. Both terminals output the

same signal

No connect these terminals if they are not used

When in master/slave mode, the same signal is output by both master and slave

Select the LCD driver duty

DUTY1 DUTY0 LCD driver dut

0 0 1/33

0 1 1/49

1 0 1/55

1 1 1/65

8

Page 9

NT7502

Functional Description

Microprocessor Interface

Interface type selection

The NT7502 can transfer data via 8-bit bi-directional data bus (D7 to D0) or via serial data input (SI). When high or lo w is

selected for the parity of P/S pad, either 8-bit parallel data input or serial data input can be selected as shown in Table 1. When

serial data input is selected, the RAM data cannot be read out.

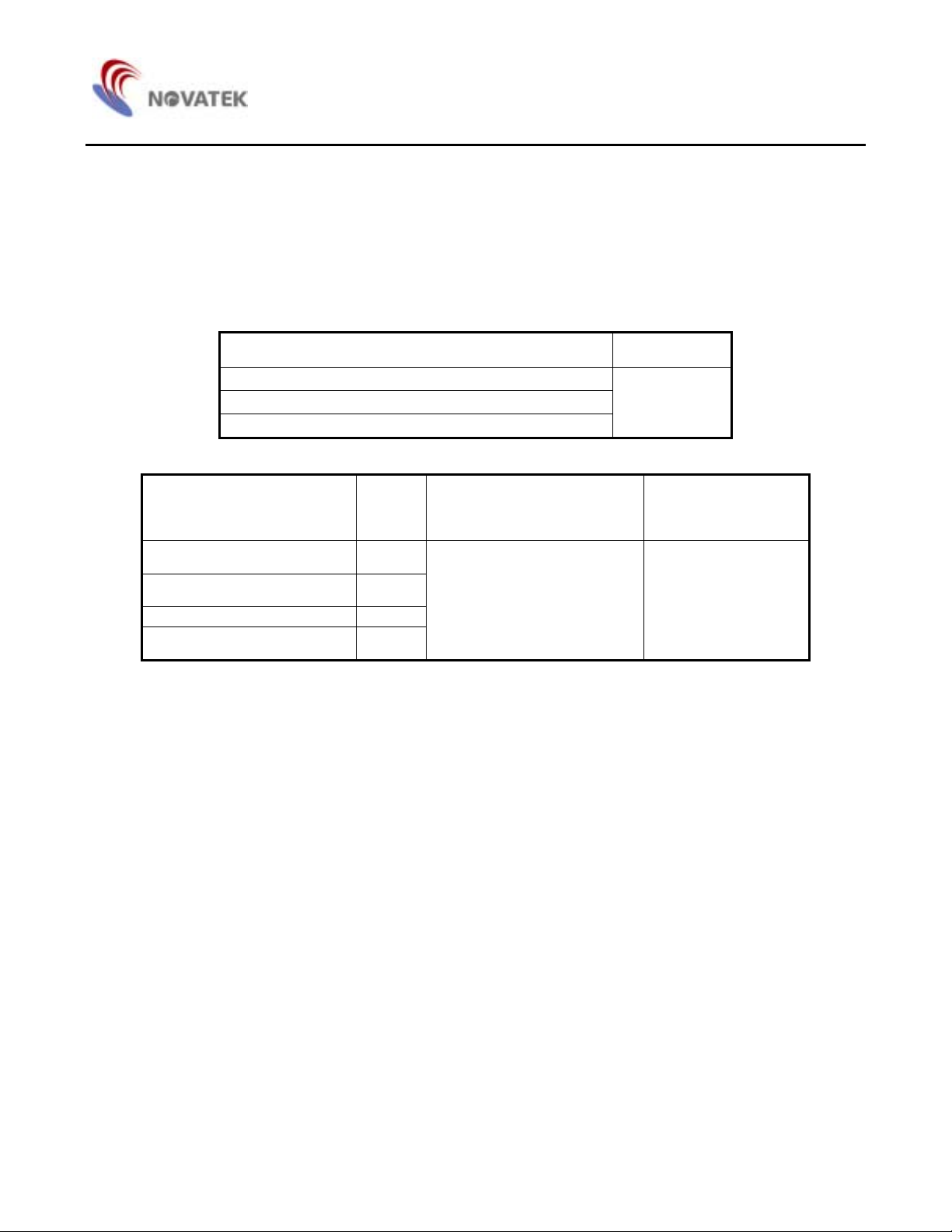

Table. 1

P/S Type

H Parallel Input

L Serial Input

Parallel Input

When the NT7502 selects parallel input (P/S = high), the 8080 series microprocess or or 6800 series microprocessor can be

selected by causing the c86 pad to go high or low as shown in Table 2.

C86 Type

H 6800 microprocessor bus

L 8080 microprocessor bus

Data Bus Signals

The NT7502 identifies the data bus signal according to A0, E,

Common 6800 processor 8080 processor

A0

1 1 0 1 Reads display data

W/R )

(

1CS

1CS

1CS

CS2 A0

CS2 A0

CS2 A0 - - - SI SCL (HZ)

1CS

1CS

1CS

RD WR

CS2 A0

CS2 A0 E

CS2 A0

RD WR

RD WR

Table. 2

WR/ (RD , WR ) signals.

Table. 3

C86 D7 D6 D0 to D5

C86 D7 D6 D0 to D5

“-” Must always be high or low

RD

RD WR

WR D0 to D7

WR/

Function

D0 to D7

D0 to D7

1 0 1 0 Writes display data

0 1 0 1 Reads status

0 0 1 0 Writes control data in internal register. (Command)

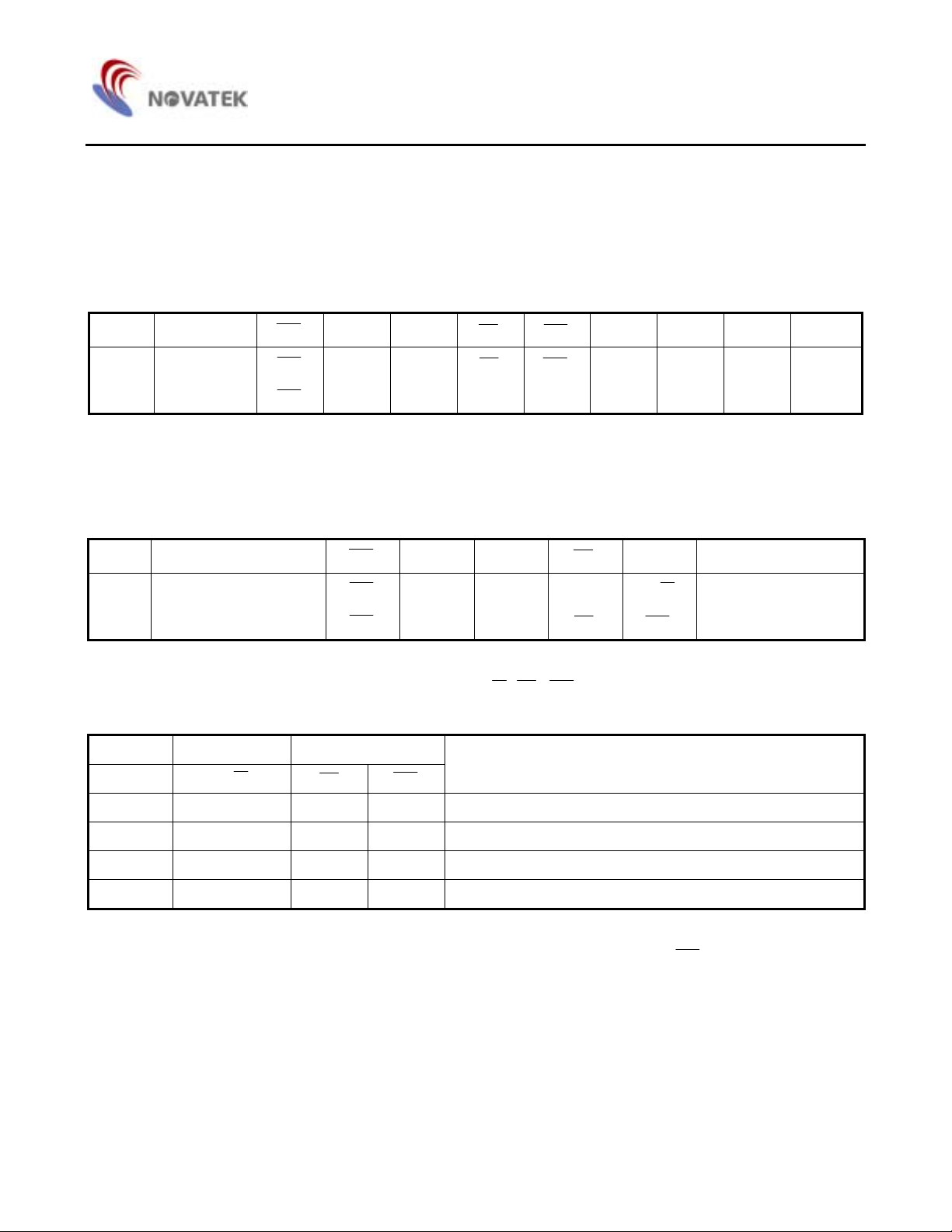

Serial Interface (P/S is low)

When the serial interface has been selected (P/S = “L”), then when the chip is in active state (

serial data input (SI) and the serial clock input (SCL) can be received. The serial data is read from the serial data input pin in the

rising edge of the serial clocks D7, D6 through D0, in this order. This data is converted to 8 bits of parallel data in the rising edge

of eighth serial clock for processing.

The A0 input is used to determine whether or the serial data input is display data, and when A0 = “L” then the data is command

data. The A0 input is read and used for detection every 8th rising edge of the serial clock after the chip becomes active.

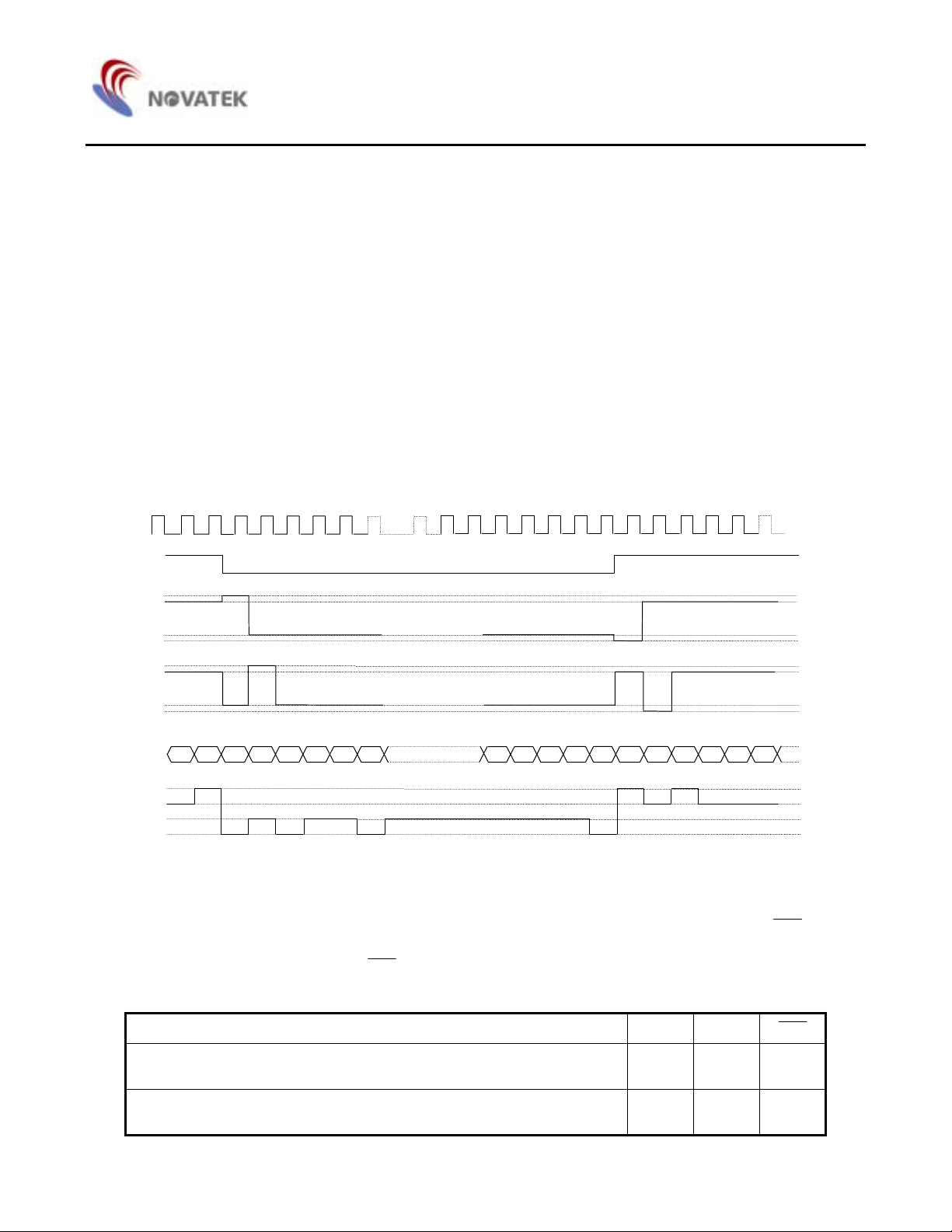

Figure 1 is the serial interface signal chart.

9

1CS = “L” and CS2 = “H”), the

Page 10

NT7502

1CS

CS2

SI

SCL

A0

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2

123456 789101112 13 14

Figure. 1

# When the chip is not active, the shift registers and the counter are reset to their initial states.

# Reading is not possible while in serial interface mode.

# Caution is required on the SCL signal when it comes to line-end reflections and external noise. We recommend the

operation be rechecked on the actual equipment.

Chip Select Inputs

The NT7502 has two chip select pads.

When these pads are set to any other combination, D0 to D7 are high impedance and A0, E and

1CS and CS2 can interface to a microprocessor when 1CS is low and CS2 is high.

WR/ inputs are disabled.

When serial input interface is selected. the shift register and counter are reset.

Access to Display Data RAM and Internal Registers

The NT7502 can perform a series of pipeline processing between LSI’s using the bus holder of the internal data bus in order to

match the operating frequency of display RAM and internal registers with the microprocessor. For example, the microprocessor

reads data from display RAM in the first read (dummy) cycle, stores it in the bus holder, and outputs it onto system bus in the

next data read cycle.

Also, the microprocessor temporarily stores display data in the bus holder, and stores it in display RAM until the next data write

cycle starts.

When viewed from the microprocessor, the NT7502 access speed greatly depends on the cycle time rather than access time to

the display RAM (t

ACC). This view shows the data transfer speed to / from the microprocessor can increase. If the cycle time is

inappropriate, the microprocessor can insert the NOP instruction that is equivalent to the wait cycle setup. However, there is a

restriction in the display RAM read sequence. When an address is set, the specified address data is NOT output at the

immediately following read instruction. The address data is output during the second data read. A single dummy read must be

inserted after address setup and after the write cycle (refer to Figure2).

10

Page 11

NT7502

A0

MPU

Internal

timing

E

R/W

DATA

Address preset

Read signal

Column address

BUS holder

N

Preset

Set address n Dummy read Data Read address n Data Read address n+1

N

N N+1 N+2

N n n+1

n n+1

Incremented

n+2

Figure. 2

Busy Flag

When the busy flag is “1”, it indicates that the NT7502 chip is running internal processes, and at this tim e no command asi de

from a status read will be received. The busy flag is outputted to D7 pad with the read instruction. If the cycle time (t

maintained,

it is not necessary to check for this flag before each command. This makes vast improvements in MPU processing

CYC) is

capabilities possible.

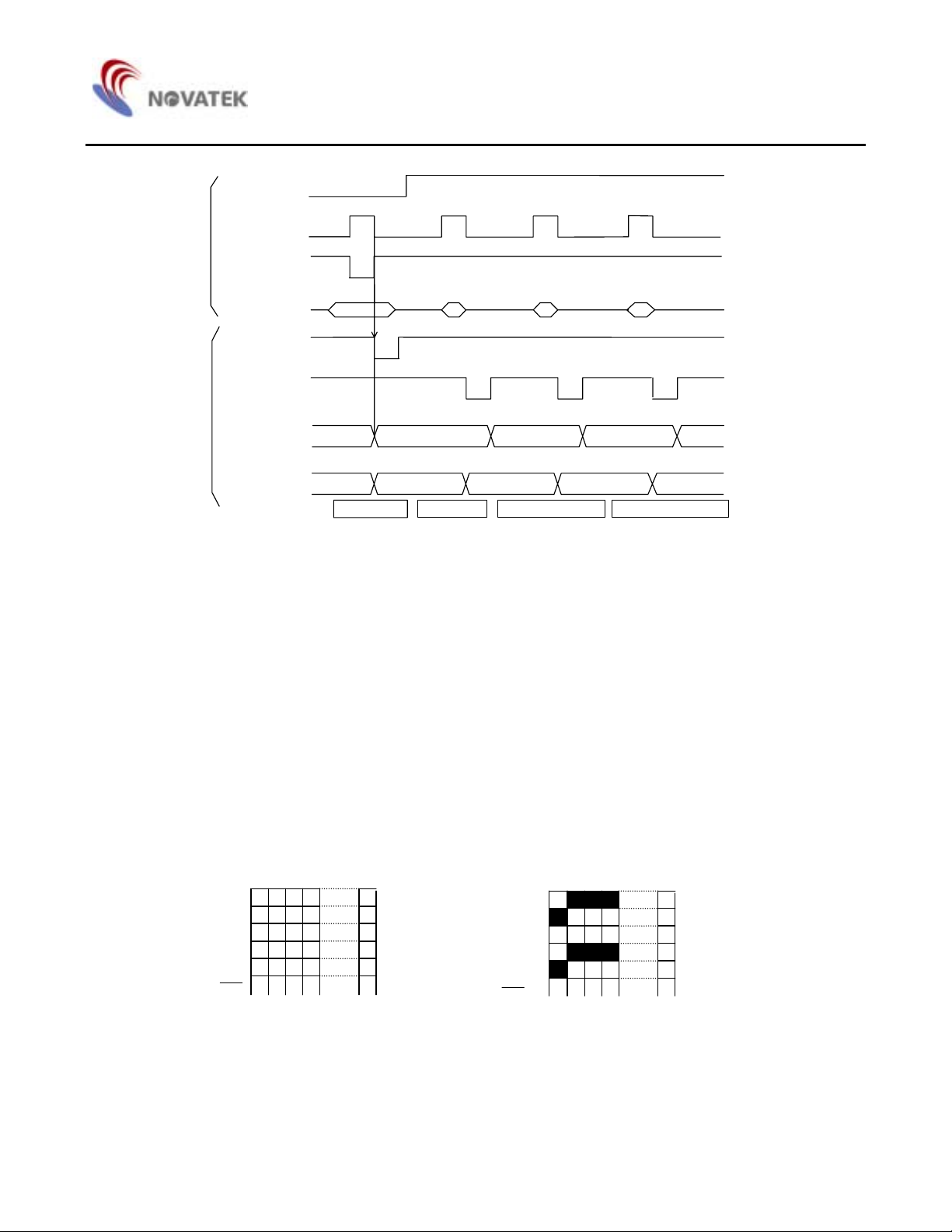

Display Data RAM

Display Data RAM

The display data RAM is RAM that stores the dot data for the display. It has a 65 (8 page * 8 bit+1)*132 bit structure. It is

possible to access the desired bit by specifying the page address and the column ad dress. Because, as is sho wn in Figure3,

the D7 to D0 display data from the MPU corresponds to the liquid crystal display common direction, there are few constraints at

the time of display common direction, and there are few constraints at the time of displa y data transfer when multiple NT7502

chips are used, thus display structures with a high degree of freedom can be created easily .

Moreover, reading from and writing to the display RAM from the MPU side is performed through the I/O buffer, which is an

independent operation from signal reading for the liquid crystal driver. Consequently, even if the display data RAM is accessed

asynchronously during liquid crystal display, it will not cause adverse effects on the displ ay (such as flickering).

D0

D1

D2

D3

D4

111

0

000

1

0000

111

0

000

1

0

0

0

0

0

COM0

COM1

COM2

COM3

COM4

Display data RAM Display on LCD

Figure. 3

11

Page 12

NT7502

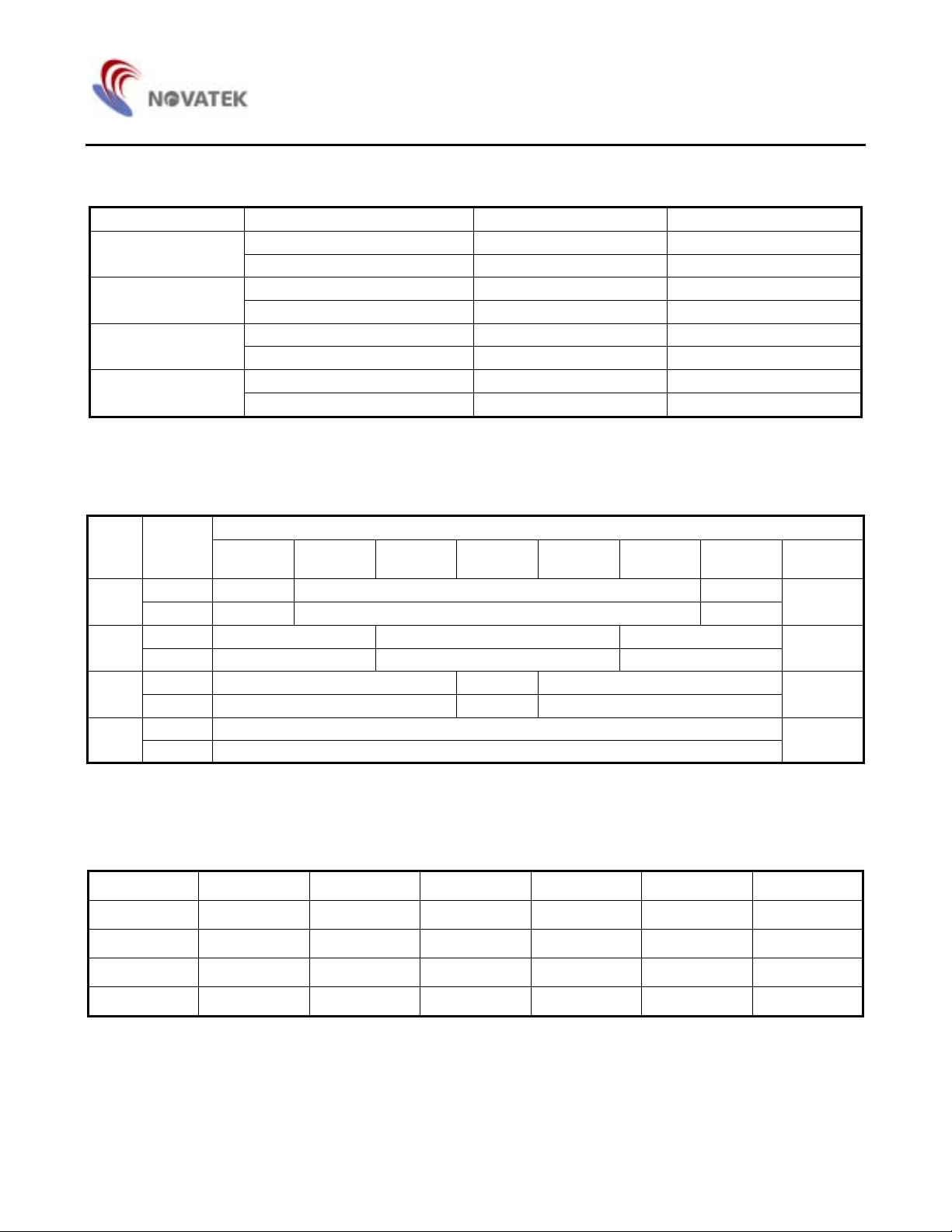

The Page Address Circuit

As shown in Figure 4, page address of the display data RAM is specified through the Page Address Set Command. The page

address must be specified again when changing pages to perform access.

Page address8 (D3, D2, D1, D0 = 1, 0, 0, 0,) is the page for the RAM region used; only display data D0 is used.

The Column Address

As shown in Figure 4, the display data RAM column address is specified by the Column Address Set command. The specified

column address is incremented (+1) with each display data read / write command. This allows the MPU display data to be

accessed continuously. Moreover, the incrimination of column addresses stops with 83H, because the column address is

independent of the page address. Thus, when moving, for exam ple, from page0 column 83H to page 1 column 00H, it is

necessary to respecify both the page address and the column address.

Furthermore, as is shown in Table 4, the ADC command (segment driver direction select command) can be used to reverse the

relationship between the display data RAM column address and the segment output. Because of this, the constraints on the IC

layout can be minimized when the LCD module is assembled.

Table. 4

SEG Output SEG0 SEG131

ADC “0” 0 (H)$ Column Address $83 (H)

(ADC) “1” 83 (H)% Column Address %0 (H)

The Line Address Circuit

The line address circuit, as shown in Table 4, specifies the line address relating to the COM output when the conten ts of the

display data RAM are displayed. Using the display start line address set command, what is normally the top line of the display

can be specified. This is the COM0 output when the common output mode is normal, and the COM63 output for NT7502, when

the common output mode is reversed. The display area is a 65-line area for the NT7502 from the display start line address.

If the line addresses are changed dynamically using the display start line address set command, screen scrolling, page

swapping, etc. can be performed.

12

Page 13

NT7502

Relationship between display data RAM and address. (if initial display line is 1DH)

Page Address Data

D0 00

D1 01

D3, D2,

D1, D0

0, 0, 0, 0

0, 0, 0, 1

0, 0, 1, 0

0, 0, 1, 1

0, 1, 0, 0

0, 1, 0, 1

0, 1, 1, 0

0, 1, 1, 1

1, 0, 0, 0 D0 Page8

Column

D2 02

D3 03

D4 04

D5 05

D6 06

D7 07

D0 08

D1 09

D2 0A

D3 0B

D4 0C

D5 0D

D6 0E

D7

D0 10

D1 11

D2 12

D3 13

D4 14

D5 15

D6 16

D7

D0 18

D1 19

D2 1A

D3 1B

D4 1C

D5 1D

D6 1E

D7

D0 20

D1 21

D2 22

D3 23

D4 24

D5 25

D6 26

D7

D0 28

D1 29

D2 2A

D3 2B

D4 2C

D5 2D

D6 2E

D7

D0 30

D1 31

D2 32

D3 33

D4 34

D5 35

D6 36

D7

D0 38

D1 39

D2 3A

D3 3B

D4 3C

D5 3D

D6 3E

D7

000102

“0”

D0=

ADC

address

D0=

”1”

838281

Page0

Page1

Page2

Page3

Page4

Page5

Page6

Page7

818283

020100

Line

Address

0F

17

1F

27

2F

37

3F

Start

COM

output

COM0

COM1

COM2

COM3

COM4

COM5

COM6

COM7

COM8

COM9

COM10

COM11

COM12

COM13

COM14

COM15

COM16

COM17

COM18

COM19

COM20

COM21

COM22

COM23

COM24

COM25

COM26

COM27

COM28

COM29

COM30

COM31

COM32

COM33

COM34

COM35

COM36

COM37

COM38

COM39

COM40

COM41

COM42

COM43

COM44

COM45

COM46

COM47

COM48

COM49

COM50

COM51

COM52

COM53

COM54

COM55

COM56

COM57

COM58

COM59

COM60

COM61

COM62

COM63

COMS

LCD

OUT

SEG0

SEG1

SEG2

SEG129

SEG130

SEG131

Figure. 4

13

Page 14

NT7502

The Display Data Latch Circuit

The display data latch circuit is a latch that temporarily stores the display data output to the liquid crystal driver circuit from the

display data RAM.

Because the display normal/reverse status, display ON/OFF status, and display all points ON/OFF commands control only the

data within the latch, they do not change the data within the display data RAM itself.

The Oscillator Circuit

This is a CR-type oscillator that produces the display clock. The oscillator circuit is only enabled when M/S = “H” and CLS = “H”.

When CLS = “L” the oscillation stops, and the display clock is input through the CL terminal.

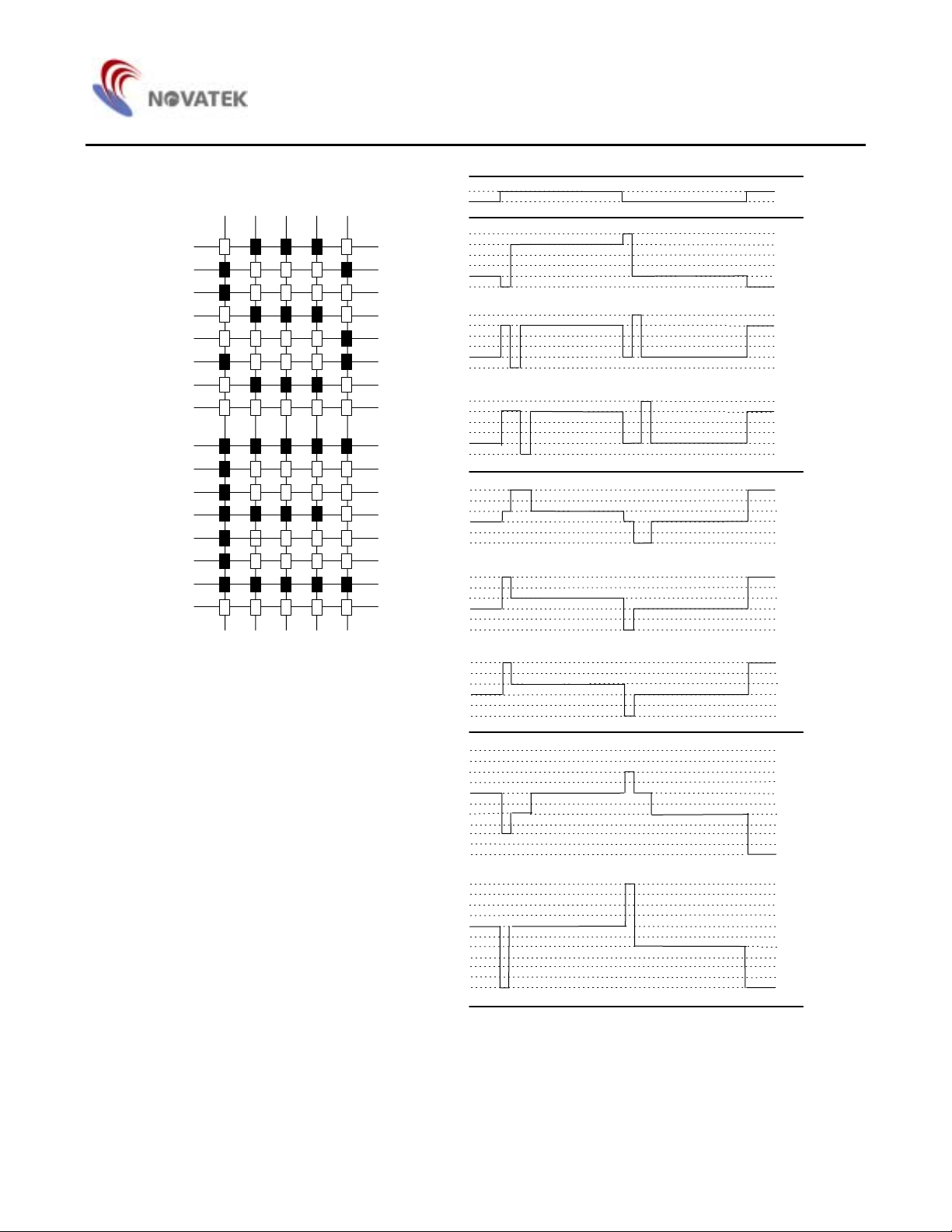

Display Timing Generator Circuit

The display timing generator circuit generates the timing signal to the line address circuit and the display data latch circuit using

the display clock. The display data is latched into the display data latch circuit synchronized with the display clock, and is output

to the data driver output terminal. Reading to the display data liquid crystal driver circuits is completely independent of access to

the display data RAM by the MPU. Consequently, even if the display data RAM is accessed as ynchronously during liquid

crystal display, there is absolutely no adverse effect (such as flickering) on the display.

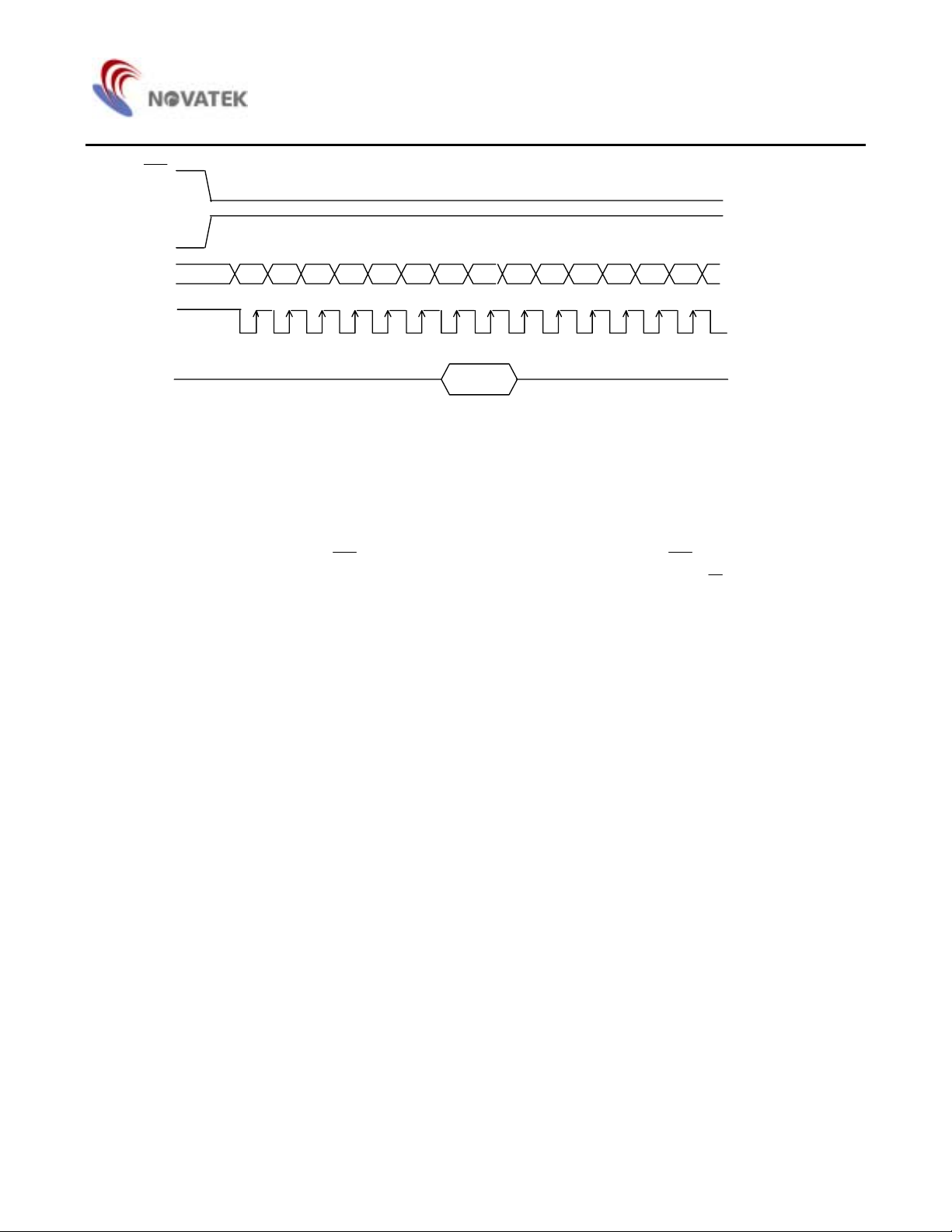

Moreover, the display timing generator circuit generates the common timing and the liquid crystal alternating current signal (FR)

from the display clock. It generates a drive waveform using a 2 frame alternating current drive method, as is shown in Figure 5,

for the liquid crystal drive circuit.

23451 6

CL

FR

61 62 63 64 65

23451

66564

60

V

0

V

V4

V

V

V

V4

V

V

V

V3

V

1

SS

0

1

SS

0

2

SS

COM0

COM1

RAM

data

SEGn

Figure. 5

When multiple NT7502 chips are used, the slave chips must be supplied with the display timing signals (FR, CL, DOF ) from the

master chip[s].

Table 5 shows the status of the FR, CL, and

DOF signals.

Table. 5

Operating Mode FR CL

Master (M/S = “H”) The internal oscillator circuit is enabled (CLS = “H”)

The internal oscillator circuit is disabled (CLS = “L”)

Slave (M/S = “L”) The internal oscillator circuit is disabled (CLS = “H”)

The internal oscillator circuit is disabled (CLS = “L”)

Output

Output

Input

Input

Output

Input

Input

Input

DOF

Output

Output

Input

Input

14

Page 15

NT7502

Table 6 shows the relationship between oscillation frequency and frame frequency

Table. 6

Duty Item f

1/65

1/55

1/49

1/33

On-chip oscillator is used fOSC/6 fCL/(2 X 65)

On-chip oscillator is not used External input f

On-chip oscillator is used fOSC/8 fCL/(2 X 55)

On-chip oscillator is not used External input f

On-chip oscillator is used fOSC/8 fCL/(2 X 49)

On-chip oscillator is not used External input f

On-chip oscillator is used fOSC/12 fCL/(2 X 33)

On-chip oscillator is not used External input f

CL fFR

CL fCL/(2 X 65)

CL fCL/(2 X 55)

CL fCL/(2 X 49)

CL fCL/(2 X 33)

Common Output Control Circuit

This circuit controls the relationship between the number of common output and specified duty ratio. Common output mode

select instruction specifies the scanning direction of the common output pads.

Table. 7

Common output pads

Duty Status

1/33

1/49

1/55

1/65

Normal COM[0-15] NC COM[16-31]

Reverse COM[31-16] NC COM[15-0]

Normal COM[0-23] NC COM[24-47]

Reverse COM[47-24] NC COM[23-0]

Normal COM[0-26] NC COM[27-53]

Reverse COM[53-27] NC COM[26-0]

Normal COM[0-63]

Reverse

COM

[0-15]

COM

[16-23]

COM

[24-26]

COM

[27-36]

COM[63-0]

COM

[37-39]

COM

[40-47]

COM

[48-63]

COMS

COMS

COMS

COMS

COMS

This is a 197-channel multiplexes that generate voltage levels for driving the liquid crystal. The combination of the display data,

the COM scan signal, and the FR signal produces the liquid crystal drive voltage output.

Figure 6 shows example of the SEG and COM output wave form.

Configuration Setting

The NT7502 has two optional configurations, configured b y DUTY0, DUTY1

DUTY1, DUTY0 Common Segment V1 V2 V3 V4

1, 1 65 132 8/9V0, 6/7V0 7/9V0, 5/7V0 2/9V0, 2/7 V0 1/9V0, 1/7V0

1, 0 55 132 7/8V0, 5/6V0 6/8V0, 4/6V0 2/8V0, 2/6 V0 1/8V0, 1/6V0

0, 1 49 132 7/8V0, 5/6V0 6/8V0, 4/6V0 2/8V0, 2/6 V0 1/8V0, 1/6V0

0, 0 33 132 5/6V0, 4/5V0 4/6V0, 3/5V0 2/6 V0, 2/5V0 1/6V0, 1/5V0

15

Page 16

NT7502

COM0

COM1

COM2

COM3

COM4

COM5

V

FR

COM0

COM1

DD

V

SS

V

0

V

1

V

2

V

3

V

4

V

SS

V

0

V

1

V

2

V

3

V

4

V

SS

COM6

V

COM7

COM8

COM2

0

V

1

V

2

V

3

V

4

V

SS

COM9

V

COM10

COM11

COM12

SEG0

0

V

1

V

2

V

3

V

4

V

SS

COM13

V

COM14

COM15

SEG1

0

V

1

V

2

V

3

V

4

V

SS

SEG2

COM0 - SEG0

COM0 - SEG1

Figure. 6

V

0

V

1

V

2

V

3

V

4

V

SS

V

0

V

1

V

2

V

3

V

4

V

SS

-V

4

-V

3

-V

2

-V

1

-V

0

V

0

V

1

V

2

V

3

V

4

V

SS

-V

4

-V

3

-V

2

-V

1

-V

0

16

Page 17

NT7502

The Power Supply Circuit

The power supply circuits are low-power consumption power supply circuits that generate the voltage le vels required for the

liquid crystal drivers. They comprise Booster circuits, voltage regulator circuits, and voltage follower circuits. They are only

enabled in master operation.

The power supply circuits can turn the Booster circuits, the voltage regulator circuits, and the vo ltage follower circuits ON or

OFF independently through the use of the Power Control Set command. Consequently, it is possible to make an external power

supply and the internal power supply function somewhat in parallel. Table 7 shows the Power Control Set Command 3-bit data

control function, and Table 8 shows reference combinations.

Table. 8 The Control Details of Each Bit of the Power Control Set Command

Item

Status

“1” “0”

D2 Booster circuit control bit ON OFF

D1 Voltage regulator circuit (V regulator circuit) control bit ON OFF

D0 Voltage follower circuit (V/F circuit) control bit ON OFF

Table. 9

Step-up

voltage

system

terminal

Use Settings D2 D1 D0

1. Only the internal power supply

is used

2. Only the V regulator circuit and

the V/F circuit are used

Step-up

circuit

Voltage

regulator

circuit

V/F circuit

External

voltage input

1 1 1 O O O V

0 1 1 X O O V

OUT, VDD2 Open

DD2 Used

3. Only the V/F circuit is used 0 0 1 X X O V0, VDD2 Open

4. Only the external power supply

is used

0 0 0 X X X V

0 to V4 Open

*The “step-up system terminals” refer CAP1+, CAP1-, CAP2+, CAP2-and CAP3+.

*While other combinations, not shown above, are also possible, these combinations are not recommended because they have

no practical use.

The Step-up Voltage Circuits

Using the step-up voltage circuits within the NT7502 chips it is possible to product 4X, 3X, 2X step-ups of the V

DD2-VSS voltage

levels

17

Page 18

NT7502

V

= 3V

DD2

SS

V

OUT

CAP3+

CAP1CAP1+

CAP2+

CAP2-

V

= 4 X V

= 3V

= 0V

SS

V

OUT

CAP3+

CAP1CAP1+

CAP2+

CAP2-

DD2

NT7502

= 12V

C1

C1

C1

C1

OUT

V

V

DD2

SS

V

4x step-up voltage relationships 3x step-up voltage relationships 2x step-up voltage relationships

V

C1

C1

C1

OUT

V

V

DD2

SS

= 3 X V

= 0V

Figure. 7

The Voltage Regulator Circuit

The step-up voltage generated at VOUT outputs the liquid

crystal driver voltage V0 through the voltage regulator circuit

Because the NT7502 chips have an internal high-accurac y

fixed voltage power supply with a 64-level electronic volume

function and internal resistors for the V0 voltage regulator,

systems can be constructed without having to include

high-accuracy voltage regulator circuit components.

Moreover, in the NT7502, three types of thermal gradients

have been prepared as VREG options: (1)

approximately –0.05%/℃ (2) approximately –0.2%/℃, and

(3) external input (supplied to the V

EXT terminal).

V0 = ( 1+Rb/Ra)*V

EV = ( 1+Rb/Ra)* (1-(63-α)/162)*VREG (Equation A-1)

SS

V

V

OUT

CAP3+

CAP1CAP1+

CAP2+

CAP2-

2x step-up voltage circuit3x step-up voltage circuit4x step-up voltage circuit

DD2

= 6V

NT7502

= 9V

NT7502

C1

C1

OUT

= 2 X V

V

V

DD2

= 3V

SS

= 0V

V

When the V0 Voltage Regulator Internal Resistors Are

Used

Through the use of the V0 voltage regulator internal resistors

and the electronic volume function the liquid crystal power

supply voltage V0 can be controlled by commands alone

(without adding any external resistors), making it possible to

adjust the liquid crystal display brightness. The V0 voltage

can be calculated using equation A-1 over the range where

TOUV0V < .

R

b

V

out

-

+

R

a

V

EV

V

o

VEV (constant voltage

supply + electronic volume)

V

ss

18

Page 19

NT7502

V

REG is the IC internal fixed voltage supply, and its voltage at Ta = 25℃ is as shown in Table 10.

Table. 10

Equipment Type TMPS VRS Thermal Gradient Units VREG

Internal power Supply 0 1 -0.05

Internal power Supply 1 1 -0.2

%/

%/

℃

2.1

2.1

℃

External input * 0 - - VEXT

α is set to 1 level of 64 possible levels by the electronic volume function depending on the data set in the 6-bit electronic volume

register. Table 10 shows the value for α depending on the electronic volume register settings. Ra/Rb is the V0 voltage regulator

internal resistor ratio, and can be set to 8 different levels through the V0 voltage regulator internal resistor ratio set command.

The (1+Rb/Ra) ratio assumes the values shown in Table11 depending on the 3-bit data settings in the V0 voltage regulator

internal resistor ratio register.

Table. 11

D5 D4 D3 D2 D1 D0

α

V0

0 0 0 0 0 0 0 Minimum

0 0 0 0 0 1 1 :

0 0 0 0 1 0 2 :

: : : :

1 0 0 0 0 0 32 (default) :

: : : :

1 1 1 1 1 0 62 :

1 1 1 1 1 1 63 Maximum

V0 voltage regulator internal resistance ratio register value and (1+ Rb/Ra) ratio (Reference value)

Table. 12

Register

Equipment Type by Thermal Gradient [Units:%/

D2 D1 D0 1. -0.05 2. -0.2 3. VREG External Input

0 0 0 3.0 3.0 1.5

0 0 1 3.5 3.5 2.0

0 1 0 4.0 4.0 2.5

0 1 1 4.5 4.5 3.0

1 0 0 5.0 5.0 3.5

1 0 1 5.5 5.5 4.0

1 1 0 6.0 6.0 4.5

1 1 1 6.4 6.4 5.0

℃]

19

Page 20

NT7502

The V0 voltage is a function of the V0 voltage regulator internal resistor ratio register and the electronic volumn register.

Setup example: When selecting T

a = 25℃ and V0 = 7V for an NT7502 model on which the temperature gradient = -0.05%℃,

using the equation A-1, the following setup is enabled.

Table. 13

Contents

D5 D4 D3 D2 D1 D0

Register

For V0 voltage regulator - - - 0 1 0

Electronic Volume 1 0 0 1 0 1

# When the V0 voltage regulator internal resistors or the elect ronic volume funct ion is used, it is necessar y to at least set the

voltage regulator circuit and the voltage follower circuit to an operating mode using the power control set commands.

Moreover, it is necessary to provide a voltage from VOUT when the Booster circuit is OFF.

# The VR terminal is enabled only when the V0 voltag e regulator internal resistors are not used (i. e. the IRS terminal = “L”).

When the V0 voltage regulator internal resistors are used (i.e. when the IRS ternimal = “H”), then the VR terminal is left open.

# Because the input impedance of the VR terminal is high, it is necessary to take into consideration short leads, shield cables,

etc. to handle noise.

The Liquid Crystal Voltage Generator Circuit

The V0 voltage is produced by a resistive voltage divider within the IC, and can be produced at the V1, V2, V3, and V4 voltage

levels required for liquid crystal driving. Moreover, when the voltage follower chan ges the impedance, it provides V1, V2,V3 ,

and V4 to the liquid crystal drive circuit. 1/9 bias or 1/ 7 bias for NT7502 can be selected.

High Power Mode

The power supply circuit equipped in the NT7502 chips has very low power consumption (normal mode: HPM = “H”). However

for LCDs or panels with large loads, this low-power power supply may cause disp lay quality to degrade. When this occurs,

setting the

HPM terminal to “L” (high power mode) can improve the quality of the dis pla y. We recommend t h at t he dis play b e

checked on actual equipment to determine whether or n ot to use this mode.

Moreover, if the improvement to the display is inadequate even after high power mode has been set, then it is necessary to add

a Command Sequence when Built-in Power Supply is turned OFF.

Follow the command sequence as shown below to turn off the built-in power supply after the system enters standby mode.

20

Page 21

NT7502

Reference Power Supply Circuit for Driving LCD Panel

-When using all LCD power circuits

(Voltage converter regulator and follower)

(In case of 3X boosting circuit)

V

DD

V

C3+

C2+

C2C1+

C1-

VR

V0

V1

V2

V3

V4

M/S

OUT

C1

C1

C1

Ra

C2

C2

C2

C2

C2

V

SS

Rb

When only using voltage follower

V

DD

-When not using voltage booster circuits

V

DD

V

C3+

C2+

C2C1+

C1-

VR

V0

V1

V2

V3

V4

M/S

OUT

V

SS

External

Power

Supply

Ra

C2

C2

C2

C2

C2

Rb

When not using internal LCD power supply circuits

V

DD

V

SS

External

Power

Supply

C2

C2

C2

C2

C2

V

C3+

C2+

C2C1+

C1-

VR

V0

V1

V2

V3

V4

OUT

M/S

*Value of External Capacitance

Item Value

C1

1.0 - 4.7

C2

0.47 - 2.2

µ

F

External

Power

Supply

V

SS

V

C3+

C2+

C2C1+

C1-

VR

V0

V1

V2

V3

V4

M/S

OUT

21

Page 22

NT7502

Reset Circuit

When the RES input falls to “L”, these LSI reenter their default state. The def ault settings are shown below:

1. Display OFF

2. Normal display

3. ADC select: Normal display (ADC command D0 = “L”)

4. Power control register (D2, D1, D0) = (0, 0, 0,)

5. Register data clear in serial interface

6. LCD power supply bias ratio 1/9 (1/65 duty), 1/8 (1/55, 1/ 49 duty), 1/6 (1/33 duty)

7. Read modify write OFF

8. Static indicator: OFF

Static indicator register: (D1, D2) = (0, 0)

9. Display start line register set at first line

10. Column address counter set at address0

11. Page address register set at page 0

12. Common output status normal

13. V0 voltage regulator internal power supply ratio set mode clear:

V0 voltage regulator internal resistor ratio register: (D2, D1, D0) = (1, 0, 0)

14. Electronic volume register set mode clear

Electronic volume register: (D5, D4, D3, D2, D1, D0) = (1, 0, 0, 0, 0, 0,)

15. Test mode clear

16. All-indicator-lamps-on OFF (All-indicator-lamps ON/OFF command D0 = “L”)

17. Output condition of COM, SEG

COM: V1

SEG: V2

On the other hand, when the reset command is used, only default settings 7 to 15 above are put into effect.

The MPU interface (Reference Example)”, the RES terminal is connected to the MPU reset terminal, making the chip

reinitialize simultaneously with the MPU. At the time of power up, it is necessary to reinitialize using the

Moreover, when the control signal from the MPU is in a high impedance state, there may be an overcurrent condition; therefore,

take measures to prevent the input terminal from entering a high impedance state.

In the NT7502, if the internal liquid crystal power supply circuit is not used, then it is necessary to apply a “L” signal to the

terminal when the external liquid crystal power supply is applied.

Even though the oscillator circuit operates while the RES terminal is “L,” the display timing generator circuit is stopped, and the

FR, FRS, and

There is no influence on the D0 to D7 terminals.

DOF terminals are fixed to “H,” and the CL pin is fixed to “H” only when the intermal oscillator circuit is used.

RES terminal.

RES

22

Page 23

NT7502

Commands

The NT7502 uses a combination of A0, RD(E) and WR ( WR/ ) signals to identify data bus signals. As the chip analyzes and

executes each command using internal timing clock only regardless of external clock, its processing speed is very high and its

busy check is usually not required. The 8080 series microprocessor interface enters a read status when a low pulse is input to

RD pad and a write status when a low pulse is input to the WR pad. The 6800 series microprocessor interface enters a

the

read status when a high pulse is input to the

pulse is input to the E pad, the command i s activated. (For timing, see AC Characteristics.). Accordingly, in t he command

explanation and command table, RD (E) becomes 1(high) when the 6800 series microprocessor interface reads status of

display data. This is the only different point from the 8080 series microprocessor interface.

Taking the 8080 series microprocessor interface as an example, commands are e xp lained below.

When the serial interface is selected, input data starting f r om D7 in sequence.

Command Set

1. Display ON/OFF

Alternatively turns the display on and off.

W/R pad and a write status when a low pulse is input to this pad. When a high

E

A0

RD

0 1 0 1 0 1 0 1 1 1 1 Display ON

0Display OFF

When the display OFF command is executed when in the display all points ON mode, power save mode is entered. See the

section on the power saver for details.

2. Set Display Start Line

Specifies line address (refer to Figure 4) to determine the initial display li ne, or COM0. T he RAM display data bec omes the

top line of LCD screen. It is followed by the higher number of lines in ascending order, corresponding to the duty cycle. When

this command changes the line address, smooth scrolling or a page change takes place.

E

A0

RD

0 1 0 0 1 A5 A4 A3 A2 A1 A0

A5 A4 A3 A2 A1 A0 Line address

0 0 0 0 0 0 0

0 0 0 0 0 1 1

0 0 0 0 1 0 2

1 1 1 1 1 0 62

1 1 1 1 1 1 63

WR/

D7 D6 D5 D4 D3 D2 D1 D0 Setting

WR

WR/

D7 D6 D5 D4 D3 D2 D1 D0

WR

: :

% High-order bit

23

Page 24

NT7502

3. Set Page Address

Specifies page address to load display RAM data to page address register. Any RAM data bit can be accessed when its page

address and column address are specified. The display remains unchanged even when the page address is changed. Page

address 8 is the display RAM area dedicated to the indicator, and only D0 is valid for data change.

E

A0

RD

0 1 0 1 0 1 1 A3 A2 A1 A0

A3 A2 A1 A0 Page address

0 0 0 0 0

0 0 0 1 1

0 0 1 0 2

0 0 1 1 3

0 1 0 0 4

0 1 0 1 5

0 1 1 0 6

0 1 1 1 7

1 0 0 0 8

4. Set Column Address

Specifies column address of display RAM. Divide the column addr ess into 4 higher bit s and 4 lower bits. Set each of them

succession. When the microprocessor repeats to access the display RAM, the column address counter is incremental by

during each access until address 132 is accessed. The page address is not changed during this time.

Higher bits 0 1 0 0 0 0 1 A7 A6 A5 A4

Lower bits 0 1 0 0 0 0 0 A3 A2 A1 A0

A7 A6 A5 A4 A3 A2 A1 A0 Line address

0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1 1

1 0 0 0 0 0 1 1 131

WR/

D7 D6 D5 D4 D3 D2 D1 D0

WR

A0

E

RD

WR/

D7 D6 D5 D4 D3 D2 D1 D0

WR

: :

24

Page 25

NT7502

5. Read Status

E

A0

RD

0 0 1 BUSY ADC ON/OFF RESET 0 0 0 0

Busy: When high, the NT7502 is busy due to internal operation or reset. Any command is rejected until BUSY goes low.

ADC: Indicates the relationship between RAM column address and segment drivers. When low, the displa y is reversed

ON/OFF: Indicates whether the display is on or off. When low, the display turns on. When high, the display turns off. This is

RESET: Indicates the initialization is in progress by

6. Write Display Data

Write 8-bit data in display RAM. As the column address aut omatically i ncrements b y 1 aft er each write, the microproc essor

can continue to write data of multiple words.

E

A0

RD

1 1 0 Write data

7. Read Display Data

Reads 8-bit data from display RAM area specified by column address and page address. As the column address

automatically increments by 1 after each write, the microprocessor can continue to read dat a of multiple words. A single

dummy read is required immediately after column address setup. Refer to the display RAM section of FUNCTIONAL

DESCRIPTION for details. Note that no display data can be read via the serial interface.

WR/

WR

The busy check is not required if enough time is provided for each cycle.

and column address “131-n” corresponds to segment driver n. When high, the displa y is normal and colum n

address corresponds to segment driver n.

the opposite of Display ON/OFF command

high, the chip is being reset.

WR

D7 D6 D5 D4 D3 D2 D1 D0

RES signal or by reset command. When lo w, the displa y is o n. W hen

WR/

D7 D6 D5 D4 D3 D2 D1 D0

A0

RD WR

1 0 1 Read data

8. ADC Select

Changes the relationship between RAM column address and segm ent dri ver. The order of segm ent driver out put pad s can

be reversed by software. This allows flexible IC layout during LCD module assembly. For details, refer to the column address

section of Figure 4. When display data is writt en or read, the column address is incremented by 1 as shown in Figure 4.

E

A0

RD

0 1 0 1 0 1 0 0 0 0 D

When D is low, rotation is to the right (normal direction)

When D is high, rotation is to the left (reverse direction)

9. Normal/ Reverse Display

Reverses the Display ON/OFF status without rewriting the content s of the display data RAM.

E

A0

RD

0 1 0 1 0 1 0 0 1 1 D

When D is low, the RAM data is high, with LCD ON potential (normal displa y)

When D is high, the RAM data is low, with LCD ON potential (reverse display)

D7 D6 D5 D4 D3 D2 D1 D0

WR/

D7 D6 D5 D4 D3 D2 D1 D0

WR

WR/

D7 D6 D5 D4 D3 D2 D1 D0

WR

25

Page 26

NT7502

10. Entire Display ON

Forcibly turns the entire display on regardless of the contents of the display data RAM. At t his time, the contents of the

display data RAM are held.

This command has priority over the Normal/Reverse Display command. When D is low, the normal display status is

provided.

E

WR/

A0

RD

D7 D6 D5 D4 D3 D2 D1 D0

WR

0 1 0 1 0 1 0 0 1 0 D

When D is high, the entire display ON status is provided. If the Entire Display ON command is executed in the display OFF

status, the LCD panel enters Power Save mode. Refer to the Power Save section for det ails.

11. Set LCD Bias

This command selects the voltage bias ratio required for the liquid crystal display.

A0

E

RD

WR/

D7 D6 D5 D4 D3 D2 D1 D0

WR

1/33 1/49 1/55 1/65

Duty

0 1 0 1 0 1 0 0 0 1 0 1/6 bias 1/8 bias 1/8 bias 1/9 bias

1 1/5 bias 1/6 bias 1/6 bias 1/7 bias

12. Read-Modify-Write

A pair of Read-Modify-Write and End commands must always be used. Once Read-Modify-Write is issued, column address

is not incremental by Read Display Data command but incremental by Write Display Data command only. It continues until

End command is issued. When the End is issued, column address returns to the address when Read-Modify-Write is

issued. This can reduce the microprocessor load when data of a specific display area is repeatedly changed during cursor

blinking or other events.

E

A0

RD

WR/

D7 D6 D5 D4 D3 D2 D1 D0

WR

0 1 0 1 1 1 0 0 0 0 0

Note: Any command except Read/Write Display Data and Set Column Address can be issued during Re ad-Modify-Write

mode.

Cursor display sequence

Set Page Address

Set Column Address

Read-Modify-Write

Dummy Read

No Data process

Read Data

Write Data

Completed?

Yes

End

26

Page 27

NT7502

13. End

Cancels Read-Modify-Write mode and returns column address to the original address (when Read-Modify-Write is issued)

E

WR/

A0

RD

D7 D6 D5 D4 D3 D2 D1 D0

WR

0 1 0 1 1 1 0 1 1 1 0

Return

Column address

N N+1 N+2 N+3 N+m N

Read-Modify-Write

mode is selected

End

14. Reset

This command resets the Display Start Line register, Column Address counter, Page Address register, and Common output

mode register, the V0 voltage regulator internal resistor ratio register, the Electronic Volume register, the static indicator

mode register, the read-modify-write mode register, and the test mode. The Reset command does not affect on the

contents of display RAM. Refer to the Reset circuit section of Function Description.

E

WR/

A0

RD

D7 D6 D5 D4 D3 D2 D1 D0

WR

0 1 0 1 1 1 0 0 0 1 0

The Reset command cannot initialize LCD power supply. Only the Reset signal to the RES pad can initialize the supplies.

15. Output Status Select Register

Applicable to the NT7502. When D is hig h or lo w, the sc an direct io n of t he COM out put p ad is s electa ble. Refer t o Out put

Status Selector Circuit in Function Description for details.

E

WR/

A0

RD

D7 D6 D5 D4 D3 D2 D1 D0

WR

0 1 0 1 1 0 0 D * * *

D: Selects the scan direction of COM output pad

D = 0: Normal (COM0 → COM63/53/47/31)

D = 1: Reverse (COM63/53/47/31 → COM0)

*: Invalid bit

16. Set Power Control

Selects one of eight power circuit functions using 3-bit register. An external power supply and part of on-chip power circuit

can be used simultaneously. Refer to Power Supply Circuit section of FUNCTIONAL DESCRIPTION for details.

E

WR/

A0

RD

D7 D6 D5 D4 D3 D2 D1 D0

WR

0 1 0 0 0 1 0 1 A2 A1 A0

When A0 goes low, voltage follower turns off. When A0 goes high, it turns on.

When A1 goes low, voltage regulator turns off. When A1 goes high, it turns on.

When A2 goes low, voltage booster turns off. When A2 goes high, it turns on.

27

Page 28

NT7502

17. V0 Voltage Regulator Internal Resistor Ratio Set

This command sets the V0 voltage regulator internal resistor ratio. For details, see explanation under “T he Power Supply

Circuits”.

E

A0

RD

WR/

D7 D6 D5 D4 D3 D2 D1 D0 Rb / Ra Ratio

WR

0 1 0 0 01 0 0000 Small

001

010

: :

110

111 Large

18. The Electronic Volume (Double Byte Command)

This command makes it possible to adjust the brightness of the liquid crystal disp lay by controlling the liquid cr ystal drive

voltage V0 through the output from the voltage regulator circuits of the internal liquid crystal power supply.

This command is a two-byte command used as a pair with the e lectronic volume mode set command an d the electronic

volume register set command, and both commands must be issued one after the other.

! The Electronic Volume Mode Set

When this command is input, the electronic volume register set command is enabled. Once the electronic volume mode has

been set, no other command except the electr onic volume register command can be used. Once the e lectronic volume

register set command has been used to set data into the register, then t he electronic volume mode is released.

E

WR/

A0

RD

D7 D6 D5 D4 D3 D2 D1 D0

WR

0 1 0 1 0 0 0 0 0 0 1

! Electronic Volume Register Set

By using this command to set six bits of data to the electronic volume register, the liquid crystal voltage V

0 assumes one of

the 64 voltage levels.

When this command is input, the electronic volume mode is released after the electronic volume register has been set.

E

WR/

A0

RD

D7 D6 D5 D4 D3 D2 D1 D0 V0

WR

0 1 0 * * 0 0 0000 Small

0 1 0 * * 0 0 0010

0 1 0 * * 0 0 0011

0 1 0 * * : :

0 1 0 * * 1 1 1110

0 1 0 * * 1 1 1111 Large

When the electronic volume function is not used, set D5 - D0 to 100000.

28

Page 29

NT7502

19. Static Indicator (Double Byte Command)

This command controls the static drive system indicator display. The static indicator display is controlled by this command

only, and is independent of other display co ntrol commands.

This is used when one of the static indicator liquid crystal drive electrodes is connected to the FR terminal, and the other is

connected to the FRS terminal. A different pattern is reco mmended for the static indicator electrodes rat her than for the

dynamic drive electrodes. If the pattern is too close, it can r esu lt in deterioration of the liquid crystal and of the electrodes.

The static indicator ON command is a double-byte command paired with the static indicator register set command, and thus

command must be executed one after the other. (The static indicator OFF command is a single byte command.)

! Static Indicator ON/OFF

When the static indicator ON command is entered, the static indicator register set command is enabl ed. Once the static

indicator ON command has been entered, no other command aside from the static indicator register set command can be

used. This mode is cleared when data is set in the register by the static indicator re gister set command.

E

WR/

A0

RD

D7 D6 D5 D4 D3 D2 D1 D0

WR

0 1 0 1 0 1 0 1 1 0 D

D = 0: Static Indicator OFF

D = 1: Static Indicator ON

! Static Indicator Register Set

This command sets two bits of data into the static indicator regist er and is used to set the static indicator into a blinki ng

mode.

E

WR/

A0

RD

D7 D6 D5 D4 D3 D2 D1 D0 Indicator Display State

WR

0 1 0 * * * * * * 0 0 OFF

0 1 ON (blinking at approximately 0.5 second intervals

1 0 ON (blinking at approximately 1 second intervals

1 1 ON (constantly on)

* Disabled bit

20. Power Save (Compound Command)

When all displays are turned on during display off, the Power Save command is issued to greatly reduce current

consumption.

If the static indicators are off, the Power Save command drives the system into sleep mode. If on, this command drives the

system into standby mode.

Release the Sleep mode using both the Power Save OFF command (Display ON command or Entire Display OFF

command) and Set Indicator On command.

Static Indicator OFF

Power Save

(Display OFF and Entire Display ON)

(Sleep mode)

Power Save OFF

(Display ON or Entire Displays OFF )

Static Indicator ON

(Standby mode)

Static Indicator ON

(Sleep mode released) (Standby mode released)

29

Page 30

NT7502

Sleep Mode

This mode stops every operation of the LCD display system, and can reduce current consumption nearly to a static current

value if no access is made from the microprocessor. The internal status in t he sleep mode is as follows:

(1) Stops the oscillator circuit and LCD power supply circuit.

(2) Stops the LCD drive, and outputs the V

SS level as the segment/common driver output.

(3) Holds the disp lay data and operation mode provided before the start of the sleep mode.

(4) The MPU can access the built-in display RAM.

Standby Mode

Stops the operation of the duty LCD display system and only turns on the static drive system to reduce current consumption

to the minimum level required for static drive.

The ON operation of the static drive system indicates that the NT7502 is in standby mode. The internal status in the standby

mode is as follows:

(1) Stops the LCD power supply circuit.

(2) Stops the LCD drive and outputs the V

SS level as the segment / common driver output. However, the static drive system

still operates.

(3) Holds the disp lay data and operation mode provided before the start of the standby mode.

(4) The MPU can access the built-in display RAM.

When the RESET command is issued in the standby mode, the sleep mode is set.

# When the LCD drive voltage level is given by an external resistive driver, the current of this resistor must be cut so that

it may be fixed to floating or V

SS level, prior to or concurrently with the situation of causing the NT7502 to enter sleep

mode or standby mode.

# When an external power supply is used, likewise, t he functi on of this ext er nal power supp ly must be stopped so t hat it

may be fixed to floating or V

SS level, prior to or concurrently with the situation of causing the NT 7502 to enter sleep

mode or standby mode.

21. NOP

Non-Operation Command

E

WR/

A0

RD

D7 D6 D5 D4 D3 D2 D1 D0

WR

0 1 0 1 1 1 0 0 0 1 1

22. Test Command

This is the dedicated IC chip test command. It must not be us ed for normal operation. If the Test command is issued

inadvertently, set the

E

A0

RD

WR

RES input to low or issue the Reset command t o release the test mode.

WR/

D7 D6 D5 D4 D3 D2 D1 D0

0 1 0 1 1 1 1 * * * *

*: Invalid bit

Cautions: The NT7502 maintains an operation status specified by each command. However, the internal operation status

may be changed by a high level of ambient noise. Users must consider how to suppress noise on the package

and system or to prevent ambient noise insertion. T o prevent a spike in noise, built-in soft ware for periodical

status refreshment is recommended.

The test command can be inserted in an unexpected place. Therefore it is recommended to enter the test mode

reset command F0h during the refresh sequence.

30

Page 31

NT7502

Command

A0

RD

D7 D6 D5 D4 D3 D2 D1 D0

WR

(1) Display ON/OFF 0 1 0 1 0 1 0 1 1 1 D

(2) Set Display Start Line 0 1 0 0 1 Display start address

(3) Set Page Address 0 1 0 1 0 1 1 Page address

(4-1) Set Column Address

4 higher bits

(4-2) Set column Address

4 lower bits

0 1 0 0 0 0 1

0 1 0 0 0 0 0

Code Function

Turns on LCD panel when goes

high, and turns off when goes low

Specifies RAM display line for

COM0

Sets the display RAM page in Page

Address register

Higher column

address

Lower column

address

Sets 4 higher bits of column

address of display RAM in register

Sets 4 lower bits of column address

of display RAM in register

(5) Read Status 0 0 1 Status 0 0 0 0 Reads the status information

(6) Write Display Data 1 1 0 Write data Writes data in display RAM

(7) Read Display Data 1 0 1 Read data Reads data from display RAM

(8) ADC select 0 1 0 1 0 1 0 0 0 0 D

(9) Normal/Reverse

Display

(10) Entire Display

ON/OFF

0 1 0 1 0 1 0 0 1 1 D

0 1 0 1 0 1 0 0 1 0

Sets the display RAM address

SEG output correspondence

Normal indication when low, but full

indication when high

0

Selects normal display (0) or Entire

Display ON (1)

1

(11) Set LCD Bias 0 1 0 1 0 1 0 0 0 1 D S ets LCD drive voltage bias ratio

(12) Read-Modify-Write 0 1 0 1 1 1 0 0 0 0 0

Increments Column Address

counter during each write

(13) End 0 1 0 1 1 1 0 1 1 1 0 Releases the Read-Modify-Write

(14) Reset 0 1 0 1 1 1 0 0 0 1 0 Resets internal functions

(15) Common output

mode select

0 1 0 1 1 0 0 D * * *

(16) Set Power Control 0 1 0 0 0 1 0 1

(17) V0 voltage regulator

internal resistor ratio set

0 1 0 0 0 1 0 0 Resistor ratio

Operation

status

Selects COM output scan direction.

* Invalid data

Selects the power circuit operation

mode

Select internal resistor ratio

(Rb / Ra) mode

(18) Electronic volume

mode set

Electronic Volume

Register set

0 1 0 1 0 0 0 0 0 0 1

0 1 0 * * Electronic control value

Sets the V0 output voltage

electronic volume register

(19) Set static indicator

On/Off

Set Static indicator

register

0 1 0 1 0 1 0 1 1 0 D

0 1 0 * * * * * * Mode Sets the flashing mode

(20) Power Save - - - - - - - - - - -

Sets static indicator On/Off

0: OFF 1: ON

Compound command of display

OFF and entire display ON

(21) NOP 0 1 0 1 1 1 0 0 0 1 1 Command for non-operation

(22) Test Command 0 1 0 1 1 1 1 * * * * IC Test command. Do not use!

(23) Test Mode Reset 0 1 0 1 1 1 1 0 0 0 0 Command of test mode reset

Note: Do not use any other command, or system malfuncti on may result.

31

Page 32

NT7502

Command Description

Instruction Setup: Reference

1. Initialization

Note: With this IC, when the power is applied, LCD driving non-selectiv e potentials V2 and V3 (SEG pin) and V1 and V4

(COM pin) are output through the LCD drivin g output pins SEG and COM. When e lectric charge ermine s in the smoothin g

capacitor connecting between the LCD driving voltage output pins (V0 - V4) and the VDD pin, the picture on the display may

instantaneously become totally dark when the po wer is turned on. T o avoid such failure, we recomm end the follo wing fl ow

sequence when turning on the power.

1.1. When the built-in power is being used immediately after turning on the power:

Turn ON the VDD-VSS power keeping the RES pin = "L"

When the power is stabilized

Release the reset state. (RES pin = "H")

Initialized state (Default)

Function setup by command input (User setup)

Function setup by command input (User setup)

Function setup by command input (User setup)

(11) LCD bias setting

(8) ADC selection

(15) Common output state selection

(17) Setting the built-in resistance radio

for regulation of the V

(18) Electronic volume control

(16) Power control setting

This concludes the initialization

0

voltage

Arrange to execute all the procedures from releasing the

reset state through setting the power control within 5ms

The target time of 5ms will vary depending on the panel characteristics and capacitance of the smoothing capacitor.

Therefore, we suggest you to conduct an operation check using the actual equipment.

32

Page 33

NT7502

1.2.

When the built-in power is not being used immediately after turning on the power

Turn ON the V

Function setup by command input (User setup)

Function setup by command input (User setup)

Function setup by command input (User setup)

DD

- VSS power keeping the RES pin = "L"

When the power is stabilized

Release the reset state. (RES pin = "H")

Initialized state (Default)

Power saver START (multiple commands)

(11) LCD bias setting

(8) ADC selection

(15) Common output state selection

(17) Setting the built-in resistance radio

for regulation of the V

(18) Electronic volume control

Power saver OFF

(16) Power control setting

0

voltage

Arrange to start the power saver within 5ms after

releasing the reset statue.

Arrange to start power control setting within

5ms after turning OFF the power saver

This concludes the initialization

The target time of 5ms will vary depending on the panel characteristics and the capacitance of t he smoothing capacitor.

Therefore, we suggest you to conduct an operation check using the actual equipment.

33

Page 34

NT7502

1. Data Display

End of initialization

2. Power OFF

Function setup by command input (User setup)

(2) Display start line set

(3) Page address set

(4) column address set

Function setup by command input (user setup)

(6) Display data write

Function setup by command input (User setup)

(1) Display ON/OFF

End of data display

Optional status

Function setup by command input (User setup)

(20) Power save

VDD-VSS power OFF

The target time of 5ms will vary depending on the panel characteristics and capacitance of the smoothing capacitor.

Therefore, we suggest you to conduct an operation check using the actual equipment.

34

Page 35

NT7502

Absolute Maximum Rating*

DC Supply Voltage (VDD, VDD2) .................... .-0.3V to +3.6V

DC Supply Voltage (V

DC Supply Voltage (V

Input Voltage..........................................-0.3V to V

Operating Ambient Temperature...................-40°C to +85°C

Storage Temperature..................................-55°C to +125°C

OUT)..............................-0.3V to +12V

0)................................-0.3V to +11.5V

DD + 0.3V

*Comments

Stresses above those listed under "Absolute Maximum

Ratings" may cause permanent damage to this device.

These are stress ratings only. Functional operation of thi s

device under these or any other conditions above those

indicated in the operational sections of this specificati on is

not implied or intended. Exposure to the absolute m aximum

rating conditions for extended periods may affect device

reliability.

Electrical Characteristics

DC Characteristics (VSS = 0V, VDD = 2.7 - 3.3V TA = -40 to 85°C unless otherwise specified)

Symbol Min. Typ. Max. Unit Condition

VDD Operating Voltage 2.4 3.5 V

VDD2 Operating Voltage

VOUT Booster output voltage 6.0 12.0 V

Voltage regulator

V0

operation voltage

VREG1 Reference voltage 2.04 2.10 2.16 V

VREG2 Reference voltage 2.00 2.10 2.20 V

Dynamic current

IDD1

consumption 1

Dynamic current

IDD2

consumption 2

Dynamic current

IDD3

consumption 3

Sleep mode current

ISP

consumption

Standby mode current

ISB

consumption

VIHC High-level input voltage 0.8 X VDD VDD V

VILC Low-level input voltage VSS 0.2 X VDD V

VOHC High-level output voltage 0.8 X VDD VDD V

VOLC Low -level output voltage VSS 0.2 X VDD

Parameter

2.4 3.5 V

2.4 3.0 V Quadruple boosting

4.5 11.5 V

A = 25°C, -0.05%/ °C

T

A = 25°C, -0.2%/ °C

T

DD = 3V, V0 = 11V, built-in power supply off,

V

- 21 35

µA

display on, display data = checker and no access,

A = 25°C

T

4X boosting,

VDD, VDD2 = 3V, V0 = 11V, built-in

power supply on, display on, display data = checker

- 96 160

and no access, T

µA

A = 25°C, temperature gradient is

-0.05%/ °C, when V0 voltage internal resistor is

used. Normal mode

4X boosting,

VDD, VDD2 = 3V, V0 = 11V, built-in

power supply on, display on, display data = checker

- 153 255

and no access, T

µA

A = 25°C, temperature gradient is

-0.05%/ °C, when V0 voltage internal resistor is

used. High power mode

0.01 5

4 8

µA During sleep, T

µA During standby, T

A0, D0 - D7,

A = 25°C

A = 25°C

RD(E), WR ( W/R ), 1CS , CS2,

CLS, CL, FR, M/S, C86, P/S,

VRS, IRS, and

I

OH = -0.5mA (D0 - D7, FR, FRS, DOF , and CL)

I

OL = 0.5mA (D0 - D7, FR, FRS, DOF, and CL)

HPM

DOF, RES , TMPS,

V

IN = VDD or VSS (A0, RD (E), WR ( W/R ), 1CS ,

ILI Input leakage current -1.0 1.0

µA

CS2, CLS, M/S, C86, P/S, IRS, TMPS, VRS and

RES )

IHZ HZ leakage current -3.0 3.0

When the D0 - D7, FR, CL, and

µA

impedance

DOF are in high

35

Page 36

NT7502

DC Characteristics (Continued)

Symbol Parameter Min. Typ. Max. Unit Condition

A = 25°C, These are the resistance

RON1 LCD driver ON resistance 2.0 3.5

k

Ω

V0 = 11.0V

T

values for when a 0.1V voltage is applied

between the output terminal SEGn or

RON2 LCD driver ON resistance 3.2 5.4

k

CIN Input pad capacity 5.0 8.0 pF

fOSC Oscillation frequency 27 33 39 kHZ

V0 = 8.0V

Ω

T

A = 25°C, f = 1MHz

T

A = 25°C

COMn and the various power supply

terminals (V1, V2, V3, V4).

Notes: 1. Voltages V0 ≧ V1 ≧ V2 ≧ V3 ≧ V4 ≧ Vss must always be satisfied.

36

Page 37

NT7502

AC Characteristics

(1) System buses Read / Write characteristics 1 (For the 8080 Series MPU)

A0

t

1CS

(CS2 = "1")

RD,WR

D0 - D7

(WRITE)

D0 - D7

(READ)

AS8

t

CCLW

t

CCLR

t

DS8

t

ACC8

t

AH8

t

CYC8

t

CCHW

t

CCHR

t

DH8

t

CH8

(V

DD = 2.7 - 3.3V, TA = -40 - 85°C)

Symbol Parameter Min. Typ. Max. Unit Condition

TAH8 Address hold time 0 ns

TAS8 Address setup time 0 ns

TCYC8 System c ycle time 300 ns

TCCLW Control L pulse width (WR) 90 ns

TCCLR Control L pulse width (RD) 120 ns

TCCHW Control H pulse width (WR) 120 ns

TCCHR Control H pulse width (RD) 60 ns

TDS8 Data setup time 40 ns

TDH8 Data hold time 15 ns

TACC8

RD access time

140 ns C

L = 100pF

TCH8 Output disable time 10 100 ns CL = 100pF

*1. The input signal rise time and fall time (tr, tf) is specified at 15ns or less. When the system cycle time is extremely fast, (tr+tf)

≤ (t

CYC8-tCCLW-tCCHW

) for (tr+tf) ≤ (t

CYC8-tCCLR-tCCHR

) are specified.

*2. All timing is specified using 20% and 80% of VDD as the reference.

*3. t

CCLW

and t

are specified as the overlap between

CCLR

1CS

being “L” (CS2 = “H”) and

WR

and RD being at the “L” level.

37

Page 38

NT7502

System buses Read/Write Characteristics 2 (6800 Series MPU)

A0

W/R

t

1CS

(CS2 = "1")

E

D0 - D7

(WRITE)

D0 - D7

(READ)

AS6

t

EWHW tEWHR

t

DS6

t

ACC6

t

AH6

t

CYC6

t

EWLW

t

EWLR

t

DH6

t

OH6

DD = 2.7 - 3.3V, TA = -40 - 85°C)

(V

Symbol Parameter Min. Typ. Max. Unit Condition

TCYC6 System cycle time 300 nS

TAS6 Address setup time 0 nS

TAH6 Address hold time 0 nS

TDS6 Data setup time 40 nS

TDH6 Data hold time 15 nS

TOH6 Output disable time 10 100 nS CL = 100pF

TACC6 Access time 140 nS CL = 100pF

TEWHR Enable H pulse width (Read) 120 nS

TEWHW Enable H pulse width (Write) 90 nS

TEWLR Enab le L pulse width (Read) 60 nS

TEWLW Enable L pulse width (Write) 120 nS

*1. The input signal rise time and fall time (tr, tf) is specified at 15ns or less. When the system cycle time is extremely fast, (tr+tf)

≤ (t

CYC6-tEWLW-tEWHW

*2. All timings are specified using 20% and 80% of V

EWLW

and t

EWLR

*3. t

) for (tr+tf) ≤ (t

CYC6-tEWLR-tEWHR

as the reference.

DD

are specified as the overlap between

) are specified.

1CS

being “L” (CS2 = “H”) and E.

38

Page 39

NT7502

(2) Serial Interface

1CS

(CS2 = "1")

t

CSS

t

SAS

t

CSH

t

SAH

A0

t

SCYC

SCL

t

SLW

t

SHW

trtf

t

SDS

t

SDH

SI

(VDD = 2.7 - 3.3V, TA = -40 - 85°C)

Symbol Parameter Min. Typ. Max. Unit Condition

TSCYC Serial clock cycle 250 nS

TSHW Serial clock H pulse width 100 nS

TSLW Serial clock L pulse width 100 nS

TSAS Address setup time 150 nS

TSAH Address hold time 150 nS

TSDS Data setup time 100 nS

TSDH Data hold time 100 nS

TCSS

TCSH

cs serial clock time

cs serial clock time

150 nS

150 nS

*1. The input signal rise time and fall time (tr, tf) are specified at 15ns or less

*2. All timings are specified using 20% and 80% of VDD as the standard.

39

Page 40

NT7502

(3) Display Control Timing

CL

(OUT)

t

DFR

FR

(VDD = 2.7 - 3.3V, TA = -40 - 85°C)

Symbol Parameter Min. Typ. Max. Unit Condition

TDFR FR delay time 20 80 nS CL = 50pF

(4) Reset Timing

t

RES

RW

t

R

Internal circuit

status

During reset End of reset

(VDD = 2.7 - 3.3V, TA = -40 - 85°C)

Symbol Parameter Min. Typ. Max. Unit Condition

TR Reset time 1.0

TRW Reset low pulse width 1.0

µS

µS

40

Page 41

NT7502

Microprocessor Interface (for reference only)

8080-series microprocessors

V

DD

V

MPU

6800-series microprocessors

V

cc

GND

CC

A0

A1 to A7

IORQ

D0 to D7

RD

WR

RES

A0

A1 to A15

VMA

Decoder

RESET

Figure. 8

Decoder

A0

1CS

CS2

D0 to D7

RD

WR

RES

A0

1CS

2CS

DD

V

NT7502

V

SS

V

DD

C86

V

SS

V

DD

P/S

V

SS