Page 1

查询IBM25NPE405L-3FA133C供应商

AMCC NPe405L

PowerNP

Data Sheet

PowerNP NPe405L Data Sheet

Document Issue 1.00

September 2004

C

OVER

Page 2

AMCC reserves the right to make changes to its products, its datasheets, or related

documentation, without notice and warrants its products solely pursuant to its

terms and conditions of sale, only to substantially comply with the latest available

datasheet. Please consult AMCC’s Term and Conditions of Sale for its warranties

and other terms, conditions and limitations. AMCC may discontinue any

semiconductor product or service without notice, and advises its customers to

obtain the latest version of relevant information to verify, before placing orders,

that the information is current. AMCC does not assume any liability arising out of

the application or use of any product or circuit described herein, neither does it

convey any license under its patent rights nor the rights of others. AMCC reserves

the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED,

AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFESUPPOR T APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL

APPLICATIONS.

AMCC is a registered Trademark of Applied Micro Circuits Corporation.

Copyright © 2004 Applied Micro Circuits Corporation.

Page 3

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Features

•PowerNP technology using an IBM PowerPC

405 32-bit RISC processor core operating up to

266 MHz

• PC-133 synchronous DRAM (SDRAM) interf ace

- 32-bit interface for non-ECC applications

- 40-bit interface serves 32 bits of data plus 8

check bits for ECC applications

• External bus for peripheral devices

- Flash and ROM interface

- Direct support for 8-, or 16-bit SRAM and

external peripherals

- Up to 4 devices

• DMA support for external peripherals, internal

UARTs and memory

- Scatter-gather chaining supported

- Four channels

• Two 10/100 Ethernet MACs supporting up to

two external PHYs via MII, RMII, or SMII

interfaces

• HDLC interface with 32 channels through two

ports at up to 4.096 Mbps each or 8.192 Mbps

for a single port

• Programmable interrupt controller

- Seven external and 29 internal

- Edge triggered or level-sensitive

- Positive or negative active

- Non-critical or critical interrupt to processor

core

- Programmable critical interrupt priority

ordering

- Programmable critical interrupt vector

• Programmable timers

• Two serial ports (16550 compatible UART)

• One IIC interface

• General Purpose I/O (GPIO) available

• Supports JTAG for board level testing

• Internal processor local bus (PLB) runs at

SDRAM interface frequency

Description

Designed specifically to address embedded

applications, the NPe405L provides a highperformance, low-power solution that interfaces to a

wide range of peripherals by incorporating on-chip

power management features and lower power

dissipation requirements.

This chip contains a high-perfo rmanc e RISC

processor core, SDRAM controller, Ethernet

EMACs, HDLC controller, external bus controller for

While the information contained herein is believed to be accurate, such information is preliminary, and should not be

relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

ROM, Flash, and peripherals, DMA with scattergather support, serial ports, IIC interface, and

general purpose I/O.

Technology: IBM CMOS SA-12E 0.25

µm L

(0.18

Package: 23mm, 324-ball enhanced plastic ball grid

array (E-PBGA)

Power (typical): 1.3W at 133MHz, 1.7W at

200MHz, 1.8W at 266MHz

eff

)

µm

1

Page 4

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Contents

Ordering, PVR, and JTAG Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Address Map Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

SDRAM Memory Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

External Bus Controller (EBC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

IIC Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

HDLCEX Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

General Purpose IO (GPIO) Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Universal Interrupt Controller (UIC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

10/100 Mbps Ethernet MAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Signal Lists . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Spread Spectrum Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

2

Page 5

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Tables

System Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

DCR Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Signals Listed Alphabetically . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Signals Listed by Ball Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Pin Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Signal Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Package Thermal Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Recommended DC Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Input Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Clocking Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Peripheral Interface Clock Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

I/O Specifications—All . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

I/O Specifications—133 and 200MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

I/O Specifications—266MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figures

NPe405L Embedded Controller Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

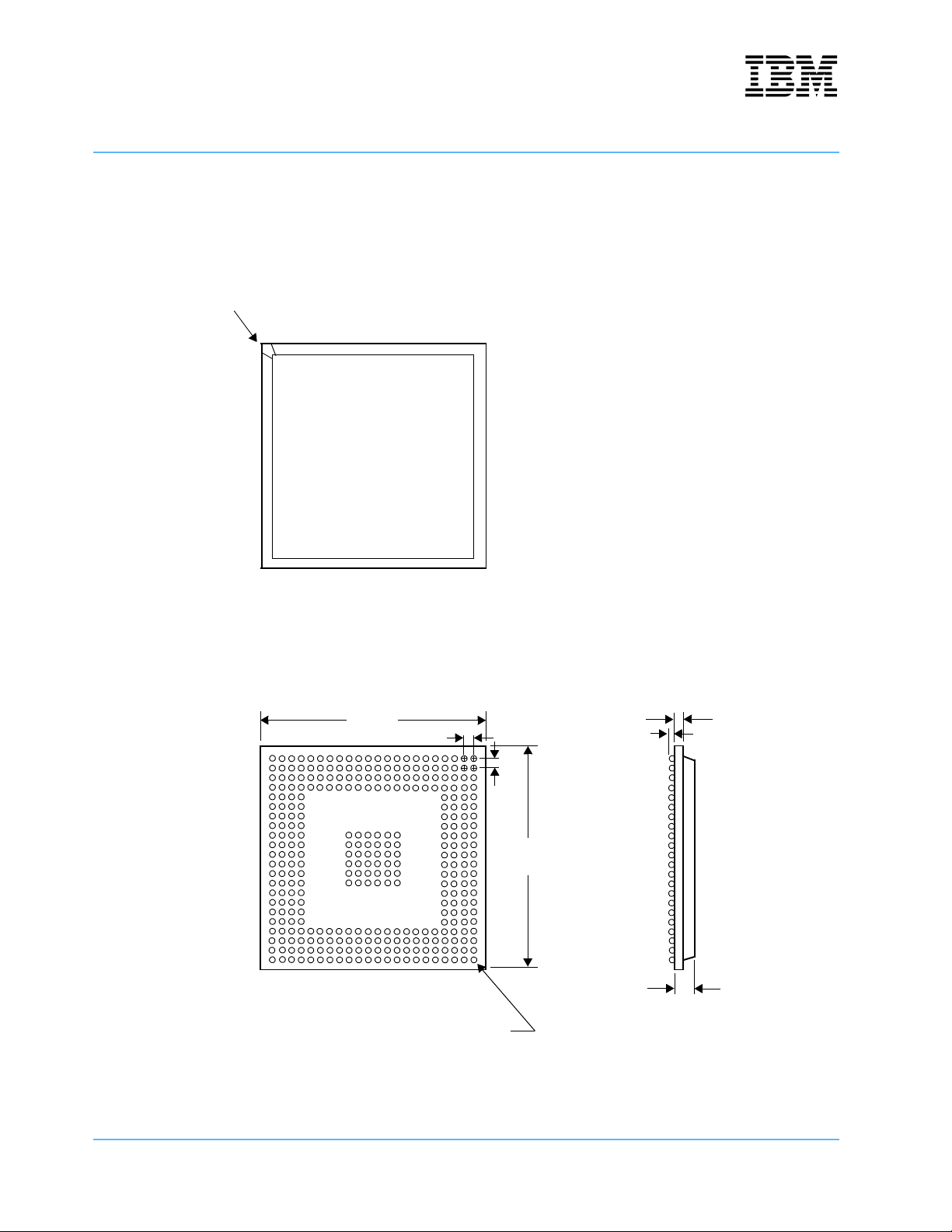

23mm, 324-Ball E-PBGA Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Input Setup and Hold Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Output Delay and Float Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3

Page 6

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Ordering, PVR, and JTAG Information

Product Name

NPe405L IBM25NPe405L-3FA133C 133M H z 23mm, 324 E-PBGA A 0x416100C0 0x04247409

NPe405L IBM25NPe405L-3FA133CZ 133M H z 23mm, 324 E-PBGA A 0x416100C0 0x04247409

NPe405L IBM25NPe405L-3FA200C 200M H z 23mm, 324 E-PBGA A 0x416100C0 0x04247409

NPe405L IBM25NPe405L-3FA200CZ 200M H z 23mm, 324 E-PBGA A 0x416100C0 0x04247409

NPe405L IBM25NPe405L-3FA266C 266M H z 23mm, 324 E-PBGA A 0x416100C0 0x04247409

NPe405L IBM25NPe405L-3FA266CZ 266M H z 23mm, 324 E-PBGA A 0x416100C0 0x04247409

Note 1: Z at the end of the Order Part Number indicates a tape and reel shipping package. Otherwise, the chips are shipped in a tray.

Order Part Number

1

Processor

Frequency

Package

Rev

Level

PVR Value JTAG ID

This section provides the part numbering nomenclature for the NPe405L. For availability, contact your local

IBM sales office.

The part number contains a part modifier. This modifier provides for identification of future enhancements (for

example, higher performance).

Each part number also contains a revision code. This refers to the die mask revision number and is specified

in the part numbering scheme for identification purposes only.

The PVR (Processor Version Register) is software accessible and contains additional information about the

revision level of the part. Refer to the NPe405L User’s Manual for details on the register content.

IBM Part Number Key

IBM25NPe405L-3FA200Cx

Shipping Package

Blank = Tray

Z = Tape and reel

IBM Part Number

Grade 3 Reliability

Package (E-PBGA)

4

Operational Case Temperature Range

(-40°C to +85°C)

Processor Speed

133MHz

200MHz

266MHz

Revision Level

Page 7

PowerNP NPe405L Embedded Processor Data Sheet

NPe405L Embedded Controller Functional Block Diagram

Preliminary

Universal

Interrupt

Controller

x2

8KB

D-Cache

Clock

Control

Reset

PPC405

Processor Core

JTAG

DCU

SDRAM

Controller

Timers

MMU

Power

Mgmt

DCRs

DCR Bus

Trace

ICU

Processor Local Bus (PLB)

External

Bus

Controller

16KB

I-Cache

Arb

DMA

Controller

(4-Channel)

MAL1

See Peripheral Interface

Clock Timing table

GPIO

IIC

On-chip Peripheral Bus (OPB)

OPB

Bridge

MAL0

HDLCEX

UART

x2

Ethernet

x2

ZMII

13-bit addr

32-bit data

28-bit addr

16-bit data

Two

32-channel

ports

MII,

RMII,

SMII

The NPe405L is designed using the IBM Microelectronics Blue Logic methodology in which major functional

blocks are integrated to create an application-specific ASIC product. This approach provides a consistent way

to generate complex ASICs using IBM CoreConnect

Bus Architecture.

Address Map Support

The NPe405L incorporates two separate address maps. The first is a fixed processor address map that

serves the PowerPC family of processors. This address map defines the possible contents of various address

regions which the processor can access. The second address map is for Device Configuration Registers

(DCRs). The DCRs are accessed by software running on the NPe405L processor through the use of mtdcr

and mfdcr commands.

5

Page 8

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

System Address Map 4GB Total System Memory

Function Subfunction Start Address End Address Size

0x00000000 0xE7FFFFFF 3712MB

SDRAM, External peripherals

General use

Boot-up

Internal peripherals

Notes:

1. When external peripheral bus boot is selected, peripheral bank 0 is automatically configured at reset to the address range listed

above.

2. After the boot process, software may reassign the boot memory regions for other uses.

3. All address ranges not listed above are reserved.

Note: Any of the address ranges listed at

right may be use for any of the above

functions.

External peripheral bus boot

UART0 0xEF600300 0xEF600307 8B

UART1 0xEF600400 0xEF600407 8B

IIC0 0xEF600500 0xEF60051F 32B

OPB Arbiter 0xEF600600 0xEF60063F 64B

GPIO0 controller registers 0xEF600700 0xEF60077F 128B

GPIO1 controller registers 0xEF600780 0xEF6007FF 128B

Ethernet MAC 0 registers 0xEF600800 0xEF6008FF 256B

Ethernet MAC 1 registers 0xEF600900 0xEF6009FF 256B

ZMII control registers 0xEF600C10 0xEF600C1F 16B

HDLCEX 0xEF610000 0xEF61FFFF 64KB

1

0xE8010000 0xE87FFFFF 8MB

0xEC000000 0xEEBFFFFF 44MB

0xEEE00000 0xEF3FFFFF 6MB

0xEF500000 0xEF5FFFFF 1MB

0xEF900000 0xFFFFFFFF 263MB

0xFFE00000 0xFFFFFFFF 2MB

6

Page 9

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

DCR Address Map 4KB Device Configuration Register

Function Start End Size

DCR address space

Reserved 0x000 0x00F 16W

Memory controller registers 0x010 0x011 2W

External bus controller registers 0x012 0x013 2W

Reserved 0x014 0x07F 108W

PLB registers 0x080 0x08F 16W

Reserved 0x090 0x09F 16W

OPB bridge-out registers 0x0A0 0x0A7 8W

Reserved 0x0A8 0x0AF 8W

Clock, control and reset 0x0B0 0x0B7 8W

Power management 0x0B8 0x0BF 8W

Interrupt controller 0 0x0C0 0x0CF 16W

Interrupt controller 1 0x0D0 0x0DF 16W

Reserved 0x0E0 0x0EF 16 W

Miscellaneous 0x0F0 0x0FF 16W

DMA controller registers 0x100 0x13F 64W

Reserved 0x140 0x17F 64W

MAL0 registers (Ethernet) 0x180 0x1FF 128W

MAL1 registers (HDLCEX) 0x200 0x27F 128W

Reserved 0x280 0x3FF 384W

Notes:

1. DCR address space is addressable with up to 10 bits (1024 or 1K unique addresses). Each unique address represents a single

32-bit (word) register, or 1 kiloword (KW) (which equals 4 KB).

1

0x000 0x3FF

1KW (4KB)

1

7

Page 10

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

SDRAM Memory Controller

The NPe405L Memory Controller provides a low latency access path to SDRAM memory. The memory

controller supports four logical banks. Up to 256MB per bank are supported, for a maximum of 1GB total.

Memory access and refresh timing, address and bank sizes, and memory addressing modes are

programmable.

Features include:

• 11x8 to 13x11 row-column address modes (2- and 4-bank devices supported)

• Memory bus operates at same frequency as PLB

• 32-bit memory interface support

• Programmable address range for each bank of memory

- 4GB address space

• Industry standard 168-pin DIMMS are supported (some configurations)

• 200 MHz NPe405H supports up to 100 MHz memory with PC100 support

• 266 MHz NPe405H supports up to 133 MHz memory with PC133 support

• 4MB to 256MB per bank

• Programmable timing

• Auto refresh

• Page Mode Accesses with up to 4 open pages

• Power Management (self-refresh)

• Error Checking and Correction (ECC) support

- Standard single error correct, double error detect coverage

- Aligned nibble error detect

- Address error logging

External Bus Controller (EBC)

• Supports four ROM, EPROM, SRAM, Flash, and Slave Peripheral I/O banks supported

• Up to 66.66MHz operation

• Burst and non-burst devices

• 8-, 16-bit byte-addressable data bus width support

• Latch data on Ready, Synchronous or Asynchronous

• Programmable 2K clock-cycle time-out counter with disable for R eady

8

Page 11

PowerNP NPe405L Embedded Processor Data Sheet

• Programmable access timing per device

- 0–255 wait states for non-bursting devices

- 0 –31 Burst Wait States for first access and up to 7 Wait States for subsequent accesses

- Programmable chip select assertion/negation relative to driving address bus

- Programmable output and write-enable assertion/negation relative to assertion of chip select

• Programmable address mapping

• Peripheral device wait via “Ready”

DMA Controller

• Supports the following transfers:

- Memory-to-memory transfers

- Buffered peripheral to memory transfers

- Buffered memory to peripheral transfers

Preliminary

• Four channels

• Scatter/Gather capability for programming multiple DMA operations

• 8-, 16-, 32-bit peripheral support (OPB and external bus attached)

• 32-bit addressing

• Address increment or decrement

• Internal 32-byte data buffering capability

• Supports internal and external peripherals

• Support for memory mapped peripherals

• Support for peripherals running on slower frequency buses

Serial Interface

• Two 8-pin UART interfaces provided

• Selectable internal or external serial clock to allow wide range of baud rates

• Register compatibility with NS16550 register set

• Complete status reporting capability

• Transmitter and receiver are each buffered with 16-byte FIFOs when in FIFO mode

• Fully programmable serial-interface characteristics

• Supports DMA using internal DMA engine

9

Page 12

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

IIC Bus Interface

• Compliant with Phillips® Semiconductors I2C Specification, dated 1995

• Operation at 100kHz or 400kHz

• 8-bit data

• 10- or 7-bit address

• Slave transmitter and receiver

• Master transmitter and receiver

• Multiple bus masters

• Supports fixed V

• Two independent 4 x 1 byte data buffers

• One programmable interrupt request signal

• Provides full management of all IIC bus protocol

• Programmable error recovery

IIC interface

DD

HDLCEX Interface

• 32-channel HDLC controller

• Two full-duplex Pulse Code Modulation (PCM) Highway ports at speeds up to 4.096 Mbps per port or

8.192 Mbps when using a single port

• Supports HDLC protocol as well as a Transparent mode

• For a single channel per port, autonomous management of I-Frames and S-Frames of the Normal

Response mode (NRM) pr otocol on one channel per port. U-frames are handled by software.

• Supports software emulation of NRM on all channels

General Purpose IO (GPIO) Controller

• Most GPIOs are pin-shared with other functions. Configuration registers are provided to determine

whether a particular pin that has GPIO capabilities acts as a GPIO or is used for another purpose. The

GPIO function has 32 I/Os.

• Each GPIO output is separately programmable to emulate an open-drain driver (drives to zero, threestated if output bit is 1)

Universal Interrupt Controller (UIC)

Two cascaded Universal Interrupt Controllers (UICs) provide the control, status, and communications

necessary for the interrupt sources and the PowerPC processor.

Features include:

10

Page 13

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

• Seven external and 29 internal interrupts

• Edge triggered or level-sensitive

• Positive or negative active

• Selectable non-critical or critical interrupt requests to the PPC405 processor core

• Programmable critical interrupt priority ordering

• Programmable critical interrupt vector generation for reduced latency interrupt handling

10/100 Mbps Ethernet MAC

• Two units capable of full- and half-duplex, 10 Mbps or 100 Mbps operation

• Integrated ZMII Bridge supports use of MII, SMII or RMII connections to external PHYs (PHYs not

included on chip)

- Reduced Media Independent Interface (RMII) or Serial Media Independent Interface (SMII) for one to

two PHY applications

- Media Independent Interface (MII) for single or dual PHY applications

• Dedicated media access layer (MAL) provides DMA support

JTAG

• IEEE 1149.1 Test Access Port

• Debugger support

• JT AG boundary scan support (BSDL file available)

11

Page 14

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

23mm, 324-Ball E-PBGA Package

Top View

Gold gate release

corresponds to

A01 ball location

Bottom View

AB

Y

V

T

P

M

K

H

F

D

B

Note:

All dimensions are in mm.

AA

W

U

R

N

L

J

G

E

C

A

01 03 050709 11 13 15 17

02 04

Thermal balls

0810

06

23.0

12 14

1.0

19

21

20

22

16 18

0.60 Solder Ball

0.60 nom

0.30 nom

1.0

23.0

2.65 max

12

Page 15

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signal Lists

The following table lists all the external signals in alphabetical order and shows the ball number on which the

signal appears. Multiplexed signals are shown with the default signal (following reset) not in brackets and the

alternate signal or signals in brackets. Multiplexed signals appear alphabetically multiple times in the list—

once for each signal name on the ball. The page number listed gives the page in “Signal Functional

Description” on page 32 where the signals in the indicated interface group begin.

Signals Listed Alphabetically (Part 1 of 11)

Signal Name Ball Interface Group Page

AV

DD

BA0 AB15

BA1 Y14

BankSel0

BankSel1

BankSel2

BankSel3

CAS

ClkEn0 Y13

ClkEn1 AA13

[DMAAck0

[DMAAck1

[DMAAck2

[DMAAck3

[DMAReq0

[DMAReq1

[[DMAReq2

[DMAReq3

DQM0 U03

DQM1 U01

DQM2 R02

DQM3 L01

DQMCB AA04 SDRAM 33

ECC0 AA05

ECC1 Y06

ECC2 AB04

ECC3 AA03

ECC4 Y05

ECC5 AB03

ECC6 Y04

ECC7 W06

EMC0MDClk AB16 Ethernet 32

EMC0MDIO AA16 Ethernet 32

[EMC0Sync]EMC0TxEn[EMC0Tx0En] AB21 Ethernet 32

]GPIO13 U22

]GPIO14 U21

]GPIO15 T20

]GPIO16 D17

]GPIO09 P19

]GPIO10 T22

]GPIO11 T21

]GPIO12 R20

H21 Power 37

SDRAM 33

AA07

Y08

AB06

AA06

AA12 SDRAM 33

SDRAM 33

SDRAM 33

External Peripheral Bus 34

External Peripheral Bus 34

SDRAM 33

SDRAM 33

13

Page 16

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed Alphabetically (Part 2 of 11)

Signal Name Ball Interface Group Page

EMC0TxD0[EMC0Tx0D0][EMC0Tx0D] AA22

EMC0TxD1[EMC0Tx0D1][EMC0Tx1D] U19

EMC0TxD2[EMC0Tx1D0] W20

EMC0TxD3[EMC0Tx1D1] Y22

EMC0TxEn[EMC0Tx0En][EMC0Sync] AB21 Ethernet 32

EMC0TxErr[EMC0Tx1En] AB20 Ethernet 32

[EMC0Tx0En]EMC0TxEn[EMC0S ync] AB21

[EMC0Tx1En]EMC0TxErr AB20

[EOT0

/TC0]GPIO24 B19

/TC1]GPIO25 B18

[EOT1

[EOT2

/TC2]GPIO26 C16

/TC3]GPIO27 B17

[EOT3

GND A01

GND A05

GND A09

GND A14

GND A18

GND A22

GND B02

GND B21

GND C03

GND C20

GND D04

GND D08

GND D11

GND D12

GND D15

GND D19

GND E01

GND E22

GND H04

GND H19

GND J01

GND J09-J14

GND J22

GND K09-K14

GND L04

GND L09-L14

GND L19

Ethernet 32

Ethernet 32

External Peripheral Bus 34

Power

Note: J09-J14, K09-K14, L09-L14, M09-M14, N09-

N14, and P09-P14 are also thermal balls.

37

14

Page 17

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed Alphabetically (Part 3 of 11)

Signal Name Ball Interface Group Page

GND M04

GND M09-M14

GND M19

GND N09-N14

GND P01

GND P09-P14

GND P22

GND R04

GND R19

GND V01

GND V22

GND W04

GND W08

GND W11

GND W12

GND W15

GND W19

GND Y03

GND Y20

GND AA02

GND AA21

GND AB01

GND AB05

GND AB09

GND AB14

GND AB18

GND AB22

Power

Note: J09-J14, K09-K14, L09-L14, M09-M14, N09-

N14, and P09-P14 are also thermal balls.

Preliminary

37

15

Page 18

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed Alphabetically (Part 4 of 11)

Signal Name Ball Interface Group Page

GPIO00[TrcClk] B20

GPIO01[TS1E]GPIO08[TS6] C18

GPIO02[TS2E] A20

GPIO03[TS1O] N20

GPIO04[TS2O] N22

GPIO05[TS3] P21

GPIO06[TS4] P20

GPIO07[TS5] R22

GPIO08[TS6] R21

GPIO09[DMAReq0

GPIO10[DMAReq1

GPIO11[DMAReq2

GPIO12[DMAReq3

GPIO13[DMAAck0

GPIO14[DMAAck1

GPIO15[DMAAck2

GPIO16[DMAAck3

GPIO17[IRQ0] F20

GPIO18[IRQ1] J20

GPIO19[IRQ2] L21

GPIO20[IRQ3] M21

GPIO21[IRQ4] A A17

GPIO22[IRQ5] A B17

GPIO23[IRQ6] W14

GPIO24[EOT0

GPIO25[EOT1

GPIO26[EOT2

GPIO27[EOT3

GPIO28[UART1_DCD

GPIO29[UART1_RI

GPIO30 T03

GPIO31[PerWE

Halt

HDLCEXRxClk L20 HDLC 32-Channel 32

HDLCEXRxDataA M 22

HDLCEXRxDataB N21

HDLCEXRxFS M20 HDLC 32-Channel 32

HDLCEXTxClk K20 HDLC 32-Channel 32

HDLCEXTxDataA K21

HDLCEXTxDataB L22

[HDLCEXTxEnA]GPIO28[UART1_DCD

[HDLCEXTxEnB]GPIO29[UART1_RI

HDLCEXTxFS K22 HDLC 32-Channel 32

]P19

]T22

]T21

]R20

]U22

]U21

]T20

]D17

/TC0]B19

/TC1]B18

/TC2]C16

/TC3]B17

][HDLCEXTxEnA] AA15

][HDLCEXTxEnB] T01

]A13

]AA15

]T01

System 37

F22 System 37

HDLC 32-Channel 32

HDLC 32-Channel 32

HDLC 32-Channel 32

16

Page 19

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed Alphabetically (Part 5 of 11)

Signal Name Ball Interface Group Page

IICSCL[IECSCL] C17

IICSDA[IECSDA] A19

[IRQ0]GPIO17 F20

[IRQ1]GPIO18 J20

[IRQ2]GPIO19 L21

[IRQ3[GPIO20 M21

[IRQ4[GPIO21 AA17

[IRQ5]GPIO22 AB17

[IRQ6[GPIO23 W14

MemAddr00 Y12

MemAddr01 Y11

MemAddr02 AB11

MemAddr03 AA11

MemAddr04 AA10

MemAddr05 Y10

MemAddr06 AB10

MemAddr07 AA09

MemAddr08 Y09

MemAddr09 AB08

MemAddr10 AA08

MemAddr11 W09

MemAddr12 AB07

MemClkOut0 AA14

MemClkOut1 AB13

Internal Peripheral 35

Interrupts 36

SDRAM

Note: During a CAS

significant bit (lsb) on this bus.

SDRAM 33

cycle MemAddr00 is the least

Preliminary

33

17

Page 20

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed Alphabetically (Part 6 of 11)

Signal Name Ball Interface Group Page

MemData00 AB02

MemData01 AA01

MemData02 U04

MemData03 W03

MemData04 Y01

MemData05 V03

MemData06 Y02

MemDatar07 W01

MemData08 W02

MemData09 V02

MemData10 U02

MemData11 R03

MemData12 T02

MemData13 P04

MemData14 R01

MemData15 P03

MemData16 P02

MemData17 N01

MemData18 N03

MemData19 N02

MemData20 M02

MemData21 M01

MemData22 M03

MemData23 L03

MemData24 L02

MemData25 K02

MemData26 K03

MemData27 K01

MemData28 J02

MemData29 J03

MemData30 H01

MemData31 H02

SDRAM

Notes:

1. MemData00 is the most significant bit (msb).

2. MemData31 is the least significant bit (lsb)

33

18

Page 21

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed Alphabetically (Part 7 of 11)

Signal Name Ball Interface Group Page

OV

OV

OV

OV

OV

OV

OV

OV

OV

OV

OV

OV

OV

OV

OV

OV

DD

DD

DD

DD

DD

DD

DD

DD

DD

DD

DD

DD

DD

DD

DD

DD

D05

D07

D16

D18

E04

E19

G04

G19

Power 37

T19

T04

V04

V19

W05

W07

W16

W18

Preliminary

19

Page 22

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed Alphabetically (Part 8 of 11)

Signal Name Ball Interface Group Page

PerAddr04 D06

PerAddr05

PerAddr06

PerAddr07

PerAddr08

PerAddr09

PerAddr10

PerAddr11

PerAddr12

PerAddr13

PerAddr14

PerAddr15

PerAddr16

PerAddr17

PerAddr18

PerAddr19

PerAddr20

PerAddr21

PerAddr22

PerAddr23

PerAddr24

PerAddr25

PerAddr26

PerAddr27

PerAddr28

PerAddr29

PerAddr30

PerAddr31

PerBLast

PerClk A17 External Peripheral Bus 34

PerCS0

PerCS1

PerCS2

PerCS3

C04

A03

C05

B03

A04

C06

B04

B05

C07

B06

C08

B07

A07

External Peripheral Bus 34

D09

B08

A08

C09

B09

A10

C10

B10

B11

A11

C11

C12

A12

B12

C15 External Peripheral Bus 34

B14

C14

External Peripheral Bus 34

A15

B15

20

Page 23

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed Alphabetically (Part 9 of 11)

Signal Name Ball Interface Group Page

PerData00 J04

PerData01 G01

PerData02 G02

PerData03 H03

PerData04 F01

PerData05 F02

PerData06 G03

PerData07 E02

PerData08 D02

PerData09 F03

PerData10 D01

PerData11 C02

PerData12 E03

PerData13 C01

PerData14 D03

PerData15 F04

PerErr J21 External Peripheral Bus 34

PerOE

PerPar0 B01

PerPar1 A02

PerR/W

PerReady B16 External Peripheral Bus 34

PerWBE0

PerWBE1

]GPIO31 A13 External Peripheral Bus 34

[PerWE

PHY0Col[PHY0Rx1Er] W17 Ethernet 32

PHY0CrS[PHY0CrS0DV] Y18 Ethernet 32

[PHY0CrS1DV]PHY0RxDV Y17 Ethernet 32

PHY0RxClk AB19 Ethernet 32

[PHY0RefClk]PHY0TxClk Y19 Ethernet 32

PHY0RxD0[PHY0Rx0 D 0 ][PHY0Rx0D] Y15

PHY0RxD1[PHY0Rx0 D 1 ][PHY0Rx1D] Y16

PHY0RxD2[PHY0Rx1D0] AA18

PHY0RxD3[PHY0Rx1D1] AA19

PHY0RxDV[PHY0CrS1D V] Y17 Ethernet 32

PHY0RxErr[PHY0Rx0Er] AA20 Ethernet 32

[PHY0Rx0Er]PHY0RxErr AA20 Ethernet 32

PHY0TxClk[PHY0RefClk] Y19 Ethernet 32

RAS

SysClk G22 System 37

SysErr C21 System 37

SysReset

TCK J19 JTAG 36

AB12 SDRAM 33

External Peripheral Bus

Note: PerData00 is the most significant bit (msb)

on this bus.

D14 External Peripheral Bus 34

External Peripheral Bus 34

A16 External Peripheral Bus 34

B13

External Peripheral Bus 34

C13

Ethernet 32

A21 System 37

34

21

Page 24

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed Alphabetically (Part 10 of 11)

Signal Name Ball Interface Group Page

[TC0/EOT0]GPIO24 B19

/EOT1]GPIO25 B18

[TC1

/EOT2]GPIO26 C16

[[TC2

[TC3

/EOT3]GPIO27 B17

TDI G21 JTAG 36

TDO F21 JTAG 36

TestEn H20 System 37

TmrClk D20 System 37

TMS E21 JTAG 36

[TrcClk]GPIO00 B20 Trace 37

TRST

[TS1E]GPIO01 C18

[TS2E]GPIO02 A20

[TS1O]GPIO03 N20

[TS2O]GPIO04 N22

[TS3]GPIO05 P21

[TS4]GPIO06 P20

[TS5]GPIO07 R22

[TS6]GPIO08 R21

UART0_CTS

UART0_DCD

UART0_DSR

UART0_DTR

UART0_RI

UART0_RTS

UART0_Rx C22

UART0_Tx F19

UART1_CTS

[UART1_DCD

UART1_DSR

UART1_DTR

[UART1_RI

UART1_RTS

UART1_Rx V20

UART1_Tx Y21

UARTSerClk E20

]GPIO28[HDLCEXTxEnA] AA15

]GPIO29[HDLCEXTxEnB] T01

External Peripheral Bus 34

H22 JTAG 36

Trace 37

Trace 37

Trace 37

B22

C19

A06

G20

Internal Peripheral 35

D22

D21

W22

W21

U20

Internal Peripheral 35

V21

22

Page 25

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed Alphabetically (Part 11 of 11)

Signal Name Ball Interface Group Page

V

V

V

V

V

V

V

V

WE

DD

DD

DD

DD

DD

DD

DD

DD

D10

D13

K19

K04

Power 37

N19

N04

W10

W13

Y07 SDRAM 33

Preliminary

23

Page 26

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed by Ball Assignment (Part 1 of 6)

Ball Signal Name Ball S ignal Name Ball Signal Name Ball Signal Name

A01 GND B01 PerPar0 C01 PerData13 D01 PerData10

A02 PerPar1 B02 GND C02 PerData11 D02 PerData08

A03 PerAddr06 B03 PerAddr08 C03 GND D03 PerData14

A04 PerAddr09 B04 PerAddr11 C04 PerAddr05 D04 GND

A05 GND B05 Pe rAddr12 C05 PerAdd7 D05

A06 UAR T0_D SR B06 PerAddr14 C06 PerAddr10 D06 P erAddr04

A07 PerAddr17 B07 PerAddr16 C07 PerAddr13 D07

A08 PerAddr20 B08 PerAddr19 C08 PerAddr15 D08 GND

A09 GND B09 Pe rAddr22 C09 P erAddr21 D09 P erAddr18

A10 PerAddr23 B10 PerAddr25 C10 PerAddr24 D10

A11 PerAddr27 B11 PerAddr26 C11 PerAddr28 D11 GND

A12 PerAddr30 B12 PerAddr31 C12 PerAddr29 D12 GND

A13 GPI O31[PerWE

A14 GND B14 PerCS0 C14 P erCS1 D14 PerOE

A15 PerCS2 B15 PerCS3 C15 PerBLast D15 GND

A16 PerR /W

A17 PerC lk B17 GPIO27[EOT3/TC3] C17 IICSCL[IECSCL] D17 GPIO16[DMAAck3]

A18 GND B18 GPIO25[EOT1

A19 IICSDA[IECSDA] B19 GPIO24[EOT0/TC0] C19 UA RT0_DCD D19 GND

A20 GPIO02[TS2E] B20 GPIO00[TrcClk] C20 GND D20 TmrClk

A21 SysReset

A22 GND B22 UART0_CTS C22 UART0_Rx D22 UART0_RI

] B13 PerWBE0 C13 PerWBE1 D13

B16 PerReady C16 G PI O 26[ EOT2/TC2]D16

/TC1] C18 GPIO01[TS1E] D18

B21 GND C21 SysErr D21 UART0_RTS

OV

OV

V

V

OV

OV

DD

DD

DD

DD

DD

DD

24

Page 27

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed by Ball Assignment (Part 2 of 6)

Ball Signal Name Ball S ignal Name Ball Signal Name Ball Signal Name

E01 GND F01 PerData04 G01 PerData01 H01 MemData30

E02 PerData07 F02 PerData05 G02 PerData02 H02 MemData31

E03 PerData12 F03 PerData09 G03 PerData06 H03 PerData03

OV

E04

E05 No ball F05 No ball G05 No ball H05 No ball

E06 No ball F06 No ball G06 No ball H06 No ball

E07 No ball F07 No ball G07 No ball H07 No ball

E08 No ball F08 No ball G08 No ball H08 No ball

E09 No ball F09 No ball G09 No ball H09 No ball

E10 No ball F10 No ball G10 No ball H10 No ball

E11 No ball F11 No ball G11 No ball H11 No ball

E12 No ball F12 No ball G12 No ball H12 No ball

E13 No ball F13 No ball G13 No ball H13 No ball

E14 No ball F14 No ball G14 No ball H14 No ball

E15 No ball F15 No ball G15 No ball H15 No ball

E16 No ball F16 No ball G16 No ball H16 No ball

E17 No ball F17 No ball G17 No ball H17 No ball

E18 No ball F18 No ball G18 No ball H18 No ball

E19

E20 UARTSerClk F20 GPIO17[IRQ0] G20 UART0_DTR

E21 TMS F21 TDO G21 TDI H21

E22 GND F22 Halt G22 SysClk H22 TRS T

OV

DD

DD

F04 PerData15 G04

F19 UART0_Tx G19

OV

OV

DD

DD

H04 GND

H19 GND

H20 TestEn

AV

DD

25

Page 28

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed by Ball Assignment (Part 3 of 6)

Ball Signal Name Ball S ignal Name Ball Signal Name Ball Signal Name

J01 GND K01 M emDat a27 L01 DQM3 M01 MemData21

J02 MemData28 K02 MemData25 L02 MemData24 M02 MemData20

J03 MemData29 K03 MemData26 L03 MemData23 M03 MemData22

J04 PerData00 K04

J05 No ball K05 No ball L05 No ball M05 No ball

J06 No ball K06 No ball L06 No ball M06 No ball

J07 No ball K07 No ball L07 No ball M07 No ball

J08 No ball K08 No ball L08 No ball M08 No ball

J09 GND K09 GND L09 G ND M09 GND

J10 GND K10 GND L10 G ND M10 GND

J11 GND K11 GND L11 G ND M11 GND

J12 GND K12 GND L12 G ND M12 GND

J13 GND K13 GND L13 G ND M13 GND

J14 GND K14 GND L14 G ND M14 GND

J15 No ball K15 No ball L15 No ball M15 No ball

J16 No ball K16 No ball L16 No ball M16 No ball

J17 No ball K17 No ball L17 No ball M17 No ball

J18 No ball K18 No ball L18 No ball M18 No ball

J19 TCK K19

J20 GPIO18[IRQ1] K20 HDLCEXTxClk L20 HDLCEXRxClk M20 HDLCEXRxFS

J21 PerErr K21 HDLCEXTxDataA L21 GPIO19[IRQ2] M21 GPIO20[IRQ3]

J22 GND K22 HDLCEXTxFS L22 HDLCEXTxDataB M22 HDLCEXRxDataA

V

DD

V

DD

L04 GND M04 GND

L19 GND M19 GND

26

Page 29

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed by Ball Assignment (Part 4 of 6)

Ball Signal Name Ball S ignal Name Ball Signal Name Ball Signal Name

N01 MemData17 P01 GND R01 MemData14 T01

N02 MemData19 P02 MemData16 R02 DQM2 T02 MemData12

N03 MemData18 P03 MemData15 R03 MemData11 T03 GPIO30

V

N04

N05 No ball P05 No ball R05 No ball T05 No ball

N06 No ball P06 No ball R06 No ball T06 No ball

N07 No ball P07 No ball R07 No ball T07 No ball

N08 No ball P08 No ball R08 No ball T08 No ball

N09 GND P09 GND R09 No ball T09 No ball

N10 GND P10 GND R10 No ball T10 No ball

N11 GND P11 GND R11 No ball T11 No ball

N12 GND P12 GND R12 No ball T12 No ball

N13 GND P13 GND R13 No ball T13 No ball

N14 GND P14 GND R14 No ball T14 No ball

N15 No ball P15 No ball R15 No ball T15 No ball

N16 No ball P16 No ball R16 No ball T16 No ball

N17 No ball P17 No ball R17 No ball T17 No ball

N18 No ball P18 No ball R18 No ball T18 No ball

N19

N20 GPIO3[TS1O] P20 GPIO06[TS4] R20 GPIO12[DMAReq3] T20 GPIO15[DMAAck2]

N21 HDLCEXRxDataB P21 GPIO 05[TS3 ] R21 GPIO08[TS6] T21 GPIO11[DMAReq2

N22 GPIO4[TS2O] P22 GND R22 GPIO07[TS5] T22 GPIO10[DMAReq1

DD

V

DD

P04 MemData13 R04 GND T04

P19 GPI O 09[D MAReq0] R19 GND T19

GPIO29[UART1_RI

[HDLCEXTxEnB]

OV

DD

OV

DD

]

]

]

27

Page 30

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed by Ball Assignment (Part 5 of 6)

Ball Signal Name Ball S ignal Name Ball Signal Name Ball Signal Name

U01 DQM1 V01 GND W01 MemData07 Y01 MemData04

U02 MemData10 V02 MemData09 W02 MemData08 Y02 MemData06

U03 DQM0 V03 MemData05 W03 MemData03 Y03 GND

U04 MemData02 V04

U05 No ball V05 No ball W05

U06 No ball V06 No ball W06 ECC7 Y06 ECC1

U07 No ball V07 No ball W07

U08 No ball V08 No ball W08 GND Y08 BankSel1

U09 No ball V09 No ball W09 MemAddr11 Y09 MemAddr08

U10 No ball V10 No ball W10

U11 No ball V11 No ball W11 GND Y11 MemAddr01

U12 No ball V12 No ball W12 GND Y12 MemAddr00

U13 No ball V13 No ball W13

U14 No ball V14 No ball W14 GPIO23[IRQ6] Y14 BA1

U15 No ball V15 No ball W15 GND Y15

U16 No ball V16 No ball W16

U17 No ball V17 No ball W17 PHY0Col[PHY0Rx1Er] Y17

U18 No ball V18 No ball W18

EMC0TxD1

U19

[EMC0Tx0D1]

[EMC0Tx1D]

U20 UART1_DTR

U21 GPIO14[DMAAck1

U22 GPIO13[DMAAck0

] V21 UART1_RTS W 21 UART1_DSR Y21 UART1_Tx

] V22 GND W22 UART1_CTS Y22

OV

DD

OV

V19

V20 UAR T1_Rx W20

DD

W04 GND Y04 ECC6

W19 GND Y19

OV

DD

OV

DD

V

DD

V

DD

OV

DD

OV

DD

EMC0TxD2

[EMC0Tx1D0]

Y05 ECC4

Y07 WE

Y10 MemAddr05

Y13 ClkEn0

PHY0RxD0

[PHY0Rx0D0]

[PHY0Rx0D]

PHYRxD1

Y16

[PHY0Rx0D1]

[PHY0Rx1D]

PHY0RxDV

[PHY0CrS1DV]

PHY0CrS

Y18

[PHY0CrS0DV]

PHY0TxClk

[PHY0RefClk]

Y20 GND

EMC0TxD3

[EMC0Tx1D1]

28

Page 31

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signals Listed by Ball Assignment (Part 6 of 6)

Ball Signal Name Ball S ignal Name Ball Signal Name Ball Signal Name

AA01 MemData01 AB01 GND

AA02 GND AB02 MemData00

AA03 ECC3 AB03 ECC5

AA04 DQMCB AB04 ECC2

AA05 ECC0 AB05 GND

AA06 BankSel3 AB06 BankSel2

AA07 BankSel0 AB07 MemAddr12

AA08 MemAddr10 AB08 MemAddr09

AA09 MemAddr07 AB09 GND

AA10 MemAddr04 AB10 MemAddr06

AA11 MemAddr03 AB11 MemAddr02

AA12 CAS AB12 RAS

AA13 ClkEn1 AB13 M emClkOut1

AA14 MemClkOut0 AB14 GND

GPIO28[UART1_DCD

AA15

[HDLCEXTxEnA]

AA16 EMC0MDIO AB16 EMC0MDClk

AA17 GPIO21[IRQ4] AB17 GPIO22[IRQ5]

PHY0RxD2

AA18

[PHY0Rx1D0]

PHY0RxD3

AA19

[PHY0Rx1D1]

PHY0RxErr

AA20

[PHY0Rx0Er]

AA21 GND AB21

EMC0TxD0

AA22

[EMC0Tx0D0]

[EMC0Tx0D]

]

AB15 BA0

AB18 GND

AB19 PHY0RxClk

EMC0TxErr

AB20

[EMC0Tx1En]

EMC0TxEn

[EMC0Tx0En]

[EMC0Sync]

AB22 GND

29

Page 32

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signal Description

The following table provides a summary of the number of package pins (balls) associated with each functional

interface group.

Pin Summary

Group No. of Pins

Nonmultiplexed Signals 167

Multiplexed Signals 48

Total Signal Pins 215

AV

DD

OV

DD

V

DD

Gnd 48

Gnd (and thermal) 36

Reserved 0

Total Pins 324

1

16

8

Multiplexed pins

In the table “Signal Functional Description” on page 32, each external signal is listed along with a short

description of the signal function. The signals are grouped together according to their function. Some signals

are multiplexed on the same package pin (ball) so that the pin can be used for different functions. In most

cases, the signal name is shown in this table unaccompanied by multiplexed signal names that may be

associated with it. In cases where multiplexed signals are in the same functional group, the names appear as

a default signal followed by secondary signals in square brackets (for example, EMC0TxErr[EMC0Tx1En]).

Active-low signals (for example, RAS

) are marked with an overline. Any signal that is not the primary (default)

signal on a multiplexed pin is shown in square brackets.

The active signal on a multiplexed pin is controlled by programming. It is expected that in any single

application, a particular pin will always be programmed to serve the same function. The flexibility of

multiplexing allows a single chip to offer a richer pin selection than would otherwise be possible.

Initialization Strapping

One group of pins is used as strapped inputs during system reset. These pins function as strapped inputs

only during reset and are used for other functions during normal operation (see “Initialization” on page 51).

Note that the use of these pins for strapping is not considered multiplexing since the strapping function is not

programmable.

Pull-up and Pull-down Resistors

Pull-up and pull-down resistors are used for strapping during reset and to retain unused or undriven inputs in

an appropriate state. The recommended pull-up value of 3k

tolerant I/Os) and pull-down value of 1k

Ω to GND, applies only to individually terminated signals. To prevent

Ω to +3.3V (10kΩ to +5V can be used on 5V

possible damage to the device, I/Os capable of becoming outputs must never be tied together and terminated

through a common resistor.

If your system-level test methodology permits, input-only signals can be connected together and terminated

through either a common resistor or directly to +3.3V or GND. When a resistor is used, its value must ensure

30

Page 33

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

that the grouped I/Os reach a valid logic zero or logic one state when accounting for the total input current into

the NPe405L.

Unused I/Os

Strapping of some pins may be necessary when they are unused. Although the NPe405L requires only the

pull-up and pull-down terminations as specified in the “Signal Functional Description” on page 32, good

design practice is to terminate all unused inputs or to configure I/Os such that they always drive. If unused,

the peripheral and SDRA M bus should be configured and terminated as follows:

• Peripheral interface—PerAddr00:31, PerData00:31, and all of the control signals are driven by default.

Terminate PerReady high and PerError low.

• SDRAM—Program SDRAM0_CFG[EMDULR]=1 and SDRAM0_CFG[DCE]=1. This causes the NPe405L

to actively drive all of the SDRAM address, data, and control signals.

External Peripheral Bus Control Signals

All external peripheral bus control signals (PerCS0:

set to the high-impedance state when ExtReset

Embedded Processor User’s Manual, the peripheral bus controller can be programmed via EBC0_CFG to

float some of these control signals between transactions. As a result, a pull-up resistor should be added to

those control signals where an undriven state may affect any devices receiving that particular signal.

The following table lists all of the I/O signals provided by the NPe405L. Please see “Signals Listed

Alphabetically” on page 13 for the pin number to which each signal is assigned. In cases where a multiplexed

signal (indicated by the square brackets) is shown without the other signals that are assigned to that pin, you

can see what the other signals are by referring to the same table.

3, PerR/W, PerWBE0:1, PerOE, PerWE, PerBLast) are

=0. In addition, as detailed in the PowerNP NPe405L

31

Page 34

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signal Functional Description (Part 1 of 6)

Notes:

1. Receiver input has hy steresis.

2. Must pull up. See “Pull-up and Pull-down Resistors” on page 30 for recommen ded termination values.

3. Must pull down. See “Pull-up and Pull-down R esistors” on page 30 for recommended termination values.

4. If not used, must pull up.

5. If not used, must pull down.

6. Strapping input during reset; pull up or pull down as required.

7. Pull-up may be required. See “External Peripheral Bus Control Signals” on page 31.

Signal Name Description I/O Type

HDLCEX Interface

HDLCEXTxClk Transmit Clock I 3.3V LVTTL

HDLCEXTxFS Transmit Frame Synchronization I 3.3V LVTTL

HDLCEXTxDataA Transmit Data port A O 3.3V LVTTL

HDLCEXTxDataB Transmit Data port B O 3.3V LVTTL

HDLCEXRxClk Receive Clock I 3.3V LVTTL

HDLCEXRxFS Receive Frame Synchronization I 3.3V LVTTL

HDLCEXRxDataA Receive Data port A I 3.3V LVTTL

HDLCEXRxDataB Receive Data port B I 3.3V LVTTL

[HDLCEXTxEnA] Transmit Enable port A O

[HDLCEXTxEnB] Transmit Enable port B O

Ethernet Interface

EMC0MDClk

EMC0MDIO

EMC0TxD0[EMC0Tx0D0][EMC0Tx0D]

EMC0TxD1[EMC0Tx0D1][EMC0Tx1D]

EMC0TxD2[EMC0Tx1D0]

EMC0TxD3[EMC0Tx1D1]

EMC0TxEn[EMC0Tx0E n][EMC0Sync]

EMC0TxErr[EMC0Tx1En]

Management Data Clock. The MDClk is sourced to the

PHY. Management information is transferred

synchronously with respect to this clock (MII, RMII, and

SMII).

Management Data Input/Output is a bidirectional signal

between the Ethernet controller and the PHY. It is used to

transfer control and status information (MII, RMII, and

SMII).

Transmit Data. A nibble wide data bus towards the net.

The data is synchronous with PHY0TxClk

(MII 0[RMII 0, 1][SMII 0, 1]).

Transmit Enable. This signal is driven by EMAC2 to the

PHY. Data is valid during the active state of this signal.

Deassertion of this signal indicates end of frame

transmission. This signal is synchronous with PHYTxClk

(MII 0[RM II 0]).

or

SMII Sync.

Transmit Error. This signal is generated by the Ethernet

controller, is connected to the PHY and is synchronous

with the PHY0TxClk. It informs the PHY that an error was

detected (MII 0).

or

Transmit Enable [RMII 1].

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

O3.3V LVTTL

5V tolerant

I/O

3.3V LVTTL

O 3.3V LVTTL

O 3.3V LVTTL

O3.3V LVTTL

Notes

1, 4

32

Page 35

PowerNP NPe405L Embedded Processor Data Sheet

Signal Functional Description (Part 2 of 6)

Notes:

1. Receiver input has hysteresis.

2. Must pull up. See “Pull-up and Pull-down Resistors” on page 30 for recommended termination values.

3. Must pull down. See “Pull-up and Pull-down R esistors” on page 30 for recommended termination values.

4. If not used, must pull up.

5. If not used, must pull down.

6. Strapping input during reset; pull up or pull down as required.

7. Pull-up may be required. See “External Peripheral Bus Control Signals” on page 31.

Preliminary

Signal Name Description I/O Type

PHY0Col[PHY0Rx1Er]l

PHY0CrS[PHY0CrS0DV]

PHY0RxClk

PHY0RxD0[PHY0Rx 0 D 0][PHY0Rx0D]

PHY0RxD1[PHY0Rx 0 D 1][PHY0Rx1D]

PHY0RxD2[PHY0Rx1 D 0]

PHY0RxD3[PHY0Rx1 D 1]

PHY0RxDV[PHY0CrS1DV]

PHY0RxErr[PHY0Rx 0Er]

PHY0TxClk[PHY0RefClk]

SDRAM Interface

MemAddr00:31

MemAddr12:00

BA1:0 Bank Address support ing up to 4 internal b anks O 3.3V LVTTL

RAS

CAS

DQM0:3

DQMCB DQM for ECC check bits. O 3.3V LVTTL

Collision [receive error] signal from the PHY. This is an

asynchronous signal (MII 0).

or

Receive Error ([RMII 1]).

Carrier Sense signal from the PHY. This is an

asynchronous signal (MII 0).

or

Carrier sense data valid ([RMII 0]).

Receiver medium clock. This signal is generated by the

PHY (MII 0).

Received Data. This is a nibble wide bus from the PHY.

The data is synchronous with PHY0RxClk

(MII 0[RMII 0, 1][SMII 0, 1]).

Receive Data Valid. Data on the Data Bus is valid when

this signal is activated. Deassertion of this signal indicates

end of the frame reception (MII 0).

or

Carrier sense data valid ([RMII 1])

Receive Error. This signal comes from the PHY and is

synchronous with PHY0RxClk (MII 0 [RMII 0]).

Transmit medium clock. This signal is generated the PHY

([MII 0]).

or

Reference Clock [RMII and SMII].

Memory Data bus

Notes:

1. MemAddr00 is the most significant bit (msb).

2. MemData31 is the least significant bit (lsb).

Memory Address bus.

Notes:

1. MemAddr12 is the most significant bit (msb).

2. MemAddr00 is the least significant bit (lsb).

Row Address Strobe. O 3.3V LVTTL

Column Address Strobe. O 3.3V LVTTL

DQM for byte lane 0 (MemAddr00:7),

1 (MemAddr08:15),

2 (MemData16:23), and

3 (MemData24:31)

I/O 3.3V LVTTL

5V tolerant

I

3.3V LVTTL

5V tolerant

I

3.3V LVTTL

5V tolerant

I

3.3V LVTTL

5V tolerant

I

3.3V LVTTL

5V tolerant

I

3.3V LVTTL

5V tolerant

I

3.3V LVTTL

5V tolerant

I

3.3V LVTTL

O3.3V LVTTL

O3.3V LVTTL

Notes

1, 5

1, 4

1, 4

1, 5

1, 5

1, 4

33

Page 36

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signal Functional Description (Part 3 of 6)

Notes:

1. Receiver input has hy steresis.

2. Must pull up. See “Pull-up and Pull-down Resistors” on page 30 for recommen ded termination values.

3. Must pull down. See “Pull-up and Pull-down R esistors” on page 30 for recommended termination values.

4. If not used, must pull up.

5. If not used, must pull down.

6. Strapping input during reset; pull up or pull down as required.

7. Pull-up may be required. See “External Peripheral Bus Control Signals” on page 31.

Signal Name Description I/O Type Notes

ECC0:7 ECC check bits 0:7. I/O 3.3V LVTTL

BankSel0:3

ClkEn0:1 SDRAM Clock Enable. O 3.3V LVTTL

MemClkOut0:1

External Peripheral Bus Interface

PerData00:15

PerAddr04:31 External peripheral address bus . O

PerPar0:1 External peripheral byte parity signals. I/O

PerWBE0:

[PerWE

PerCS0

PerOE

PerR/W

Select up to four external SDRAM banks. O 3.3V LVTTL

WE

1

]

:3

Write Enable. O 3.3V LVTTL

Two copies of an SDRAM clock allows, in some cases,

glueless SDRAM attachment without requiring this signal

to be repowered by a PLL or zero-delay buffer.

External peripheral data bus .

Note: PerData00 is the most significant bit (msb) on this

bus.

Peripheral write-bte enable. Byte-enables which are valid

for an entire cycle or write-byte-enables which are valid for

each byte on each data transfer, allowing partial word

transactions. Used by either external bus controller or DMA

controller depending upon the type of transfer involved.

Peripheral write enable. Low when any of the two PerWBE

signals are low.

Peripheral Chip Selects O

Peripheral output enable. Used by either the external bus

controller or the DMA controller depending upon the type

of transfer involved. When the NPe405L is the bus master,

it enables the peripherals to drive the bus.

Peripheral read/write. Used by either the external bus

controller or DMA controller depending upon the type of

transfer involved. High indicates a read from memory, low

indicates a write to memory.

O3.3V LVTTL

I/O

O

I/O

O

O

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

1

1

2, 7

7

7

34

PerReady Indicates peripheral is ready to transfer data. I

PerBLast

PerClk Peripheral Clock. Used by synchronous peripherals. O

PerErr Used to indicate errors from peripherals. I

Peripheral burst last. Used to indicate the last transfer of a

memory access.

O

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

1

7

1, 5

Page 37

PowerNP NPe405L Embedded Processor Data Sheet

Signal Functional Description (Part 4 of 6)

Notes:

1. Receiver input has hysteresis.

2. Must pull up. See “Pull-up and Pull-down Resistors” on page 30 for recommended termination values.

3. Must pull down. See “Pull-up and Pull-down R esistors” on page 30 for recommended termination values.

4. If not used, must pull up.

5. If not used, must pull down.

6. Strapping input during reset; pull up or pull down as required.

7. Pull-up may be required. See “External Peripheral Bus Control Signals” on page 31.

Preliminary

Signal Name Description I/O Type

[DMAReq0:3]

[DMAAck0:3

[EOT0:3

]

/TC0:3]

Internal Peripheral Interface

UARTSerClk

UART0_Rx UART0 Receive data. I

UART0_Tx UA RT0 Transmit data. O

[UART0_DCD

[UART0_DSR

[UART0_CTS

[UART0_DTR

[UART0_RTS

[UART0_RI

] UAR T 0 Data C arrier Detec t. I

] UART0 Data Set Ready. I

] UART0 Clear To Send. I

] UART0 Data Terminal Ready. O

] UART0 Request To Send. O

] UART0 Ring Indicator. I

DMA request. Used by peripherals to request a data

transfer. Following a system reset, the default mode of the

signals is active-low. They may be programmed to activehigh using the DMA0_POL register.

DMA acknowledge. Used to indicate to peripherals that

data transfer is complete. Following a system reset, the

default mode of the signals is active-low. They may be

programmed to active-high using the DMA0_POL register.

End Of Transfer/Terminal Count. Indication by peripherals

that all data has been transfered, or by DMA controller that

programmed amount of data has been transfered.

Following a system reset, the default mode of the signals is

active-low. They may be programmed to active-high using

the DMA0_POL register.

Serial Clock used to provide an alternative clock to the

internally generated serial clock. Used in cases where the

allowable internally generated baud rates are not

satisfactory. This input can be individually connected to

either or both UART0 and UART1.

I

O

I/O

I

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL r

Notes

1

1

1

1

1

1

1

1

35

Page 38

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Signal Functional Description (Part 5 of 6)

Notes:

1. Receiver input has hy steresis.

2. Must pull up. See “Pull-up and Pull-down Resistors” on page 30 for recommen ded termination values.

3. Must pull down. See “Pull-up and Pull-down R esistors” on page 30 for recommended termination values.

4. If not used, must pull up.

5. If not used, must pull down.

6. Strapping input during reset; pull up or pull down as required.

7. Pull-up may be required. See “External Peripheral Bus Control Signals” on page 31.

Signal Name Description I/O Type Notes

I

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

UART1_Rx UART1 Receive data. I

UART1_Tx UA RT1 Transmit data. O

[UART1_DCD

[UART1_DSR

[UART1_CTS

[UART1_DTR

[UART1_RTS

[UART1_RI

IICSCL IIC Serial Clock. I/O

IICSDA IIC Serial Data. I/O

Interrupts Interface

[IRQ0:6] Interrupt Requests. I

JTAG Interface

TDI Test Data In. I

TMS Test Mode Select. I

TDO Test Data Out. O

TCK Test Clock. I

TRST

] UAR T 1 Data C arrier D etec t. I

] UART1 Data Set Ready. I

] UART1 Clear To Send. I

] UART1 Data Terminal Ready. O

] UART1 Request To Send. O

] UART1 Ring Indicator. I

Test Reset. TRST must be low at power-on to reset the

JTAG boundary scan state machine.

1

6

1, 4

1, 4

1, 4

6

6

1, 4

1, 2

1, 2

1

1, 4

1, 4

1, 4

5

36

Page 39

PowerNP NPe405L Embedded Processor Data Sheet

Signal Functional Description (Part 6 of 6)

Notes:

1. Receiver input has hysteresis.

2. Must pull up. See “Pull-up and Pull-down Resistors” on page 30 for recommended termination values.

3. Must pull down. See “Pull-up and Pull-down R esistors” on page 30 for recommended termination values.

4. If not used, must pull up.

5. If not used, must pull down.

6. Strapping input during reset; pull up or pull down as required.

7. Pull-up may be required. See “External Peripheral Bus Control Signals” on page 31.

Preliminary

Signal Name Description I/O Type

System Interface

SysClk Main System Clock input. I

SysReset

SysErr Set to 1 when a Machine Check is generated. O

Halt

GPIO00:31

TestEn

TmrClk

Trace Interface

[TS1E]

[TS2E]

[TS1O]

[TS2O]

[TS3:6]

[TrcClk]

Power Pins

GND

V

OV

AV

Other Pins

Reserved Do not connect signals, voltage, or ground to these pins. n/a n/a

DD

DD

DD

3.3V Analog

Wire w/ESD

Main System Reset. I/O

Halt from external debugger. I

General Purpose I/O. To access this function, software

must toggle a DCR bit.

Test Enable. Used only for manufacturing tests. Pull down

for normal operation.

This input must toggle at a rate of less than one half the

CPU core frequency (less than 100MHz in most cases). In

most cases this input toggles much slower (in the 1MHz to

10MHz range).

Even Trace execution status.To access this function,

software must toggle a DCR bit.

Odd Trace execution status. To access this function,

software must toggle a DCR bit.

Trace Status. To access this function, software must toggle

a DCR bit.

Trace interface clock. A toggling signal that is always half

of the CPU core frequency. To access this function,

software must toggle a DCR bit.

Ground

Note: J09-J14, K09-K14, L09-L14, M09-M14, N09-N14,

and P09-P14 are also thermal balls.

Logic voltage—2.5V I Hardwire

Output driver voltage—3.3V I Hardwire

Filtered PLL voltage—2.5V I

I/O

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

5V tolerant

3.3V LVTTL

3.3V LVTTL

I

Rcvr w/PD

5V tolerant

I

3.3V LVTTL

5V tolerant

O

3.3V LVTTL

5V tolerant

O

3.3V LVTTL

5V tolerant

O

3.3V LVTTL

5V tolerant

O

3.3V LVTTL

I Hardwire

3.3V DC

Wire w/ESD

Notes

1, 2

1

1

1

1

37

Page 40

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Absolute Maximum Ratings

The absolute maximum ratings below are stress ratings only. Operation at or beyond these maximum ratings can cause

permanent damage to the device.

Characteristic Symbol Value Unit

Supply Voltage (Internal Logic)

Supply Voltage (I/O Interface)

PLL Supply Voltage

Input Voltage (3.3V LVTTL receivers)

Input Voltage (5.0V LVTTL receivers)

Storage Temperature Range

Case temperature under bias

Notes:

1. All voltages are specified with respect to ground (GND).

2. AV

should be derived from VDD using the following circuit:

DD

2

V

OV

AV

T

V

V

STG

T

DD

DD

DD

IN

IN

C

0 to +2.7 V

0 to +3.6 V

0 to +2.7 V

-0.6 to (OVDD + 0.6)

-0.6 to (OVDD + 2.4)

-55 to +150 °C

-40 to +120 °C

V

V

L1 – 2.2µH SMT inductor (equivalent to MuRata

V

DD

L1

C1

C2

C3

AV

DD

LQH3C2R2M34) or SMT chip ferrite bead (equivalent

to MuRata BLM31A700S)

C1 – 3.3

C2 –

C3 – 0.01

µF SMT tantalum

0.1µF SMT monolithic ceramic capacitor with X7R

dielectric or equivalent

µF SMT monolithic ceramic capacitor with X7R

dielectric or equivalent

Package Thermal Specifications

The NPe405L is designed to operate within a case temperature range of -40°C to 85°C. Thermal resistance values for the

E-PBGA packages in a convection environment are as follows:

Airflow

Package—Thermal Resistance

23mm, 324-balls—Junction-to-Case

23mm, 324-balls—Case-to-Ambient

Notes:

1. For a chip mounted on a JEDEC 2S2P card without a heat sink.

2. For a chip mounted on a card with at least one signal and two power planes, the following relationships exist:

a. Case temperature, T

b. T

= TC – P×θCA, where TA is ambient temperature and P is power consumption.

A

= T

c. T

CMax

– P×θJC, where T

JMax

, is measured at top center of case surface with device soldered to circuit board.

C

1

is maximum junction temperature and P is power consumption.

JMax

Symbol

θ

JC

θ

CA

0 (0) 100 (0.51) 200 (1.02)

222°C/W

17 15 14 °C/W

ft/min (m/sec)

Unit

38

Page 41

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Recommended DC Operating Conditions

Device operation beyond the conditions specified is not recommended. Extended operation beyond the recommended

conditions can affect device reliability.

Parameter Symbol Minimum Typical Maximum Unit Notes

Logic Supply Voltage

I/O Supply Voltage

PLL Supply Voltage

Input Logic High (3.3V LVTTL

receivers)

Input Logic High (2.5V CMOS

receivers)

Input Logic High (5.0V LVTTL

receivers)

Input Logic Low

Output Logic High

Output Logic Low

3.3V I/O input current (no pull-up or

pull-down)

Input Current (with internal pulldown)

Input Current (with internal pull-up)

Input Max Allowable Overshoot

(2.5V CMOS receivers)

Input Max Allowable Overshoot

(3.3V LVTTL receivers)

Input Max Allowable Overshoot

(5.0V LVTTL receivers)

Input Max Allowable Undershoot

(3.3V or 5.0V receivers)

Output Max Allowable Overshoot

(3.3V or 5.0V receivers)

Output Max Allowable Undershoot

(3.3V and 5.0V receivers)

Case Temperature

V

OV

AV

V

V

V

V

V

V

I

I

I

V

IMAO25

V

IMAO3

V

IMAO5

V

IMAU

V

OMAO

V

OMAU3

T

DD

DD

DD

IH

IH

IH

IL

OH

OL

IL1

IL2

IL3

C

Notes:

1. See “5V-Tolerant I/O Input Current” on page 40

+2.3 +2.5 +2.7 V

+3.0 +3.3 +3.6 V

+2.3 +2.5 +2.7 V

+2.0

+1.7

OV

V

DD

DD

V

V

+2.0 +5.5 V

0+0.8V

+2.4

OV

DD

V

0+0.4V

±10

±10 (@ 0V) 400 (@ 3.6V)

-250 (@ 0V) ±10 (@ 3.6V)

VDD + 0.6

OV

+ 0.6

DD

µA

µA

µA

V

V

+5.5 V

− 0.6

− 0.6

− 40

OVDD + 0.3

+85

V

V

V

°C

39

Page 42

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

5V-Tolerant I/O Input Current

100

0

-100

A)

-200

µ

-300

-400

Input Current (

-500

-600

-700

Input Capacitance

3.3V LVTTL I/O)

5 V tolerant LVTTL I/O

RX only pins

1.0 2.0 3.0 4.0 5.00.0

Input Voltage (V)

Parameter Symbol Maximum Unit Notes

C

IN1

C

IN2

C

IN4

2.5 pF

3.5 pF

0.75 pF

40

Page 43

PowerNP NPe405L Embedded Processor Data Sheet

DC Electrical Characteristics

Parameter Symbol Minimum Typical Maximum Unit

Active Operating Current for V

Active Operating Current for V

Active Operating Current for V

Active Operating Current for O V

Active Operating Current for O V

Active Operating Current for O V

Active Operating Current for AV

Active Operating Power @ 133MHz

Active Operating Power @ 200MHz

Active Operating Power @ 266MHz

Notes:

1. Maximum power is characterized at V

while running an application designed to maximize power consumption. The maximum power values are measured with the

following clock rate combinations:

a. CPU=133.33MHz, PLB=66.66MHz, OPB=66.66MHz, EBC=33.33MH z

b. CPU=200 MHz, PLB=100MHz, OPB=50MHz, EBC=50MHz

c. CPU=266.66MHz, PLB=66.66MHz, OPB=66.66MHz, EBC=33.33MHz

@ 133MHz I

DD

@ 200MHz I

DD

@ 266MHz I

DD

@ 133MHz I

DD

@ 200MHz I

DD

@ 266MHz I

DD

DD

=2.7V, OVDD=3.6V, TC=85°C, across the silicon process (worse case to best case),

DD

ODD

ODD

ODD

I

ADD

P

P

P

DD

DD

DD

DD

DD

DD

444 497 543 mA

468 565 676 mA

490 590 700 mA

17 23 36 mA

24 36 51 mA

27 44 61 mA

5.566.5mA

1.1 1.3

1.4 1.7

1.5 1.8

1.6

2.1

1

1

2

1

Preliminary

W

W

W

Test Conditions

Clock timing and switching characteristics are specified in accordance

with operating conditions shown in the table “Recommended DC

Operating Conditions.” AC specifications are characterized at

= 3.00V and TJ = 85°C with the 50pF test load shown in the

OV

DD

figure at right.

Output

Pin

50pF

41

Page 44

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Clocking Specifications

Symbol Parameter Min Max Units

SysClk Input

F

C

T

C

T

CS

T

CH

T

CL

Note: Input slew rate > 2V/ns

MemClkOut Output

F

C

T

C

F

C

T

C

F

C

T

C

T

CH

T

CL

Other Clocks

F

C

F

C

F

C

F

C

F

C

F

C

F

C

Notes:

1. If HDLCEX is not used, the maximum OPB frequency is 66.66MHz.

SysClk clock input frequency 25 66.66 MHz

SysClk clock period 15 40 ns

Clock edge stability (phase jitter, cycle to cycle) 0.15 ns

Clock input high time 40% of nominal period 60% of nominal period ns

Clock input low time 40% of nominal period 60% of nominal period ns

MemClkOut clock output frequency–133MHz 66.66 MHz

MemClkOut clock period–133MHz 15 ns

MemClkOut clock output frequency–200MHz 100 MHz

MemClkOut clock period–200MHz 10 ns

MemClkOut clock output frequency–266MHz 133.33 MHz

MemClkOut clock period–266MHz 7.5 ns

Clock output high time 45% of nominal period 55% of nominal period ns

Clock output low time 45% of nominal period 55% of nominal period ns

VCO frequency 400 800 MHz

PLB frequency–133MHz 66.66 MHz

PLB frequency–200MHz 100 MHz

PLB frequency–266MHz 133.33 MHz

OPB frequency–133MHz

50

1

OPB frequency–200MHz 50 MHz

OPB frequency–266MHz

50

1

MHz

MHz

Clocking W aveform

42

2.0V

1.5V

0.8V

T

CH

T

C

T

CL

Page 45

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Spread Spectrum Clocking

Care must be taken when using a spread spectrum clock generator (SSCG) with the NPe405L. This

controller uses a PLL for clock generation inside the chip. The accuracy with which the PLL follows the SSCG

is referred to as tracking skew. The PLL bandwidth and phase angle determine how much tracking skew

there is between the SSCG and the PLL for a given frequency deviation and modulation frequency. When

using an SSCG with the NPe405L the following conditions must be met:

• The frequency deviation must not violate the minimum clock cycle time. Therefore, when operating the

NPe405L with one or more internal clocks at their maximum supported frequency, the SSCG can only

lower the frequency.

• The maximum frequency deviation cannot exceed

40kHz. In some cases, on-board NPe405L peripherals impose more stringent requirements (see Note 1).

• Use the peripheral bus clock (PerClk) for logic that is synchronous to the peripheral bus since this clock

tracks the modulation.

• Use the SDRAM MemClkOut since it also tracks the modulation.

Please refer to the application note Using a Spread Spectrum Clock Generator with the PowerPC 405GP for

additional details. This application note is available on the IBM Microelectronics web site at

http://www.chips.ibm.com.

Notes:

1. The serial port baud rates are synchronous to the modulated clock. The serial port has a tolerance of

approximately 1.5% on baud rate before framing errors begin to occur. The 1.5% tolerance assumes that

the connected device is running at precise baud rates. If an external serial clock is used the baud rate is

unaffected by the modulation

2. Ethernet operation is unaffected.

3. IIC operation is unaffected.

Caution: It is up to the system designer to ensure that any SSCG used with the NPe405L meets the above

requirements and does not adversely affect other aspects of the system.

−3%, and the modulation frequency cannot exceed

43

Page 46

Preliminary

PowerNP NPe405L Embedded Processor Data Sheet

Peripheral Interface Clock Timings

Parameter Min Max Units

EMC0MDClk output frequency – 2.5 MHz

EMC0MDClk period 400 – ns

EMC0MDClk output high time 160 – ns

EMC0MDClk output low time 160 – ns

PHY0TxClk input frequency 2.5 25 MHz

PHY0TxClk period 40 400 ns

PHY0TxClk input high time 35% of nominal period – ns

PHY0TxClk input low time 3 5% of no minal period – ns

PHY0RxClk input frequency 2.5 25 MHz

PHY0RxClk period 40 400 ns