Page 1

DATA BULLETIN

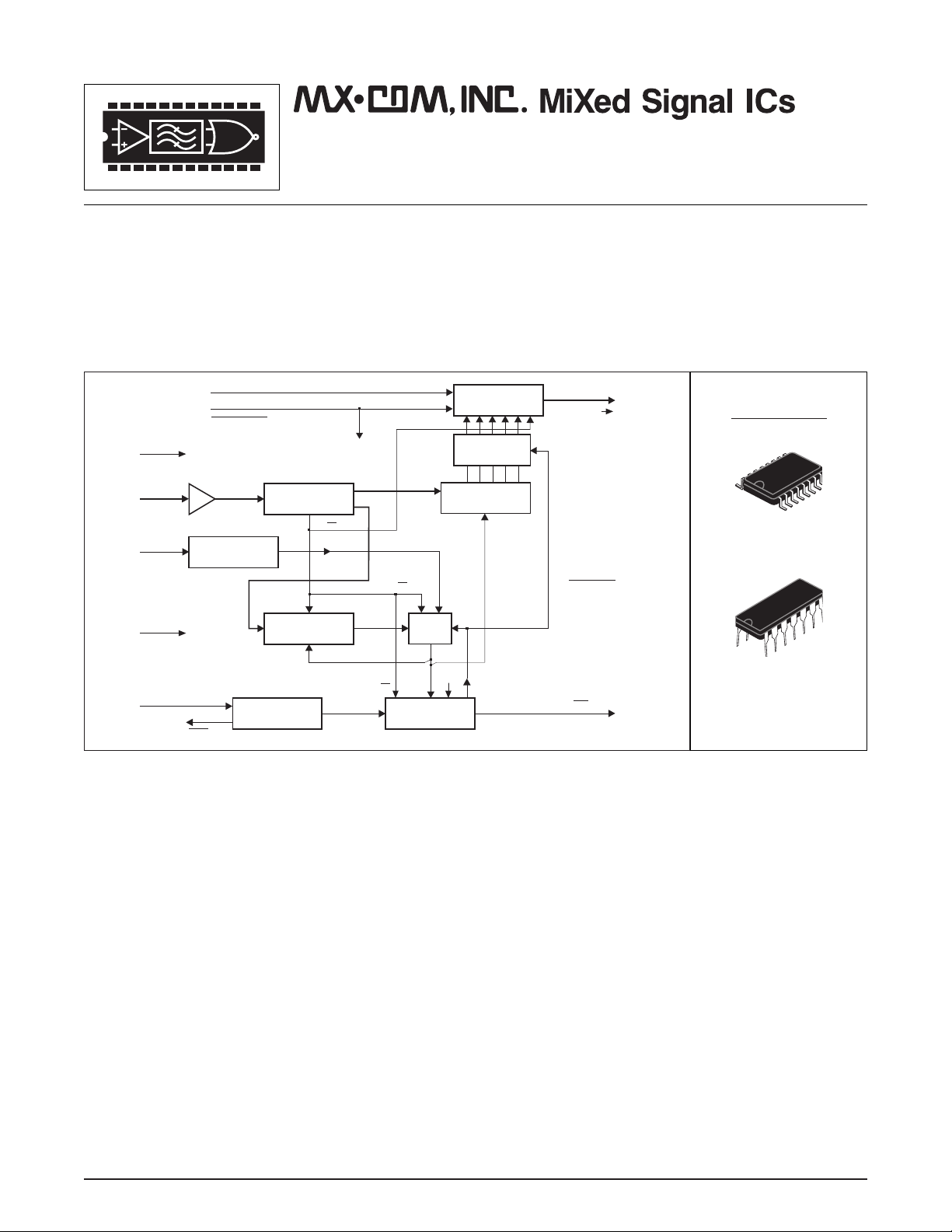

MX613

MXCOM MiXed Signal CMOS

Covers Worldwide Call Progress Frequencies

(300Hz TO 2150Hz)

Decode Single or Modulated Tones

SERIAL CLOCK

CHIP SELECT

V

DD

SIGNAL IN

LEVEL IN

V

SS

XTAL/CLOCK

3.579545MHz

XTAL

LEVEL

DETECTOR

f/4

BAND SELECTOR

SIGNAL QUALITY

ASSESSOR

CLOCK

GENERATOR

FILTER &

HI / BANDLO

RESET

CS

f

f/4

GOOD/BAD

HI/LO

HI/LO

DECODE

ON / OFF

LOGIC

TIMER

LO = 39.4ms

HI = 13.16ms

COUNT

RESET

CS

Global Call Progress Detector

PRELIMINARY INFORMATION

Analog In / Serial Data Out

µProcessor Compatible Outputs

Speech Discrimination Ability

Low Power Operation

SERIAL OUTPUT

PORT (6-BITS)

LATC H

FREQUENCY

COUNTER

RESET

TIME

DAT A OUT

012345

TIME

V

IRQ

AVAILABLE

PACKAGES

MX613DW

16-pin SOIC

BIAS

14-pin PDIP

MX613P

The MX613 is a wide-band, ‘N-Tone’ non-predictive tone decoder that measures telephone system call progress

tones in PABX, Pay/Feature-Phone, Fax and Modem systems.

Adhering to Must/Must-Not Decode limits and able to measure inband frequencies in outband modulation, this

decoder measures the frequency of input signals in the range 300 to 2,150Hz. The result of each measurement is

presented to a system µProcessor as a 6-bit serial word.

The decode frequency range, which covers the world's call progress application spectrum, is processed internally

as two bands: LO = 300 to 660Hz and HI = 900 to 2150Hz. Frequency measurement is achieved by counting the

number of cycles in a set time period

(LO = 39.47ms or HI = 13.16ms). Bad signal/level quality or NOTONE results in a count-abort, timing-reset and no

output from the decoder.

Front-end filtering is achieved using our patented Auto-Correlator. Current frequency information is output for the

µProcessor using a Serial Data, Clock and Interrupt interface.

Data from the MX613 should be processed by a µProcessor whose algorithms are able to recognize the

frequency, sequence and/or cadence of input signals as national call progress information; e.g.: ‘Dial,’ ‘Busy,’

‘Number-Unobtainable,’ ‘Ringing’ and automatic tones used by fax and modem systems. Software can be simply

configured to reject speech frequencies.

Available in SOIC and PDIP packages, this low-cost, mixed signal IC has a typical power requirement of less

than 1mA at 3 volts and utilizes a telecom-system clock input of 3.579545MHz to maintain frequency accuracy.

© 1997 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 910 744-5050 Fax: 910 744-5054 Doc. # 20480086.003

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USAAll trademarks and service marks are held by their respective companies

Page 2

Global Call Progress Tone Detector 2 MX613 Preliminary Information

Pin Number Function

MX613DW

1

2

3

4

5

6

MX613P

1

2

3

4

5

6

Xtal/Clock: The input to the on-chip clock oscillator inverter. A 3.579545MHz Xtal or

externally derived telephone system clock (f

) should be connected here. Operation

XTAL

of the MX613 without a suitable Xtal/Clock input may cause device damage.

Xtal: The output of the on-chip clock oscillator inverter. See Figure 2.

No internal connection.

V

: The internal circuitry bias line, held at VDD/2 this pin must be decoupled to VSS.

BIAS

Level In: The input for level discrimination. This input is internally biased to V

. Signals

BIAS

must be a.c. coupled, and the audio signal must be fed to both this pin and the Signal In

pin. Correct level detection determines the operation of this device (see Principles of

Decoder Operation). But if you wish to disregard the amplitude of the input levels, the

MX613 may be permanently enabled by pulling this pin to VDD and disabled by pulling to

VSS.

Signal In: The input for frequency discrimination and decoding. This input is internally

biased to V

. Signals must be a.c. coupled. The audio signal must be fed to both this

BIAS

pin and the Level In pin.

7

8

9

10

11

12

13

14

7

8

9

10

11

12

No internal connection.

VSS: Signal ground (GND).

No internal connection.

No internal connection.

IRQ: This Interrupt Request output from the MX613 is ‘wire-OR able’ allowing the

interrupt outputs of other peripherals to be combined and connected to the Interrupt input

of a µProcessor. This input has a low-impedance pulldown to V

when active and a high-

SS

impedance when inactive. An interrupt is produced on completion of a HI or LO frequency

measurement.

Serial Clock: The serial clock from the µProcessor. Data Out is clocked into the

µProcessor on the rising edge of the Serial Clock. See Data-Read Timing diagram.

Chip Select: A logic “0” at this input will select this device.

Data Out: The serial data output. Under the control of the Chip Select and Serial Clock

inputs, data should be read from this output in 6-bit blocks MSB (Bit-5) first.

If 8 serial clock pulses are applied, two additional logic “0s” will be output after Bit-0.

15

16

13

14

No internal connection.

VDD: Positive supply input. A single, stable supply is required. Levels and voltages within

the MX613 are dependent upon this supply. This pin should be decoupled to VSS by a

capacitor located close to the MX613 pins.

© 1997 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 910 744-5050 Fax: 910 744-5054 Doc. # 20480086.003

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USAAll trademarks and service marks are held by their respective companies

Page 3

Global Call Progress Tone Detector 3 MX613 Preliminary Information

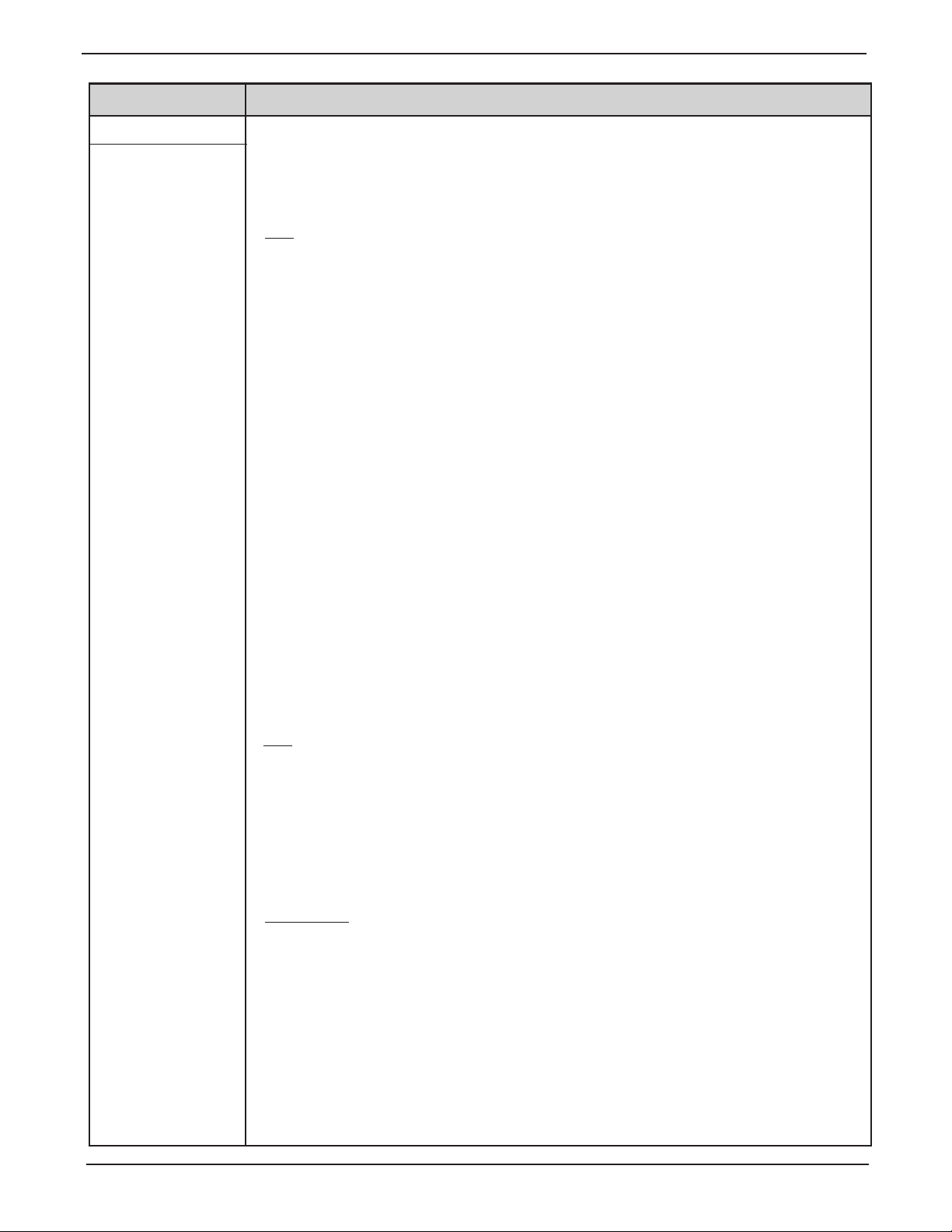

Application Information

1

R

2

X

1

C

5

2

C

6

XT AL/CLOCK

XT AL

1

2

3

V

AUDIO SIGNAL

C

2

C

1

BIAS

LEVEL IN

SIGNAL IN

4

5

6

7

C

3

Notes

(1) The Xtal/Clock input may be driven from the host telephone

system's 3.579545MHz clock; if a Xtal drive is required, the

configuration shown in the INSET is recommended.

(2) The audio signal should be input to both Signal In and Level In

pins via separate coupling capacitors. If it is wished to operate

the device with disregard to on-chip level thresholds and

permanently enable the MX613, the Level In pin should be held

at VDD.

To disable the MX613 the Level In pin should be held at VSS.

Level thresholds are preset internally.

V

SS

8

Figure 2 - External Component Connections

MX613DW

V

DD

V

16

15

14

13

12

11

DD

C

4

DAT A OUT

CHIP SELECT

SERIAL CLOCK INPUT

IRQ

10

9

Component Value

R

1

R

2

C

1

C

2

C

3

C

4

C

5

C

6

X

1

Tolerances: C = ± 20% R = ± 10%

3.579545MHz

R

22.0kΩ

1.0MΩ

0.01µF

0.1µF

1.0µF

1.0µF

33.0pF

33.0pF

V

DD

1

V

DD

775mVrms

0

-10

-20

Low Band

(LO)

High Band

(HI)

Must

Decode

-30

Level (dB)

-40

Must-Not

Decode

-50

0

200 400 600 800 1000 1200 1400 1600 1800 2000 2200

Frequency (Hz)

Figure 3 - HI/LO Decode Bands

© 1997 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 910 744-5050 Fax: 910 744-5054 Doc. # 20480086.003

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USAAll trademarks and service marks are held by their respective companies

Page 4

Global Call Progress Tone Detector 4 MX613 Preliminary Information

Application Information ......

Principles of Decoder Operation

Level Detection

Because level and frequency discrimination operations tak e place in parallel, the audio signal should, under normal

circumstances, be input to both Signal In and Lev el In pins via coupling capacitors.

If the input signal level (Level In) is outside the preset ‘Must/Must Not Decode’ thresholds (see Specifications), the

Universal Call Progress Decoder will be disabled.

If it is wished to disregard signal input

may be permanently enabled by holding the Level In pin at VDD.

The MX613 can disabled by pulling Level In to VSS.

NOTONE Recognition

The NOTONE condition can be recognized using µProcessor software timing as below.

a. Set the µP timer period to a period greater than the relevant frequency-band measurement period (13.16ms

or 39.47ms).

b. Each ‘Tone Measurement Complete’ interrupt from the MX613 must reset the µP timer.

c. With NOTONE or white noise at the decoder input, the MX613 on-chip timer will be continually reset.

i. ‘Tone Measurement Complete' interrupt will not occur - the µP timer will run.

ii. The µP Timer time-out can be considered as a NOTONE indication.

Level In Timer IRQ Data Out

In Limits Running Enabled Enabled

Out of Limits Reset Disabled Disabled (frozen to previous bit-5 level

V

DD

V

SS

Running/Reset Enabled/Disabled Enabled (dependent upon Quality measurement)

Reset Disabled Disabled (frozen to previous bit-5 level)

levels

at the Level In pin and attempt to decode under all conditions, the decoder

Frequency Band Discrimination

The input signal is amplified by a self-biased (zero-crossing) inverting amplifier and then ‘filtered’ to remove highfrequency noise and jitter.

High (HI) and Low (LO) counters are employed to determine the input frequency band (HI = 900Hz to 2150Hz,

LO = 300Hz to 660Hz).

If the input frequency is in the LO Band, the device will operate as a LO Band decoder and will remain so until a

HI frequency signal is detected. If the input frequency is in the HI Band, the device will operate as a HI Band

decoder and will remain so until a LO frequency signal is detected.

Frequency band monitoring is continuous with the band selection taking place every 9.8ms. It will therefore take

9.8ms from Power-Up to set up the initial correct decode frequency band.

On-Chip Timer Operation

For frequency measurement, the MX613 counts the number of input cycles in a fixed time period. This fixed

period, measured by the continuous on-chip timer, is set to 13.16ms for HI Band inputs and 39.47ms for LO Band

inputs.

When the timer expires the following actions take place:

a. A HI or LO (“1” or “0”) band indication bit is latched into Bit-5 of the Serial Output Port.

b. The Frequency Counter count of 5-bits is latched into the Serial Output Port (Bit-4 [MSB] to Bit-0). The

Serial Output Port Contains 6-bits, if 8 Serial Clock edges are employed, two extra “0s”, which should be

ignored, will be output last.

c. An interrupt is generated (IRQ) to the µProcessor. The contents of the Serial Output Port should be read

before the next interrupt is expected; if not data will be overwritten.

When the Chip Select input is set to “0” the interrupt is reset.

The On-Chip Timer and Frequency Counter will be reset in mid-count, and therefore unable to allow a valid

measurement, under the following conditions:

a. A change of decode frequency band.

b. Decoder disabled; signal input level out of specification or Level Detect input set to VSS.

c. Signal Quality Assessment considered ‘Bad’.

d. Input signal frequency outside limits.

© 1997 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 910 744-5050 Fax: 910 744-5054 Doc. # 20480086.003

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USAAll trademarks and service marks are held by their respective companies

Page 5

Global Call Progress Tone Detector 5 MX613 Preliminary Information

Application Information ......

N = int (Frequency x Measurement Period)

Measurement Period = 39.47ms for Low Band (300Hz to 660Hz)

= 13.16ms for High Band (900Hz to 2150Hz)

Note: For input frequencies of between 661Hz and 899Hz the MX613 will give no reliable output.

When a ‘correct’ decode has been allowed and an interrupt generated, a 6-bit data word is presented at the Serial Output

Port. This 6-bit word indicates the input frequency's band (Bit 5) and value ‘N’ as indicated below.

Bit 5

Output

First

Band Bit (5) MSB (4) (3) (2) (1) LSB (0)

HI-“1”/LO-“0” Bits 0 to 4 represent the measured frequency in the selected band

Bits

0 to 4

=

N

When a ‘correct’ decode has been allowed and an interrupt generated, a 6-bit data word will be presented at the Serial

Output Port. This 6-bit word indicates the input frequency's band and value as described below.

As an example, the following binary-word presented at the Serial Output Port (1 1 0 1 1 0) will indicate a frequency

in the HI Band of between 1680Hz and 1740Hz (Bit-5 = “1” = HI, ‘N’ = 22).

LO Band HI Band N B5B4B3B2B1B0LO Band HI Band N B5B4B3B2B1B

280 840

285 855

290 870

295

300 900 11 525 1575 20

305 915 12 H/L 01100 530 1590 20

310 930 12 535 1605 21 H/L 1 0 1 0 1

315 945 12 540 1620 21

320 960 12 545 1635 21

325 975 12 550 1650 21

330 990 13 H/L 01101 555 1665 21

335 1005 13 560 1680 22 H/L 1 0 1 1 0

340 1020 13 565 1695 22

345 1035 13 570 1710 22

350 1050 13 575 1725 22

355 1065 14 H/L 01110 580 1740 22

360 1080 14 585 1755 23 H/L 1 0 1 1 1

885 11 520 1560 20

365 1095 14 590 1770 23

11 H/L 01011 505 1515 19 H/L 1 0 0 1 1

11 510 1530 20 H/L 1 0 1 0 0

11 515 1545 20

0

370 1110 14 595 1785 23

375 1125 14 600 1800 23

380 1140 14 605 1815 23

385 1155 15 H/L 01111 610 1830 24 H/L 1 1 0 0 0

390 1170 15 615 1845 24

395 1185 15 620 1860 24

400 1200 15 625 1875 24

405 1215 15 630 1890 24

410 1230 16 H/L 10000 635 1905 25 H/L 1 1 0 0 1

415 1245 16 640 1920 25

420 1260 16 645 1935 25

425 1275 16 650 1950 25

430 1290 16 655 1965 25

435 1305 17 H/L 10001 660 1980 26 H/L 1 1 0 1 0

440 1320 17

445 1335 17

450 1350 17

455 1365 17

460 1380 18 H/L 10010

465 1395 18

470 1410 18

475 1425 18

480 1440 18

485 1455 19 H/L 10011

490 1470 19

495 1485 19

500 1500 19

665

670

675

680

685

690

695

700

705

710

715

720

725 2175

1995 26

2010 26

2025 26

2040 26

2055 27 H/L 1 1 0 1 1

2070 27

2085 27

2100 27

2115 27

2130 28 H/L 1 1 1 0 0

2145 28

2160 28

28

Table 1 - Decode Frequency Data

© 1997 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 910 744-5050 Fax: 910 744-5054 Doc. # 20480086.003

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USAAll trademarks and service marks are held by their respective companies

Page 6

Global Call Progress Tone Detector 6 MX613 Preliminary Information

Application Information ......

Decoder Timing

CHIP SELECT

t

CSE

SERIAL CLOCK

t

DE

DA TA OUT

TRI-STATE

t

IR

BIT 5

IRQ

Figure 4 - Data-Read Timing

Decoder Timing Characteristics

With reference to Figure 4,

Data-Read Timing

BIT 0

t

CSH

t

HIZ

t

CYC

t

t

CDS

PWL

BIT 4

t

PWH

t

DH

.

Characteristics Min. Typ. Max. Unit

t

PWH

t

PWL

t

CYC

t

CSE

t

CSH

t

DH

t

CDS

t

IR

t

DE

t

HIZ

Serial Clock “High” Pulse Width 250 - - ns

Serial Clock “Low” Pulse Width 250 - - ns

Serial Clock-Cycle Time 600 - - ns

Chip Select Low to Clock “High” Edge 450 - - ns

Last Clock “High” Edge to CS “High” 600 - - ns

Data Out Hold Time 0 - - ns

Clock Edge to Data Out Set Time - - 200 ns

Interrupt (IRQ) Reset Time - - 200 ns

Chip Select “Low” to Data Enable - - 200 ns

Chip Select “High” to Output Tri-State - - 1000 ns

Notes

1 Data is output bit 5 first. Bit 5 can be clocked into the µProcessor by the first Serial Clock rising edge.

If 8 Serial Clock pulses are employed the last 2 data-bits will be “0” and should be ignored by the software.

2 Chip Select should be used to react to Interrupts and then returned to a logic “1”.

If Chip Select stays low there will be no further Interrupts and no Data Output update.

© 1997 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 910 744-5050 Fax: 910 744-5054 Doc. # 20480086.003

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USAAll trademarks and service marks are held by their respective companies

Page 7

Global Call Progress Tone Detector 7 MX613 Preliminary Information

Specifications

Absolute Maximum Ratings

Exceeding the maximum rating can result in device

damage. Operation of the device outside the operating

Operating Limits

All devices were measured under the following

conditions unless otherwise noted.

limits is not suggested.

Supply Voltage -0.3 to 7.0V

VDD = 3.3V

Input Voltage at any pin

(ref VSS=0V) -0.3 to (VDD+ 0.3V)

TOP = 25°C

Sink/Source Current

(supply pins) ± 30mA

Audio Level 0dB ref = 775 mVrms

(other pins) ±20mA

Total Device Dissipation

(@ T

=25°C) 800mW max.

AMB

Xtal/Clock f0 = 3.579545 MHz

Derating 10 mW/°C

Operating Temperature -40°C to +85°C

Storage Temperature -55°C to +125°C

Characteristics See Note Min. Typ. Max. Unit

Static Values

Supply Voltage (VDD) at 25°C 3.0 - 5.5 V

Supply Current - 0.3 1.0 mA

Input Logic “1” 70.0 - 100 % V

Input Logic “0” 0 - 30.0 % V

Output Logic “1” 1 90.0 - 100 % V

Output Logic “0” 1 - - 10.0 % V

DD

DD

DD

DD

Impedances

Chip Select and Serial Clock Input 10.0 - - MΩ

Signal Input - 50.0 - kΩ

Level Input - 210 - kΩ

IRQ Output (Logic “0”) - - 500 Ω

Data Output (Logic “0”) - 500 - Ω

(Logic “1”) - - 2.5 kΩ

Dynamic Values

On-Chip Xtal Oscillator

R

IN

R

OUT

10.0 - - MΩ

- 230 825 kΩ

DC Voltage Gain 25.0 42.0 - V/V

Bandwidth at Unity Gain 5.0 11.0 - MHz

Single Tone Operation

Must-Decode Input Level 2 -25.2 - - dB

© 1997 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 910 744-5050 Fax: 910 744-5054 Doc. # 20480086.003

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USAAll trademarks and service marks are held by their respective companies

Page 8

Global Call Progress Tone Detector 8 MX613 Preliminary Information

Characteristics See Note Min. Typ. Max. Unit

Must-Not Decode Input Level 2 - - -46.0 d B

LO Band Frequency Range 4 300 660 Hz

HI Band Frequency Range 4 900 2150 Hz

Frequency Resolution (Table 1)

LO Band - - 25.0 Hz

HI Band - - 75.0 Hz

Input Signal/White-Noise Ratio (HI & LO Bands) - 18.0 - dB

Interrupt Rate (LO Band) 3 19.0 - - /sec

(HI Band) 3 57.0 - - /sec

False Decodes Due to Noise 6 - 1.0 - /2 secs

Outband modulation level limits

for correct decode (fIN = 340Hz to 620Hz) 5 - - 10.0 %

Notes

1. Into a high-impedance load (>1.0MΩ).

2. Must decode signal above -25.2dB; Must Not decode signal below -46.0dB.

If a supply other than 3.3 volts is used, levels will change pro-rata.

3. Under ‘Pure Tone’ input conditions.

4. For input frequencies of between 661Hz and 899Hz the MX613 will provide no reliable output.

5. With an amplitude modulating frequency of between 16.0Hz and 100Hz.

6. Test noise input = 5.0kHz at 100mVrms

Packa geTolerances

DIM.

0.395 (10.03)

A

0.286 (7.26)

B

C

0.390 (9.90)

E

H

0.013 (0.33) 0.020 (0.51)

J

K

0.016 (0.41)

L

P

0.009 (0.23) 0.0125 (0.32)

T

W

X

Y

Z

NOTE: All dimensions in inches (mm.)

0° 10°

5°

Angles are in degrees

ALTERNATIVE

PIN

LOCATION

MARKING

A

B

E

W

Z

L

PIN 1

T

X

Y

K

C

P

J

H

Figure 5: 16-pin SOIC Mechanical Outline:

© 1997 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 910 744-5050 Fax: 910 744-5054 Doc. # 20480086.003

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USAAll trademarks and service marks are held by their respective companies

order as part no. MX613DW

TYP.

0.041 (1.04)

0.050 (1.27)

45°

5°

MAX.MIN.

0.413 (10.49)

0.299 (7.59)

0.105 (2.67)0.093 (2.36)

0.419 (10.64)

0.020 (0.51)0.003 (0.08)

0.050 (1.27)

7°

Page 9

Global Call Progress Tone Detector 9 MX613 Preliminary Information

K

H

L

PIN 1

A

B

E1

Y

C

P

J1

J

Figure 6: 16-pin PDIP Mechanical Outline:

PackageTolerances

DIM.

A

0.740 (18.80)

B

E

T

0.240 (6.10)

C

0.135 (3.43)

E

0.300 (7.62)

E1

0.290 (7.37) 0.325 (8.26)

H

0.015 (0.38) 0.070 (1.77)

0.014 (0.35) 0.023 (0.58)

J

0.040 (1.02) 0.065 (1.65)

J1

K

0.056 (1.42) 0.064 (1.63)

0.121 (3.07)

L

P

T

0.008 (0.20) 0.015 (0.38)

Y

NOTE: All dimensions in inches (mm.)

Angles are in degrees

TYP. MAX.MIN.

0.810 (20.57)

0.262 (6.63)

0.200 (5.06)

0.390 (9.91).

0.150 (3.81)

0.100 (2.54)

7°

order as part no. MX613P

© 1997 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 910 744-5050 Fax: 910 744-5054 Doc. # 20480086.003

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USAAll trademarks and service marks are held by their respective companies

Loading...

Loading...