Page 1

FEA TURES

MX23L3222

32M-BIT MASK ROM (16/32 BIT OUTPUT)

• Bit organization

- 2M x 16 (word mode)

- 1M x 32 (double word mode)

• Fast access time

- Random access: 100ns (max.)

- Page access: 30ns (max.)

• Page

- 8 double words per page

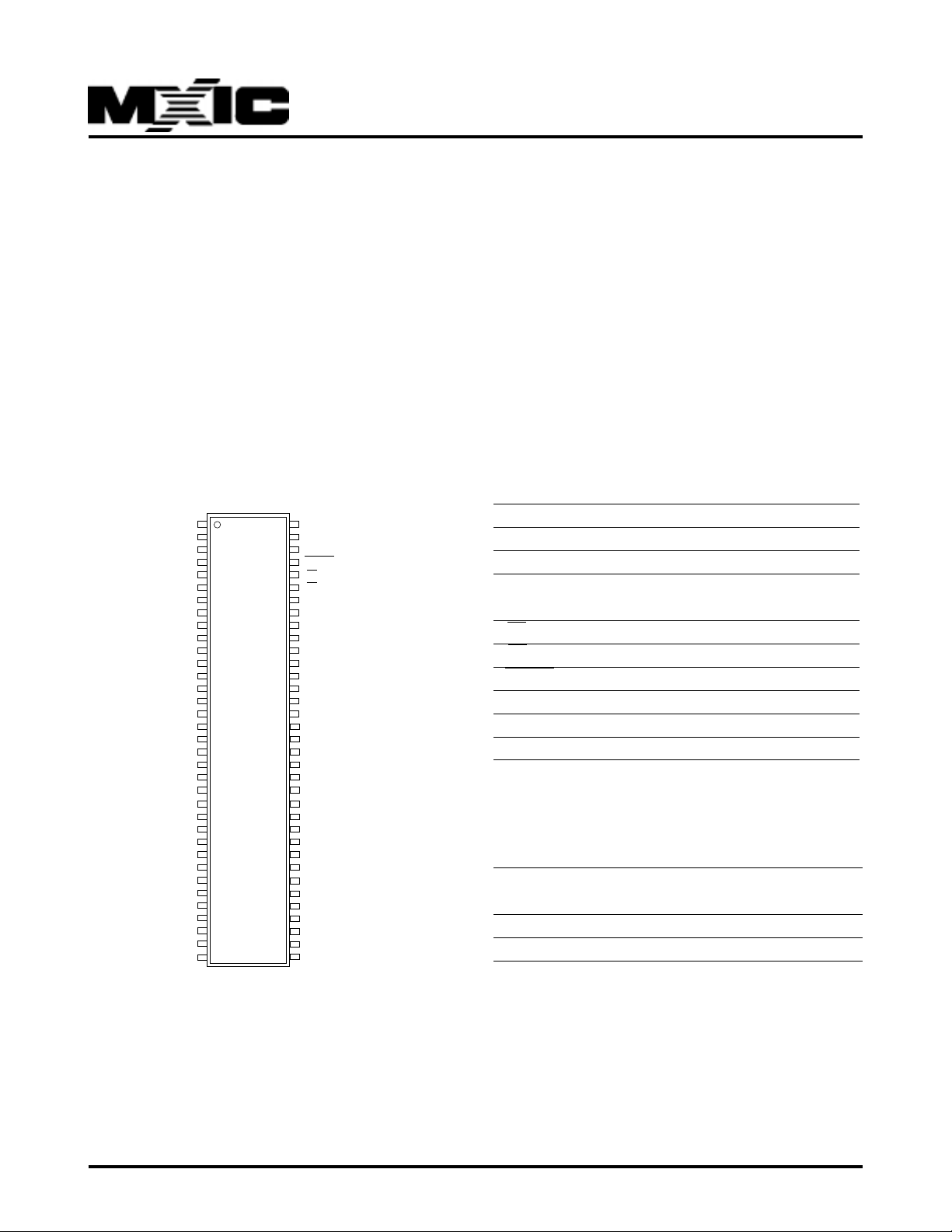

PIN CONFIGURATION

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

MX23L3222

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

VCC

D16

D17

VSS

VCC

D18

D19

D20

D21

VSS

VCC

D22

D23

VSS

A10

A11

A12

A0

2

A1

3

A2

4

A3

5

A4

6

A5

7

8

D0

9

10

D1

11

12

13

14

D2

15

16

D3

17

18

D4

19

20

D5

21

22

23

24

D6

25

26

D7

27

28

29

A6

30

A7

31

A8

32

A9

33

34

35

NC

NC

NC

WORD

OE

CE

VSS

D31/A-1

D15

D30

D14

VSS

VCC

D29

D13

D28

D12

D27

D11

D26

D10

VSS

VCC

D25

D9

D24

D8

VCC

A19

A18

A17

A16

A15

A14

A13

• Current

- Operating:60mA

- Standby:50uA

• Supply voltage

- 3.3V±10%

• Package

- 70 pin SSOP (500mil)

PIN DESCRIPTION

Symbol Pin Function

A0~A19 Address Inputs

D0~D30 Data Outputs

D31/A-1 D15 (Word Mode)/ LSB Address

(Byte Mode)

CE Chip Enable Input

OE Output Enab le Input

WORD Double W ord/ Word Mode Selection

VCC Po wer Supply Pin

VSS Ground Pin

NC No Connection

ORDER INFORMATION

Part No. Access Page Access Package

Time Time

MX23L3222MC-10 100ns 30ns 70 pin SSOP

MX23L3222MC-12 120ns 45ns 70 pin SSOP

P/N:PM0396 REV. 2.0, OCT. 19, 2001

1

Page 2

MX23L3222

MODE SELECTION

CE OE WORD D31/A-1 D0~D15 D16~D31 Mode Power

H X X X High Z High Z - Stand-by

L H X X High Z High Z - Active

L L H Output D0~D15 D16~D31 Double W ord Active

L L L Input D0~D15 High Z Word Active

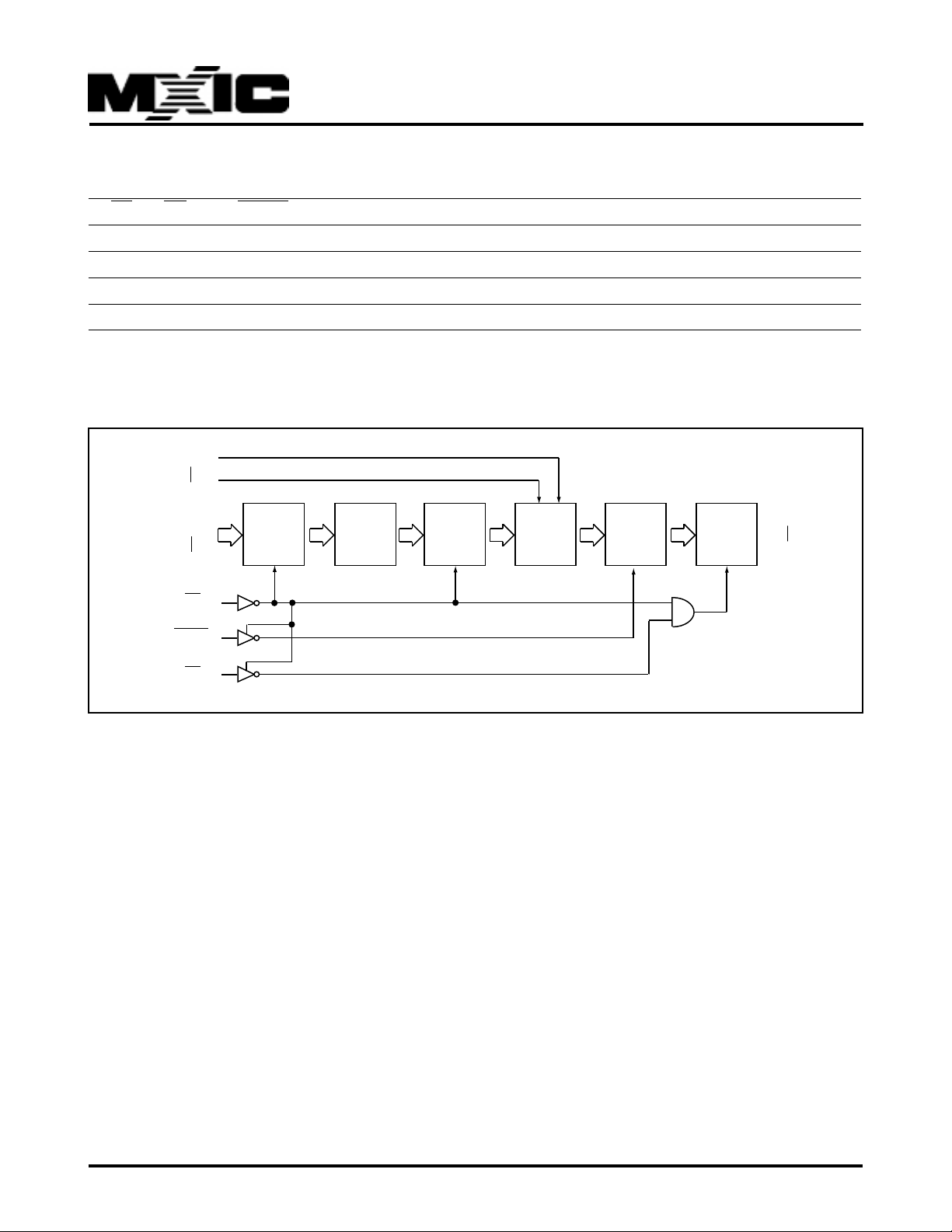

BLOCK DIAGRAM

A0/(A-1)

A2

A3

A19

Address

Buffer

Memory

Array

Page

Buffer

Page

Decoder

Word/

Byte

Output

Buffer

D31/(D15)

D0

CE

BYTE

OE

P/N:PM0396

REV. 2.0, OCT. 19, 2001

2

Page 3

MX23L3222

ABSOLUTE MAXIMUM RATINGS

Item Symbol Ratings

V oltage on any Pin Relativ e to VSS VIN -1.3V to VCC+2.0V (Note)

Ambient Operating Temperature Topr 0°C to 70°C

Storage T emperature Tstg -65°C to 125°C

Note: Minimum DC voltage on input or I/O pins is -0.5V . During voltage transitions, inputs ma y undershoot VSS to

-1.3V for periods of up to 20ns. Maximum DC voltage on input or I/O pins is VCC+0.5V. During voltage

transitions, input may ov ershoot VCC to VCC+2.0V for periods of up to 20ns.

DC CHARACTERISTICS (Ta = 0°C ~ 70°C, VCC = 3.3V±10%)

Item Symbol MIN. MAX. Conditions

Output High Voltage VOH 2.4V - IOH = -0.4mA

Output Low V oltage VOL - 0.4V IOL = 1.6mA

Input High Voltage VIH 2.2V VCC+0.3V

Input Low V oltage VIL -0.3V 0.8V

Input Leakage Current ILI - 5uA 0V, VCC

Output Leakage Current ILO - 5uA 0V, VCC

Operating Current ICC1 - 60mA tRC = 100ns, all output open

Standby Current (TTL) ISTB1 - 1mA CE = VIH

Standby Current (CMOS) ISTB2 - 50uA CE>VCC-0.2V

Input Capacitance CIN - 10pF Ta = 25°C, f = 1MHZ

Output Capacitance COUT - 10pF T a = 25°C, f = 1MHZ

AC CHARACTERISTICS (Ta = 0°C ~ 70°C, VCC = 3.3V±10%)

Item Symbol 23L3222-10 23L3222-12

MIN. MAX. MIN. MAX.

Read Cycle Time tRC 100ns - 120ns Address Access Time tAA - 100ns - 120ns

Chip Enable Access Time tACE - 30ns - 45ns

Page Mode Access Time tPA - 30ns - 45ns

Output Enable Time tOE - 30ns - 45ns

Output Hold After Address tOH 0ns - 0ns Output High Z Delay tHZ - 20ns - 20ns

Note: Output high-impedance delay (tHZ) is measured from OE or CE going high, and this par ameter guaranteed

by design over the full v oltage and temper ature operating r ange - not tested.

P/N:PM0396

3

REV. 2.0, OCT. 19, 2001

Page 4

AC T est Conditions

MX23L3222

Input Pulse Levels 0.4V~ 2.4V

Input Rise and Fall Times 10ns

Input Timing Level 1.5V

Output Timing Le v el 0.8V and 2.0V

Output Load See Figure

TIMING DIAGRAM

RANDOM READ

ADD

CE

ADD ADD ADD

tACE

tOE

IOH (load)=-04.mA

DOUT

IOL (load)=1.6mA

Note:No output loading is present in tester load board.

Active loading is used and under software programming control.

Output loading capacitance includes load board's and all stray capacitance.

tRC

C<100pF

PAGE READ

(A-1),A0,A1,A2

OE

tAA

DATA

A3-A19

1'st ADD

tAA

DATA

Note: CE, OE are enable.

Page size is 8 double words in 32-bit mode, 16 words in 16-bit mode.

VALID VALID VALID

VALID ADD

VALID

2'nd ADD

tPA

VALID

3'rd ADD

VALID

tOH

tHZ

P/N:PM0396

REV. 2.0, OCT. 19, 2001

4

Page 5

MX23L3222

REVISION HISTORY

Revision Description Page Date

1.8 AC Characteristics: The page mode access time (tPA) and output MAR/25/1998

enable time (tOE) are changed as 45ns instead of 50ns.

Added 100ns speed grade.

Package: Added 100 pin TQFP package, dimension is

14mm x 14mm x 1mm.

1.9 AC CHARA CTERISTICS tOH 10ns-->0ns P3 JAN/29/1999

2.0 Delete package:100-pin TQFP P1,2 OCT/19/2001

P/N:PM0396

REV. 2.0, OCT. 19, 2001

5

Page 6

MX23L3222

MACRONIX INTERNATIONAL CO., LTD.

HEADQUARTERS:

TEL:+886-3-578-6688

FAX:+886-3-563-2888

EUROPE OFFICE:

TEL:+32-2-456-8020

FAX:+32-2-456-8021

JAPAN OFFICE:

TEL:+81-44-246-9100

FAX:+81-44-246-9105

SINGAPORE OFFICE:

TEL:+65-348-8385

FAX:+65-348-8096

TAIPEI OFFICE:

TEL:+886-2-2509-3300

FAX:+886-2-2509-2200

MACRONIX AMERICA, INC.

TEL:+1-408-453-8088

FAX:+1-408-453-8488

CHICAGO OFFICE:

TEL:+1-847-963-1900

FAX:+1-847-963-1909

http : //www.macronix.com

MACRONIX INTERNATIONAL CO., LTD. reserves the right to change product and specifications without notice.

6

Loading...

Loading...