Page 1

E2B0019-27-Y2

¡ Semiconductor

This version: Nov. 1997

Previous version: Mar. 1996

MSM5259¡ Semiconductor

MSM5259

40-DOT SEGMENT DRIVER

GENERAL DESCRIPTION

The MSM5259 is a dot matrix LCD segment driver which is fabricated using low power CMOS

metal gate technology. This LSI consists of 40-bit shift register, 40-bit latch and 40-bit 4-level

driver.

It converts serial data, which is received from an LCD controller LSI, to parallel data and outputs

LCD driving waveforms to LCD.

Expansion of the display can be easily made according to the number and structure of characters.

Since the 40-bit shift register of this device consists of two 20-bit shift registers, it is possible to

allot bits efficiently according to the number of characters.

The MSM5259 can drive a variety of LCD panels because the bias voltage, which determines the

LCD driving voltage, can be optionally supplied from the external source. For static operation

only, the device is available with a power supply voltage of 2.5V or more.

FEATURES

• Supply voltage : 3.5 to 6.0V (Dynamic display)

: 2.5 to 6.0V (Static display)

• LCD driving voltage : 2.5 to 6.0V (Static display)

• Applicable LCD duty : 1/8 to 1/16

• Interface with MSM6222-xx (Dot matrix LCD controller with 16-dot common driver and 40-

dot segment driver)

• Bias voltage can be supplied externally.

• Package options:

56-pin plastic QFP (QFP56-P-910-0.65-K) (Product name : MSM5259GS-K)

56-pin plastic QFP (QFP56-P-910-0.65-L2) (Product name : MSM5259GS-L2)

56-pin plastic QFP (QFP56-P-910-0.65-2K) (Product name : MSM5259GS-2K)

56-pin plastic QFP (QFP56-P-910-0.65-2L2) (Product name : MSM5259GS-2L2)

1/18

Page 2

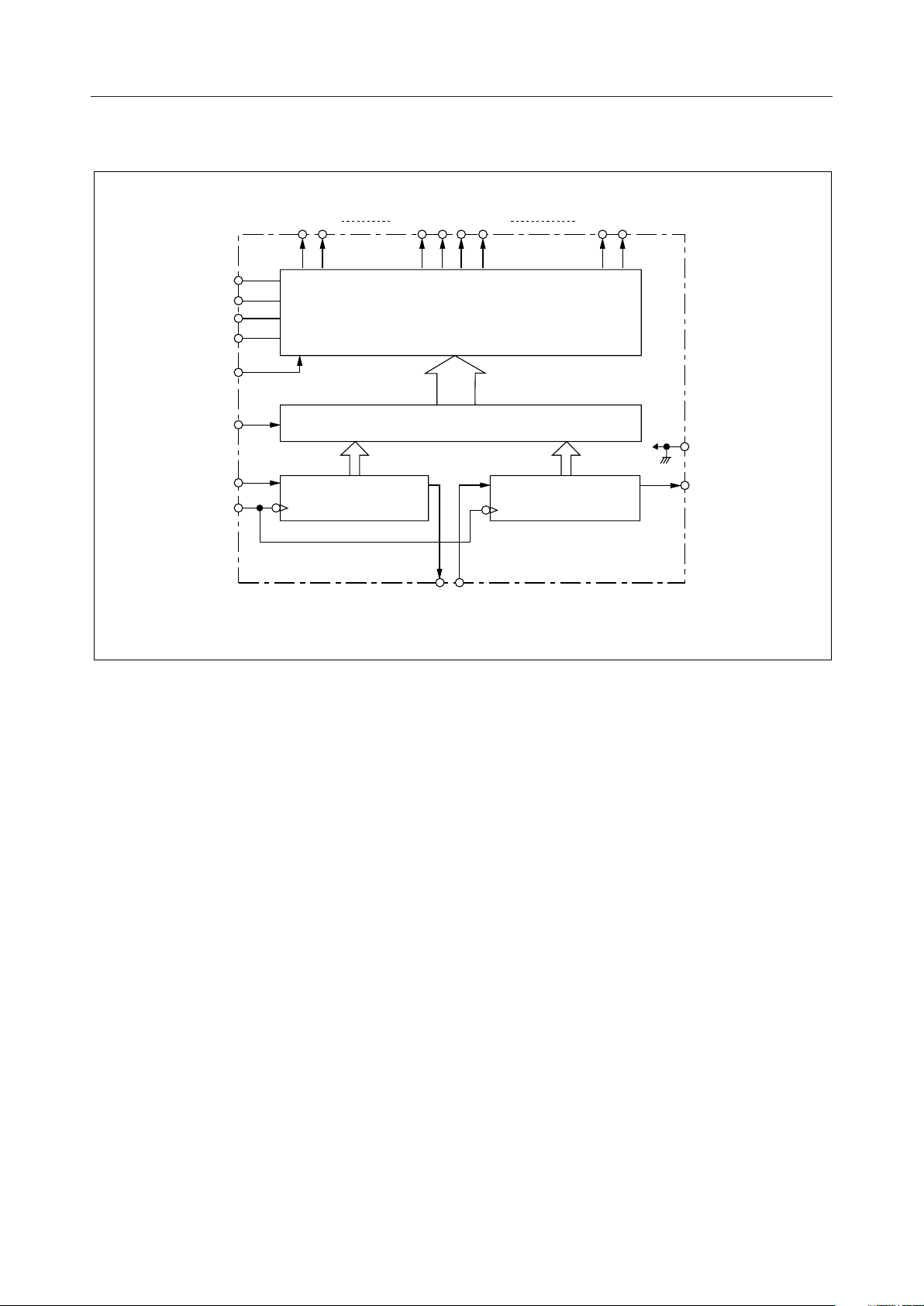

BLOCK DIAGRAM

MSM5259¡ Semiconductor

V

DD

V

2

V

3

V

5

DF

LOAD

DI

1

CP

O

O

1

2

20-Bit Shift

Register

O19O20O21O

22

40-Bit 4-Level Driver

40-Bit Latch

DO

20DI21

O

20-Bit Shift

Register

O

40

39

V

SS

DO

40

2/18

Page 3

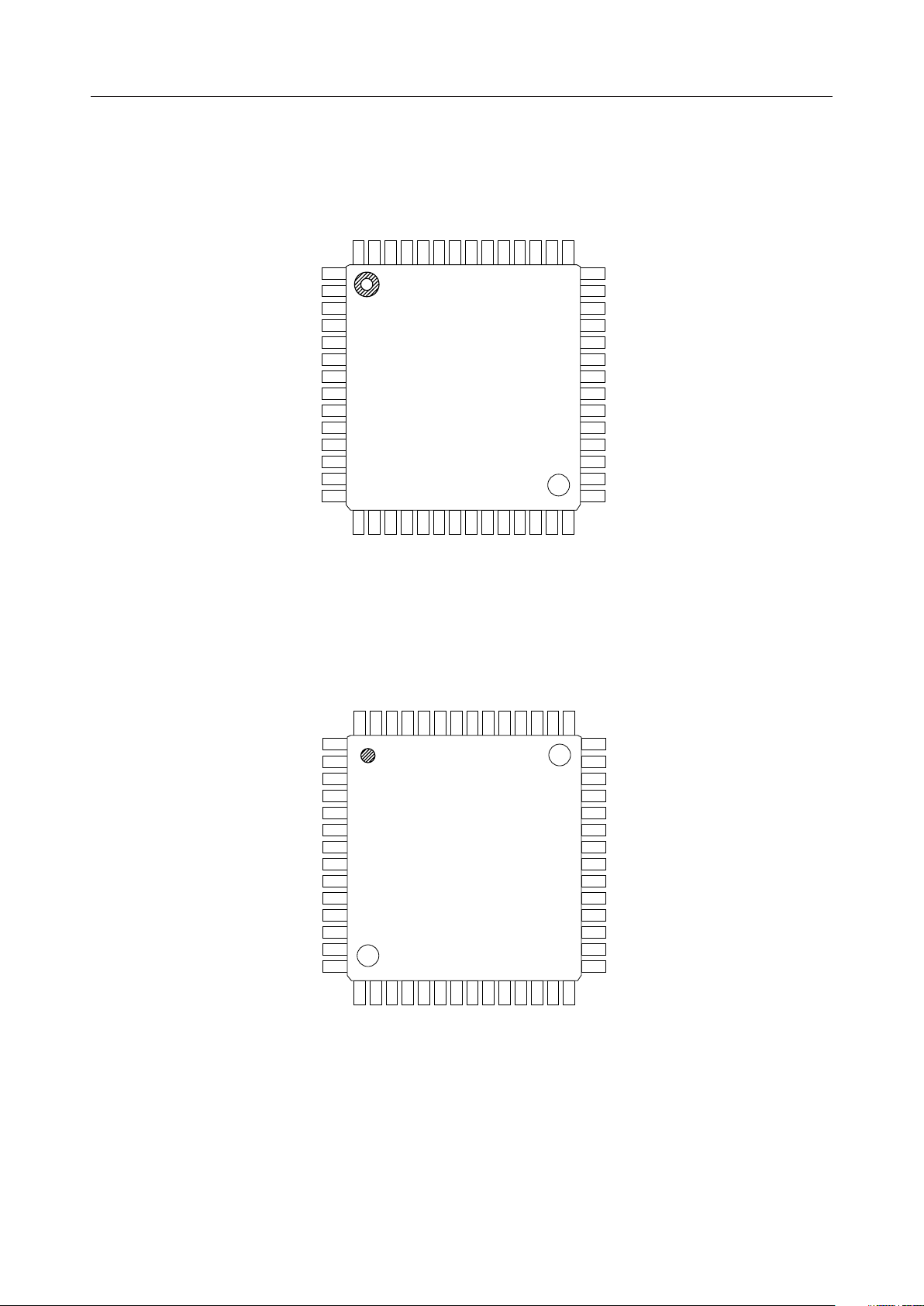

PIN CONFIGURATION

MSM5259¡ Semiconductor

(Top View)

NC

56555453525150494847464544

1

O

1

O

2

2

O

3

3

4

O

4

5

O

5

6

O

6

7

O

7

8

O

8

9

O

9

10

O

10

11

O

11

12

O

12

13

O

13

14

O

14

15161718192021222324252627

15

O18O17O16O

CP

)

20

19

DD

O

O

1

LOAD

DI

DF

NC

NC

*(V

NC : No connection

56-Pin Plastic QFP (Type K)

DD

V

21

O

2

V

VSSV

23

22

O

20

5

3

O24O

DI 21DO

V

43

42

DO

40

O

41

40

O

40

39

39

O

38

38

O

37

37

O

36

36

O

35

35

O

34

34

O

33

33

O

32

32

O

31

31

O

30

30

O

29

29

O

28

28

27O26

25

O

O

NC

NC

NC

DF

LOAD

DI

CP

V

DD

V

SS

V

V

V

DO

DI

5

8

1

123456789

56

55

54

53

52

51

50

49

48

47

2

46

3

45

5

44

20

43

21

42414039383736353433323130

40

40

DO

6

7

O

O

O

O4O3O2O

O38O39O

O

36

37

O

O34O35O

NC : No connection

56-Pin Plastic QFP (Type L)

10

11

O

O9O

1011121314

32

33

O31O

O

O

12

O14O13O

15

O

15

O

16

16

O

17

17

18

O

18

19

O

19

20

O

20

21

*(VDD)

22

O

21

23

O

22

24

O

23

25

O

24

26

O

25

27

O

26

28

O

27

29

29

30

O28O

* Do not connect pin 21 to the other signal pins, because the pin is internally connected to VDD.

Do not use pin 21 as a single VDD signal line. It is permissible to use pin 21 for supplying a

higher power of VDD.

Note : The figure for Type L shows the configuration viewed from the reverse side of the package.

Pay attention to the difference in pin arrangement.

3/18

Page 4

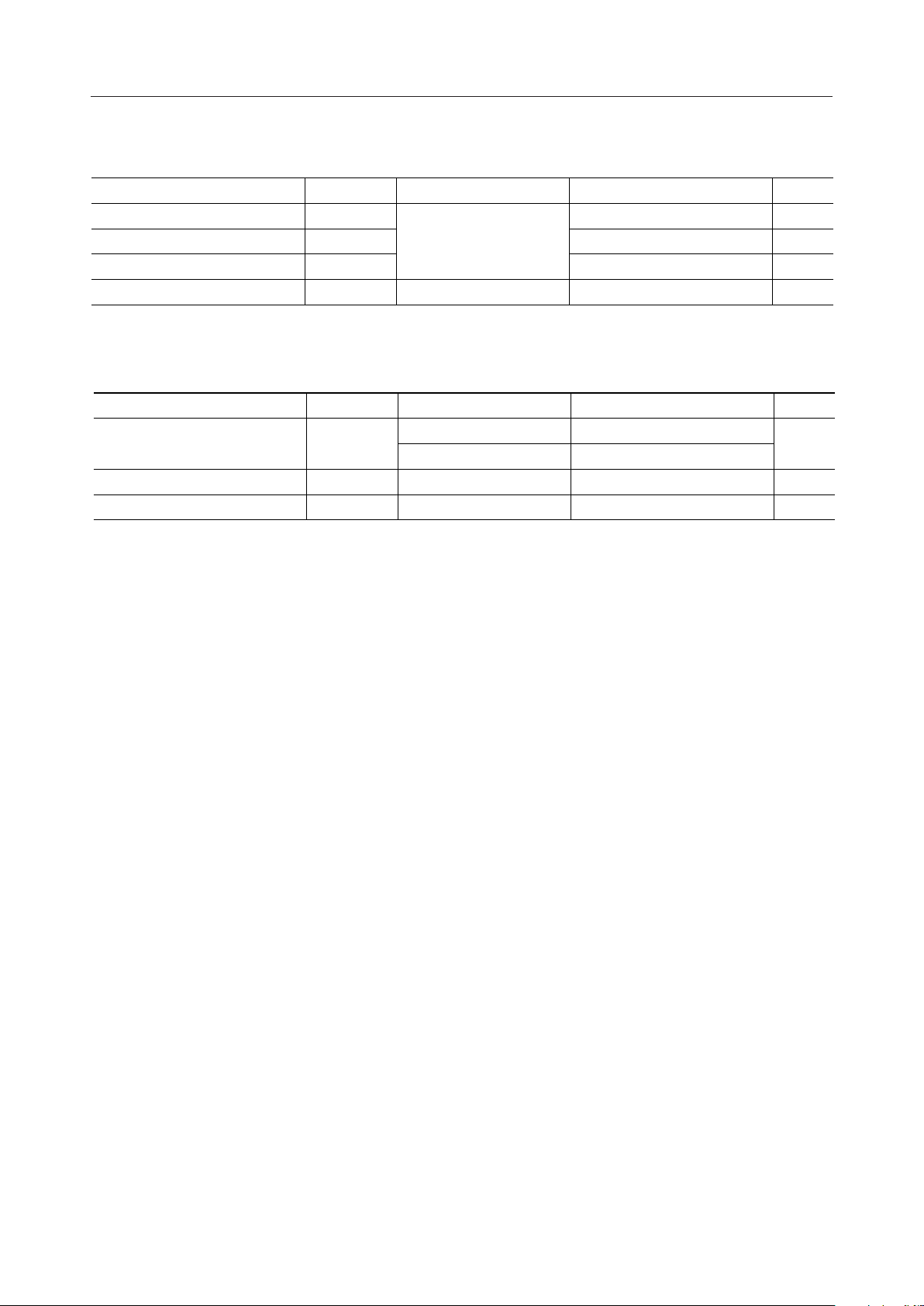

ABSOLUTE MAXIMUM RATINGS

MSM5259¡ Semiconductor

Parameter

Supply Voltage (1)

Supply Voltage (2) V

Input Voltage V

Storage Temperature T

Symbol Condition Rating Unit

–0.3 to +6.5 V

–0.3 to V

DD

DD

V

DD

–

STG

*1

V

5

I

Ta = 25°C 0 to +6.5 V

— –55 to +150 °C

RECOMMENDED OPERATING CONDITIONS

Parameter

Supply Voltage (1)

Supply Voltage (2) V

Operating Temperature T

*1 VDD > V2 > V3 > V5 > VSS (Dynamic display)

VDD = V3 > V2 = V5 = VSS (Static display)

For VDD of less than 3.5V, the device is available only for static operation.

*2 VDD is the reference potential for the LCD driving voltage.

To determine the LCD driving voltage, change the value of V5. (0V Minimum)

Symbol Condition Rnage Unit

3.5 to 6.0

2.5 to 6.0 V

DD

DD

–

op

V

5

Static 2.5 to 6.0

—*1 *2

— –30 to +85 °C

V

Dynamic

+0.3 V

V

4/18

Page 5

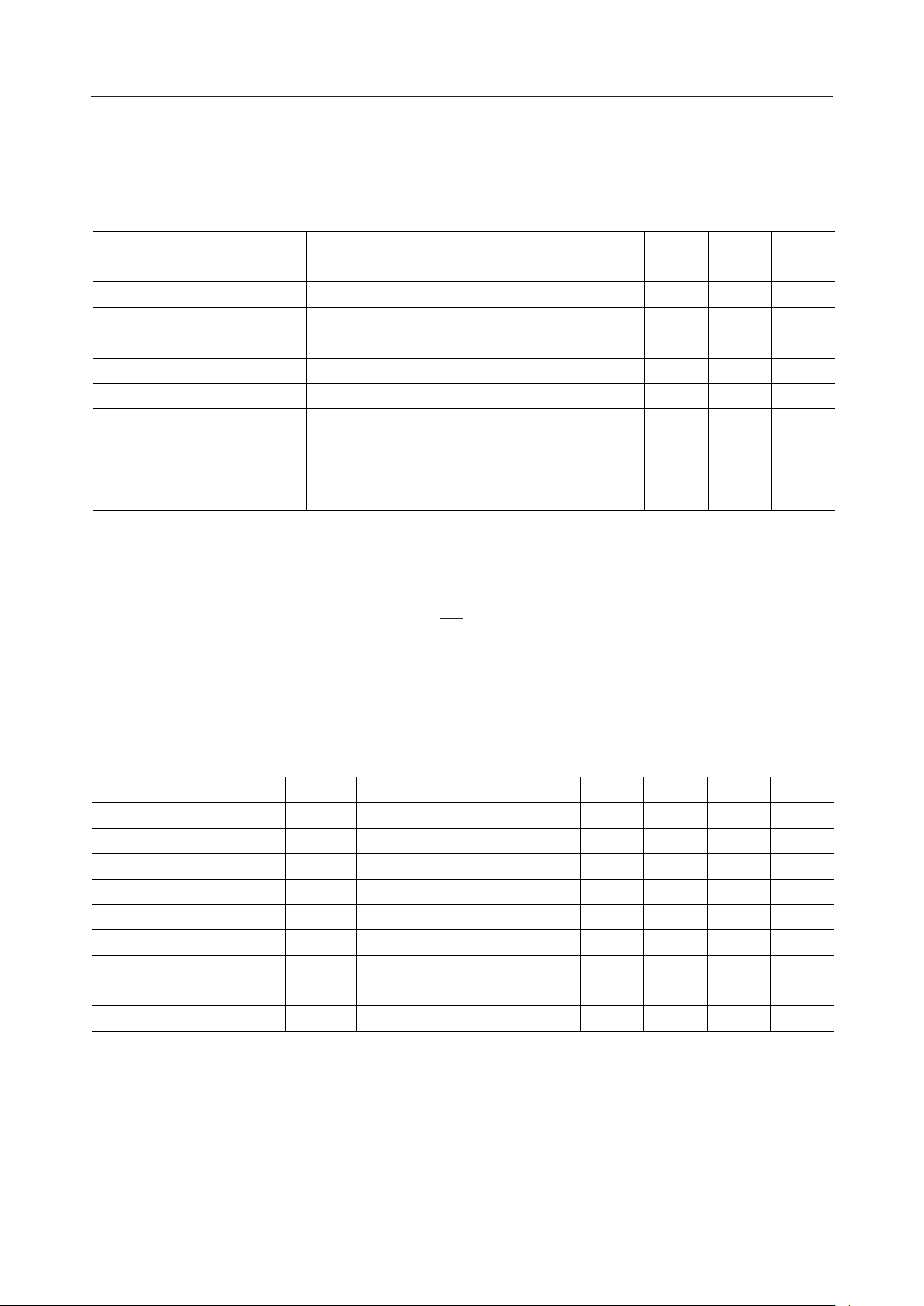

ELECTRICAL CHARACTERISTICS

DC Characteristics (1)

Parameter

"H" Input Voltage

"L" Input Voltage V

"H" Input Current I

"L" Input Current I

"H" Output Voltage V

"L" Output Voltage V

ON Resistance R

Symbol Condition Min. Typ. Max. Unit

V

*1

IH

*1

IL

*1

IH

*1

IL

*2

OH

*2

OL

*3

ON

MSM5259¡ Semiconductor

= 5V±10%, Ta=–30 to +85°C)

(V

DD

— 0.8V

DD

— 0 — 0.2V

V

= V

IH

DD

V

= 0V — — –1 mA

IL

I

= –40mA 4.2 — — V

O

I

= 0.4mA — — 0.4 V

O

—— 1 mA

VDD–V5= 5V

|V

N–VO

| = 0.25V

—— 5 kW

*4

—VDDV

DD

V

Supply Current I

DD

f

= 0Hz, No load — — 0.5 mA

CP

*1 Applicable to DF, LOAD, DI1 and DI21.

*2 Applicable to DO20 and DO40.

*3 Applicable to O1 to O40.

*4 Dynamic display : VN = VDD to V5, V2 = (VDD – V5), V3 = (VDD – V5)

Static display : VN = VDD to V5, V3 = VDD, V2 = V5 = V

2

3

SS

1

3

DC Characteristics (2)

(Only for static operation)

Parameter

Symbol Condition Min. Typ. Max. Unit

"H" Input Voltage

"L" Input Voltage V

"H" Input Current I

"L" Input Current I

"H" Output Voltage V

"L" Output Voltage V

ON Resistance R

Supply Current I

V

*1

IH

*1

IL

V

IH

IL

OH

OL

*1

*1

*5

*5

= V

IH

DD

V

= 0V — — –1 mA

IL

I

= –40mA 2.2 — — V

O

I

= 0.2mA — — 0.4 V

O

— 0.8V

— 0 — 0.2V

V3 = VDD = 3V, V2 = V5 = VSS = 0V,

*6

ON

| VN–VO | = 0.25V

DD

fCP = 0Hz, No load — — 0.5 mA

= 3V±0.5V, Ta=–30 to +85°C)

(V

DD

DD

—VDDV

—— 1 mA

——10kW

DD

V

*5 Applied to DO20 and DO40.

*6 Applied to O1 to O40.

5/18

Page 6

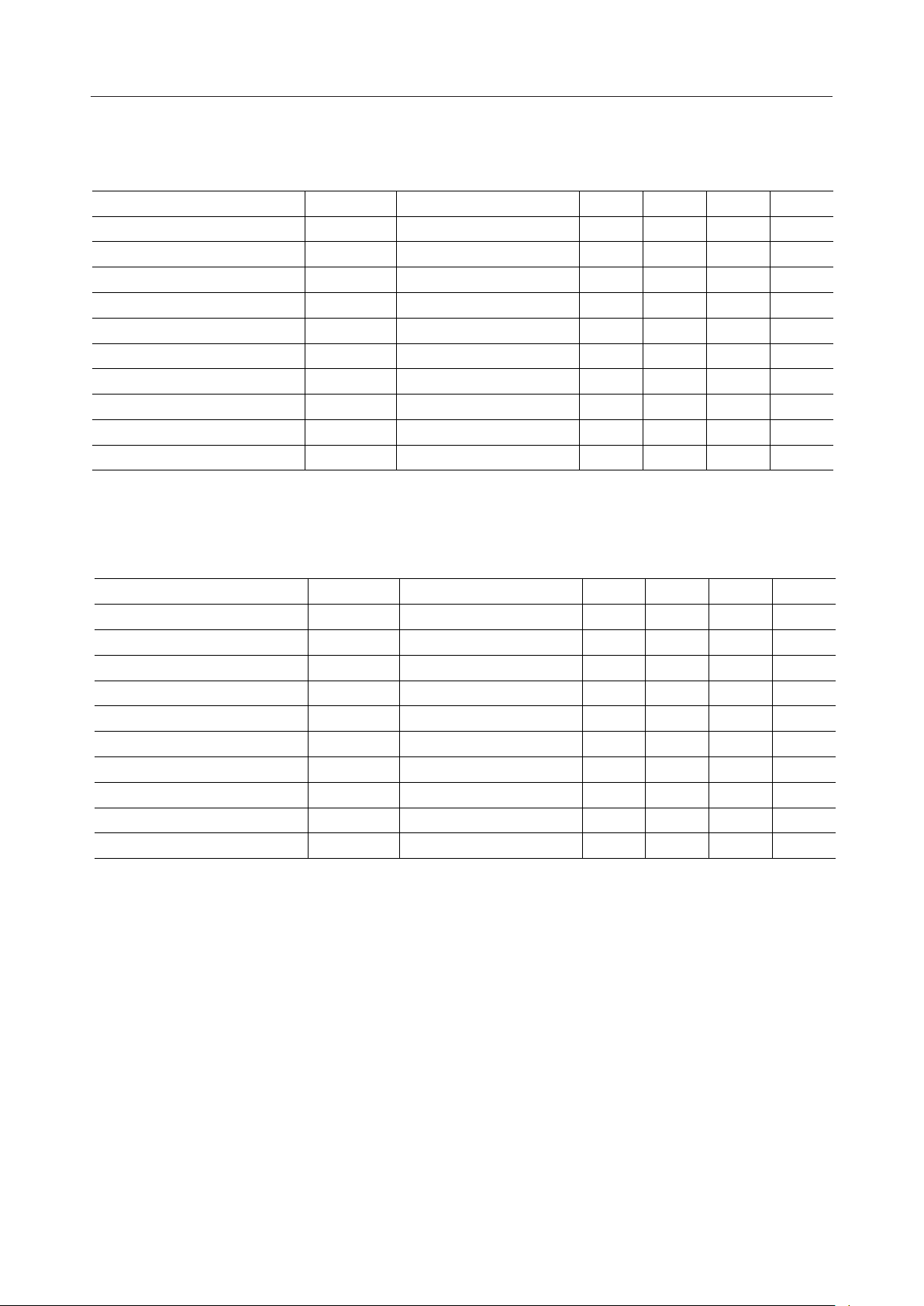

Switching Characteristics (1)

Parameter

"H", "L" Propagation Delay Time

Clock Frequency f

Clock Pulse Width t

Load Pulse Width t

Data Set-up Time DI

Data Hold Time DI

CP t

Æ

CP t

Æ

CP Æ LOAD Set-up Time t

LOAD Æ CP Hold Time t

CP Rise/Fall Time t

LOAD Rise/Fall Time t

Symbol Condition Min. Typ. Max. Unit

t

r(CP)

Switching Characteristics (2)

PLH, tPHL

CP

W (CP)

W (L)

SETUP

HOLD

CL

LC

, t

(CP)

f

, t

r(L)

f(L)

MSM5259¡ Semiconductor

(V

= 5V±10%, Ta=–30 to +85°C, CL=15pF)

DD

— — — 250 ns

Duty = 50% — — 3.3 MHz

—

—

—

—

—

—

—

—

125 — — ns

125 — — ns

50——ns

50——ns

250 — — ns

0——ns

——50ns

—— 1 ms

(Only for static operation)

Parameter

"H", "L" Propagation Delay Time

Symbol Condition Min. Typ. Max. Unit

t

PLH, tPHL

Clock Frequency f

Clock Pulse Width t

Load Pulse Width t

DI Æ CP Set-up Time t

DI Æ CP Hold Time t

CP Æ LOAD Set-up Time t

LOAD Æ CP Hold Time t

CP Rise/Fall Time t

LOAD Rise/Fall Time t

r(L)

CP

W (CP)

W (L)

SETUP

HOLD

CL

LC

r(CP)

, t

f(L)

(V

= 3V±0.5V, Ta=–30 to +85°C, CL=15pF)

DD

— — — 800 ns

Duty = 50% — — 1.0 MHz

—

—

—

—

—

—

—

—

300 — — ns

300 — — ns

200 — — ns

200 — — ns

800 — — ns

0——ns

—— 1 ms

—— 1 ms

6/18

Page 7

MSM5259¡ Semiconductor

CP

DI

DI

DO

DO

LOAD

tf(CP)

tw(CP)

t

SETUP

0.8V

DD

0.8V

0.2V

DD

DD

0.8V

0.2V

0.8V

DD

1

21

20

40

0.2V

DD

t

t

DD

PLH

PHL

DD

t

(CP)

w

t

HOLD

0.8V

0.2V

DD

DD

t

CL

0.8V

0.2V

DD

t

(L)

r

DD

0.2V

tw(L)

tr(CP)

0.8V

DD

DD

0.8V

t

SETUP

DD

tf(L)

0.8

V

DD

0.2

V

DD

t

LC

0.2V

0.8V

DD

DD

0.2V

0.8

V

0.2

V

DD

t

HOLD

DD

DD

7/18

Page 8

TIMING DIAGRAM

1/5 bias, 1/16 duty

Frame

signal

LOAD

LATCH

DATA

DF

DF

LOAD

MSM5259¡ Semiconductor

16 1 2 316 1 2 3

DI

CP

LATCH

DATA

LOAD

LATCH

DATA

DF

L

H

V

DD

V

a

V

b

V

c

V

d

V

e

V

DD

LL L

HHHH

V

LCD

V

DD

R

V

V

2

V

3

MSM5259

V

5

VR

a

V

= V

R

V

b

R

R

V

LCD

V

c

V

d

R

V

e

a

V

= V

b

V

= V

c

V

= V

d

V

= V

e

V

LCD

1

–

– V

DD

DD

DD

DD

DD

= LCD driving voltage

5

2

–

– V

5

3

–

– V

5

4

–

– V

5

– V

LCD

LCD

LCD

LCD

LCD

V

ss

8/18

Page 9

Static Display

DF

Output (lighting on)

Output (lighting off)

VDD

MSM5259¡ Semiconductor

V

DD

V

SS

VDD, V

3

VSS, V5, V

VDD, V

VSS, V5, V

V

DD

V

2

V

3

V

5

V

SS

O

1

O

40

DF

Common signal

2

3

2

Bias supply pin

9/18

Page 10

MSM5259¡ Semiconductor

FUNCTIONAL DESCRIPTION

Pin Functional Description

•DI

1

The data (1st to 20th bit) from the LCD controller LSI is input to 20-bit shift register from DI1.

(Positive logic)

•DI

21

Data input to the shift register (21st to 41st bit).

Connecting DO20 and DI21 allows configuration of a 40-bit register.

If DI21 is not used, connect this pin to VSS.

•CP

Clock pulse input pin for the two 20-bit shift registers. The data is input to the 20-bit shift

register at the falling edge of the clock pulse. A data set up time (t

(t

) are required between the DI1 and DI21 signals and a clock pulse.

HOLD

) and data hold time

SETUP

•DO

20

20th bit of the shift register contents is output from DO20. The data which was input from DI

is output from this pin with a delay of the number of bits of the shift register (20), synchronized

with the clock pulse. By connecting DO20 to DI21, two 20-bit shift registers can be used as a

40-bit shift register.

•DO

40

40th bit of the shift register contents is output from DO40. The data which was input from DI

is output from this pin with a delay of the number of bits of the shift register (20), synchronized

with the clock pulse. By connecting DO40 to the next MSM5259’s DI1, this LSI is applicable

to a wide screen LCD.

Refer to the application circuit.

•DF

Alternate signal input pin for LCD driving.

• LOAD

Signal for latching the shift register contents is input from this pin. When the LOAD pin is

set at "H" level, the shift register contents are transferred to the 40-bit 4-level driver. When

LOAD pin is set at "L" level, the last display output data (O1 - O40), which was transferred

when LOAD pin was at "H" level, is held.

1

21

•VDD, V

SS

Supply voltage pins.

VDD is generally set to 4.0 to 6.0V. VSS is a ground pin (VSS = 0V)

•V2, V3, V

5

Bias supply voltage pins to drive the LCD. Bias voltage divided by the register is usually used

as supply voltage source.

Refer to the application circuit.

For static operation, connect V3 to VDD and also connect V2, V5, to VSS.

10/18

Page 11

MSM5259¡ Semiconductor

•O1 to O

40

Display data output pin which corresponds to each data bit in the latch. One of VDD, V2, V

and V5 is selected as a display driving voltage source according to the combination of latched

data level and DF signal. (Refer to the truth table below.)

Truth Table

Latched data DF Driver output level

"H"

(Select)

"L"

(Non-select)

HV

LV

HV

LV

5

DD

3

2

3

11/18

Page 12

LCD Driving Waveform (1/5 bias, 1/16 duty)

Common

O

1

O

2

O

3

O

4

O

5

O

6

O

7

O

8

O

9

O

10

O

11

O

12

O

13

O

14

O

15

O

16

V

= V

a

V

= V

b

V

= V

c

V

= V

d

V

= V

e

O1O2O3O4O

Segment

1

–

– V

DD

DD

DD

DD

DD

5

2

–

– V

5

3

–

– V

5

4

–

– V

5

– V

LCD

LCD

LCD

LCD

LCD

V

DD

V

a

V

b

O

1

V

c

V

d

V

e

V

DD

V

a

V

b

V

O

c

2

V

d

V

e

V

DD

V

a

V

O

b

1

V

5

c

V

d

V

e

V

DD

V

a

V

b

V

O

c

2

V

d

V

e

V

LCD

1 2 3 4 16 1

MSM5259¡ Semiconductor

V

LCD

Common O1-Segment O

(Select waveform)

Common O

-Segment O

2

(Non-select waveform)

1

–

V

LCD

1

1

5

1

–

– V

5

–V

LCD

V

LCD

3

–

V

5

1

–

V

5

1

–

– V

5

3

–

– V

5

–V

LCD

O

LCD

O

LCD

LCD

LCD

LCD

1 frame

12/18

Page 13

MSM5259¡ Semiconductor

13/18

APPLICATION CIRCUITS

(Connected to MSM6222B-01 LCD Controller)

LCD

COM 1-16

SEG 1-40

DO

MSM6222B-01

MSM5259

V

DD

V

SS

V

2

V

3

V

5

CP

L

DF

V

DD

GND

V

1

V

2

V

3

V

4

V

5

O1-O

40

DF

CP

LOAD

DI

1

DO

20

DI

21

DO

40

MSM5259

V

DD

V

SS

V

2

V

3

V

5

O1-O

40

DF

CP

LOAD

DI

1

DO

20

DI

21

DO

40

MSM5259

V

DD

V

SS

V

2

V

3

V

5

O1-O

40

DF

CP

LOAD

DI

1

DO

20

DI

21

DO

40

CC

C

CC

OV

RR RR R

+5V

Page 14

MSM5259¡ Semiconductor

14/18

Application Circuit for Static Display

V

5

V

3

V

DD

V

2

O

1

CP

DI

1

DF

LOAD

V

SS

(GND)

COM

COM

MSM4069

32-120H

Z

Duty 50%

COMMON

SIGNAL

DATA IN

SHIFT

CLOCK

LOAD

DO

20DI21

MSM5259

O

40

DO

40

+5V

V

5

V

3

V

DD

V

2

O

1

CP

DI

1

DF

LOAD

V

SS

(GND)

DO

20DI21

MSM5259

O

40

+5V

80-DOT LCD PANEL

Seg

40

Seg

1

Seg

80

Seg

41

The MSM5259 is applicable to a static LCD by setting V2 and V5 at ground level, connecting V3 to VDD and

inputting COMMON SIGNAL to DF pin.

This sample application circuit below is the case when the MSM5259 is applied to an 80-bit LCD panel by connecting

two MSM5259s in series.

Page 15

PACKAGE DIMENSIONS

QFP56-P-910-0.65-K

Mirror finish

MSM5259¡ Semiconductor

(Unit : mm)

Package material

Lead frame material

Pin treatment

Solder plate thickness

Package weight (g)

Epoxy resin

42 alloy

Solder plating

5 mm or more

0.36 TYP.

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which

are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki’s responsible sales person for the

product name, package name, pin number, package code and desired mounting conditions

(reflow method, temperature and times).

15/18

Page 16

QFP56-P-910-0.65-L2

Spherical surface

MSM5259¡ Semiconductor

(Unit : mm)

Package material

Lead frame material

Pin treatment

Solder plate thickness

Package weight (g)

Epoxy resin

42 alloy

Solder plating

5 mm or more

0.36 TYP.

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which

are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki’s responsible sales person for the

product name, package name, pin number, package code and desired mounting conditions

(reflow method, temperature and times).

16/18

Page 17

QFP56-P-910-0.65-2K

Mirror finish

MSM5259¡ Semiconductor

(Unit : mm)

Package material

Lead frame material

Pin treatment

Solder plate thickness

Package weight (g)

Epoxy resin

42 alloy

Solder plating

5 mm or more

0.43 TYP.

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which

are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki’s responsible sales person for the

product name, package name, pin number, package code and desired mounting conditions

(reflow method, temperature and times).

17/18

Page 18

QFP56-P-910-0.65-2L2

Spherical surface

MSM5259¡ Semiconductor

(Unit : mm)

Package material

Lead frame material

Pin treatment

Solder plate thickness

Package weight (g)

Epoxy resin

42 alloy

Solder plating

5 mm or more

0.43 TYP.

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which

are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki’s responsible sales person for the

product name, package name, pin number, package code and desired mounting conditions

(reflow method, temperature and times).

18/18

Loading...

Loading...