Page 1

ISO-9001 CERTIFIED BY DSCC

ULTRA HIGH SPEED/VOLTAGE

NEGATIVE OUTPUT

VIDEO AMPLIFIER

M.S.KENNEDY CORP.

4707 Dey Road Liverpool, N.Y. 13088 (315) 701-6751

1933

SERIES

FEATURES:

Low Cost Complete Amplifier System

100Vpp Output Signal Into 10pF

Ultra Fast Transition Times: 2.5nS @ 50Vpp

User Adjustable Contrast and Brightness

TTL Compatible Blanking

On Board DC Reference Output

Customized Versions Readily Available

Available with Three Lead Bend Options

MIL-PRF-38534 CERTIFIED

DESCRIPTION:

The MSK 1933 Series of High Speed, High Voltage Video Amplifiers are designed to drive the grid of today's high

performance CRTs. The MSK 1933 has user adjustable contrast and brightness levels and also comes with a blanking

function. The MSK 1933 can be directly connected to many video sources including RS170, RS343 and high speed

video D/A converters. The MSK 1933 is available in four versions for different applications. The MSK 1933-0 has no

internal high voltage resistor or inductor allowing the user to dissipate much of the power externally. The MSK 1933-

2, MSK 1933-4 and the MSK 1933-6 each have an internal resistor-inductor designed for optimum bandwidth. The

MSK 1933-6 has slightly lower bandwidth but can be operated from up to -120V. Each version of the MSK 1933 is

packaged in an isolated 22 pin insulated ceramic substrate that can be directly connected to a heat sink using

standard mounting techniques. The leads are available straight out, bent up or bent down.

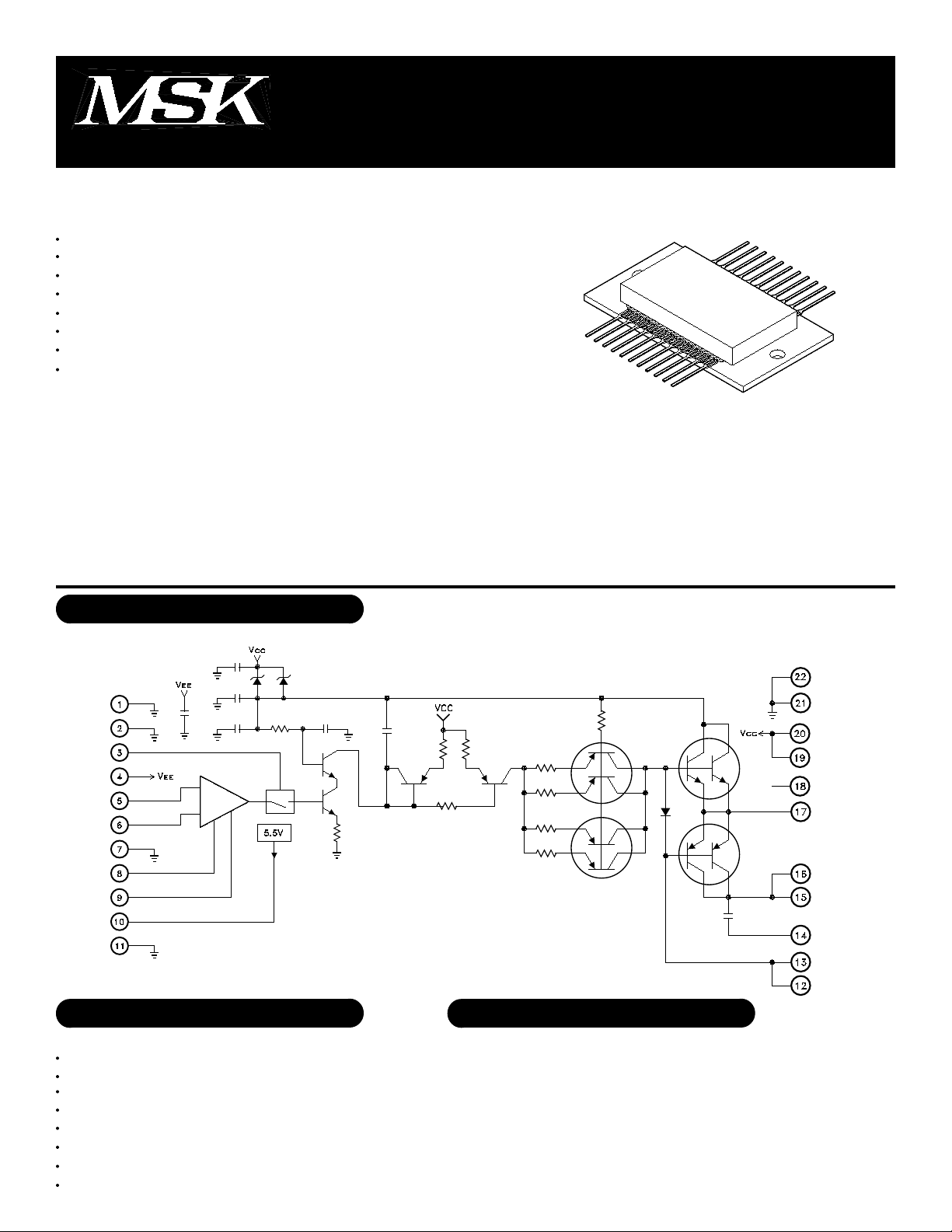

EQUIVALENT SCHEMATIC

TYPICAL APPLICATIONS

Helmet Mounted Displays

High Resolution RGB Displays

High Resolution Monochrome Displays

Automatic Test Equipment

Medical Monitors

CAE/CAD Station Monitors

Projection Displays

Beam Index Displays

PIN-OUT INFORMATION

Ground

1

2

3

4

5

6

7

8

Ground

Blank

VEE

-Input

+Input

Ground

VGain

1

9

10

11

12

13

14

15

16

Voff

Vref

Ground

-VHV RES

-VHV RES

Ground

-VHV

-VHV

17

18

19

20

21

22

Output

N/C

Vcc

Vcc

Ground

Ground

Rev. A 8/00

Page 2

ABSOLUTE MAXIMUM RATINGS

-VHV

High Voltage Supply (1933-0)

(1933-2)

(1933-4)

(1933-6)

VCC

VEE

VIN

VIC

VGAIN

VOFF

Positive Supply Voltage

Negative Supply Voltage

Differential Input Voltage

Common Mode Input Voltage

Gain Adjust Input Voltage

Offset Adjust Input Voltage

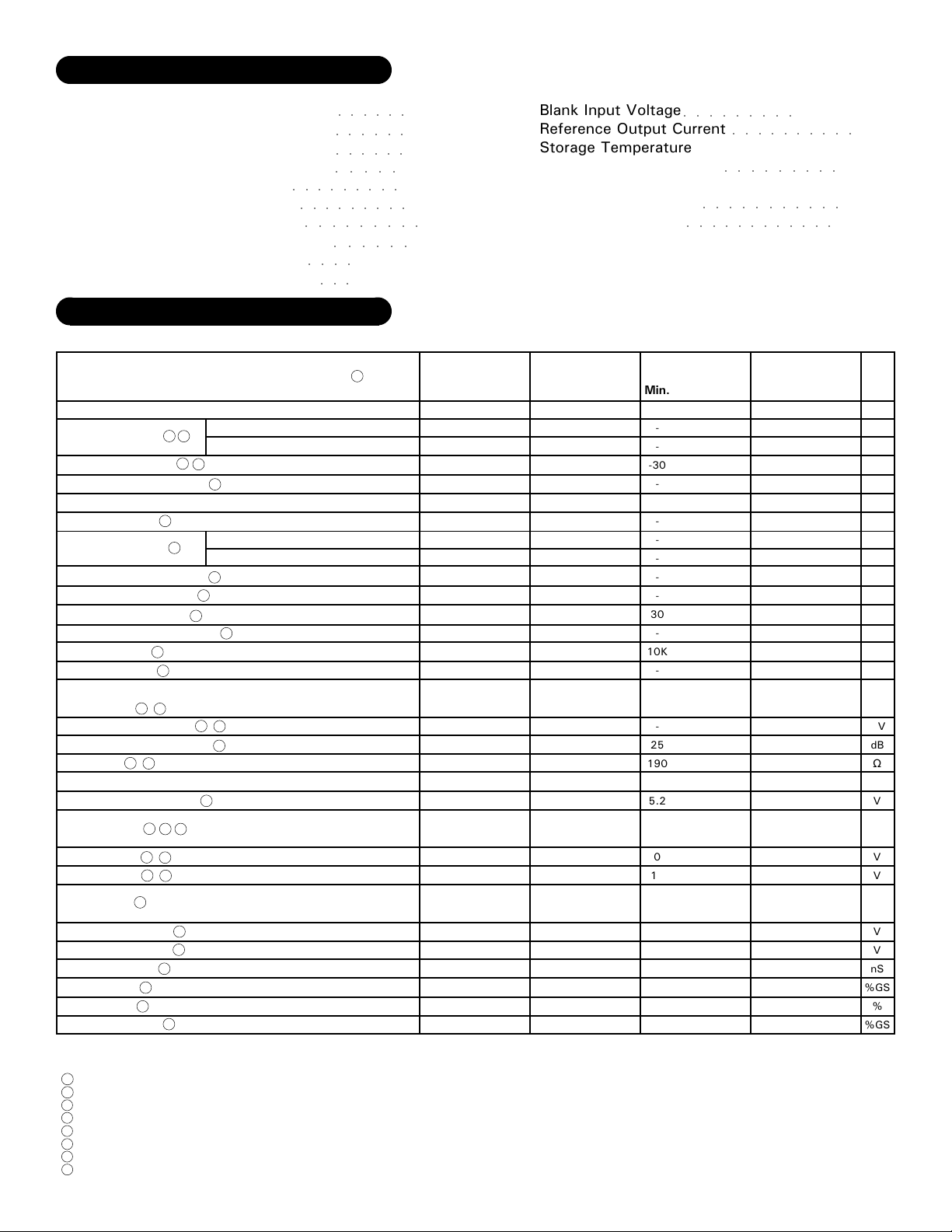

ELECTRICAL SPECIFICATIONS

Parameter

STATIC

6

Quiescent Current

High Voltage Supply

Thermal Resistance to Case

INPUT

Input Bias Current

Blank Input Current

Offset Adjust Input Current

Gain Adjust Input Current

Blank Input Pulse Width

Common Mode Rejection Ratio

Input Impedance

Input Capacitance

Blank Mode Input

Rejection ∆V

Gain Adjust Rejection ∆V

Power Supply Rejection Ratio

Internal Rp

OUTPUT

Reference Output Voltage

∆V Blank Mode

∆V Min Offset

∆V Max Offset

Voltage Gain

Output Voltage High

Output Voltage Low

Transistion Times

Linearity Error

Gain Linearity

Thermal Distortion

3

8

2

3

6

6

7

3

3

3

3

4

4

6

4

5

6

5

5

6

3

3

∆V=VHV-VOUT VOFF=0V VGAIN=3V

6

6

6

6

7

VGAIN =4V VOFF=1V VCM=0.5V

3

○○○○○○

○○○○○○

○○○○○○

○○○○○

○○○○○○○○○

○○○○○○○○○

○○○○○○○○○

○○○○○○

-0.6 to +6V

○○○○

-0.6 to +6V

○○○

Test Conditions

VCM=0V @ +20V

VCM=0V @ -10.5V

QOUT and QCAS

3

VCM=0V

VBLANK=0.4V

VBLANK=2.4V

7

3

4

+VCC and -VEE=Nom ±5%

3

VBLANK=2.4V VGAIN=5V

VOFF=1V VIN=2.0V VCM=0.5V

VOFF=1V

VGAIN=5V

Normal Operation

VCM=±0.5V F=10Hz

Either Input F=DC

Either Input

VBLANK=2.4V VIN=0.3V

∆V=VHV-VOUT

∆VGAIN=5V

IOUT<2mA

∆V=VHV-VOUT VOFF=1V

∆V=VHV-VOUT VOFF=5V

VIN=0.6V F=10KHz

VGAIN=3V Both Inputs

VGAIN=3V F=10KHz

VGAIN=3V F=10KHz

VIN=0.6V TR=TF<0.5nS

1

-95V

-95V

-75V

-120V

+22V

-12V

2V

±2V

Min.

-30

30

10K

25

5.2

32

-85

VBLANK

IREF

TST

TLD

TJ

IRP

TC

MSK1933-0

Typ.

75

-

-75

-

-90

10

-

±1

-

500

-

300

-

2

-

2

-

-

40

-

20K

2

-

-

-

30

0

-

5.5

3

0

42

-88

-1

-

3.5

-

-

-

-

-

-

-

Blank Input Voltage

Reference Output Current

Storage Temperature Range

Lead Temperature Range

(10 Seconds)

Junction Temperature

Current Through Rp

Case Operating Temperature

(All Devices)

MSK1933-2

Max.

Min.

100

-

-100

-

-95

-30

13

-

±50

-

600

-

400

-

10

-

10

-

-

30

-

-

-

10K

-

-

-

-

25

-

380

5.8

5.2

3xRpRp-3xRp 3xRpRp-3xRp

6

0

52

32

-

-85

-5

-

6.0

-

±2

-

±2

-

±2

-

Typ.

75

-75

-90

10

±1

500

300

2

2

-

40

20K

2

-

30

400

5.5

3

42

-88

-1

3.0

-

-

-

Max.

100

-100

-95

13

±50

600

400

10

10

-

-

-

-

-

420

5.8

6

52

1381107213811072

-

-5

5.0

±2

±2

±2

Min.

-30

10K

190

5.2

36

-65

○○○○○○○○○

○○○○○○○○○○

○○○○○○○○○

○○○○○○○○○○○

○○○○○○○○○○○○

MSK1933-4

Max.

Typ.

75

-75

-70

10

±1

500

300

2

2

-

40

20K

2

-

30

200

5.5

3

21

-68

-1

2.5

-

-

-

100

-100

-75

13

±50

600

400

10

10

-

-

-

-

±10xRp±10xRp±10xRp3

-

210

5.8

3xRpRp-3xRp

6

26

6855

-

-5

4.0

±2

±2

±2

-

-

-

-

-

-

-

-

30

-

-

-

25

0

16

-

-

-

-

-

-0.6 to +6V

5mA

-40°C to +150°C

300°C

150°C

290mA

-25°C to +125°C

MSK1933-6

Units

Max.

Typ.

Min.

100

-100

-120

12

±50

600

400

10

10

-

-

-

-

-

420

5.8

3xRpRp-3xRp

10

52

145

-

-5

8

±2

±2

±2

mA

mA

V

°C/W

µA

µA

µA

µA

µA

nS

dB

Ω

pF

mV

mV

dB

Ω

V

mV

V

V

V/V

V

V

nS

%GS

%

%GS

-30

30

10K

25

380

5.2

0

32

72

-95

75

-

-75

-

-100

8

-

±1

-

500

-

300

-

2

-

2

-

-

40

-

20K

2

-

--±2xRp--±2xRp--±2xRp--±2xRp

±10xRp

-

-

30

400

5.5

3

42

120

-98

-1

-

6

-

-

-

-

-

-

-

NOTES:

1

CC = +20V, -VEE = -10.5V, VBLANK = VGAIN = VOFF = ±VIN = 0V, CL=10pF, TC=25°C unless otherwise specified.

+V

2

VHV=Typical Value for each dash number for all parameters.

3

This parameter is guaranteed by design but need not be tested. Typical parameters are representative of actual device performance but are for reference only.

4

RP=Internal RP except MSK 1933-0. External value = 400Ω unless otherwise specified for the MSK 1933-0.

5

∆V is defined as the difference between -VHV and the output.

6

Parameter is 100% tested on production devices.

7

Parameter is sample tested in accordance with MSK industrial grade quality devices.

8

When the output is amplifying a video signal, the output current will be present at +VCC and -VHV since the output is referred to +VCC internally.

2

Rev. A 8/00

Page 3

APPLICATION NOTES

POWER SUPPLIES

The input stage of the MSK 1933 requires power supplies of

+20V and -10.5V for optimum operation. The negative power

supply can be increased to -12V if -10.5V is not available, but

additional power dissipation will cause the internal temperature

to rise. Both low voltage power supplies should be effectively

decoupled with tantalum capacitors (at least 4.7µF) connected

as close to the amplifier's pins as possible. The MSK 1933 has

internal 0.01µF capacitors that also improve high frequency

performance. It is also recommended to put 0.1µF decoupling

capacitors on the +20V and -10.5V supplies as well. Since

the output stage is returned to +20V internally, all of the out-

put current will flow through this supply pin.

The high voltage power supply (-VHV) is connected to the

amplifier's output stage and must be kept as stable as possible.

The internal or external Rp is connected to -VHV and as such,

the amplifier's DC output is directly related to the high voltage

value. The -VHV pins of the hybrid should be decoupled to

ground with as large a capacitor as possible to improve output

stability.

SUPPLY SEQUENCING

The power supply sequence is VHV, VCC, VEE followed by the

other DC control inputs. If power supply sequencing is not

possible, the time difference between each supply should be

less than five milliseconds. If the DC control signals are being

generated from a low impedance source other than the VREF

output, reverse biased diodes should be connected from each

input (VGAIN, VOFF) to the VCC pin. This will protect the inputs

until VCC is turned on.

VIDEO INPUTS

The video input signals should be kept below ±2VMAX total,

including both common mode offset and signal levels. The

input structure of the MSK 1933 was designed for ±0.714Vpp

RS343 signals. If either input is not used it should be con-

nected directly to the analog ground or through a 25Ω resistor

to ground if input offset currents are to be minimized.

OUTPUT PROTECTION

The output pin of the MSK 1933 should be protected from

transients by connecting reversed biased ultra-low capacitance

diodes from the output pin to both -VHV and ground. The out-

put can also be protected from arc voltages by inserting a small

value (25-50Ω) resistor in series with the amplifier. This resis-

tor will reduce system bandwidth along with the load capaci-

tance, but a series inductor can reduce the problem substan-

tially.

VGAIN CONTROL INPUT

The VGAIN control (contrast) input is designed to allow the

user to vary the video gain. By simply applying a DC voltage

from 0V to VREF, the video gain can be linearly adjusted from 0

to 195V/V (MSK 1933-2). The VGAIN input should be connected

to the VREF pin through a 5KΩ pot to ground. For convenient

stable gain adjustment, a 0.1µF bypass capacitor should be con-

nected near the VGAIN input pin to prevent output instability due

to noisy sources. Digital gain control can be accomplished by

connecting a D/A converter to the VGAIN pin. However, some

temperature tracking performance may be lost when using an

external DC voltage source other than VREF for gain adjustment.

The bandwidth of the VGAIN input is approximately 1MHz.

The overall video output of the MSK 1933 can be character-

ized using the following expression:

VIDEO OUTPUT

When power is first applied and VIN=VGAIN=VOFF=0V, the

output will be practically at the -VHV rail voltage. The output

voltage is a function of the value of Rp and also the VGAIN and

VOFF DC inputs. The maximum output voltage swing for any of

the MSK 1933 variants is determined by Vpp = (250mA) x

(Rp). The bandwidth of the amplifier largely depends on both

Rp and Lp.

Hybrid pins 12 and 13 are directly connected to Rp. Addi-

tional external resistance can be added to reduce power dissi-

pation, but slower transition times will result. If an additional

resistor is used, it must be low capacitive and the layout should

minimize capacitive coupling to ground (ie: no ground plane

under Rp).

The MSK 1933 Series is conservatively specified with low

values for Lp which yield about 5% overshoot. Additional peak-

ing can be obtained by using a high self-resonant frequency

inductor in series with pins 12 & 13. Since this value of induc-

tance can be very dependent on circuit layout, it is best to

determine its value by experimentation. A good starting point

is typically 0.47µH for the MSK 1933-0 and 0.0047µH for the

remaining devices.

If external resistors or inductors are not used, be sure to

connect high frequency bypass capacitors directly from pins

12 and 13 to ground for the devices that contain an internal

Rp.

Vpp=VHV-VOUT

VHV-VOUT=(VIN)(VGAIN)(Rp)(0.09)

(or)

Voltage Gain=VOUT/VIN=(VGAIN)(Rp)(0.09)

Here is a sample calculation for the MSK 1932-2:

Given information

VIN=0.7V

VGAIN=1VDC

Rp=400Ω (internal)

VHV=-80VDC

VHV-VOUT=(0.7V)(1V)(400Ω)(0.09)

VHV-VOUT=25.2V Nominal

The expected video output would swing from approximately

-80V to -54.8V assuming that VOFF=0V. This calculation should

be used as a nominal result because the overall gain may vary as

much as ±20% due to internal high speed device variations.

Changing ambient conditions can also effect the video gain of

the amplifier by as much as 150 PPM/°C. It is wise to connect

all video amplifiers to a common heat sink to maximize thermal

tracking when multiple amplifiers are used in applications such

as RGB systems. Additionally, only one of the VREF outputs

should be shared by all three amplifiers. This voltage should be

buffered with a suitable low drift op-amp for best tracking per-

formance.

3

Rev. A 8/00

Page 4

APPLICATION NOTES CON'T

VOFF CONTROL INPUT

The brightness (output offset) can be linearly adjusted by

applying a 0 to VREF DC voltage to the VOFF input pin. The

output quiescent voltage range is from approximately (5µA)(Rp)

to (100mA)(Rp) from -VHV. This control voltage is normally

generated by connecting the VOFF control pin to a 5K potenti-

ometer between VREF and ground. The VOFF input pin should

be bypassed with a 0.1µF capacitor to ground placed as close

as possible to the hybrid. This DC voltage can be any stable

system source. The bandwidth of the VOFF pin is approximately

1MHz.

Keep hybrid power dissipation in mind when adjusting the

output quiescent voltage. Practically all of the voltage is seen

across Rp! This power must be taken into account when high

Rp currents are used. If the quiescent level is set too close to

-VHV, the power dissipation will be minimal but the rise time

will suffer slightly. If the quiescent level is set too far from

-VHV, the power dissipation will increase dramatically and the

output fall time will be limited. The output black level is obvi-

ously dependent on system requirements but a little experi-

mentation will strike the optimum balance between power dis-

sipation and bandwidth. Total current through Rp should be

limited to less than 290mA when operating from power sup-

plies greater than 90V. The gain adjust alone can set the AC

current to 250mA (ie: 250mApp=100Vpp/400Ω). Typically,

most applications use about 10V from -VHV for a black level.

BLANK INPUT

The video input can be electrically disconnected from the

ampliifer by applying a TTL high input to the blank pin. When

this occurs, the output will be set to approximately -VHV. The

VGAIN and VOFF control pins have little or no effect on the out-

put when it is in blank mode.

When the TTL compatible blank input is not used, the pin

must be connected to ground to enable the amplifier. The blank

input will float high when left unconnected which will disable

the video.

VREF OUTPUT

The MSK 1933 has an on board buffered DC zener reference

output. The VREF output is nominally 5.5V DC and has full

temperature test limits of 5.2V to 5.8V DC. This output is

provided for gain and offset adjustment and can source up to

4mA of current.

THERMAL MANAGEMENT

The MSK 1933 package has mounting holes that allow the

user to connect the amplifier to a heat sink or chassis. Since

the package is electrically isolated from the internal circuitry,

mounting insulators are not required or desired for best thermal

performance. Use 4 to 6 inch/pounds for mounting the device

to the heat sink.

The power dissipation of the amplifier depends mainly on the

load requirements, bandwidth, pixel size, black level and the

value of Rp. The following table illustrates a few examples:

DEVICE

TYPE

1933-6

1933-6

1933-4

1933-4

This table does not include power dissipation due to output switching since this is dependent on individual load requirements. The input stage

power dissipation is typically 2.5 watts and is essentially independent of output levels.

-VHV

-120V

-120V

-70V

-70V

BLACK

LEVEL

-110V

-110V

-65V

-65V

WHITE

LEVEL

-20V

-20V

-15V

-15V

OUTPUT

VOLTAGE

0V

-90V

0V

-50V

PERCENT OF SIGNAL

BLANK

100%

20%

100%

20%

BLACK

0%

40%

0%

40%

WHITE

0%

40%

0%

40%

OUTPUT

AVE. Pd

0W

13.3W

0W

8.4W

TOTAL

AVE. Pd

2.5W

15.7W

2.5W

10.6W

RESOLUTION TABLE FOR TYPICAL CRT'S

Display

Resolution

320 x 200

640 x 350

640 x 480

800 x 560

1024 x 900

1024 x 1024

1280 x 1024

1664 x 1200

2048 x 2048

4096 x 3300

All data assumes retrace time equal to 30% of frame time and a 60Hz refresh rate.

Maximun

Pixel

Time

182nS

52nS

38nS

26nS

12.6nS

11nS

8.9nS

5.8nS

2.8nS

860pS

Minimum Pixel

Clock

Frequency

5MHz

19MHz

26MHz

38MHz

80MHz

90MHz

112MHz

170MHz

360MHz

1.2GHz

4

Required Rise Time

at CRT

60nS

17nS

12.5nS

8.6nS

4.2nS

3.7nS

2.9nS

1.9nS

1nS

280pS

Required System

Bandwidth

(F-3dB)

6MHz

20MHz

28MHz

41MHz

84MHz

95MHz

120MHz

180MHz

380MHz

1.23GHz

Rev. A 8/00

Page 5

TYPICAL CONNECTION CIRCUIT

The connection circuit shown above is for the MSK 1933-0 evaluation board. The Rp and Lp are external compo-

nents and must not be located near ground planes if possible. A high quality resistor such as Bradford Electronics P/

N FP10-400 is required for optimum response times. Use an inductor with a high self-resonant frequency that can

withstand the currents required for the application.

When using the other variants of the MSK 1933, place an additional bypass capacitor on pins 12 and 13 if series

(Rp and Lp) components are not utilized. The pin should connect to -VHV with a short low impedance path.

For additional applications information, please contact the factory. Evaluation amplifiers with test boards are

readily available for MSK.

NOTES:

5

Rev. A 8/00

Page 6

MECHANICAL SPECIFICATIONS

ESD TRIANGLE INDICATES PIN 1. TORQUE SPECIFICATION 4 TO 6 IN/LBS.

ALL DIMENSIONS ARE ±0.010 INCHES UNLESS OTHERWISE LABELED.

ORDERING INFORMATION

PART

NUMBER

MSK 1933S-0

MSK 1933D-0

MSK 1933U-0

MSK 1933S-2

MSK 1933D-2

MSK 1933U-2

MSK 1933S-4

MSK 1933D-4

MSK 1933U-4

MSK 1933S-6

MSK 1933D-6

MSK 1933U-6

LEAD

OPTION

STRAIGHT

DOWN

UP

STRAIGHT

DOWN

UP

STRAIGHT

DOWN

UP

STRAIGHT

DOWN

UP

4707 Dey Road, Liverpool, New York 13088

The information contained herein is believed to be accurate at the time of printing. MSK reserves the right to make

changes to its products or specifications without notice, however, and assumes no liability for the use of its products.

-VHV

MAX

-95V

-95V

-75V

-120V

INTERNAL

RP

NONE

400Ω

200Ω

400Ω

M.S. Kennedy Corp.

Phone (315) 701-6751

FAX (315) 701-6752

www.mskennedy.com

6

TYPICAL

RISE TIME

3.5nS

3.0nS

2.5nS

6.0nS

SCREENING

Industrial

Industrial

Industrial

Industrial

LEVEL

Rev. A 8/00

Loading...

Loading...