Datasheet MM74HC4538SJ, MM74HC4538MX, MM74HC4538SJX, MM74HC4538N, MM74HC4538M Datasheet (Fairchild Semiconductor)

Page 1

© 2000 Fairchild Semiconductor Corporation DS005217 www.fairchildsemi.com

February 1984

Revised August 2000

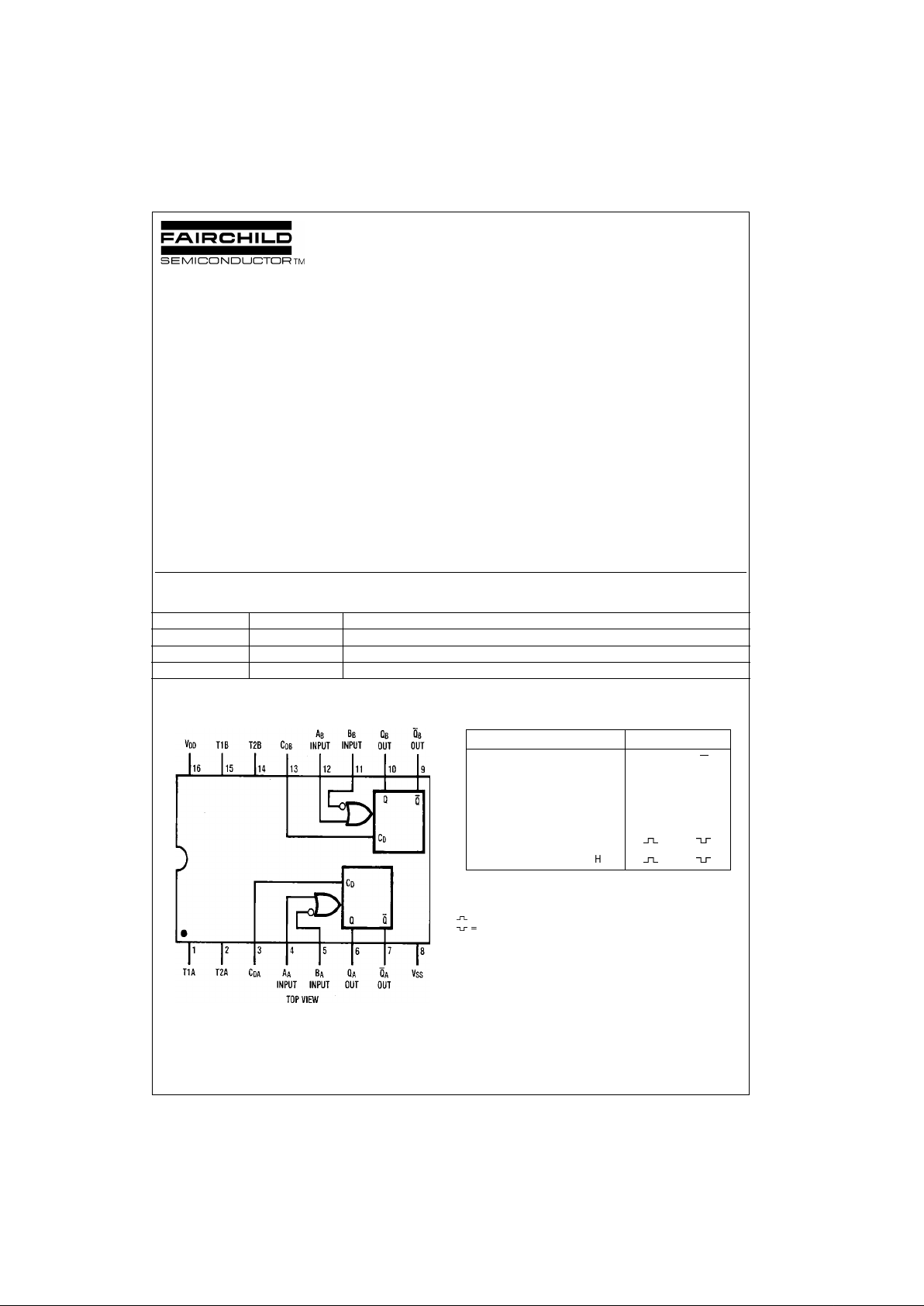

MM74HC4538 Dual Retriggerable Monostable Multivibrator

MM74HC4538

Dual Retriggerable Monostable Multivibrator

General Description

The MM74HC4538 high speed monostable multivibrator

(one shots) is implemented in advanced silicon-gate

CMOS technology. They feature speeds comparable to low

power Schottky TTL circuitry whil e retaining the l ow power

and high noise immunity characteristic of CMOS circuits.

Each multivibrator fea tures b oth a n egative , A, a nd a po sitive, B, transition trigg ered input, either of which can be

used as an inhibit input. Also includ ed is a clear input that

when taken low rese ts the one shot . The M M74HC 4538 is

retriggerable. Th at is, it may be triggered repeatedly w hile

their outputs are generating a pulse and the pulse will be

extended.

Pulse width stability over a wide range of temperature and

supply is achieved using linear CMOS techniques. The output pulse equatio n is s imply: PW

= 0.7(R)(C) where PW is

in seconds, R is in ohms, and C is in fa rads. This de vice is

pin compatible with the CD4528, and the CD4538 one

shots. All inputs are prote cted from damage due to stat ic

discharge by diodes to V

CC

and ground.

Features

■ Schmitt trigger on A and B inputs

■ Wide power supply range: 2–6V

■ Typical trigger propagation delay: 32 ns

■ Fanout of 10 LS-TTL loads

■ Low input current: 1

µA max

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

Connection Diagram Truth Table

H = HIGH Level

L = LOW Level

↑ = Transition from LOW-to-HIGH

↓ = Transition from HIGH -t o-LOW

= One HIGH Level Pulse

= One LOW Level Pu ls e

X = Irrelevant

Order Number Package Number Package Description

MM74HC4538M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

MM74HC4538SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

MM74HC4538N N16E 16-Lead Plastic D ual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Inputs Outputs

Clear A B Q Q

LXXLH

XHXLH

XXLLH

HL

↓

H ↑ H

Page 2

www.fairchildsemi.com 2

MM74HC4538

Block Diagrams

Note: Pin 1 and Pin 15 must be hard-wired to GND.

Logic Diagram

Page 3

3 www.fairchildsemi.com

MM74HC4538

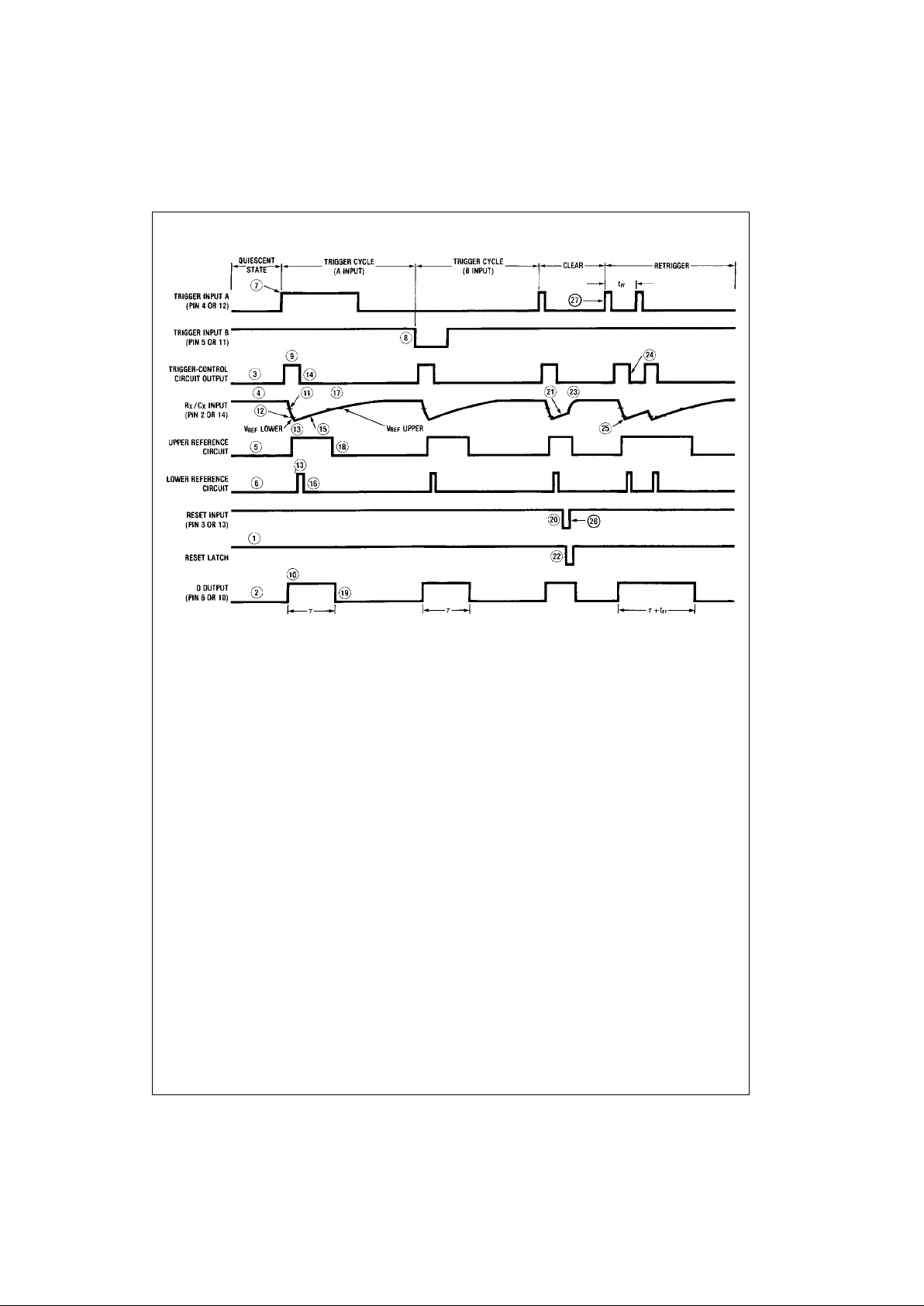

Timing Diagram

Circuit Operation

The MM74HC4538 op erates as follow s (refer to lo gic diagram). In the quiescent state, th e external timing capacitor,

C

X

, is charged to VCC. When a trigger occurs, the Q output

goes HIGH and C

X

discharges quickly to the lowe r refer-

ence voltage (V

REF

Lower = 1/3 VCC). CX then charges,

through R

X

, back up to the upper refere nce voltage (V

REF

Upper = 2/3 VCC), at which point the one-shot has timed out

and the Q output goes LOW.

The following, more de tailed description of the ci r cuit o pe r-

ation refers to both the logic diagram and the timing diagram.

QUIESCENT STATE

In the quiescent state, before an inp ut trigger appe ars, the

output latch is HIGH and the reset latch is HIGH (#1 in logic

diagram).

Thus the Q output (pin 6 or 10) of the mono stable multivi brator is LOW (#2, timing diagram).

The output of the trigge r-control circuit is LOW (#3), and

transistors M1, M2, and M3 are turned off. The external

timing capacitor, C

X

, is charged to VCC (#4), and the upper

reference circuit has a LO W output (#5). Transistor M4 i s

turned ON and transmission gate T1 is turned OFF. Thus

the lower reference circuit has V

CC

at the noninverting

input and a resulting LOW output (#6).

In addition, the output of the trigger-con trol reset circuit is

LOW.

TRIGGER OPERATION

The MM74HC4538 is tr iggere d by e ithe r a r ising -edge signal at input A (#7) or a falling-edge signal at input B (#8),

with the unused tr igger input and the Reset input held a t

the voltage levels sho wn in the Truth Table. Either trigger

signal will cause the output of the trigger-control circuit to

go HIGH (#9).

The trigger-control circ uit going HIGH simultaneously initiates three events. Fir st, the output l atch goes LOW, thus

taking the Q output of the HC4538 to a H IGH State (#10) .

Second, transistor M3 is tur ned on , whi ch allows the external timing capacitor, C

X

, to rapidly discharge toward

ground (#11). (Note that the voltag e across C

X

appears at

the input of the upper refer ence circuit comp arator.) Third,

transistor M4 is turned off and transmission gate T1 is

turned ON, thus allowing the voltage across C

X

to also

appear at the input of the lowe r reference circuit comparator.

When C

X

discharges to the referen ce voltage of the low er

reference circuit (#12), the outputs of both reference circuits will be HIGH (#13). The trigger-control reset circuit

goes HIGH, resetting the trigger-control circuit flip-flop to a

LOW State (#14). This turns transistor M3 OFF again,

allowing C

X

to begin to charge back up toward VCC, with a

time constant t

= R

XCX

(#15). In addition, tran sistor M4 is

turned ON and transmission gate T1 is turned OFF. Thus a

high voltage level is applied to the input of the lower reference circuit comparator, causing its output to go LOW

(#16). The monos table multivi brator may b e retriggere d at

any time after the trigger-control circuit goes LOW.

When C

X

charges up to the reference vo ltag e of the up per

reference circuit (#17) , the output of the upper reference

circuit goes LOW (#1 8). This causes the output latch to

Page 4

www.fairchildsemi.com 4

MM74HC4538

Circuit O p e ration (Continued)

toggle, taking the Q output of the HC4538 to a LOW State

(#19), and completing the time-out cycle.

RESET OPERATI ON

A low voltage applied to the Rese t pin alway s forces the Q

output of the HC4538 to a LOW State.

The timing diagram illustrates the case in which reset

occurs (#20) while C

X

is charging up toward th e referen ce

voltage of the upper refe rence circuit (#21) . When a reset

occurs, the output of the r eset latch goes LOW (# 22) , turning ON transistor M1. Thu s C

X

is allowed to quickly charge

up to V

CC

(#23) to await the next trigger signal.

Recovery time is the requi red delay after reset go es inactive to a new trigger rising edge. On the diagram it is shown

as (#26) to (#27).

RETRIGGER OPERATION

In the retrigger able mode , the HC45 38 ma y be retrigg ere d

during timing out of the outp ut pulse at any time after the

trigger-control circuit flip-flop has been reset (#24).

Because the trigger-control circuit flip-flop resets shortly

after C

X

has discharged t o the reference voltage of the

lower reference circuit (#25), the minimum retrigger time, t

rr

is a function of internal propagation delays and the discharge time of C

X

:

at room temperature

POWER-DOWN CONSIDERATIONS

Large values of C

X

may cause problems when po wering

down the MM74HC4538 because of the amount of e nergy

stored in the capacitor. When a system containing this

device is powered down, the capacit or ma y dis char ge from

V

CC

through the input pr otection diodes at pin 2 or pin 14.

Current through the protection diodes must be limited to 30

mA; therefore, the tu rn-off time of the V

CC

power supply

must not be faster than t

= V

CC•CX

/(30 mA). For exa mpl e, if

V

CC

= 5V an d CX = 15 µF, the VCC supply must turn OF F

no faster than t

= (15V)•(15 µF)/30 mA = 2.5 ms. This is

usually not a problem because p ower su pplies are h eavily

filtered and cannot discharge at this rate.

When a more rapid decrease of V

CC

to zero volts occurs,

the MM74HC4538 may sust ai n da ma ge. To avoid this possibility, use an external clamping diode, D

X

, connected

from V

CC

to the CX pin.

SET UP RECOMMENDATIONS

Minimum R

X

= 1 kΩ

Minimum CX = 0 pF.

Page 5

5 www.fairchildsemi.com

MM74HC4538

Absolute Maximum Ratings(Note 1)

(Note 2)

Recommended Operating

Conditions

Note 1: Maximum Ratings ar e those val ues beyo nd which damage to t he

device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation Temperature Derating: Plas tic “N” Package: −

12mW/°C from 65°C to 85°C.

DC Electrical Characteristics (Note 4)

Note 4: For a power supply of 5V ±10% the worst case output voltages (VOH, and VOL) occur for HC at 4.5V. Thus the 4. 5V valu es shou ld be u sed when

designing with this supply. Worst case V

IH

and VIL occur at VCC = 5.5V and 4.5 V respectively. (The VIH value at 5.5V is 3.85V.) The worst case leakage cur-

rent (I

IN

, ICC, and IOZ) occur for CMOS at the higher voltage and so th e 6. 0V values should be use d.

Supply Voltage (VCC) −0.5 to +7.0V

DC Input Voltage (V

IN

) −1.5 to V

CC

+1.5V

DC Output Voltage (V

OUT

) −0.5 to V

CC +

0.5V

Clamp Diode Current (I

IK

, IOK) ±20 mA

DC Output Current, per pin (I

OUT

) ±25 mA

DC V

CC

or GND Current, per pin (ICC) ±50 mA

Storage Temperature Range (T

STG

) −65°C to +150°C

Power Dissipation (P

D

)

(Note 3) 600 mW

S.O. Package only 500 mW

Lead Temperature (T

L

)

(Soldering 10 seconds) 260

°C

Min Max Units

Supply Voltage (V

CC

)26V

DC Input or Output Voltage 0 V

CC

V

(V

IN

, V

OUT

)

Operating Temperature Range (T

A

) −40 +85 °C

Input Rise or Fall Times

(Reset only)

(t

r

, tf) V

CC

= 2.0V 1000 ns

V

CC

= 4.5V 500 ns

V

CC

= 6.0V 400 ns

Symbol Parameter Conditions

V

CC

TA = 25°CTA = −40 to 85°CTA = −55 to 125°C

Units

Typ Guaranteed Limits

V

IH

Minimum HIGH Level Input 2.0V 1.5 1.5 1.5 V

Voltage 4.5V 3.15 3.15 3.15 V

6.0V 4.2 4.2 4.2 V

V

IL

Maximum LOW Level Input 2.0V 0.5 0.5 0.5 V

Voltage 4.5V 1.35 1.35 1.35 V

6.0V 1.8 1.8 1.8 V

V

OH

Minimum HIGH Level Output V

IN

= VIH or V

IL

Voltage |I

OUT

| ≤ 20 µA 2.0V 2.0 1.9 1.9 1.9 V

4.5V 4.5 4.4 4.4 4.4 V

6.0V 6.0 5.9 5.9 5.9 V

V

IN

= VIH or V

IL

|I

OUT

| ≤ 4.0 mA 4.5V 3.98 3.84 3.7 V

|I

OUT

| ≤ 5.2 mA 6.0V 5.48 5.34 5.2 V

V

OL

Maximum LOW Level Output V

IN

= VIH or V

IL

2.0V 0 0.1 0.1 0.1 V

Voltage |I

OUT

| ≤ 20 µA 4.5V 0 0.1 0.1 0.1 V

6.0V 0 0.1 0.1 0.1 V

V

IN

= VIH or V

IL

|I

OUT

| ≤ 4.0 mA 4.5V 0.26 0.33 0.4 V

|I

OUT

| ≤ 5.2 mA 6.0V 0.26 0.33 0.4 V

I

IN

Maximum Input Current V

IN

= VCC or GND 6.0V ±0.1 ±1.0 ±1.0 µA

(Pins 2, 14) (Note 5)

I

IN

Maximum Input Current V

IN

= VCC or GND 6.0V ±0.1 ±1.0 ±1.0 µA

(all other pins)

I

CC

Maximum Active Supply Pins 2, 14 = 0.5 V

CC

Active Current Q1, Q2 = HIGH 6.0V 150 250 400 µA

VIN = VCC or GND

ICC Maximum Quiescent Supply Pins 2, 14 = OPEN

Quiescent Current Q1, Q2 = LOW 6.0V 130 220 350 µA

VIN = VCC or GND

Page 6

www.fairchildsemi.com 6

MM74HC4538

DC Electrical Characteristics (Continued)

Note 5: The device must be set up w it h 3 s t eps before measuring IIN:

AC Electrical Characteristics

V

CC

= 5V, T

A

= 25° C, C

L

= 15 pF, tr = t

f

= 6 ns

AC Electrical Characteristics

C

L

= 50 pF, tr = t

f

= 6 ns (unless otherwise specified)

Clear A B

1. H L H

2. H H H

3. H L H

Symbol Parameter Conditions Typ Limit Units

t

PLH

Maximum Propagation Delay A, or B to Q 23 45 ns

t

PHL

Maximum Propagation Delay A, or B to Q 26 50 ns

t

PHL

Maximum Propagation Delay Clear to Q 23 45 ns

t

PLH

Maximum Propagation Delay Clear to Q 26 50 ns

t

W

Minimum Pulse Width A, B or Clear 10 16 ns

Symbol Parameter Conditions

V

CC

TA=25°CTA=−40 to 85°CTA = −55 to 125°C

Units

Typ Guaranteed Limits

t

PLH

Maximum Propagation 2.0V 100 250 315 373 ns

Delay A, or B to Q 4.5V 25 50 63 75 ns

6.0V 21 43 54 63 ns

t

PHL

Maximum Propagation 2.0V 110 275 347 410 ns

Delay A, or B to Q 4.5V 28 55 69 82 ns

6.0V 23 47 59 70 ns

t

PHL

Maximum Propagation 2.0V 100 250 315 373 ns

Delay Clear to Q 4.5V 25 50 63 75 ns

6.0V 21 43 54 63 ns

t

PLH

Maximum Propagation 2.0V 110 275 347 410 ns

Delay Clear to Q 4.5V 28 55 69 82 ns

6.0V 23 47 59 70 ns

t

TLH

, t

THL

Maximum Output 2.0V 30 75 95 110 ns

Rise and Fall 4.5V 10 15 19 22 ns

Time 6.0V 8 13 16 19 ns

tr, t

f

Maximum Input 2.0V 1000 1000 1000 ns

Rise and Fall 4.5V 500 500 500 ns

Time (Reset only) 6.0V 400 400 400 ns

t

W

Minimum Pulse Width 2.0V 80 101 119 ns

A, B, Clear 4.5V 16 20 24 ns

6.0V 14 17 20 ns

t

REC

Minimum Recovery 2.0V −50 0 0 ns

Time, Clear 4.5V 0 0 0 ns

Inactive to A or B 6.0V 0 0 0 ns

t

WQ

Output Pulse Width CX = 12 pF Min 3.0V 283 190 ns

RX = 1 kΩ 5.0V 147 120 ns

Max 3.0V 283 400 ns

5.0V 147 185 ns

t

WQ

Output Pulse Width CX = 100 pF Min 3.0V 1.2 µs

RX = 10 kΩ 5.0V 1.0 µs

Max 3.0V 1.2 µs

5.0V 1.0 µs

Page 7

7 www.fairchildsemi.com

MM74HC4538

AC Electrical Characteristics (Continued)

Note 6: CPD determines the no lo ad dynamic consumption, PD = CPD V

CC

2

f+ICC VCC, and the no load dynam ic c urrent consumption , IS = VCC f + ICC.

Symbol Parameter Conditions

V

CC

TA=25°CTA=−40 to 85°CTA = −55 to 125°C

Units

Typ Guaranteed Limits

t

WQ

Output Pulse Width CX = 1000 pF Min 3.0V 10.5 9.4 µs

R

X

= 10 kΩ 5.0V 10.0 9.3 µs

Max 3.0V 10.5 11.6 µs

5.0V 10.0 10.7 µs

t

WQ

Output Pulse Width CX = 0.1µF Min 5.0V 0.63 0.602 0.595 ms

R

X

= 10k Max 5.0V 0.77 0.798 0.805 ms

C

IN

Maximum Input 25 pF

Capacitance (Pins 2 & 14)

C

IN

Maximum Input 5 10 10 10 pF

Capacitance (other inputs)

C

PD

Power Dissipation (per one shot) 150 pF

Capacitance (Note 6)

∆t

WQ

Pulse Width Match

Between Circuits in ±1%

Same Package

Page 8

www.fairchildsemi.com 8

MM74HC4538

Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

Package Number M16A

Page 9

9 www.fairchildsemi.com

MM74HC4538

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

Package Number M16D

Page 10

www.fairchildsemi.com 10

MM74HC4538 Dual Retriggerable Monostable Multivibrator

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Package Number N16E

Fairchild does not assume any responsibility for use of any circuitr y described, no circuit patent licenses are implied and

Fairchild reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

1. Life supp or t devices o r syste ms a re devices or syste ms

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be reasonably expected to result in a significant inju ry to the

user.

2. A critic al com ponent in any compon ent of a life supp ort

device or system whose failure t o perform can be reasonably expected to ca use the failure of the life supp ort

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

Loading...

Loading...