Page 1

查询MM74C912供应商

MM74C912

6-Digit BCD Display Controller/Driver

MM74C912 6-Digit BCD Display Controller/Driver

October 1987

Revised January 1999

General Description

The MM74C912 display contr oller s are interface el emen ts,

with memory, that drive a 6-digit, 8-segment LED display.

The display controllers receive data infor mation through 5

data input s A, B, C, D an d DP, and digit i n f o rmat i o n th ro ug h

3 address inputs K1, K2 and K3.

The input data is wr itten into the register se lected by the

address information when CHIP ENABLE, (CE

WRITE ENABLE, (WE

either CE

required. A self-contained internal oscillator sequentially

presents the stored da ta to a decoder where 4 data bits

control the format of the displayed character an d 1 bit co ntrols the decimal point. The internal oscillator is controlled

by a control input labeled OSCILLATOR ENABLE, (OSE

which is tied LOW in normal operation. A high level at OSE

prevents automatic refresh of the display.

The 7-segment plus decimal point output information

directly drives an LE D display through high dr ive (100 mA

or WE return HIGH. Data hold time is not

), are LOW and is latched when

), and

typ.) output drivers. The drivers are active when the control

pin labeled SEGMENT OUTPUT ENABLE, (SOE

and go into 3-STATE when SOE

allows for duty cycle bright ness control and for disabling

the output drivers for power conservati on.

The MM74C912 segment de coder conver ts BCD data into

7-segment format.

All inputs are TTL compati ble and do not clam p to the V

supply.

is HIGH. This feature

Features

■ Direct segment drive (100 mA typ.) 3-STATE

■ 6 registers addressed like RAM

■ Internal oscillator and scanning circuit

),

■ Direct base drive to digit transistor (20 mA typ.)

■ Internal segment decoder

■ TTL compatible inputs

Ordering Code:

Order Number Package Number Package Description

MM74C912N N28B 28-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600” Wide

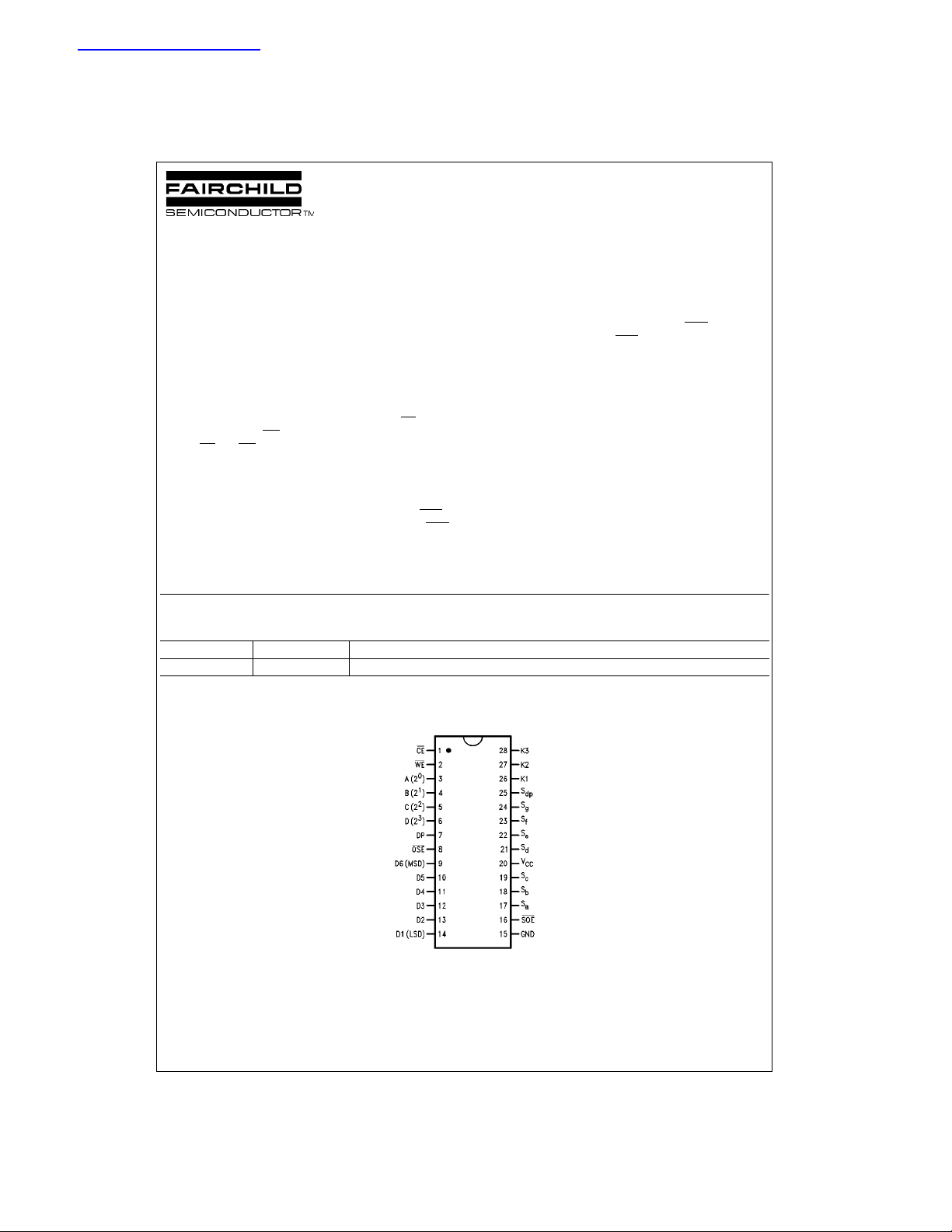

Connection Diagram

Dual-In-Line Package

), is LOW

CC

Top View

© 1999 Fairchild Semiconductor Corporation DS005916.prf www.fairchildsemi.com

Page 2

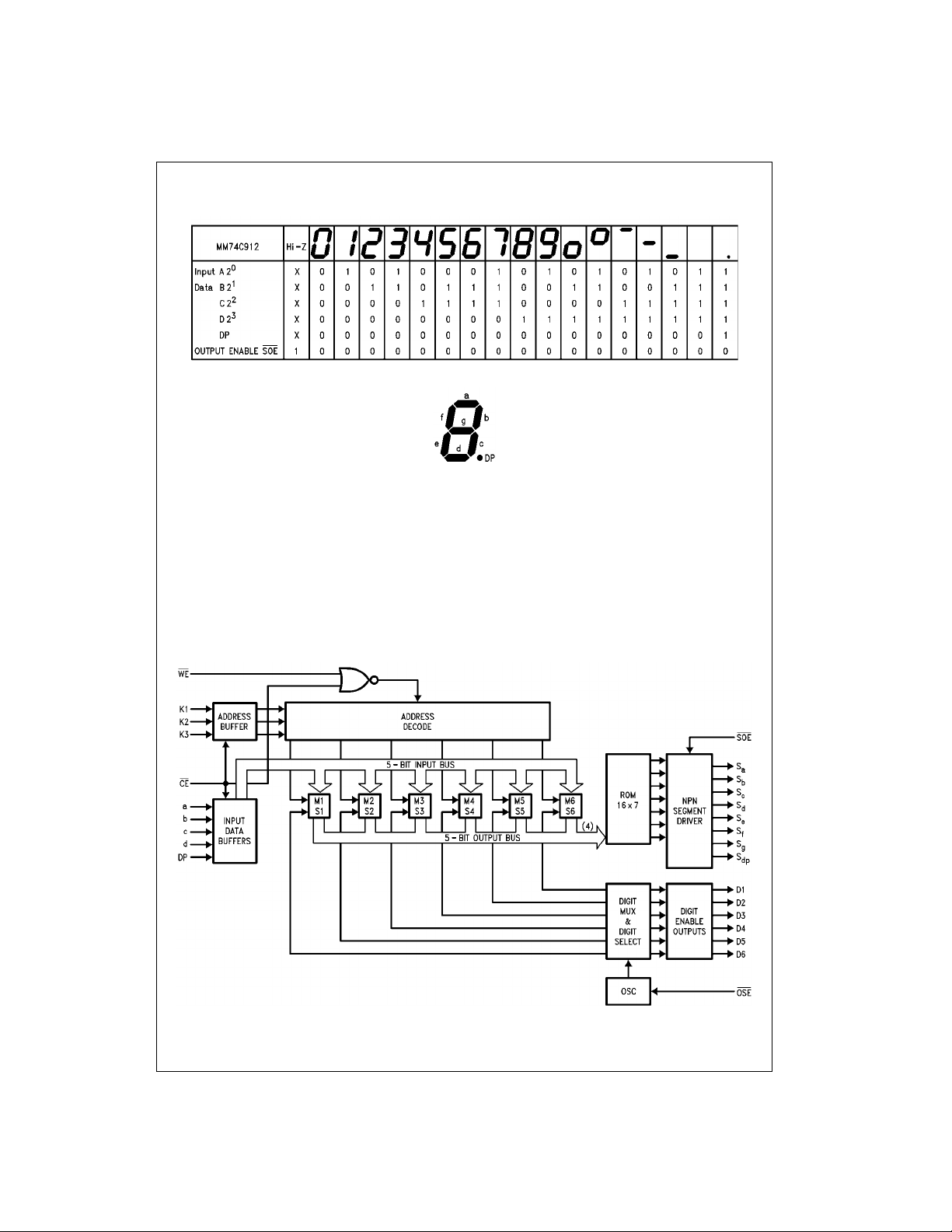

Truth Tables

MM74C912

X = Don’t Care

Input Contr o l

CE Digit Address WE Operation

K3 K2 K1

00000Write Digit 1

00001Latch Digit 1

00010Write Digit 2

00011Latch Digit 2

00100Write Digit 3

00101Latch Digit 3

00110Write Digit 4

00111Latch Digit 4

01000Write Digit 5

01001Latch Digit 5

01010Write Digit 6

01011Latch Digit 6

01100Write Null Digit

01101Latch Null Digit

01110Write Null Digit

01111Latch Null Digit

1XXXXDisable Writing

Output Control

SOE

0 0 Refresh Display

0 1 Stop Oscillator (Note 1)

1 0 Disable Segment Outputs

1 1 Standby Mode

Note 1: Segment drive may exceed maximum display dissip at ion.

www.fairchildsemi.com 2

OSE Operation

Page 3

Functional Description

MM74C912

Character Font

Segment Identi fic at i on

The MM74C912 display controll er is manufactured using

metal gate CMOS technology. A single 5V 74 series TTL

supply can be used for power and shou ld be bypassed at

pin.

the V

CC

All inputs are TTL co mpatible; the segment outputs dr ive

the LED display directly through current limiting resistors.

The digit outputs ar e desi gned to dir ectly dr ive the base of

Block Diagram

a grounded emitte r digit transistor without the ne ed of a

Darlington configuration.

As seen in the block diagram, these display controllers

contain six 5-bit register s; any one of which may be randomly written. Th e internal multi plexer scans the registers

and refreshes the di splay. This combination of write only

memory and self-scan display makes the display controller

a “refreshing experi ence” for an over-burdened microprocessor.

3 www.fairchildsemi.com

Page 4

Absolute Maximum Ratings(Note 2)

(Note 3)

Voltage at Any Pin

Except Inputs −0.3V to V

MM74C912

Voltage at Any Input −0.3V to +15V

Operating Temperature

Range (T

Storage Temperature

Range (T

Power Dissipation (P

) −40°C to +85°C

A

) −65°C to +150°C

S

) Refer to P

D

D MAX

vs TA Graph

CC

+ 0.3V

Operating V

Absolute Maximum (V

Lead Temperature

(Soldering, 10 seconds) 260°C

Note 2: “Absolute Maxi mum Ratings” are those valu es beyond which the

safety of the device cann ot be guaran teed. Excep t for “Operating R ange”

they are not meant to imply that the device should be operated at these limits. The table of “Electr ical Characteristic s” provides conditions for a ctual

device operation.

Note 3: All voltages reference to ground.

Range 3V to 6V

CC

)6.5V

CC

DC Electrical Characteristics

Min/Max limits apply at 40°C ≤ TJ ≤ 85°C, unless otherwise noted

Symbol Parameter Conditions Min Typ Max Units

CMOS TO CMOS

V

IN(1)

V

IN(0)

I

IN(1)

I

IN(0)

I

CC

I

OUT

CMOS/LPTTL INTERFA CE

V

IN(1)

V

IN(0)

OUTPUT DRIVE

I

SH

I

DH

V

OUT(1)

V

OUT(0)

θ

JA

Note 4: θJA measured in free air w it h device soldered into print ed circuit board.

Logical “1” Input Voltage VCC = 5V 3.0 V

Logical “0” Input Voltage VCC = 5V 1.5 V

Logical “1” Input Current VCC = 5V, VIN = 15V 0.005 1.0 µA

Logical “0” Input Current VCC = 5V, VIN = 0V −1.0 −0.005 µA

Supply Current VCC = 5V, Outputs Open 0.5 2 mA

3-STATE VCC = 5V, VO = 5V 0.03 10 µA

Output Current VCC = 5V, VO = 0V −10 −0.03 µA

Logical “1” Input Voltage VCC = 4.75V VCC − 2.0 V

Logical “0” Input Voltage VCC = 4.75V 0.8 V

High Level VCC = 5V, VO = 3.4V

Segment Current TJ = 25°C −60 −100 mA

TJ = 100°C −40 −60 mA

High Level VCC = 5V, VO = 1V

Digit Current TJ = 25°C −10 −20 mA

TJ = 100°C −7 −15 mA

Logical “1” Output Voltage VCC = 5V, IO = −360µA4.6 V

Any Digit

Logical “0” Output Voltage VCC = 5V, IO = 360µA0.4V

Any Digit

Thermal Resistance (Note 4) 100 °C/W

www.fairchildsemi.com 4

Page 5

AC Electrical Characteristics (Note 5)

VCC = 5V, tr = tf = 20 ns, CL = 50 pF

Symbol Parameter Conditions Min Typ Max Units

t

CW

t

AW

t

WW

t

DW

t

WD

t

WA

t

WC

t1H, t

tH1, t

t

IB

f

MUX

C

IN

C

OUT

Note 5: AC Parameters are guaranteed by DC correlated testing.

Note 6: Capacitance is guaranteed by periodic testing.

Chip Enable to Write TJ = 25°C3515ns

Enable Setup Time TJ = 125°C5020ns

Address to Write TJ = 25°C3515ns

Enable Setup Time TJ = 125°C5020ns

Write Enable Width TJ = 25°C 400 225 ns

TJ = 125°C 450 250 ns

Data to Write Enable TJ = 25°C 390 225 ns

Setup Time TJ = 125°C 430 250 ns

Write Enable to Data TJ = 25°C0−10 ns

Hold Time TJ = 125°C0−15 ns

Write Enable to Address TJ = 25°C0−10 ns

Hold Time TJ = 125°C0−15 ns

Write Enable to Chip Enable TJ = 25°C5030ns

Hold Time TJ = 125°C7540ns

Logical “1”, Logical “0” RL = 10k, TJ = 25°C 275 500 ns

0H

Levels into 3-STATE CL = 10 pF, TJ = 125°C 325 600 ns

3-STATE to Logical “1” to RL = 10k, TJ = 25°C 325 600 ns

H0

Logical “0” Level CL = 50 pF, TJ = 125°C 375 700 ns

Interdigit Blanking Time TJ = 25°C510µs

TJ = 125°C1020µs

Multiplex Scan Frequency TJ = 25°C350Hz

TJ = 125°C250Hz

Input Capacitance (Note 6) 5 7.5 pF

3-STATE Output Capacitance (Note 6) 30 50 pF

MM74C912

5 www.fairchildsemi.com

Page 6

Switching Time Waveforms

MM74C912

T = 1/f

MUX

Multiplexing Output Waveforms

Typical Performance Characteristics

ISH vs V

OUT

Segment output s if shorted to ground w ill exceed maximum power

dissipation of the device

IDH vs V

OUT

www.fairchildsemi.com 6

I

vs R

AVG

LIM

VCE is the saturation voltage of the digit drive transistor.

Power Dissipation vs.

Temperature for

Plastic Packages

Page 7

Typical Applications

Digit Output Structure Segment Output Structure

MM74C912

Input Protectio n

7 www.fairchildsemi.com

Page 8

Physical Dimensions in ches (millimeters) unless otherwise noted

28-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600” Wide

Package Number N28B

MM74C912 6-Digit BCD Display Controller/Dri ver

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or system s ar e devices or syste ms

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the

user.

2. A critical component in a ny compon ent of a life suppor t

device or system whose failure to perform can be reasonably expected to cause the failure of the life suppor t

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

Loading...

Loading...