Page 1

2

C BUS Control 4-Input 1-Output AV Switch MM1311

MITSUMI

I

I2C BUS Control 4-Input 1-Output AV Switch

Monolithic IC MM1311

Outline

This IC is a 4-input 1-output AV switch with I2C control, developed for use in televisions.

Features

1. Serial control by I2C BUS.

2. 4 inputs, 1 output.

3. Video and audio system switches can be controlled independently.

4. 6 dB amplifier built in to video system.

5. Built-in Y/C MIX circuit.

6. Slave address can be changed : 90H or 92H.

7. Audio muting possible by external pin.

8. Maintains high impedance even when I

9. Built-in 3 value discrimination function.

10. On-chip power ON reset function.

11. Two types of audio input impedance : 60kΩ and 30kΩ.

MM1311AD : 60kΩ MM1311BD : 30kΩ

2

C BUS line (SDA, SCL) power supply is off.

Package

SDIP-32A (MM1311AD, MM1311BD)

Applications

1. Television

2. Other video equipment

Page 2

MITSUMI

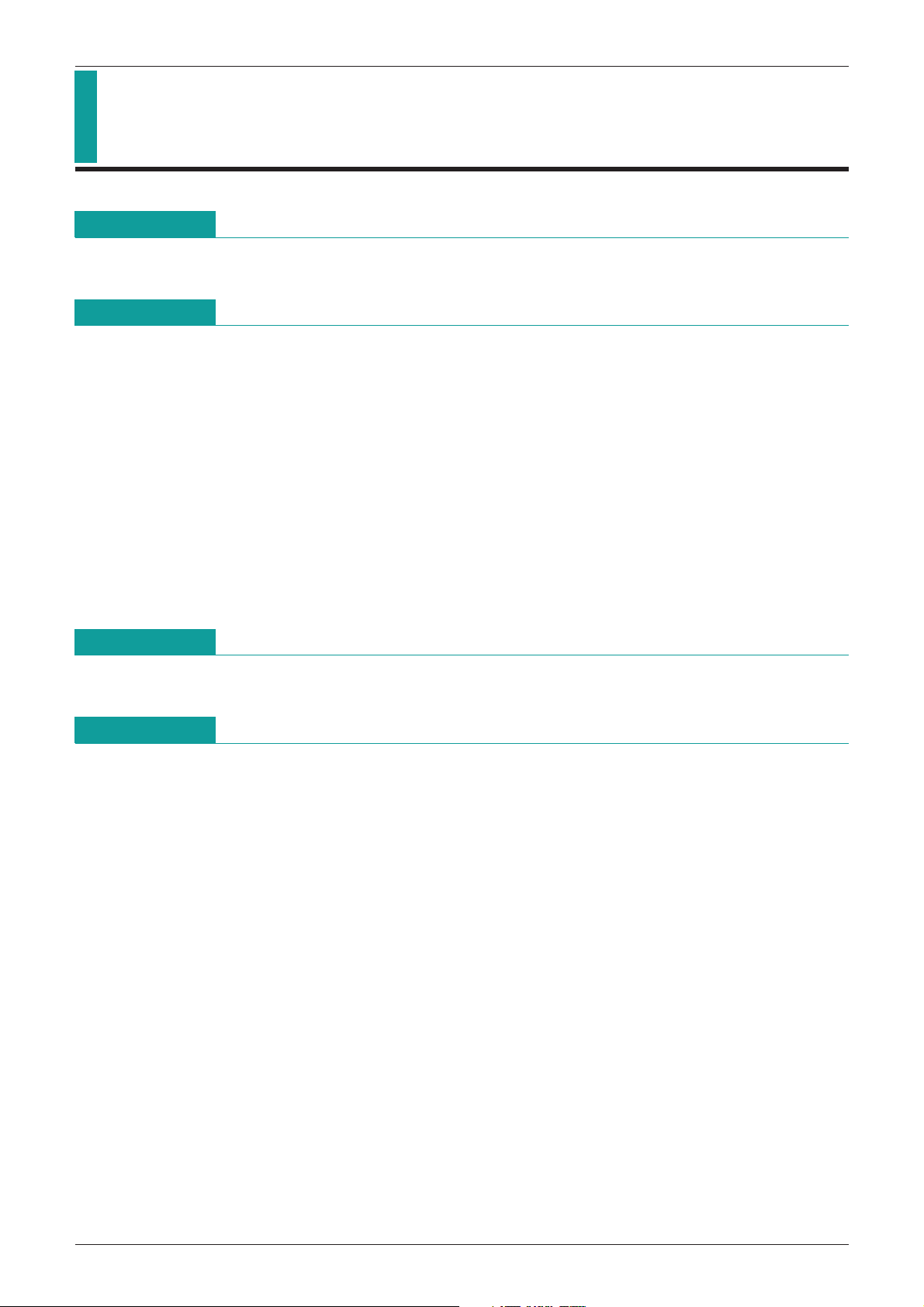

Equivalent Block Diagram

2

C BUS Control 4-Input 1-Output AV Switch MM1311

I

Page 3

MITSUMI

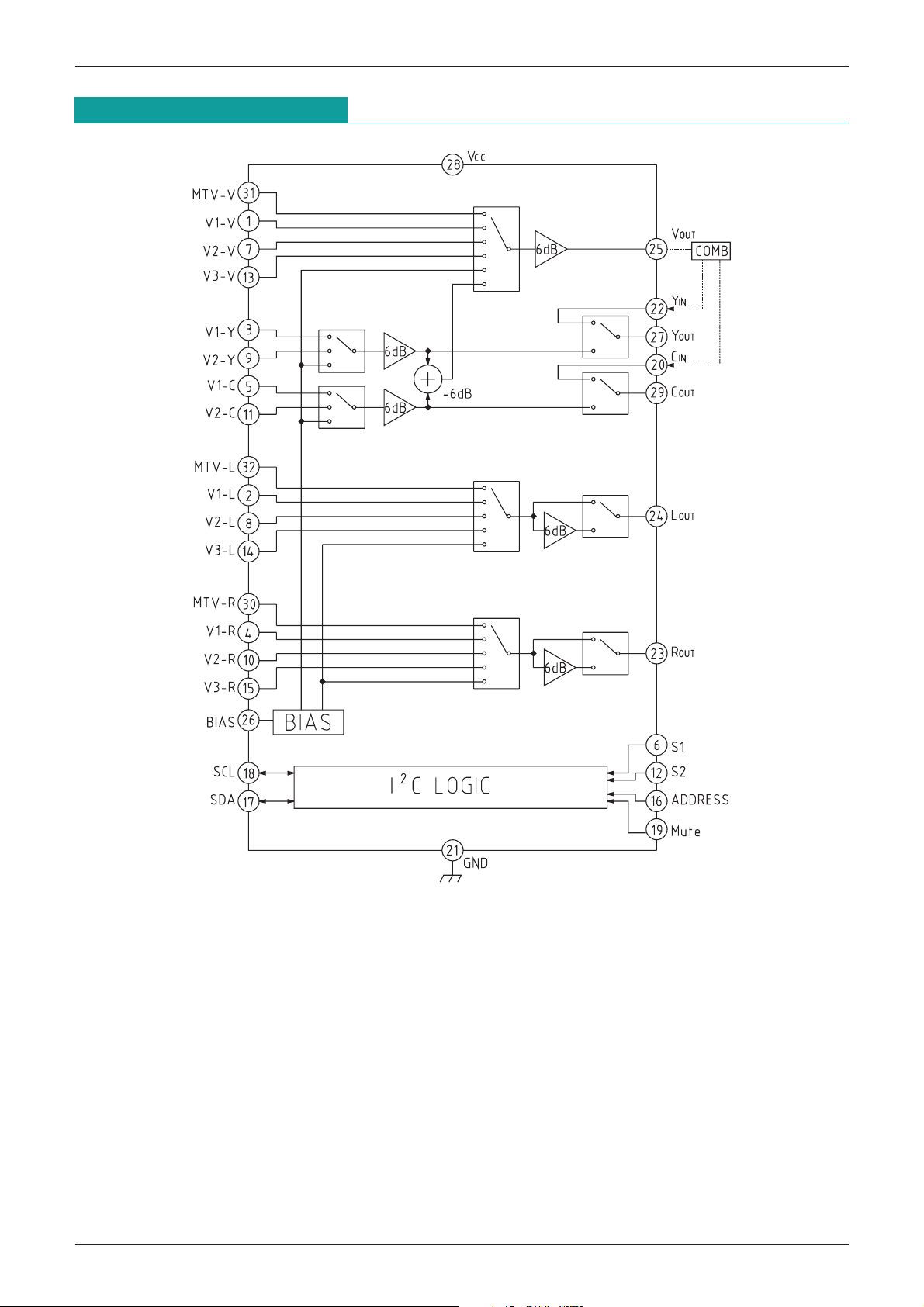

Pin Description

2

C BUS Control 4-Input 1-Output AV Switch MM1311

I

Pin No.

Name

31 MTV-V

1 V1

7 V2

13 V3

3 V1

9 V2

22 Y

5 V1-C

11 V2

20 C

32 MTV-L

2 V1

Internal equivalent circuit diagram

Pin No.

Name

Internal equivalent circuit diagram

27 YOUT

-

V

-

V

-

V

-

Y

-

Y

IN

-

C

IN

29 COUT

24 LOUT

23 ROUT

26 BIAS

-

L

8 V2

14 V3

30 MTV

4 V1

10 V2

15 V3

-

L

-

L

-

R

-

R

-

R

-

R

25 VOUT

Absolute Maximum Ratings

18 SCL

17 SDA

6 S1

12 S2

16 ADR

19 Mute

(Ta=25°C)

Item Symbol Ratings Units

Storage temperature T

Operating temperature T

Power supply voltage V

STG

OPR

CC 12 V

-

40~+125 °C

-

20~+75 °C

Allowable power dissipation Pd 950 mW

Page 4

MITSUMI

2

C BUS Control 4-Input 1-Output AV Switch MM1311

I

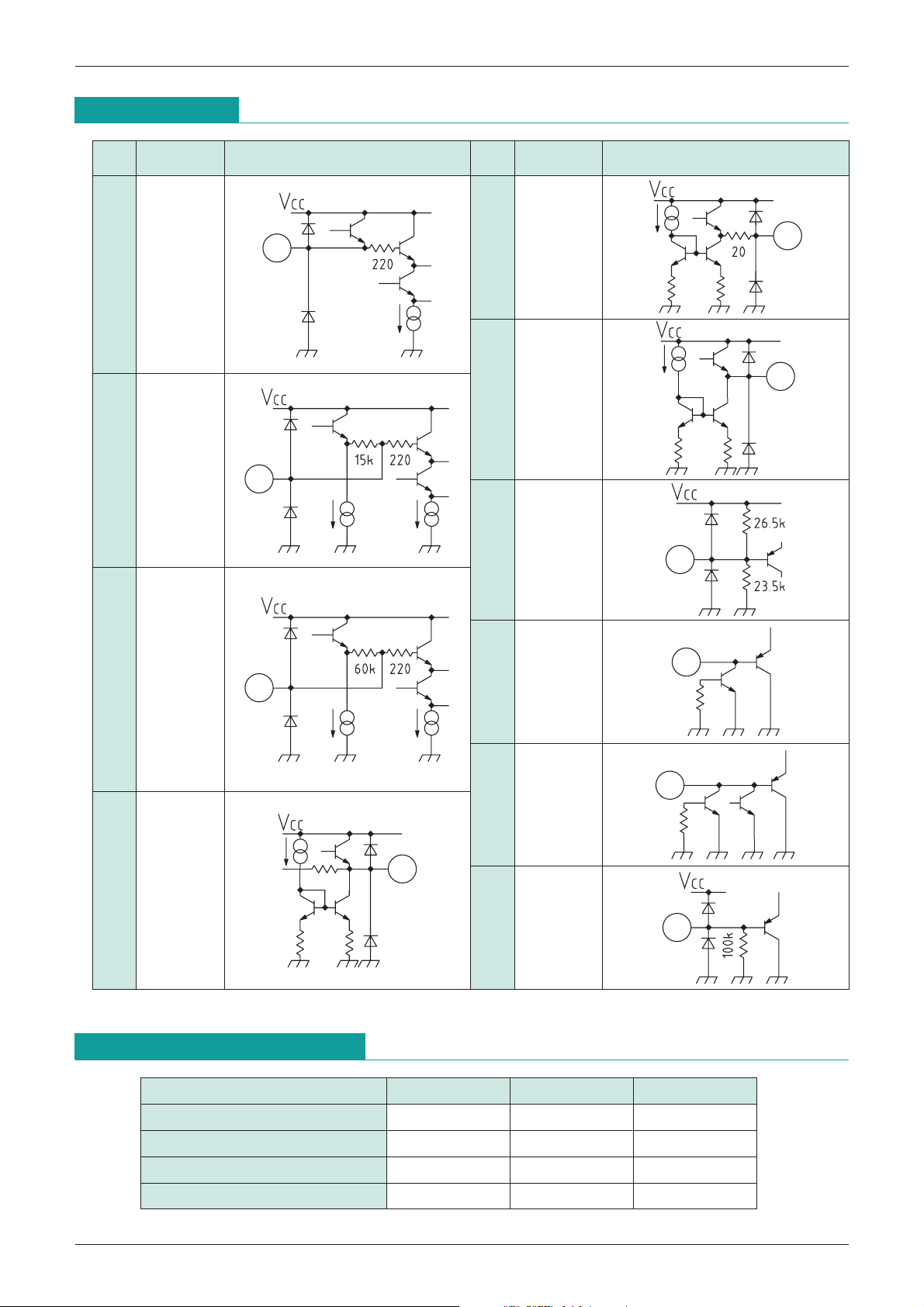

Electrical Characteristics

Item Symbol

Operating power supply voltage

Current consumption I

V

OUT output

Voltage gain G

Frequency characteristics F

(Ta=25°C, VCC=9V)

Measure

ment pin

(unless otherwise indicated, Min. Typ. Max. Units

Measurement Circuit Figure 1)

Conditions

VCC 8 9 10 V

CC 28 VCC=9V, no signal, no load 27 35 mA

V TP1 Sine wave, 1.0VP-P, 100kHz 5.5 6.0 6.5 dB

V TP1

Sine wave, 1.0V

-

V : Staircase, 1VP

Vn

P-P

APL=10~90%

Differential gain DG

V TP1

Vn-Y : Staircase (luminance signal) 1V

Vn-C : Chroma signal 0.3V

APL=10~90%

Vn

-

V : Staircase, 1VP

APL=10~90%

Differential phase DP

V TP1

Vn-Y : Staircase (luminance signal) 1V

Vn

-

C : Chroma signal 0.3VP

APL=10~90%

Sine wave, 100kHz

Maximum input for total higher

harmonic distortion factor < 1.0%

Input dynamic range D

V1

SG

1~3

YOUT output

G

Voltage gain

Frequency characteristics 10MHz/100kHz

Y1 TP2

Y2 TP2 YIN : Sine wave, 2.0VP-P, 100kHz

G

F

Y1 TP2

F

Y2 TP2

Vn-Y : Sine wave, 1.0V

Vn

-

Y : Sine wave, 1.0VP

YIN: Sine wave, 2.0V

Vn

-

Y : Staircase, 1VP

Differential gain DGY TP2 APL=10~90%

YIN: Staircase, 2V

Vn-Y : Staircase, 1VP

Differential phase DPY TP2 APL=10~90%

YIN: Staircase, 2V

Vn-Y : Sine wave100kHz

Input dynamic range

Y1SG2

D

D

Y2SG4

Maximum input for total higher

harmonic distortion factor < 1.0%

YIN : Sine wave, 100kHz

Maximum input for total higher

harmonic distortion factor < 1.0%

Output impedance Z

OUT output

C

Voltage gain

Frequency characteristics 10MHz/100kHz

Differential gain DG

Differential phase DP

Input dynamic range

OY 50 Ω

G

C1 TP3

C2 TP3 CIN : Sine wave, 2.0VP-P, 100kHz

G

F

C1 TP3

F

C2 TP3

C TP3

C TP3

D

C1SG3

Vn-C : Sine wave, 1.0V

Vn

-

C : Sine wave, 1.0VP

CIN: Sine wave, 2.0V

CIN: Staircase, 2V

CIN: Staircase, 2V

Vn

-

C : Sine wave, 100kHz

Maximum input for total higher

harmonic distortion factor < 1.0%

CIN : Sine wave, 100kHz

D

C2SG5

Maximum input for total higher

harmonic distortion factor < 1.0%

Input impedance Z

Output impedance Z

L

OUT output

Voltage gain

Frequency characteristics F

IC Vn

OC 50 Ω

G

L1 TP4 b7=0, Sine wave, 2.5VP-P, 1kHz

L2 TP4 b7=1, Sine wave, 2.5VP-P, 1kHz

G

L TP4 Sine wave, 2.5VP-P, 1MHz/1kHz

-

, 10MHz/100kHz-1.0 0 1.0 dB

-

P

P-P

-

30 3 %

P-P

-

P

P-P

-

3 0 3 deg

-

P

1.6 1.9 VP

P-P

, 100kHz

-

P

P-P,

10MHz/100kHz-1.0 0 1.0

-

P

P-P

, APL=10~90%

-

P

P-P

, APL=10~90%

5.5 6.0 6.5

-

0.5 0 0.5

-

1.0 0 1.0

-

30 3 %

-

3 0 3 deg

dB

dB

1.6 1.9

VP

3.2 3.8

P-P

, 100kHz

-

P

P-P

, 10MHz/100kHz-1.0 0 1.0

P-P

, APL=10~90%-30 3 %

P-P

, APL=10~90%-3 0 3 deg

5.5 6.0 6.5

-

0.5 0 0.5

-

1.0 0 1.0

dB

dB

2.75 3.25

V

P-P

5.5 6.5

C, CIN 10 15 20 kΩ

-

6.5-6.0-5.5

-

0.5 0 0.5

-

3.0 0 1.0 dB

dB

-

P

-

P

Page 5

MITSUMI

SDA

SCL

tBUF

P PS

tHD:STA tHD:DAT tHIGH tSU:DAT tSU:STA tSU:STO

tLOW

Sr

tR tF

2

C BUS Control 4-Input 1-Output AV Switch MM1311

I

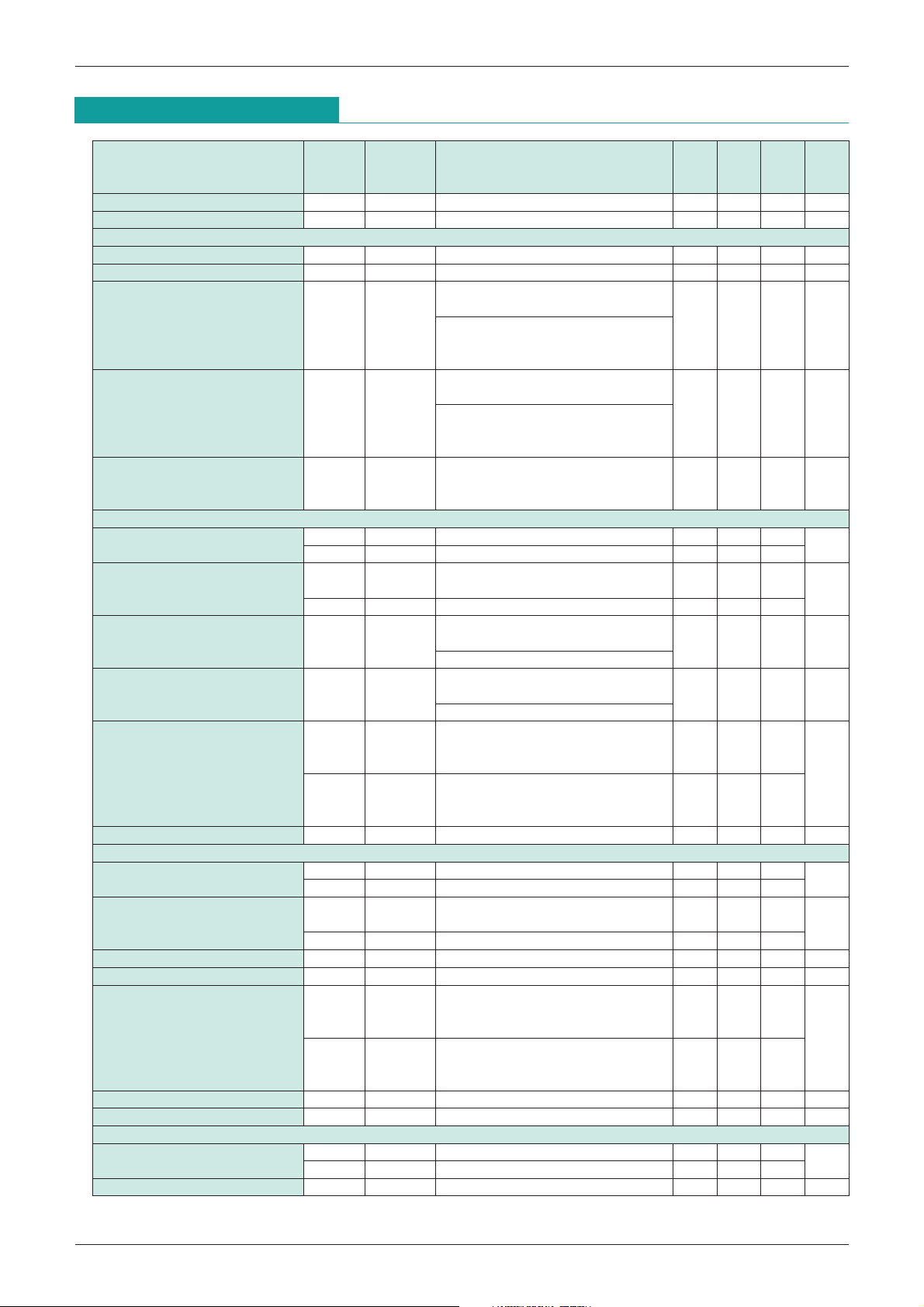

Item Symbol

Total higher harmonic distortion

THDL TP4 Sine wave, 2.5VP

Input dynamic range D

Output offset voltage V

OFFL 24

Input impedance Z

Output impedance Z

R

OUT output

Voltage gain

OL 120 Ω

G

R1 TP5

R2 TP5

G

Frequency characteristics F

Total higher harmonic distortion

THDR TP5 Sine wave, 2.5VP

Input dynamic range D

Output offset voltage V

OFFR 23

Input impedance Z

Output impedance Z

OR 120 Ω

Crosstalk

OUT CTV TP1 Measurement Circuit Figure 2

V

Y

OUT CTY TP2 SG1 input : 4.43MHz, 1VP-P

C

OUT CTC TP3 SG2 input : 4.43MHz, 0.5VP-P

L

OUT CTL TP4 Measurement Circuit Figure 2

R

OUT CTR TP5 1kHz, 2.5VP-P

Video I/O Pin Voltage

Input pin voltage V

Output pin voltage

VIP No signal, no load 4.0 4.3 4.6 V

V

VOP VOUT pin, No signal, no load 4.1 4.4 4.7 V

SOP

V

Audio I/O Pin Voltage

Input pin voltage V

Output pin voltage V

AIP No signal, no load 4.6 4.9 5.2 V

AOP No signal, no load 3.9 4.2 4.5 V

Logic section (Refer to figure below)

Input voltage L V

Input voltage H V

Low level output voltage (SDA)

High level input current I

Low level input current I

Clock frequency f

Data transmission waiting time

SCL start hold time t

SCL low level hold time t

SCL high level hold time t

SCL start set-up time t

SDA data hold time t

SDA data set-up time t

VOL SDA for 3mA inflow 0.0 0.4 V

IH when SDA, SCL=4.5V impressed

IL when SDA, SCL=0.4V impressed

SCL 100 kHz

tBUF 4.7 µS

HD : STA 4.0 µS

LOW 4.7 µS

HIGH 4.0 µS

SU : STA 4.7 µS

HD : DAT 200 nS

SU : DAT 250 nS

SCL rise time t

SCL fall time t

SCL stop set-up time t

SU : STO 4.0 µS

Measure

ment pin

(unless otherwise indicated, Min. Typ. Max. Units

Measurement Circuit Figure 1)

Conditions

-

P, 1kHz 0.03 0.1 %

Sine wave, 1kHz

L SG6

Maximum input for total higher

2.6 2.8 Vrms

harmonic distortion factor < 0.5%

L

OUT

pin DC difference during SW switching

IL 42 60 78 kΩ

R TP5

b7=0, Sine wave, 2.5V

b7=1, Sine wave, 2.5V

Sine wave, 2.5V

P-P

, 1kHz

P-P

, 1kHz

P-P

, 1MHz/1kHz-3.0 0 1.0 dB

-

P, 1kHz 0.03 0.1 %

-

-

0 ±15 mV

6.5-6.0-5.5

0.5 0

-

0.5

dB

Sine wave, 1kHz

R SG7 Maximum input for total higher 2.6 2.8 Vrms

harmonic distortion factor < 0.5%

R

OUT

pin DC difference during switching

IR 42 60 78 kΩ

Y

OUT

pin, C

OUT

IL I

IH I

pin, No signal, no load

2

C logic low level discrimination value 0.0 1.5 V

2

C logic high level discrimination value 3.0 5.0 V

3.3 3.6 3.9 V

-

-

R 1000 nS

F 300 nS

0 ±15 mV

-

60-53 dB

-

60-53 dB

-

60-53 dB

-

90-80 dB

-

90-80 dB

10 +10 µA

10 +10 µA

I2C BUS Control Signal

Page 6

MITSUMI

Measurement Circuit

Measurement Circuit 1

2

C BUS Control 4-Input 1-Output AV Switch MM1311

I

Page 7

MITSUMI

Measurement Circuit 2 (Crosstalk measurement)

2

C BUS Control 4-Input 1-Output AV Switch MM1311

I

Page 8

2

SDA

SCL

S

123456 78A123 8A P··

S:Start Condition

P:Stop Condition

ACK:Acknowledge

C BUS Control 4-Input 1-Output AV Switch MM1311

MITSUMI

I

I2C BUS

The I2C BUS is a BUS system developed by Philips for internal use in equipment. Data transmission is carried

out by the two SDA and SCL lines, in byte units, with the MSB first from start condition.

Control Register

The control register contains data sent from the master in order to determine the status of each switch.

S

A

Slave address R/W

Control register

AP

1 0 0 1 0 00/10 b7b6b5b4b3b2b1b0

Address byte Control data

The data format is set as shown in the figure above. The first 7 bits in the address byte are allocated to the

slave address, and the remaining 1 bit is allocated to the read/write bit. The read/write bit is set at 0 when

using as a control register.

The MM1311 slave address can be selected as 90H/92H depending on the status of the ADR pin. When the

ADR pin is low it is 90H. The relationship between the control register bits and switch control is as shown

below.

b7 b6 b5 b4 b3 b2 b1 b0

Audio

S/Comp

Video-Select Audio-Select

Gain Select

The control register bits are reset to 0 when power is applied.

MM1311 control is carried out by the 2-byte structure of the 1 address byte and 1 control data byte. All of the

remaining data (third byte and after) are ignored.

Refer to the separate tables for details on switch control.

Page 9

2

Reset released

Reset status

Undefined

0.6V 4.3V 5.4V V

CC

C BUS Control 4-Input 1-Output AV Switch MM1311

MITSUMI

I

Status Register

The status register contains data for sending device status to the master.

S

A

Slave address R/W

Control register

NA P

1 0 0 1 0 00/11 b7b6b5b4b3b2b1b0

Address byte Control data

The data format is set as shown in the figure above. The first 7 bits in the address byte are allocated to the

slave address, and the remaining 1 bit is allocated to the read/write bit. The read/write bit is set at 1 when

using as a status register.

The MM1311 slave address can be selected as 91H/93H depending on the status of the ADR pin. When the

ADR pin is low it is 91H. However, the confirmation response after completion of the status register should be

non-acknowledge. The status register output data as shown below.

b7 b6 b5 b4 b3 b2 b1 b0

P-ON S1 S1 S2 S2

RESET OPEN SEL OPEN SEL

P-ON RESET : Returns 1 for power on reset. However once data read begins, 0 is returned next.

S1/S2 OPEN : Returns 0 when the S1/S2 pin is not open, and returns 1 when the S1/S2 pin is open

S1/S2 SEL : Returns 0 when the S1/S2 pin is not grounded, and returns 1 when the S1/S2 pin is

grounded.

S1/S2 OPEN, SEL have 3-value discrimination, and the combinations are as shown below.

S1/S2 pin DC voltage S1/S2 OPEN S1/S2 SEL

0.8V or less 01

1.3V or more, 3.5V or less 00

4.5V or more 10

Power On Reset

Power on reset is built in to reset each control register to 0 when power is turned on.

Power on reset threshold has hysteresis as shown in the figure below. The IC power on reset status can be

discriminated by reading the status register P-ON RESET.

Page 10

MITSUMI

Switch Control Table

1. Video Output

b6 b5 b4 b3 VOUT YOUT COUT

0 0 0 0 Mute Mute Mute

2

C BUS Control 4-Input 1-Output AV Switch MM1311

I

2. Audio Output

0001 MTV

0010 V1-VYIN CIN

0011 V2-VYIN CIN

0100 V3-VYIN CIN

01

01

1 0 0 0 Mute Mute Mute

1001 MTV

1010 V1-Y+C V1-YV1

1011 V2

1100 V3

11

Mute pin b2 b1 b0 LOUT ROUT

~~

11

01

11

0 0 0 Mute Mute

-

VYIN CIN

Mute Mute Mute

-

VYIN CIN

-

C

-

Y+C V2-YV2

-

VYIN CIN

Mute Mute Mute

-

C

1.5V or less

(OPEN)

3.0V or more

3. Audio Gain Switching

0 0 1 MTV

010 V1

011 V2

100 V3

01

1

---

~

11

b7 Output gain

0

1 0dB output

-

6dB output

-

L MTV-R

-

LV1

-

LV2

-

LV3

Mute Mute

Mute Mute

-

R

-

R

-

R

Page 11

MITSUMI

Example of Application Circuit

2

C BUS Control 4-Input 1-Output AV Switch MM1311

I

Notes 1 : VOUT is set at 4.4V and CIN at 4.3V.

Please note that capacitance polarity may vary depending on

comb filter bias.

Notes 2 : Each audio output can be muted by making pin 19 high. Mute is

off when it is open or low.

Loading...

Loading...