Datasheet ML4875CS-T, ML4875ES-3, ML4875ES-5, ML4875ES-T, ML4875CS-3 Datasheet (Micro Linear Corporation)

...Page 1

July 2000

ML4875*

Low Voltage Boost Regulator with Shutdown

GENERAL DESCRIPTION

The ML4875 is a boost regulator designed for DC to DC

conversion in 1 to 3 cell battery powered systems. The

combination of BiCMOS process technology, internal

synchronous rectification, variable frequency operation,

and low supply current make the ML4875 ideal for 1 cell

applications. The ML4875 is capable of start-up with input

voltages as low as 1V and is available in 5V, 3.3V, and 3V

output versions with an output voltage accuracy of ±3%.

Unlike regulators using external Schottky diodes, the

ML4875 isolates the load from the battery when the

FEATURES

■ Guaranteed start-up and operation at 1V input

■ Pulse Frequency Modulation and Internal Synchronous

Rectification for high efficiency

■ Isolates the load from the input during shutdown

■ Minimum external components

■ Low ON resistance internal switching FETs

■ Micropower operation

■ 5V, 3.3V, and 3V output versions

SHDN pin is high. This is accomplished by an integrated

synchronous rectifier which eliminates the need for an

external Schottky diode and provides a lower forward

voltage drop, resulting in higher conversion efficiency. In

addition, low quiescent battery current and variable

frequency operation result in high efficiency even at light

loads. The ML4875 requires only one inductor and two

capacitors to build a very small regulator circuit capable

of achieving conversion efficiencies in excess of 90%.

The circuit contains a RESET output which goes low when

the DETECT input drops below 200mV. *Some Packages Are End Of Life Or Obsolete

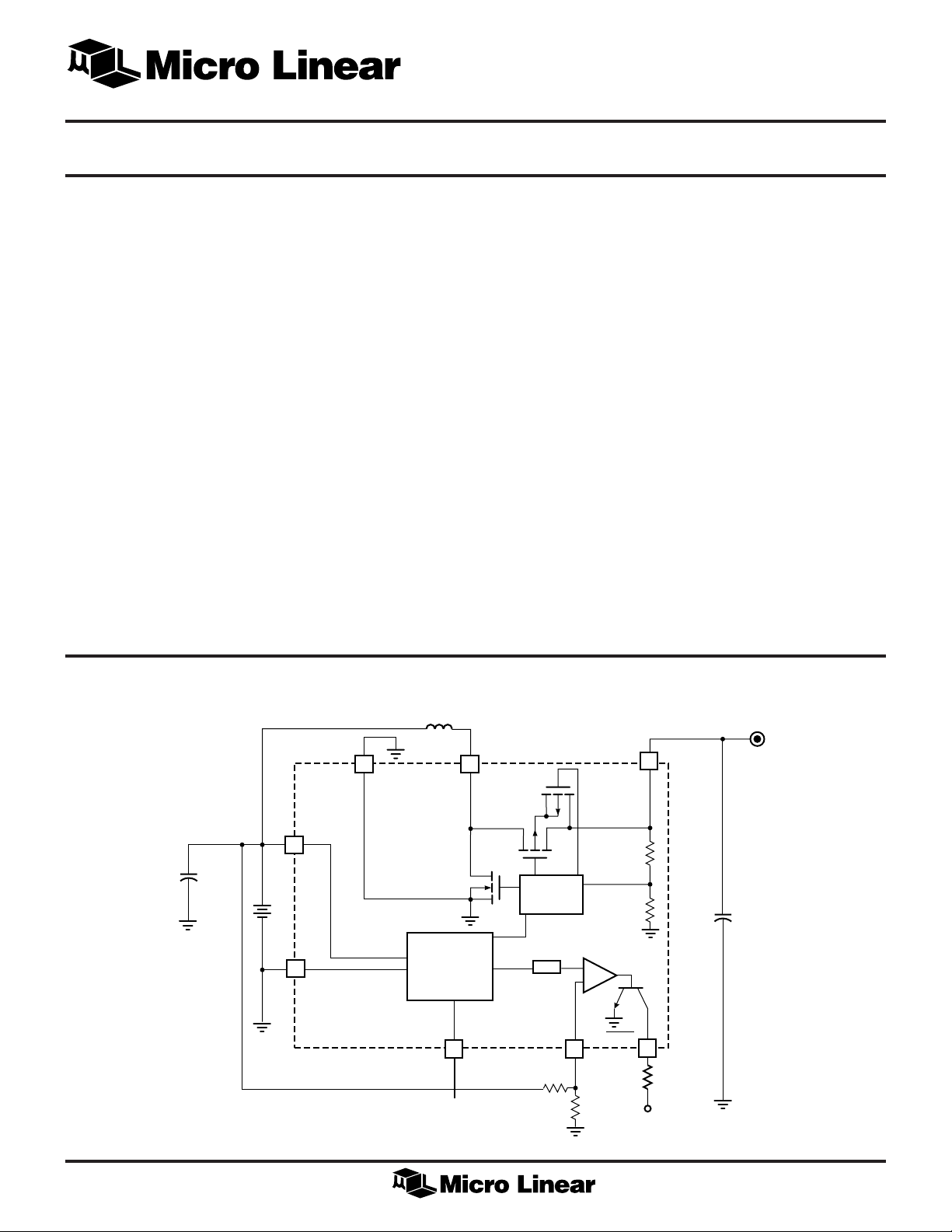

BLOCK DIAGRAM

*C

IN

*Optional

L1

V

C

OUT

OUT

8

PWR

GND

V

IN

1

V

BAT

GND

3

REGULATION

SHUTDOWN

FROM POWER

MANAGEMENT

V

L

&

CONTROL

SHDN

2

6

BOOST

CONTROL

REF

DETECT

FEEDBACK

+

–

4

*R

A

*R

B

V

RESET

5

OUT

7

5V

1

Page 2

ML4875

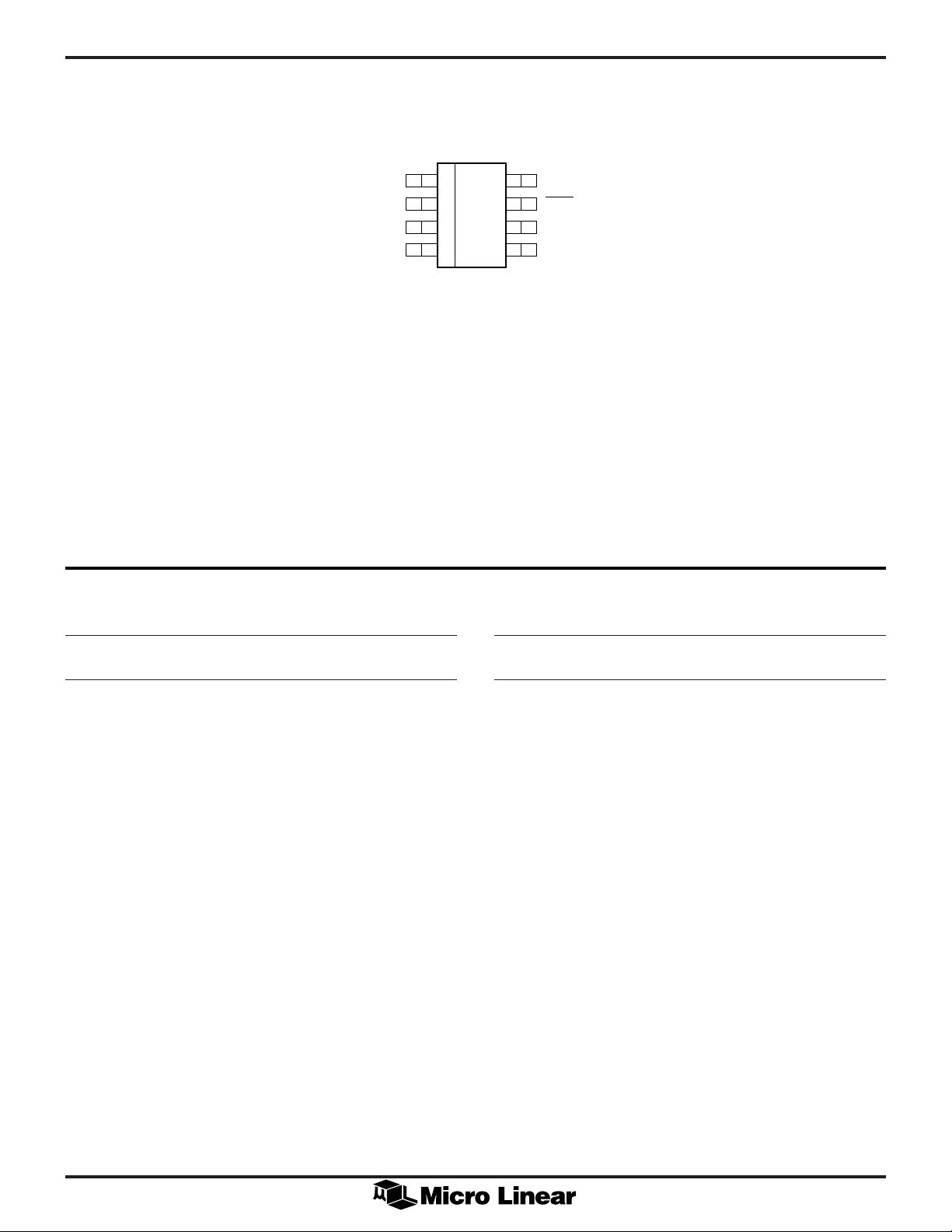

PIN CONNECTION

ML4875-5/-3/-T

8-Pin SOIC (S08)

PIN DESCRIPTION

V

SHDN

GND

DETECT

IN

1

2

3

4

TOP VIEW

8

7

6

5

PWR GND

RESET

V

L

V

OUT

PIN

NO. NAME FUNCTION

1V

IN

Battery input voltage

2 SHDN Pulling this pin high shuts down the

regulator, isolating the load from the

input

3 GND Analog signal ground

4 DETECT When this pin below V

REF

, causes

the RESET pin to go low

PIN

NO. NAME FUNCTION

5V

OUT

6V

L

Boost regulator output

Boost inductor connection

7 RESET Output goes low when regulation

cannot be achieved or when DETECT

goes below 200mV

8 PWR GND Return for the NMOS output transistor

2

Page 3

ML4875

ABSOLUTE MAXIMUM RATINGS

Lead Temperature (Soldering 10 sec.) ..................... 260°C

Thermal Resistance (qJA) Plastic SOIC ................. 160°C/W

Absolute maximum ratings are those values beyond which

the device could be permanently damaged. Absolute

maximum ratings are stress ratings only and functional

device operation is not implied.

V

................................................................................................ 7V

OUT

Voltage on any other pin ......GND – 0.3V to V

Peak Switch Current, I

Average Switch Current, I

................................................. 1.5A

(PEAK)

....................................... 300mA

(AVG)

OUT

+ 0.3V

Junction Temperature ............................................. 150°C

OPERATING CONDITIONS

Temperature Range

ML4875CS-X ..............................................0°C to 70°C

ML4875ES-X ........................................... –20°C to 70°C

V

Operating Range

IN

ML4875CS-X ................................. 1.0V to V

ML4875ES-X .................................. 1.1V to V

OUT

OUT

–0.2V

–0.2V

Storage Temperature Range ...................... –65°C to 150°C

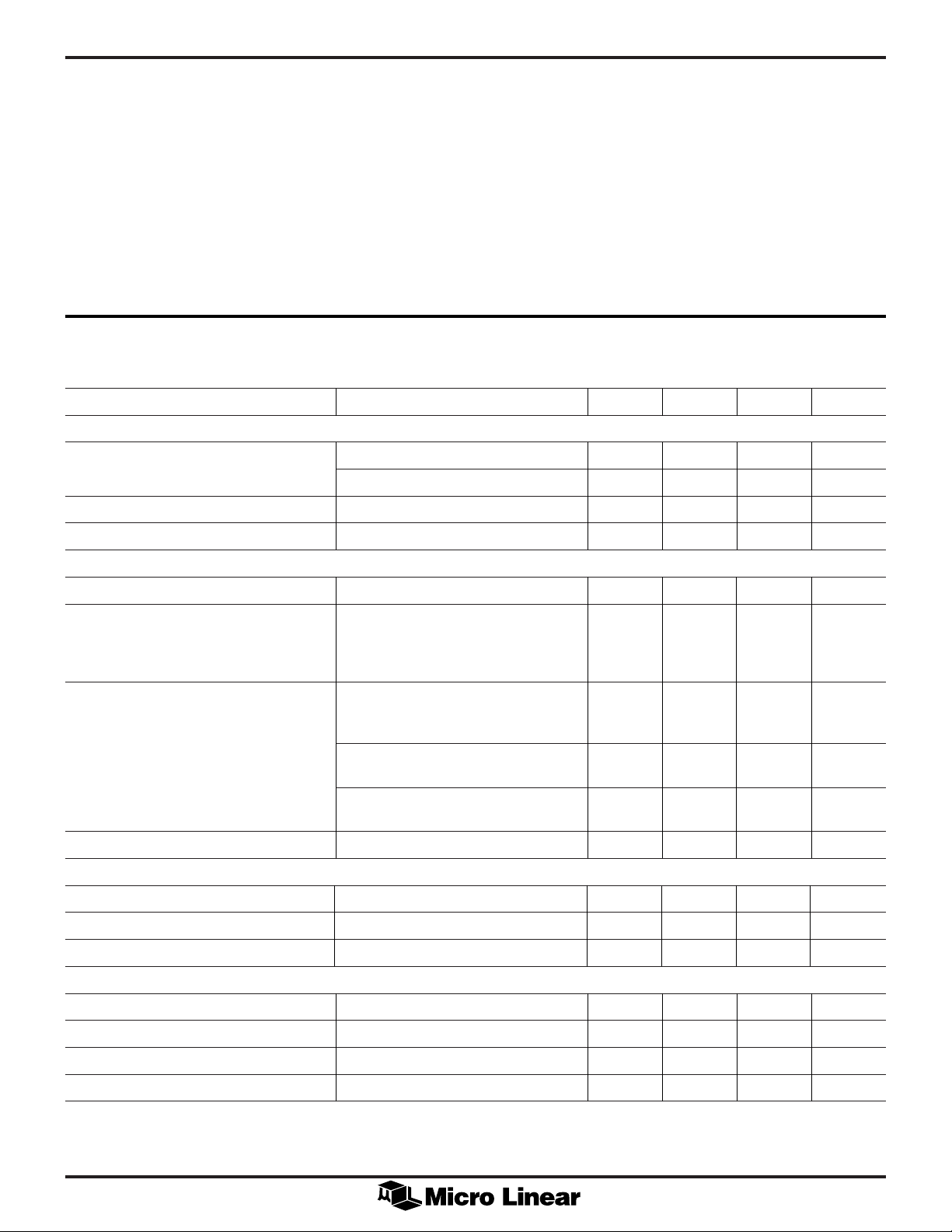

ELECTRICAL CHARACTERISTICS

Unless otherwise specified, V

PARAMETER CONDITIONS MIN TYP. MAX UNITS

SUPPLY

VIN Current VIN = V

V

Quiescent Current 812µA

OUT

V

Quiescent Current 1µA

L

PFM REGULATOR

= Operating Voltage Range, TA = Operating Temperature Range (Note 1).

IN

– 0.2V 50 65 µA

OUT

VIN = 4.8V, SHDN = V

IN

20 30 µA

Pulse Width (TON) 8.9 10 11.1 µs

Output Voltage (V

ML4875-5 T

ML4875-3 8.9µs - T

ML4875-T 2.91 3.0 3.09 V

Load Regulation See Figure 1

ML4875-5 V

ML4875-3 V

ML4875-T V

Under-Voltage Lockout Threshold 0.85 1 V

SHUTDOWN

Input Bias Current –100 100 nA

Shutdown Threshold V

Shutdown Hysteresis 50 70 mV

RESET COMPARATOR

DETECT Threshold 194 200 206 mV

DETECT Bias Current –100 100 nA

OUT

)

= 0 at V

ON

= 1.2V, I

IN

VIN = 2.4V, I

= 1.2V, I

IN

VIN = 2.4V, I

= 1.2V, I

IN

VIN = 2.4V, I

= high to low 180 200 220 mV

SHDN

(MAX), 4.85 5.0 5.15 V

OUT

- 11.1µs V

ON

OUT

OUT

OUT

OUT

OUT

OUT

- 20mA 4.85 5.0 5.15 V

- 100mA 4.85 5.0 5.15 V

- 30mA 3.2 3.3 3.4 V

- 140mA 3.2 3.3 3.4 V

- 35mA 2.91 3.0 3.09 V

- 160mA 2.91 3.0 3.09 V

(MIN) 3.2 3.3 3.4 V

OUT

RESET ON Voltage I

RESET OFF Current V

Note 1: Limits are guaranteed by 100% testing, sampling or correlation with worst case test conditions.

= 50µA 100 200 mV

RESET

= 5V 1 µA

RESET

3

Page 4

ML4875

27µH

V

IN

100µF

(Sumida CD75)

V

PWR GND

IN

SHDN

GND

DETECT

RESET

V

OUT

V

L

V

OUT

I

100µF

OUT

Figure 1. Application Test Circuit

R

Q

S

START-UP

V

IN

L1

Q3

6

V

L

Q2

+

A2

–

Q1

10µs

ONE SHOT

–

A1

+

200mV

Figure 2. PFM Regulator Block Diagram

SHUTDOWN

R1

R2

V

OUT

C1

V

+

OUT

–

5

4

Page 5

ML4875

FUNCTIONAL DESCRIPTION

The ML4875 combines Pulse Frequency Modulation

(PFM) and synchronous rectification to create a boost

converter that is both highly efficient and simple to use.

A PFM regulator charges a single inductor for a fixed

period of time and then completely discharges before

another cycle begins, simplifying the design by

eliminating the need for conventional current limiting

circuitry. Synchronous rectification is accomplished by

replacing an external Schottky diode with an on-chip

PMOS device, reducing switching losses and external

component count.

REGULATOR OPERATION

A block diagram of the boost converter is shown in Figure

2. The circuit remains idle when V

desired output voltage, drawing 50µA from VIN, and 8µA

from V

When V

through the feedback resistors R1 and R2.

OUT

drops below the desired output level, the

OUT

output of amplifier A1 goes high, signaling the regulator to

deliver charge to the output. Since the output of amplifier

A2 is normally high, the flip-flop captures the A1 set signal

and creates a pulse at the gate of the NMOS transistor Q1.

The NMOS transistor will charge the inductor L1 for 10µs,

resulting in a peak current given by:

TV

×

I

L PEAK

()

ON IN IN

=

L

11

For reliable operation, L1 should be chosen so that I

does not exceed 1.5A.

When the one-shot times out, the NMOS transistor

releases the VL pin, allowing the inductor to fly-back and

momentarily charge the output through the body diode of

PMOS transistor Q2 in series with shutdown transistor Q3.

But, as the voltage across the PMOS transistor changes

polarity, its gate will be driven low by the current sense

amplifier A2, causing Q2 to short out its body diode. The

inductor then discharges into the load through Q2. The

output of A2 also serves to reset the flip-flop and one-shot

in preparation for the next charging cycle. A2 releases the

gate of Q2 when its current falls to zero. If V

low, the flip-flop will immediately initiate another pulse.

The output capacitor (C1) filters the inductor current,

limiting output voltage ripple. Inductor current and oneshot waveforms are shown in Figure 3.

is at or above the

OUT

10µ

sV

≈

×

L

OUT

(1)

L(PEAK)

is still

SHUTDOWN

The ML4875 output can be shut down by pulling the

SHDN pin high. When SHDN is high, the regulator stops

switching, the control circuitry is powered down, and the

body diode of the PMOS synchronous rectifier is

disconnected from the output, allowing the output voltage

to drop below the input voltage. This feature is unique to

the ML4875, as most boost regulators use external

Schottky diode rectifier which cannot be disconnected

during shutdown. Leaving the Schottky diode connected

causes excess power dissipation in the load during

shutdown because the Schottky conducts whenever the

output voltage drops 300mV below the input voltage.

RESET COMPARATOR

An additional comparator is provided to detect low VIN,

or any other error condition that is important to the user.

The inverting input of the comparator is internally

connected to V

, while the non-inverting input is

REF

provided externally at the DETECT pin. The output of the

comparator is the RESET pin, which swings from V

OUT

to

GND when an error is detected.

DESIGN CONSIDERATIONS

INDUCTOR

Selecting the proper inductor for a specific application

usually involves a trade-off between efficiency and

maximum output current. Choosing too high a value will

keep the regulator from delivering the required output

current under worst case conditions. Choosing too low a

value causes efficiency to suffer. It is necessary to know

the maximum required output current and the input

voltage range to select the proper inductor value. The

maximum inductor value can be estimated using the

following formula:

2

IN MIN ON MIN

2

××

() ()

VI

××

OUT OUT MAX

L

VT

=

MAX

where h is the efficiency, typically between 0.8 and 0.9.

Note that this is the value of inductance that just barely

delivers the required output current under worst case

conditions. A lower value may be required to cover

inductor tolerance, the effect of lower peak inductor

currents caused by resistive losses, and minimum dead

time between pulses.

η

()

(2)

INDUCTOR

CURRENT

Q(ONE SHOT)

Q1 ON Q1 ON

Q1 & Q2 OFF

Q2

ON

Q2

ON

Figure 3. PFM Inductor Current Waveforms and Timing.

Another method of determining the appropriate inductor

value is to make an estimate based on the typical

performance curves given in Figures 4 and 5. Figure 4

shows maximum output current as a function of input

voltage for several inductor values. These are typical

performance curves and leave no margin for inductance

and ON-time variations. To accommodate worst case

conditions, it is necessary to derate these curves by at

least 10% in addition to inductor tolerance.

For example, a two cell to 5V application requires 80mA

of output current while using an inductor with 15%

tolerance. The output current should be derated by 25%

to 100mA to cover the combined inductor and ON-time

5

Page 6

ML4875

400

300

(mA)

200

OUT

I

100

0

ML4875-5.0

0

1.0 3.0

2.0

400

300

(mA)

200

OUT

I

100

0

ML4875-3.3

0

1.0 3.0

2.0

V

IN

L = 15µH

L = 27µH

L = 56µH

4.0 5.0

(V)

L = 15µH

L = 27µH

L = 56µH

4.0 5.0

(V)

V

IN

ML4875-3.0

400

300

(mA)

200

OUT

I

100

L = 15µH

L = 27µH

L = 56µH

0

0

1.0 3.0

Figure 4. Output Current vs Input Voltage.

tolerances. Assuming that 2V is the end of life voltage of a

two cell input, Figure 4 shows that with a 2V input, the

ML4875-5 delivers 99mA with a 27µH inductor.

Figure 5 shows efficiency under the conditions used to

create Figure 4. It can be seen that efficiency is mostly

independent of input voltage and is closely related to

inductor value. This illustrates the need to keep the

inductor value as high as possible to attain peak system

efficiency. As the inductor value goes down to 15µH, the

efficiency drops to between 70% and 75%. With 56µH,

the efficiency approaches 90% and there is little room for

improvement. At values greater than 100µH, the operation

of the synchronous rectifier becomes unreliable because

the inductor current is so small that it is difficult for the

control circuitry to detect. The data used to generate

Figures 4 and 5 is provided in Table 1.

After the appropriate inductor value is chosen, it is

necessary to find the minimum inductor current rating

required. Peak inductor current is determined from the

following formula:

I

L PEAK

()

TV

ON MAX IN MAX

=

×

() ()

L

MIN

(3)

2.0

(V)

V

IN

4.0

In the two cell application previously described, a

maximum input voltage of 3V would give a peak current

of 1.2A. When comparing various inductors, it is

important to keep in mind that suppliers use different

criteria to determine their ratings. Many use a

conservative current level, where inductance has dropped

to 90% of its normal level. In any case, it is a good idea to

try inductors of various current ratings with the ML4875 to

determine which inductor is the best choice. Check

efficiency and maximum output current, and if a current

probe is available, look at the inductor current to see if it

looks like the waveform shown in Figure 3. For additional

information, see Applications Note 29.

Suitable inductors can be purchased from the following

suppliers:

Coilcraft (708) 639-6400

Coiltronics (407) 241-7876

Dale (605) 665-9301

Sumida (708) 956-0666

6

Page 7

ML4875

ML4875-5.0

100

90

80

70

EFFICIENCY (%)

60

50

1.0 3.0 4.0

0

2.0

ML4875-3.3

100

L = 56µH

L = 27µH

L = 15µH

5.0

(V)

V

IN

90

80

70

EFFICIENCY (%)

60

50

1.0 3.0

0

L = 56µH

L = 27µH

L = 15µH

2.0

(V)

V

IN

ML4875-3.0

100

90

80

70

EFFICIENCY (%)

L = 56µH

L = 27µH

L = 15µH

60

50

1.0 3.0

0

Figure 5. Typical Efficiency as a Function of VIN.

OUTPUT CAPACITOR

The choice of output capacitor is also important, as it

controls the output ripple and optimizes the efficiency of

the circuit. Output ripple is influenced by three capacitor

parameters: capacitance, ESR, and ESL. The contribution

due to capacitance can be determined by looking at the

change in capacitor voltage required to store the energy

delivered by the inductor in a single charge-discharge

cycle, as determined by the following formula:

22

TV

×

∆V

OUT

=

ON IN

2( )

LC V V

×× × −

OUT IN

(4)

For a 2.4V input, and 5V output, a 27µH inductor, and a

47µF capacitor, the expected output ripple due to

capacitor value is 87mV.

Capacitor Equivalent Series Resistance (ESR) and

Equivalent Series Inductance (ESL), also contribute to the

output ripple due to the inductor discharge current

waveform. Just after the NMOS transistor turns off, the

2.0

(V)

V

IN

output current ramps quickly to match the peak inductor

current. This fast change in current through the output

capacitor’s ESL causes a high frequency (5ns) spike that

can be over 1V in magnitude. After the ESL spike settles,

the output voltage still has a ripple component equal to

the inductor discharge current times the ESR. This

component will have a sawtooth shape and a peak value

equal to the peak inductor current times the ESR. ESR also

has a negative effect on efficiency by contributing

I-squared R losses during the discharge cycle.

An output capacitor with a capacitance of 100µF, an ESR

of less than 0.1ý, and an ESL of less than 5nH is a good

general purpose choice. Tantalum capacitors which meet

these requirements can be obtained from the following

suppliers:

Matsuo (714) 969-2491

Sprague (603) 224-1961

If ESL spikes are causing output noise problems, an EMI

filter can be added in series with the output.

7

Page 8

ML4875

INPUT CAPACITOR

Unless the input source is a very low impedance battery,

it will be necessary to decouple the input with a capacitor

with a value of between 47µF and 100µF. This provides

the benefits of preventing input ripple from affecting the

ML4875 control circuitry, and it also improves efficiency

by reducing I-squared R losses during the charge and

discharge cycles of the inductor. Again, a low ESR

capacitor (such as tantalum) is recommended.

DRIVING THE SHDN INPUT

Unlike other boost regulators which use external Schottky

diodes, the ML4875 has the ability to isolate the load from

the battery input when the SHDN pin is high. Since there

may be no other voltage available when the regulator is in

shutdown, the SHDN input threshold is set well below the

minimum VIN voltage. SHDN can be driven directly from

an open collector device with a high value pull-up resistor

to VIN. If SHDN is driven from a TTL or CMOS output

device, a resistor divider should be used to prevent the

SHDN input high level from exceeding VIN, and to ensure

the SHDN input low level is below the 200mV threshold.

SETTING THE RESET THRESHOLD

To use the RESET comparator as an input voltage monitor,

it is necessary to use an external resistor divider tied to the

DETECT pin as shown in the block diagram. The resistor

values RA and RB can be calculated using the following

equation:

LAYOUT

Good PC board layout practices will ensure the proper

operation of the ML4875. Important layout considerations

include:

• Use adequate ground and power traces or planes

• Keep components as close as possible to the ML4875

• Use short trace lengths from the inductor to the VL pin

and from the output capacitor to the V

• Use a single point ground for the ML4875 ground pins,

and the input and output capacitors

OUT

pin

RR

()

+

V

IN MIN

The value of RB should be 100ký or less to minimize bias

current errors. RA is then found by rearranging the

equation:

RR

=×

()

AB

02

=× −

.

V

IN MIN

AB

R

B

()

.02

1

(5)

(6)

8

Page 9

TABLE 1. MAXIMUM OUTPUT CURRENT AND EFFICIENCY.

ML4875

ML4875-5.0

VIN (V) IIN (mA) I

L = 15µH

1.0 237.5 35.7 75.2

1.5 373.3 86.2 77.0

2.0 494.6 151.8 76.7

2.5 616.0 233.5 75.8

3.0 710.5 319.7 75.0

3.5 793.9 410.5 73.9

L = 27µH

1.0 138.2 22.0 79.6

1.5 220.7 54.8 82.8

2.0 296.2 98.8 83.4

2.5 374.1 156.1 83.5

3.0 441.6 220.7 83.3

3.5 496.4 289.4 83.3

4.0 538.2 358.5 83.3

4.5 542.6 408.0 83.5

L = 56µH

1.0 72.5 12.2 84.1

1.5 113.1 29.8 87.8

2.0 158.7 56.3 88.7

2.5 201.6 89.7 89.0

3.0 237.5 127.0 89.1

3.5 270.4 169.0 89.3

4.0 297.4 212.9 89.5

4.5 310.4 251.0 89.8

(mA) EFFICIENCY %

OUT

ML4875-3.0

VIN (V) IIN (mA) I

L = 15µH

1.0 242.8 59.2 73.1

1.5 362.6 131.3 72.4

2.0 461.6 219.2 71.2

2.5 523.5 308.5 70.7

L = 27µH

1.0 144.9 38.9 80.5

1.5 218.7 88.2 80.7

2.0 286.8 153.4 80.2

2.5 325.6 217.5 80.2

L = 56µH

1.0 74.3 21.5 86.8

1.5 119.1 52.0 87.3

2.0 154.9 90.2 87.3

2.5 183.0 133.2 87.3

(mA) EFFICIENCY %

OUT

ML4875-3.3

VIN (V) IIN (mA) I

L = 15µH

1.0 243.1 54.6 74.1

1.5 346.6 122.1 77.5

2.0 473.6 207.8 72.4

2.5 551.9 299.9 71.7

3.0 563.6 368.0 71.8

L = 27µH

1.0 144.5 35.4 80.8

1.5 218.4 80.9 81.5

2.0 292.3 143.6 81.1

2.5 345.7 211.8 80.9

3.0 357.2 263.7 81.2

L = 56µH

1.0 73.9 19.5 87.1

1.5 118.5 47.2 87.6

2.0 156.8 83.4 87.8

2.5 189.0 125.7 87.8

3.0 206.6 165.5 88.1

(mA) EFFICIENCY %

OUT

9

Page 10

ML4875

PHYSICAL DIMENSIONS inches (millimeters)

Package: S08

0.189 - 0.199

(4.80 - 5.06)

8

PIN 1 ID

1

0.017 - 0.027

(0.43 - 0.69)

(4 PLACES)

0.050 BSC

(1.27 BSC)

8-Pin SOIC

Package: S08

8-Pin SOIC

0.148 - 0.158

0.228 - 0.244

(3.76 - 4.01)

(5.79 - 6.20)

0.059 - 0.069

(1.49 - 1.75)

0º - 8º

ORDERING INFORMATION

PART NUMBER OUTPUT VOLTAGETEMPERATURE RANGE PACKAGE

ML4875CS-T (Obsolete) 3.0V0°C to 70°C8-Pin SOIC (S08)

ML4875CS-3 3.3V0°C to 70°C8-Pin SOIC (S08)

ML4875CS-5 5.0V0°C to 70°C8-Pin SOIC (S08)

ML4875ES-T 3.0V –20°C to 70°C 8-Pin SOIC (S08)

ML4875ES-3 (End Of Life) 3.3V –20°C to 70°C 8-Pin SOIC (S08)

ML4875ES-5 (End Of Life) 5.0V –20°C to 70°C 8-Pin SOIC (S08)

0.055 - 0.061

(1.40 - 1.55)

0.012 - 0.020

(0.30 - 0.51)

SEATING PLANE

0.004 - 0.010

(0.10 - 0.26)

0.015 - 0.035

(0.38 - 0.89)

0.006 - 0.010

(0.15 - 0.26)

© Micro Linear 1996 is a registered trademark of Micro Linear Corporation

Products described in this document may be covered by one or more of the following patents: 4,897,611; 4,964,026;

5,027,116;

5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940. Other patents are pending.

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or

design. Micro Linear does not assume any liability arising out of the application or use of any product

described herein, neither does it convey any license under its patent right nor the rights of others. The

circuits contained in this data sheet are offered as possible applications only. Micro Linear makes no

warranties or representations as to whether the illustrated circuits infringe any intellectual property rights of

others, and will accept no responsibility or liability for use of any application herein. The customer is urged

to consult with appropriate legal counsel before deciding on a particular application.

10

DS4875-01

2092 Concourse Drive

San Jose, CA 95131

Tel: 408/433-5200

Fax: 408/432-0295

7/16/96 Printed in U.S.A.

Loading...

Loading...