Page 1

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

8MB Synchronous Fast Static

Order this document

by MCM72F10/D

MCM72F10

RAM Module

The MCM72F10 (2MB) is configured as 1M x 72 bits. It is packaged in a

168–pin dual–in–line memory module DIMM. The module uses Motorola’s 3.3 V ,

256K x 18 bit flow–through BurstRAMs.

Address (A), data inputs (DQ, DP), and all control signals except output enable

) are clock (K) controlled through positive–edge–triggered noninverting

(G

registers.

Write cycles are internally self–timed and initiated by the rising edge of the

clock (K) input. This feature provides increased timing flexibility for incoming

signals. Synchronous byte write (W

both bytes.

• Single 3.3 V + 10%, – 5% Power Supply

• Plug and Pin Compatibility with 1MB, 2MB, and 4MB

• Multiple Clock Pins for Reduced Loading

• All Inputs and Outputs are L VTTL Compatible

• Byte Write Capability

• Fast SRAM Access Times: 8/9/12 ns

• High Quality Multi–Layer FR4 PWB With Separate Power and Ground

Planes

• Amp Connector, Part Number: 390064–4

• 168–Pin DIMM Module

) allows writes to either individual bytes or to

168–LEAD DIMM

CASE TBD

TOP VIEW

1

11

40

41

REV 1

11/26/97

Motorola, Inc. 1997

MOTOROLA FAST SRAM

84

MCM72F10

1

Page 2

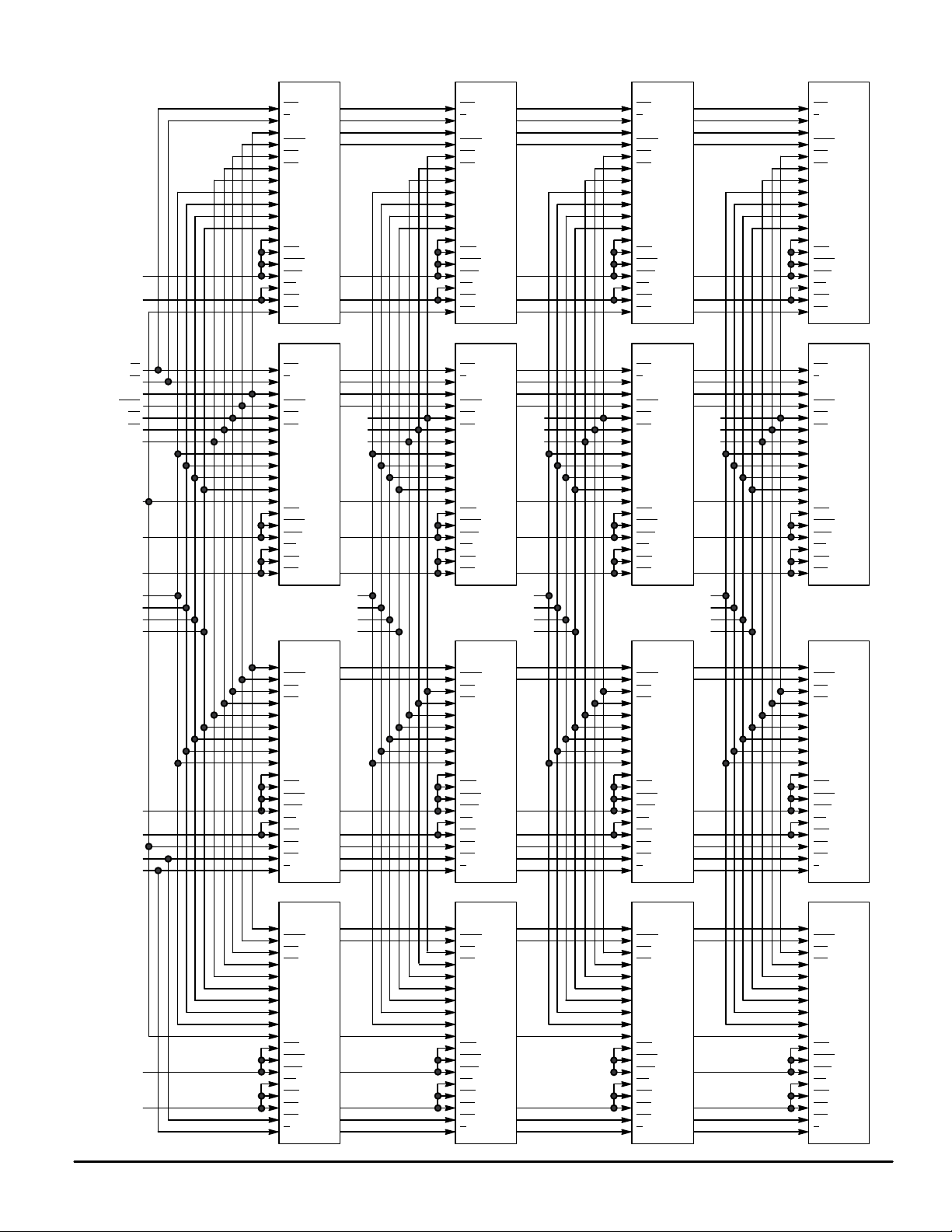

BLOCK DIAGRAM

256K x 18

SE1

G

A0 – A17

ADSC

SBa

SBb

K

DQa0 – DQa7

DQa8

DQb0 – DQb7

DQb8

SE2

ADV

V

DD

V

SS

ADSP

SGW

SW

LBO

SE3

256K x 18

SE1

G

A0 – A17

ADSC

SBa

SBb

K

DQa0 – DQa7

DQa8

DQb0 – DQb7

DQb8

SE2

ADV

ADSP

SGW

SW

LBO

SE3

256K x 18

SE1

G

A0 – A17

ADSC

SBa

SBb

K

DQa0 – DQa7

DQa8

DQb0 – DQb7

DQb8

SE2

ADV

ADSP

SGW

SW

LBO

SE3

256K x 18

SE1

G

A0 – A17

ADSC

SBa

SBb

K

DQa0 – DQa7

DQa8

DQb0 – DQb7

DQb8

SE2

ADV

ADSP

SGW

SW

LBO

SE3

E0

G0

A0 – A17

ADSP

W0

W1

KO

A18

V

DD

V

SS

DQ0 – DQ7

DP0

DQ8 – DQ15

DP1

V

DD

V

SS

E1

G1

256K x 18

SE1

G

A0 – A17

ADSC

SBa

SBb

K

DQa0 – DQa7

DQa8

DQb0 – DQb7

DQb8

SE2

ADV

ADSP

SGW

SW

LBO

SE3

DQ16 – DQ23

DQ24 – DQ31

256K x 18

A0 – A17

ADSC

SBa

SBb

K

DQb8

DQb0 – DQb7

DQa8

DQa0 – DQa7

SE2

ADV

ADSP

SGW

SW

LBO

SE3

SE1

G

DP2

DP3

W2

W3

256K x 18

SE1

G

A0 – A17

ADSC

SBa

K1

SBb

K

DQa0 – DQa7

DQa8

DQb0 – DQb7

DQb8

SE2

ADV

ADSP

SGW

SW

LBO

SE3

DQ32 – DQ39

DQ40 – DQ47

DP4

DP5

W4

W5

K2

256K x 18

SE1

G

A0 – A17

ADSC

SBa

SBb

K

DQa0 – DQa7

DQa8

DQb0 – DQb7

DQb8

SE2

ADV

ADSP

SGW

SW

LBO

SE3

DQ48 – DQ55

DQ56 – DQ63

DP6

DP7

W6

W7

256K x 18

SE1

G

A0 – A17

ADSC

SBa

K3

SBb

K

DQa0 – DQa7

DQa8

DQb0 – DQb7

DQb8

SE2

ADV

ADSP

SGW

SW

LBO

SE3

256K x 18 256K x 18 256K x 18

A0 – A17

ADSC

SBa

SBb

K

DQb8

DQb0 – DQb7

DQa8

DQa0 – DQa7

SE2

ADV

ADSP

SGW

SW

LBO

SE3

SE1

G

A0 – A17

ADSC

SBa

SBb

K

DQb8

DQb0 – DQb7

DQa8

DQa0 – DQa7

SE2

ADV

ADSP

SGW

SW

LBO

SE3

SE1

G

A0 – A17

ADSC

SBa

SBb

K

DQb8

DQb0 – DQb7

DQa8

DQa0 – DQa7

SE2

ADV

ADSP

SGW

SW

LBO

SE3

SE1

G

V

DD

V

SS

MCM72F10

2

256K x 18

A0 – A17

ADSC

SBa

SBb

K

DQb8

DQb0 – DQb7

DQa8

DQa0 – DQa7

SE2

ADV

ADSP

SGW

SW

LBO

SE3

SE1

G

256K x 18 256K x 18 256K x 18

A0 – A17

ADSC

SBa

SBb

K

DQb8

DQb0 – DQb7

DQa8

DQa0 – DQa7

SE2

ADV

ADSP

SGW

SW

LBO

SE3

SE1

G

A0 – A17

ADSC

SBa

SBb

K

DQb8

DQb0 – DQb7

DQa8

DQa0 – DQa7

SE2

ADV

ADSP

SGW

SW

LBO

SE3

SE1

G

A0 – A17

ADSC

SBa

SBb

K

DQb8

DQb0 – DQb7

DQa8

DQa0 – DQa7

SE2

ADV

ADSP

SGW

SW

LBO

SE3

SE1

G

MOTOROLA FAST SRAM

Page 3

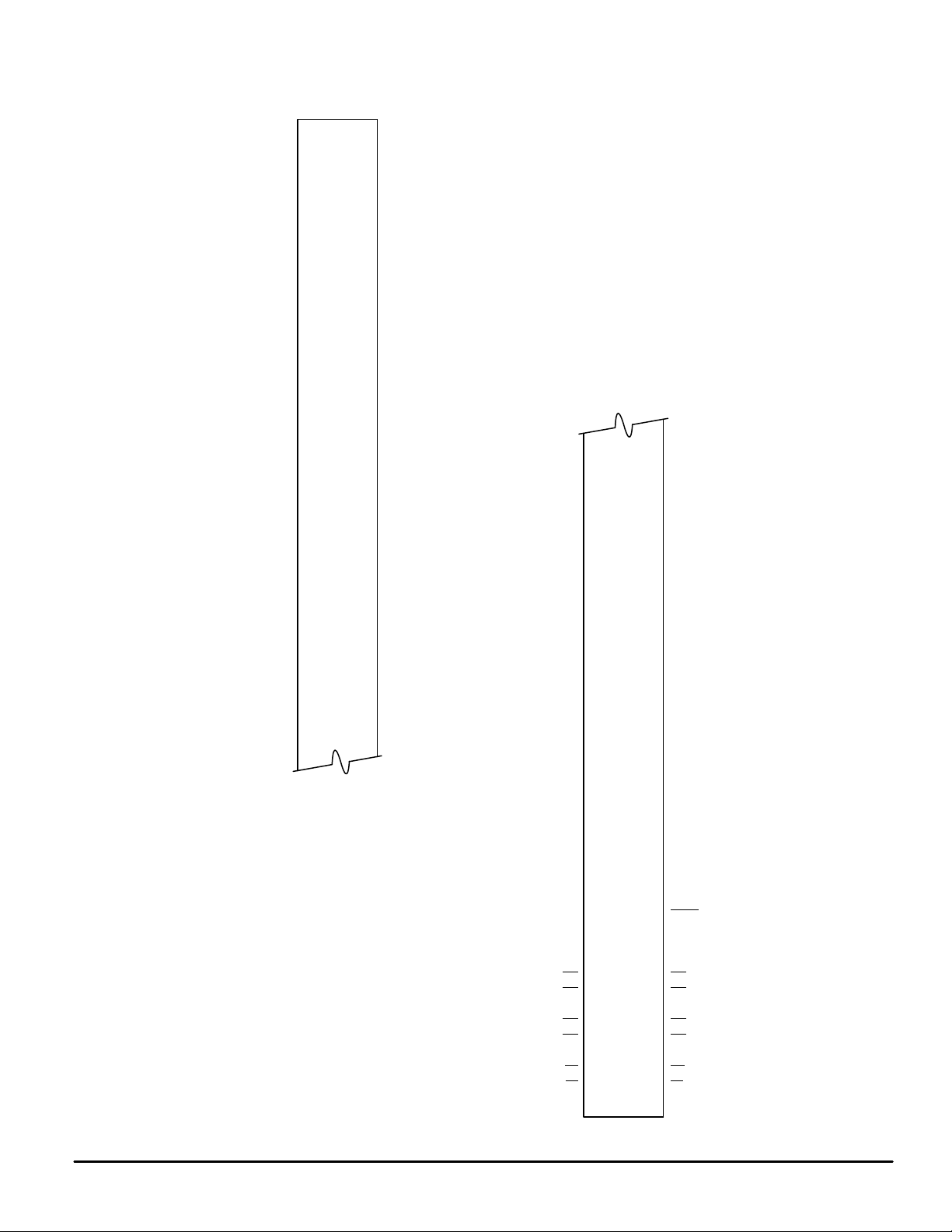

V

SS

DQ63

DQ62

V

DD

DQ60

DQ58

V

SS

DQ56

DQ55

V

SS

1

2

3

4

5

6

7

8

9

10

85

86

87

88

89

90

91

92

93

94

PIN ASSIGNMENT

168–LEAD DIMM

TOP VIEW

V

SS

DP7

DQ61

V

SS

DQ59

DQ57

V

SS

DP6

DQ54

V

DD

DQ53

DQ51

V

SS

DQ49

DP5

V

DD

DQ46

DQ44

V

SS

DQ42

DQ40

V

SS

DQ39

DQ37

V

SS

DQ35

DQ33

V

SS

K3

V

SS

DP3

DQ30

V

DD

DQ28

DQ26

V

SS

DQ24

DQ23

V

SS

DQ21

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

DQ52

DQ50

V

SS

DQ48

DQ47

V

SS

DQ45

DQ43

V

SS

DQ41

DP4

V

DD

DQ38

DQ36

V

SS

DQ34

DQ32

V

SS

K2

V

SS

DQ31

DQ29

V

SS

DQ27

DQ25

V

SS

DP2

DQ22

V

DD

DQ20

DQ19

V

SS

DQ17

DP1

V

DD

DQ14

DQ12

V

SS

DQ10

DQ8

V

SS

DQ7

DQ5

V

SS

DQ3

DQ1

V

DD

NC

A18

V

SS

A16

A14

V

SS

A12

A10

V

SS

A8

A6

V

DD

A4

A2

A0

V

SS

K1

V

SS

W7

W5

V

SS

W3

W1

V

SS

G1

E1

V

SS

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

DQ18

V

SS

DQ16

DQ15

V

SS

DQ13

DQ11

V

SS

DQ9

DP0

V

DD

DQ6

DQ4

V

SS

DQ2

DQ0

V

SS

NC

A17

V

SS

A15

A13

V

DD

A11

A9

V

SS

A7

A5

V

SS

A3

A1

ADSP

V

SS

K0

V

SS

W6

W4

V

SS

W2

W0

V

DD

G0

E0

V

SS

MOTOROLA FAST SRAM

MCM72F10

3

Page 4

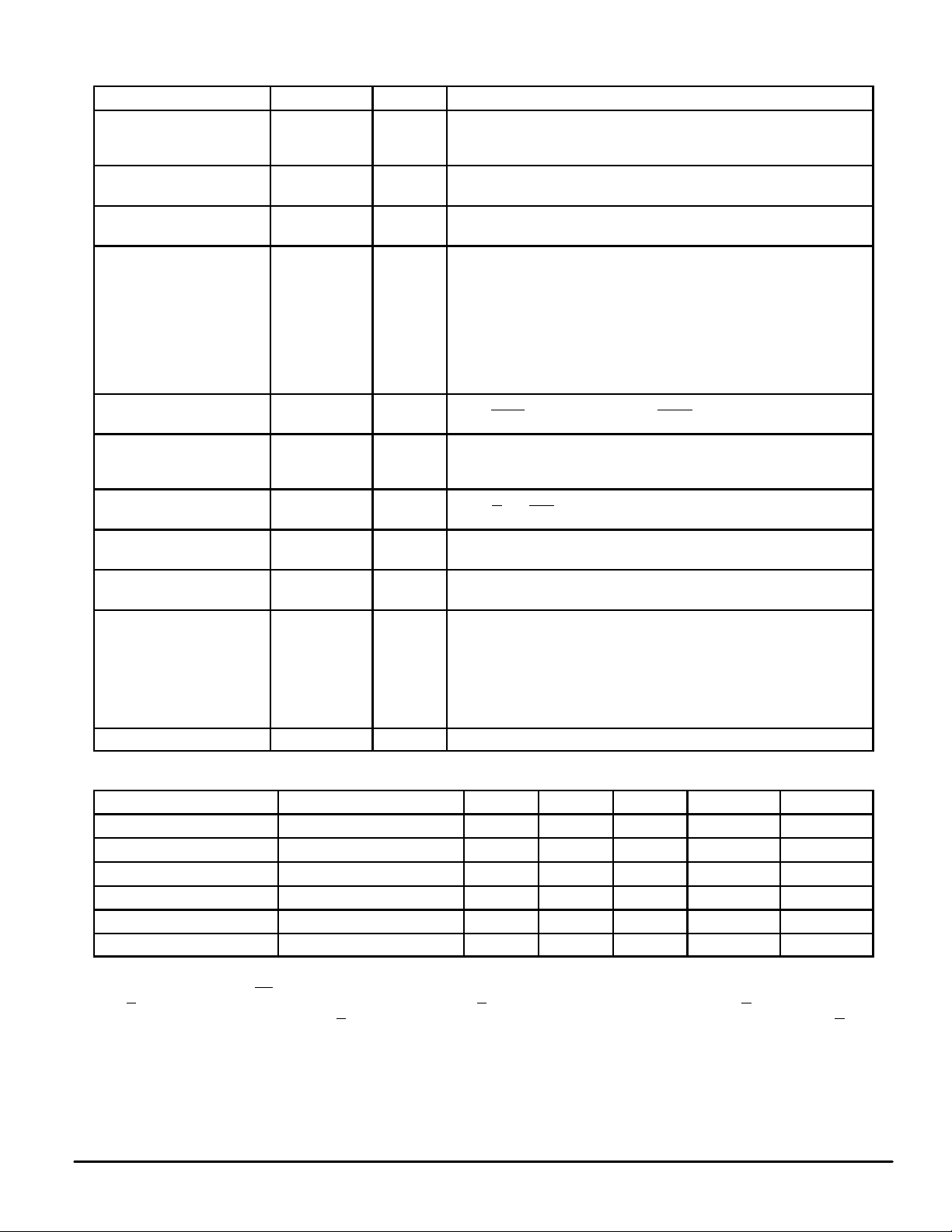

PIN DESCRIPTIONS

Pin Locations Symbol Type Description

59, 61, 62, 64, 65, 67, 68, 70,

71, 72, 143, 145, 146, 148,

149, 151, 152, 154, 155

156 ADSP Input Synchronous Addresss Status Controller: Initiates read, write, or chip

15, 31, 44, 86, 92, 105, 121,

134

2, 3, 5, 6, 8, 9, 11, 12, 14, 17,

18, 20, 21, 23, 24, 26, 27, 32,

34, 35, 37, 38, 40, 41, 43, 46,

47, 49, 50, 52, 53, 55, 56, 87,

89, 90, 93, 95, 96, 98, 99,

101, 102, 104, 107, 108, 110,

111, 115, 1 16, 118, 119, 122,

124, 125, 127, 128, 130, 131,

133, 136, 137, 139, 140

83, 167 E0, E1 Input Synchronous Chip Enable: Active low to enable chip. Negated high —

82, 166 G0, G1 Input Asynchronous Output Enable Input:

29, 74, 113, 158 K0 – K3 Input Clock: This signal registers the address, data in, and all control signals

76, 77, 79, 80, 160, 161, 163,

164

4, 16, 33, 45, 57, 69, 94, 106,

123, 135, 147, 165

1, 7, 10, 13, 19, 22, 25, 28,

30, 36, 39, 42, 48, 51, 54, 60,

63, 66, 73, 75, 78, 81, 84, 85,

88, 91, 97, 100, 103, 109,

112, 114, 117, 120, 126, 129,

132, 138, 141, 144, 150, 153,

157, 159, 162, 168

58, 142 NC No Connection: There is no connection to the chip.

A0 – A18 Input Synchronous Address Inputs: These inputs are registered and must meet

DP0 – DP7 Synchronous Parity Data Inputs/Outputs.

DQ0 – DQ63 I/O Synchronous Data Inputs/Outputs.

W0 – W7 Input Synchronous Byte Write Inputs: x refers to the byte being written (byte a,

V

DD

V

SS

Supply Power Supply: 3.3 V + 10%, – 5%. Must be connected on all modules.

Supply Ground.

setup and hold times.

deselect cycle.

blocks ADSP

Low — enables output buffer.

High — DQx pins are high impedance.

except G

b).

or deselects chip when ADSC is asserted.

and LBO.

DATA RAM MCM69F618A SYNCHRONOUS TRUTH TABLE (See Notes 1, 2, 3, and 4)

Next Cycle Address Used E ADSP G DQx WRITE

Deselect None 1 0 X High–Z X

Begin Read External Address 0 0 0 DQ Read

Read Current X 1 1 High–Z Read

Read Current X 1 0 DQ Read

Begin Write External 0 0 X High–Z Write

Write Current X 1 X High–Z Write

NOTES:

1. X = don’t care, 1 = logic high, 0 = logic low.

2. Write is defined as any Wx

3. G

is an asynchronous signal and is not sampled by the clock K. G drives the bus immediately (t

4. On write cycles that follow read cycles, G

also remain negated at the completion of the write cycle to ensure proper write data hold times.

low.

must be negated prior to the start of the write cycle to ensure proper write data setup times. G must

MCM72F10

4

) following G going low.

GLQX

MOTOROLA FAST SRAM

Page 5

ABSOLUTE MAXIMUM RATINGS (See Note 1)

Rating Symbol Value Unit

Power Supply Voltage V

Voltage Relative to VSS

(See Note 2)

Input Voltage Three State I/O

(See Note 2)

Output Current (per I/O) I

Power Dissipation P

Temperature Under Bias T

Storage Temperature T

NOTES:

1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are

exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended

periods of time could affect device reliability.

2. This is a steady–state DC parameter that is in effect after the power supply has

achieved its nominal operating level. Power sequencing can not be controlled and

is not allowed.

3. Power dissipation capability is dependent upon package characteristics and use

environment. See Package Thermal Characteristics.

DD

Vin, V

V

out

bias

stg

out

IT

D

– 0.5 to + 4.6 V

– 0.5 to VDD + 0.5 V

VSS – 0.5 to VDD + 0.5 V

± 20 mA

4.6 W

– 10 to + 85 °C

– 55 to + 125 °C

This device contains circuitry to protect the

inputs against damage due to high static voltages or electric fields; however, it is advised that

normal precautions be taken to avoid application

of any voltage higher than maximum rated voltages to this high–impedance circuit.

PACKAGE THERMAL CHARACTERISTICS — PBGA

Rating Symbol Max Unit Notes

Junction to Ambient (@ 200 lfm) Single Layer Board

Four Layer Board

Junction to Board (Bottom) R

Junction to Case (Top) R

NOTES:

1. Junction temperature is a function of on–chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient

temperature, air flow, board population, and board thermal resistance.

2. Per SEMI G38–87.

3. Indicates the average thermal resistance between the die and the printed circuit board.

4. Indicates the average thermal resistance between the die and the case top surface via the cold plate method (MIL SPEC–883 Method

1012.1).

R

θJA

θJB

θJC

41

19

11 °C/W 3

19 °C/W 4

°C/W 1, 2

MOTOROLA FAST SRAM

MCM72F10

5

Page 6

DC OPERA TING CONDITIONS AND CHARACTERISTICS

(3.6 V ≥ VDD ≥ 3.1 V, TJ = 20 to + 1 10 °C, Unless Otherwise Noted)

RECOMMENDED OPERATING CONDITIONS

Parameter

Supply Voltage (Operating Voltage Range) V

Input High Voltage V

Input Low Voltage V

*VIL ≥ – 2.0 V for t ≤ t

KHKH

/2.

VSS – 1.0 V

(Voltages Referenced to VSS = 0 V)

V

IH

V

SS

Symbol Min Typ Max Unit

DD

IH

IL

20% t

KHKH

(MIN)

Figure 1. Undershoot Voltage

DC CHARACTERISTICS

Parameter Symbol Min Max Unit

Input Leakage Current (0 V ≤ Vin ≤ VDD) I

Output Leakage Current (0 V ≤ Vin ≤ VDD) I

Output Low Voltage (IOL = + 8.0 mA) V

Output High Voltage (IOH = – 4.0 mA) V

3.135 3.3 3.6 V

1.7 — VDD + 0.3 V

– 0.3* — 0.7 V

lkg(I)

lkg(O)

OL

OH

— ± 1.0 µA

— ± 1.0 µA

— 0.4 V

2.4 — V

POWER SUPPLY CURRENTS

Parameter Symbol Min Max Unit

AC Supply Current (Device Selected, All Outputs Open, MCM72F10DG8

Cycle Time ≥ t

CMOS Standby Supply Current (Deselected, Clock (K) Cycle Time ≥ t

Clock Running Supply Current (Deselected, Clock (K) Cycle Time ≥ t

All Other Inputs Held to Static CMOS Levels Vin ≤ VSS + 0.2 V or ≥ VDD – 0.2 V)

CAPACITANCE (f = 1.0 MHz, dV = 3.0 V, T

Input Capacitance Address, ADSP

I/O Capacitance C

min) MCM72F10DG9

KHKH

= 20 to 110 °C, Periodically Sampled Rather Than 100% Tested)

J

Parameter Symbol Typ Max Unit

MCM72F10DG12

KHKH

KHKH

,

E, G

Other Inputs

I

DDA

I

SB1

I

SB2

C

in

I/O

— 3580

— 3040 mA

— 1360 mA

74

42

26

38 42 pF

3480

3380

90

50

30

MASS (Periodically Sampled Rather Than 100% Tested)

Parameter Max Unit

Mass 36 g

mA

pF

MCM72F10

6

MOTOROLA FAST SRAM

Page 7

AC OPERA TING CONDITIONS AND CHARACTERISTICS

(3.6 V ≥ VDD ≥ 3.1 V, TJ = 20 to + 1 10 °C, Unless Otherwise Noted)

Input Timing Measurement Reference Level 1.25 V. . . . . . . . . . . . . .

Input Pulse Levels 0 to 2.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input Slew Rate (See Notes 1 and 2) 1.0 V/ns. . . . . . . . . . . . . . . . . . .

Output Timing Reference Level 1.25 V. . . . . . . . . . . . . . . . . . . . . . . . .

Output Load See Figure 2 Unless Otherwise Noted. . . . . . . . . . . . . .

Output Rise/Fall Time 1.8 ns. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DATA RAMs READ/WRITE CYCLE TIMING (See Notes 1, 2, and 3)

MCM72F10–8 MCM72F10–9 MCM72F10–12

Parameter Symbol

Cycle Time t

Clock Access Time t

Output Enable to Output Valid t

Clock High to Output Active t

Clock High to Output Change t

Output Enable to Output Active t

Output Disable to Q High–Z t

Clock High to Q High–Z t

Clock High Pulse Width t

Clock Low Pulse Width t

Setup Times: Address

Hold Times: Address

ADSP

NOTES:

1. In setup and hold times, write refers to either any SBx

2. Chip enable is defined as SE1

3. All read and write cycle timings are referenced from K or G

4. Tested per AC Test Load (Figure 2).

5. Measured at ± 200 mV from steady state. Tested per High–Z Test Load (Figure 2).

6. This parameter is sampled and not 100% tested.

7. At any given voltage and temperature, t

ADSP

Data In

Write

Chip Enable

, ADSC, ADV

Data In

Write

Chip Enable

low, SE2 high, and SE3 low whenever ADSP or ADSC is asserted.

KHKH

KHQV

GLQV

KHQX1

KHQX2

GLQX

GHQZ

KHQZ

KHKL

KLKH

t

AVKH

t

ADKH

t

DVKH

t

WVKH

t

EVKH

t

KHAX

t

KHADX

t

KHDX

t

KHWX

t

KHEX

(Max) is less than t

KHQZ

Min Max Min Max Min Max

10 — 11 — 16.6 — ns

— 8 — 9 — 12 ns 4

— 3.5 — 3.5 — 5 ns 4

0 — 0 — 0 — ns 4, 5, 6, 7

2 — 2 — 2 — ns 4, 6

0 — 0 — 0 — ns 4, 5, 6

— 3.5 — 3.5 — 3.5 ns 4, 5, 6

2 3.5 2 3.5 2 3.5 ns 4, 5, 6, 7

4 — 4.5 — 5 — ns

4 — 4.5 — 5 — ns

2 — 2 — 2 — ns

0.5 — 0.5 — 0.5 — ns

and SW or SGW is low.

.

KHQX1

Unit Notes

(Min) for a given device and from device to device.

MOTOROLA FAST SRAM

OUTPUT

Z0 = 50

Ω

VL = 1.25 V

Figure 2. AC Test Load

RL = 50

Ω

MCM72F10

7

Page 8

OUTPUT LOAD

INPUT

WAVEFORM

OUTPUT

WAVEFORM

NOTES:

1. Input waveform has a slew rate of 1 V/ns.

2. Rise time is measured from 0.3 to 2.1 V unloaded.

3. Fall time is measured from 2.1 to 0.3 V unloaded.

Figure 3. Unloaded Rise and Fall Time Characterization

PULL–UP

VOLTAGE (V)

– 0.5

0

0.8

1.25

1.5

2.3

2.7

2.9

3.4

3.6 0 0

I (mA) MIN I (mA) MAX

– 38

– 38

– 38

– 26

– 20

0

0

0

0

OUTPUT

BUFFER

UNLOADED RISE AND FALL TIME MEASUREMENT

2.1 2.1

0.3 0.3

2.1

0.3 0.3

t

r

– 105

– 105

– 105

– 83

– 70

– 30

– 10

0

0

TEST POINT

3.6

2.9

2.5

2.3

2.1

1.25

VOLTAGE (V)

0.8

0

0 – 38 – 105

(a) Pull–Up

2.1

t

f

50 Ω LOAD

CURRENT (mA)

TEST POINT

VOLTAGE (V)

MCM72F10

8

PULL–DOWN

I (mA) MIN I (mA) MAX

– 0.5

0

0.4

0.8

1.25

1.6

2.8

3.2

3.4

3.6 46 120

0

0

10

20

31

40

40

40

40

V

DD

0

0

20

40

63

80

80

80

80

1.6

1.25

VOLTAGE (V)

0.3

0

040 80

(b) Pull–Down

Figure 4. Output Buffer Characteristics

TEST POINT

50 Ω LOAD

CURRENT (mA)

MOTOROLA FAST SRAM

Page 9

READ/WRITE CYCLES

K

Ax

ADSP

E

W

G

DQx

t

GHQZ

t

KLKH

t

GLQV

t

GLQX

WRITESREAD

t

KHKH

A

Q(n) Q(A) Q(B) Q(C) D(D) D(E) D(F) Q(G)

t

KHQZ

DESELECTED

B C D E F G

t

KHQV

t

KHQX1

t

KHKL

t

KHQX2

READ

Motorola Memory Prefix

Part Number

Full Part Numbers — MCM72F10DG8 MCM72F10DG9 MCM72F10DG12

ORDERING INFORMATION

(Order by Full Part Number)

MCM 72F X XX XX

Speed (8 = 8 ns, 9 = 9 ns, 12 = 12 ns)

Package (DG = Gold Pad DIMM)

Memory Size (10 = 8MB)

MOTOROLA FAST SRAM

MCM72F10

9

Page 10

P ACKAGE DIMENSIONS

DG PACKAGE

CASE TBD

MCM72F10

10

MOTOROLA FAST SRAM

Page 11

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty , representation or guarantee regarding

the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and

specifically disclaims any and all liability, including without limitation consequential or incidental damages. “T ypical” parameters which may be provided in Motorola

data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals”

must be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent rights nor the rights of

others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other

applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury

or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola

and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees

arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that

Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal

Opportunity/Affirmative Action Employer.

How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; JAP AN: Nippon Motorola Ltd.: SPD, Strategic Planning Office, 141,

P.O. Box 5405, Denver , Colorado, 80217. 1-303-675-2140 or 1-800-441-2447 4-32-1 Nishi-Gotanda, Shagawa-ku, Tokyo, Japan. 03-5487-8488

Mfax: RMFAX0@email.sps.mot.com – TOUCHTONE 1-602-244-6609 ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park,

Motorola Fax Back System – US & Canada ONLY 1-800-774-1848 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298

– http://sps.motorola.com/mfax/

HOME PAGE: http://motorola.com/sps/ CUSTOMER FOCUS CENTER: 1-800-521-6274

Mfax is a trademark of Motorola, Inc.

MOTOROLA FAST SRAM

◊

MCM72F10/D

MCM72F10

11

Loading...

Loading...