Datasheet MCM6264CJ35R2, MCM6264CP12, MCM6264CP15, MCM6264CJ35, MCM6264CJ15R2 Datasheet (Motorola)

...Page 1

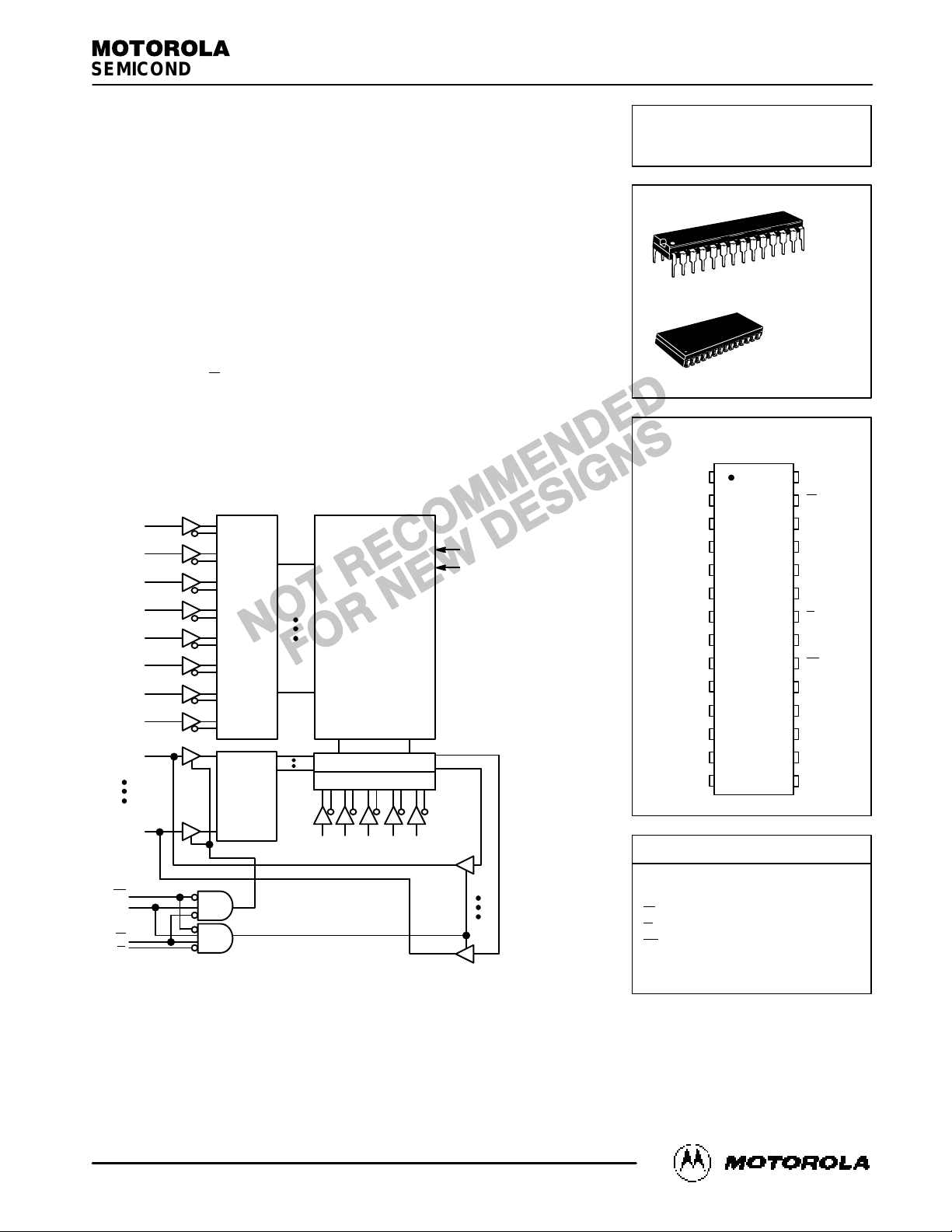

MCM6264C

1

MOTOROLA FAST SRAM

8K x 8 Bit Fast Static RAM

The MCM6264C is fabricated using Motorola’s high–performance silicon–gate

CMOS technology. Static design eliminates the need for external clocks or timing

strobes, while CMOS circuitry reduces power consumption and provides for

greater reliability.

This device meets JEDEC standards for functionality and pinout, and is available in plastic dual–in–line and plastic small–outline J–leaded packages.

• Single 5 V ± 10% Power Supply

• Fully Static — No Clock or Timing Strobes Necessary

• Fast Access Times: 12, 15, 20, 25, and 35 ns

• Equal Address and Chip Enable Access Times

• Output Enable (G

) Feature for Increased System Flexibility and to

Eliminate Bus Contention Problems

• Low Power Operation: 110 – 150 mA Maximum AC

• Fully TTL Compatible — Three State Output

ROW

DECODER

MEMORY MATRIX

256 ROWS x 32

x 9 COLUMNS

INPUT

DATA

CONTROL

COLUMN I/O

COLUMN DECODER

DQ0

E1

W

V

CC

V

SS

A1

DQ7

G

BLOCK DIAGRAM

E2

A0 A6 A10 A12

A11

A9

A8

A7

A5

A4

A3

A2

Order this document

by MCM6264C/D

PIN ASSIGNMENT

MCM6264C

P PACKAGE

300 MIL PLASTIC

CASE 710B–01

A0 – A12 Address Input. . . . . . . . . . . . .

DQ0 – DQ7 Data Input/Data Output. . .

W

Write Enable. . . . . . . . . . . . . . . . . . . .

G

Output Enable. . . . . . . . . . . . . . . . . . .

E1

, E2 Chip Enable. . . . . . . . . . . . . . . . .

V

CC

Power Supply (+ 5 V). . . . . . . . . . .

V

SS

Ground. . . . . . . . . . . . . . . . . . . . . . .

PIN NAMES

J PACKAGE

300 MIL SOJ

CASE 810B–03

5

4

3

2

1

10

9

8

7

6

11

12

13

14

20

21

22

23

24

25

26

19

27

28

18

17

16

15

A3

A6

A7

A12

NC

DQ0

A2

A5

V

SS

DQ2

DQ1

A4

A1

A0

A9

A8

E2

W

V

CC

DQ4

DQ5

DQ6

DQ3

E1

G

A11

DQ7

A10

REV 2

5/95

Motorola, Inc. 1995

Page 2

MCM6264C

2

MOTOROLA FAST SRAM

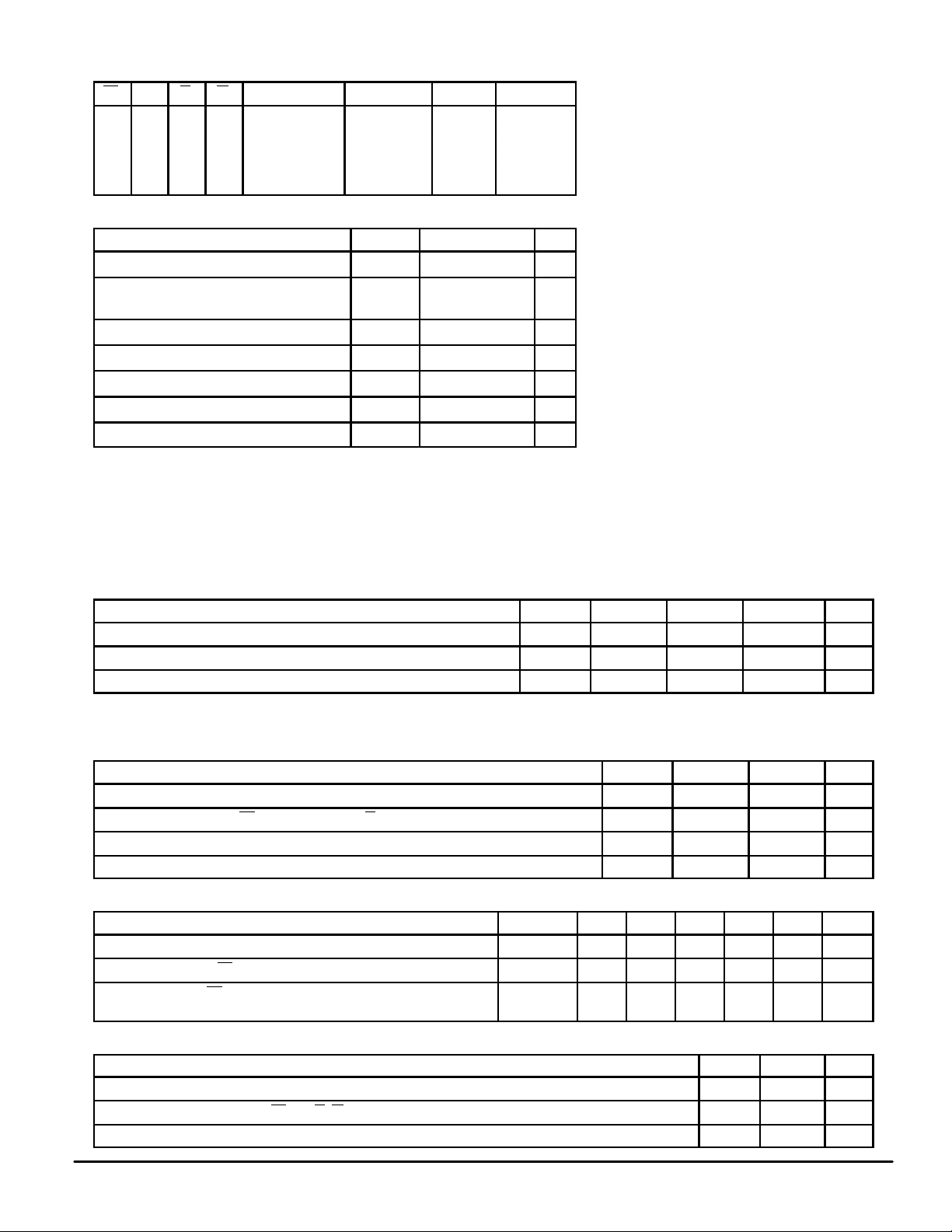

TRUTH TABLE (X = Don’t Care)

E1

E2 G W Mode VCC Current Output Cycle

H X X X Not Selected I

SB1

, I

SB2

High–Z —

X L X X Not Selected I

SB1

, I

SB2

High–Z —

L H H H Output Disabled I

CCA

High–Z —

L H L H Read I

CCA

D

out

Read Cycle

L H X L Write I

CCA

High–Z Write Cycle

ABSOLUTE MAXIMUM RATINGS (See Note)

Rating

Symbol Value Unit

Power Supply Voltage V

CC

– 0.5 to + 7.0 V

Voltage Relative to VSS for Any Pin

Except V

CC

Vin, V

out

– 0.5 to VCC + 0.5 V

Output Current I

out

± 20 mA

Power Dissipation P

D

1.0 W

Temperature Under Bias T

bias

– 10 to + 85 °C

Operating Temperature T

A

0 to + 70 °C

Storage Temperature — Plastic T

stg

– 55 to + 125 °C

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are

exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for

extended periods of time could affect device reliability.

DC OPERATING CONDITIONS AND CHARACTERISTICS

(VCC = 5.0 V ± 10%, TA = 0 to +70°C, Unless Otherwise Noted)

RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Min Typ Max Unit

Supply Voltage (Operating Voltage Range) V

CC

4.5 5.0 5.5 V

Input High Voltage V

IH

2.2 — VCC + 0.3** V

Input Low Voltage V

IL

– 0.5* — 0.8 V

*VIL (min) = – 0.5 V dc; VIL (min) = – 2.0 V ac (pulse width ≤ 20 ns)

**VIH (max) = VCC + 0.3 V dc; VIH (max) = VCC + 2 V ac (pulse width ≤ 20 ns)

DC CHARACTERISTICS

Parameter Symbol Min Max Unit

Input Leakage Current (All Inputs, Vin = 0 to VCC) I

lkg(I)

— ± 1 µA

Output Leakage Current (E1 = VIH, E2 = VIL, or G = VIH, V

out

= 0 to VCC) I

lkg(O)

— ± 1 µA

Output Low Voltage (IOL = 8.0 mA) V

OL

— 0.4 V

Output High Voltage (IOH = – 4.0 mA) V

OH

2.4 — V

POWER SUPPLY CURRENTS

Parameter Symbol – 12 – 15 – 20 – 25 – 35 Unit

AC Active Supply Current (I

out

= 0 mA, VCC = Max, f = f

max

) I

CCA

150 140 130 120 110 mA

AC Standby Current (E1 = VIH or E2 = V

IL, VCC

= Max, f = f

max

) I

SB1

45 40 35 30 30 mA

Standby Current (E1 ≥ VCC – 0.2 V or E2 ≤ VSS + 0.2 V,

Vin ≤ VSS + 0.2 V or ≥ VCC – 0.2 V)

I

SB2

20 20 20 20 20 mA

CAPACITANCE (f = 1 MHz, dV = 3 V, T

A

= 25°C, Periodically Sampled Rather Than 100% Tested)

Parameter

Symbol Max Unit

Address Input Capacitance C

in

6 pF

Control Pin Input Capacitance (E1, E2, G, W) C

in

6 pF

I/O Capacitance C

I/O

7 pF

device contains circuitry to protect the

inputs against damage due to high static voltages or electric fields; however, it is advised

that normal precautions be taken to avoid

application of any voltage higher than maximum rated voltages to these high–impedance

circuits.

This CMOS memory circuit has been designed to meet the dc and ac specifications

shown in the tables, after thermal equilibrium

has been established. The circuit is in a test

socket or mounted on a printed circuit board

and transverse air flow of at least 500 linear

feet per minute is maintained.

This

Page 3

MCM6264C

3

MOTOROLA FAST SRAM

AC OPERATING CONDITIONS AND CHARACTERISTICS

(VCC = 5.0 V ± 10%, TA = 0 to + 70°C, Unless Otherwise Noted)

Input Timing Measurement Reference Level 1.5 V. . . . . . . . . . . . . . .

Input Pulse Levels 0 to 3.0 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input Rise/Fall Time 5 ns. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output Timing Measurement Reference Level 1.5 V. . . . . . . . . . . . .

Output Load See Figure 1A Unless Otherwise Noted. . . . . . . . . . . .

READ CYCLE (See Notes 1 and 2)

– 12 – 15 – 20 – 25 – 35

Parameter Symbol Min Max Min Max Min Max Min Max Min Max Unit Notes

Read Cycle Time t

AVAV

12 — 15 — 20 — 25 — 35 — ns 3

Address Access Time t

AVQV

— 12 — 15 — 20 — 25 — 35 ns

Enable Access Time t

ELQV

— 12 — 15 — 20 — 25 — 35 ns 4

Output Enable Access Time t

GLQV

— 6 — 8 — 10 — 11 — 12 ns

Output Hold from Address Change t

AXQX

4 — 4 — 4 — 4 — 4 — ns

Enable Low to Output Active t

ELQX

4 — 4 — 4 — 4 — 4 — ns 5, 6 ,7

Enable High to Output High–Z t

EHQZ

0 6 0 8 0 9 0 10 0 11 ns 5, 6, 7

Output Enable Low to Output Active t

GLQX

0 — 0 — 0 — 0 — 0 — ns 5, 6, 7

Output Enable High to Output High–Z t

GHQZ

0 6 0 7 0 8 0 9 0 10 ns 5, 6, 7

Power Up Time t

ELICCH

0 — 0 — 0 — 0 — 0 — ns

Power Down Time t

EHICCL

— 12 — 15 — 20 — 25 — 35 ns

NOTES:

1. W

is high for read cycle.

2. E1

and E2 are represented by E in this data sheet. E2 is of opposite polarity to E.

3. All timings are referenced from the last valid address to the first transitioning address.

4. Addresses valid prior to or coincident with E

going low.

5. At any given voltage and temperature, t

EHQZ

(max) is less than t

ELQX

(min), and t

GHQZ

(max) is less than t

GLQX

(min), both for a given

device and from device to device.

6. Transition is measured ± 500 mV from steady–state voltage with load of Figure 1B.

7. This parameter is sampled and not 100% tested.

8. Device is continuously selected (E1

= VIL, E2 = VIH, G = VIL).

Z0 = 50

Ω

50

Ω

VL = 1.5 V

Figure 1A Figure 1B

5 pF

+ 5 V

OUTPUT

255

Ω

480

Ω

AC TEST LOADS

The table of timing values shows either

a minimum or a maximum limit for each parameter. Input requirements are specified

from the external system point of view.

Thus, address setup time is shown as a

minimum since the system must supply at

least that much time (even though most

devices do not require it). On the other

hand, responses from the memory are

specified from the device point of view.

Thus, the access time is shown as a maximum since the device never provides data

later than that time.

TIMING LIMITS

OUTPUT

Page 4

MCM6264C

4

MOTOROLA FAST SRAM

READ CYCLE 1 (See Note 8)

Q (DATA OUT)

A (ADDRESS)

DATA VALIDPREVIOUS DATA VALID

t

AVAV

t

AXQX

t

AVQV

READ CYCLE 2 (See Note 4)

I

SB

I

CC

t

EHQZ

t

EHICCL

DATA VALID

t

GHQZ

t

AVAV

t

ELQX

t

ELQV

E (CHIP ENABLE)

Q (DATA OUT)

A (ADDRESS)

t

ELICCH

t

AVQV

t

GLQX

t

GLQV

G (OUTPUT ENABLE)

V

CC

SUPPLY

CURRENT

HIGH–Z HIGH–Z

Page 5

MCM6264C

5

MOTOROLA FAST SRAM

WRITE CYCLE 1 (W Controlled, See Notes 1, 2, and 3)

– 12 – 15 – 20 – 25 – 35

Parameter Symbol Min Max Min Max Min Max Min Max Min Max Unit Notes

Write Cycle Time t

AVAV

12 — 15 — 20 — 25 — 35 — ns 4

Address Setup Time t

AVWL

0 — 0 — 0 — 0 — 0 — ns

Address Valid to End of Write t

AVWH

10 — 12 — 15 — 17 — 20 — ns

Write Pulse Width t

WLWH

,

t

WLEH

10 — 12 — 15 — 17 — 20 — ns

Write Pulse Width, G High t

WLWH

,

t

WLEH

8 — 10 — 12 — 15 — 17 — ns 5

Data Valid to End of Write t

DVWH

6 — 7 — 8 — 10 — 12 — ns

Data Hold Time t

WHDX

0 — 0 — 0 — 0 — 0 — ns

Write Low to Output High–Z t

WLQZ

0 6 0 7 0 8 0 10 0 12 ns 6, 7, 8

Write High to Output Active t

WHQX

4 — 4 — 4 — 4 — 4 — ns 6, 7, 8

Write Recovery Time t

WHAX

0 — 0 — 0 — 0 — 0 — ns

NOTES:

1. A write occurs during the overlap of E

low and W low.

2. E1

and E2 are represented by E in this data sheet. E2 is of opposite polarity to E.

3. If G

goes low coincident with or after W goes low, the output will remain in a high impedance state.

4. All timings are referenced from the last valid address to the first transitioning address.

5. If G

≥ VIH, the output will remain in a high impedance state.

6. At any given voltage and temperature, t

WLQZ

(max) is less than t

WHQX

(min), both for a given device and from device to device.

7. Transition is measured ±500 mV from steady–state voltage with load of Figure 1B.

8. This parameter is sampled and not 100% tested.

WRITE CYCLE 1 (W Controlled, See Notes 1, 2, and 3)

DATA VALID

t

DVWH

t

AVWL

t

AVWH

t

AVAV

t

WHAX

t

WLWH

t

WHDX

t

WLQZ

t

WHQX

HIGH–Z

HIGH–Z

A (ADDRESS)

W

(WRITE ENABLE)

E

(CHIP ENABLE)

Q (DATA OUT)

D (DATA IN)

t

WLEH

Page 6

MCM6264C

6

MOTOROLA FAST SRAM

WRITE CYCLE 2 (E Controlled, See Notes 1 and 2)

– 12 – 15 – 20 – 25 – 35

Parameter Symbol Min Max Min Max Min Max Min Max Min Max Unit Notes

Write Cycle Time t

AVAV

12 — 15 — 20 — 25 — 35 — ns 3

Address Setup Time t

AVEL

0 — 0 — 0 — 0 — 0 — ns

Address Valid to End of Write t

AVEH

12 — 12 — 15 — 20 — 25 — ns

Enable to End of Write t

ELEH

,

t

ELWH

10 — 10 — 12 — 15 — 25 — ns 4, 5

Write Pulse Width t

WLEH

10 — 12 — 15 — 17 — 20 — ns

Data Valid to End of Write t

DVEH

7 — 7 — 8 — 10 — 15 — ns

Data Hold Time t

EHDX

0 — 0 — 0 — 0 — 0 — ns

Write Recovery Time t

EHAX

0 — 0 — 0 — 0 — 0 — ns

NOTES:

1. A write occurs during the overlap of E

low and W low.

2. E1

and E2 are represented by E in this data sheet. E2 is of opposite polarity to E.

3. All timings are referenced from the last valid address to the first transitioning address.

4. If E

goes low coincident with or after W goes low, the output will remain in a high impedance state.

5. If E

goes high coincident with or before W goes high, the output will remain in a high impedance state.

WRITE CYCLE 2 (E Controlled, See Notes 1 and 2)

t

EHDX

t

DVEH

t

EHAX

t

ELEH

t

ELWH

t

WLEH

t

AVEL

t

AVEH

DATA VALID

t

AVAV

HIGH–Z

A (ADDRESS)

W

(WRITE ENABLE)

E

(CHIP ENABLE)

Q (DATA OUT)

D (DATA IN)

ORDERING INFORMATION

(Order by Full Part Number)

Motorola Memory Prefix

Part Number

Package (P = 300 mil Plastic, J = 300 mil SOJ)

Full Part Numbers — MCM6264CP12 MCM6264CJ12 MCM6264CJ12R2

MCM6264CP15 MCM6264CJ15 MCM6264CJ15R2

MCM6264CP20 MCM6264CJ20 MCM6264CJ20R2

MCM6264CP25 MCM6264CJ25 MCM6264CJ25R2

MCM6264CP35 MCM6264CJ35 MCM6264CJ35R2

Shipping Method (R2 = Tape and Reel, Blank = Rails)

Speed (12 = 12 ns, 15 = 15 ns, 20 = 20 ns,

25 = 25 ns, 35 = 35 ns)

MCM 6264C X XX XX

Page 7

MCM6264C

7

MOTOROLA FAST SRAM

PACKAGE DIMENSIONS

28 LEAD

300 MIL PDIP

CASE 710B–01

MIN MINMAX MAX

MILLIMETERS INCHES

DIM

A

B

C

D

E

F

G

J

K

L

M

N

34.55

7.12

3.81

0.39

1.15

0.21

3.18

0

°

0.51

34.79

7.62

4.57

0.53

1.39

0.30

3.42

15

°

1.01

1.360

0.280

0.150

0.015

0.045

0.008

0.125

0

°

0.020

1.370

0.300

0.180

0.021

0.055

0.012

0.135

15

°

0.040

1.27 BSC

2.54 BSC

7.62 BSC

0.050 BSC

0.100 BSC

0.300 BSC

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEAD WHEN

FORMED PARALLEL.

4. DIMENSION A AND B DOES NOT INCLUDE MOLD

FLASH. MAXIMUM MOLD FLASH 0.25 (0.010).

28

1

15

14

-B-

-A-

K

L

M

C

N

E

F

D

28 PL

G

J

28 PL

-T-

SEATING

PLANE

0.25 (0.010)MTSB

0.25 (0.010)MTSA

28 LEAD

300 MIL SOJ

CASE 810B–03

MIN MINMAX MAX

MILLIMETERS INCHES

DIM

A

B

C

D

E

F

G

H

K

L

M

N

P

R

S

0

°

10

°

1.27 BSC

0.64 BSC

0.050 BSC

0.025 BSC

0°

10

°

18.29

7.50

3.26

0.39

2.24

0.67

—

0.89

0.76

8.38

6.60

0.77

18.54

7.74

3.75

0.50

2.48

0.81

0.50

1.14

1.14

8.64

6.86

1.01

0.720

0.295

0.128

0.015

0.088

0.026

—

0.035

0.030

0.330

0.260

0.030

0.730

0.305

0.148

0.020

0.098

0.032

0.020

0.045

0.045

0.340

0.270

0.040

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. DIMENSION A & B DO NOT INCLUDE MOLD

PROTRUSION. MOLD PROTRUSION SHALL NOT

EXCEED 0.15 (0.006) PER SIDE.

3. CONTROLLING DIMENSION: INCH.

4. DIM R TO BE DETERMINED AT DATUM -T-.

5. 810B-01 AND -02 OBSOLETE, NEW STANDARD

810B-03.

28

1

15

14

L

G

M

K

DETAIL Z

DETAIL Z

S RAD

F

-B-

-AP

R

N

0.10 (0.004)

SEATING PLANE

-T-

0.25 (0.010) TSB

0.18 (0.007)MTSA

0.18 (0.007) TSB

S

S

M

C

E

D

24 PL

H BRK

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty , representation or guarantee regarding

the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit,

and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “T ypical” parameters can and do vary in different

applications. All operating parameters, including “T ypicals” must be validated for each customer application by customer’s technical experts. Motorola does

not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in

systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of

the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such

unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless

against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Af firmative Action Employer.

Page 8

MCM6264C

8

MOTOROLA FAST SRAM

Literature Distribution Centers:

USA/EUROPE: Motorola Literature Distribution; P .O. Box 20912; Phoenix, Arizona 85036.

JAPAN: Nippon Motorola Ltd.; 4–32–1, Nishi–Gotanda, Shinagawa–ku, Tokyo 141, Japan.

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

MCM6264C/D

*MCM6264C/D*

◊

CODELINE TO BE PLACED HERE

Loading...

Loading...