Page 1

SEMICONDUCTOR TECHNICAL DATA

3–1

REV 6

Motorola, Inc. 1995

10/95

High–Performance Silicon–Gate CMOS

The MC574HC4046A is similar in function to the MC14046 Metal gate

CMOS device. The device inputs are compatible with standard CMOS

outputs; with pullup resistors, they are compatible with LSTTL outputs.

The HC4046A phase–locked loop contains three phase comparators, a

voltage–controlled oscillator (VCO) and unity gain op–amp DEM

OUT

. The

comparators have two common signal inputs, COMPIN, and SIGIN. Input

SIGIN and COMPIN can be used directly coupled to large voltage signals, or

indirectly coupled (with a series capacitor to small voltage signals). The

self–bias circuit adjusts small voltage signals in the linear region of the

amplifier. Phase comparator 1 (an exclusive OR gate) provides a digital error

signal PC1

OUT

and m aintains 90 d egrees phase shift at the center

frequency between SIGIN and COMPIN signals (both at 50% duty cycle).

Phase comparator 2 (with leading–edge sensing logic) provides digital error

signals P C2

OUT

and P CP

OUT

and maintains a 0 degree phase shift

between SIGIN and COMPIN signals (duty cycle is immaterial). The linear

VCO produces an output signal VCO

OUT

whose frequency is determined by

the voltage of input VCOIN signal and the capacitor and resistors connected

to pins C1A, C1B, R1 and R2. The unity gain op–amp output DEM

OUT

with

an external resistor is used where the VCOIN signal is needed but no loading

can be tolerated. The inhibit input, when high, disables the VCO and all

op–amps to minimize standby power consumption.

Applications include FM and FSK modulation and demodulation, frequency synthesis and multiplication, frequency discrimination, tone decoding,

data synchronization and conditioning, voltage–to–frequency conversion

and motor speed control.

• Output Drive Capability: 10 LSTTL Loads

• Low Power Consumption Characteristic of CMOS Devices

• Operating Speeds Similar to LSTTL

• Wide Operating Voltage Range: 3.0 to 6.0 V

• Low Input Current: 1.0

µA Maximum (except SIG

IN

and COMPIN)

• In Compliance with the Requirements Defined by JEDEC Standard

No. 7A

• Low Quiescent Current: 80 µA Maximum (VCO disabled)

• High Noise Immunity Characteristic of CMOS Devices

• Diode Protection on all Inputs

• Chip Complexity: 279 FETs or 70 Equivalent Gates

Pin No. Symbol Name and Function

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

PCP

OUT

PC1

OUT

COMP

IN

VCO

OUT

INH

C1A

C1B

GND

VCO

IN

DEM

OUT

R1

R2

PC2

OUT

SIG

IN

PC3

OUT

V

CC

Phase Comparator Pulse Output

Phase Comparator 1 Output

Comparator Input

VCO Output

Inhibit Input

Capacitor C1 Connection A

Capacitor C1 Connection B

Ground (0 V) V

SS

VCO Input

Demodulator Output

Resistor R1 Connection

Resistor R2 Connection

Phase Comparator 2 Output

Signal Input

Phase Comparator 3 Output

Positive Supply Voltage

PIN ASSIGNMENT

D SUFFIX

SOIC PACKAGE

CASE 751B–05

N SUFFIX

PLASTIC PACKAGE

CASE 648–08

1

16

1

16

ORDERING INFORMATION

MC74HCXXXXAN

MC74HCXXXXAD

Plastic

SOIC

13

14

15

16

9

10

11

125

4

3

2

1

8

7

6

R2

PC2

out

SIG

in

PC3

out

V

CC

VCO

in

DEM

out

R1

VCO

out

COMP

in

PC1

out

PCP

out

GND

C1B

C1A

INH

Page 2

MC74HC4046A

MOTOROLA High–Speed CMOS Logic Data

DL129 — Rev 6

3–2

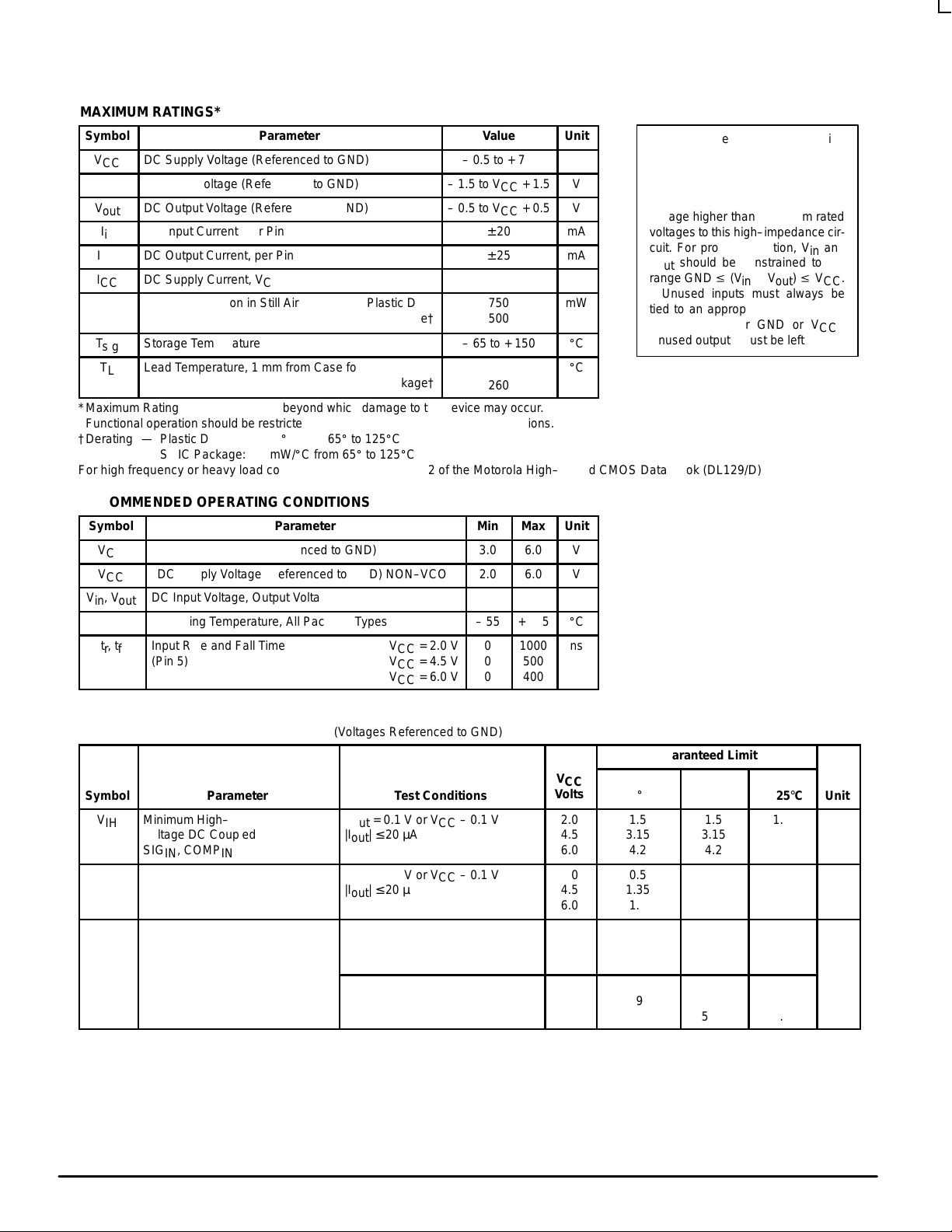

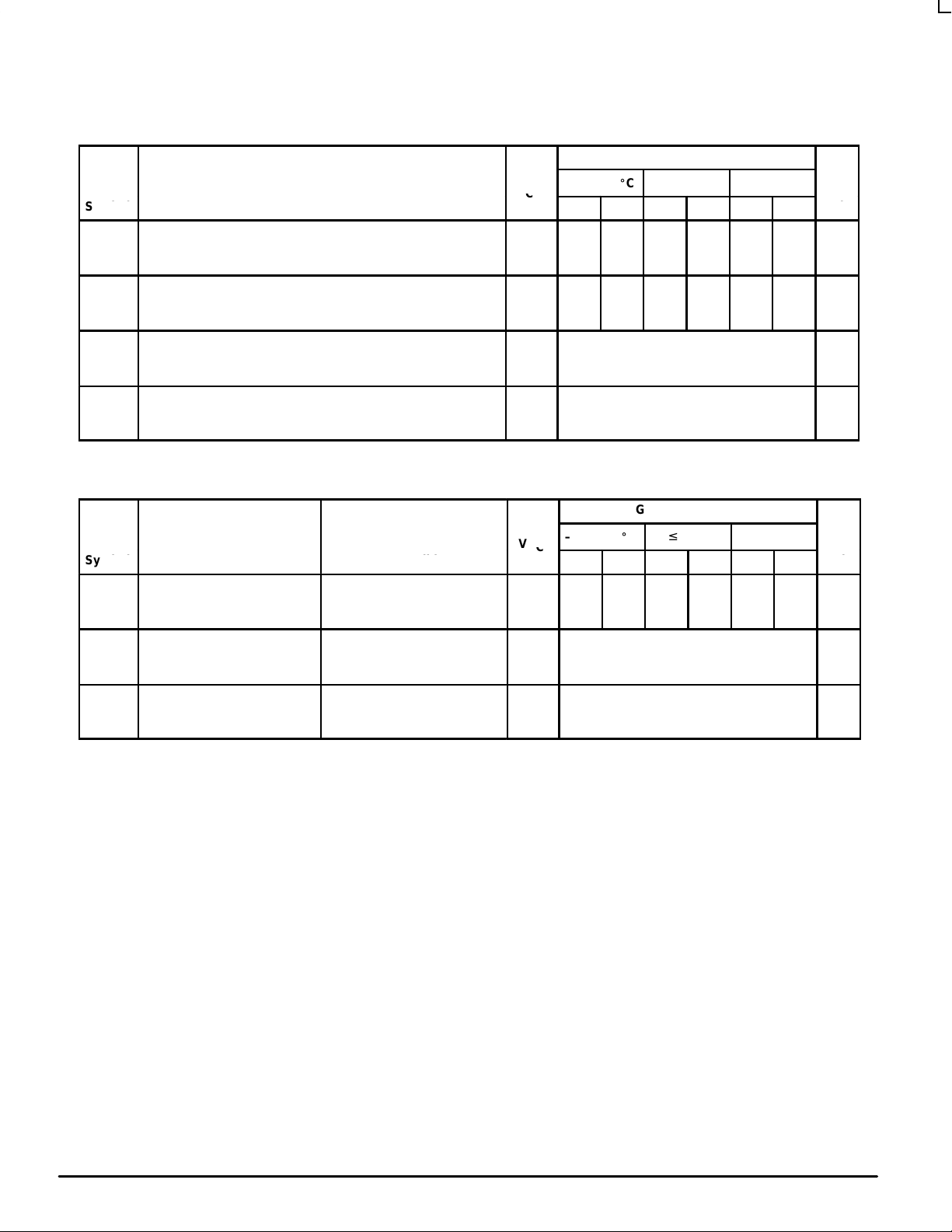

MAXIMUM RATINGS*

Symbol

Parameter

Value

Unit

V

CC

DC Supply Voltage (Referenced to GND)

– 0.5 to + 7.0

V

V

in

DC Input Voltage (Referenced to GND)

– 1.5 to VCC + 1.5

V

V

out

DC Output Voltage (Referenced to GND)

– 0.5 to VCC + 0.5

V

I

in

DC Input Current, per Pin

± 20

mA

I

out

DC Output Current, per Pin

± 25

mA

I

CC

DC Supply Current, VCC and GND Pins

± 50

mA

P

D

Power Dissipation in Still Air Plastic DIP†

SOIC Package†

750

500

mW

T

stg

Storage Temperature

– 65 to + 150

_

C

T

L

Lead Temperature, 1 mm from Case for 10 Seconds

Plastic DIP and SOIC Package†

260

_

C

*Maximum Ratings are those values beyond which damage to the device may occur.

Functional operation should be restricted to the Recommended Operating Conditions.

†Derating — Plastic DIP: – 10 mW/_C from 65_ to 125_C

SOIC Package: – 7 mW/_C from 65_ to 125_C

For high frequency or heavy load considerations, see Chapter 2 of the Motorola High–Speed CMOS Data Book (DL129/D).

RECOMMENDED OPERATING CONDITIONS

Symbol

Parameter

Min

Max

Unit

V

CC

DC Supply Voltage (Referenced to GND)

3.0

6.0

V

V

CC

DC Supply Voltage (Referenced to GND) NON–VCO 2.0 6.0 V

Vin, V

out

DC Input Voltage, Output Voltage (Referenced to GND)

0

V

CC

V

T

A

Operating Temperature, All Package Types

– 55

+ 125

_

C

tr, t

f

Input Rise and Fall Time VCC = 2.0 V

(Pin 5) VCC = 4.5 V

VCC = 6.0 V

0

0

0

1000

500

400

ns

[Phase Comparator Section]

DC ELECTRICAL CHARACTERISTICS

(Voltages Referenced to GND)

Guaranteed Limit

Symbol

Parameter

Test Conditions

V

CC

Volts

– 55 to

25_C

≤ 85°C

≤ 125°C

Unit

V

IH

Minimum High–Level Input

Voltage DC Coupled

SIGIN, COMP

IN

V

out

= 0.1 V or VCC – 0.1 V

|I

out

| ≤ 20 µA

2.0

4.5

6.0

1.5

3.15

4.2

1.5

3.15

4.2

1.5

3.15

4.2

V

V

IL

Maximum Low–Level Input

Voltage DC Coupled

SIGIN, COMP

IN

V

out

= 0.1 V or VCC – 0.1 V

|I

out

| ≤ 20 µA

2.0

4.5

6.0

0.5

1.35

1.8

0.5

1.35

1.8

0.5

1.35

1.8

V

V

OH

Minimum High–Level

Output Voltage

PCP

OUT

, PCn

OUT

Vin = VIH or V

IL

|I

out

| ≤ 20 µA

2.0

4.5

6.0

1.9

4.4

5.9

1.9

4.4

5.9

1.9

4.4

5.9

V

Vin = VIH or V

IL

|I

out

| ≤ 4.0 mA

|I

out

| ≤ 5.2 mA

4.5

6.0

3.98

5.48

3.84

5.34

3.7

5.2

(continued)

This device contains protection

circuitry to guard against damage

due to high static voltages or electric

fields. However, precautions must

be taken to avoid applications of any

voltage higher than maximum rated

voltages to this high–impedance circuit. For proper operation, Vin and

V

out

should be constrained to the

range GND v (Vin or V

out

) v VCC.

Unused inputs must always be

tied to an appropriate logic voltage

level (e.g., either GND or VCC).

Unused outputs must be left open.

Page 3

MC74HC4046A

High–Speed CMOS Logic Data

DL129 — Rev 6

3–3 MOTOROLA

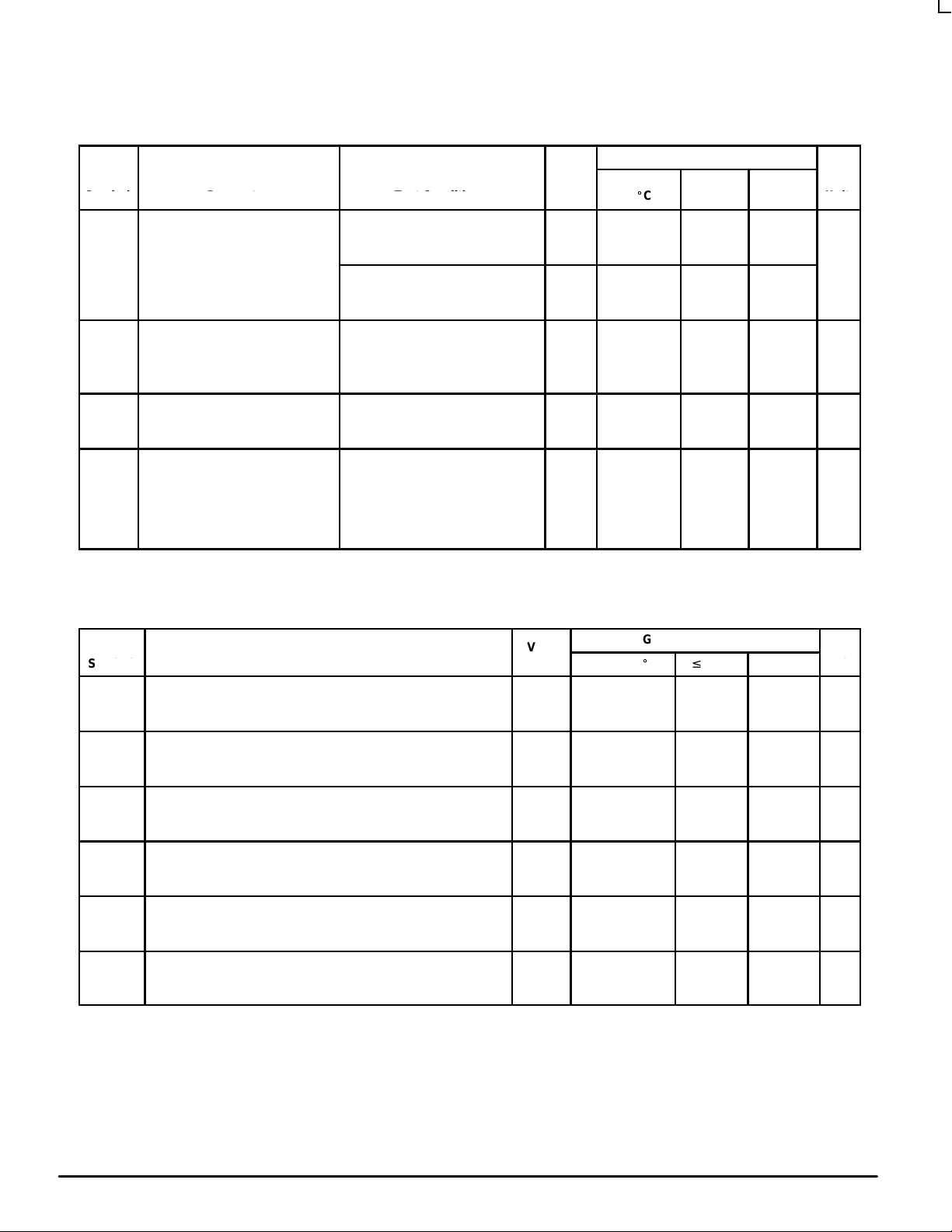

[Phase Comparator Section]

DC ELECTRICAL CHARACTERISTICS – continued

(Voltages Referenced to GND)

Guaranteed Limit

Symbol

Parameter

Test Conditions

V

CC

Volts

– 55 to

25_C

≤ 85°C

≤ 125°C

Unit

V

OL

Maximum Low–Level

Output Voltage Qa–Qh

PCP

OUT

, PCn

OUT

V

out

= 0.1 V or VCC – 0.1 V

|I

out

| ≤ 20 µA

2.0

4.5

6.0

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.1

V

Vin = VIH or V

IL

|I

out

| ≤ 4.0 mA

|I

out

| ≤ 5.2 mA

4.5

6.0

0.26

0.26

0.33

0.33

0.4

0.4

I

in

Maximum Input Leakage Current

SIGIN, COMP

IN

Vin = VCC or GND

2.0

3.0

4.5

6.0

± 3.0

± 7.0

± 18.0

± 30.0

± 4.0

± 9.0

± 23.0

± 38.0

± 5.0

± 11.0

± 27.0

± 45.0

µA

I

OZ

Maximum Three–State

Leakage Current

PC2

OUT

Output in High–Impedance State

Vin = VIH or V

IL

V

out

= VCC or GND

6.0 ± 0.5 ± 5.0 ± 10 µA

I

CC

Maximum Quiescent Supply

Current (per Package)

(VCO disabled)

Pins 3, 5 and 14 at V

CC

Pin 9 at GND; Input Leakage at

Pins 3 and 14 to be excluded

Vin = VCC or GND

|I

out

| = 0 µA

6.0 4.0 40 160 µA

NOTE: Information on typical parametric values can be found in Chapter 2 of the Motorola High–Speed CMOS Data Book (DL129/D).

[Phase Comparator Section]

AC ELECTRICAL CHARACTERISTICS

(CL = 50 pF, Input tr = tf = 6.0 ns)

Guaranteed Limit

Symbol

Parameter

V

CC

Volts

– 55 to 25_C

≤ 85°C ≤ 125°C

Unit

t

PLH

,

t

PHL

Maximum Propagation Delay, SIGIN/COMPIN to PC1

OUT

(Figure 1)

2.0

4.5

6.0

175

35

30

220

44

37

265

53

45

ns

t

PLH

,

t

PHL

Maximum Propagation Delay, SIGIN/COMPIN to PCP

OUT

(Figure 1)

2.0

4.5

6.0

340

68

58

425

85

72

510

102

87

ns

t

PLH

,

t

PHL

Maximum Propagation Delay, SIGIN/COMPIN to PC3

OUT

(Figure 1)

2.0

4.5

6.0

270

54

46

340

68

58

405

81

69

ns

t

PLZ

,

t

PHZ

Maximum Propagation Delay, SIGIN/COMPIN Output

Disable Time to PC2

OUT

(Figures 2 and 3)

2.0

4.5

6.0

200

40

34

250

50

43

300

60

51

ns

t

PZH

,

t

PZL

Maximum Propagation Delay, SIGIN/COMPIN Output

Enable Time to PC2

OUT

(Figures 2 and 3)

2.0

4.5

6.0

230

46

39

290

58

49

345

69

59

ns

t

TLH

,

t

THL

Maximum Output Transition Time

(Figure 1)

2.0

4.5

6.0

75

15

13

95

19

16

110

22

19

ns

Page 4

MC74HC4046A

MOTOROLA High–Speed CMOS Logic Data

DL129 — Rev 6

3–4

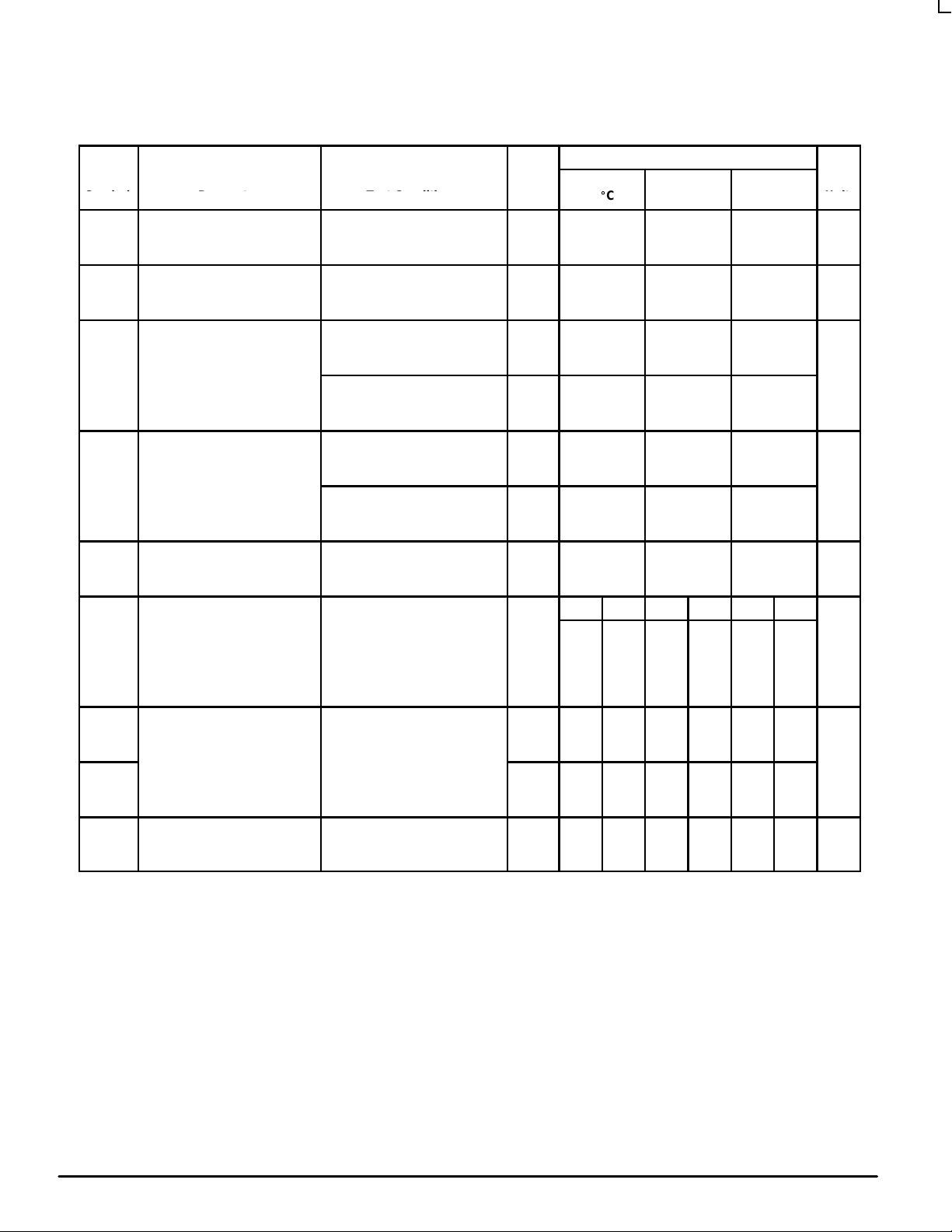

[VCO Section]

DC ELECTRICAL CHARACTERISTICS

(Voltages Referenced to GND)

Guaranteed Limit

Symbol

Parameter

Test Conditions

V

CC

Volts

– 55 to

25_C

≤ 85°C

≤ 125°C

Unit

V

IH

Minimum High–Level

Input Voltage

INH

V

out

= 0.1 V or VCC – 0.1 V

|I

out

| ≤ 20 µA

3.0

4.5

6.0

2.1

3.15

4.2

2.1

3.15

4.2

2.1

3.15

4.2

V

V

IL

Maximum Low–Level

Input Voltage

INH

V

out

= 0.1 V or VCC – 0.1 V

|I

out

| ≤ 20 µA

3.0

4.5

6.0

0.90

1.35

1.8

0.9

1.35

1.8

0.9

1.35

1.8

V

V

OH

Minimum High–Level

Output Voltage

VCO

OUT

Vin= VIH or V

IL

|I

out

| ≤ 20 µA

3.0

4.5

6.0

1.9

4.4

5.9

1.9

4.4

5.9

1.9

4.4

5.9

V

Vin= VIH or V

IL

|I

out

| ≤ 4.0 mA

|I

out

| ≤ 5.2 mA

4.5

6.0

3.98

5.48

3.84

5.34

3.7

5.2

V

OL

Maximum Low–Level

Output Voltage

VCO

OUT

V

out

= 0.1 V or VCC – 0.1 V

|I

out

| ≤ 20 µA

3.0

4.5

6.0

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.1

V

Vin= VIH or V

IL

|I

out

| ≤ 4.0 mA

|I

out

| ≤ 5.2 mA

4.5

6.0

0.26

0.26

0.33

0.33

0.4

0.4

I

in

Maximum Input

Leakage Current

INH, VCO

IN

Vin= VCC or GND 6.0 0.1 1.0 1.0 µA

Min Max Min Max Min Max

Operating Voltage Range at

VCOIN over the range

specified for R1; For linearity

see Fig. 15A, Parallel value of

R1 and R2 should be > 2.7 kΩ

INH = V

IL

3.0

4.5

6.0

0.1

0.1

0.1

1.0

2.5

4.0

0.1

0.1

0.1

1.0

2.5

4.0

0.1

0.1

0.1

1.0

2.5

4.0

V

R1 Resistor Range 3.0

4.5

6.0

3.0

3.0

3.0

300

300

300

3.0

3.0

3.0

300

300

300

3.0

3.0

3.0

300

300

300

kΩ

R2 3.0

4.5

6.0

3.0

3.0

3.0

300

300

300

3.0

3.0

3.0

300

300

300

3.0

3.0

3.0

300

300

300

C1 Capacitor Range 3.0

4.5

6.0

40

40

40

No

Limit

pF

V

VCO

IN

Page 5

MC74HC4046A

High–Speed CMOS Logic Data

DL129 — Rev 6

3–5 MOTOROLA

[VCO Section]

AC ELECTRICAL CHARACTERISTICS

(CL = 50 pF, Input tr = tf = 6.0 ns)

Guaranteed Limit

V

– 55 to 25_C

≤ 85°C

≤ 125°C

Symbol

Parameter

V

CC

Volts

Min Max Min Max Min Max

Unit

∆f/T Frequency Stability with

Temperature Changes

(Figure 13A, B, C)

3.0

4.5

6.0

%/K

fo VCO Center Frequency

(Duty Factor = 50%)

(Figure 14A, B, C, D)

3.0

4.5

6.0

3

11

13

MHz

∆fVCO VCO Frequency Linearity 3.0

4.5

6.0

See Figures 15A, B, C %

∂ VCO Duty Factor at VCO

OUT

3.0

4.5

6.0

Typical 50% %

[Demodulator Section]

DC ELECTRICAL CHARACTERISTICS

Guaranteed Limit

V

– 55 to 25_C

≤ 85°C

≤ 125°C

Symbol

Parameter

Test Conditions

V

CC

Volts

Min Max Min Max Min Max

Unit

RS Resistor Range At RS > 300 kΩ the

Leakage Current can

Influence VDEM

OUT

3.0

4.5

6.0

50

50

50

300

300

300

kΩ

V

OFF

Offset Voltage

VCOIN to VDEM

OUT

Vi = VVCOIN = 1/2 VCC;

Values taken over RS

Range.

3.0

4.5

6.0

See Figure 12 mV

RD Dynamic Output

Resistance at DEM

OUT

VDEM

OUT

= 1/2 V

CC

3.0

4.5

6.0

Typical 25 Ω Ω

Page 6

MC74HC4046A

MOTOROLA High–Speed CMOS Logic Data

DL129 — Rev 6

3–6

SWITCHING WAVEFORMS

Figure 1. Figure 2.

Figure 3. Figure 4. Test Circuit

SIGIN, COMP

IN

INPUTS

50%

90%

50%

10%

PCP

OUT

, PC1

OUT

PC3

OUT

OUTPUTS

V

CC

GND

t

PHL

t

PLH

t

TLH

t

THL

SIGIN

INPUT

COMP

IN

INPUT

50%

90%

50%

PC2

OUT

OUTPUT

V

CC

GND

t

PZH

t

PHZ

50%

V

CC

GND

V

OH

HIGH

IMPEDANCE

SIGIN

INPUT

COMP

IN

INPUT

50%

10%

PC2

OUT

OUTPUT

V

CC

GND

t

PZL

t

PLZ

50%

V

CC

GND

V

OL

HIGH

IMPEDANCE

TEST POINT

CL*

OUTPUT

DEVICE

UNDER

TEST

*INCLUDES ALL PROBE AND JIG CAPACITANCE

50%

Page 7

MC74HC4046A

High–Speed CMOS Logic Data

DL129 — Rev 6

3–7 MOTOROLA

DETAILED CIRCUIT DESCRIPTION

Voltage Controlled Oscillator/Demodulator Output

The VCO requires two or three external components to operate. These are R1, R2, C1. Resistor R1 and Capacitor C1

are selected to determine the center frequency of the VCO

(see typical performance curves Figure 14). R2 can be used

to set the offset frequency with 0 volts at VCO input. For example, if R2 is decreased, the offset frequency is increased.

If R2 is omitted the VCO range is from 0 Hz. The effect of R2

is shown in Figure 24, typical performance curves. By increasing the value of R2 the lock range of the PLL is increased and the gain (volts/Hz) is decreased. Thus, for a

narrow lock range, large swings on the VCO input will cause

less frequency variation.

Internally, the resistors set a current in a current mirror, as

shown in Figure 5. The mirrored current drives one side of

the capacitor. Once the voltage across the capacitor charges

up to V

ref

of the comparators, the oscillator logic flips the capacitor which causes the mirror to charge the opposite side

of the capacitor. The output from the internal logic is then taken to VCO output (Pin 4).

The input to the VCO is a very high impedance CMOS input and thus will not load down the loop filter, easing the filters design. In o rder t o make s ignals at t he VCO i nput

accessible without degrading the loop performance, the VCO

input voltage is buffered through a unity gain Op–amp to Demod Output. This Op–amp can drive loads of 50K ohms or

more and provides no loading effects to the VCO input voltage (see Figure 12).

An inhibit input is provided to allow disabling of the VCO

and all Op–amps (see Figure 5). This is useful if the internal

VCO is not being used. A logic high on inhibit disables the

VCO and all Op–amps, minimizing standby power consumption.

Figure 5. Logic Diagram for VCO

_

+

_

+

_

+

I

1

I

2

R

2

12

V

REF

VCO

IN

R

1

9

11

10

5

6

7

4

+ +

V

ref

C1

(EXTERNAL)

DEMOD

OUT

CURRENT

MIRROR

I1 + I2 = I

3

VCO

OUT

INH

I

3

–

–

Page 8

MC74HC4046A

MOTOROLA High–Speed CMOS Logic Data

DL129 — Rev 6

3–8

The output of the VCO is a standard high speed CMOS

output with an equivalent LS–TTL fan out of 10. The VCO

output is approximately a square wave. This output can either directly feed the COMPIN of the phase comparators or

feed external prescalers (counters) to enable frequency synthesis.

Phase Comparators

All three phase comparators have two inputs, SIGIN and

COMPIN. The SIGIN and COMPIN have a special DC bias

network that enables AC coupling of input signals. If the signals are not AC coupled, standard 54HC/74HC input levels

are required. Both input structures are shown in Figure 6.

The outputs of these comparators are essentially standard

54HC/74HC outputs (comparator 2 is TRI–STATEABLE). In

normal operation VCC and ground voltage levels are fed to

the loop filter. This differs from some phase detectors which

supply a current to the loop filter and should be considered in

the design. (The MC14046 also provides a voltage).

Figure 6. Logic Diagram for Phase Comparators

SIG

IN

COMP

IN

V

CC

V

CC

V

CC

14

3

13

1

15

2

PC2

OUT

PCP

OUT

PC3

OUT

PC1

OUT

Phase Comparator 1

This c omparator i s a simple X OR gate s imilar to t he

54/74HC86. Its operation is similar to an overdriven balanced modulator. To maximize lock range the input frequencies must have a 50% duty cycle. Typical input and output

waveforms are shown in Figure 7. The output of the phase

detector feeds the loop filter which averages the output voltage. The frequency range upon which the PLL will lock onto

if initially out of lock is defined as the capture range. The capture range for phase detector 1 is dependent on the loop filter

design. The capture range can be as large as the lock range,

which is equal to the VCO frequency range.

To see how the detector operates, refer to Figure 7. When

two square wave signals are applied to this comparator, an

output waveform (whose d uty cycle is dependent on the

phase difference between the two signals) results. As the

phase difference increases, the output duty cycle increases

and the voltage after the loop filter increases. In order to

achieve lock when the PLL input frequency increases, the

VCO input voltage must increase and the phase difference

between COMPIN and SIGIN will increase. At an input frequency equal to f

min

, the VCO input is at 0 V. This requires

the phase detector output to be grounded; hence, the two input signals must be in phase. When the input frequency is

f

max

, the VCO input must be VCC and the phase detector in-

puts must be 180 degrees out of phase.

Figure 7. Typical Waveforms for PLL Using

Phase Comparator 1

V

CC

GND

SIG

IN

COMP

IN

PC1

OUT

VCO

IN

Page 9

MC74HC4046A

High–Speed CMOS Logic Data

DL129 — Rev 6

3–9 MOTOROLA

The XOR is more susceptible to locking onto harmonics of

the SIGIN than the digital phase detector 2. For instance, a

signal 2 times the VCO frequency results in the same output

duty cycle as a signal equal to the VCO frequency . The difference is that the output frequency of the 2f example is twice

that of the other example. The loop filter and VCO range

should be designed to prevent locking on to harmonics.

Phase Comparator 2

This detector is a digital memory network. It consists of

four flip–flops and some gating logic, a three state output and

a phase pulse output as shown in Figure 6. This comparator

acts only on the positive edges of the input signals and is independent of duty cycle.

Phase comparator 2 operates in such a way as to force the

PLL into lock with 0 phase difference between the VCO output and the signal input positive waveform edges. Figure 8

shows some typical loop waveforms. First assume that SIG

IN

is leading the COMPIN. This means that the VCO’s frequency must be increased to bring its leading edge into proper

phase alignment. Thus the phase detector 2 output is set

high. This will cause the loop filter to charge up the VCO input, increasing the VCO frequency . Once the leading edge of

the COMPIN is detected, the output goes TRI–STATE holding the VCO input at the loop filter voltage. If the VCO still

lags the SIGIN then the phase detector will again charge up

the VCO input for the time between the leading edges of both

waveforms.

If the VCO leads the SIGIN then when the leading edge of

the VCO is seen; the output of the phase comparator goes

low. This discharges the loop filter until the leading edge of

the SIGIN is detected at which time the output disables itself

again. This has the effect of slowing down the VCO to again

make the rising edges of both waveforms coincidental.

When the PLL is out of lock, the VCO will be running either

slower or faster than the SIGIN. If it is running slower the

phase detector will see more SIGIN rising edges and so the

output of the phase comparator will be high a majority of the

time, raising the VCO’s frequency. Conversely, if the VCO is

running faster than the SIGIN, the output of the detector will

be low most of the time and the VCO’s output frequency will

be decreased.

As one can see, when the PLL is locked, the output of

phase comparator 2 will be disabled except for minor corrections at the leading edge of the waveforms. When PC2 is

TRI–STATED, the PCP output is high. This output can be

used to determine when the PLL is in the locked condition.

This detector has several interesting characteristics. Over

the entire VCO frequency range there is no phase difference

between the COMPIN and the SIGIN. The lock range of the

PLL is the same as the capture range. Minimal power was

consumed in the loop filter since in lock the detector output is

a high impedance. When no SIGIN is present, the detector

will see only VCO leading edges, so the comparator output

will stay low, forcing the VCO to f

min

.

Phase comparator 2 is more susceptible to noise, causing

the PLL to unlock. If a noise pulse is seen on the SIGIN, the

comparator treats it as another positive edge of the SIG

IN

and will cause the output to go high until the VCO leading

edge is seen, potentially for an entire SIGIN period. This

would cause the VCO to speed up during that time. When using PC1, the output of that phase detector would be disturbed

for only the short duration of the noise spike and would cause

less upset.

Phase Comparator 3

This is a positive edge–triggered sequential phase detector using an RS flip–flop as shown in Figure 6. When the PLL

is using this comparator, the loop is controlled by positive signal transitions and the duty factors of SIGIN and COMP

IN

are not important. It has some similar characteristics to the

edge sensitive comparator. To see how this detector works,

assume input pulses are applied to the SIGIN and COMPIN’s

as shown in Figure 9. When the SIGIN leads the COMPIN,

the flop is set. This will charge the loop filter and cause the

VCO to speed up, bringing the comparator into phase with

the SIGIN. The phase angle between SIGIN and COMPIN varies from 0° to 360° and is 180° at fo. The voltage swing for

PC3 is greater than for PC2 but consequently has more ripple

in the signal to the VCO. When no SIGIN is present the VCO

will be forced to f

max

as opposed to f

min

when PC2 is used.

The operating characteristics of all three phase comparators should be compared to the requirements of the system

design and the appropriate one should be used.

Figure 8. Typical Waveforms for PLL Using

Phase Comparator 2

V

CC

GND

SIG

IN

COMP

IN

PC2

OUT

VCO

IN

PCP

OUT

HIGH IMPEDANCE OFF–STATE

Figure 9. Typical Waveform for PLL Using

Phase Comparator 3

VCC

GND

SIG

IN

COMP

IN

PC3

OUT

VCO

IN

Page 10

MC74HC4046A

MOTOROLA High–Speed CMOS Logic Data

DL129 — Rev 6

3–10

Figure 10. Input Resistance at SIGIN, COMPIN with

∆VI = 1.0 V at Self–Bias Point

Figure 11. Input Current at SIGIN, COMPIN with

∆VI = 500 mV at Self–Bias Point

Figure 12. Offset Voltage at Demodulator Output as

a Function of VCOIN and R

S

Figure 13A. Frequency Stability versus Ambient

Temperature: VCC = 3.0 V

800

0

VCC=3.0 V

VCC=4.5 V

VCC=6.0 V

1/2 VCC–1.0 V 1/2 V

CC

4.0

–4.0

1/2VCC – 500 mV

VI (V)

1/2 V

CC

1/2 VCC + 500 mV

0

6.0

0

0

3.0 6.0

VCC=4.5 V RS=300 k

VCC=4.5 V RS=50 k

VCC=3.0 V RS=300 k

VCC=3.0 V RS=50 k

DEMOD OUT

15

10

5.0

0

–5.0

–10

–15

–100 –50 0 50 100 150

R1=100 k

Ω

R1=300 k

Ω

R1=3.0 k

Ω

R1=100 k

Ω

R1=300 k

Ω

R1=3.0 k

Ω

VCC = 3.0 V

C1 = 100 pF; R2 =

∞

; V

VCOIN

=1/3 V

CC

FREQUENCY STABILITY (%)

AMBIENT TEMPERATURE (°C)

VCC=3.0 V

VCC=4.5 V

VCC=6.0 V

R

I

Ω

)(k

400

I

I

( A)

µ

V

DEM

OUT

VCC=6.0 V RS=300 k

VCC=6.0 V RS=50 k

Figure 13B. Frequency Stability versus Ambient

Temperature: VCC = 4.5 V

Figure 13C. Frequency Stability versus Ambient

Temperature: VCC = 6.0 V

R1=100 k

Ω

R1=300 k

Ω

R1=3.0 k

Ω

15

10

5.0

0

–5.0

–10

–15

–100 –50 0 50 100 150

VCC= 4.5 V

C1 = 100 pF; R2 =

∞

; V

VCOIN

= 1/2 V

CC

AMBIENT TEMPERATURE (

°

C)

FREQUENCY STABILITY (%)

FREQUENCY STABILITY (%)

R1=100 k

Ω

R1=3.0 k

Ω

6.0

4.0

0

–2.0

–10

–100 –50 0 50 100 150

VCC= 6.0 V

C1 = 100 pF; R2 =

∞

; V

VCOIN

=1/2 V

CC

AMBIENT TEMPERATURE (

°

C)

–8.0

–6.0

–4.0

2.0

8.0

10

R1=300 k

Ω

1/2 VCC+1.0 V

VI (V)

VCOIN (V)

=

Page 11

MC74HC4046A

High–Speed CMOS Logic Data

DL129 — Rev 6

3–11 MOTOROLA

Figure 14A. VCO Frequency (f

VCO

) as a Function

of the VCO Input Voltage (V

VCOIN

)

Figure 14B. VCO Frequency (f

VCO

) as a Function

of the VCO Input Voltage (V

VCOIN

)

VCC = 6.0 V

VCC = 4.5 V

VCC = 3.0 V

R1 = 3.0 k

Ω

C1 = 39 pF

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

23

21

19

17

15

13

11

9

7.0

V

VCOIN

(V)

(MHz)f

VCO

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

70

60

50

40

30

20

10

0

V

VCOIN

(V)

(KHz)f

VCO

VCC = 6.0 V

VCC = 4.5 V

VCC = 3.0 V

R1 = 3.0 k

Ω

C1 = 0.1 µ

F

Figure 14C. VCO Frequency (f

VCO

) as a Function

of the VCO Input Voltage (V

VCOIN

)

Figure 14D. VCO Frequency (f

VCO

) as a Function

of the VCO Input Voltage (V

VCOIN

)

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

2.0

1.0

0

V

VCOIN

(V)

(MHz)f

VCO

VCC = 6.0 V

VCC = 4.5 V

VCC = 3.0 V

R1 = 300 k

Ω

C1 = 39 pF

4.5

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

1.0

V

VCOIN

(V)

(KHz)f

VCO

4.5

0.9

0.8

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0

VCC = 6.0 V

VCC = 4.5 V

VCC = 3.0 V

R1 = 300 k

Ω

C1 = 0.1 µ

F

Figure 15A. Frequency Linearity versus

R1, C1 and V

CC

Figure 15B. Definition of VCO Frequency Linearity

∆

f

VCO

(%)

2.0

1.0

–2.0

0

–1.0

10

0

10

1

10

2

10

3

R1 (k

Ω

)

R2 = ∞

; ∆

V = 0.5 V

C1 = 39 pF

C1 = 1.0 µ

F

f

2

f

0

f

0

′

f

1

MIN 1/2 V

CC

MAX

∆

V = 0.5 V OVER THE VCC RANGE:

FOR VCO LINEARITY

f

0

′

= (f1 + f2) / 2

LINEARITY = (f

0

′

– f0) / f0′

) x 100%

VCC=

4.5 V

6.0 V

3.0 V

4.5 V

6.0 V

3.0 V

Page 12

MC74HC4046A

MOTOROLA High–Speed CMOS Logic Data

DL129 — Rev 6

3–12

Figure 16. Power Dissipation versus R1 Figure 17. Power Dissipation versus R2

Figure 18. DC Power Dissipation of

Demodulator versus R

S

Figure 19. VCO Center Frequency versus C1

R1 (kΩ)

10

6

10

5

10

4

10

3

10

0

10

1

10

2

10

3

P

R1

W)

µ

(

VCC= 6.0 V, C1= 40 pF

VCC= 6.0 V, C1= 1.0 µF

VCC= 4.5 V, C1= 40 pF

VCC= 3.0 V, C1= 40 pF

VCC= 3.0 V, C1= 1.0 µF

CL= 50 pF; R2 =∞; V

VCOIN

= 1/2 VCC FOR VCC= 4.5 V AND 6.0 V;

V

VCOIN

= 1/3 VCC FOR VCC= 3.0 V; T

amb

= 25°C

VCC= 6.0 V, C1= 40 pF

VCC= 6.0 V, C1= 1.0 µF

VCC= 4.5 V, C1= 40 pF

VCC= 4.5 V, C1= 1.0 µF

VCC= 4.5 V, C1= 1.0 µF

VCC= 3.0 V, C1= 1.0 µF

CL= 50 pF; R1 =∞; V

VCOIN

= 0 V; T

amb

= 25°C

10

6

10

5

10

4

10

3

10

0

10

1

10

2

10

3

R2 (k

Ω

)

P

R2

W)

µ

(

P

DEM

( W)

µ

RS (kΩ)

10

3

10

2

10

1

10

0

10

1

10

2

10

3

R1 = R2 =∞; T

amb

= 25°C

VCC=6.0 V

VCC=4.5 V

VCC=3.0 V

10

1

10

2

10

3

10

4

10

5

10

6

C1 (pF)

6.0 V

4.5 V

3.0 V

6.0 V

4.5 V

3.0 V

VCC=

INH = GND; T

amb

= 25°C; R2 =∞; V

VCOIN

= 1/3 V

CC

R1=3.0 k

Ω

R1=100 k

Ω

R1=300 k

Ω

f

VCO

(Hz)

10

8

10

7

10

6

10

5

10

4

10

3

10

2

VCC= 3.0 V, C1= 40 pF

6.0 V

4.5 V

3.0 V

Figure 20. Frequency Offset versus C1 Figure 21. Typical Frequency Lock Range (2fL)

versus R1C

1

f

off

(Hz)

10

8

10

7

10

6

10

5

10

4

10

3

10

2

10

1

C1 (pF)

10

1

10

2

10

3

10

4

10

5

10

6

6.0 V

4.5 V

3.0 V

6.0 V

4.5 V

3.0 V

6.0 V

4.5 V

3.0 V

VCC=

10

8

10

7

10

6

10

5

10

4

10

3

10

2

2

fL

(Hz)

10

–7

10

–6 10–5

10

–4

10

–3

10

–2

10

–1

R1C1

R1 =∞; V

VCOIN

= 1/2 VCC FOR VCC= 4.5 V AND 6.0 V;

V

VCOIN

= 1/3 VCC FOR VCC= 3.0 V; INH = GND; T

amb

= 25°C

R2=3.0 k

Ω

R2=100 k

Ω

R2=300 k

Ω

VCC= 4.5 V; R2 =

∞

Page 13

MC74HC4046A

High–Speed CMOS Logic Data

DL129 — Rev 6

3–13 MOTOROLA

Figure 22. R2 versus f

max

Figure 23. R2 versus f

min

Figure 24. R2 versus Frequency Lock Range (2fL)

FREQ. (MHz)

1.0 10

1

10

4

10

5

10

2

10

3

0

5.0

10

15

20

C1=39 pF

R2 ( k

Ω

)

10

0

10

1

10

4

10

5

10

6

C1=39 pF

10

2

10

3

–2.0

0

4.0

2.0

6.0

8.0

10

12

14

FREQ. (MHz)

R2 ( kΩ)

R1=10 k

Ω

R1=3 k

Ω

R1=20 k

Ω

R1=30 k

Ω

R1=40 k

Ω

R1=50 k

Ω

R1=100 k

Ω

R1=300 k

Ω

R1=3.0 k

Ω

R1=20 k

Ω

R1=30 k

Ω

R1=100 k

Ω

R1=300 k

Ω

R1=50 k

Ω

R2 ( kΩ)

1.0 10

1

10

2

10

3

10

4

10

5

2f

0

10

20

C1=39 pF

R1=10 k

Ω

R1=3.0 k

Ω

R1=20 k

Ω

R1=30 k

Ω

R1=40 k

Ω

R1=50 k

Ω

R1=100 k

Ω

R1=300 k

Ω

R1=40 k

Ω

L

(MHz)

R1=10 k

Ω

Page 14

MC74HC4046A

MOTOROLA High–Speed CMOS Logic Data

DL129 — Rev 6

3–14

APPLICATION INFORMATION

The following information is a guide for approximate values of R1, R2, and C1. Figures 19, 20, and 21 should be used as

references as indicated below, also the values of R1, R2, and C1 should not violate the Maximum values indicated in the DC

ELECTRICAL CHARACTERISTICS tables.

Phase Comparator 1 Phase Comparator 2 Phase Comparator 3

R2 = ∞ R2 0

R

R2 = ∞ R2 0

R

R2 = ∞ R2 0

R

• Given f0

• Use f0 with Figure

19 to determine

R1 and C1.

(see Figure 23 for

characteristics of

the VCO operation)

• Given f0 and fL

• Calculate f

min

f

min

= f0–fL

• Determine values

of C1 and R2 from

Figure 20.

• Determine R1–C1

from Figure 21.

• Calculate value of

R1 from the value

of C1 and the

product of R1C1

from Figure 21.

(see Figure 24 for

characteristics of the

VCO operation)

• Given f

max

and f0

• Determine the

value of R1 and

C1 using Figure 19

and use Figure 21

to obtain 2fL and

then use this to

calculate f

min

.

• Given f0 and fL

• Calculate f

min

f

min

= f0–fL

• Determine values

of C1 and R2 from

Figure 20.

• Determine R1–C1

from Figure 21.

• Calculate value of

R1 from the value

of C1 and the

product of R1C1

from Figure 21.

(see Figure 24 for

characteristics of the

VCO operation)

• Given f

max

and f0

• Determine the

value of R1 and

C1 using Figure 19

and Figure 21 to

obtain 2fL and

then use this to

calculate f

min

.

• Given f0 and fL

• Calculate f

min:

f

min

= f0–fL

• Determine values

of C1 and R2 from

Figure 20.

• Determine R1–C1

from Figure 21.

• Calculate value of

R1 from the value

of C1 and the

product of R1C1

from Figure 21.

(see Figure 24 for

characteristics of the

VCO operation)

Page 15

MC74HC4046A

High–Speed CMOS Logic Data

DL129 — Rev 6

3–15 MOTOROLA

OUTLINE DIMENSIONS

N SUFFIX

PLASTIC PACKAGE

CASE 648–08

ISSUE R

MIN MINMAX MAX

INCHES MILLIMETERS

DIM

A

B

C

D

F

G

H

J

K

L

M

S

18.80

6.35

3.69

0.39

1.02

0.21

2.80

7.50

0

°

0.51

19.55

6.85

4.44

0.53

1.77

0.38

3.30

7.74

10

°

1.01

0.740

0.250

0.145

0.015

0.040

0.008

0.110

0.295

0

°

0.020

0.770

0.270

0.175

0.021

0.070

0.015

0.130

0.305

10

°

0.040

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEADS WHEN

FORMED PARALLEL.

4. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

5. ROUNDED CORNERS OPTIONAL.

2.54 BSC

1.27 BSC

0.100 BSC

0.050 BSC

–A

–

B

1 8

916

F

H

G

D

16 PL

S

C

–T

–

SEATING

PLANE

K

J

M

L

T A0.25 (0.010)

M M

0.25 (0.010) T B A

M

S S

MIN MINMAX MAX

MILLIMETERS INCHES

DIM

A

B

C

D

F

G

J

K

M

P

R

9.80

3.80

1.35

0.35

0.40

0.19

0.10

0

°

5.80

0.25

10.00

4.00

1.75

0.49

1.25

0.25

0.25

7

°

6.20

0.50

0.386

0.150

0.054

0.014

0.016

0.008

0.004

0

°

0.229

0.010

0.393

0.157

0.068

0.019

0.049

0.009

0.009

7

°

0.244

0.019

1.27 BSC 0.050 BSC

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE

MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006)

PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.127 (0.005) TOTAL

IN EXCESS OF THE D DIMENSION AT

MAXIMUM MATERIAL CONDITION.

1

8

916

–A

–

–B

–

D 16 PL

K

C

G

–T

–

SEATING

PLANE

R X 45°

M

J

F

P 8 PL

0.25 (0.010) B

M M

D SUFFIX

PLASTIC SOIC PACKAGE

CASE 751B–05

ISSUE J

How to reach us:

USA/EUROPE: Motorola Literature Distribution; JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, Toshikatsu Otsuki,

P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–3521–8315

MFAX: RMFAX0@email.sps.mot.com –TOUCHTONE (602) 244–6609 HONG KONG: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park,

INTERNET: http://Design–NET.com 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty , representation or guarantee regarding

the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit,

and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “T ypical” parameters can and do vary in different

applications. All operating parameters, including “T ypicals” must be validated for each customer application by customer’s technical experts. Motorola does

not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in

systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of

the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such

unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless

against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

MC74HC4046A/D

*MC74HC4046A/D*

◊

CODELINE

Loading...

Loading...