Page 1

1

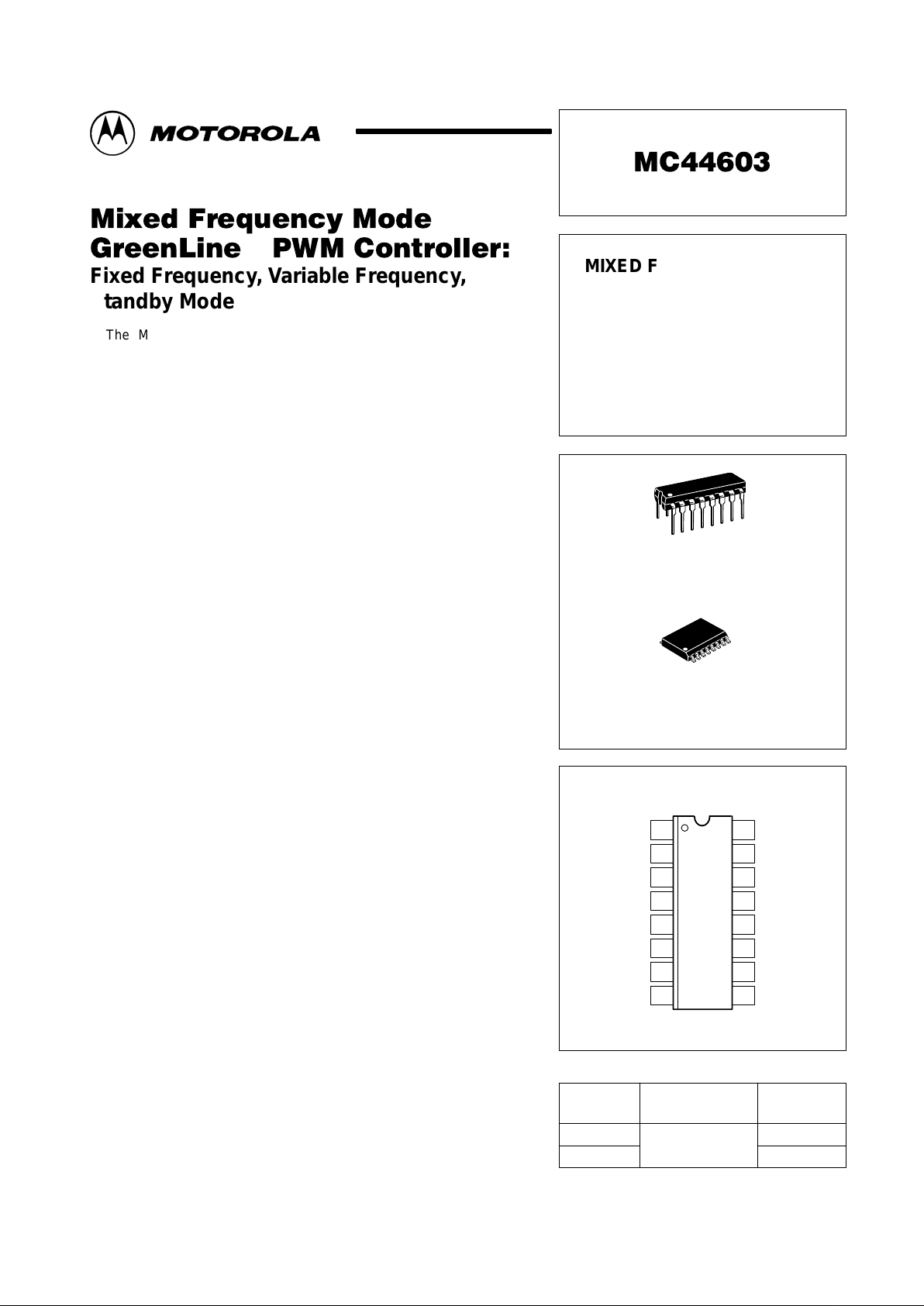

Device

Operating

Temperature Range

Package

MIXED FREQUENCY MODE

GREENLINE PWM*

CONTROLLER:

ORDERING INFORMATION

MC44603P

TA = –25° to +85°C

Plastic DIP–16

P SUFFIX

PLASTIC PACKAGE

CASE 648

16

1

16

15

14

13

12

11

10

9

2

3

4

5

6

7

8

(Top View)

V

CC

V

C

Output

R

ref

Sync Input

PIN CONNECTIONS

Order this document by MC44603/D

Gnd

Foldback Input

Overvoltage

Protection (OVP)

Current Sense Input

Demag Detection

R

Frequency

Standby

Voltage Feedback

Input

Error Amp Output

R

Power Standby

Soft–Start/D

max

/

Voltage Mode

C

T

V ARIABLE FREQUENCY,

FIXED FREQUENCY,

ST ANDBY MODE

* PWM = Pulse Width Modulation

MC44603DW SOP–16L

16

1

DW SUFFIX

PLASTIC PACKAGE

CASE 751G

(SOP–16L)

1

MOTOROLA ANALOG IC DEVICE DATA

Fixed Frequency, Variable Frequency,

Standby Mode

The MC44603 is an enhanced high performance controller that is

specifically designed for off–line and dc–to–dc converter applications. This

device has the unique ability of automatically changing operating modes if

the converter output is overloaded, unloaded, or shorted, offering the

designer additional protection for increased system reliability. The MC44603

has several distinguishing features when compared to conventional SMPS

controllers. These features consist of a foldback facility for overload

protection, a standby mode when the converter output is slightly loaded, a

demagnetization detection for reduced switching stresses on transistor and

diodes, and a high current totem pole output ideally suited for driving a power

MOSFET. It can also be used for driving a bipolar transistor in low power

converters (< 150 W). It is optimized to operate in discontinuous mode but

can also operate in continuous mode. Its advanced design allows use in

current mode or voltage mode control applications.

Current or Voltage Mode Controller

• Operation up to 250 kHz Output Switching Frequency

• Inherent Feed Forward Compensation

• Latching PWM for Cycle–by–Cycle Current Limiting

• Oscillator with Precise Frequency Control

High Flexibility

• Externally Programmable Reference Current

• Secondary or Primary Sensing

• Synchronization Facility

• High Current Totem Pole Output

• Undervoltage Lockout with Hysteresis

Safety/Protection Features

• Overvoltage Protection Against Open Current and Open Voltage Loop

• Protection Against Short Circuit on Oscillator Pin

• Fully Programmable Foldback

• Soft–Start Feature

• Accurate Maximum Duty Cycle Setting

• Demagnetization (Zero Current Detection) Protection

• Internally Trimmed Reference

GreenLine Controller: Low Power Consumption in Standby Mode

• Low Startup and Operating Current

• Fully Programmable Standby Mode

• Controlled Frequency Reduction in Standby Mode

• Low dV/dT for Low EMI Radiations

GreenLine is a trademark of Motorola, Inc.

Motorola, Inc. 1999 Rev 1

Page 2

MC44603

2

MOTOROLA ANALOG IC DEVICE DATA

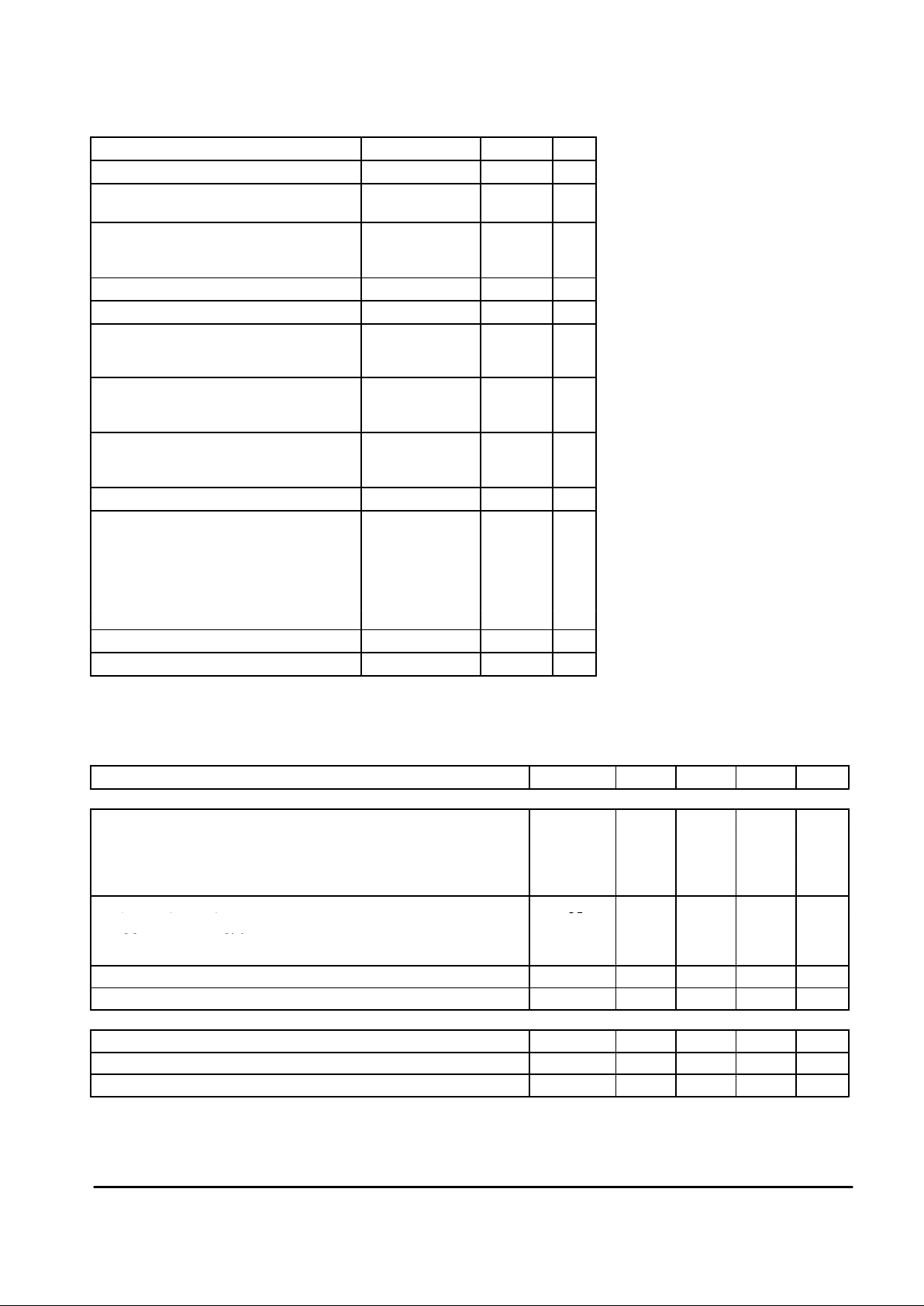

MAXIMUM RATINGS

Rating Symbol Value Unit

Total Power Supply and Zener Current (ICC + IZ) 30 mA

Supply Voltage with Respect to Ground (Pin 4) V

C

V

CC

18 V

Output Current (Note 1) mA

Source I

O(Source)

–750

Sink I

O(Sink)

750

Output Energy (Capacitive Load per Cycle) W 5.0 µJ

RF

Stby

, CT, Soft–Start, R

ref

, RP

Stby

Inputs V

in

–0.3 to 5.5 V

Foldback Input, Current Sense Input,

E/A Output, Voltage Feedback Input,

Overvoltage Protection, Synchronization Input

V

in

–0.3 to

VCC + 0.3

V

Synchronization Input

High State Voltage V

IH

VCC + 0.3 V

Low State Reverse Current V

IL

–20 mA

Demagnetization Detection Input Current mA

Source I

demag–ib (Source)

–4.0

Sink I

demag–ib (Sink)

10

Error Amplifier Output Sink Current I

E/A (Sink)

20 mA

Power Dissipation and Thermal Characteristics

P Suffix, Dual–In–Line, Case 648

Maximum Power Dissipation at TA = 85°C P

D

0.6 W

Thermal Resistance, Junction–to–Air R

θJA

100 °C/W

DW Suffix, Surface Mount, Case 751G

Maximum Power Dissipation at TA = 85°C P

D

0.45 W

Thermal Resistance, Junction–to–Air R

θJA

145 °C/W

Operating Junction Temperature T

J

150 °C

Operating Ambient Temperature T

A

–25 to +85 °C

NOTES: 1. Maximum package power dissipation limits must be observed.

2. ESD data available upon request.

ELECTRICAL CHARACTERISTICS (V

CC

and VC = 12 V, [Note 3], R

ref

= 10 kΩ, CT = 820 pF, for typical values TA = 25°C,

for min/max values TA = –25° to +85°C [Note 4], unless otherwise noted.)

Characteristic

Symbol Min Typ Max Unit

OUTPUT SECTION

Output Voltage (Note 5) V

Low State (I

Sink

= 100 mA)

Low State (I

Sink

= 500 mA)

V

OL

–

–

1.0

1.4

1.2

2.0

High State (I

Source

= 200 mA)

High State (I

Source

= 500 mA)

V

OH

–

–

1.5

2.0

2.0

2.7

Output Voltage During Initialization Phase V

OL

V

pgg

VCC = 0 to 1.0 V, I

Sink

= 10 µA

OL

– –

1.0

VCC = 1.0 to 5.0 V , I

Sink

= 100 µA

–

–

0.1

1.0

V

CC

= 5.0 to 13 V,

I

Sink

= 1.0

mA

–

0.1

1.0

Output Voltage Rising Edge Slew–Rate (CL = 1.0 nF, TJ = 25°C) dVo/dT – 300 – V/µs

Output Voltage Falling Edge Slew–Rate (CL = 1.0 nF, TJ = 25°C) dVo/dT – –300 – V/µs

ERROR AMPLIFIER SECTION

Voltage Feedback Input (V

E/A out

= 2.5 V) V

FB

2.42 2.5 2.58 V

Input Bias Current (VFB = 2.5 V) I

FB–ib

–2.0 –0.6 – µA

Open Loop Voltage Gain (V

E/A out

= 2.0 to 4.0 V) A

VOL

65 70 – dB

NOTES: 3. Adjust VCC above the startup threshold before setting to 12 V.

4.Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

5.VC must be greater than 5.0 V.

Page 3

MC44603

3

MOTOROLA ANALOG IC DEVICE DATA

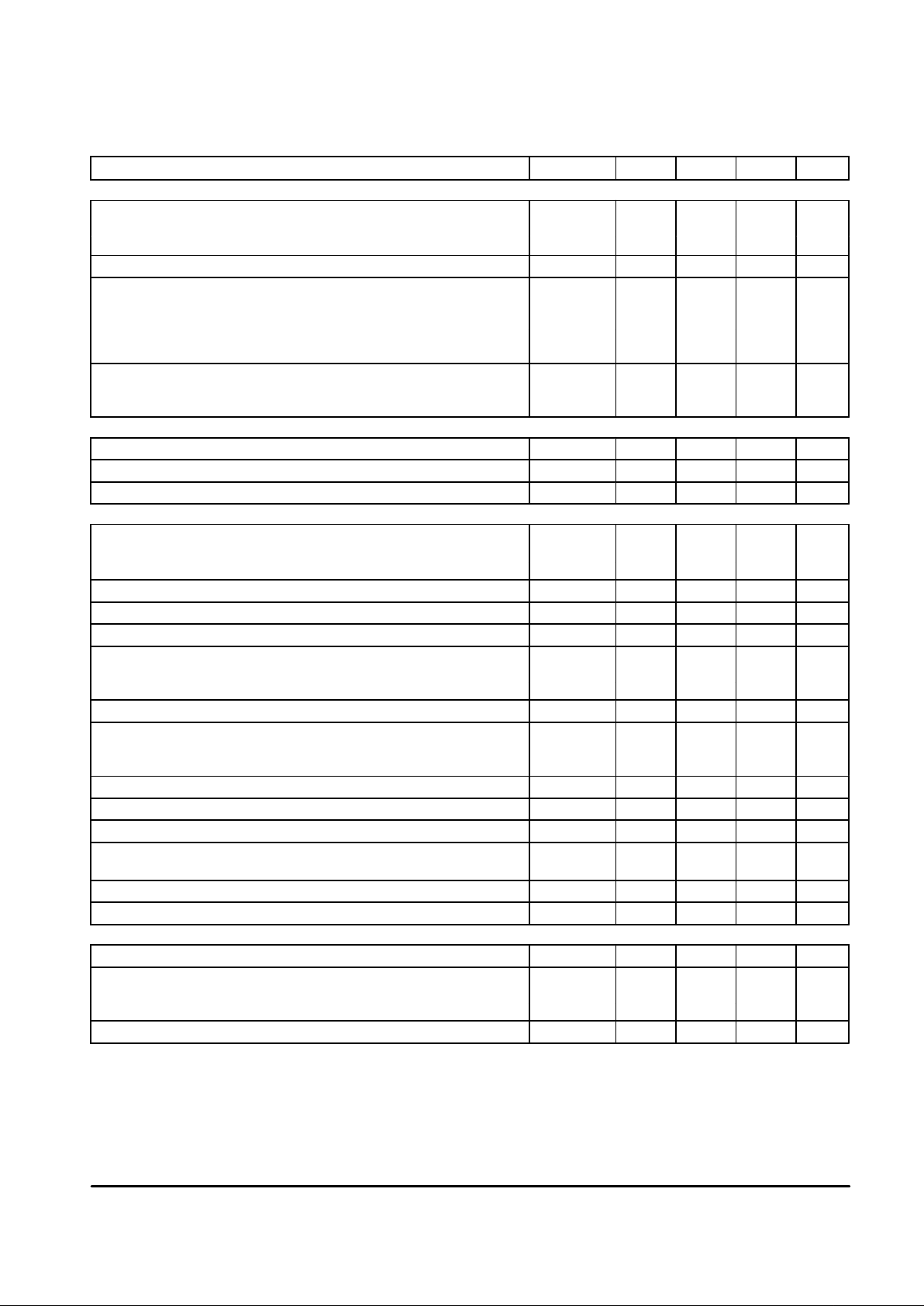

ELECTRICAL CHARACTERISTICS (continued) (V

CC

and VC = 12 V , [Note 3], R

ref

= 10 kΩ, CT = 820 pF , for typical values TA = 25°C,

for min/max values TA = –25° to +85°C [Note 4], unless otherwise noted.)

Characteristic

Symbol Min Typ Max Unit

ERROR AMPLIFIER SECTION (continued)

Unity Gain Bandwidth BW MHz

TJ = 25°C – 4.0 –

TJ = –25° to +85°C – – 5.5

Voltage Feedback Input Line Regulation (VCC = 10 to 15 V) V

FBline–reg

–10 – 10 mV

Output Current mA

Sink (V

E/A out

= 1.5 V , VFB = 2.7 V)

TA = –25° to +85°C

I

Sink

2.0 12 –

Source (V

E/A out

= 5.0 V , VFB = 2.3 V)

TA = –25° to +85°C

I

Source

–2.0 – –0.2

Output Voltage Swing V

High State (I

E/A out (source)

= 0.5 mA, VFB = 2.3 V) V

OH

5.5 6.5 7.5

Low State (I

E/A out (sink)

= 0.33 mA, VFB = 2.7 V) V

OL

– 1.0 1.1

REFERENCE SECTION

Reference Output Voltage (VCC = 10 to 15 V) V

ref

2.4 2.5 2.6 V

Reference Current Range (I

ref

= V

ref/Rref

, R = 5.0 k to 25 kΩ) I

ref

–500 – –100 µA

Reference Voltage Over I

ref

Range ∆V

ref

–40 – 40 mV

OSCILLATOR AND SYNCHRONIZATION SECTION

Frequency f

OSC

kHz

TA = 0° to +70°C 44.5 48 51.5

TA = –25° to +85°C 44 – 52

Frequency Change with Voltage (VCC = 10 to 15 V) ∆f

OSC

/∆V – 0.05 – %/V

Frequency Change with Temperature (TA = –25° to +85°C) ∆f

OSC

/∆T – 0.05 – %/°C

Oscillator Voltage Swing (Peak–to–Peak) V

OSC(pp)

1.65 1.8 1.95 V

Ratio Charge Current/Reference Current I

charge/Iref

–

TA = 0° to +70°C (VCT = 2.0 V) 0.375 0.4 0.425

TA = –25° to +85°C 0.37 – 0.43

Fixed Maximum Duty Cycle = I

discharge

/(I

discharge

+ I

charge

) D 78 80 82 %

Ratio Standby Discharge Current versus IR F

Stby

(Note 6) I

disch–Stby

/ –

TA = 0° to +70°C IR F

Stby

0.46 0.53 0.6

TA = –25° to +85°C (Note 8) 0.43 – 0.63

VR F

Stby

(IR F

Stby

= 100 µA) VR F

Stby

2.4 2.5 2.6 V

Frequency in Standby Mode (RF

Stby

(Pin 15) = 25 kΩ) F

Stby

18 21 24 kHz

Current Range IR F

Stby

–200 – –50 µA

Synchronization Input Threshold Voltage (Note 7) V

inthH

V

inthL

3.2

0.45

3.7

0.7

4.3

0.9

V

Synchronization Input Current I

Sync–in

–5.0 – 0 µA

Minimum Synchronization Pulse Width (Note 8) T

Sync

– – 0.5 µs

UNDERVOLTAGE LOCKOUT SECTION

Startup Threshold V

stup–th

13.6 14.5 15.4 V

Output Disable Voltage After Threshold T urn–On (UVLO 1) V

disable1

V

TA = 0° to +70°C 8.6 9.0 9.4

TA = –25° to +85°C 8.3 – 9.6

Reference Disable Voltage After Threshold T urn–On (UVLO 2) V

disable2

7.0 7.5 8.0 V

NOTES: 13. Adjust VCC above the startup threshold before setting to 12 V.

14. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

16. Standby is disabled for VR P

Stby

< 25 mV typical.

17. If not used, Synchronization input must be connected to Ground.

18. Synchronization Pulse Width must be shorter than T

OSC

= 1/f

OSC

.

Page 4

MC44603

4

MOTOROLA ANALOG IC DEVICE DATA

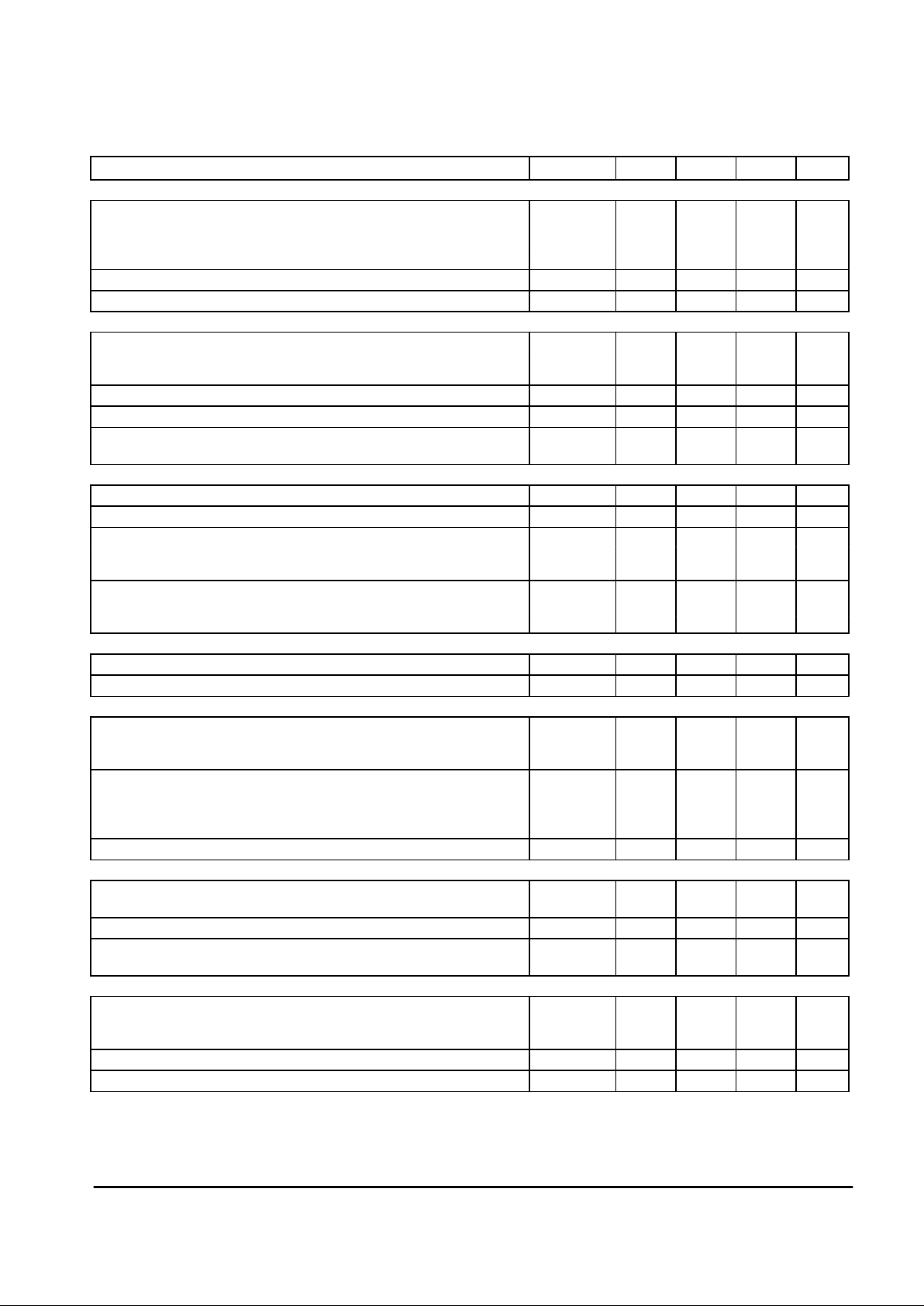

ELECTRICAL CHARACTERISTICS (continued) (V

CC

and VC = 12 V , [Note 3], R

ref

= 10 kΩ, CT = 820 pF , for typical values TA = 25°C,

for min/max values TA = –25° to +85°C [Note 4], unless otherwise noted.)

Characteristic

Symbol Min Typ Max Unit

DEMAGNETIZATION DETECTION SECTION (Note 9)

Demagnetization Detect Input

Demagnetization Comparator Threshold (V

Pin 9

Decreasing) V

demag–th

50 65 80 mV

Propagation Delay (Input to Output, Low to High) – – 0.25 – µs

Input Bias Current (V

demag

= 65 mV) I

demag–lb

–0.5 – – µA

Negative Clamp Level (I

demag

= –2.0 mA) C

L(neg)

– –0.38 – V

Positive Clamp Level (I

demag

= 2.0 mA) C

L(pos)

– 0.72 – V

SOFT–START SECTION (Note 11)

Ratio Charge Current/I

ref

I

ss(ch)/Iref

–

TA = 0° to +70°C 0.37 0.4 0.43

TA = –25° to +85°C 0.36 – 0.44

Discharge Current (V

soft–start

= 1.0 V) I

discharge

1.5 5.0 – mA

Clamp Level V

ss(CL)

2.2 2.4 2.6 V

Duty Cycle (R

soft–start

= 12 kΩ)

Duty Cycle (V

soft–start (Pin 11)

= 0.1 V)

D

soft–start 12k

D

soft–start

36

–

42

–

49

0

%

OVERVOLTAGE SECTION

Protection Threshold Level on V

OVP

V

OVP–th

2.42 2.5 2.58 V

Propagation Delay (V

OVP

> 2.58 V to V

out

Low) 1.0 – 3.0 µs

Protection Level on V

CC

VCC

prot

V

TA = 0° to +70°C 16.1 17 17.9

TA = –25° to +85°C 15.9 – 18.1

Input Resistance – kΩ

TA = 0° to +70°C 1.5 2.0 3.0

TA = –25° to +85°C 1.4 – 3.4

FOLDBACK SECTION (Note 10)

Current Sense Voltage Threshold (V

foldback (Pin 5)

= 0.9 V) V

CS–th

0.86 0.89 0.9 V

Foldback Input Bias Current (V

foldback (Pin 5)

= 0 V) I

foldback–lb

–6.0 –2.0 – µA

STANDBY SECTION

Ratio IR P

Stby/Iref

IR P

Stby/Iref

–

TA = 0° to +70°C 0.37 0.4 0.43

TA = –25° to +85°C 0.36 – 0.44

Ratio Hysteresis (Vh Required to Return to Normal Operation from Standby

Operation)

Vh/VR P

Stby

–

TA = 0° to +70°C 1.42 1.5 1.58

TA = –25° to +85°C 1.4 – 1.6

Current Sense Voltage Threshold (VR P

Stby (Pin 12)

= 1.0 V) V

CS–Stby

0.28 0.31 0.34 V

CURRENT SENSE SECTION

Maximum Current Sense Input Threshold

(V

feedback (Pin 14)

= 2.3 V and V

foldback (Pin 6)

= 1.2 V)

V

CS–th

0.96 1.0 1.04 V

Input Bias Current I

CS–ib

–10 –2.0 – µA

Propagation Delay (Current Sense Input to Output at VTH of

MOS transistor = 3.0 V)

– – 120 200 ns

TOTAL DEVICE

Power Supply Current I

CC

mA

Startup (VCC = 13 V with VCC Increasing) – 0.3 0.45

Operating TA = –25° to +85°C (Note 3) 13 17 20

Power Supply Zener Voltage (ICC = 25 mA) V

Z

18.5 – – V

Thermal Shutdown – – 155 – °C

NOTES: 13. Adjust VCC above the startup threshold before setting to 12 V.

14. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

19. This function can be inhibited by connecting Pin 8 to Gnd. This allows a continuous current mode operation.

10. This function can be inhibited by connecting Pin 5 to VCC.

11. The MC44603 can be shut down by connecting the Soft–Start pin (Pin 11) to Ground.

Page 5

MC44603

5

MOTOROLA ANALOG IC DEVICE DATA

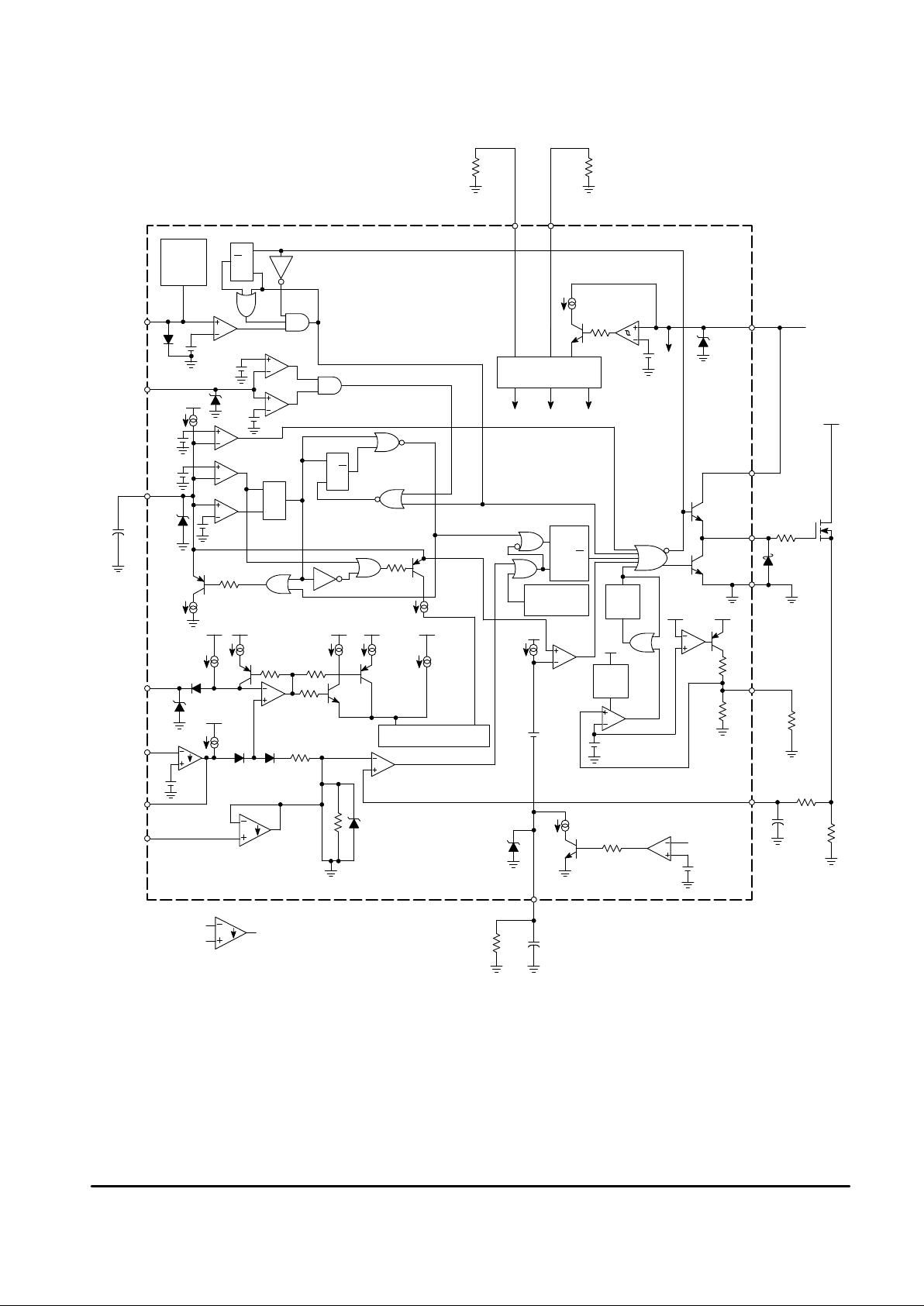

Representative Block Diagram

This device contains 243 active transistors.

S

RF

Stby

R

ref

RF

Stby

V

ref

15 16

Reference

Block

V

refIref

+

V

CC

V

CC

1

14.5 V/7.5 V

V

aux

18.0 V

To Powe

r

Transform

e

V

C

2

Output

3

Gnd

4

OVP

6

Current

Sense Input

7

V

CC

V

ref

V

OVP

Out

2.0

µ

s

Delay

V

ref

5.0

µ

s

Delay

+

2.5 V

R

OVP

11.6 k

2.0 k

V

CC

+

9.0 V

SS/D

max

/VM

2.4 V

R

SS

C

SS

11

1.0 V

Demag

Detect

8

Sync

Input

9

V

ref

+

+

+

65 mV

3.7 V

1.0 V

0.4 I

ref

C

T

10

R

Pwr Stby

12

Feed–

back

14

Compen–

sation

13

Foldback

Input

5

1.6 V

3.6 V

+

C

T

0.7 V

V

Demag Out

Synchro

V

OSC prot

0.4 I

ref

V

refVref

V

refVref

V

ref

0.4 I

ref

0.6 I

ref

0.8 I

ref

0.25

IF

Stby

0.2 I

ref

I

Discharge

I

Discharge/2

Current Mirror X2

0.4 I

ref

V

ref

2R

V

CC

1.0 mA

Error Amplifier

R

Q

S

R

Q

S

R

Q

S

R

Q

= Sink only

= Positive True Logic

+

2.5 V

Thermal

Shutdown

IF

Stby

UVLO2

V

OSC

+

1.6 V

UVLO1

5.0 mA

Negative

Active

Clamp

Page 6

MC44603

6

MOTOROLA ANALOG IC DEVICE DATA

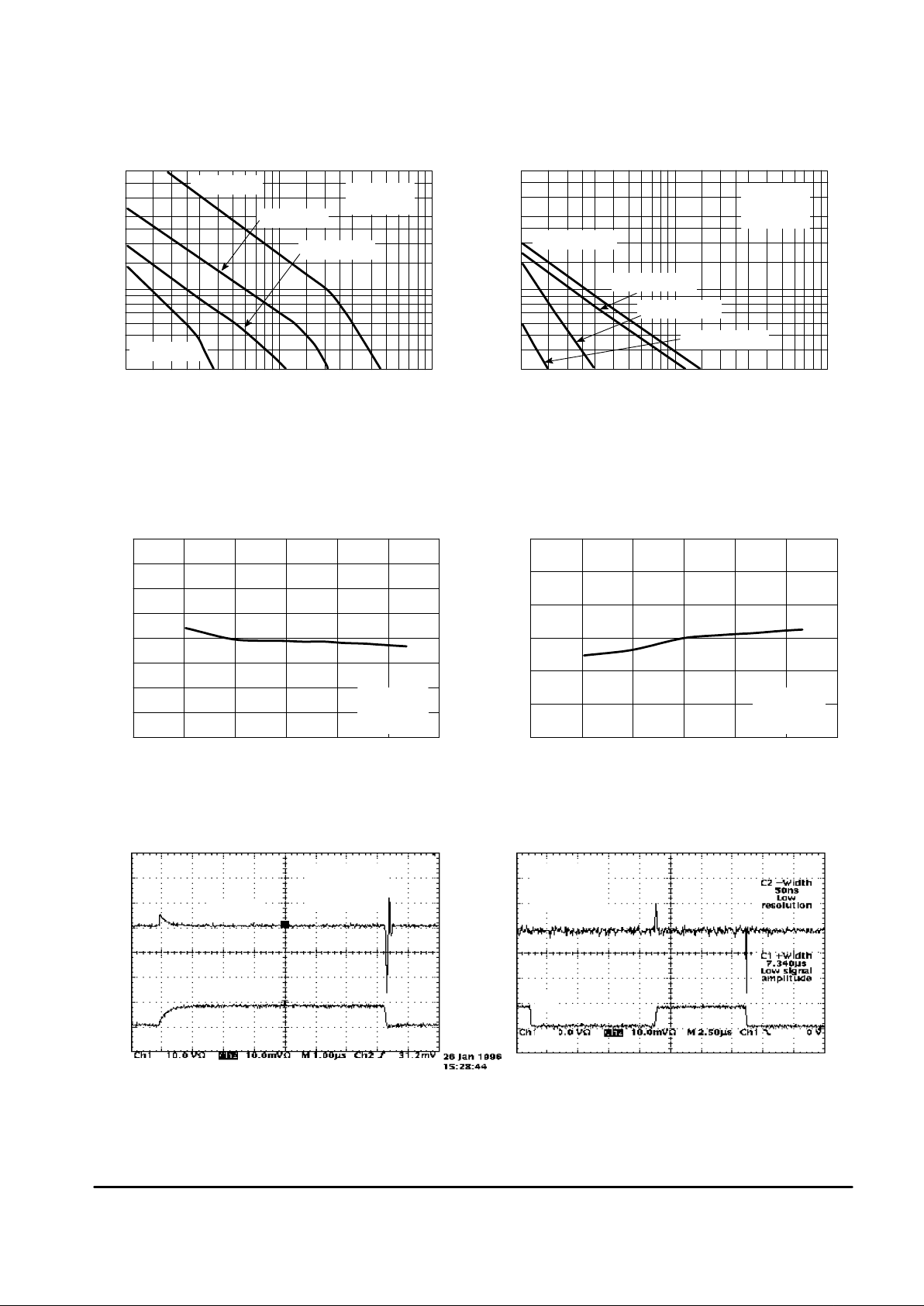

Figure 1. Timing Resistor versus

Oscillator Frequency

Figure 2. Standby Mode Timing Capacitor

versus Oscillator Frequency

10 k

10000

C

T

, TIMING CAPACIT OR (pF)

f

OSC

, Oscillator Frequency (Hz)

VCC = 16 V

TA = 25

°

C

R

ref

= 10 k

10 k

100

R

ref

, TIMING RESISTANCE (k )

Ω

f

OSC

, Oscillator Frequency (Hz)

VCC = 16 V

TA = 25

°

C

100010

3003.0

100 k100 k 1.0 Meg1.0 Meg

CT = 100 pF

CT = 500 pF

CT = 2200 pF

CT = 1000 pF

RF

Stby

= 2.0 k

RF

Stby

= 5.0 k

RF

Stby

= 27 k

RF

Stby

= 100 k

TA, AMBIENT TEMPERATURE (°C)

Figure 3. Oscillator Frequency

versus Temperature

TA, AMBIENT TEMPERATURE (°C)

Figure 4. Ratio Charge Current/Reference

Current versus Temperature

52

51

48

47

46

45

44

–50 –25 0 25 50 75 100

VCC = 12 V

R

ref

= 10 k

CT = 820 pF

0.43

0.41

0.40

0.37

0.38

–50 –25 0 25 50 75 100

0.39

f

OSC

, OSCILLATOR FREQUENCY (kHz)

= RATIO CHARGE CURRENT/I

charge

/I

ref

REFERENCE CURRENT

49

50

0.42

VCC = 12 V

R

ref

= 10 k

CT = 820 pF

Figure 5. Output Waveform Figure 6. Output Cross Conduction

V

O

I

CC

VCC = 12 V

CL = 2200 pF

TA = 25

°

C

Current

Voltage

Current

Voltage

1.0

µ

s/Div1.0 µs/Div

VCC = 12 V

CL = 2200 pF

TA = 25

°

C

600

400

–200

–400

–600

–800

–1000

I

O

, OUTPUT CURRENT (mA)

0

200

70

60

30

20

10

0

–10

V

O

, OUTPUT DRIVE VOL TAGE (V)

40

50

70

60

30

20

10

0

–10

40

50

300

200

–10

0

–20

0

–30

0

–40

0

–50

0

0

100

V

O

, OUTPUT DRIVE VOL TAGE (V)

Page 7

MC44603

7

MOTOROLA ANALOG IC DEVICE DATA

500

425

400

375

350

325

300

–50 –25 0 25 50 75 100

I

source

, OUTPUT SOURCE CURRENT (mA)TA, AMBIENT TEMPERATURE (

°

C)

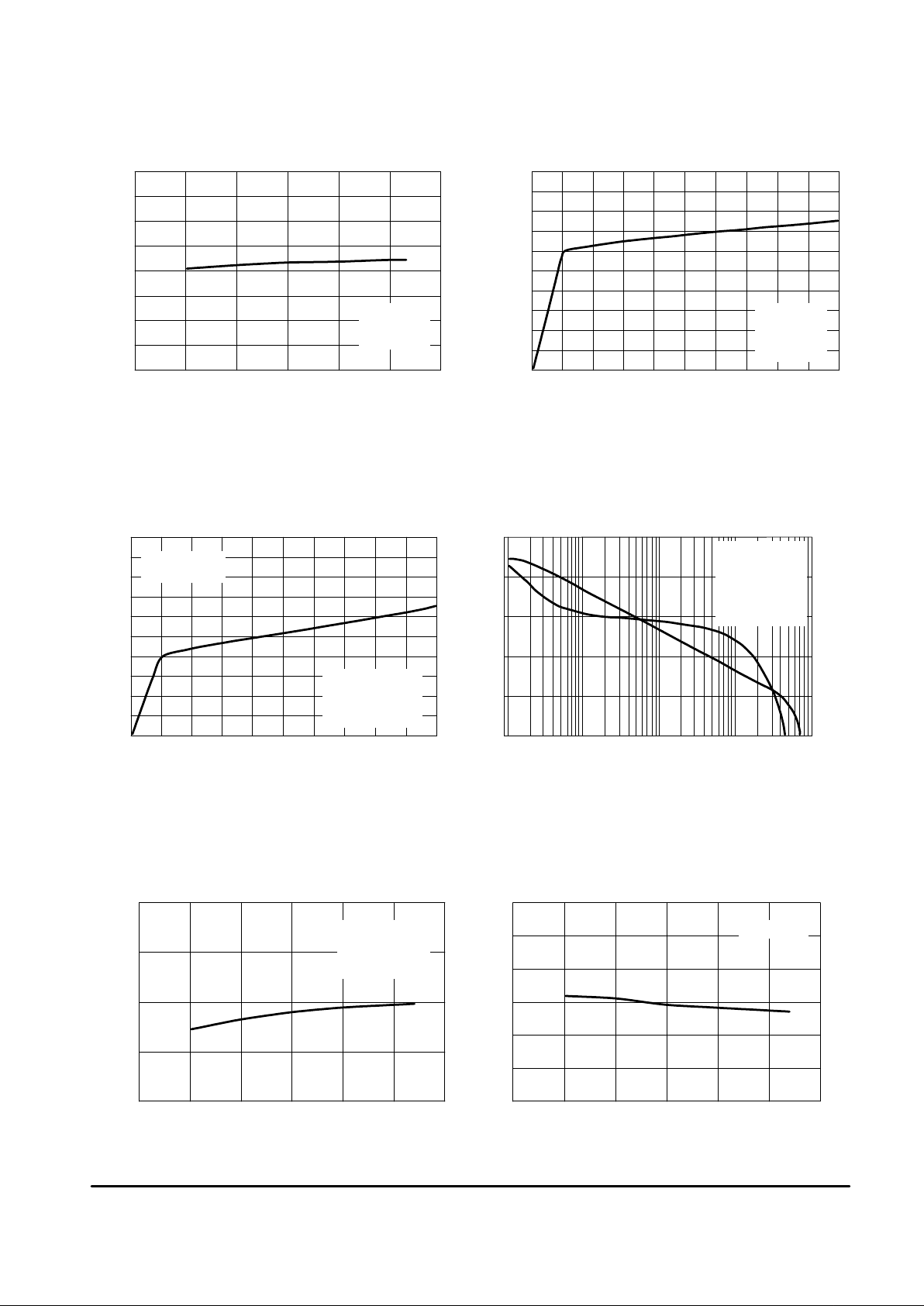

Figure 7. Oscillator Discharge Current

versus Temperature

Figure 8. Source Output Saturation Voltage

versus Load Current

2.5

2.0

1.5

1.0

0 100 200 300 400 500

I

disch

, DISCHARGE CURRENT (

µ

A)

V

OH

, SOURCE OUTPUT SATURATION VOLT AGE (V)

450

475

VCC = 12 V

R

ref

= 10 k

CT = 820 pF

VCC = 12 V

R

ref

= 10 k

CT = 820 pF

TA = 25

°

C

f, FREQUENCY (kHz)

Figure 9. Sink Output Saturation Voltage

versus Sink Current

I

sink

, SINK OUTPUT CURRENT (mA)

Figure 10. Error Amplifier Gain and Phase

versus Frequency

1.6

0

0 100

802.0

1.2

0.8

0.4

200 300 400 500

V

OL

, SINK OUTPUT SA TURATION VOLTAGE (V)

GAIN (dB)

60

40

20

0

–20

1001.0 10 1000

140

50

–40

PHASE (DEGREES)

VCC = 12 V

G = 10

Vin = 30 mV

VO = 2.0 to 4.0 V

RL = 100 k

TA = 25

°

C

TA = 25°C

VCC = 12 V

80

µ

s Pulsed Load

120 Hz Rate

Sink Saturation

(Load to VCC)

Figure 11. Voltage Feedback Input

versus Temperature

Figure 12. Demag Comparator Threshold

versus Temperature

2.60

2.55

2.40

2.45

–50 –25 0 25 50 75 100

2.50

TA, AMBIENT TEMPERATURE (

°

C)

V

FB

, VOLTAGE FEEDBACK INPUT (V)

80

75

70

65

60

50

–50 –25 0 25 50 75 100

TA, AMBIENT TEMPERATURE (

°

C)

V

demag–th

, DEMAG COMPARATOR THRESHOLD (mV)

55

VCC = 12 V

G = 10

VO = 2.0 to 4.0 V

RL = 100 k

VCC = 12 V

Page 8

MC44603

8

MOTOROLA ANALOG IC DEVICE DATA

0

0

100

R

JA

, THERMAL RESISTANCE JUNCTION–TO–AIR ( C/W)

θ

80

60

40

20

10 20 30 40 50

L, LENGTH OF COPPER (mm)

°

P

D

, MAXIMUM POWER DISSIPATION (W)

5.0

4.0

3.0

2.0

1.0

0

Graphs represent symmetrical layout

3.0 mm

Printed circuit board heatsink example

L

L

2.0 oz

Copper

P

D(max)

for TA = 70°C

R

θ

JA

3.2

3.1

2.8

2.9

3.0

–50 –25 0 25 50 75 100

TA, AMBIENT TEMPERATURE (

°

C)

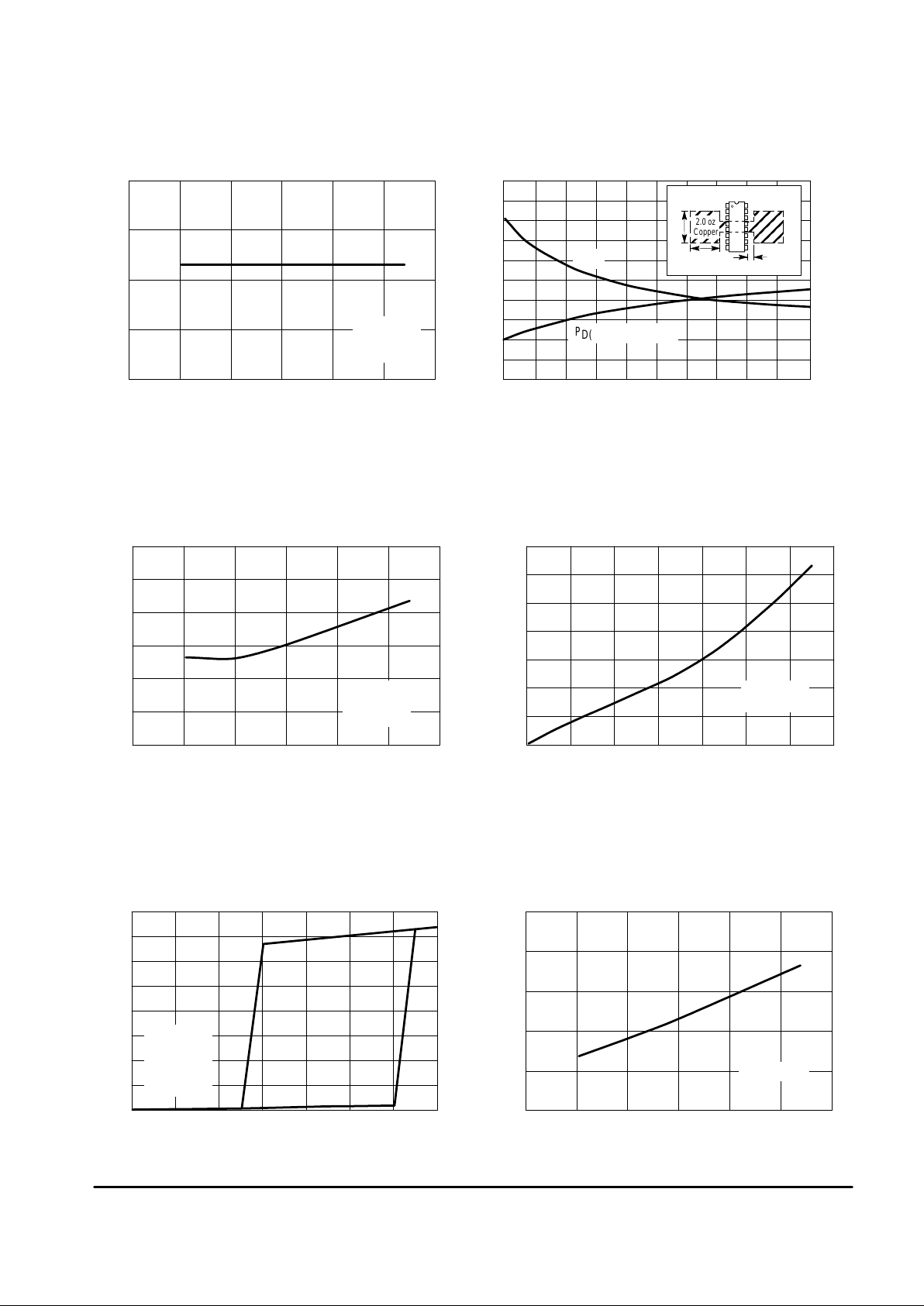

Figure 13. Current Sense Gain

versus Temperature

Figure 14. Thermal Resistance and Maximum

Power Dissipation versus P.C.B. Copper Length

A

VCS

, CURRENT SENSE GAIN

VCC = 12 V

R

ref

= 10 k

CT = 820 pF

VCC, SUPPLY VOLTAGE (V)

Figure 15. Propagation Delay Current Sense

Input to Output versus Temperature

TA, AMBIENT TEMPERATURE (°C)

Figure 16. Startup Current versus V

CC

PROPAGATION DELAY (ns)

STAR TUP CURRENT (mA)

0

4.00 2.0 6.0

140

120

100

80

–50 –25 0 25 50 75 100

0.35

0.30

0.25

0.20

0.15

0.10

0.05

8.0 10 12 14

VCC = 12 V

R

ref

= 10 k

CT = 820 pF

R

ref

= 10 k

CT = 820 pF

Figure 17. Supply Current versus

Supply Voltage

Figure 18. Power Supply Zener Voltage

versus Temperature

16

0

VCC, SUPPLY VOLTAGE (V)

21.0

20.5

20.0

19.5

19.0

–50 –25 0 25 50 75 100

TA, AMBIENT TEMPERATURE (

°

C)

I

CC

, SUPPLY CURRENT (mA)

V

Z

, ZENER VOLTAGE (V)

14

12

10

8.0

6.0

4.0

2.0

2.0 4.0 6.0 8.0 10 12 14 16

21.5

TA = 25°C

R

ref

= 10 k

CT = 820 pF

VFB = 0 V

VCS = 0 V

ICC = 25 mA

Page 9

MC44603

9

MOTOROLA ANALOG IC DEVICE DATA

–50 –25 0 25 50 75 100

TA, AMBIENT TEMPERATURE (

°

C)

Figure 19. Startup Threshold Voltage

versus Temperature

Figure 20. Disable Voltage After Threshold

Turn–On (UVLO1) versus Temperature

–50 –25 0 25 50 75 100

TA, AMBIENT TEMPERATURE (

°

C)

V

stup–th

, STARTUP THRESHOLD VOLTAGE (V)

V

disable1

, UVLO1 (V)

15.5

15.0

14.5

14.0

13.5

9.50

9.00

8.55

8.50

9.25

VCC Increasing VCC Decreasing

TA, AMBIENT TEMPERATURE (°C)

Figure 21. Disable Voltage After Threshold

Turn–On (UVLO2) versus Temperature

TA, AMBIENT TEMPERATURE (°C)

Figure 22. Protection Threshold Level on

V

OVP

versus Temperature

2.608.0

2.30

V

disable2

, UVLO2 (V)

–50 –25 0 25 50 75 100

7.8

7.6

7.4

7.2

7.0

6.8

2.55

2.50

2.45

2.40

2.35

–50 –25 0 25 50 75 100

V

OVP–th

, PROTECTION THRESHOLD LEVEL (V)

VCC Decreasing

VCC = 12 V

Figure 23. Protection Level on V

CC

versus Temperature

Figure 24. Propagation Delay (V

OVP

> 2.58 V

to V

out

Low) versus Temperature

18

TA, AMBIENT TEMPERATURE (

°

C)

3.0

2.0

1.5

1.0

–50 –25 0 25 50 75 100

TA, AMBIENT TEMPERATURE (°C)

2.517.5

17

16.5

16

–50 –25 0 25 50 75 100

V

CC prot

, PROTECTION LEVEL (V)

µ

PROPAGATION DELAY ( s)

R

ref

= 10 k

CT = 820 pF

Pin 6 Open

VCC = 12 V

R

ref

= 10 k

CT = 820 pF

Page 10

MC44603

10

MOTOROLA ANALOG IC DEVICE DATA

–50 –25 0 25 50 75 100

TA, AMBIENT TEMPERATURE (

°

C)

Figure 25. Standby Reference Current

versus Temperature

Figure 26. Current Sense Voltage Threshold

Standby Mode versus Temperature

–50 –25 0 25 50 75 100

TA, AMBIENT TEMPERATURE (

°

C)

270

260

250

240

230

0.33

0.32

0.31

0.30

µ

IA)

V

CS–stby

, CURRENT SENSE THRESHOLD

265

255

245

235

STANDBY MODE (V)

VR P

Stdby (Pin 12)

Voltage Increasing

VCC = 12 V

R

ref

= 10 k

CT = 820 pF

Pin 12 Clamped

at 1.0 V

R P Stby

, STANDBY REFERENCE CURRENT (

PIN FUNCTION DESCRIPTION

Pin Name Description

1 V

CC

This pin is the positive supply of the IC. The operating voltage range after startup is 9.0 to 14.5 V .

2 V

C

The output high state (VOH) is set by the voltage applied to this pin. With a separate connection to the

power source, it can reduce the effects of switching noise on the control circuitry .

3 Output Peak currents up to 750 mA can be sourced or sunk, suitable for driving either MOSFET or Bipolar

transistors. This output pin must be shunted by a Schottky diode, 1N5819 or equivalent.

4 Gnd The ground pin is a single return, typically connected back to the power source; it is used as control and

power ground.

5 Foldback Input The foldback function provides overload protection. Feeding the foldback input with a portion of the V

CC

voltage (1.0 V max) establishes on the system control loop a foldback characteristic allowing a smoother

startup and sharper overload protection. Above 1.0 V the foldback input is inactive.

6 Overvoltage

Protection

When the overvoltage protection pin receives a voltage greater than 17 V , the device is disabled and

requires a complete restart sequence. The overvoltage level is programmable.

7 Current Sense

Input

A voltage proportional to the current flowing into the power switch is connected to this input. The PWM

latch uses this information to terminate the conduction of the output buffer when working in a current

mode of operation. A maximum level of 1.0 V allows either current or voltage mode operation.

8 Demagnetization

Detection

A voltage delivered by an auxiliary transformer winding provides to the demagnetization pin an indication

of the magnetization state of the flyback transformer. A zero voltage detection corresponds to complete

core saturation. The demagnetization detection ensures a discontinuous mode of operation. This

function can be inhibited by connecting Pin 8 to Gnd.

9 Synchronization

Input

The synchronization input pin can be activated with either a negative pulse going from a level between

0.7 V and 3.7 V to Gnd or a positive pulse going from a level between 0.7 V and 3.7 V up to a level

higher than 3.7 V . The oscillator runs free when Pin 9 is connected to Gnd.

10 C

T

The normal mode oscillator frequency is programmed by the capacitor CT choice together with the R

ref

resistance value. CT, connected between Pin 10 and Gnd, generates the oscillator sawtooth.

11 Soft–Start/D

max

/

Voltage–Mode

A capacitor, resistor or a voltage source connected to this pin limits the switching duty–cycle. This pin

can be used as a voltage mode control input. By connecting Pin 11 to Ground, the MC44603 can be

shut down.

12 RP

Standby

A voltage level applied to the RP

Standby

pin determines the output power level at which the oscillator will

turn into the reduced frequency mode of operation (i.e. standby mode). An internal hysteresis

comparator allows to return in the normal mode at a higher output power level.

13 E/A Out The error amplifier output is made available for loop compensation.

14 Voltage Feedback This is the inverting input of the Error Amplifier. It can be connected to the switching power supply output

through an optical (or other) feedback loop.

15 RF

Standby

The reduced frequency or standby frequency programming is made by the RF

Standby

resistance choice.

16 R

ref

R

ref

sets the internal reference current. The internal reference current ranges from 100 µA to 500 µA.

This requires that 5.0 kΩ ≤ R

ref

≤ 25 kΩ.

Page 11

MC44603

11

MOTOROLA ANALOG IC DEVICE DATA

Figure 27. Starting Behavior and Overvoltage Management

Figure 28. Demagnetization

VCC

prot

V

stup–th

V

disable1

V

disable2

V

ref

V

CC

UVLO1

V

Pin 11

(Soft–Start)

V

OVP Out

Output

I

CC

17 mA

0.3 mA

Startup Restart

>2.0

µ

s

No–Take Over Loop Failure

Normal Mode

V

Demag In

Output

(Pin 3)

V

Demag Out

V

Demag In

V

Demag Out

Demagnetization

Management

Oscillator

Buffer Output

Page 12

MC44603

12

MOTOROLA ANALOG IC DEVICE DATA

Figure 29. Switching Off Behavior

Figure 30. Oscillator

V

CC

V

stup–th

V

disable1

V

disable2

V

ref

UVLO1

V

Pin 11

(Soft–Start)

Output

(Pin 3)

I

CC

17 mA

0.3 mA

V

CT

1.0 V

V

Stby

V

Demag Out

V

OSC

V

OSC prot

V

Demag Out

Synchronization

Input

V

OSC prot

V

OSC

V

Stby

C

T

1.6 V

3.6 V

Oscillator

Page 13

MC44603

13

MOTOROLA ANALOG IC DEVICE DATA

Figure 31. Soft–Start & D

max

3.6 V

1.6 V

V

CT

VCT low

V

ref

Output

(Pin 3)

V

CSS

+ 1.6 V

Soft–Start

Internal Clamp

External Clamp

V

OSC

OPERA TING DESCRIPTION

Error Amplifier

A fully compensated Error Amplifier with access to the

inverting input and output is provided. It features a typical dc

voltage gain of 70 dB. The noninverting input is internally

biased at 2.5 V and is not pinned out. The converter output

voltage is typically divided down and monitored by the

inverting input. The maximum input bias current with the

inverting input at 2.5 V is –2.0 µA. This can cause an output

voltage error that is equal to the product of the input bias

current and the equivalent input divider source resistance.

The Error Amp output (Pin 13) is provided for external loop

compensation. The output voltage is offset by two diode

drops (≈ 1.4 V) and divided by three before it connects to the

inverting input of the Current Sense Comparator. This

guarantees that no drive pulses appear at the Output (Pin 3)

when Pin 13 is at its lowest state (VOL). The Error Amp

minimum feedback resistance is limited by the amplifier’s

minimum source current (0.2 mA) and the required output

voltage (VOH) to reach the current sense comparator’s 1.0 V

clamp level:

R

f(min)

[

3.0 (1.0 V))1.4 V

0.2 mA

+

22 k

W

+

1.0 mA

2.5 V

Compensation

R

FB

C

f

R1

R2

From Power Supply Output

R

f

13

Voltage

Feedback

Input

Error

Amplifier

2R

R

Current Sense

Comparator

Gnd

4

Foldback

Input

5

14

Figure 32. Error Amplifier Compensation

Current Sense Comparator and PWM Latch

The MC44603 can operate as a current mode controller or

as a voltage mode controller. In current mode operation, the

MC44603 uses the current sense comparator. The output

switch conduction is initiated by the oscillator and terminated

when the peak inductor current reaches the threshold level

Page 14

MC44603

14

MOTOROLA ANALOG IC DEVICE DATA

established by the Error Amplifier output (Pin 13). Thus, the

error signal controls the peak inductor current on a

cycle–by–cycle basis. The Current Sense Comparator PWM

Latch ensures that only a single pulse appears at the Source

Output during the appropriate oscillator cycle.

The inductor current is converted to a voltage by inserting

the ground referenced sense resistor RS in series with the

power switch Q1.

This voltage is monitored by the Current Sense Input

(Pin 7) and compared to a level derived from the Error Amp

output. The peak inductor current under normal operating

conditions is controlled by the voltage at Pin 13 where:

Ipk[

V

(Pin 13) – 1.4 V

3R

S

The Current Sense Comparator threshold is internally

clamped to 1.0 V. Therefore, the maximum peak switch

current is:

I

pk(max)

[

1.0 V

R

S

Figure 33. Output Totem Pole

R

RSQ

UVLO

V

OSC prot

V

Demag Out

Thermal

Protection

PWM

Latch

Current Sense

Comparator

Substrate

Current

Sense

14

3

7

C

R

S

R

R3

Q1

V

in

V

C

R2

1N5819

Oscillator

The oscillator is a very accurate sawtooth generator that

can work either in free mode or in synchronization mode. In

this second mode, the oscillator stops in the low state and

waits for a demagnetization or a synchronization pulse to

start a new charging cycle.

• The Sawtooth Generation:

In the steady state, the oscillator voltage varies between

about 1.6 V and 3.6 V.

The sawtooth is obtained by charging and discharging an

external capacitor CT (Pin 10), using two distinct current

sources = I

charge

and I

discharge

. In fact, CT is permanently

connected to the charging current source (0.4 I

ref

) and so,

the discharge current source has to be higher than the

charge current to be able to decrease the CT voltage (refer

to Figure 35).

This condition is performed, its value being (2.0 I

ref

) in

normal working and (0.4 I

ref

+ 0.5 IF

Stby

in standby mode).

Figure 34. Oscillator

10

C

T

1.0 V

1.6 V

3.6 V

V

ref

0.4 I

ref

C

VOS prot

C

OSC Low

C

OSC High

C

OSC Regul

Synchro

10

I

Regul

R

S

Disch

Q

CT < 1.6 V

V

OSC prot

R

S

L

OSC

Q

V

OSC

V

Demag

Out

01

I

Discharge

Discharge

Figure 35. Simplified Block Oscillator

V

ref

C

T

10

I

Charge

0.4 I

ref

01

0: Discharge Phase

1: Charge Phase

C

OSC Regul

I

Regul

1.6 V

I

Discharge

Two comparators are used to generate the sawtooth. They

compare the CT voltage to the oscillator valley (1.6 V) and

peak reference (3.6 V) values. A latch (L

disch

) memorizes the

oscillator state.

In addition to the charge and discharge cycles, a third

state can exist. This phase can be produced when, at the end

of the discharge phase, the oscillator has to wait for a

synchronization or demagnetization pulse before restarting.

During this delay, the CT voltage must remain equal to the

oscillator valley value (]1.6 V). So, a third regulated current

source I

Regul

controlled by C

OSC Regul

, is connected to CT in

order to perfectly compensate the (0.4 I

ref

) current source

that permanently supplies CT.

The maximum duty cycle is 80%. Indeed, the on–time is

allowed only during the oscillator capacitor charge.

Consequently:

T

charge

= CT x ∆V/I

charge

T

discharge

= CT x ∆V/I

discharge

where:

T

charge

is the oscillator charge time

∆V is the oscillator peak–to–peak value

I

charge

is the oscillator charge current

and

T

discharge

is the oscillator discharge time

I

discharge

is the oscillator discharge current

Page 15

MC44603

15

MOTOROLA ANALOG IC DEVICE DATA

So, as fS = 1 /(T

charge

+ T

discharge

) when the Regul

arrangement is not activated, the operating frequency can be

obtained from the graph in Figure 1.

NOTE: The output is disabled by the signal V

OSC prot

when

VCT is lower than 1.0 V (refer to Figure 30).

Synchronization and Demagnetization Blocks

To enable the output, the L

OSC

latch complementary

output must be low. Reset is activated by the L

disch

output

during the discharge phase. T o restart, the L

OSC

has to be set

(refer to Figure 34). To perform this, the demagnetization

signal and the synchronization must be low.

• Synchronization:

The synchronization block consists of two comparators

that compare the synchronization signal (external) to 0.7 and

3.7 V (typical values). The comparators’ outputs are

connected to the input of an AND gate so that the final output

of the block should be :

– high when 0.7 < SYNC < 3.7 V

– low in the other cases.

As a low level is necessary to enable the output,

synchronized low level pulses have to be generated on the

output of the synchronization block. If synchronization is not

required, the Pin 9 must be connected to the ground.

Figure 36. Synchronization

Oscillator

Output Buffer

3.7 V

0.7 V

9

Sync

• Demagnetization:

In flyback applications, a good means to detect magnetic

saturation of the transformer core, or demagnetization,

consists in using the auxiliary winding voltage. This voltage is:

– negative during the on–time,

– positive during the off–time,

– equal to zero for the dead–time with generally some

– ringing (refer to Figure 37).

That is why, the MC44603 demagnetization detection

consists of a comparator that can compare the auxiliary

winding voltage to a reference that is typically equal to

65 mV.

Figure 37. Demagnetization Detection

V

Pin 8

0.75 V

65 mV

–0.33 V

Zero Current

Detection

On–Time Off–Time Dead–Time

A diode D has been incorporated to clamp the positive

applied voltages while an active clamping system limits the

negative voltages to typically –0.33 V. This negative clamp

level is sufficient to avoid the substrate diode switching on.

In addition to the comparator, a latch system has been

incorporated in order to keep the demagnetization block

output level low as soon as a voltage lower than 65 mV is

detected and as long as a new restart is produced (high level

on the output) (refer to Figure 38). This process prevents

ringing on the signal at Pin 8 from disrupting the

demagnetization detection. This results in a very accurate

demagnetization detection.

The demagnetization block output is also directly

connected to the output, disabling it during the

demagnetization phase (refer to Figure 33).

NOTE: The demagnetization detection can be inhibited by

connecting Pin 8 to the ground.

Figure 38. Demagnetization Block

C Dem

Oscillator Output

Buffer

RSQ

Demag

V

CC

Negative Active

Clamping System

8

D

65 mV

V

Demag Out

Standby

• Power Losses in a Classical Flyback Structure

Figure 39. Power Losses in a Classical

Flyback Structure

V

in

R

ICL

AC Line

+

R

startup

V

CC

Clamping

Network

Snubber

MC44603

R

S

+

In a classical flyback (as depicted in Figure 39), the

standby losses mainly consist of the energy waste due to:

– the startup resistor R

startup

P

startup

– the consumption of the IC and

– the power switch control P

control

– the inrush current limitation resistor R

ICL

P

ICL

– the switching losses in the power switch P

SW

– the snubber and clamping network P

SN–CLN

P

startup

is nearly constant and is equal to:

ǒ

(Vin–VCC)2ń

R

startup

Ǔ

Page 16

MC44603

16

MOTOROLA ANALOG IC DEVICE DATA

P

ICL

only depends on the current drawn from the mains.

Losses can be considered constant. This waste of energy

decreases when the standby losses are reduced.

P

control

increases when the oscillator frequency is

increased (each switching requires some energy to turn on

the power switch).

PSW and P

SN–CLN

are proportional to the switching

frequency.

Consequently, standby losses can be minimized by

decreasing the switching frequency as much as possible.

The MC44603 was designed to operate at a standby

frequency lower than the normal working one.

• Standby Power Calculations with MC44603

During a switching period, the energy drawn by the

transformer during the on–time to be transferred to the output

during the off–time, is equal to:

E

+

1

2

xLxI

pk

2

where:

– L is the transformer primary inductor,

– lpk is the inductor peak current.

Input power is labelled Pin:

Pin+

0.5xLxI

pk

2

xf

S

where fS is the normal working switching frequency.

Also,

Ipk+

V

CS

R

S

where RS is the resistor used to measure the power switch

current.

Thus, the input power is proportional to V

CS

2

(VCS being

the internal current sense comparator input).

That is why the standby detection is performed by creating

a VCS threshold. An internal current source (0.4 x I

ref

) sets

the threshold level by connecting a resistor to Pin 12.

As depicted in Figure 40, the standby comparator

noninverting input voltage is typically equal to (3.0 x VCS + VF)

while the inverter input value is (VR P

Stby

+ VF).

Figure 40. Standby

C

Stby

Current Mirror X2

RP

Stby

ER

AmpOut

0.4 I

ref

0.6 I

ref

0

1

2R

1R

C. S. Comparator

0.8 I

ref

0.25

IF

Stby

V

refVref

V

refVref

V

ref

0.2 I

ref

Oscillator

Discharge

Current

10

I

Discharge/2IDischarge

12

13

The VCS threshold level is typically equal to

[(V

R P Stby

)/3] and if the corresponding power threshold is

labelled P

thL

:

P

thL

+

0.5xLx

ǒ

V

RPStby

3.0 R

S

Ǔ

2

xf

S

And as:

V

RPStby

+

R

PStby

x0.4xI

ref

+

R

RPStby

x0.4x

V

ref

R

ref

R

PStby

+

10.6 x RSxR

ref

V

ref

x

P

thL

Lxf

S

Ǹ

Thus, when the power drawn by the converter decreases,

VCS decreases and when VCS becomes lower than [V

CS–th

x (VR P

Stby

)/3], the standby mode is activated. This results in

an oscillator discharge current reduction in order to increase

the oscillator period and to diminish the switching frequency.

As it is represented in Figure 40, the (0.8 x I

ref

) current

source is disconnected and is replaced by a lower value one

(0.25 x IF

Stby

).

Where: IF

Stby

= V

ref/RF Stby

In order to prevent undesired mode switching when power

is close to the threshold value, a hysteresis that is

proportional to VR P

Stby

is incorporated creating a second

VCS threshold level that is equal to [2.5 x (VR P

Stby

)/3]. When

the standby comparator output is high, a second current

source (0.6 x I

ref

) is connected to Pin 12.

Finally, the standby mode function can be shown

graphically in Figure 41.

Figure 41. Dynamic Mode Change

P

thL

P

thH

P

in

[(VR P

Stby

)/3] 2.5 x [(VR P

Stby

)/3]

1

V

CS

f

Stby

f

S

Normal

Working

Standby

This curve shows that there are two power threshold

levels:

– the low one:

P

thL

fixed by VR P

Stby

P

thH

+

(2.5)2xP

thL

x

f

Stby

f

S

– the high one:

P

thH

+

6.25 x P

thL

x

f

Stby

f

S

Page 17

MC44603

17

MOTOROLA ANALOG IC DEVICE DATA

Maximum Duty Cycle and Soft–Start Control

Maximum duty cycle can be limited to values less than

80% by utilizing the D

max

and soft–start control. As depicted

in Figure 42, the Pin 11 voltage is compared to the oscillator

sawtooth.

Figure 42. D

max

and Soft–Start

C

Dmax

11

Soft–Start

Capacitor

V

OSC

Oscillator

D

max

Output

Drive

Output

Control

0.4 I

ref

V

ref

2.4 VD

Z

Figure 43. Maximum Duty Cycle Control

Voltage

D

max

Pin 11

V

CT

(Pin 10)

Using the internal current source (0.4 I

ref

), the Pin 11

voltage can easily be set by connecting a resistor to this pin.

If a capacitor is connected to Pin 11, the voltage increases

from 0 to its maximum value progressively (refer to Figure

44), thereby, implementing a soft–start. The soft–start

capacitor is discharged internally when the VCC (Pin 1)

voltage drops below 9.0 V.

Figure 44. Different Possible Uses of Pin 11

Pin 11

RI

RI

R Connected to Pin 11

I = 0.4 I

ref

V

Z

V

Z

C C // R

τ

= RC

If no external component is connected to Pin 11, an

internal zener diode clamps the Pin 11 voltage to a value V

Z

that is higher than the oscillator peak value, disabling

soft–start and maximum duty cycle limitation.

Foldback

As depicted in Fgure 32, the foldback input (Pin 5) can be

used to reduce the maximum VCS value, providing foldback

protection. The foldback arrangement is a programmable

peak current limitation.

If the output load is increased, the required converter peak

current becomes higher and VCS increases until it reaches its

maximum value (normally, VCS

max

= 1.0 V).

Then, if the output load keeps on increasing, the system is

unable to supply enough energy to maintain the output

voltages in regulation. Consequently, the decreasing output

can be applied to Pin 5, in order to limit the maximum peak

current. In this way, the well known foldback characteristic

can be obtained (refer to Figure 45).

Figure 45. Foldback Characteristic

V

out

V

O

Nominal

V

CC

V

disable2

Ipk

max

New Startup

Sequence Initiated

I

out

Overload

NOTE: Foldback is disabled by connecting Pin 5 to VCC.

Overvoltage Protection

The overvoltage arrangement consists of a comparator

that compares the Pin 6 voltage to V

ref

(2.5 V) (refer to

Figure 46).

If no external component is connected to Pin 6, the

comparator noninverting input voltage is nearly equal to:

ǒ

2.0 k

W

11.6 kW)

2.0 k

W

Ǔ

xV

CC

ǒ

2.0 k

W

11.6 kW)

2.0 k

W

Ǔ

xVCCw

2.5 V

The comparator output is high when:

à

VCCw

17 V

A delay latch (2.0 µs) is incorporated in order to sense

overvoltages that last at least 2.0 µs.

If this condition is achieved, V

OVP out

, the delay latch

output, becomes high. As this level is brought back to the

input through an OR gate, V

OVP out

remains high (disabling

the IC output) until V

ref

is disabled.

Consequently, when an overvoltage longer than 2.0 µs is

detected, the output is disabled until VCC is removed and

then re–applied.

The VCC is connected after V

ref

has reached steady state

in order to limit the circuit startup consumption.

The overvoltage section is enabled 5.0 µs after the

regulator has started to allow the reference V

ref

to stabilize.

By connecting an external resistor to Pin 6, the threshold

VCC level can be changed.

Figure 46. Overvoltage Protection

V

CC

V

ref

0

T

V

OVP

External

Resistor

2.5 V

(V

ref

)

2.0 k

11.6 k

2.5 V

5.0

µ

s

V

OVP out

2.0

µ

s

(If V

OVP out

= 1.0,

the Output is Disabled)

In Out

Delay

τ

Enable

C

OVLO

6

Delay

In

Out

τ

Page 18

MC44603

18

MOTOROLA ANALOG IC DEVICE DATA

Undervoltage Lockout Section

Figure 47. VCC Management

Reference Block:

Voltage and Current

Sources Generator

(V

ref

, I

ref

, ...)

V

CC

V

ref enable

C

startup

10

1

0

V

disable2

7.5 V

Startup

14.5 V

UVLO1

(to Soft–Start)

V

disable1

9.0 V

C

UVLO1

RF

Stby

R

ref

Pin 15 Pin 16

1

As depicted in Figure 47, an undervoltage lockout has

been incorporated to garantee that the IC is fully functional

before allowing system operation.

This block particularly, produces V

ref

(Pin 16 voltage) and

I

ref

that is determined by the resistor R

ref

connected between

Pin 16 and the ground:

I

ref

+

V

ref

R

ref

where V

ref

+

2.5 V (typically)

Another resistor is connected to the Reference Block:

R

F Stby

that is used to fix the standby frequency.

In addition to this, VCC is compared to a second threshold

level that is nearly equal to 9.0 V (V

disable1

). UVLO1 is

generated to reset the maximum duty cycle and soft–start

block disabling the output stage as soon as VCC becomes

lower than V

disable1

. In this way, the circuit is reset and made

ready for the next startup, before the reference block is

disabled (refer to Figure 29). Finally, the upper limit for the

minimum normal operating voltage is 9.4 V (maximum value

of V

disable1

) and so the minimum hysteresis is 4.2 V.

((V

stup–th) min

= 13.6 V).

The large hysteresis and the low startup current of the

MC44603 make it ideally suited for off–line converter

applications where efficient bootstrap startup techniques are

required.

Page 19

MC44603

19

MOTOROLA ANALOG IC DEVICE DATA

Figure 48. 250 W Input Power Off–Line Flyback Converter with MOSFET Switch

185 Vac

to

270 Vac

RFI

Filter

R1

1.0/5.0 W

C4 ... C7

1.0 nF/1000 V

D1 ... D4

1N4007

C1

220

µ

F

R2

68 k/2.0 W

C2

220

µ

F

D5

1N4934

C17

47 nF

D7

M856

L1

1.0

µ

H

Sync

C8 2.2 nF

C9 1.0 nF

C10 1.0

µ

F

R15

5.6 k

R15

22 k

C11

1.0 nF

R17

22 k

R25

1.0 k

C12

6.8 nF

R18

27 k

R19

10 k

C13

100 nF

R12 22

R11 39

R10 10

R7 180 k

R8

15 k

R9 1.0 k

R12

27

k

C16

100 pF

C15

1.0 nF

9

10

11

12

13

14

15

16

8

7

6

5

4

3

2

1

D6

1N4148

R5

1.2 k

R6

150

R26

1.0 k

R14

0.2

R13

1.0 k

D12

MR856

MTP6N60E

C14

4.7 nF

C18

2.2 nF

L

aux

L

p

D8

MR856

D9

MR852

D10

MR852

D11

MR852

C32 220 pF

C29 220 pF

C26 220 pF

C23 220 pF

C27

1000

µ

F

C28

0.1

µ

F

C25

1000

µ

F

C24

0.1 µF

C21

1000

µ

F

C22

0.1 µF

C30

100

µ

F

C33

100 µF

C31

0.1 µF

R20

22 k

5.0 W

R24

270

R23

147.5 k

R22

2.5 k

L2

22.5

µ

H

150 V/0.6 A

30 V/2.0 A

14 V/2.0 A

7.0 V/2.0 A

C20

33 nF

C19

100 nF

R21

10

k

TL431

MOC8101

C3

1.0 nF/1.0 kV

R3

4.7

M

D14

1N4733

MC44603P

D15 1N5819

Page 20

MC44603

20

MOTOROLA ANALOG IC DEVICE DATA

250 W Input Power Fly–Back Converter

185 V – 270 V Mains Range

MC44603P & MTP6N60E

Tests Conditions Results

Line Regulation

150 V

130 V

114 V

7.0 V

Vin = 185 Vac to 270 Vac

F

mains

= 50 Hz

I

out

= 0.6 A

I

out

= 2.0 A

I

out

= 2.0 A

I

out

= 2.0 A

10 mV

10 mV

10 mV

20 mV

Load Regulation

150 V

Vin = 220 Vac

I

out

= 0.3 A to 0.6 A

50 mV

Cross Regulation

150 V

Vin = 220 Vac

I

out

(150 V) = 0.6 A

I

out

(30 V) = 0 A to 2.0 A

I

out

(14 V) = 2.0 A

I

out

(7.0 V) = 2.0 A

< 1.0 mV

Efficiency Vin = 220 Vac, Pin = 250 W 81%

Standby Mode

P input

Switching Frequency

Vin = 220 Vac, P

out

= 0 W 3.3 W

20 kHz fully stable

Output Short Circuit P

out (max)

= 270 W Safe on all outputs

Startup Pin = 250 W Vac = 160 V

Page 21

MC44603

21

MOTOROLA ANALOG IC DEVICE DATA

Figure 49. 125 W Input Power Off–Line Flyback Converter with Bipolar Switch

185 Vac

to

270 Vac

RFI

Filter

R1

1.0/5 W

C4 ... C7

1.0 nF/1000 V

D1 ... D4

1N4007

C1

100

µ

F

R2

68 k/2 W

C2

220

µ

F

D5

1N4934

L1

1.0

µ

H

C9 1.0 nF

C10 1.0

µ

F

R15

5.6 k

R16

22 k

C11

1.0 nF

R17

22 k

R25

1.0 k

C12

6.8 nF

R18

27 k

R19

10 k

C13

100 nF

R7 180 k

R8

15 k

R9 1.0 k

R4

27

k

C16

100 pF

C15

1.0 nF

D6

1N4148

R5

1.2 k

R6

150

R14

0.33

R13

1.0 k

D12

MR856

MJF18006

C14

4.7 nF

C18

2.2 nF

L

aux

L

p

D8

MR856

D9

MR852

D10

MR852

D11

MR852

C32 220 pF

C29 220 pF

C26 220 pF

C23 220 pF

C27

1000

µ

F

C28

0.1 µF

C25

1000

µ

F

C24

0.1

µ

F

C21

1000

µ

F

C22

0.1 µF

C30

100 µF

C31

0.1 µF

R24

270

R23

117.5 k

R22

2.5 k

120 V/0.5 A

28 V/1.0 A

15 V/1.0 A

8.0 V/1.0 A

C20

33 nF

C19

100 nF

R21

10

k

TL431

MOC8101

C3

1.0 nF/1.0 kV

R3

4.7

M

V

CC

9

10

11

12

13

14

15

16

8

7

6

5

4

3

2

1

D13 1N4728

C34 1.0 µF

D14

1N4733

MC44603P

R11 39

R10 10

D15 1N5819

Page 22

MC44603

22

MOTOROLA ANALOG IC DEVICE DATA

125 W Input Power Fly–Back Converter

185 V – 270 V Mains Range

MC44603P & MJF18006

Tests Conditions Results

Line Regulation

120 V

128 V

115 V

8.0 V

Vin = 185 Vac to 270 Vac

F

mains

= 60 Hz

I

out

= 0.5 A

I

out

= 1.0 A

I

out

= 1.0 A

I

out

= 1.0 A

10 mV

10 mV

10 mV

20 mV

Load Regulation

120 V

Vin = 220 Vac

I

out

= 0.2 A to 0.5 A

= 0.05 V

Cross Regulation

120 V

Vin = 220 Vac

I

out

(120 V) = 0.5 A

I

out

(28 V) = 0 A to 1.0 A

I

out

(15 V) = 1.0 A

I

out

(8.0 V) = 1.0 A

< 1.0 mV

Efficiency Vin = 220 Vac, Pin = 125 W 85%

Standby Mode

P input

Switching Frequency

Vin = 220 Vac, P

out

= 0 W 2.46 W

20 kHz fully stable

Output Short Circuit P

out (max)

= 140 W Safe on all outputs

Startup Pin = 125 W Vac = 150 V

Page 23

MC44603

23

MOTOROLA ANALOG IC DEVICE DATA

P SUFFIX

PLASTIC PACKAGE

CASE 648–08

ISSUE R

OUTLINE DIMENSIONS

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEADS WHEN

FORMED PARALLEL.

4. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

5. ROUNDED CORNERS OPTIONAL.

–A–

B

F

C

S

H

G

D

J

L

M

16 PL

SEATING

18

916

K

PLANE

–T–

M

A

M

0.25 (0.010) T

DIM MIN MAX MIN MAX

MILLIMETERSINCHES

A 0.740 0.770 18.80 19.55

B 0.250 0.270 6.35 6.85

C 0.145 0.175 3.69 4.44

D 0.015 0.021 0.39 0.53

F 0.040 0.70 1.02 1.77

G 0.100 BSC 2.54 BSC

H 0.050 BSC 1.27 BSC

J 0.008 0.015 0.21 0.38

K 0.110 0.130 2.80 3.30

L 0.295 0.305 7.50 7.74

M 0 10 0 10

S 0.020 0.040 0.51 1.01

____

DIM MIN MAX MIN MAX

INCHESMILLIMETERS

A 10.15 10.45 0.400 0.411

B 7.40 7.60 0.292 0.299

C 2.35 2.65 0.093 0.104

D 0.35 0.49 0.014 0.019

F 0.50 0.90 0.020 0.035

G 1.27 BSC 0.050 BSC

J 0.25 0.32 0.010 0.012

K 0.10 0.25 0.004 0.009

M 0 7 0 7

P 10.05 10.55 0.395 0.415

R 0.25 0.75 0.010 0.029

M

B

M

0.010 (0.25)

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MOLD

PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER

SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN

EXCESS OF D DIMENSION AT MAXIMUM

MATERIAL CONDITION.

–A–

–B– P8X

G14X

D16X

SEATING

PLANE

–T–

S

A

M

0.010 (0.25) B

S

T

16 9

81

F

J

R

X 45

_

____

M

C

K

DW SUFFIX

PLASTIC PACKAGE

CASE 751G–02

(SOP–16L)

ISSUE A

Page 24

MC44603

24

MOTOROLA ANALOG IC DEVICE DATA

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty , representation or guarantee regarding

the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and

specifically disclaims any and all liability, including without limitation consequential or incidental damages. “T ypical” parameters which may be provided in Motorola

data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals”

must be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent rights nor the rights of

others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other

applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury

or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola

and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees

arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that

Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal

Opportunity/Affirmative Action Employer.

Mfax is a trademark of Motorola, Inc.

How to reach us:

USA/EUROPE /Locations Not Listed: Motorola Literature Distribution; JAPAN: Motorola Japan Ltd.; SPD, Strategic Planning Office, 141,

P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan. 81–3–5487–8488

Customer Focus Center: 1–800–521–6274

Mfax: RMFAX0@email.sps.mot.com – TOUCHTONE 1–602–244–6609 ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre,

Motorola Fax Back System – US & Canada ONLY 1–800–774–1848 2, Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

– http://sps.motorola.com/mfax/ 852–26629298

HOME PAGE: http://motorola.com/sps/

MC44603/D

◊

Loading...

Loading...