Page 1

SEMICONDUCTOR

TECHNICAL DATA

Y–C PICTURE–IN–PICTURE

(PIP) CONTROLLER

B SUFFIX

PLASTIC PACKAGE

CASE 859

(SDIP)

56

1

Order this document from Analog Marketing

Device

Operating

Temperature Range

Package

ORDERING INFORMATION

MC44462B TJ = –65° to +150°C SDIP

1

MOTOROLA ANALOG IC DEVICE DATA

The MC44462 Y–C PIP controller is a low cost member of a family of high

performance PIP controllers and video signal processors for television. It is a

follow–up to the MC44461 PIP and has a modified input selection to allow

higher performance in TV systems which have S–Video inputs on the back

panel. The S–Video input is separate luma (luminance) and chroma

components. It is NTSC compatible and contains all the analog signal

processing, control logic and memory necessary to provide for the overlay of

a small picture from a second non synchronized source onto the main picture

of a television. All control and setup of the MC44462 is via a standard two pin

I2C bus interface. The device is fabricated using BICMOS technology. It is

available in a 56–pin shrink dip (SDIP) package.

The main features of the MC44462 are:

• Switchable PIP Composite Video Signals – Video 1 and Video 2

• S–Video Output Allows High Performance in TV

• Two PIP Sizes; 1/16 and 1/9 Screen Area

• Freeze Field Feature

• Variable PIP Position in 64–X by 64–Y Steps

• PIP Border with Programmable Color

• Programmable PIP Tint and Saturation Control

• Automatic Main to PIP Contrast Balance

• Vertical Filter

• Integrated 64 k Bit DRAM Memory Resulting in Minimal RFI

• Minimal RFI Allows Simple Low Cost Application into TV

• I

2

C Bus Control – No External Variable Adjustments Needed

• Operates from a Single 5.0 V Supply

• Economical 56–Pin Shrink DIP Package

YC–PIP System Diagram

Video

Processor

Y

in

C

in

CV

Main

(unused)

Y

main out

C

main out

CV

1

CV

2

YC PIP

MC44462

Y

main in

C

main in

S

W

M

T

R

X

Y

C

Comb

Filter

(MC141625)

IIC

IIC

CV

Tuner/IF

Cable

Y

C

CV

Back Panel

S–VHS Inputs

Back Panel

Composite

Video Input

R

G

B

This document contains information on a product under development. Motorola reserves the

right to change or discontinue this product without notice.

Motorola, Inc. 1996 Issue 2

Page 2

MC44462

2

MOTOROLA ANALOG IC DEVICE DATA

MAXIMUM RATINGS

Rating Symbol Value Unit

Power Supply Voltage

V

DD

–0.5 to +6.0

V

Power Supply Voltage

V

CC

–0.5 to +6.0

V

ББББББББББББ

Á

Input Voltage Range

ÁÁ

Á

V

IR

ÁÁÁ

Á

–0.5,

V

DD

+ 0.5

Á

Á

V

Output Current

I

O

160

mA

Power Dissipation

Maximum Power Dissipation @ 70°C

P

D

1.3

W

Thermal Resistance, Junction–to–Air

R

θJA

59

°C/W

Junction T emperature (Storage and Operating)

T

J

–65 to +150

°C

NOTE: ESD data available upon request.

ELECTRICAL CHARACTERISTICS (V

CC

= VDD = 5.0 V , TA = 25°C, unless otherwise noted.)

Characteristic

Symbol Min Typ Max Unit

POWER SUPPLY

Total Supply (Pins 8, 15, 43 and 50)

Total I

Supply

–

100

160

ÁÁÁ

mA

VIDEO

Composite Video Input (Pin 34 or 36)

CVi

–

1.0

–

ÁÁÁ

Vpp

Luma Output (Pin 49, Unterminated)

–

–

2.0

–

ÁÁÁ

Vpp

Video Output DC Level (Sync Tip)

–

–

1.0

–

ÁÁÁ

Vdc

Video Gain

–

–

6.0

–

ÁÁÁ

dB

Video Frequency Response (Main Video to –1.0 dB)

–

–

10

–

ÁÁÁ

MHz

Color Bar Accuracy

–

–

±4.0

–

ÁÁÁ

deg

Video Crosstalk (@ 75% Color Bars)

–

ÁÁÁ

dB

Main to PIP

–

55

–

ÁÁÁ

PIP to Main

–

55

–

БББББББББББББББББ

Output Impedance

ÁÁÁ–ÁÁ–ÁÁ

5.0

ÁÁ

–

ÁÁÁ

ÁÁ

Ω

HORIZONTAL TIMEBASE

Free Run HPLL Frequency (Pin 16)

–

–

15734

–

ÁÁÁ

Hz

HPLL Pull–In Range

–

–

±400

–

ÁÁÁ

Hz

HPLL Jitter

–

–

±4.0

–

ÁÁÁ

ns

Burst Gate Timing (from Trailing Edge Hsync, Pin 24)

–

–

1.0

–

ÁÁÁ

µs

Burst Gate Width

–

–

4.0

–

ÁÁÁ

µs

VERTICAL TIMEBASE

Vertical Countdown Window

–

–

232 – 296

–

ÁÁÁ

H lines

Vertical Sync Integration T ime

–

–

31

–

ÁÁÁ

µs

ANALOG TO DIGITAL CONVERTER

Resolution

–

–

6

–

ÁÁÁ

Bits

Integral Non–Linearity

–

–

±1

–

ÁÁÁ

LSB

Differential Non–Linearity

–

–

+2/–1

–

ÁÁÁ

LSB

ADC – Y Frequency Response @ –5.0 dB

–

–

1.0

–

ÁÁÁ

MHz

ADC – U, V Frequency Response @ –5.0 dB

–

–

200

–

ÁÁÁ

kHz

Sample Clock Frequency (4/3 FSC)

–

–

4.773

–

ÁÁÁ

MHz

Page 3

MC44462

3

MOTOROLA ANALOG IC DEVICE DATA

ELECTRICAL CHARACTERISTICS (continued) (V

CC

= VDD = 5.0 V , TA = 25°C, unless otherwise noted.)

Characteristic UnitMaxTypMinSymbol

DIGITAL TO ANALOG CONVERTER

Resolution

–

–

–

6

ÁÁÁ

Bits

Integral Non–Linearity

–

–

±1

–

ÁÁÁ

LSB

Differential Non–Linearity

–

–

+2/–1

–

ÁÁÁ

LSB

Tint DAC Control Range (in 64 Steps)

–

–

±10

–

ÁÁÁ

Deg

Saturation DAC Control Range (in 64 steps)

–

–

±6.0

–

ÁÁÁ

dB

NTSC DECODER

Color Kill Threshold

–

–

–24/–16

–

ÁÁÁ

dB

Threshold Hysteresis

–

–

±1.0

–

ÁÁÁ

dB

ACC (Chroma Amplitude Change, +3.0 dB to –12 dB)

–

–

±0.5

–

ÁÁÁ

dB

PIP CHARACTERISTICS

PIP Size

–

ÁÁÁ

1/9 Screen Horizontal

–

114

–

ÁÁÁ

pels

1/9 Screen Vertical

–

71

–

ÁÁÁ

lines

1/16 Screen Horizontal

–

84

–

ÁÁÁ

pels

1/16 Screen Vertical

–

53

–

ÁÁÁ

lines

Border Size Horizontal

–

–

3

–

ÁÁÁ

pels

Border Size Vertical

–

–

2

–

ÁÁÁ

lines

Output PEL Clock (4 FSC)

–

–

14.318

–

ÁÁÁ

MHz

Position Control Range Horizontal (% of Main Picture), 64 Steps

–

–

100

–

ÁÁÁ

%

Position Control Range Vertical (% of Main Picture), 64 Steps

–

–

100

–

ÁÁÁ

%

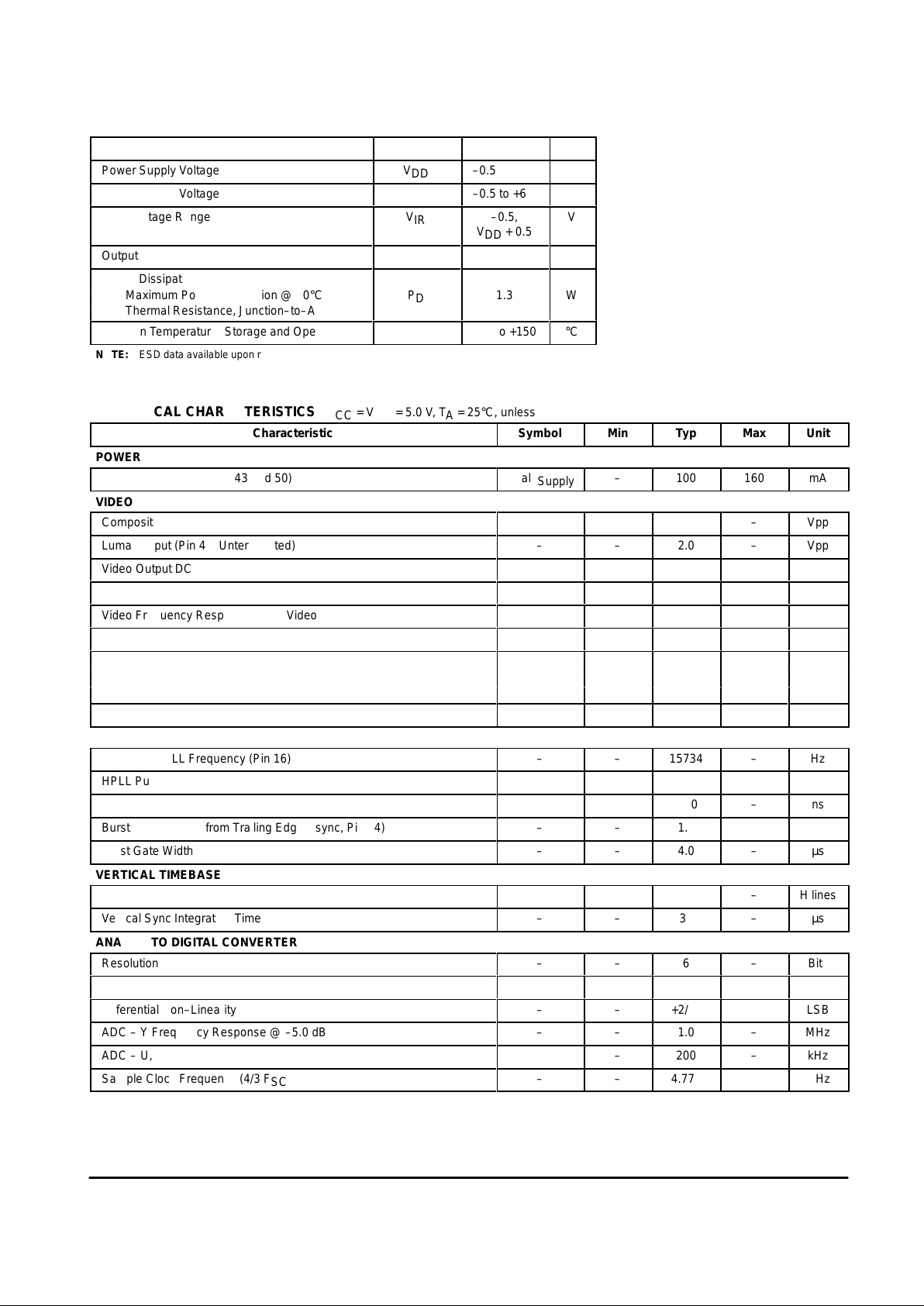

Figure 1. Representative Block Diagram

This device contains approximately 500,000 active transistors.

Y

V

U

YUV

Clamp

Input

Switch

Low Pass

Filter

Band Pass

Filter

NTSC

Decoder

PIP

Switch

4X S/C

Osc + PLL

16X S/C

Osc + PLL

YUV

Clamp

NTSC

Encoder

4X S/C

Osc + PLL

Filter

Tracking

6–Bit

ADC

H and V

Timebase

Digital

Logic

Memory

8.0 k x 8

DRAM

Tint DAC

Sat DAC

V DAC

Y DAC

3.0 MHz

LPF

3.0 MHz

LPF

3.0 MHz

LPF

33

Y

V

U

40 41 42

31

1

2

3

4

5

10

30

5453524746

6

6

6

6

6

3

6

Vert

57.28 MHz

90

°

0

°

14.32 MHz

90

°

0

°

36

34

37

49

38

39

7

44

45

Multiplexer

Video 1/ Luma

Video 2/Chroma

Decoder ACC

Y Out

Decoder Xtal

Decoder PLL

16 FSC PLL

Encoder Phase

Encoder ACC

H PLL

H

in

V

in

SCL

SDA

Reset

Vid 1/2 Sel

Multi T est

Encoder Clamp Caps

Encoder

Xtal

Encoder

PLL

Decoder Clamp Caps

Filter PLL

U DAC

51

C Out

29

Y Main

32

C Main

28

Sync Sep

Page 4

MC44462

4

MOTOROLA ANALOG IC DEVICE DATA

10 µF

Figure 2. Application Circuit

40

39

38

37

36

35

34

33

46

45

44

43

42

41

32

31

30

29

48

47

56

55

54

53

52

51

50

49

1

2

3

4

5

6

9

10

11

12

13

14

15

16

7

8

17

18

19

20

21

22

23

24

25

26

27

28

N/C

N/C

N/C

N/C

N/C

N/C

N/C

N/C

VSS (dig)

Video 1/2 Select

N/C

N/C

N/C

VDD (mem)

VSS (mem)

N/C

H

in

V

in

SCL

SDA

Reset

N/C

16 FSC Filter

VDD (dig)

N/C

N/C

N/C

SN Sep

Decoder PLL

Decoder Y Cap

Decoder Xtal

Decoder ACC

V1/YPIP

Analog Gnd

V2/CPIP

Filter PLL

Analog Gnd

Encoder Xtal

Encoder PLL

Encoder ACC

Encoder Phase

Analog V

CC

Decoder V Cap

Decoder U Cap

N/C

N/C

Encoder V Cap

Encoder U Cap

Endoder Y Cap

C Out

Video Out V

CC

Y Out

C Main

H PLL

Multi Test

Y Main

0.01

0.01

0.01

0.01

0.1

0.1

0.01

0.01

0.01

0.01

1000

100 k

75

X3

12

Luma Output

5.0 V

2700

0.068

68 k

X2

0.22

0.1

0.1

Video 1/

Luma Input

Video 2/

Chroma Input

75 75

0.01

0.0068

12 k

1.0

µ

F

1.0 µF

5.0 V

Video 1/2

Select Out

1001000

100

2.2

µ

F

470 k

5.0 V

X2 – 14.31818 MHz – Fox 143–20 or equivalent

X3 – 14.31818 MHz – Fox 143–20 or equivalent

MC44462

NOTE: For proper noise isolation, Power Supply Pins 8, 14, 43 and 50 should be bypassed by both high and low

frequency capacitors. As a guideline, a 10 µF in parallel with a 0.1 µF at each supply pin is recommended.

0.0110 µF

5.0 V

0.0110 µF

0.01 10 µF

Main

Chroma

Input

Main

Luma

Input

12

75

Chroma Output

5.0 V

75

75

Horiz In

Vert In

I2C Ser Cl

I2C Ser Data

1.0 k

1.0 k

1.0 k

1.0 k

5.0 V 5.0 V

Page 5

MC44462

5

MOTOROLA ANALOG IC DEVICE DATA

I2C REGISTER DESCRIPTIONS

Base write address = 24h

Base read address = 25h

Read Register

There are two active bits in the single read byte available

from the MC44462 as follows:

Write Vertical Indicator (WVI0) – D7

When 0 indicates that the write operation specified by the

last I2C command has been completed.

PIP Sync Detect Bit (PSD0) – D1

When 0 indicates that the PIP video H pulses are present

and the horizontal timebase oscillator is within acceptable

limits.

Write Registers

Read Start Position/Write Start Position Registers

Sub–address = 00h

Write Raster Position Start Bits (WPS0–2) – D0–D2

Establishes the horizontal beginning of the PIP and its

black level measurement gate. This beginning may be varied

by approximately 3.0 µs. The position of this pulse may be

observed through the Multi Test Pin 30 (See Test Mode

Register Sub–address 03h).

Read Raster Position Bits (RPS0–3) – D4–D7

Establishes the clamp gate position for the black level

reference for the main picture. This position may be varied by

approximately 5.0 µs. The position of this pulse may be

observed through the Multi Test Pin 30 (See Test Mode

Register Sub–address 03h).

Pip Switch Delay/Vertical Filter Register

Sub–address = 01h

PIP Switch Delay Bits (PSD0–3) – D0–D3

Delays the start of PIP on time relative to the PIP picture.

These bits are used to center the PIP border and PIP picture

in the horizontal direction.

Vertical Filter Bit (VFON) – D4

When the filter is activated (VFON = 1) a three line

weighted average is taken to provide the data stored in the

field memory.

Border Color Register

Sub–address = 02h

Border Color Bits (BC0–2) – D0–D2

These Bits control the color of the border. Note that when

using one of the saturated border colors it is possible to get

objectionable dot crawl at the edge of the border in some TVs

unless appropriate comb filtering is used in the TV circuitry.

BC (2:0)

Border Color

000

Black

001

White 70%

010

No Border (clear)

011

No Border (clear)

100

Blue

101

Green

110

Red

111

White

Test Mode/Main Vertical and Horizontal Polarity Register

Sub–address = 03h

Internal Test Mode Register (ITM0–2) – D0–D2

Sets the Multi Test Pin output to provide one of several

internal signals for test and production alignment. Also

controls the test memory address counter.

ББББББ

ITM (2:0)

Multi–Test I/O and Function

ББББББ

000

Input – Analog Test mode

ББББББ

001

Input – Digital Test mode

ББББББ

010

Output – Sync Detect

ББББББ

011

Output – PIP Switch

ББББББ

100

Output – PIP H Detect

ББББББ

101

Output – PIP V Detect

ББББББ

110

Output – PIP Clamp

ББББББ

111

Output – Main Clamp

Main vertical polarity select bit (MVP0) – D6

Selects polarity of active level of vertical reference input.

0 = positive going, 1 = negative going.

Main horizontal polarity select bit (MHP0) – D7

Selects polarity of active level of horizontal reference

input. 0 = positive going, 1 = negative going.

PIP Freeze/PIP Size/Main and PIP Video Source Register

Sub–address = 04h

PIP Freeze Bit (STIL0) – D4

When set to one, the most recently received field is

continuously displayed until the freeze bit is cleared.

PIP Size Bit (PSI90) – D5

Switches the PIP size between 1/16 main size (when 0)

and 1/9 main size (when 1).

Video Type Select Bit (YCPSEL) – D6

Selects which video type will be applied to the PIP input.

PIP Video Source Select Bit (PSEL0) – D7

Selects which composite video input will be applied to the

video decoder to provide the PIP video in CV mode.

ÁÁÁÁ

PSEL

YCPSEL

Function

ÁÁÁÁ

0

1

YC Input to PIP

ÁÁÁÁ

0

CV1 Input to PIP

0

1

0

CV1 Input to PIP

CV2 Input to PIP

PIP On/PIP Blank Register

Sub–address = 05h

PIP On Bit (PON0) – D0

When on (1) turns the PIP on.

PIP Blanking Bit (PBL0) – D4

When on (1) sets the PIP to black. If the PIP is off, then it

will be black if it is turned on. Overrides all other settings of

the PIP control.

PIP X Position Register

Sub–address = 06h

X Position Bits (XPS0–5) – D0–D5

Moves the PIP start position from the left to the right

edge of the display in 64 steps. There is protection circuitry

Page 6

MC44462

6

MOTOROLA ANALOG IC DEVICE DATA

to prevent the PIP from interfering with the main picture

sync pulses.

PIP Y Position Register

Sub–address = 07h

Y Position Bits (YPS0–5) – D0–D5

Moves the PIP start position from the top to the bottom

edge of the display in 64 steps. There is protection circuitry to

prevent the PIP from interfering with the main picture sync

pulses.

PIP Chroma Level Register

Sub–address = 08h

Chroma (C0–5) – D0–D5

The color of the PIP can be adjusted to suit viewer

preference by setting the value stored in these bits. A total of

64 steps varies the color from no color to maximum. This

control acts in conjunction with the auto phase control.

PIP Tint Level Register

Sub–address = 09h

Tint (T0–5) – D0–D5

An auto phase control compares the main color burst to

the internally generated pseudo color burst so that the tints

are matched. In addition to this, the tint of the PIP can be

varied ±10° in a total of 64 steps by changing the value of

these bits to suit viewer preference.

PIP Luma Delay Register

Sub–address = 0Ah

Y Delay (YDL0–2) – D0–D2

Since the Chroma passes through a bandpass filter and

the color decoder, it is delayed with respect to the Luma

signal. Therefore, to time match the Luma and Chroma these

bits are set to a single value determined to be correct in the

application.

Pip Fill/Test Register

Sub–address = 0Ch

PIP Fill Bits (PIPFILL0–1) – D0–D1

May be used to fill the PIP with one of three selectable

solid colors

Test Register Bits (INTC0 and MACR0) – D6–D7

Used for production test only.

I2C REGISTER TABLE

–

Data Bit

Sub

–

address

D7

D6

D5

D4

D3

D2

D1

D0

00

RPS3

RPS2

RPS1

RPS0

–

WPS2

WPS1

WPS0

01

–

–

–

VFON

PSD3

PSD2

PSD1

PSD0

02

–

–

–

–

–

BC2

BC1

BC0

03

MHP0

MVP0

–

–

–

ITM2

ITM1

ITM0

04

PSEL0

YCPSEL

PSI90

STIL0

–

–

–

–

05

–

–

–

PBL0

–

–

–

PON0

06

–

–

XPS5

XPS4

XPS3

XPS2

XPS1

XPS0

07

–

–

YPS5

YPS4

YPS3

YPS2

YPS1

YPS0

08

–

–

C5

C4

C3

C2

C1

C0

09

–

–

T5

T4

T3

T2

T1

T0

0A

–

–

–

–

–

YDL2

YDL1

YDL0

0B

–

–

–

–

–

–

–

–

0C

–

–

–

–

–

–

–

–

Page 7

MC44462

7

MOTOROLA ANALOG IC DEVICE DATA

B SUFFIX

PLASTIC PACKAGE

CASE 859–01

(SDIP)

ISSUE O

OUTLINE DIMENSIONS

51.69

13.72

3.94

0.36

0.81

0.20

2.92

0

°

0.51

52.45

14.22

5.08

0.56

1.17

0.38

3.43

15

°

1.02

MILLIMETERS

2.035

0.540

0.155

0.014

0.032

0.008

0.115

0

°

0.020

2.065

0.560

0.200

0.022

0.046

0.015

0.135

15

°

0.040

-T-

SEATING

PLANE

C

D

56 PL

E

F

J

56 PL

K

M

G

N

128

56 29

NOTES:

1. DIMENSIONS AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEAD WHEN

FORMED PARALLEL.

4. DIMENSIONS A AND B DO NOT INCLUDE MOLD

FLASH. MAXIMUM MOLD FLASH 0.25 (0.010).

MIN MINMAX MAX

INCHES

DIM

A

B

C

D

E

F

G

H

J

K

L

M

N

15.24 BSC0.600 BSC

1.778 BSC

7.62 BSC

0.070 BSC

0.300 BSC

0.89 BSC0.035 BSC

L

H

-A-

-B-

0.25 (0.010) T A

M

S

0.25 (0.010) T B

M

S

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding

the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and

specifically disclaims any and all liability, including without limitation consequential or incidental damages. “T ypical” parameters which may be provided in Motorola

data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals”

must be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent rights nor the rights of

others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other

applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury

or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola

and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees

arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that

Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal

Opportunity/Affirmative Action Employer.

How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; JAP AN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center,

P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454 3–14–2 Tatsumi Koto–Ku, T okyo 135, Japan. 03–81–3521–8315

MFAX: RMF AX0@email.sps.mot.com – TOUCHT ONE 602–244–6609 ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park,

INTERNET: http://Design–NET .com 51 Ting Ko k Road, Tai Po, N.T., Hong Kong. 852–26629298

MC44462/D

*MC44462/D*

◊

Loading...

Loading...