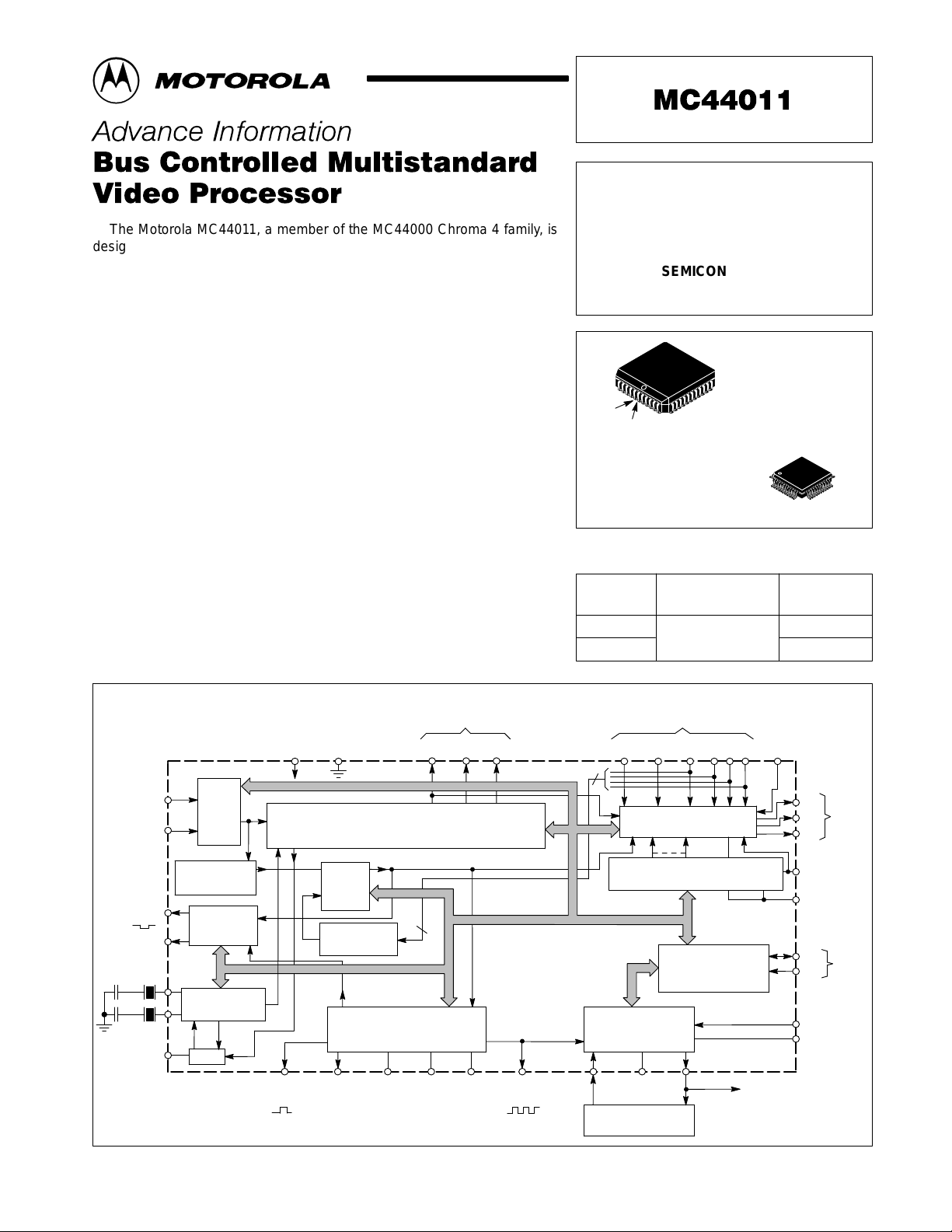

Page 1

The Motorola MC44011, a member of the MC44000 Chroma 4 family, is

designed to provide RGB or YUV outputs from a variety of inputs. The inputs

can be composite video (two inputs), S–VHS, RGB, and color difference

(R–Y, B–Y). The composite video can be PAL and/or NTSC as the MC44011

is capable of decoding both systems. Additionally , R–Y and B–Y outputs and

inputs are provided for use with a delay line where needed. Sync separators

are provided at all video inputs.

In addition, the MC44011 provides a sampling clock output for use by a

subsequent triple A/D converter system which digitizes the RGB/YUV

outputs. The sampling clock (6.0 to 40 MHz) is phase–locked to the

horizontal frequency.

Additional outputs include composite sync, vertical sync, field

identification, luma, burst gate, and horizontal frequency.

Control of the MC4401 1, and reading of status flags, is via an I2C bus.

• Accepts NTSC and PAL Composite Video, S–VHS, RGB, and R–Y, B–Y

• Includes Luma and Chroma Filters, Luma Delay Lines, and Sound Traps

• Digitally Controlled via I

• R–Y, B–Y Inputs for Alternate Signal Source

• Line–Locked Sampling Clock for A/D Converters

• Burst Gate, Composite Sync, Vertical Sync and Field Identification Outputs

• RGB/YUV Outputs can Provide 3.0 Vpp for A/D Inputs

• Overlay Capability

• Single Power Supply: 5.0 V, ±5%, 550 mW (Typical)

• 44 Pin PLCC and QFP Packages

2

C Bus

BUS CONTROLLED

MULTISTANDARD

VIDEO PROCESSOR

44

1

FB SUFFIX

PLASTIC PACKAGE

CASE 824E

ORDERING INFORMATION

Device

MC44011FN

MC44011FB

Order this document by MC44011/D

SEMICONDUCTOR

TECHNICAL DATA

FN SUFFIX

PLASTIC PACKAGE

CASE 777

(PLCC)

44

(QFP)

Operating

Temperature Range

TA = 0° to +70°C

1

Package

PLCC–44

QFP

Comp

Video 1

Comp

Video 2

Vertical

Output

Field ID

17.7 MHz

14.3 MHz

Filter

Input

Select

Sync

Separator

Vertical

Decoder

Oscillator

PLL

CC1

Burst

Gate

Representative Block Diagram

Outputs

Gnd1V

Sound Trap/Luma Filter/Luma Delay/

Chroma Filter/P AL and NTSC

Decoder/Hue and Saturation Control

Select

Sync

Separator

16Fh/

C

Sync

PLL #1 Horizontal

Filter

Switch

4

PLL/VCO

H

Filter

B–YR–YY1

Quiet

Gnd

MC44011

Fh

Ref

4

15 k

Ret

R–Y

Data Bus

PLL #2

Pixel Clock

PLL/VCO

Frequency

Divider

Inputs

Y2

B–Y

Color Difference

Stage

Contrast, Brightness,

Saturation Control DACs

Interface/

Registers

PLL

Filter

G

R

I2C Data

Clock

B

Fast

Comm

R/V

G/Y

B/U

V

CC2

Gnd2

SDL

SCL

V

CC3

Gnd3

To A/D Converters

Outputs

µ

P

To

This document contains information on a new product. Specifications and information herein

are subject to change without notice.

MOTOROLA ANALOG IC DEVICE DATA

Motorola, Inc. 1996 Rev 1

1

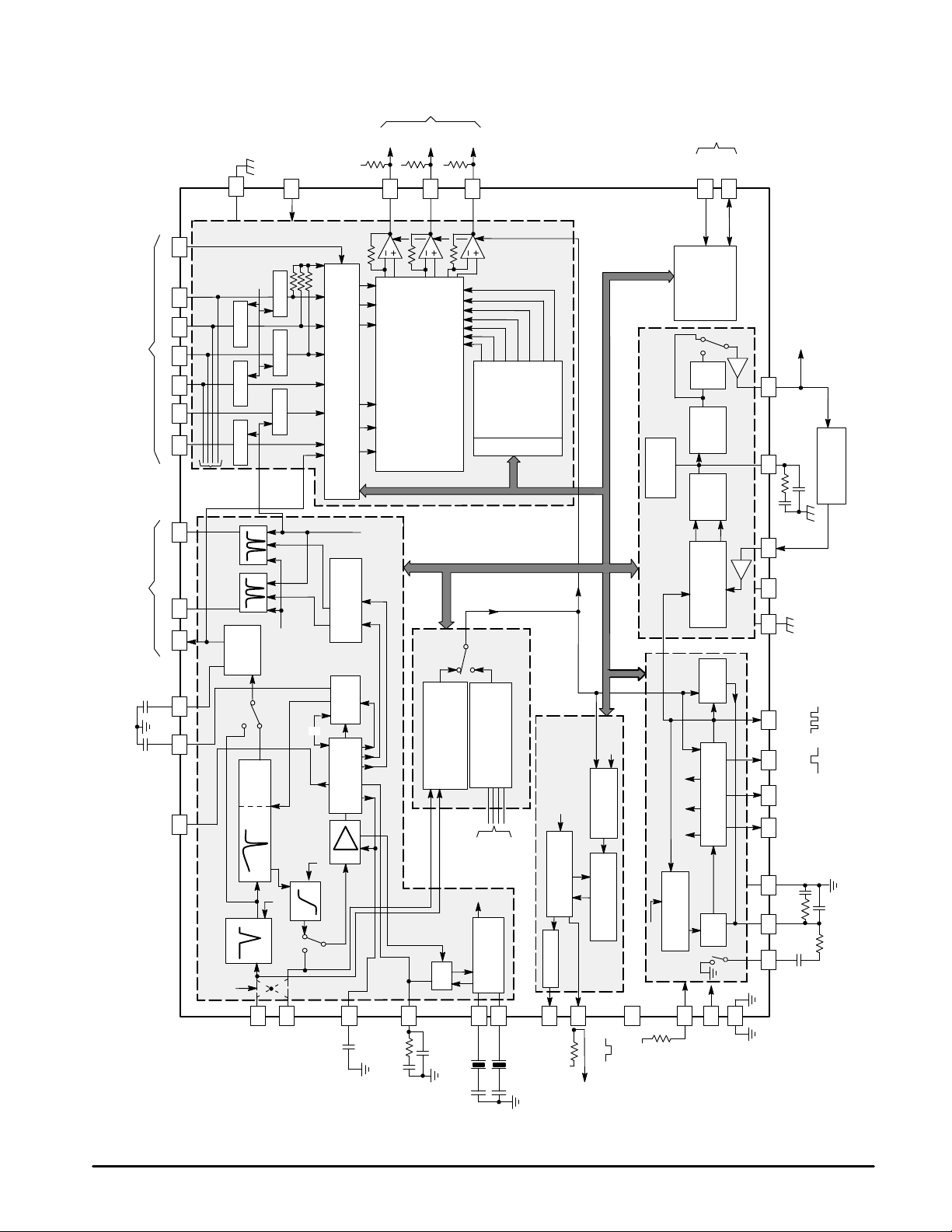

Page 2

MC44011

Inputs

Outputs

R/V

5.0

5.0

20

Color Matrix and

Blank

Burst

Clamp Clamp Clamp

Gate

CC2

V

(5.0 V)

23

ClampClampClamp

Signal Selection

B–YY R–Y B G R

Gnd2

24

25282726293031424133324334

Sep

T o Sync

G/Y

5.0

21

Controls

B/U

22

Contrast

Saturation

Red Gain

Blue Gain

Brightness

∆

∆

DACs

Color Difference Stage

Red DC

Blue DC

∆

∆

2Fo

Bus Control & Flag Status Read

Voltage

Monitor

SCL

5

C Data

2

Interface/

I

Fo

2

÷

VCO

12–40 MHz

Pump

Charge

U

D

P

µ

To

SDL

6

Registers

T o A/D Converters

Clock

PLL #2

Filter

Ret

15 k

Divider

Frequency

R–Y

B–Y

Hue DACs

C

Saturation/

Outputs

Fs Notch

X1, X2, X8

Delay

Adj. Luma

Figure 1. Representative Block Diagram

Y1

Clamp Y1 B–Y R–Y R–Y B–Y Y2 B G R FC

Ident

Filter

Select

System

Luma

4.4/4.8/5.2

5.5/6.0/6.5 MHz

Select

Delay

1

Comp Video 1

Luma Peaking

Chroma Trap &

C

Sound Trap

3

Comp Video 2

Ident

C

Decoder

PAL/NTSC

C

Chroma Filter

2

ACC Filter

R–Y

B–Y

Separator &

Adaptive Sync

ACC

PAL/NTSC/S–VHS Decoder

PLL

44

Chroma PLL Filter

Selector

Sync Separator

From

C

Oscillator

38

Xtal 1

17.7 MHz

Sync Separator

& Selector

Inputs

RGB & Y2

36

Xtal 2

14.3 MHz

Comp Sync

Vertical Decoder

2Fh

Vert. Sync

525, 625

& Decoder

Line Counter

Coincidence

Field ID

7

4

Field ID

Vertical Sync

5.0 V

16Fh

Separator

Counter

37

NC

5.0

PLL #2

PLL #1

C

ref

I

Comparator

Phase & Frequency

Det

Phase

64

÷

16Fh Blank 2Fh

Circuit

Calibration

VCO

9

40

CC1

V

(5.0 V)

Figure 1.

39

Gnd1

12 11 10 13 35 8 14 17 19 15 16 18

CC3

V

Gnd3

Fh

S/C Burst

16Fh/

Quiet

H Fil

H Filt

(5.0 V)

Ref

Gate

Sync

C

GND

Switch

2

MOTOROLA ANALOG IC DEVICE DATA

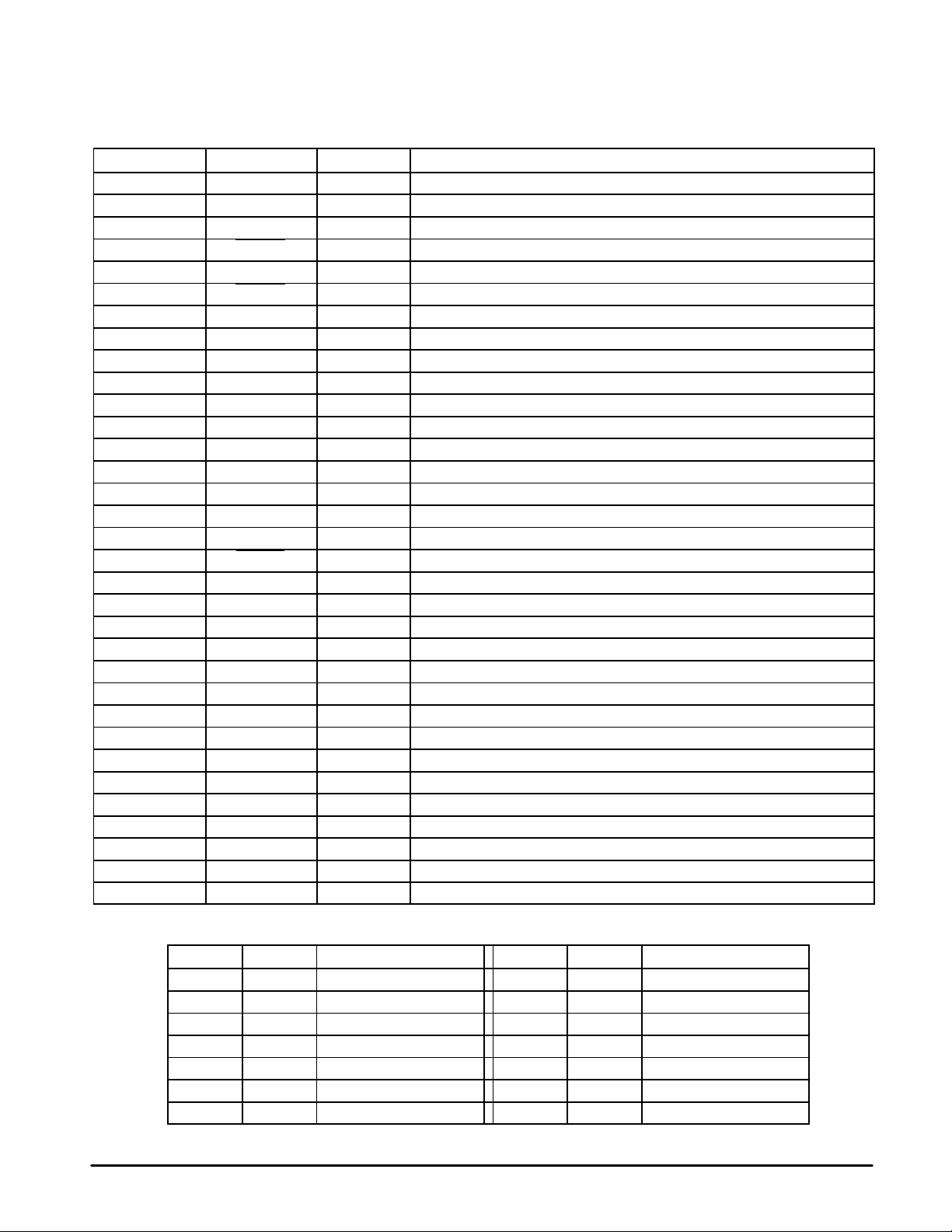

Page 3

MC44011

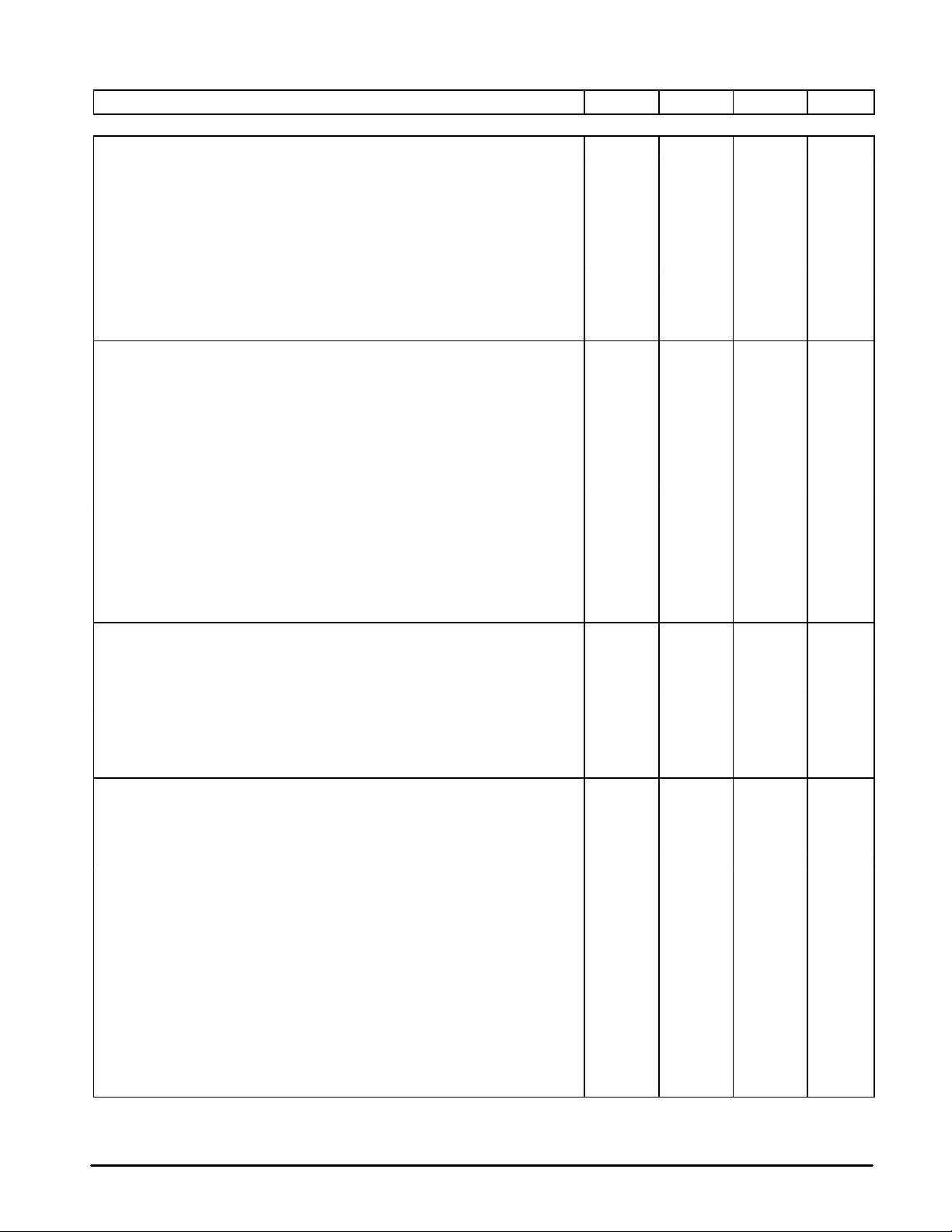

ELECTRICAL CHARACTERISTICS (The tested electrical characteristics are based on the conditions shown in Table 1 and 2.

Composite Video input signal = 1.0 Vpp, composed of: 0.7 Vpp Black–to–White; 0.3 Vpp Sync–to–Black; 0.3 Vpp Color Burst. V

= V

CC3

= 5.0 V, I

= 32 µA (Pin 9), unless otherwise noted.)

ref

Table 1. Control Bit Test Settings

Control Bit Name Value Function

$77–7 S–VHS–Y 0 Composite Video input selected.

$77–6 S–VHS–C 0 Composite Video input selected.

$77–5 FSI 0 50 Hz Field Rate selected.

$77–4 L2 GATE 0 PLL #2 Gating enabled.

$77–3 BLCP 0 Clamp Pulse Gating enabled.

$77–2 L1 GATE 0 Vertical Gating enabled.

$77–1, 0 CB1, CA1 1,1 Vertical section Auto–Countdown mode

$78–7 36/68 µs 0 Time from beginning of Line 4 to V ertical Sync is 36 µs.

$78–6 CalKill 0 Horizontal Calibration Loop enabled.

$79–7, 6 HI, VI 1,1 Normal

$7A–7 Xtal – 0 = 17.7 MHz crystal selected, 1 = 14.3 MHz crystal selected.

$7A–6 SSD 0 Normal

$7B–7, 6 T1, T2 1,1 Sound Trap Notch filter set to 5.5 MHz (with 17.7 MHz crystal).

$7C–7 SSC 0 Permits PAL and NTSC selection.

$7C–6, $7D–6 SSA, SSB – 0, 1 = PAL decoding, 1,0 = NTSC decoding

$7D–7, $7E–7, 6 P1, P3, P2 1, 1, 1 Sets Luma Peaking at 0 dB.

$7F–7, 6, $80–6 D3, D1, D2 0, 0, 0 Set Luma Delay to minimum

$80–7 RGB EN 0 Fast Commutate input can enable RGB inputs.

$81–7 Y2 EN 0 Y2 input (Pin 29) deselected

$81–6 Y1 EN 1 Y1 luma path from PAL/NTSC decoder selected.

$82–7 YUV EN 0 RGB output mode selected

$82–6 YX EN 0 Disable luma matrix from RGB inputs.

$83–7 L2 Gain 0 Set PLL #2 Phase/Frequency detector gain high.

$83–6 L1 Gain 1 Set PLL #1 Phase Detector gain high.

$84–7 H Switch 0 Set Horizontal Phase Detector filter switch open.

$84–6 525/625 – 0 = 625 lines (PAL), 1 = 525 lines (NTSC)

$85–7 F

$85–6 C

$86–7 Vin Sync 1 Composite Video inputs (Pin 1 or 3) Sync Source selected.

$86–6 H EN 0 Enabled Horizontal Timebase.

$87–7 Y2 Sync 0 Y2 sync source not selected.

$88–7 V2/V1 1 Select Video 1 input (Pin 1).

$88–6 RGB Sync 0 RGB inputs Sync Source not selected.

÷ 2 0 Select direct VCO output from PLL #2.

osc

Sync

0 16 Fh output selected at Pin 13.

CC1

= V

CC2

DAC Value Function DAC Value Function

$78 32 R–Y/B–Y Gain $82 32 Red Contrast Trim

$79 32 Sub Carrier Phase $83 32 Blue Brightness Trim

$7D 00 Blue Output DC Bias $84 32 Main Brightness

$7E 00 Red Output DC Bias $85 32 Red Brightness Trim

$7F 63 Pixel Clock VCO Gain $86 32 Saturation (Color Diff.)

$80 32 Blue Contrast Trim $87 16 Saturation (Decoder)

$81 32 Main Contrast $88 32 Hue

NOTE: Currents out of a pin are designated –, and those into a pin are designated +.

MOTOROLA ANALOG IC DEVICE DATA

Table 2. DAC Test Settings

3

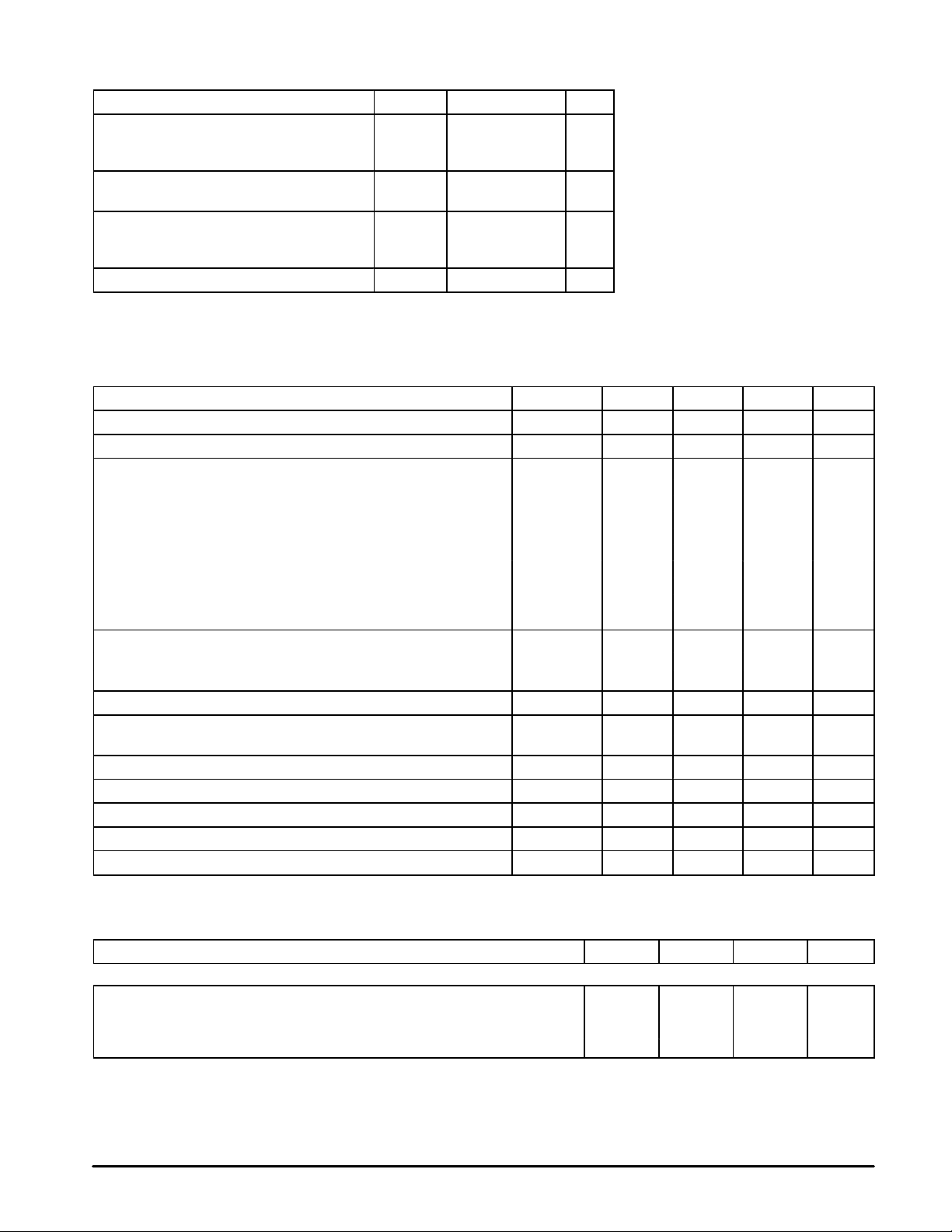

Page 4

MC44011

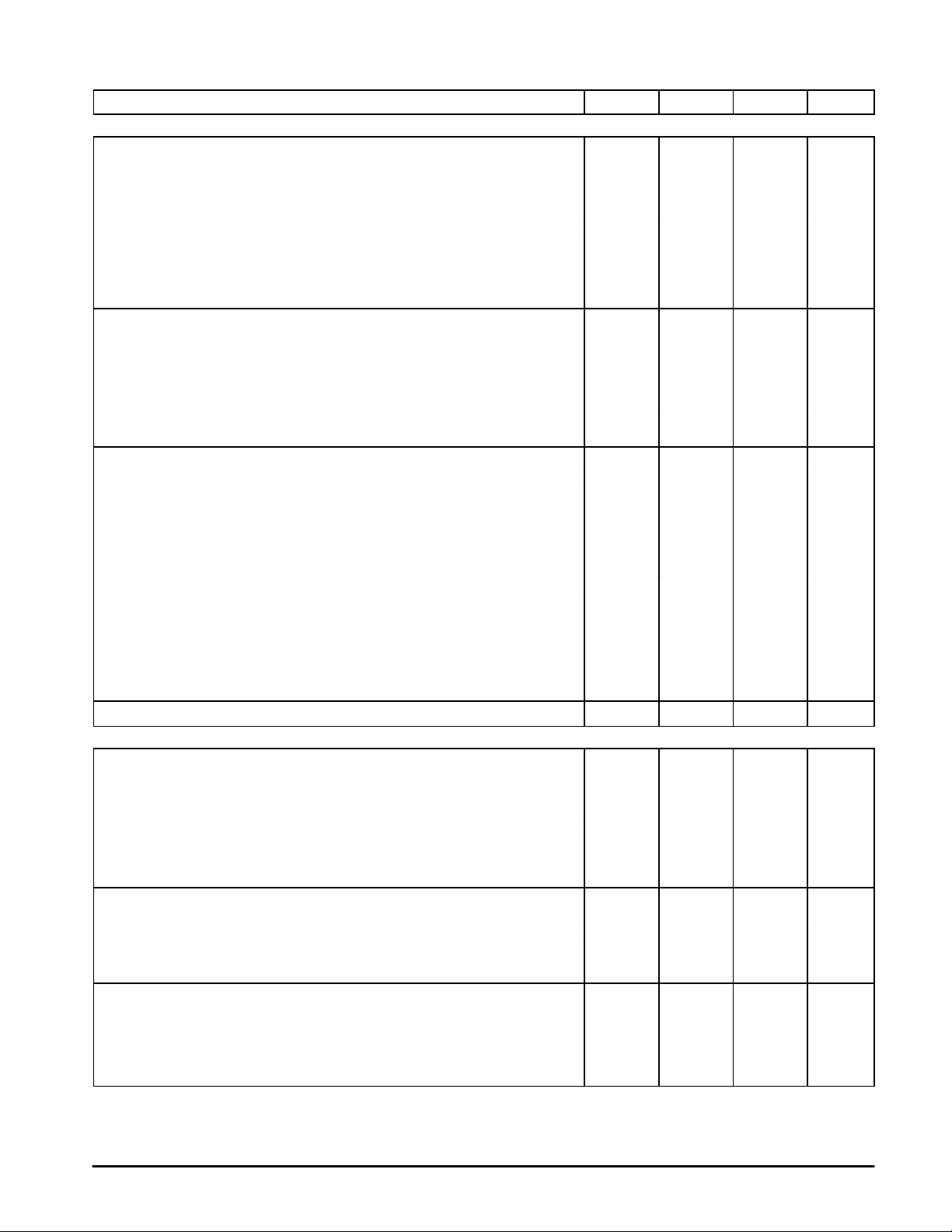

MAXIMUM RATINGS

Rating Symbol Value Unit

Power Supply Voltage V

Power Supply Difference

(Between any two VCC pins)

Input Voltage: Video 1, 2, SCL, SDL V

Input Voltage: 15 kHz Return –0.5, V

Input Voltage: R–Y, B–Y, Y2, RGB, FC –0.5, V

Junction T emperature (Storage and Operating) T

NOTES: 1. Devices should not be operated at these limits. The “Recommended Operating Conditions”

table provides for actual device operation.

2.ESD data available upon request.

CC1

V

CC2

V

CC3

– ±0.5 Vdc

in

J

RECOMMENDED OPERATING CONDITIONS

Characteristics Symbol Min Typ Max Unit

Power Supply Voltage V

Power Supply Difference (Between any two VCC pins) ∆V

Input Voltage: V ideo 1, 2 (Sync–White) V

Input Voltage: Chroma (S–VHS Mode) – – 1.2

Input Voltage: Y2 0.7 1.0 1.4

Input Voltage: RGB 0.5 0.7 1.0

Input Voltage: R–Y, B–Y (Pins 30, 31) 0 – 1.8

Input Voltage: 15 kHz Return 0 – V

Input Voltage: SCL, SDL 0 – V

Input Voltage: FC 0 – V

Input Voltage: Burst Signal 30 280 560 mVpp

Input Voltage: Sync Amplitude 60 300 V

Output Load Impedance to Ground: RGB (Pull–Up = 390 Ω) RL

Output Load Impedance to Ground: B–Y, R–Y RL

Output Load Impedance to Ground: Y1 RL

Pull–Up Resistance at Vertical Sync (Pin 4) R

Source Impedance: Video 1, 2 – 0 – 1.0 kΩ

Source Impedance: Pins 26 to 31 0 – 1.0

Pixel Clock Frequency (Pin 18, see PLL #2 Electrical Characteristic) f

15 kHz Return Pulse Width (Low Time) PW

I2C Clock Frequency f

Reference Current (Pin 9) I

Operating Ambient Temperature T

NOTE: All limits are not necessarily functional concurrently.

–0.5 to +6.0 Vdc

–0.5 to +6.0

–0.5 to +6.0

–0.5, V

–65 to +150 °C

+0.5 Vdc

CC1

+0.5

CC3

+0.5

CC2

CC1, 2, 3

CC

in

RGB

CD

Y1

VS

px

15k

I2C

ref

A

4.75 5.0 5.25 Vdc

–0.5 0 0.5 Vdc

0.7 1.0 1.4 Vpp

CC3

CC1

CC2

CC1

1.0 –

10 –

1.0 –

1.0 10 – kΩ

– 2.0 to 45 – MHz

0.2 – 45 µs

– – 100 kHz

– 32 – µA

0 – 70 °C

∞

∞

∞

Vdc

mVpp

kΩ

ELECTRICAL CHARACTERISTICS (T

Characteristics Min Typ Max Unit

POWER SUPPLIES

Power Supply Current (VCC = 5.0 V) Pin 40 75 95 115 mA

4

= 25°C, V

A

Pin 23 6.0 9.0 12

Pin 19 3.5 6.0 8.0

Total 85 110 135

CC1

= V

CC2

= V

= 5.0 V, unless otherwise noted.)

CC3

MOTOROLA ANALOG IC DEVICE DATA

Page 5

MC44011

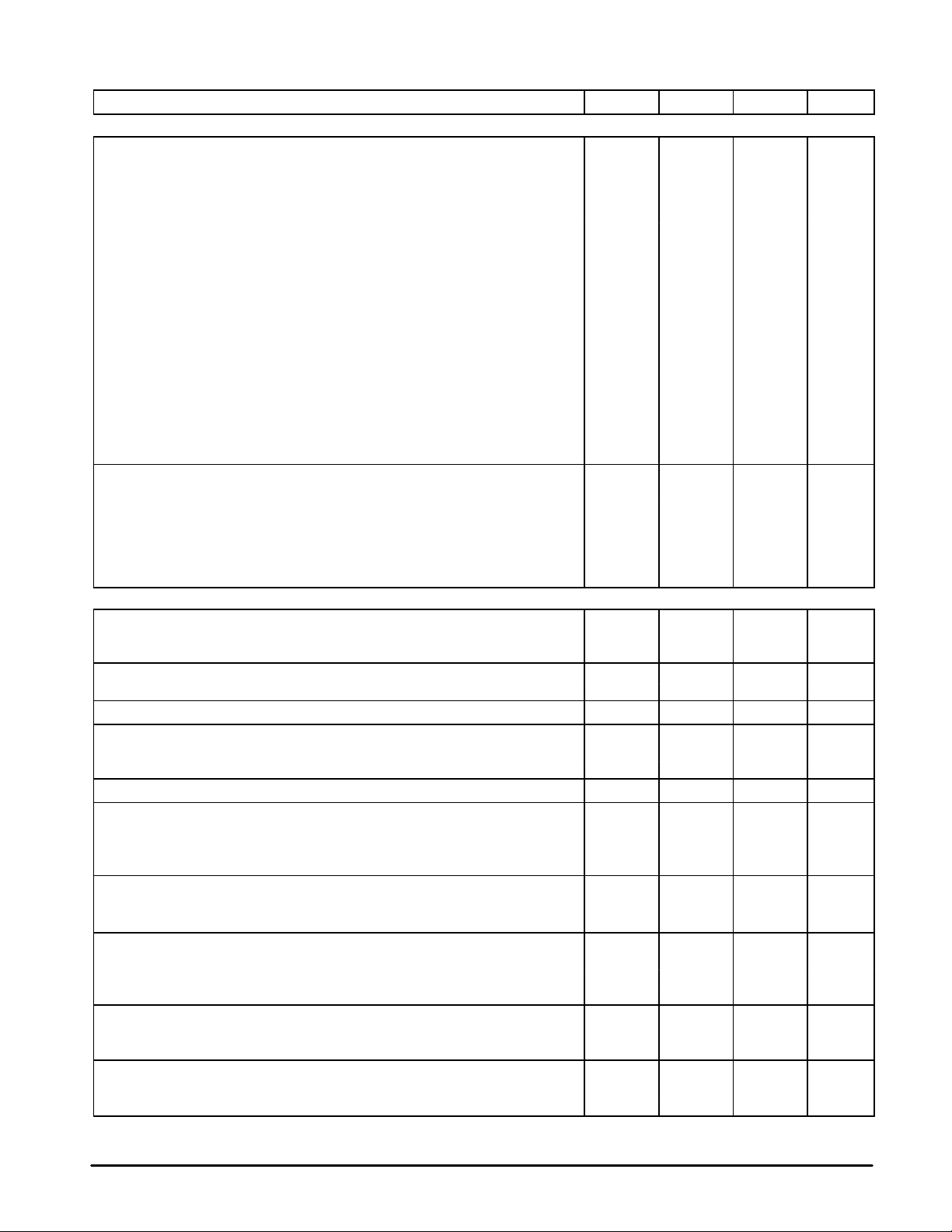

ELECTRICAL CHARACTERISTICS (continued) (T

Characteristics UnitMaxTypMin

PAL/NTSC/S–VHS DECODER

Video 1, 2 Inputs

Crosstalk Rejection, f = 1.0 MHz

(Measured at Y1 output, Luma Peaking = 0 dB, $77–7 = 1)

DC Level: @ Selected Input – 2.8 – Vdc

DC Level: @ Unselected Input – 0.7 –

Clamp Current –30 –20 –10 µA

Sound Trap Rejection (See Figures 14 to 23)

With 17.7 MHz Crystal: @ 6.5 MHz (T1, T2 = 00) 15 30 – dB

With 17.7 MHz Crystal: @ 6.0 MHz (T1, T2 = 10) 15 30 –

With 17.7 MHz Crystal: @ 5.5 MHz (T1, T2 = 11) 10 43 –

With 17.7 MHz Crystal: @ 5.74 MHz (T1, T2 = 01) 15 26 –

With 14.3 MHz Crystal: @ 4.44 MHz (T1, T2 = 11) – 35 –

R–Y, B–Y Outputs (Pins 41, 42)

Output Amplitude (with 100% Saturated Color Bars)

Saturation (DAC 87) = 00 – <1.0 – mVpp

Saturation (DAC 87) = 16 – 1.6 – Vpp

Saturation (DAC 87) = 63 1.8 3.0 –

DC Level During Blanking – 2.4 – Vdc

Hue Control – Minimum Phase (DAC 88 = 00) – –30 – Deg

Hue Control – Maximum Phase (DAC 88 = 63) – 30 –

Nominal Saturation (with respect to Y1 Output, Note 1) – 100 – %

R–Y/B–Y Ratio: Balance (DAC 78) = 63 1.35 1.69 2.06 V/V

B–Y/R–Y Ratio: Balance (DAC 78) = 32 0.98 1.27 1.58

B–Y/R–Y Ratio: Balance (DAC 78) = 00 0.60 0.77 0.96

Output Amplitude V ariation as Burst is varied from 80 mVpp to 600 mVpp – 3.0 – dB

Color Kill Attenuation ($7C–7, 6 and $7D–6 = 011) – 40 – dB

Crosstalk with respect to Y1 Output (@ 1.0 MHz) –27 –20 –

Chroma Subcarrier Residual

(Measured at Y1 Output, with 17.7 MHz Crystal)

f = Subcarrier – 25 60 mVpp

2nd Harmonic Residual – 4.0 12

4th Harmonic Residual – 12 30

(Measured at R–Y, B–Y Outputs, with 17.7 or 14.3 MHz Crystal)

f = Subcarrier – 5.0 20

2nd Harmonic Residual – 5.0 20

4th Harmonic Residual – 15 50

Y1 Luma Output (Pin 33)

Clamp Level 0.4 1.1 1.8 Vdc

Output Impedance – 300 – Ω

Composite Video Mode ($77–6, 7 = 00)

Output Level versus Input Level

Delay = 000, Peaking = 111, f = 100 kHz 1.0 1.1 1.2 V/V

Delay = Min–to–Max, Peaking = Min–to–Max – 1.1 –

–3.0 dB Bandwidth (17.7 MHz Crystal, PAL Decoding selected,

Sound trap at 6.5 MHz, Peaking off)

Peaking Range ($7D–7, $7E–6/7 = 000 to 111, @ 3.0 MHz, with 17.7 MHz Crystal,

Sound trap at 6.5 MHz)

Overshoot with Minimum Peaking – 0 – %

Differential Non–linearity (Measured with Staircase) – 2.0 – %

Delay (Pin 1 or 3 to 33)

With 14.3 MHz Crystal: Minimum – 690 – ns

Maximum – 1040 –

With 17.7 MHz Crystal: Minimum – 594 –

Maximum – 876 –

NOTE: 1. This spec indicates a correct output amplitude at Pins 41 and 42, with respect to Y1 output. For standard color bar inputs, the output amplitude is

NOTE: 1. between 1.5 and 1.7 Vpp, with the settings in T ables 1 and 2.

= 25°C, V

A

CC1

= V

CC2

= V

= 5.0 V, unless otherwise noted.)

CC3

20 40 – dB

– 2.8 – MHz

5.0 8.0 10 dB

MOTOROLA ANALOG IC DEVICE DATA

5

Page 6

MC44011

ELECTRICAL CHARACTERISTICS

PAL/NTSC/S–VHS DECODER

S–VHS Mode ($77–6, 7 = 11)

Output Level versus Input Level (Delay = Min–to–Max) 1.0 1.1 1.2 V/V

–3.0 dB Bandwidth (17.7 MHz crystal, PAL Decoding selected,

Sound trap at 6.5 MHz)

Y/C Crosstalk Rejection 20 40 – dB

Delay (Luma input to Pin 33)

14.3 MHz Crystal: Minimum – 395 – ns

14.3 MHz Crystal: Maximum – 745 –

17.7 MHz Crystal: Minimum – 350 –

17.7 MHz Crystal: Maximum – 632 –

Crystal Oscillator

PLL Pull–in range with respect to Subcarrier Frequency

(Burst Level ≥ 30 mVpp): with 17.7 MHz Crystal – ±350 – Hz

(Burst Level ≥ 30 mVpp): with 14.3 MHz Crystal – ±300 –

4fsc Filter (Pin 44) DC Voltage

@ 14.3 MHz – 2.4 – Vdc

@ 17.7 MHz – 3.5 –

No Burst present – 1.3 –

DC Voltages Vdc

System Select (Pin 34)

NTSC Mode (SSA = 1, SSB = 0, SSC = 0, SSD = 0) 1.5 1.75 2.0

PAL Mode (SSA = 0, SSB = 1, SSC = 0, SSD = 0) 0 0.075 0.4

Color Kill Mode (SSA = 1, SSB = 1, SSC = 0, SSD = 0) – 0.075 –

External Mode (SSA = X, SSB = X, SSC = 1, SSD = 0) 3.7 4.0 4.3

Ident Filter (Pin 43)

NTSC Mode – 1.6 –

PAL Mode 1.2 1.5 1.8

No Burst present – 0.2 –

ACC Filter (Pin 2)

No Burst present – 0.25 –

Threshold for ACC Flag on 0.8 1.2 1.6

Burst = 50 mVpp – 1.4 –

Burst = 280 mVpp – 1.7 –

System Select Output Impedance – 40 100 kΩ

COLOR DIFFERENCE SECTION

RGB/YUV Outputs

Output Swing, Black–to–White (DAC $81 = 63) 2.0 3.0 – Vpp

THD (RGB Inputs to RGB Outputs @ 1.0 MHz, 0.7 Vpp) – 0.5 2.0 %

–3.0 dB Bandwidth – 6.0 – MHz

Clamp Level

RGB Outputs ($7D, 7E = 00) – 1.4 – Vdc

UV Outputs ($7D, 7E = 32) – 2.3 –

Red, Blue Clamp Level Change (DACs $7D, 7E varied from 00 to 63) 0.85 1.8 2.4

Crosstalk Rejection

Among RGB Outputs @ 1.0 MHz 20 40 – dB

Y1 to Y2 20 40 –

From RGB Outputs to Y1 or Y2 20 40 –

Input Black Clamp Voltage at Y2, B–Y, R–Y, and RGB 2.4 3.0 3.6 Vdc

Fast Commutate Input (Pin 25)

Switching Threshold Voltage – 0.5 – Vdc

Input Current @ Vin = 0 V – –7.5 – µA

Input Current @ Vin = 5.0 V – 0 –

Timing: Input Low–to–High (RGB Enable) – 50 – ns

Timing: Input High–to–Low (RGB Disable) – 90 –

(continued) (TA = 25°C, V

Characteristics UnitMaxTypMin

CC1

= V

CC2

= V

= 5.0 V, unless otherwise noted.)

CC3

– 4.5 – MHz

6

MOTOROLA ANALOG IC DEVICE DATA

Page 7

MC44011

ELECTRICAL CHARACTERISTICS (continued) (T

Characteristics UnitMaxTypMin

COLOR DIFFERENCE SECTION

Contrast (Gain) V/V

Y1 to RGB (DAC $81 = 32, DAC $86 = 00) 1.9 2.4 3.0

Y2 to RGB (DAC $81 = 32, DAC $86 = 00) 1.8 2.3 2.8

Green In (Pin 27) to Green Out (Pin 21) with YX Enabled 1.8 2.3 2.4

($82–6 = 1, DAC $81 and DAC $86 = 32)

Red–to–Green and Blue–to–Green Gain Ratio 0.8 1.0 1.2

RGB Input to RGB Output with YX Not Enabled 2.0 2.6 3.2

($82–6 = 0, DAC $81 and DAC $86 = 32)

Ratio (DAC $81 = 00 versus 32) – 0.2 0.4

Ratio (DAC $81 = 63 versus 32) 1.5 2.0 2.5

Red and Blue Trim Control (DACs $80, 82 varied from 00 to 63) ±5.0 ±30 ±60 %

Saturation (Average of R, G, B saturation levels with respect to Luma)

Inputs at Pins 29 to 31 (DAC $86 = 32) 50 90 130 %

Ratio (DAC $86 = 00 versus 32) – – 5

Ratio (DAC $86 = 63 versus 32) 150 170 190

Inputs at Pins 26 to 28 (DAC $86 = 32, $82–6 = 1) 70 125 180

Brightness

Black Level Range (Brightness = 00 to 63 with respect to Brightness setting of 32) ±0.3 ±0.5 ±0.7 Vdc

Red and Blue Trim Control (DACs $83, 85 varied from 00 to 63) ±0.05 ±0.3 ±0.6

Color Coefficients

G–Y Matrix Coefficient versus B–Y –0.21 –0.19 –0.17

G–Y Matrix Coefficient versus R–Y –0.56 –0.51 –0.46

YX Matrix (Inputs at Pins 26 to 28, $82–6 = 1):

Y versus R 0.28 0.30 0.32

Y versus G 0.57 0.59 0.61

Y versus B 0.09 0.11 0.13

HORIZONTAL TIME BASE SECTION (PLL #1)

Free–Running Period (Calibration mode in effect, Bit $86–6 = 1)

17.7 MHz Crystal selected ($84–6 = 0) 62.5 64.0 65.5 µs

14.3 MHz Crystal selected ($84–6 = 1) 62.5 63.5 65.5

VCO minimum period (Pin 11 Voltage at 1.2 V) 56 59.5 62 µs

VCO maximum period (Pin 11 Voltage at 2.8 V) 66 69.5 72

VCO Control Gain factor 5.0 8.5 12 µs/V

Phase Detector Current

High Gain ($83–6 = 1)

Low Gain–to–High Gain Current Ratio 0.32 0.38 0.44 µA/µA

Noise Gate Width ($77–2 = 0, Low Gain, see Figure 26) – 16 – µs

Horizontal Filter Switch (Pin 12)

Saturation Voltage (I12 = 20

Dynamic Impendance ($84–7 = 1) – <5.0 – kΩ

Parallel Resistance ($84–7 = 0) 0.6 1.0 – MΩ

Pins 8, 13, 14 Output Level

High (lO = –40 µA)

Low (lO = 800 µA) – 0.1 0.8

Burst Gate (Pin 8) Timing (See Figures 25, 27) µs

Rising edge from Sync leading edge (Pins 1, 3) 4.4 5.6 6.8

Rising edge from Sync center (Pins 26 to 29) – 2.5 –

Pulse Width 3.0 3.5 4.0

16Fh Output (Pin 13) Timing (Bit $85–6 = 0) (See Figures 25, 27)

Rising edge from Fh rising edge – 1.3 – µs

Duty Cycle – 50 – %

Composite Sync Output (Pin 13) Timing (Bit $85–6 = 1) µs

Input Sync center to Output Sync center (Pins 1, 3) – 0.95 –

Input Sync center to Output Sync center (Pins 26 to 29) – 0.4 –

µA)

= 25°C, V

A

CC1

= V

CC2

= V

= 5.0 V, unless otherwise noted.)

CC3

15 50 85 µA

– 10 100 mV

2.4 4.5 – Vdc

MOTOROLA ANALOG IC DEVICE DATA

7

Page 8

MC44011

ELECTRICAL CHARACTERISTICS

HORIZONTAL TIME BASE SECTION (PLL #1)

Fh Reference (Pin 14) Timing (See Figures 25, 27)

Rising edge from Sync center (Pins 1, 3) – 1.3 – µs

Rising edge from Sync center (Pins 26 to 29) – 650 – ns

Duty cycle – 50 – %

Sandcastle Output (Pin 35, see Figures 25, 27) Vdc

Output Voltage – Level 1 3.7 4.0 4.3

Output Voltage – Level 2 2.8 3.0 3.2

Output Voltage – Level 3 – 1.55 –

Output Voltage – Level 4 – 0.07 –

Rising edge from Sync center (Pins 1, 3) – –2.6 – µs

Rising edge from Sync center (Pins 26 to 29) – –3.3 –

High Time – 6.0 –

Level 2 Time – 5.0 –

Reference Voltage @ Pin 9 (I

PHASE–LOCKED PIXEL CLOCK SECTION (PLL #2)

VCO Frequency @ Pin 18 MHz

Minimum (Pin 16 = 1.6 V , $85–7 = 1) – 2.0 4.0

Maximum (Pin 16 = 4.0 V , $85–7= 0) 30 45 60

VCO Up (Flag 19) Threshold Voltage @ Pin 16 1.5 1.7 1.9 Vdc

VCO Down (Flag 20) Threshold Voltage @ Pin 16 3.1 3.3 3.5

VCO Control Voltage Range @ Pin 16 1.2 – 3.8 Vdc

VCO Control Gain factor ($7FDAC = 00, $85–7 = 0) 4.0 8.0 12 MHz/V

Charge Pump Current (Pin 16) 25 50 75 µA

High Gain ($83–7 = 0)

Current Ratio 0.3 0.4 0.5 µA/µA

Low Gain–to–High Gain

Pixel Clock Output (Pin 18) (Load = 3 FAST TTL loads + 10 pF)

Output Voltage – High – 3.9 – Vdc

Output Voltage – Low – 0.15 –

Rise Time @ 50 MHz – 7.0 – ns

Rise Time @ 9.0 MHz – 17 –

Fall Time @ 50 MHz – 5.0 –

Fall Time @ 9.0 MHz – 8.0 –

15 kHz Return (Pin 15)

Input Threshold Voltage – 1.5 – Vdc

Falling edge from Fh rising edge – 60 – ns

Minimum Input Low Time 200 – –

VERTICAL DECODER

Vertical Frequency Range 43.3 – 122 Hz

Vertical Sync Output

Saturation Voltage (lO = 800 µA) – 0.1 0.8 V

Leakage Current @ 5.0 V (Output high) – – 40 µA

Timing from Sync polarity reversal to Pin 4 falling edge (See Figures 33, 34) µs

($78–7 = 0) 32 36 40

($78–7 = 1) 62 68 74

Vertical Sync Pulse Width (Pin 4, NTSC or PAL) 490 500 510 µs

Field Ident (Pin 7) Output Voltage – High (lO = –40 µA) 2.4 4.5 – Vdc

Field Ident (Pin 7) Output Voltage – Low (lO = 800 µA) – 0.1 0.8

Field Ident (Pin 7) Timing – Fig. 33, 34 –

HORIZONTAL SYNC SEPARATOR

Sync Slicing Levels (Pins 1, 3) – 120 – mV

From Black Levelāā(Pins 26 to 29)

ref

(continued) (TA = 25°C, V

Characteristics UnitMaxTypMin

= 32 µA) 1.0 1.2 1.4 Vdc

CC1

= V

CC2

= V

= 5.0 V, unless otherwise noted.)

CC3

– 150 –

8

MOTOROLA ANALOG IC DEVICE DATA

Page 9

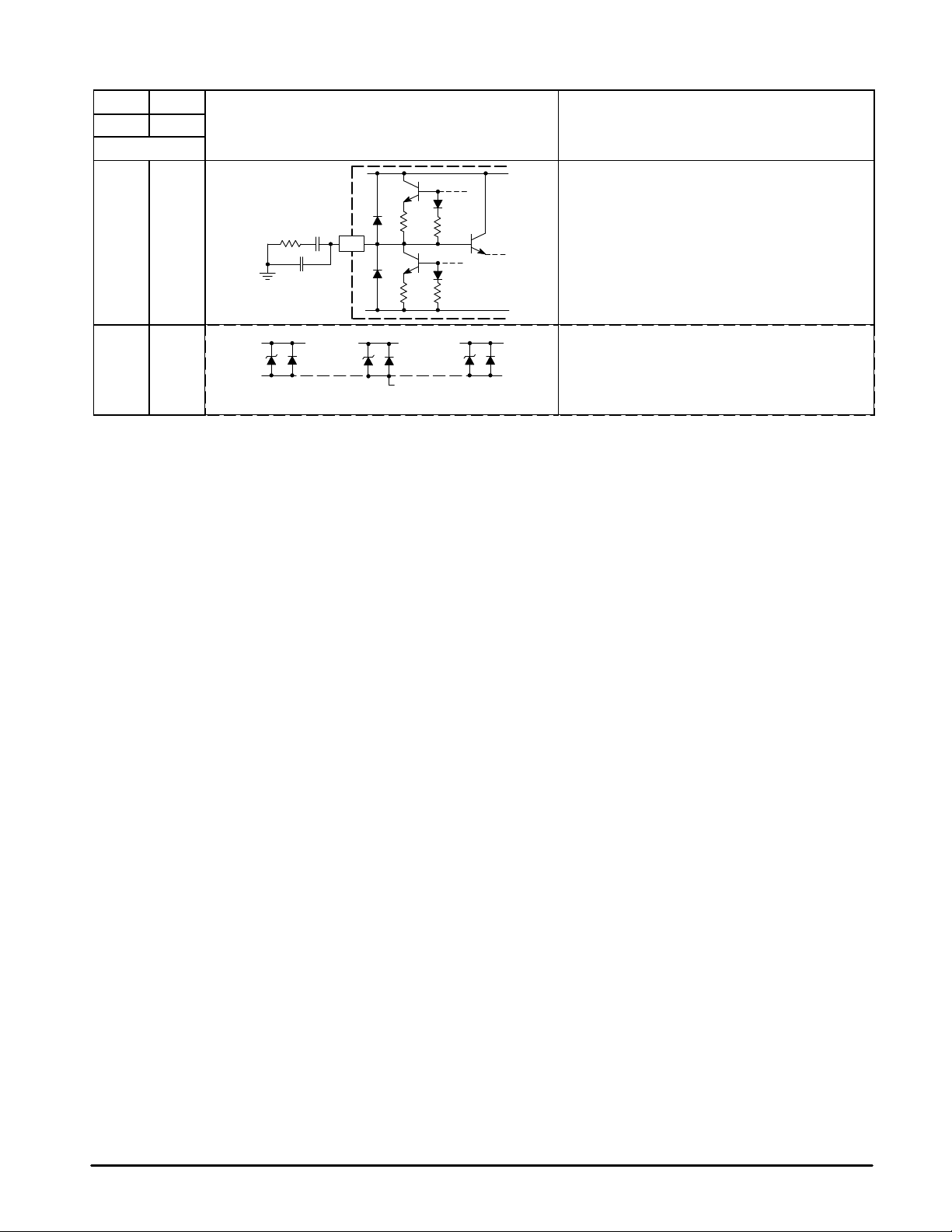

FB FN

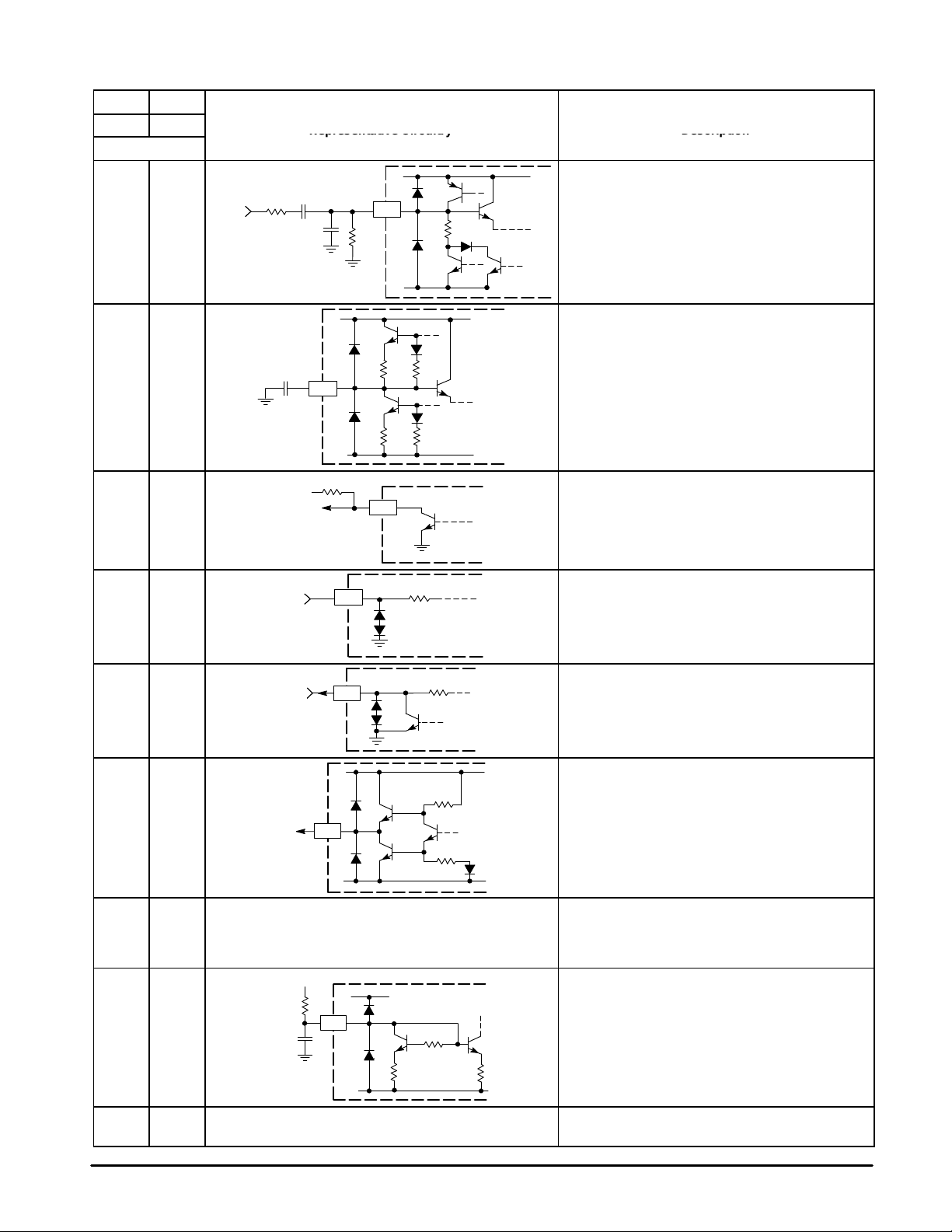

Representative Circuitry

Description

QFP PLCC

Pin

39, 41 1, 3

Video

Input

MC44011

PIN FUNCTION DESCRIPTION

Representative Circuitry Description

(Pin numbers refer to PLCC package)

0.47

470

47 pF

10 M

20 k

(Pin numbers refer to PLCC package)

Video Input 1 & 2 – Video 1 (Pin 1) and Video 2

(Pin 3) are composite video inputs. Either can be

NTSC or PAL. Input impedance is high, termination

must be external. Also used for the luma and chroma

components of an S–VHS signal. Selection of these

inputs is done by software. External components

protect against ESD and noise.

40 2

42 4

43 5

44 6

0.1

5.0

Vertical Sync

From MCU

To/From MCU

2

10 k

ACC Filter – A 0.1 µF capacitor at this pin filters the

feedback loop of the chroma automatic gain control

amplifier. Input chroma burst amplitude can be

between 30 and 600 mVpp.

Vertical Sync Output – An open collector output

4

5

6

100 k

180 k

requiring an external pull–up. Output is an active low

pulse, 500 µs wide, occurring each field. Timing of this

pulse depends on Bit $78–7.

SCL – Clock for the I2C bus interface. See Appendix C

for specifications. Maximum frequency is 100 kHz.

SDL – Bidirectional data line for the I2C bus interface.

As an output, it is an open collector. (Write Address

$8A, Read Address $8B)

1 7

7

(Same as Pin 7)

5.0

9

2 8

3 9

4 10

Field ID

110 k

2.2 µF / /

0.01

(See power distribution diagram at the end of this section.)

MOTOROLA ANALOG IC DEVICE DATA

8.0 k

100 k

20 k

12 k

Field ID – TTL level output indicating Field 1 or Field 2.

Polarity depends on state of Bit $78–7 (Vertical Sync

Delay). See T able 1 1 and Figure 33 and 34.

Burst Gate – TTL level output used for external

clamps, as well as internally. Pulse is active high,

≈ 3.5 µs wide, with the rising edge ≈ 3.0 µs after

center of selected incoming sync pulse.

Reference Current Input – Current supplied to this

pin, typically 32 µA from 5.0 V through a 110 kΩ

resistor, is the reference current for the calibration

circuit. Noise filtering should be done at the pin.

Voltage at this pin is typically 1.2 V.

Quiet Ground – Ground for the horizontal PLL filter

(PLL #1) at Pin 1 1.

9

Page 10

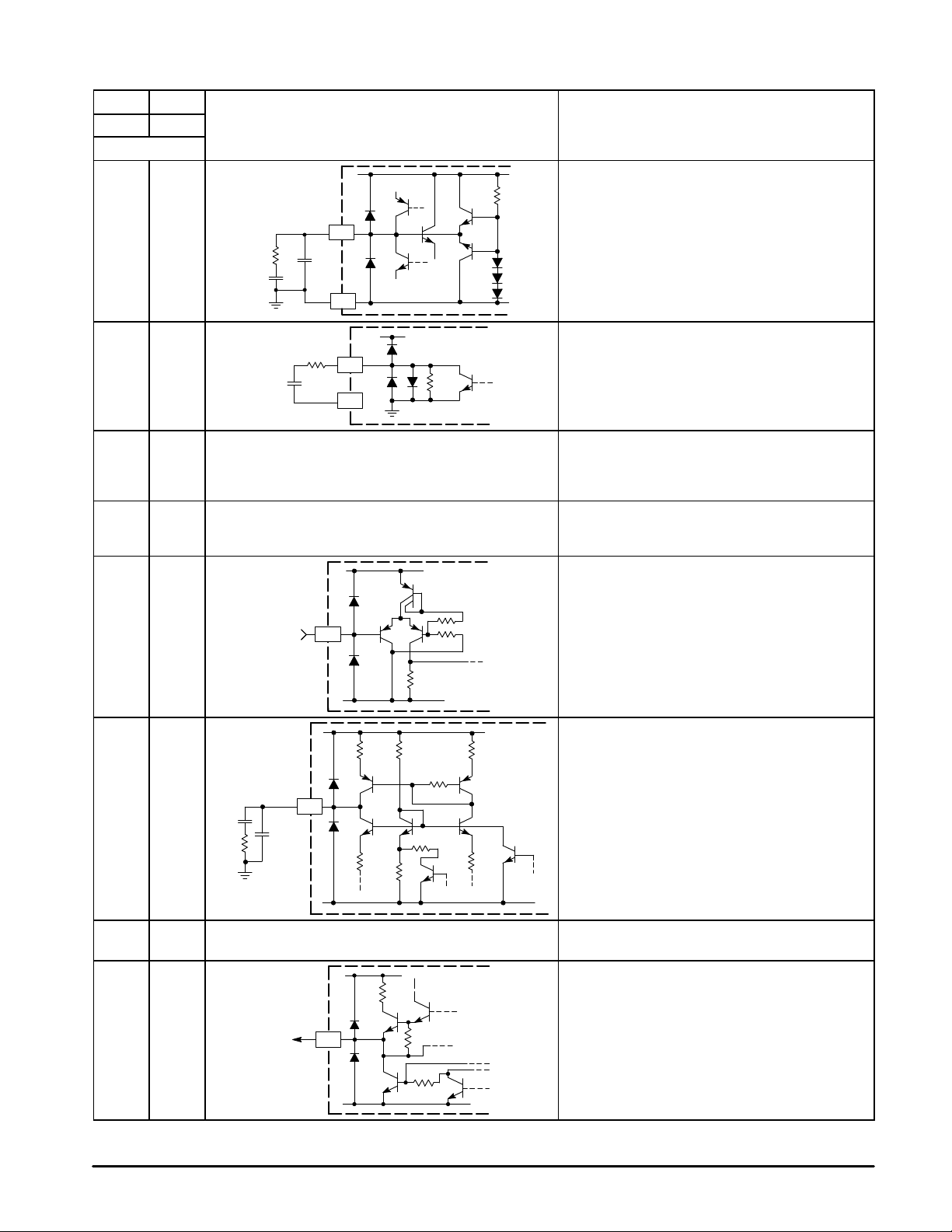

FB FN

QFP

PLCC

Pin

5 11

PIN FUNCTION DESCRIPTION (continued)

Representative Circuitry

Representative Circuitry

(Pin numbers refer to PLCC package)

(Pin numbers refer to PLCC package)

11

100 k

0.1

68 pF

10

MC44011

Description

(Pin numbers refer to PLCC package)

(Pin numbers refer to PLCC package)

H Filter – Components at this pin filter the output of

the phase detector of PLL #1. This PLL becomes

phase–locked to the selected incoming horizontal

sync. External component values are valid for NTSC

and PAL systems.

Description

6 12

7 13

8 14

9 15

10 16

0.047

10 k

470 pF

15 kHz

Return

4700 pF

12 k

12

(Same as Pin 7)

(Same as Pin 7)

15

16

11

Down

1.0 k

6.0 k

6.0 k

1.0 M

10 k

20 k

UpGain

Vert

Gate

H Filter Switch – An internal switch–to–ground which

permits altering the filtering action of the components

at Pin 11.

16 Fh/C

pin provides either a square wave equal to Fh x 16

(≈ 250 kHz), or composite sync, depending on the

setting of Bit $85–6.

Fh Reference – A TTL square wave output which is

phase–locked to the selected incoming horizontal sync.

The rising edge occurs ≈ 1.3 µs after sync center.

15 kHz Return – This TTL input receives the output of

an external frequency divider which is part of PLL #2

(Pixel Clock PLL). This signal will be phase and

frequency–locked to the Fh signal at Pin 14. If PLL #2

is not used, this pin should be connected to a 5.0 V

supply.

PLL #2 Filter – Components at this pin filter the output

of the phase detector of PLL 2. This PLL becomes

phase–locked to the Fh signal at Pin 14.

Recommended values for filter components are

shown. External components should be connected to

ground at Pin 17. If PLL #2 is not used, this pin should

be grounded.

– A TTL level output from PLL #1. This

Sync

11 17

12 18

10

(See power distribution diagram at the end of this section.)

200

Pixel

Clock

Output

18

Gnd3 – Ground for the high frequency PLL #2. Signals

at Pins 15 to 19 should be referenced to this ground.

Pixel Clock Output – Sampling clock output (TTL) for

external A/D converters, and for the external frequency

divider. Frequency range at this pin is 6.0 to 40 MHz.

MOTOROLA ANALOG IC DEVICE DATA

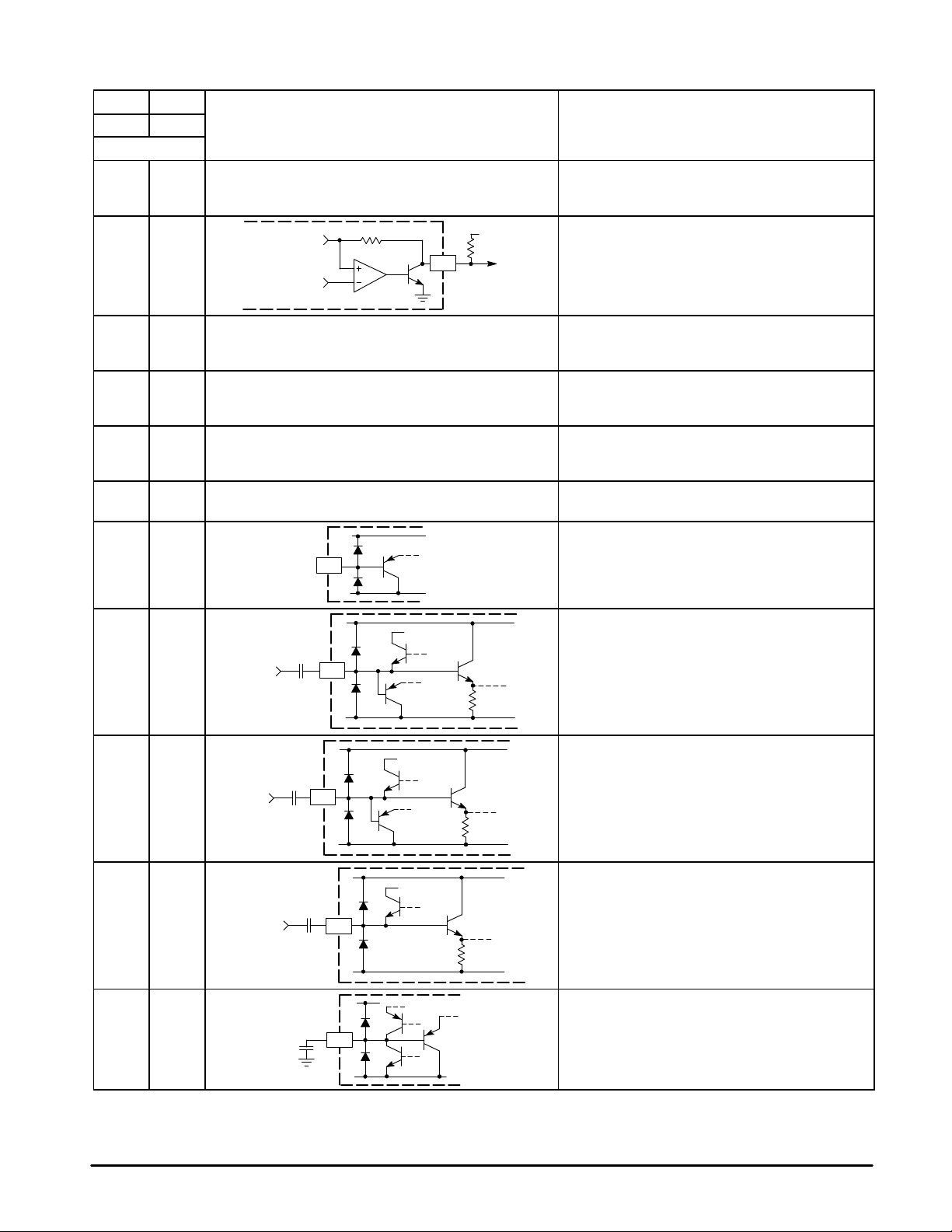

Page 11

FB FN

QFP

PLCC

Pin

13 19

14 20

MC44011

PIN FUNCTION DESCRIPTION (continued)

Representative Circuitry

Representative Circuitry

(Pin numbers refer to PLCC package)

(Pin numbers refer to PLCC package)

(See power distribution diagram at the end of this section.)

20

5.0 V

390

Output

Color

& Gain

Brightness

36 k

Description

(Pin numbers refer to PLCC package)

(Pin numbers refer to PLCC package)

V

– A 5.0 V supply (±5%), for the high frequency

CC3

PLL #2. Decoupling must be provided from this pin to

Pin 17. Ripple on this pin will affect pixel clock jitter.

R/V Output – Red (in RGB mode), or R–Y (in YUV

mode), output from the color difference stage. A

pull–up (390 Ω) to 5.0 V is required. Blank level is

≈ 1.4 Vdc. Maximum amplitude is ≈ 3.0 Vpp,

black–to–white.

Description

15 21

16 22

17 23

18 24

19 25

20, 21,2226, 27,

28

23 29

(Same as Pin 20)

(Same as Pin 20)

(See power distribution diagram at the end of this section.)

(See power distribution diagram at the end of this section.)

25

V

ref

R, G, B

Inputs

100 k

V

ref

Y2

Input

29

100 k

G/Y Output – Green (in RGB mode), or Y (in YUV

mode), output from the color difference stage (same

as Pin 20).

B/U Output – Blue (in RGB mode), or B–Y (in YUV

mode), output from the color difference stage (same

as Pin 20).

V

– A 5.0 V supply (±5%), for the color difference

CC2

stage. Decoupling must be provided from this pin to

Pin 24.

Gnd2 – Ground for the color difference stage. Signals

at Pins 20 to 31 should be referenced to this pin.

FC – Fast Commutate switch. Taking this pin high

(TTL level) connects the RGB inputs (Pins 26 to 28)

to the RGB outputs (Pins 20 to 22), permitting an

overlay function. The switch can be disabled in

software (Bit $80–7).

Blue (26), Green (27), Red (28) Inputs – Inputs to

the color difference stage. Designed to accept

standard analog video levels, these input pins have a

clamp and sync separator. They are selected with

Pin 25 or in software (Bit $80–7).

Y2 Input – Luma #2/Composite sync input. This

luma input to the color difference stage is used in

conjunction with auxiliary color difference inputs,

and/or as a sync input. Clamp and sync separator

are provided.

24, 25 30, 31

R–Y, B–Y

Inputs

26 32

0.47

32

MOTOROLA ANALOG IC DEVICE DATA

B–Y (30), R–Y (31) Inputs – Inputs to the color

V

ref

100 k

difference stage. Designed for standard color

difference levels, these inputs can be capacitor

coupled from the color difference outputs, from a delay

line, or an auxiliary signal source. Input clamp is

provided.

Y1 Clamp – A 0.47 µF capacitor at this pin provides

clamping for the Luma #1 output.

11

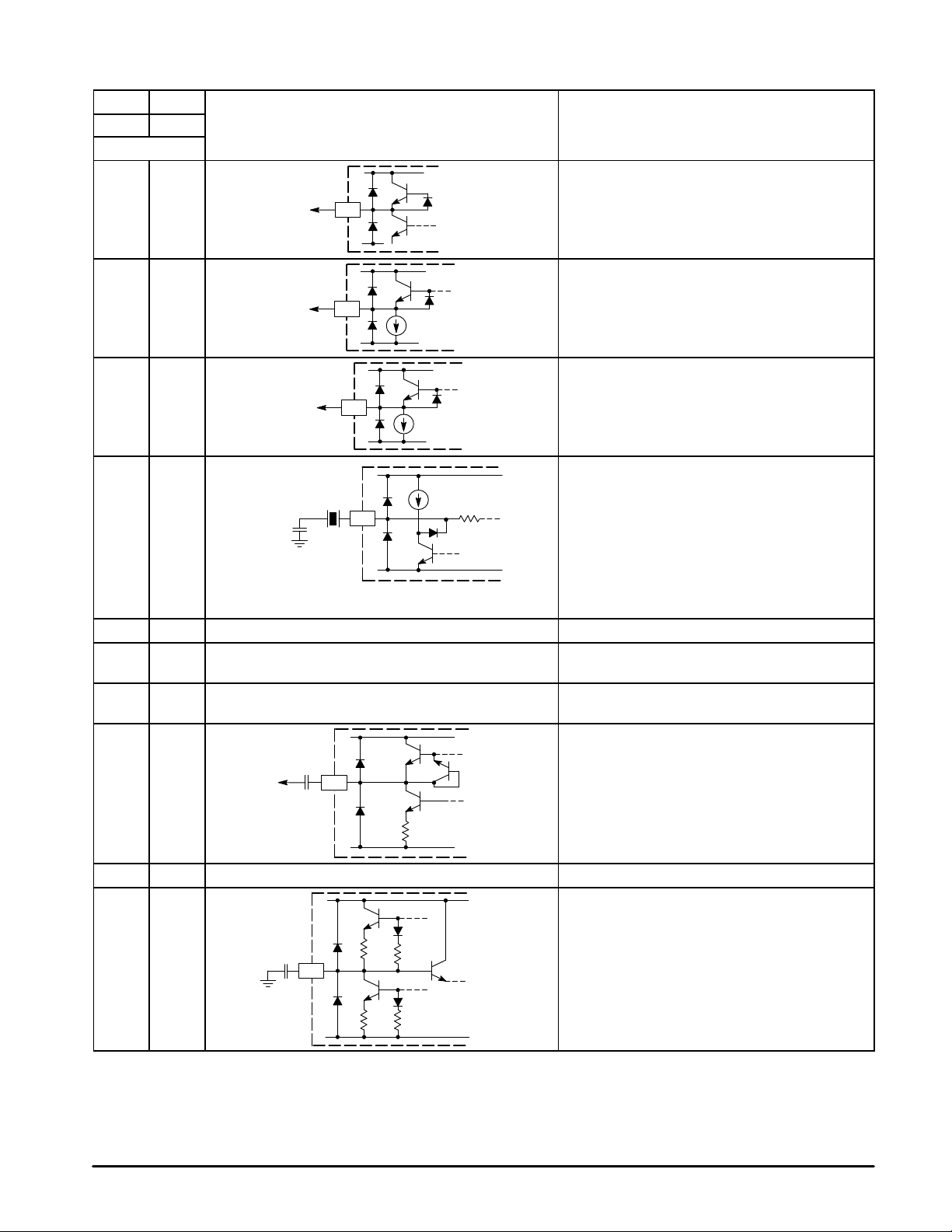

Page 12

FB FN

QFP

PLCC

Pin

27 33

MC44011

PIN FUNCTION DESCRIPTION (continued)

Representative Circuitry

Representative Circuitry

(Pin numbers refer to PLCC package)

(Pin numbers refer to PLCC package)

Y1

Output

33

Description

(Pin numbers refer to PLCC package)

(Pin numbers refer to PLCC package)

Y1 Output – Luma #1 output. This output from the

PAL/NTSC/S–VHS decoder is the luma component of

the decoded composite video at Pin 1 or 3. It is

internally directed to the color difference stage.

Description

28 34

System

Select

29 35

Sandcastle

Pulse

30, 32 36, 38

R = 400 Ω at Pin 38

Ω

R = 300

31 37 No Connect – This pin is to be left open.

33 39

34 40

35 41

(See power distribution diagram at the end of this section.)

(See power distribution diagram at the end of this section.)

at Pin 36

B–Y

34

35

14.3 MHz

17.7 MHz

41

20 µA

R

System Select – A multi–level dc output which

indicates the color decoding system to which the

PAL/NTSC detector is set by the software. This output

is used by the MC44140 chroma delay line.

Sandcastle Pulse – A multi–level timing pulse output

used by the MC44140 chroma delay line. This pulse

encompasses the horizontal sync and burst time.

Xtal 2 (36), Xtal 1 (38) – Designed for connection of 4x

subcarrier color crystals. Selection is done in software.

The selected frequency is used by the PAL/NTSC

detector; system identifier; all notches and traps; delay

lines; and the horizontal calibration circuit.

The crystal frequency should be:

14.3 MHz at Pin 36 for NTSC,

17.7 MHz at Pin 38 for PAL.

(See Table 17 for crystal specifications)

Ground 1 – Ground for all sections except PLL #2

and the color difference stage.

V

– A 5.0 V (±5%), supply to all sections except

CC1

PLL #2 and the color difference stage.

B–Y Output – Output from the PAL/NTSC decoder, it

is typically capacitor–coupled to a delay line or to the

B–Y input. This pin is clamped, and filtered at the

color subcarrier frequency , 2x, and 8x that frequency.

36 42 (Same as Pin 41) R–Y Output – Output from the PAL/NTSC decoder.

37 43

0.1

43

12

Ident Filter – A 0.1 µF capacitor filters the system

identification circuit in the NTSC/PAL decoder.

MOTOROLA ANALOG IC DEVICE DATA

Page 13

FB FN

QFP

PLCC

Pin

38 44

MC44011

PIN FUNCTION DESCRIPTION (continued)

Representative Circuitry

Representative Circuitry

(Pin numbers refer to PLCC package)

(Pin numbers refer to PLCC package)

0.1

47 k

2200 pF

44

Description

(Pin numbers refer to PLCC package)

(Pin numbers refer to PLCC package)

Crystal PLL Filter – Components at this pin filter the

PLL for the crystal chroma oscillator circuit.

Description

4, 11,

13, 17,

18, 33,

34

10, 17,

19, 23,

24, 39,

40

V

CC1

7.0 V

(Dashed lines indicate substrate connection.)

7.0 V

V

CC2

7.0 V

V

CC3

Power Distribution – The three VCC pins must be

externally connected to 5.0 V (±5%) supply. The four

grounds must be externally tied together, preferably to

a ground plane.

MOTOROLA ANALOG IC DEVICE DATA

13

Page 14

10

MC44011

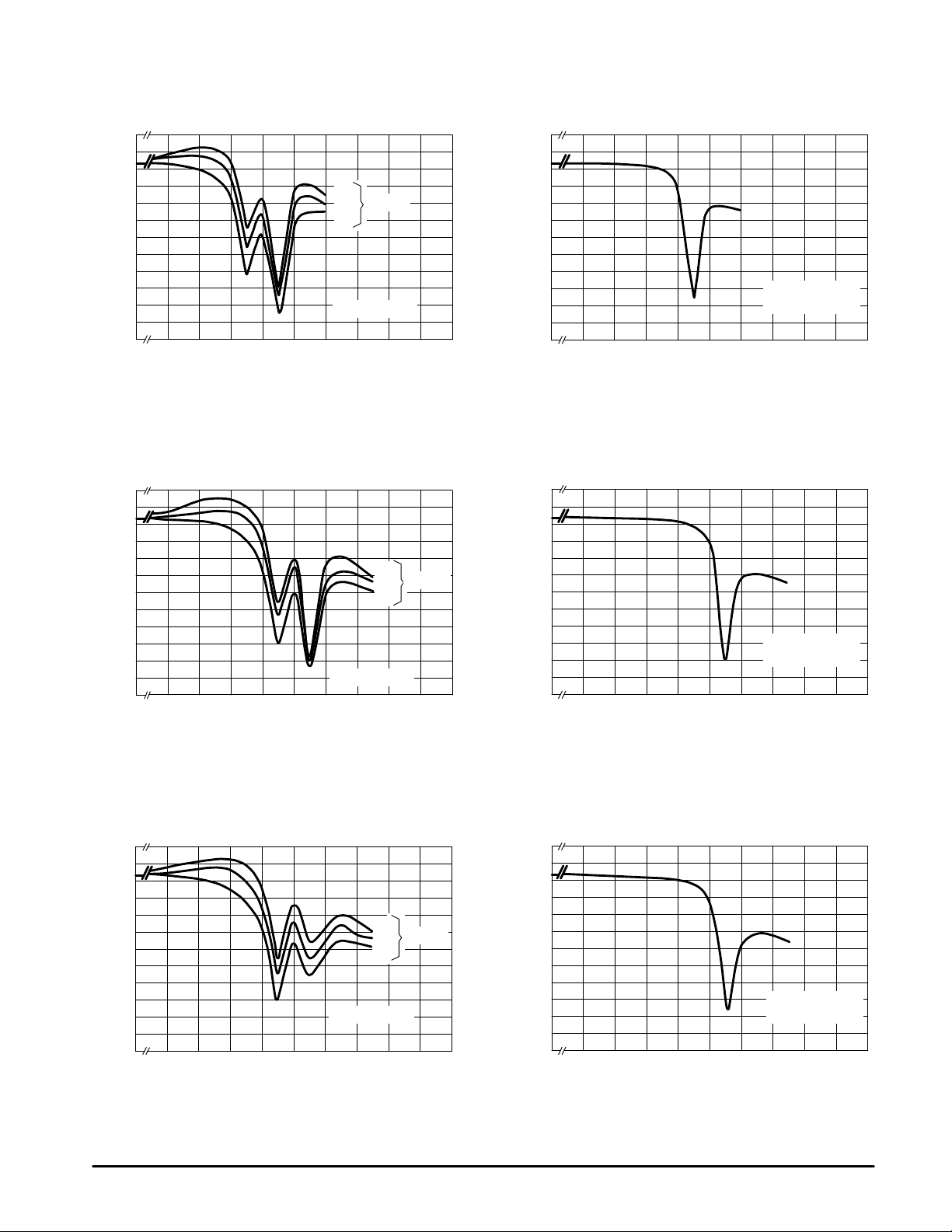

Luma Frequency Response (14.3 MHz) Crystal, (4.5 MHz) Sound Trap

Figure 2. Composite Video Mode Figure 3. S–VHS Mode

10

0

–10

–20

–30

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–50

0.1

10

0

–10

–20

–30

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–50

0.1

0

000

Peaking

010

111

Sound Trap = 1,1

1.0 3.0 5.0 7.0 10

f, FREQUENCY (MHz)

–10

–20

–30

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–50

0.1 1.0 3.0 5.0 7.0 10

f, FREQUENCY (MHz)

Sound Trap = 1,1

All Peaking Settings

Luma Frequency Response (17.7 MHz) Crystal, (5.5 MHz) Sound Trap

Figure 4. Composite Video Mode Figure 5. S–VHS Mode

10

0

000

Peaking

010

111

Sound Trap = 1,1

1.0 3.0 5.0 7.0 10 0.1 1.0 3.0 5.0 7.0 10

f, FREQUENCY (MHz) f, FREQUENCY (MHz)

–10

–20

–30

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–50

Sound Trap = 1,1

All Peaking Settings

10

0

–10

–20

–30

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–50

0.1

14

Luma Frequency Response (17.7 MHz) Crystal, (5.5/5.75 MHz) Sound Trap

Figure 6. Composite Video Mode

000

Peaking

010

111

Sound Trap = 1,1

1.0 3.0 5.0 7.0 10

f, FREQUENCY (MHz)

10

0

–10

–20

–30

Sound Trap = 0,1

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–50

0.1 1.0 3.0 5.0 7.0 10

f, FREQUENCY (MHz)

All Peaking Settings

MOTOROLA ANALOG IC DEVICE DATA

Figure 7. S–VHS Mode

Page 15

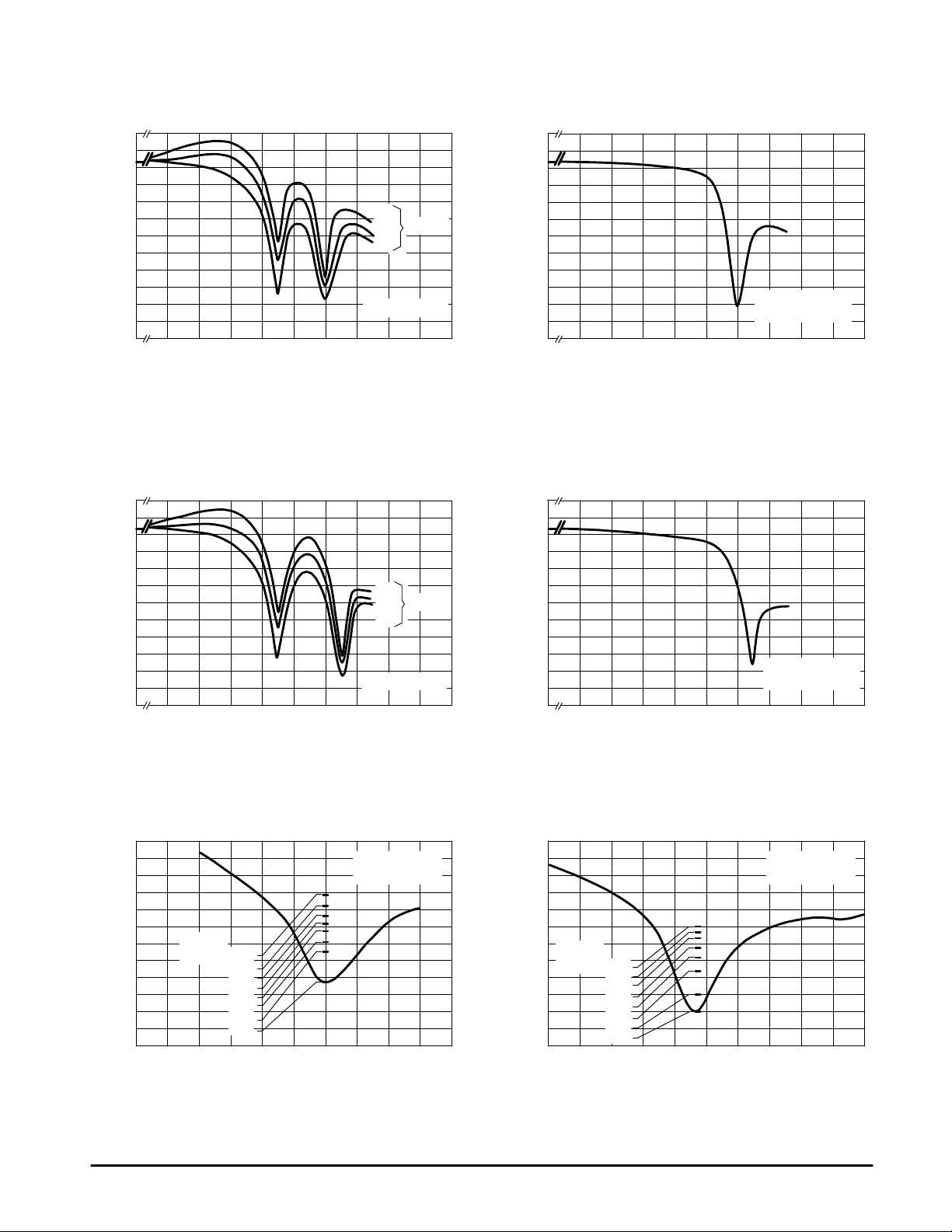

MC44011

Luma Frequency Response (17.7 MHz) Crystal, (6.0 MHz) Sound Trap

Figure 8. Composite Video Mode

10

0

–10

000

Peaking

–20

010

111

–30

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–50

0.1 1.0 3.0 5.0 7.0 10 0.1 1.0 3.0 5.0 7.0 10

Sound Trap = 1,0

10

0

–10

–20

–30

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–50

Figure 9. S–VHS Mode

Sound Trap = 1,0

All Peaking Settings

f, FREQUENCY (MHz)f, FREQUENCY (MHz)

Luma Frequency Response (17.7 MHz) Crystal, (6.5 MHz) Sound Trap

Figure 10. Composite Video Mode Figure 11. S–VHS Mode

10

–10

–20

–30

0

000

Peaking

010

111

10

0

–10

–20

–30

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–50

0.1

–10

–15

–20

–25

–30

–35

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–40

3.0

Sound Trap = 0,0

All Peaking Settings

Sound Trap = 0,0

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–50

1.0 3.0 5.0 7.0 10 1.0 3.0 5.0 7.0 10

0.1

f, FREQUENCY (MHz) f, FREQUENCY (MHz)

Figure 12. (3.58 MHz) Chroma Notch Figure 13. (4.43 MHz) Chroma Notch

–10

Gain at

Peaking =

000

001

100

101

010

011

110

111

Sound Trap = 1,1

14.3 MHz Crystal

–15

–20

–25

Gain at

Peaking =

–30

–35

dB GAIN AT Y1 RELATIVE TO VIDEO 1

3.5 4.0 4.5 5.0

–40

4.0

000

001

100

101

010

011

110

111

f, FREQUENCY (MHz)f, FREQUENCY (MHz)

Sound Trap = 1,1

17.7 MHz Crystal

MOTOROLA ANALOG IC DEVICE DATA

15

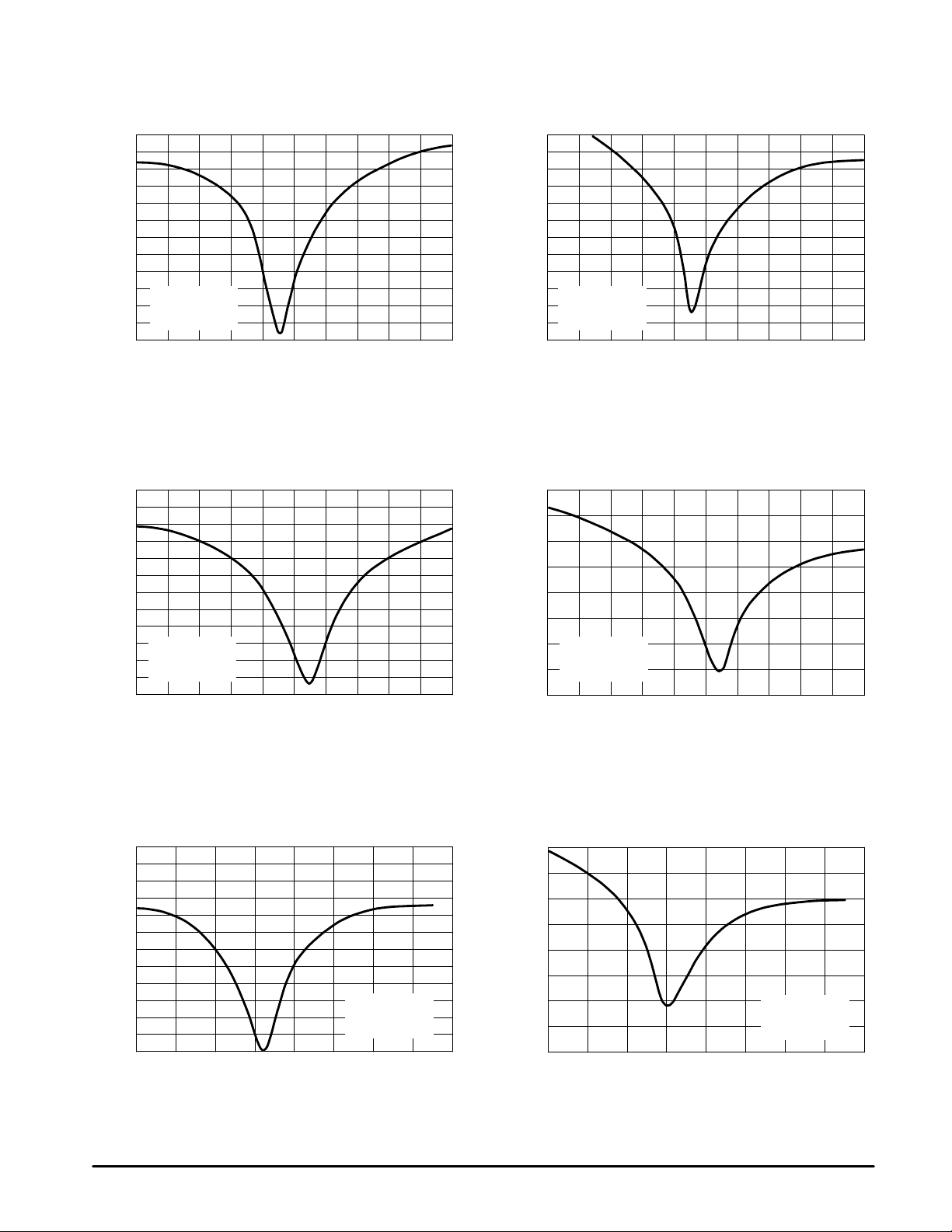

Page 16

–15

MC44011

(4.5 MHz) Sound Trap

Figure 14. Composite Video Mode Figure 15. S–VHS Mode

–10

–20

–25

–30

–35

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–45

4.0

–15

–20

–25

–30

–35

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–45

5.0

–15

–20

–25

–30

Sound Trap = 1,1

Peaking = 111

14.3 MHz Crystal

dB GAIN AT Y1 RELATIVE TO VIDEO 1

4.5 5.0 4.0 4.5 5.0

Sound Trap = 1,1

–35

Peaking = 111

14.3 MHz Crystal

–40

f, FREQUENCY (MHz)f, FREQUENCY (MHz)

(5.5 MHz) Sound Trap

Figure 16. Composite Video Mode Figure 17. S–VHS Mode

–5.0

–10

–15

–20

–25

–30

–35

Sound Trap = 1,1

Peaking = 111

17.7 MHz Crystal

dB GAIN AT Y1 RELATIVE TO VIDEO 1

5.5 6.0 5.5 6.0

f, FREQUENCY (MHz) f, FREQUENCY (MHz)

Sound Trap = 1,1

Peaking = 111

–40

17.7 MHz Crystal

–45

5.0

–10

–15

–20

–25

–30

–35

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–40

5.0

16

(5.5 + 5.75 MHz) Sound Trap

Figure 18. Composite Video Mode

Sound Trap = 0,1

Peaking = 111

17.7 MHz Crystal

5.4 6.6 5.4 6.65.8 6.25.8 6.2

–5.0

–10

–15

–20

–25

–30

–35

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–45

5.0

Figure 19. S–VHS Mode

Sound Trap = 0,1

Peaking = 111

17.7 MHz Crystal

f, FREQUENCY (MHz)f, FREQUENCY (MHz)

MOTOROLA ANALOG IC DEVICE DATA

Page 17

MC44011

(6.0 MHz) Sound Trap

–10

–15

–20

–25

–30

–35

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–40

5.5

–15

–20

Figure 20. Composite Video Mode

Sound Trap = 1,0

Peaking = 111

17.7 MHz Crystal

6.0 6.5 5.5 6.0 6.5

Figure 22. Composite Video Mode

–5.0

–10

–15

–20

–25

–30

–35

–40

–45

(6.5 MHz) Sound Trap

–15

–20

Figure 21. S–VHS Mode

Sound Trap = 1,0

Peaking = 111

17.7 MHz Crystal

f, FREQUENCY (MHz)f, FREQUENCY (MHz)

Figure 23. S–VHS Mode

–25

–30

–35

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1

–45

6.0

–25

–30

–35

Sound Trap = 0,0

Peaking = 111

17.7 MHz Crystal

6.5 7.0 6.5 7.0

f, FREQUENCY (MHz) f, FREQUENCY (MHz)

–40

dB GAIN AT Y1 RELATIVE TO VIDEO 1 dB GAIN AT Y1 RELATIVE TO VIDEO 1

–45

6.0

Figure 24. FC Input Current

0

–20

A)

µ

(

–40

–60

INPUT CURRENT

,l

in

–80

VCC = 5.0 V

Sound Trap = 0,0

Peaking = 111

17.7 MHz Crystal

–100

0

MOTOROLA ANALOG IC DEVICE DATA

1.0 4.02.0 3.0

PIN 25 VOLTAGE (V)

5.0

17

Page 18

Video Input

(@ Pins 1 or 3)

MC44011

Figure 25. Horizontal PLL1 Timing/Composite Video Inputs

C

L

Burst Gate

(Pin 8)

Fh Ref

(Pin 14)

16Fh Out

(Pin 13)

Comp Sync Out

(Pin 13)

Sandcastle Out

(Pin 35)

1.3

µ

2.6

3.1 µs

s

0.7

3.3 µs

µ

s

3.5 µs

4.5 V

1/2Fh

1.3

µ

s

µ

s

(1.4 µs during vertical interval)

4.0 V

3.0 V

5.0 µs5.9 µs

4.5 V

4.5 V

1/16Fh

4.5 V

1.55 V

0 V

18

NOTE: In above waveforms, all timing is referenced to the center of the incoming Sync Pulse at Pin 1 or 3.

Above timings based on a 4.6

Lower two levels of Sandcastle output alternate, based on video system in effect.

All timings are nominal, and apply to both PAL and NTSC signals.

µs wide sync pulse.

Figure 26. Horizontal PLL1 Noise Gate and Filter Pin

Video Input

(@ Pins 1 or 3)

Noise Gate

Charge Pump Current

(Pin 11)

Voltage Waveform

(Pin 11)

16 µs

700 mVpp with High Gain

250 mVpp with Low Gain

MOTOROLA ANALOG IC DEVICE DATA

Page 19

Video Input

(@ Pins 26 to 29)

MC44011

Figure 27. Horizontal PLL1 Timing/R, G, B and Y2 Inputs

C

L

Burst Gate

(Pin 8)

Fh Ref

(Pin 14)

16Fh Out

(Pin 13)

Comp Sync Out

(Pin 13)

Sandcastle Out

(Pin 35)

650 ns

3.3 µs

5.9 µs

2.5

µ

2.0

4.7 µs

3.5 µs

s

µ

s

1.3

µ

s

(1.4 µs during vertical interval)

4.0 V

5.0 µs

4.5 V

4.5 V

1/2Fh

4.5 V

1/16Fh

4.5 V

3.0 V

1.55 V

0 V

R, G, B Outputs

(@ Pins 20 to 22)

NOTE: In above waveforms, all timing is referenced to the center of the incoming Sync Pulse at Pin 26 to 28, or 29.

Above timings based on a 4.6

Lower two levels of Sandcastle output alternate, based on video system in effect.

C

L

70 ns

MOTOROLA ANALOG IC DEVICE DATA

µs wide sync pulse.

19

Page 20

Video Input

(@ Pins 1 or 3)

R–Y, B–Y Outputs

(@ Pins 41, 42)

MC44011

Figure 28. System Timing/Video Inputs to RGB Outputs

50%

700 ns

50%

850 ns

50%

R, G, B Outputs

(@ Pins 20 to 22)

Input @ Pin 25

R, G, B Outputs

(@ Pins 20 to 22)

50 ns

Color Difference

Inputs Enabled

Figure 29. Fast Commutate Timing

0.5 V

50%

RGB Inputs

Enabled

0.5 V

90 ns

50%

Color Difference

Inputs Enabled

20

MOTOROLA ANALOG IC DEVICE DATA

Page 21

Composite Input

(@ Pins 1, 3, 26 to 29)

Fh Ref

(Pin 14)

Burst Gate

(Pin 8)

Composite Sync

(Pin 13)

MC44011

Figure 30. Horizontal Outputs versus Fields (NTSC System)

Line 1

Field 1Field 2

Composite Input

(@ Pins 1, 3, 26 to 29)

Fh Ref

(Pin 14)

Burst Gate

(Pin 8)

Composite Sync

(Pin 13)

Field 2Field 1

MOTOROLA ANALOG IC DEVICE DATA

21

Page 22

Composite Input

(@ Pins 1, 3, 26 to 29)

Fh Ref

(Pin 14)

Burst Gate

(Pin 8)

Composite Sync

(Pin 13)

MC44011

Figure 31. Horizontal Outputs versus Fields (PAL System)

Line 1

Field 1/3Field 2/4

Composite Input

(@ Pins 1, 3, 26 to 29)

Fh Ref

(Pin 14)

Burst Gate

(Pin 8)

Composite Sync

(Pin 13)

Fh Ref

(Pin 14)

Field 2/4Field 1/3

Figure 32. Horizontal PLL2 Timing

60 ns

22

15 kHz Return

(Pin 15)

Determined by

External Circuit

(Must be > 200 ns)

MOTOROLA ANALOG IC DEVICE DATA

Page 23

MC44011

Figure 33. Vertical T iming (NTSC System)

A) Bit $78–7 = 0

Video Input

Vert Sync Out

(Pin 4)

Field Ident Out

(Pin 7)

Video Input

Vert Sync Out

(Pin 4)

Field Ident Out

(Pin 7)

B) Bit $78–7 = 1

Line 1

Line 1

36

µ

s

Field 1Field 2

110 µs

µ

s

36

Field 2Field 1

68 µs

500 µs

500 µs

Video Input

Vert Sync Out

(Pin 4)

Field Ident Out

(Pin 7)

Video Input

Vert Sync Out

(Pin 4)

Field Ident Out

(Pin 7)

µ

s

68

Field 1Field 2

100

µ

s

µ

s

68

Field 2Field 1

144 µs

500 µs

500 µs

MOTOROLA ANALOG IC DEVICE DATA

23

Page 24

MC44011

Figure 34. Vertical T iming (PAL System)

A) Bit $78–7 = 0

Video Input

Vert Sync Out

(Pin 4)

Field Ident Out

(Pin 7)

Video Input

Vert Sync Out

(Pin 4)

Field Ident Out

(Pin 7)

Line 1

36

36 µs

Field 1/3Field 2/4

Field 2/4Field 1/3

68 µs

µ

s

110 µs

500 µs

500 µs

B) Bit $78–7 = 1

Video Input

Vert Sync Out

(Pin 4)

Field Ident Out

(Pin 7)

Video Input

Vert Sync Out

(Pin 4)

Field Ident Out

(Pin 7)

Line 1

Field 1/3Field 2/4

Field 2/4Field 1/3

µ

68

100 µs

68

µ

144 µs

s

500 µs

s

500 µs

24

MOTOROLA ANALOG IC DEVICE DATA

Page 25

MC44011

FUNCTIONAL DESCRIPTION

Introduction

The MC44011, a member of the MC44000 Chroma 4

family , is a composite video decoder which has been tailored

for applications involving multimedia, picture–in–picture, and

frame storage (although not limited to those applications).

The first stage of the MC44011 provides color difference

signals (R–Y, B–Y, and Y) from one of two (selectable)

composite video inputs, which are designed to receive PAL,

NTSC, and S–VHS (Y,C) signals. The second stage provides

either RGB or YUV outputs from the first stage’s signals, or

from a separate (internally selectable) set of RGB inputs,

permitting an overlay function to be performed. Adjustments

can be made to saturation; hue; brightness; contrast;

brightness balance; contrast balance; U and V bias;

subcarrier phase; and color difference gain ratio.

The above mentioned video decoding sections provide the

necessary luma/delay function, as well as all necessary

filters for sound traps, luma/chroma separation, luma

peaking, and subcarrier rejection. External tank circuits and

luma delay lines are not needed. For PAL applications, the

MC44140 chroma delay line provides the necessary

line–by–line corrections to the color difference signals

required by that system.

The MC44011 provides a pixel clock to set the sampling

rate of external A/D converters. This pixel clock, and other

horizontal frequency related output signals, are

phase–locked to the incoming sync. The VCO’s gain is

adjustable for optimum performance. The MC44011 also

provides vertical sync and field identification (Field 1, Field 2)

outputs.

Selection of the various inputs, outputs, and functions, as

well as the adjustments, is done by means of a two–wire I2C

interface. The basic procedure requires the microprocessor

system to read the internal flags of the MC44011, and then

set the internal registers appropriately. This I2C interface

eliminates the need for manual controls (potentiometers) and

external switches. All of the external components for the

MC44011, except for the two crystals, are standard value

resistors and capacitors, and can be non–precision.

(The DACs mentioned in the following description are 6–bits wide. The

settings mentioned for them are given in decimal values of 00 to 63.

These are not hex values.)

P AL/NTSC/S–VHS Decoder

A block diagram of this decoder section is shown in

Figure 35. This section’s function is to take the incoming

composite video (at Pins 1 or 3), separate it into luma and

chroma information, determine if the signal is PAL or NTSC

(for the flags), and then provide color difference and luma

signals at the outputs. If the input is S–VHS, the luma/chroma

separation is bypassed, but the other functions are still

in effect.

Comp

Video 1

Comp

Video 2

ACC Filter

Chroma PLL Filter

Xtal 1

Xtal 2

Figure 35. PAL/NTSC/S–VHS Decoder Block Diagram

Select

($88–7)

1

3

To

Sync

Sep

2

44

38

36

Switches shown with control bits = 0.

4.4/4.8/5.2

5.5/6.0/6.5 MHz

($7B–7,6)

($77–6)

PLL

Oscillator

Sound

Trap

Phase Adjust ($79–5/0)

C

Chroma

Filter

Crystal Select

($7A–7)

Chroma Trap and

Luma Peaking

($7D–7; $7E–7,6)

Flag 23

C

(ACC Active)

ACC

($77–7)

295/244 ns

Luma

Delay

Flag 24

(PAL)

PAL/NTSC

Decoder

Saturation ($87–5/0)

Hue ($88–5/0)

Color Balance ($78–5/0)

Color System

($7C–7,6; $7D–6)

Blanking

To Color

Diff Stage

Adjustable

Luma Delay

($7F–7,6; $80–6)

Ident

Circuit

3.6/7.2/28.6/4.4/

8.8/35.4 MHz Notch

C

3.6/7.2/28.6/4.4/

8.8/35.4 MHz Notch

33

32

34

43

42

41

Y1 Out

Y1 Clamp

System

Select

Ident

Filter

R–Y Out

B–Y Out

MOTOROLA ANALOG IC DEVICE DATA

25

Page 26

MC44011

17.73 MHZ

14.32 MHz

Inputs

The inputs at Pins 1 and 3 are high impedance inputs

designed to accept standard 1.0 Vpp positive video signals

(with negative going sync). The inputs are to be

capacitor–coupled so as not to upset the internal dc bias.

When normal composite video is applied, the desired input is

selected by Bit $88–7. Bits $77–6 and $77–7 must be set to

0 so that their switches are as shown in Figure 35. The

selected signal passes through the sound trap, and is then

separated by the chroma trap and the chroma (high

pass) filter.

When S–VHS signals (Y,C) are applied to the two inputs,

Bit $88–7 is used to direct the luma information to the sound

trap, and the chroma information to the ACC circuit

(Bit $77–6 must be set to a Logic 1). Bit $77–7 is normally

set to a Logic 1 in this mode to bypass the first luma delay

line and the chroma trap, but it can be left 0 if the additional

delay is desired.

Sound Trap

The sound trap will filter out any residual sound subcarrier

at the frequency selected by control bits T1 and T2 according

to Table 3. The accuracy of the notch frequency is directly

related to the selected crystal frequency.

T able 3. Sound Trap Frequency

Crystal

Frequency

T1

($7B–7)T1($7B–6)

0 0 6.5 MHz

0 1 5.5 + 5.75 MHz

1 0 6.0 MHz

1 1 5.5 MHz

0 0 5.25 MHz

0 1 4.44 + 4.64 MHz

1 0 4.84 MHz

1 1 4.44 MHz

Notch

Frequency

Code 01 (for T1, T2) is used to widen the band rejection

where stereo is in use. Typical rejection is 30 dB.

ACC and PAL/NTSC Decoder

The chroma filter bandpass characteristics (3.58 or

4.43 MHz) is determined by the selected crystal. The output

of the chroma filter is sent to the ACC circuit which detects

the burst signal, and provides automatic gain control once

the crystal oscillator has achieved phase lock–up to the

burst. The dc voltage at Pin 2 is ≈ 1.5 to 2.0 V . This will occur

if the burst amplitude exceeds 30 mVpp, and if the correct

crystal is selected (Bit $7A–7). A 17.734472 MHz crystal is

required for PAL, and a 14.31818 MHz crystal is required for

NTSC. When Flag 23 is high, it indicates that the crystal’s

PLL has locked up, and the ACC circuit is active, providing

automatic gain control. A small amount of phase adjustment

(≈±5°) of the crystal PLL, for color correction, can be made

with control DAC $79–5/0. Pin 2 is the filter for the ACC loop,

and Pin 44 is the filter for the crystal oscillator PLL.

The PAL/NTSC decoder then determines if the signal is

PAL or NTSC by looking for the alternating phase

characteristic of the PAL burst. When Flag 24 is high, PAL

has been detected. Bits SSA, SSB, SSC, and SSD (Table 4)

must then be sent to the decoder to set the appropriate

decoding method.

T able 4. Color System Select

SSA

($7C–6)

0 0 0 0 Not Used

0 1 0 0 PAL

1 0 0 0 NTSC

1 1 0 0 Color Kill

X X 1 0 External

SSB

($7D–6)

SSC

($7C–7)

SSD

($7A–6)

Color

System

Upon receiving the SSA to SSD bits, the decoder provides

the correct color difference signals, and with the Identification

circuit, provides the correct level at the System Select output

(Pin 34). This output is used by the MC44140 delay line.

The color kill setting (SSA = SSB = 1) should be used

when the ACC flag is 0, when the color system cannot be

properly determined, or when it is desired to have a

black–and–white output (the ACC circuit and flag will still

function if the input signal has a burst signal). The “External”

setting (SSC = 1) is used when an external (alternate) source

of color difference signals are applied to the MC44140 delay

line. (See Miscellaneous Applications Information for more

details.)

Color Difference Controls and Outputs

The color difference signals (R–Y, B–Y) from the

PAL/NTSC decoder are directed to the saturation, hue and

color balance controls, and then through a series of notch

filters before being output at Pins 41 and 42. Blanking and

clamping are applied to these outputs.

The saturation control DAC($87–5/0) varies the amplitude

of the two signals from 0 Vpp (DAC setting = 00), to a

maximum of ≈ 1.8 Vpp (at a DAC setting of 63). The

maximum amplitude (without clipping) is ≈ 1.5 Vpp, but a

nominal setting is ≈ 1.3 Vpp at a DAC setting of 15.

The hue control ($88–5/0) varies the relative amplitude of

the two signals to provide a hue adjustment. The nominal

setting for this DAC is 32.

The color balance control ($78–5/0) provides a fine

adjustment of the relative amplitude of the two outputs. This

provides for a more accurate color setting, particularly when

NTSC signals are decoded. The nominal setting for this DAC

is 32, and should be adjusted before the hue control is

adjusted.

The notch filters provide filtering at the color burst

frequency, and at 2x and 8x that frequency. Additionally,

blanking and clamping (derived from the horizontal PLL) are

applied to the signals at this stage. The nominal output dc

level is ≈ 2.0 to 2.5 Vdc, and the load applied to these outputs

should be >10 kΩ. Sync is not present on these outputs.

26

MOTOROLA ANALOG IC DEVICE DATA

Page 27

MC44011

Luma Peaking, Delay Line, and Y1 Output

When composite video is applied, the luma information

extracted in the chroma trap is then applied to a stage which

allows peaking at ≈ 3.0 MHz with the 17.7 MHz crystal

(≈ 2.2 MHz with the 14.3 MHz crystal). The amount of

peaking at Y1 is with respect to the gain at the minimum

peaking value (P1, P2, P3 = 111), and is adjustable with

Bits $7D–7, and $7E–7,6 according to Table 5.

The luma delay lines allow for adjustment of that delay so

as to correspond to the chroma delay through this section.

Table 6 indicates the amount of delay using the D1–D3 bits

($7F–7,6, and $80–6). The delay indicated is the total delay

from Pin 1 or 3 to the Y1 output at Pin 33. The amount of

delay depends on whether Composite Video is applied, or YC

signals (S–VHS) are applied.

The output impedance at Y1 is ≈ 300 Ω, and the black level

P1

($7D–7)P2($7E–6)P3($7E–7)

0 0 0 9.5 dB

0 0 1 8.5

1 0 0 7.7

1 0 1 6.5

0 1 0 5.3

0 1 1 3.8

1 1 0 2.2

1 1 1 0

17.7 MHz Crystal, 6.5 MHz Sound Trap, Composite V ideo Mode

T able 5. Luma Peaking

clamp is at ≈ 1.1 V. Sync is present on this output. Y1 is also

internally routed to the color difference stage.

T able 6. Luma Delay

14.3 MHz Crystal 17.7 MHz Crystal

D1

($7F–6)D2($80–6)

0 0 0 690 ns 395 ns 594 ns 350 ns

0 0 1 760 465 650 406

0 1 0 830 535 707 463

0 1 1 900 605 763 519

1 0 0 970 675 819 575

1 0 1 1040 745 876 632

1 1 0 970 675 819 575

1 1 1 1040 745 876 632

D3

($7F–7)

Comp. Video

($77–7 = 0)

S–VHS

($77–7 = 1)

Composite Video

($77–7 = 0)

Y1

Peaking

S–VHS

($77–7 = 1)

Color Difference Stage and RGB/YUV Outputs

A block diagram of this section is shown in Figure 36. This

section’s function is to take the color difference input signals

(Pins 30, 31), or the RGB inputs (Pins 26 to 28), and output

the information at Pins 20 to 22 as either RGB or YUV.

The inputs (on the left side of Figure 36) are analog RGB,

or color difference signals (R–Y and B–Y) with Y1 or Y2 as

the luma component. Pin 25 (Fast Commutate) is a logic level

T able 7. Color Difference Input/Output Selection

RGB EN

FC

1 0 0 0 RGB inputs, RGB outputs, no saturation control

1 0 1 0 RGB inputs, RGB outputs, with saturation control

1 0 1 1 RGB inputs, YUV outputs, with saturation control

1 0 0 1 Not usable

FC Low and/or

RGB EN

FC Low and/or

RGB EN Hi

$80–7

Hi

YX EN

$82–6

X 0 R–Y, B–Y inputs, RGB outputs. Y1 or Y2 must be selected

X 1 R–Y, B–Y inputs, YUV outputs. Y1 or Y2 must be selected

YUV EN

$82–7

input, used in conjunction with RGB EN

(Bit $80–7), to select

the RGB inputs or the color difference inputs. The outputs

(Pins 20 to 22) are either RGB or YUV, selected with

Bit $82–7. The bit numbers adjacent to the various switches

and gates indicate the bits used to control those functions.

Table 7 indicates the modes of operation.

Function

MOTOROLA ANALOG IC DEVICE DATA

27

Page 28

MC44011

In addition to Table 7, the following guidelines apply:

a. To select the RGB inputs, both FC must be high and

RGB EN

must be low. Therefore, the RGB inputs can

be selected either by the I2C bus by leaving FC

permanently high, or by the FC input by leaving

Bit $80–7 permanently low. For overlay functions,

where high speed, well controlled switching is

necessary, the FC pin must be the controlling input.

b. When the R–Y, B–Y inputs are selected, either Y1 or Y2

must be selected, and the other must be deselected.

The YX input is automatically disabled in this mode.

c. In applications where the color difference inputs are

obtained from the NTSC/PAL decoder (from a

composite video signal), Y1 is used. The Y2 input is

normally used where alternately sourced color

difference signals are applied, either through the

MC44140 delay line, or through other external switching

to Pins 30 and 31.

In Figure 36, the bit numbers followed by “–0/5” indicate

DAC operated controls (contrast, brightness, etc.), which are

controlled by the I2C bus. The DACs have 6–bit resolution,

allowing 64 adjustment steps. Table 8 provides guidelines on

the DAC operation.

Table 8. DAC Operation – Color Difference Section

Function Bits RGB Outputs ($82–7 = 0) YUV Outputs ($82–7 = 1)

Brightness $84–0/5 Affects dc black and maximum levels of the three

∆ DC – Red

∆ DC – Blue

Contrast $81–0/5 Provides gain adjustment (black–to–white) of the

∆ Gain – Red

∆ Gain – Blue

V DC

U DC

Main Saturation $86–0/5 Affects color saturation, except when the RGB

$85–0/5

$83–0/5

$82–0/5

$80–0/5

$7E–0/5

$7D–0/5

outputs, but not the clamp level, nor the amplitude.

Fine tune the Red and Blue brightness levels. Allows a small amount of color tint control (not to

three outputs.

Fine tune the Red and Blue contrast levels. Fine tune of the U and V gain levels.

Must be set to 00. Should nominally be set to 32. This sets the dc

inputs bypass this section (YX EN = 0).

Affects dc black and white levels of the Y output

only, but not the clamp level, nor the amplitude.

be confused with hue).

Provides gain adjustment of the three outputs.

level of the U and V outputs at ≈ mid–scale.

Affects color saturation levels of the UV outputs.

Does not affect the Y output.

Inputs

R

G

B

R–Y

B–Y

Y2

F/C

C

28

C

27

26

C

31

C

C

30

29

C

(From Decoder)

25

YX

$81–7

$81–6

Y1

$80–7

Matrix

Decoder

$82–6

Figure 36. Color Difference Stage and Outputs

Contrast

$81–0/5

$82–0/5

Main Saturation

$86–0/5

R–YB–YYX

R–Y

G–Y

B–Y

Y

R

G

B

$82–7

NOTES:

Brightness

$84–0/5

$82–7

∆

∆

Gain

∆

($80–0/5)

1. = Clamp Circuit

C

2. Switches controlled by

I2C Interface – See Text.

DC ($85–0/5)

V DC ($7E–0/5)

∆

DC ($83–0/5)

Gain

U DC ($7D–0/5)

20

21

22

5.0

R/V

5.0

G/Y

5.0

B/U

390

390

390

Ω

Ω

Outputs

Ω

28

MOTOROLA ANALOG IC DEVICE DATA

Page 29

MC44011

The RGB and Y2 inputs are designed to accept standard

1.0 Vpp analog video signals. They are not designed for TTL

level signals. The color difference inputs are designed to

accept signals ranging up to 1.8 Vpp. All signals are to be

capacitor–coupled as clamping is provided internally. Input

impedance at these six pins is high.

For applications involving externally supplied color

difference signals, sync can be supplied on the luma input

(Y2), or it can be supplied separately at the RGB inputs.

Where the color difference signals are obtained from the

NTSC/PAL decoder, sync is provided to this section on the

internal Y1 signal. See Sync Separator section for more

details on injecting sync into the MC4401 1.

Sync is present on all three outputs in the RGB mode, and

on the Y output only (Pin 21) in the YUV mode.

The Fast Commutate input (FC, Pin 25) is a logic level

input with a threshold at ≈ 0.5 V. Input impedance is ≈ 67 kΩ,

and the graph of Figure 24 shows the input current

requirements. Propagation delay from the FC pin to the

RGB/YUV outputs is ≈ 50 ns when enabling the RGB inputs,

and ≈ 90 ns when disabling the inputs. (See Figure 29 Fast

Commutate Timing diagram.) If Pin 25 is open, that is

equivalent to a Logic 1, although good design practices

dictate that inputs should never be left open. The voltage on

this pin should not be allowed to go more than 0.5 V above

V

or below ground.

CC2

The three outputs (Pins 20 to 22) are open–collector,

requiring an external pull–up. A representative schematic is

shown in Figure 37.

The output amplitude can be varied from 100 mVpp to

3.0 Vpp by use of the contrast and saturation controls. Any

output load to ground should be kept larger than 1.0 kΩ. In

the RGB mode, DACs $7D and $7E should be set to 00,

which results in clamping levels of ≈ 1.4 Vdc. In the YUV

mode, DACs $7D and $7E should be set to 00, which results

Figure 37. Output Stage

∆

DC

5.0

36 k

5.0

390

Output

Color or

Color Diff

Contrast

∆

Gain

Brightness

in clamping levels of ≈ 1.4 Vdc. In the YUV mode, the DACs

should be set to 32 to bias the U and V outputs to ≈ 2.3 V. The

Y output clamp will remain at ≈ 1.4 V in the YUV mode.

Horizontal PLL (PLL1)

PLL1 (shown in Figure 38) provides several outputs which

are phase–locked to the incoming horizontal sync. In normal

operation, the two switches at the left side of Figure 38 are as

shown, and (usually) the transistor at Pin 12 is off.

The phase detector compares the incoming sync (from the

sync separator) to the frequency from the ÷ 64 block. The

phase detector’s output, filtered at Pin 11, controls the VCO

to set the correct frequency (≈ 1.0 MHz) so that the output of

the ÷ 64 is equal to the incoming horizontal frequency.

The line–locked outputs are:

1) Fh Ref (Pin 14) – A square wave, TTL levels, at the

horizontal frequency, and phase–locked to the sync

source according to the timing diagram of Figures 25

and 27.

2) Burst Gate (Pin 8) – This is a positive going pulse, TTL

levels, coincident with the burst signal. See the timing

diagram of Figures 25 and 27.

Frequency

Divider

4.43 MHz/

3.58 MHz

SC

$78–6

525/625

($84–6)

$86–6

Frequency

Comparator

Up/Down

Converter

VCO

From Sync

Separator

Figure 38. Horizontal PLL (PLL1)

Calibration Loop

Counter

D–to–A

1.0 MHz

16Fh

13 11

16Fh/

C

Sync

Divide By 64

$85–6

Frame

I

ref

Burst

Gate

358

S/C

OutFhRef

f

H

Horiz Sync

14

from Sync

Separator

Phase

Det 1

H Filter

To PLL #2

Flag 12

(Horizontal not locked)

Coincidence

Detector

L1 Gain

$83–6

Gate

$77–2

$84–7

12

H Filter

Switch

MOTOROLA ANALOG IC DEVICE DATA

29

Page 30

MC44011

3) Sandcastle Output (Pin 35) – This is a multilevel

output, at the horizontal frequency, used by the

MC44140 delay line. See the timing diagram of

Figures 25 and 27.

4) 16Fh/C

TTL levels, user selectable. When Bit $85–6 is set to 0,

Pin 13 is a square wave at 16x the horizontal frequency

(250 kHz for PAL, ≈ 252 kHz for NTSC). When Bit $85–6

is set to 1, Pin 13 is negative composite sync, derived

from the internal sync separator. See the timing diagram

of Figures 25 and 27.

The first three outputs mentioned above, and Pin 13 when

set to 16Fh, are consistent, and do not change duty cycle or

wave shape during the vertical sync interval. These four

outputs will also be present regardless of the presence of a

video signal at the selected input.

When Pin 13 is set to C

composite sync format. If there is no video signal present at

the selected input, this output will be a steady logic high.

Loading on these pins should not be less than 2.0 kΩ to

either ground or 5.0 V.

Pin 11 is the filter for the PLL, and requires the

components shown in Figure 38, and with the values shown

in the application circuit of Figure 42. Pin 12 is a switch which

allows the filtering characteristics at Pin 11 to be changed.

Switching in the additional components (set $84–7 = 1)

increases the filter time constant, permitting better

performance in the presence of noisy signals.

The gain of the phase detector may be set high or low,

depending on the jitter content of the incoming horizontal

frequency, by using Bit $83–6. Broadcast signals usually

have a very stable horizontal frequency, in which case the

low gain setting ($83–6 = 0) should be used. When the video

source is, for example, a VCR, the high gain setting may be

preferable to minimize instability artifacts which may show up

on the screen.

The gating function ($77–2) provides additional control

where the stability of the incoming horizontal frequency is in

question. With this bit set to 0, gating is in effect, causing the

phase detector to not respond to the incoming sync pulses

during the vertical interval. This reduces disturbances in this

PLL due to the half–line pulses and their change in polarity.

The gating may be disabled by setting this bit to 1 where the

timing of the incoming sync is known to be stable. The gating

cannot be enabled if the phase detector gain is set high

($83–6 = 1).

Calibration Loop

The calibration loop (upper left portion of Figure 38)

maintains a near correct frequency of this PLL in the absence

of incoming sync signals. This feature minimizes

re–adjustment and lock time when sync signals are

re–applied. The calibration loop is similar to the PLL function,

receiving one frequency from the crystal (either 4.43 MHz or

3.58 MHz) divided down to a frequency similar to the

standard horizontal frequency. Bit $84–6 is used to set the

frequency divider to the correct ratio, depending on which

crystal is selected (see Table 9). The output of the frequency

comparator operates an up/down counter, which in turn sets

(Pin 13) – This is a dual purpose output,

Sync

output, it follows the incoming

Sync

the D–to–A converter to drive the VCO through switch Sc.

The resulting frequency at the output of the divide–by–64

block is then fed to the frequency comparator to complete

the loop.

When a sync signal is not present at Phase Detector #1,

and at the Coincidence Detector, as indicated by the

coincidence detector’s output (Flag 12), Bit $78–6 should be

set to 0. This will cause the switch (Sc) to transfer to the

D–to–A converter for two lines (lines 4, 5) in each vertical

field, and will maintain the PLL1 at a frequency near the

standard horizontal frequency (between 14 to 16 kHz). When

lock to an incoming sync is established, Bit $78–6 may be set

to 1, disabling the periodic recalibration function, or it may be

left set to 0.

If a more accurate horizontal frequency is desired in the

absence of an input signal, Bit $86–6. can be set to 1 (and

Bit $84–6 set according to Table 9). This holds the horizontal

frequency to ≈ 15.7 kHz. In this mode, Flag 12 will stay 0, as

the PLL will not be able to lock–up to a newly applied external

signal. To reset the system, set $86–6 to 0, write $00 to

register $00, and then check Flag 12 to determine when the

loop locks to an incoming signal.

T able 9. Calibration Loop

Crystal Set Bit $84–6 to

14.3 MHz 1

17.7 MHz 0

On initial power up, Bit $86–6 (PLL1 EN) is automatically

set to 1, engaging the calibration loop continuously. This

condition will remain until this bit is set to 0, and $00 is written

to register $00, as part of the initialization routine.

Pixel Clock PLL (PLL2)

The second PLL, depicted in Figure 39, generates a high

frequency clock which is phase–locked to the horizontal

frequency.

Figure 39. Pixel Clock PLL (PLL2)

fH from PLL1

Phase and

Frequency

Comparator

Up

Down

15 k

Return

15625 Hz or

15750 Hz

L2 Gain

$83–7

Charge

Pump

Voltage

Monitor

16 1815

VCO Gain

$7F–5/0

PLL2 Filter

Flag 19 (VCO HI)

Flag 20 (VCO LO)

B

2VCO

Frequency

Divider

$85–7

Pixel

Clock

30

MOTOROLA ANALOG IC DEVICE DATA

Page 31

MC44011

The phase and frequency comparator receive inputs from

PLL1 (fH, the horizontal frequency), and the frequency

returned from the external divider. Any difference between

these two signals causes the Up or Down output to change

the charge pump’s timing. The charge pump output is

composed of two equal current sources which alternately

source and sink current to the filter at Pin 16. The voltage at

Pin 16 (which is the input to the VCO) is therefore determined

by the relative timing of those two current sources, and the

filter characteristics. A coarse control of the loop gain is set

with Bit $83–7. Low gain is obtained by setting this bit to a 1,

which sets the charge pump’s output current sources to

≈±20 µA. Setting this bit to 0 sets the current sources to

≈±50 µA, or high gain.

Depending on the output frequency desired, and whether

or not a 50–50 square wave is needed at the pixel clock, the

÷ 2 may be engaged (Bit $85–7). Generally, the ÷ 2 should

not be engaged for high frequencies, and should be engaged

for low frequencies, so as to keep the VCO’s input voltage in

a comfortable range (between 1.7 and 3.3 V). If the input

voltage is outside this range, Flag 19 or 20 will switch high,

indicating the need to fine tune the VCO’s gain (control DAC

$7F). The usable adjustment range for this DAC is 00 to ≈ 50.

Settings of 51 to 62 will generally produce non–square wave

outputs, and can be unstable. A setting of 63 will shut off the

VCO, which should be done if the pixel clock is not used.

When not used, Pin 18 will be at a constant low level.

The pixel clock frequency is equal to the horizontal

frequency (fH) x the frequency divider ratio. The frequency

divider can be made up of programmable counters (e.g.,

MC74F161A Applications Information), or it can be

integrated into another device (e.g., an ASIC). The returned

signal to Pin 15 must be TTL/CMOS logic levels, and must

have a low time of > 200 ns. The phase comparator will

phase–lock the falling edge of the returned signal with the